(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6017476号

(P6017476)

(45) 発行日 平成28年11月2日(2016.11.2)

(24) 登録日 平成28年10月7日(2016.10.7)

(51) Int.Cl.

G06F 1/32 (2006.01)

F 1

G06F 1/32

Z

請求項の数 27 (全 26 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2014-34243 (P2014-34243)    |

| (22) 出願日     | 平成26年2月25日(2014.2.25)         |

| (65) 公開番号    | 特開2014-182801 (P2014-182801A) |

| (43) 公開日     | 平成26年9月29日(2014.9.29)         |

| 審査請求日        | 平成26年2月25日(2014.2.25)         |

| 審判番号         | 不服2015-22309 (P2015-22309/J1) |

| 審判請求日        | 平成27年12月18日(2015.12.18)       |

| (31) 優先権主張番号 | 13/835, 275                   |

| (32) 優先日     | 平成25年3月15日(2013.3.15)         |

| (33) 優先権主張国  | 米国(US)                        |

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 593096712<br>インテル コーポレイション<br>アメリカ合衆国 95054 カリフォルニア州 サンタクララ ミッション カレッジ ブールバード 2200 |

| (74) 代理人  | 100107766<br>弁理士 伊東 忠重                                                             |

| (74) 代理人  | 100070150<br>弁理士 伊東 忠彦                                                             |

| (74) 代理人  | 100091214<br>弁理士 大貫 進介                                                             |

| (72) 発明者  | マヘシュ ワーグ<br>アメリカ合衆国 97229 オレゴン州 ポートランド ノースウェスト ホーガン ストリート 13527                    |

最終頁に続く

(54) 【発明の名称】ルートポート及びRPIE (Root Port Integrated End point) のレジューム時間を向上させるための方法、装置及びシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

デバイスが低電力状態にあると判断し、

前記低電力状態からアクティブ状態への前記デバイスの遷移を開始し、

前記低電力状態から前記アクティブ状態への前記デバイスの遷移に対応する前記デバイスに固有のインタラプト能力とレジューム時間能力とがサポートされているか特定し、

前記サポートされている前記デバイスに固有のインタラプト能力とレジューム時間能力とに少なくとも部分的に基づき前記低電力状態から前記アクティブ状態への前記デバイスの遷移を完了させるリカバリロジックを有する装置であって、

前記低電力状態から前記アクティブ状態への遷移について固定的な最小リカバリ時間が規定され、 10

前記遷移は、前記サポートされている前記デバイスに固有のインタラプト能力とレジューム時間能力との1つ以上に基づき、前記固定的な最小リカバリ時間の経過前に完了される装置。

## 【請求項 2】

前記リカバリロジックはさらに、前記デバイスからインタラプトを受信し、

前記インタラプトは、前記デバイスが前記遷移を完了する準備ができているという通知である、請求項1記載の装置。

## 【請求項 3】

前記リカバリロジックはさらに、前記インタラプトについて前記デバイスをモニタリン 20

グする、請求項 2 記載の装置。

【請求項 4】

前記リカバリロジックは、前記インターラプトが前記規定されたリカバリ時間前に受信されなかった場合、前記デバイスについて規定されたリカバリ時間に従って前記遷移を完了させる、請求項 3 記載の装置。

【請求項 5】

前記規定されたリカバリ時間は、前記固定的な最小リカバリ時間を含む、請求項 4 記載の装置。

【請求項 6】

前記規定されたリカバリ時間は、前記デバイスに固有の通知されたリカバリ時間有する、請求項 4 記載の装置。 10

【請求項 7】

前記レジューム時間能力は、前記デバイスについて通知されたリカバリ時間有し、

前記通知されたリカバリ時間は、前記固定的な最小リカバリ時間より短い、請求項 1 記載の装置。

【請求項 8】

前記リカバリロジックはさらに、前記固定的な最小リカバリ時間の代わりに、前記低電力状態から前記アクティブ状態への前記デバイスの遷移に対して、前記通知されたリカバリ時間を適用する、請求項 7 記載の装置。

【請求項 9】

前記リカバリロジックはさらに、前記低電力状態から前記アクティブ状態への他のデバイスの遷移において、前記他のデバイスに対して前記固定的な最小リカバリ時間を適用する、請求項 8 記載の装置。 20

【請求項 10】

前記デバイスは、PCIe (Peripheral Component Interconnect Express) に準拠したデバイスを含む、請求項 1 記載の装置。

【請求項 11】

前記低電力状態は D3 状態を含み、前記アクティブ状態は D0 状態を含む、請求項 10 記載の装置。 30

【請求項 12】

前記低電力状態から前記アクティブ状態への前記デバイスの遷移の完了は、前記デバイスにコンフィギュレーションアクセスリクエストを送信することを含む、請求項 1 記載の装置。

【請求項 13】

前記デバイスは、ルートポート、ダウンストリームポート又は RCIE (Root Complex Integrated Endpoint) の少なくとも 1 つを含む、請求項 1 記載の装置。

【請求項 14】

少なくとも 1 つのデバイスの電力管理能力を規定する電力管理能力構造を格納する機械可読メモリと、 40

前記電力管理能力構造から前記デバイスに固有のインターラプト能力とレジューム時間能力とがサポートされているか特定し、前記サポートされている前記デバイスに固有のインターラプト能力とレジューム時間能力とに少なくとも部分的に基づき、低電力状態からアクティブ状態への前記デバイスの遷移を完了させる電力管理コントローラと、

を有する装置であって、

前記遷移は、前記サポートされている前記デバイスに固有のインターラプト能力とレジューム時間能力との 1 つ以上に基づき、前記低電力状態から前記アクティブ状態への遷移について規定された固定的な最小リカバリ時間の経過前に完了される装置。

【請求項 15】

前記電力管理能力構造は、前記デバイスについて他のリカバリ時間が通知されているか 50

前記デバイスについて規定する、請求項 1 4 記載の装置。

【請求項 1 6】

前記電力管理能力構造は、前記固定的な最小リカバリ時間より短い前記デバイスの他のリカバリ時間を規定する、請求項 1 5 記載の装置。

【請求項 1 7】

前記電力管理コントローラは、前記低電力状態から前記アクティブ状態への前記デバイスの遷移を完了させるため、前記他のリカバリ時間を適用する、請求項 1 6 記載の装置。

【請求項 1 8】

前記電力管理コントローラは、他のリカバリ時間が通知されていない場合、前記固定的な最小リカバリ時間を適用する、請求項 1 5 記載の装置。 10

【請求項 1 9】

前記電力管理能力構造は、前記デバイスによりインタラプトがサポートされているか前記デバイスについて規定し、

前記電力管理コントローラは、前記デバイスからの前記インタラプトの受信に基づき、前記低電力状態から前記アクティブ状態への前記デバイスの遷移を完了させる、請求項 1 4 記載の装置。 11

【請求項 2 0】

前記電力管理コントローラは、前記デバイスが前記インタラプトをサポートしていることを前記電力管理能力構造が示す場合、前記デバイスを前記インタラプトについてモニタリングする、請求項 1 9 記載の装置。 20

【請求項 2 1】

デバイスが低電力状態にあると判断するステップと、

前記低電力状態からアクティブ状態への前記デバイスの遷移を開始するステップであって、前記低電力状態から前記アクティブ状態への遷移について固定的な最小リカバリ時間が規定される、開始するステップと、

前記低電力状態から前記アクティブ状態への前記デバイスの遷移に対応する前記デバイスに固有のインタラプト能力とレジューム時間能力とがサポートされているか特定するステップと、

前記サポートされている前記デバイスに固有のインタラプト能力とレジューム時間能力とに少なくとも部分的にに基づき、前記低電力状態から前記アクティブ状態への前記デバイスの遷移を完了するステップであって、前記遷移は、前記サポートされている前記デバイスに固有のインタラプト能力とレジューム時間能力との 1 つ以上に基づき、前記固定的な最小リカバリ時間の経過前に完了される、完了するステップと、

を有する方法。 30

【請求項 2 2】

前記デバイスからインタラプトを受信するステップを更に有し、

前記インタラプトは、前記デバイスが前記遷移を完了する準備ができているという通知である、請求項 2 1 記載の方法。

【請求項 2 3】

前記レジューム時間能力は、前記デバイスについて通知されたリカバリ時間を含み、 40

前記通知されたリカバリ時間は、前記固定的な最小リカバリ時間より短い、請求項 2 1 記載の方法。

【請求項 2 4】

前記低電力状態から前記アクティブ状態への前記デバイスの遷移を開始するステップは、前記デバイスに電力を提供することを含む、請求項 2 1 記載の方法。

【請求項 2 5】

デバイスと、

前記デバイスに通信接続される電力管理コントローラと、

を有するシステムであって、

前記電力管理コントローラは、 50

前記デバイスが低電力状態にあると判断し、

前記低電力状態からアクティブ状態への前記デバイスの遷移を開始し、

前記低電力状態から前記アクティブ状態への前記デバイスの遷移に対応する前記デバイスに固有のインタラプト能力とレジューム時間能力とがサポートされているか特定し、

前記サポートされている前記デバイスに固有のインタラプト能力とレジューム時間能力とに少なくとも部分的に基づき、前記低電力状態から前記アクティブ状態への前記デバイスの遷移を完了し、

前記低電力状態から前記アクティブ状態への遷移について固定的な最小リカバリ時間が規定され、

前記遷移は、前記サポートされている前記デバイスに固有のインタラプト能力とレジューム時間能力との1つ以上に基づき、前記固定的な最小リカバリ時間の経過前に完了されるシステム。 10

#### 【請求項 26】

前記デバイスは、ルートポートを含む、請求項 25 記載のシステム。

#### 【請求項 27】

前記デバイスは、R C I E ( R o o t C o m p l e x I n t e g r a t e d E n d p o i n t ) を含む、請求項 25 記載のシステム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本開示は、計算システムに関し、特に（限定することなく）ルートポート及びルートポートが搭載されたエンドポイント（R P I E）に関する。 20

##### 【背景技術】

##### 【0002】

ユーザの日常生活において電子装置がより複雑になり、ユビキタスなものになるに従って、それらに対してより多様な要求が求められる。これらの要求の多くを充足するため、多くの電子装置は、C P U、通信デバイス、グラフィックアクセラレータなどの多数の異なるデバイスを有することになる。多くの状況では、これらのデバイスの間の通信量が多くなる可能性がある。さらに、多くのユーザは装置のパフォーマンスに関して高い期待を有している。ユーザは、自分の装置により処理が実行されることを待機するのにあまり寛容でなくなりつつある。さらに、多くの装置は、かなりの量のデバイス間通信に伴うより複雑かつ負担の大きなタスクを実行している。 30

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0003】

従って、本発明の1つの課題は、迅速なレスポンス時間を可能にするデバイス間の通信を可能にすることである。

##### 【課題を解決するための手段】

##### 【0004】

上記課題を解決するため、本発明の一態様は、デバイスが低電力状態にあると判断し、前記低電力状態からアクティブ状態への前記デバイスの遷移を開始し、前記低電力状態から前記アクティブ状態への前記デバイスの遷移に対応する前記デバイスの能力を特定し、前記能力に少なくとも部分的に基づき前記低電力状態から前記アクティブ状態への前記デバイスの遷移を完了させるリカバリロジックを有する装置であって、前記低電力状態から前記アクティブ状態への遷移について固定的な最小リカバリ時間が規定され、前記遷移は、前記固定的な最小リカバリ時間の経過前に完了される装置に関する。 40

##### 【発明の効果】

##### 【0005】

本発明によると、迅速なレスポンス時間を可能にするデバイス間の通信を可能にすることができる。

10

20

30

40

50

**【図面の簡単な説明】**

**【0006】**

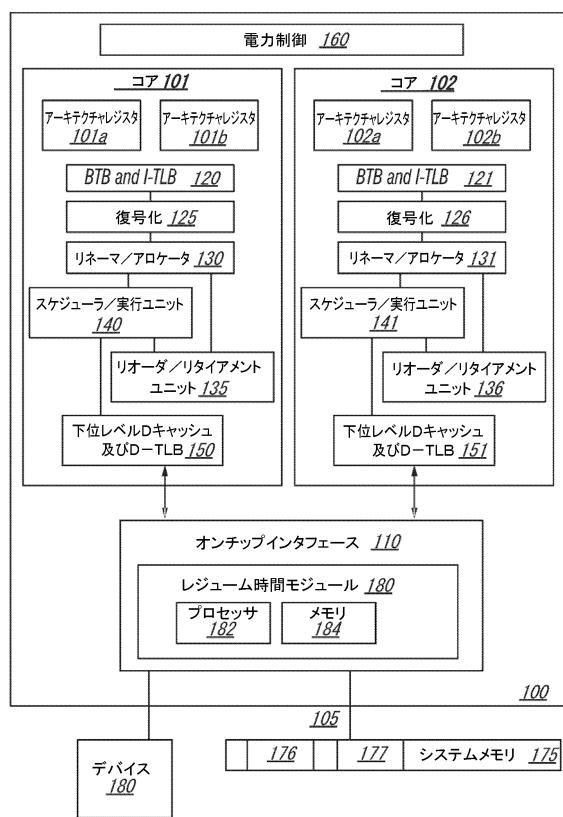

【図1】図1は、少なくとも1つの実施例によるマルチコアプロセッサを有する計算システムのブロック図の一実施例を示す。

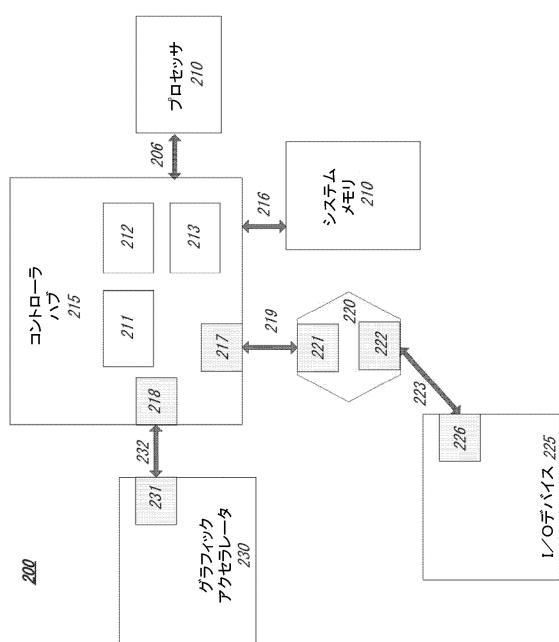

【図2】図2は、少なくとも1つの実施例によるインターネットアーキテクチャを有する計算システムの一実施例を示す。

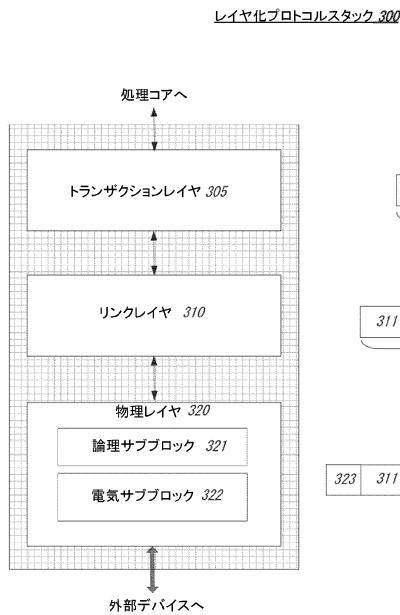

【図3】図3は、少なくとも1つの実施例によるレイヤ化スタックを有するインターネットアーキテクチャの一実施例を示す。

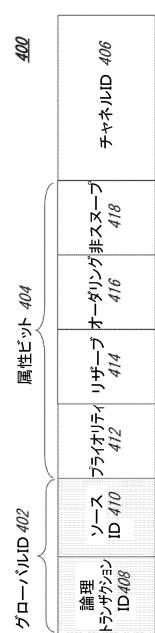

【図4】図4は、少なくとも1つの実施例によるインターネットアーキテクチャ内で生成又は受信されるリクエスト又はパケットの一実施例を示す。 10

【図5】図5は、少なくとも1つの実施例によるインターネットアーキテクチャの送信機及び受信機のペアの一実施例を示す。

【図6】図6は、一例となる電力管理状態遷移図を示す。

【図7】図7は、少なくとも1つの実施例によるフロー図である。

【図8】図8は、少なくとも1つの実施例によるフロー図である。

【図9】図9は、少なくとも1つの実施例によるフロー図である。

【図10】図10は、計算システムのブロック図の他の実施例を示す。

**【発明を実施するための形態】**

**【0007】**

以下、図面に基づいて本発明の実施の形態を説明する。 20

**【0008】**

以下の説明では、特定のタイプのプロセッサ及びシステムコンフィギュレーション、特定のハードウェア構造、特定のアーキテクチャ及びマイクロアーキテクチャの詳細、特定のレジスタコンフィギュレーション、特定の命令タイプ、特定のシステムコンポーネント、特定の測定／高さ、特定のプロセッサバイオペラインステージ及び処理などの多数の具体的な詳細が、本発明の完全な理解を提供するため与えられる。しかしながら、これらの具体的な詳細が本発明を実現するのに利用される必要がないことは明らかであろう。他の例では、特定の他のプロセッサアーキテクチャ、説明されたアルゴリズムのための特定の論理回路／コード、特定のファームウェアコード、特定のインターネット処理、特定のロジックコンフィギュレーション、特定の製造技術及び物質、特定のコンパイラ実装、特定のコードによるアルゴリズムの表現、特定の電力ダウン及びゲート化技術／ロジック及びコンピュータシステムの他の特定の処理の詳細などの周知のコンポーネント又は方法は、本発明を不要に不明瞭にすることを回避するため詳細には説明されない。 30

**【0009】**

以下の実施例は計算プラットフォーム又はマイクロプロセッサなどにおけるルートポート及びルートポートが搭載されたエンドポイントのレジューム時間の向上を参照して説明されるが、他の実施例は、他のタイプの集積回路及びロジックデバイスに適用可能である。ここに説明される実施例の同様の技術及び教示は、レジューム時間の向上を享受する他のタイプの回路又は半導体デバイスに適用されてもよい。例えば、開示される実施例は、デスクトップコンピュータシステム又はUltrabooks<sup>TM</sup>に限定されるものではなく、携帯デバイス、タブレット、他のシンノートブック、SOC(System On Chip)デバイス及び埋め込みアプリケーションなどの他のデバイスにおいて利用されてもよい。携帯デバイスのいくつかの具体例は、携帯電話、インターネットプロトコルデバイス、デジタルカメラ、PDA(Personal Digital Assistant)及び携帯PCを含む。埋め込みアプリケーションは、典型的には、マイクロコントローラ、デジタル信号プロセッサ(DSP)、SOC、ネットワークコンピュータ(Network PC)、セットトップボックス、ネットワークはぶ、WAN(Wide Area Network)スイッチ、又は後述される機能及び処理を実行可能な他の何れかのシステムを含む。さらに、ここに説明される装置、方法及びシステムは、物理的な計算デバイスに限定されず、レジューム時間を向上させるためのソフトウェア最適化に関するものであ 40

つてもよい。

#### 【0010】

図1は、少なくとも1つの実施例によるルートポート及びルートポートを搭載したエンドポイント（R P I E）のレジューム時間の向上に関連するコンポーネントを示すブロック図である。図1の具体例は、ルートポート及びルートポートを搭載したエンドポイントのレジューム時間の向上に関連するコンポーネントの単なる一例であり、請求項の範囲を限定するものでない。例えば、コンポーネントに帰属する処理は可変的であり、コンポーネントの個数も可変的であり、コンポーネントの合成も可変的である。例えば、いくつかの実施例では、図1の具体例の1つのコンポーネントに帰属可能な処理は、1以上の他のコンポーネントに配分されてもよい。

10

#### 【0011】

プロセッサ100は、マイクロプロセッサ、埋め込みプロセッサ、デジタル信号プロセッサ（D S P）、ネットワークプロセッサ、携帯プロセッサ、アプリケーションプロセッサ、コプロセッサ、S O C又はコードを実行する他のデバイスなどの何れかのプロセッサ又は処理デバイスを含む。一実施例では、プロセッサ100は、非シンメトリックコア又はシンメトリックコア（図示された実施例）を含むものであってもよい少なくとも2つのコア101，102を有する。しかしながら、プロセッサ100は、シンメトリック又は非シンメトリックな何れかの個数の処理要素を含むものであってもよい。

#### 【0012】

一実施例では、処理要素は、ソフトウェアスレッドをサポートするハードウェア又はロジックを表す。ハードウェア処理要素の具体例として、スレッドユニット、スレッドスロット、スレッド、プロセスユニット、コンテクスト、コンテクストユニット、論理プロセッサ、ハードウェアスレッド、コア及び／又は実行状態又はアーキテクチャ状態などのプロセッサの状態を保持可能な他の何れかの要素があげられる。すなわち、一実施例では、処理要素は、ソフトウェアスレッド、オペレーティングシステム、アプリケーション又は他のコードなどのコードに独立に関連付け可能な何れかのハードウェアを表す。物理プロセッサ（又はプロセッサソケット）は、典型的には、コア又はハードウェアスレッドなどの何れかの個数の他の処理要素を含むものであってもよい集積回路を表す。

20

#### 【0013】

コアは、しばしば独立したアーキテクチャ状態を維持可能な集積回路に配置されるロジックを表し、独立して維持される各アーキテクチャ状態は、少なくともいくつかの専用の実行リソースに関連付けされる。コアと対照的に、ハードウェアスレッドは、典型的には、独立したアーキテクチャ状態を維持可能な集積回路に配置された何れかのロジックを表し、独立に維持されたアーキテクチャ状態は、実行リソースへのアクセスを共有する。理解できるように、特定のリソースが共有され、他のものがアーキテクチャ状態に専用とされるとき、ハードウェアスレッドとコアとの用語の間には重複がある。また、コアとハードウェアスレッドとはしばしば、オペレーティングシステムが各論理プロセッサ上の処理を個別にスケジューリング可能である場合、個々の論理プロセッサとしてオペレーティングシステムによりみなされる。

30

#### 【0014】

図1に示されるように、物理プロセッサ100は、2つのコア101，102を有する。ここで、コア101，102は、シンメトリックコア、すなわち、同一のコンフィギュレーション、機能ユニット及び／又はロジックを備えたコアとみなされる。他の実施例では、コア101はアウトオブオーダプロセッサコアを有し、コア102はインオーダプロセッサコアを有する。しかしながら、コア101，102は、ネイティブコード、ソフトウェアにより管理されたコア、ネイティブI S A（Instruction Set Architecture）を実行するよう構成されるコア、変換されたI S Aを実行するよう構成されたコア、一緒に設計されたコア又は他の既知のコアなどの何れかのタイプのコアから個別に選択されてもよい。ヘテロジニアスコア環境（すなわち、非シンメトリックコア）では、バイナリ変換などのある変換形態が、一方又は双方のコア上のコアをス

40

50

ケジューリング又は実行するのに利用されてもよい。さらなる説明のため、コア101に示される機能ユニットは、以下においてさらに詳細に説明され、コア102のユニットは、図示された実施例において同様に動作する。

#### 【0015】

図示されるように、コア101は、ハードウェアスレッドスロット101a, 101bとして参照されてもよい2つのハードウェアスレッド101a, 101bを有する。従つて、一実施例では、オペレーティングシステムなどのソフトウェアエンティティは、4つの別個のプロセッサ、すなわち、4つのソフトウェアスレッドを同時に実行可能な4つの論理プロセッサ又は処理要素としてプロセッサ100をみなすことが可能である。上述されるように、第1スレッドはアーキテクチャ状態レジスタ101aに関連付けされ、第2スレッドはアーキテクチャ状態レジスタ101bに関連付けされ、第3スレッドはアーキテクチャ状態レジスタ102aに関連付けされ、第4スレッドはアーキテクチャ状態レジスタ102bに関連付けされてもよい。ここで、各アーキテクチャ状態レジスタ(101a, 101b, 102a, 102b)は、上述されるように、処理要素、スレッドスロット又はスレッドユニットとして参照されてもよい。図示されるように、アーキテクチャ状態レジスタ101aは、アーキテクチャ状態レジスタ101bにおいて複製され、個々のアーキテクチャ状態/コンテキストは、論理プロセッサ101a, 101bのための格納可能である。コア101では、アロケータリネーマブロック103の命令ポインタ及び梨ネーミングロジックなどの他のより小さなリソースがまた、スレッド101a, 101bのために複製されてもよい。リオーダ/リタイアメントユニット135におけるリオーダバッファ、プランチターゲットバッファ(BTB)及び命令変換バッファ(I-TLB)120、ロード/ストアバッファ及びキューなどのいくつかのリソースは、パーティション処理を介し共有されてもよい。汎用内部レジスタ、ページテーブルベースレジスタ、低レベルデータキャッシュ及びデータTLB150、実行ユニット140及びアウトオブオーダユニット135の一部などの他のリソースは、完全に共有される可能性がある。

#### 【0016】

プロセッサ100はしばしば、完全に共有される、パーティション化を介し共有される、又は処理要素に専用であってもよい他のリソースを含む。図1において、プロセッサの例示的な論理ユニット/リソースを備えた一例となるプロセッサの実施例が示される。プロセッサは、これらの機能ユニットの何れかを含む又は省略すると共に、他の何れか既知の図示されない機能ユニット、ロジック又はファームウェアを含むものであってもよいことに留意されたい。図示されるように、コア101は、簡略化された典型的なアウトオブオーダ(OOO)プロセッサコアを有する。しかしながら、インオーダプロセッサは、異なる実施例において利用されてもよい。OOOコアは、実行/選択されるプランチを予測するBTB及びI-TLB120と、命令のためアドレス変換エントリを格納するためのBTB及びI-TLB120とを含む。

#### 【0017】

コア101はさらに、BTB及びI-TLB120に接続され、フェッチされた要素を復号化する復号化モジュール125を有する。一実施例では、フェッチロジックは、スレッドスロット101a, 101bに関連付けされる個々のシーケンサを含む。通常、コア101は、プロセッサ100上で実行可能な命令を規定/指定する第1ISAに関連付けられる。しばしば、第1ISAの一部であるマシーンコード命令は、実行される命令又は処理を参照/指定する命令の一部(オペコードと呼ばれる)を含む。復号化ロジック125は、オペコードから命令を認識し、第1ISAにより規定されるような処理のためのバイナリコードにより復号化された命令をわたす回路を含む。例えば、以下においてより詳細に説明されるように、一実施例では、デコーダ125は、トランザクション命令などの特定の命令を認識するよう設計又は構成されるロジックを含む。デコーダ125による認識の結果として、アーキテクチャ又はコア101は、適切な命令に関連付けされたタスクを実行するため特定の所定のアクションを選択する。ここで説明されたタスク、ブロック、処理及び方法の何れかが、单一の命令、又は一部が新たな又は古い命令であってもよい複

10

20

30

40

50

数の命令に応答して実行されてもよいことに留意することが重要である。一実施例では、デコーダ125は同一のISA(又はそのサブセット)を認識することに留意されたい。あるいは、ヘテロジニアスコア環境では、デコーダ125は第2ISA(第1ISAのサブセット又は異なるISA)を認識する。

#### 【0018】

一例では、リネーマ／アロケータブロック130は、命令処理結果を格納するためのレジスタファイルなど、リソースを確保するためのアロケータを含む。しかしながら、スレッド101a, 101bは、アウトオブオーダ実行が可能であり、アロケータリネーマブロック130はまた、命令結果をトラックするためのリオーダバッファなどの他のリソースを確保する。ユニット130はまた、プログラム／命令リファレンスレジスタをプロセッサ100の内部の他のレジスタにリネーミングするためのレジスタリネーマを有してもよい。リオーダ／リタイアメントユニット135は、アウトオブオーダ命令と、以降のアウトオブオーダに実行された命令のインオーダリタイアメントとをサポートするため、上述したリオーダバッファ、ロードバッファ及びストアバッファなどのコンポーネントを含む。

#### 【0019】

一実施例では、スケジューラ実行ユニットブロック140は、実行ユニット上の命令／処理をスケジューリングするためのスケジューラユニットを有する。例えば、浮動小数点命令は、利用可能な浮動小数点実行ユニットを有する実行ユニットのポート上でスケジューリングされる。実行ユニットに関連するレジスタファイルはまた、情報命令処理結果を格納するため含まれる。一例となる実行ユニットは、浮動小数点実行ユニット、整数実行ユニット、ジャンプ実行ユニット、ロード実行ユニット、ストア実行ユニット及び他の既知の実行ユニットを含む。

#### 【0020】

下位レベルデータキャッシュ及びデータ変換バッファ(D-TLB)150は、実行ユニット140に接続される。データキャッシュは、メモリコヒーレンシ状態において保持されるデータオペランドなどの最近利用された／動作した要素を格納するものである。D-TLBは、最近のバーチャル／リニアから物理アドレスへの変換を格納するものである。具体例として、プロセッサは、物理メモリを複数のバーチャルページに分割するためのページテーブル構造を有してもよい。

#### 【0021】

ここで、コア101, 102は、オンチップインタフェース110に関連付けされた第2レベルキャッシュなどの上位レベル又はさらなるアウトキャッシュへのアクセスを共有する。上位レベル又はさらなるアウトは実行ユニットから増加又は離れるキャッシュレベルを表すことに留意されたい。一実施例では、上位レベルキャッシュは、第2又は第3レベルデータキャッシュなどのラストレベルデータキャッシュ、すなわち、プロセッサ100上のメモリ階層における最後のキャッシュである。しかしながら、上位レベルキャッシュはこれに限定されず、命令キャッシュに関連付け又は含むものであってもよい。あるタイプの命令キャッシュであるトレースキャッシュが、直近に復号化されたトレースを格納するため、デコーダ125の後に接続されてもよい。ここで、命令はマイクロ命令(すなわち、デコーダにより認識される汎用命令)を表し、複数のマイクロ命令(マイクロ処理)に復号化されてもよい。

#### 【0022】

図示されたコンフィギュレーションでは、プロセッサ100はまた、オンチップインタフェースモジュール110を有する。従来、以下でより詳細に説明されるメモリコントローラは、プロセッサ100の外部の計算システムに含まれていた。このシナリオでは、オンチップインタフェースモジュール110は、システムメモリ175、チップセット(しばしばメモリ175に接続するためのメモリコントローラハブと、周辺デバイスに接続するためのI/Oコントローラハブとを含む)、メモリコントローラハブ、ノースブリッジ又は他の集積回路など、プロセッサ100の外部のデバイスと通信するためのものである

10

20

30

40

50

。このシナリオでは、バス 105 は、マルチドロップバス、ポイント・ツー・ポイントインターフェース、シリアルインターフェース、パラレルバス、コヒーレント（キャッシュコヒーレントなど）バス、レイヤ化プロトコルアーキテクチャ、異なるバス及び G T L バスなどの何れか既知のインターフェースを有してもよい。

#### 【0023】

メモリ 175 は、プロセッサ 100 に専用とされてもよいし、又はシステムの他のデバイスと共有されてもよい。一般的なタイプのメモリ 175 は、DRAM、SRAM、不揮発性メモリ（NVメモリ）及び他の既知の記憶デバイスを含む。デバイス 180 は、グラフィックアクセラレータ、メモリコントローラハブに接続されるプロセッサ若しくはカード、I/Oコントローラハブに接続されるデータストレージ、無線送受信機、フラッシュデバイス、オーディオコントローラ、ネットワークコントローラ又は他の既知のデバイスを含むものであってもよい。10

#### 【0024】

しかしながら、最近、より多くのロジック及びデバイスが SOC などの単一のダイに統合されるに従って、これらのデバイスのそれぞれはプロセッサ 100 上に搭載される可能性がある。例えば、一実施例では、メモリコントローラハブは、プロセッサ 100 と同一パッケージ及び / 又はダイ上にある。ここで、コア 110 の一部（オンコア部分）は、メモリ 175 やデバイス 180 などの他のデバイスとインターフェースをとるための 1 以上のコントローラを有する。当該デバイスとインターフェースをとるためのインターフェース及びコントローラを含むコンフィギュレーションは、しばしばオンコア（又はアンコアコンフィギュレーション）と呼ばれる。一例として、オンチップインターフェース 110 は、オンチップ通信のためのリングインターフェースと、オフチップ通信のための高速シリアルポイント・ツー・ポイントリンク 105 とを有する。さらに、SOC 環境では、ネットワークインターフェース、コプロセッサ、メモリ 175、デバイス 180 及び他の何れか既知のコンピュータデバイス /インターフェースなどのさらに多くのデバイスが、高機能及び低電力消費をスマートフォームファクタに提供するため、単一のダイ又は集積回路上に搭載されてもよい。20

#### 【0025】

一実施例では、プロセッサ 100 は、ここに開示される装置及び方法をサポートするため、又はそれらとインターフェースをとるため、アプリケーションコード 176 をコンパイル、変換及び / 又は最適化するコンパイラ、最適化及び / 又は変換コード 177 を実行可能である。コンパイラはしばしば、ソーステキスト / コードをターゲットテキスト / コードに変換するためのプログラム又はプログラムセットを含む。通常、コンパイラによるプログラム / アプリケーションコードのコンパイルは、ハイレベルプログラミング言語コードを低レベルマシン又はアセンブリ言語コードに変換するため複数のフェーズ及びバスにおいて実行される。さらに、単一バスコンパイラが、シンプルなコンパイルのため依然として利用されてもよい。コンパイラは、何れか既知のコンパイル技術を利用し、レキシカル解析、前処理、パーサリング、意味解析、コード生成、コード変換及びコード最適化などの何れか既知のコンパイラ処理を実行してもよい。30

#### 【0026】

より大きなコンパイラはしばしば複数のフェーズを有するが、最も頻繁には、これらのフェーズは 2 つの一般的なフェーズ、(1) フロントエンド、すなわち、一般に構文処理、意味処理及び変換 / 最適化が行われるところ、(2) バックエンド、すなわち、一般に解析、変換、最適化及びコード生成が行われるところに含まれる。一部のコンパイラは、コンパイラのフロントエンドとバックエンドとの間の描写を曖昧に示すミドルを表す。この結果、コンパイラの挿入、関連付け、生成又は他の処理の参照は、上述されたフェーズ又はバスの何れかと共に、コンパイラの他の何れか既知のフェーズ又はバスにおいて実行されてもよい。例示的な具体例として、コンパイラは、コンパイルのフロントエンドフェーズにおけるコール / 処理の挿入と、その後の変換フェーズにおけるコール / 処理の下位レベルコードへの変換などのコンパイルの 1 以上のフェーズにおける処理、コール、ファ4050

ンクションなどを挿入する。動的なコンパイル中、コンパイラコード又は動的最適化コードは、当該処理／コールを挿入すると共に、ランタイム中に実行用のコードを最適化してもよいことに留意されたい。特定の例示的な具体例として、バイナリコード（すでにコンパイルされたコード）は、ランタイム中に動的に最適化されてもよい。ここで、プログラムコードは、動的な最適化コード、バイナリコード又はこれらの組み合わせを含むものであってもよい。

#### 【0027】

コンパイラと同様に、バイナリトランスレータなどのトランスレータは、コードを最適化及び／又は変換するため、静的又は動的にコードを変換する。従って、コード、アプリケーションコード、プログラムコード又は他のソフトウェア環境の実行の表現は、（1）プログラムコードをコンパイルし、ソフトウェア構造を維持し、他の処理を実行し、コードを最適化し、又はコードを変換するための最適化装置又はトランスレータのコンパイラプログラム及び最適化コードの動的又は静的な実行、（2）最適化／コンパイルされたアプリケーションコードなどの処理／コールを含むメインプログラムコードの実行、（3）ソフトウェア構造を維持し、他のソフトウェア関連処理を実行し、又はコードを最適化するためメインプログラムコードに関連するライブラリなどの他のプログラムコードの実行、又は（4）これらの組み合わせを表すものであってもよい。

10

#### 【0028】

いくつかの実現形態では、電力管理コントローラ160がまた設けられ、ハードウェア及びソフトウェアにより実現可能である。システム及び当該システムに接続されるデバイスは、他の（中間など）状態及び状況のうちフル電力、低電力及び無電力状態を含む複数の電力状態をサポート可能である。電力管理コントローラ160は、他の機能のうちシステムの電力消費を最小化するのを支援し、システムの熱制限を管理し、システムのバッテリ寿命を最大化するため、機能を提供してタスクを実行することが可能である。電力管理は、他の具体例のうちシステムスピード、ノイズ、バッテリ寿命及びAC電力消費を含むシステムの他の機能及び特性を管理することを含むことが可能である。

20

#### 【0029】

オンチップインターフェースは、レジューム時間モジュール104を有することが可能である。レジューム時間モジュール104は、プロセッサ182及びメモリ184を有することが可能である。オンチップインターフェース110及びデバイス180は、PCIe (Peripheral Component Interconnect express) に準拠した又は他の接続を介し通信してもよい。PCI及びPCIeなどのいくつかのインターフェースでは、アーキテクチャ機構が、デバイスのエントリをフル電力状態に遅延させるため設けることができる（例えば、特定の電力管理ポリシー及び能力に関して）。例えば、デバイスのオペレーティングシステムの電力管理ロジックなどのソフトウェアは、少なくとも部分的にエントリを制御し、各種電力状態にイグジットする。いくつかの具体例では、プラットフォームポリシーは、例えば、電力状態の初期化に関して、デバイスにコンフィギュレーションリクエストをソフトウェアが発行することを許可する前に最小限のリカバリ時間（遅延）を提供することができる。例えば、アイドル電力の利用を向上させるため、電力管理ポリシー及び機能は、インターフェースを介し接続された外部デバイスと共に、個別のアタッチされたデバイス、Root Port (RP) 及びRoot Complex Integrated End Point (RCIE) を含むデバイスを、当該デバイスへの電力が取り除くことが可能であるか、当該デバイスが低電力状態により動作可能であるか、又は当該デバイスが補助電力下で動作可能である電力管理状態に配置することを試みることが可能である。これらの電力状態から再開すると、ソフトウェアは、コンフィギュレーションリクエストを発行するまで指定された時間（10ms、100msなど）待機する。これは、レジューム時間に対して有意な影響を有する可能性がある。しかしながら、このような規定された最小リカバリ時間は、ある状況及びデバイスにおいて効果的であるが、他の状況及びデバイスにおいては所望されない可能性がある。

30

40

50

**【 0 0 3 0 】**

いくつかの実現形態では、オンチップインターフェースは、レジューム時間モジュール104を含むことができる。レジューム時間モジュール104は、プロセッサ182とメモリ184とを有することができる。レジューム時間モジュール104は、ルートポート、D P ( D e s i g n a t e d P o r t ) 又は R C I E などの内部デバイスが電力状態遷移後（例えば、初期的な電力オン、D3からD0への移行など）に第1コンフィギュレーション（ソフトウェアなどに関して）の準備がどの程度すぐにできるか示すデバイス固有のリカバリ時間を通知することを可能にするよう構成可能である。一実施例では、レジューム時間モジュール104はさらに、内部デバイスがエンドを所定のリカバリ時間に強制するため、又はソフトウェアによりコンフィギュレーションタスクが実行されるのを開始するため、電力状態遷移を完了又は完了する準備ができると、インタラプトをトリガするためのインタラプト機構（能力記述、インタラプトを可能にするための制御機構など）を有することが可能である。

**【 0 0 3 1 】**

いくつかの実現形態では、デバイス固有のレジューム時間能力は、1以上の能力レジスタにおいて規定でき、ソフトウェアベースツールを含む1以上の電力管理ツールによりアクセス可能である。一例では、デバイスの数え上げ中（例えば、外部又は内部デバイスを含む1以上のデバイス180など）、レジューム時間モジュール104は、デバイスのレジューム時間能力にアクセスし、以降の利用のためそれをメモリ184に格納してもよい。レジューム時間モジュール104はまた、デバイスのインタラプト能力を読み、内部デバイスがコンフィギュレーションアクセスの準備がでくると、インタラプトのトリガ及び認識を可能にするため、ポーリング機構の代わりにインタラプト機構を実装してもよい。例えば、あるポイントでは、内部デバイスは低電力状態に遷移可能である。一実施例では、レジューム時間モジュール104は、内部デバイスが低電力状態からフル電力状態に遷移することを決定できる。さらに、レジューム時間モジュール104は、メモリ184からデバイス180のレジューム時間通知値を抽出し、対応する能力構成により内部デバイスにより通知されたメモリ184における期間の待機後に第1コンフィギュレーションリクエストを発行してもよい。

**【 0 0 3 2 】**

他の実施例では、レジューム時間モジュール104は、それがデバイス180の制御を有するサブシステムに電力を印加することを決定できる。デバイス180が低電力状態からイグジットしたときにインタラプトを送信するよう構成される場合、レジューム時間モジュール104は、第1コンフィギュレーションアクセスの準備ができていることを通知するインタラプトがデバイス180から受信されることを待機してもよい。双方のケースにおいて、レジューム時間モジュールは、第1コンフィギュレーションアクセスによってデバイスにアクセスする前、100msの固定的な設定された待機時間を取り除くことができる。レジューム時間モジュール104はまた、電力管理制御状態レジスタ（P M C S R）への書き込み後、第1コンフィギュレーションアクセスによりデバイスにアクセスする前に、ソフトウェアのための固定的な設定された待機時間を取り除くようにしてもよい。後方互換性を維持するため、設定されたリカバリ時間（レガシー100ms又は10ms（P M C S Rライト後のアクセスのため）遅延など）はレジューム時間モジュール104により延長されるべきでなく、カスタムレジューム時間能力を利用しないデバイスについてデフォルトとしてサポートできる。上述されるように、オンチップインターフェース110及びデバイス180は、P C I e、M I P I、Q P I又は他のプロトコルに準拠したインターフェースなどのリンク接続を介し通信してもよい。

**【 0 0 3 3 】**

P C I e の主要な目標は、異なるベンダからのデバイス及びコンポーネントが、クライアント（デスクトップ及びモバイル）、サーバ（標準及び企業）及び埋め込み通信デバイスの複数のマーケットセグメントに及ぶオープンアーキテクチャにおいて連携することを可能にすることである。P C I e は、広範な将来的な計算及び通信プラットフォームに対

10

20

30

40

50

して規定されるハイパフォーマンスな汎用的な I / O インターコネクトである。その利用モデル、ロードストアーキテクチャ及びソフトウェアインターフェースなどのいくつかの PCI 属性がその改訂を介し維持される一方、以前のパラレルバス実装はスケーラビリティの高い完全にシリアルなインターフェースと置換された。PCIe のより最近のバージョンは、新たなレベルのパフォーマンス及び機能を提供するため、ポイント・ツー・ポイントインターフェース、スイッチベース技術及びパケット化プロトコルにおける進歩を利用する。電力管理、QoS (Quality of Service)、ホットプラグ / ホットスワップサポート、データインテグリティ及びエラーハンドリングは、PCIe によりサポートされる先進的な機能の一部である。

## 【0034】

10

図 2 を参照して、コンポーネントセットを相互接続するポイント・ツー・ポイントリンクから構成されるファブリックの実施例が示される。システム 200 は、コントローラハブ 215 に接続されるシステムメモリ 210 とプロセッサ 205 とを有する。プロセッサ 205 は、マイクロプロセッサ、ホストプロセッサ、埋め込みプロセッサ、コプロセッサ又は他のプロセッサなどの何れかの処理要素を含む。プロセッサ 205 は、フロントサイドバス (FSB) 206 を介しコントローラハブ 215 に接続される。一実施例では、FSB 206 は、後述されるようなシリアルポイント・ツー・ポイントインターフェースである。他の実施例では、リンク 206 は、異なるインターフェース規格に準拠するシリアルな差動インターフェースアーキテクチャを有する。

## 【0035】

20

システムメモリ 210 は、RAM (Random Access Memory)、不揮発性 (NV) メモリ又はシステム 200 のデバイスによりアクセス可能な他のメモリなどの何れかのメモリデバイスを含む。システムメモリ 210 は、メモリインターフェース 216 を介しコントローラハブ 215 に接続される。メモリインターフェースの具体例は、DDR (Double - Data Rate) メモリインターフェース、デュアルチャネル DDR メモリインターフェース及びDRAM メモリインターフェースを含む。

## 【0036】

一実施例では、コントローラハブ 215 は、PCIe インターコネクション階層におけるルートハブ、ルートコンプレックス又はルートコントローラである。コントローラハブ 215 の具体例は、チップセット、メモリコントローラハブ (MCH)、ノースブリッジ、インターフェクトコントローラハブ (ICH)、サウスブリッジ及びルートコントローラ / ハブを含む。しばしば、チップセットという用語は、2つの物理的に分離したコントローラハブ、すなわち、インターフェクトコントローラハブ (ICH) に接続されたメモリコントローラハブ (MCH) を表す。現在のシステムはしばしばプロセッサ 205 により統合された MCH を有し、コントローラ 215 は後述されるような同様の方法により I/O デバイスと通信するためのものであることに留意されたい。いくつかの実施例では、ピア・ツー・ピアルーティングは、任意的には、ルートコンプレックス 215 を介しサポートされる。

30

## 【0037】

40

ここで、コントローラハブ 215 は、シリアルリンク 219 を介しスイッチ / ブリッジ 220 に接続される。インターフェース / ポート 217, 221 として参照されてもよい入力 / 出力モジュール 217, 221 は、コントローラハブ 215 とスイッチ 220 との間の通信を提供するため、レイヤ化プロトコルスタックを有する / 実装する。一実施例では、複数のデバイスが、スイッチ 220 に接続可能である。

## 【0038】

50

スイッチ / ブリッジ 220 は、デバイス 225 からコントローラハブ 215 に上流に、すなわち、ルートコンプレックスまで階層を上方に、及びプロセッサ 205 又はシステムメモリ 210 からデバイス 225 に下流に、すなわち、ルートコントローラから階層を下方にパッケージ / メッセージをルーティングする。一実施例では、スイッチ 220 は、複数のバーチャル PCI - to - PCI ブリッジデバイスの論理アセンブリとして参照され

る。デバイス 225 は、I/O デバイス、ネットワークインターフェースコントローラ (NIC)、アドインカード、オーディオプロセッサ、ネットワークプロセッサ、ハードドライブ、ストレージデバイス、CD/DVD ROM、モニタ、プリンタ、マウス、キーボード、ルータ、ポータブルストレージデバイス、ファイアワイイヤデバイス、USB (Universal Serial Bus) デバイス、スキャナ及び他の入出力デバイスなどの電子システムに接続される内部又は外部デバイス又はコンポーネントを含む。しばしば PCIe において、デバイスなどの用語はエンドポイントとして参照される。具体的に図示しないが、デバイス 225 は、レガシー又は他のバージョンの PCI デバイスをサポートするための PCIe から PCI / PCI-X へのブリッジを有してもよい。PCIe のエンドポイントデバイスは、しばしばレガシー、PCIe 又はルートコンプレックスが搭載されたエンドポイントとして分類される。10

#### 【0039】

グラフィックアクセラレータ 230 がまた、シリアルリンク 232 を介しコントローラハブ 215 に接続される。一実施例では、グラフィックアクセラレータ 230 は、ICH に接続される MCH に接続される。スイッチ 220 及び I/O デバイス 225 は、その後に ICH に接続される。I/O モジュール 231, 218 はまた、グラフィックアクセラレータ 230 とコントローラハブ 215との間で通信するため、レイヤ化プロトコルスタックを実装する。上述した MCH と同様に、グラフィックコントローラ又はグラフィックアクセラレータ 230 自体は、プロセッサ 205 に統合されてもよい。さらに、いくつかの実現形態では、1 以上の内部デバイス (211, 212, 213 など) が、例えば、チップセット、コントローラハブ、ルートコンプレックスなどに備えることが可能である。例えば、RCIE (Root Complex Integrated Endpoint)、ダウンストリームポート若しくはルートポート (217 など)、内部 PCIe デバイス及び他の内部デバイスを備えることができる。ここに説明される機能は、外部デバイスと共に内部デバイスに適用可能である。20

#### 【0040】

図 3 を参照して、レイヤ化プロトコルスタックの実施例が示される。レイヤ化プロトコルスタック 300 は、クイックバスインターフェース (QPI) スタック、PCIe スタック、次世代ハイパフォーマンス計算インターフェーススタック又は他のレイヤ化スタックなどのレイヤ化通信スタックの何れかの形態を含む。図 2 ~ 5 を参照して以降の説明は PCIe スタックに関するものであるが、同じコンセプトが他のインターフェーススタックに適用されてもよい。一実施例では、プロトコルスタック 300 は、トランザクションレイヤ 305、リンクレイヤ 310 及び物理レイヤ 320 を含む PCIe プロトコルスタックである。図 2 のインターフェース 217, 218, 221, 222, 226 及び 231 などのインターフェースは、通信プロトコルスタック 300 として表されてもよい。通信プロトコルスタックとしての表現はまた、プロトコルスタックを実装 / 内蔵するモジュール又はインターフェースとして参照されてもよい。30

#### 【0041】

PCIe は、コンポーネント間で情報を通信するためパケットを利用する。パケットは、送信元コンポーネントから受信先コンポーネントに情報を搬送するため、トランザクションレイヤ 305 及びデータリンクレイヤ 310 において構成される。送信されたパケットはその他のレイヤを通過するとき、これらのレイヤにおいてパケットを処理するのに必要な追加的情報により拡張される。受信サイドでは、逆の処理が行われ、パケットはその物理レイヤ 320 の表現からデータリンクレイヤ 310 の表現に変換され、最終的には (トランザクションレイヤパケットのため) 受信先デバイスのトランザクションレイヤ 305 により処理可能な形式に変換される。40

#### 【0042】

##### トランザクションレイヤ

一実施例では、トランザクションレイヤ 305 は、データリンクレイヤ 310 及び物理レイヤ 320 などのインターフェースとアーキテクチャとデバイスの処理コアとの間のイン50

タフェースを提供する。これに関して、トランザクションレイヤ305の主要な役割は、パケットのアセンブリ及びデアセンブリである（すなわち、トランザクションレイヤパケット又はTLP）。トランザクションレイヤ305は、典型的には、TLPのためのクレジットベースフロー制御を管理する。PCIeは、ターゲットデバイスがレスポンスのためのデータを収集しながら、リンクが他のトラフィックを搬送することを可能にするため、分離されたトランザクション、すなわち、時間により分離されたリクエスト及びレスポンスによるトランザクションを実現する。

#### 【0043】

さらに、PCIeは、クレジットベースフロー制御を利用する。このスキームでは、デバイスは、トランザクションレイヤ305における各受信バッファの初期的なクレジット量を通知する。図2のコントローラハブ115などのリンクの反対のエンドの外部デバイスは、各TLPにより消費されるクレジット数をカウントする。トランザクションがクレジットリミットを超過しない場合、当該トランザクションは送信されてもよい。レスポンスを受信すると、クレジット量が復元される。クレジットスキームの効果は、クレジットリミットに直面しない場合、クレジットリターンの遅延がパフォーマンスに影響を与えることである。

#### 【0044】

一実施例では、4つのトランザクションアドレススペースは、コンフィギュレーションアドレススペース、メモリアドレススペース、入出力アドレススペース及びメッセージアドレススペースを含む。メモリスペーストランザクションは、メモリにマッピングされた位置との間でデータを伝送するため、リードリクエスト及びライトリクエストの1以上を含む。一実施例では、メモリスペーストランザクションは、32ビットアドレスなどのショートアドレスフォーマット又は64ビットアドレスなどのロングアドレスフォーマットなどの2つの異なるアドレスフォーマットを利用することができます。コンフィギュレーションスペーストランザクションは、PCIeデバイスのコンフィギュレーションスペースにアクセスするのに利用される。コンフィギュレーションスペースに対するトランザクションは、リードリクエストとライトリクエストとを含む。メッセージスペーストランザクション（又は単にメッセージ）は、PCIeエージェントの間のインバンド通信をサポートするため規定される。従って、一実施例では、トランザクションレイヤ305は、パケットヘッダ/ペイロード306を構成する。現在のパケットヘッダ/ペイロードのためのフォーマットは、PCIe規格のウェブサイトにおけるPCIe規格において見つけられる。

#### 【0045】

図4を参照して、PCIeトランザクション記述子の実施例が示される。一実施例では、トランザクション記述子400は、トランザクション情報を搬送するための機構である。これに関して、トランザクション記述子400は、システムにおけるトランザクションの特定をサポートする。他の可能性のある利用は、デフォルトトランザクションオーダリングの修正とトランザクションとチャネルとの関連付けをトラッキングすることを含む。

#### 【0046】

トランザクション記述子400は、グローバル識別子フィールド402、属性フィールド404及びチャネル識別子フィールド406を含む。図示された例では、グローバル識別子フィールド402は、ローカルトランザクション識別子フィールド408及びソース識別子フィールド410を含むように示される。一実施例では、グローバルトランザクション識別子402は、すべての発行済みリクエストに対して一意的である。

#### 【0047】

一実現形態によると、ローカルトランザクション識別子フィールド408は、要求元のエージェントにより生成されるフィールドであり、それは、当該要求元のエージェントに対して完了を要求する全ての発行済みのリクエストに対して一意的である。さらに、本例では、ソース識別子410は、PCIe階層内で要求元のエージェントを一意的に特定する。従って、ソースID410と共に、ローカルトランザクション識別子408のフィー

10

20

30

40

50

ルドは、階層ドメイン内のトランザクションのグローバルな特定を提供する。

#### 【0048】

属性フィールド404は、トランザクションの特性及び関係を指定する。これに関して、属性フィールド404は、トランザクションのデフォルト処理の変更を可能にする追加的な情報を提供するため利用可能である。一実施例では、属性フィールド404は、プライオリティフィールド412、リザーブフィールド414、オーダリングフィールド416及び非スヌープフィールド418を有する。ここで、プライオリティサブフィールド412は、トランザクションにプライオリティを割り当てるのに発信元により変更されてもよい。リザーブ属性フィールド414は、以降における又はベンダにより規定された利用のため確保される。プライオリティ又はセキュリティ属性を利用した可能な利用モデルは、リザーブ属性フィールドを用いて実現されてもよい。10

#### 【0049】

本例では、オーダリング属性フィールド416は、デフォルトオーダリングルールを変更可能なオーダリングのタイプを伝える任意的情報を供給するのに利用される。一実現形態によると、“0”のオーダリング属性は、デフォルトオーダリングルールが適用されることを示し、“1”のオーダリング属性は、ライトが同一方向にライトをパスし、リード完了が同一方向にライトをパスすることが可能な緩和されたオーダリングを示す。スヌープ属性フィールド418は、トランザクションがスヌープされるか判断するのに利用される。図示されるように、チャネルIDフィールド406は、トランザクションが関連付けされるチャネルを特定する。20

#### 【0050】

##### リンクレイヤ

データリンクレイヤ310とも呼ばれるリンクレイヤ310は、トランザクションレイヤ305と物理レイヤ320との間の中間ステージとして機能する。一実施例では、データリンクレイヤ310の役割は、2つのコンポーネントの間でトランザクションレイヤパケット(TLP)を交換するための信頼できる機構を提供する。データリンクレイヤ310の一方のサイドは、トランザクションレイヤ305により構成されたTLPを受理し、パケットシーケンス識別子311、すなわち、識別番号又はパケット番号を適用し、誤り検出コード、すなわち、CRC312を計算及び適用し、物理レイヤを介し外部デバイスに送信するため変更されたTLPを物理レイヤ320に送信する。30

#### 【0051】

##### 物理レイヤ

一実施例では、物理レイヤ320は、外部デバイスにパケットを物理的に送信するため、論理サブプロック321及び電子サブプロック322を有する。ここで、論理サブプロック321は、物理レイヤ321の“デジタル”機能のためのものである。これに関して、論理サブプロックは、物理サブプロック322による送信用の出力情報を準備するための送信セクションと、リンクレイヤ310に渡す前に受信した情報を特定及び準備するための受信セクションとを有する。

#### 【0052】

物理プロック322は、送信機及び受信機を有する。送信機には論理サブプロック321によりシンボルが供給され、送信機は、シリアル化して外部デバイスに送信する。受信機には、外部デバイスからシリアル化されたシンボルが供給され、受信信号をビットストリームに変換する。ビットストリームは、シリアル化解除され、論理サブプロック321に供給される。一実施例では、10ビットシンボルが送受信される場合、8b/10b送信コードが利用される。ここで、特別なシンボルは、フレーム323によりパケットをフレーム化するのに利用される。さらに、一例では、受信機はまた、入力されたシリアルストリームから復元されたシンボルクロックを提供する。40

#### 【0053】

上述されるように、トランザクションレイヤ305、リンクレイヤ310及び物理レイヤ320がPCIeプロトコルスタックの特定の実施例を参照して説明されるが、レイヤ50

化プロトコルスタックはこれに限定されるものでない。実際、何れかのレイヤ化プロトコルが包含／実装されてもよい。一例として、レイヤ化プロトコルとして表されるポート／インターフェースは、(1)パケットを構成するための第1レイヤ、すなわち、トランザクションレイヤ、パケットをシーケンス化するための第2レイヤ、すなわち、リンクレイヤ、及びパケットを送信するための第3レイヤ、すなわち、物理レイヤを含む。具体例として、CSI(Common Standard Interface)レイヤ化プロトコルが利用される。

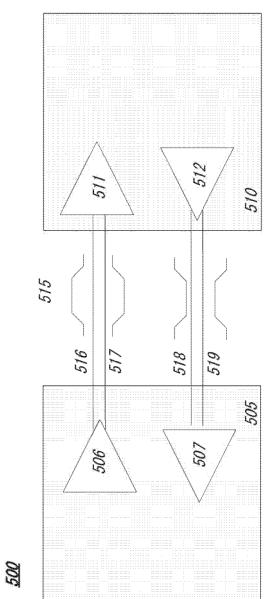

#### 【0054】

次に図5を参照して、PCIeシリアルポイント・ツー・ポイントファブリックの実施例が説明される。PCIeシリアルポイント・ツー・ポイントリンクの実施例が示されるが、シリアルポイント・ツー・ポイントリンクはこれに限定されず、シリアルデータを送信する何れかの送信パスを含む。図示された実施例では、ベーシックPCIeリンクは、2つの低電圧差動駆動される信号ペア、すなわち、送信ペア506/511と受信ペア512/507とを有する。従って、デバイス505は、データをデバイス510に送信するための送信ロジック506と、データをデバイス510から受信するための受信ロジック507とを有する。すなわち、2つの送信パス、すなわち、パス516, 517と、2つの受信パス、すなわち、パス518, 519とがPCIeリンクに含まれる。

10

#### 【0055】

送信パスは、送信ライン、銅線、光ライン、無線通信チャネル、赤外線通信リンク又は他の通信パスなどのデータを送信するための何れかのパスを表す。デバイス505, 510などの2つのデバイスの間の接続は、リンク415などのリンクとして参照される。リンクは1つのレーンをサポートし、各レーンは差動信号バスのセットを表す(送信用の1つのパスと受信用の1つのパス)。帯域幅をスケーリングするため、リンクは×Nにより示される複数のレーンを集約するものであってもよく、Nは、1, 2, 4, 8, 12, 16, 32, 64又はさらに広い何れかのサポートされたリンク幅である。

20

#### 【0056】

差動ペアは、差動信号を送信するためのライン416, 417などの2つの送信パスを表す。一例として、ライン416が低電圧レベルから高電圧レベルに、すなわち、ライジングエッジに切り替わると、ライン417は、高い論理レベルから低い論理レベルに、すなわち、フォーリングエッジに駆動する。差動信号は、より良好な信号インテグリティ、すなわち、クロスカッピング、電圧オーバーシュート／アンダーシュート、リンギングなどのより良好な電気特性を示しうる。これは、より良好なタイミングウィンドウを可能にし、より高速な送信周波数を可能にする。

30

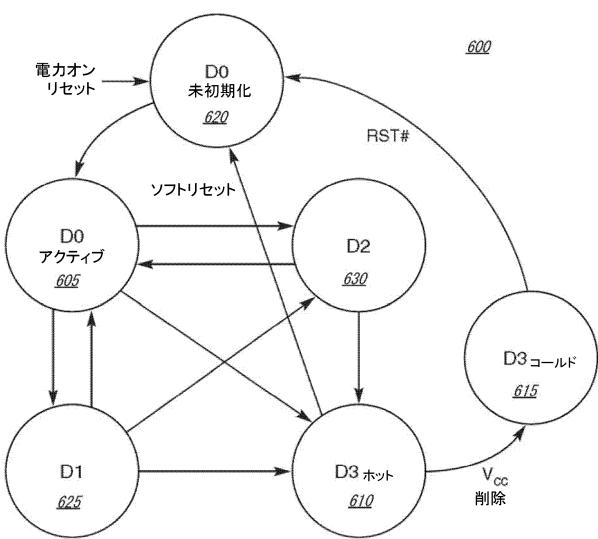

#### 【0057】

上述されるように、PCIeなどの各種プラットフォームは、複数の電力管理状態をサポート可能である。図6は、一例となる電力管理状態(605, 610, 615, 620, 625, 630など)とこれらの状態間の遷移とを示す一例となる状態遷移図600を示す。図6の例では、4つの主要な電力状態がサポートされる。例えば、D0状態(605, 620など)は1つの極限において最大電力又はアクティブ状態とすることが可能であり、D3状態(610, 615など)は電力“オフ”状態を提供する。状態D1(625など)及びD2(630など)は、例えば、デバイスのスリープ又はライトスリープ状態などを表す中間的な電力状態を提供することができる。一例では、Vccがデバイスを完全に電力オフするため取り除かれるD3コールド状態(615など)と区別するため、Vccがデバイスに依然として印加されるD3ホット状態(610など)が提供可能である。

40

#### 【0058】

図6に示されるように、各種状態(605, 610, 615, 620, 625, 630など)間の遷移が規定可能である。例えば、一実現形態では、状態D3のホットのデバイスは、例えば、D0状態コマンドを対応する電力管理制御状態レジスタに書き込むことなどによって、電力アップに応答してまずデバイスをD0非初期化620の状態にすること

50

によって D 0 に戻すことができる。他の例では、デバイス状態 D 3 コールドにおいて、ファンクションは D 3 コールドから D 0 に戻すことができる（D 3 コールドからの唯一の正当な状態遷移）。いくつかの具体例では、例えば、その対応するコンフィギュレーションスペースを含むファンクションのフル又はパーシャル再初期化を実行するため、電力管理状態遷移に関してソフトウェアが呼び出し可能である。さらに、上述されたように、最小リカバリ時間要求が、いくつかの例において（システムソフトウェアにより実施されるなど）、ファンクションが D 3 から D 0 にプログラムされたときと、ファンクションがアクセス（コンフィギュレーションアクセスを含む）されたときとの間で規定できる。これは、自らをリセットし、電力オン状態に移行させるための当該ファンクションの時間を許容することができる。しかしながら、上述されたように、このようなデフォルト最小リカバリ時間は、不要な遅延を特定のデバイスのレジューム時間に導入する可能性がある。従って、いくつかの実現形態では、レジューム時間能力は、デバイスが代わりに設定された最小リカバリ時間より（短い又は長い）デバイス固有のリカバリ時間を通知することを可能にするため設けることができる。さらに、デバイスが他の可能な具体例のうち設定された（又はいくつかの実現形態では、デバイスにより通知された）最小リカバリ時間を決定する前に、コンフィギュレーションアクセスをトリガするためのインタラプトを開始することを可能にするため備えることができる。10

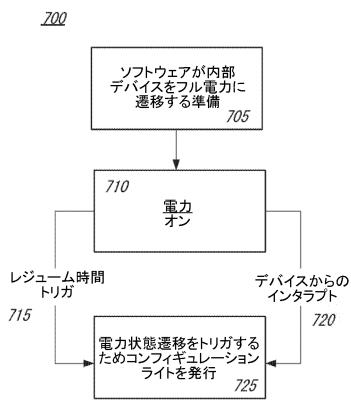

#### 【 0 0 5 9 】

図 7 に戻って、簡略化されたフロー図 7 0 0 が示される。オペレーティングシステムの電力管理ツールなどのソフトウェアコントローラは、チップセットの内部デバイス又は SOC などの特定のデバイスがフル電力に遷移し、デバイス電力オンし（710）、低電力状態又は無電力状態からアクティブ状態に遷移することを開始する準備をすることができる（例えば、デバイスを用いて実行される特定のファンクションなどに関して）。ポーリング（710など）は、対応する電力管理レジスタ、拡張された能力構造又は他の構造若しくはレジスタにおいてデバイスに対して規定される能力に基づき行うことができる。例えば、コントローラは、デバイスのレジューム時間を特定し（例えば、設定された時間又は通知された時間遅延など）、レジューム時間が経過したことを特定すると、電力状態遷移の完了をトリガするため（725）、コンフィギュレーションライトを発信することが可能である。あるいは、デバイスは、能力構造又はレジスタなどにおいて規定されるインタラプト能力を有することが可能であり、コントローラは、当該能力を特定し、デバイスがアクティブ状態に入り、コンフィギュレーションアクセスを受信する準備ができたことを示すデバイスからのインタラプト 720 を待機することができる。20

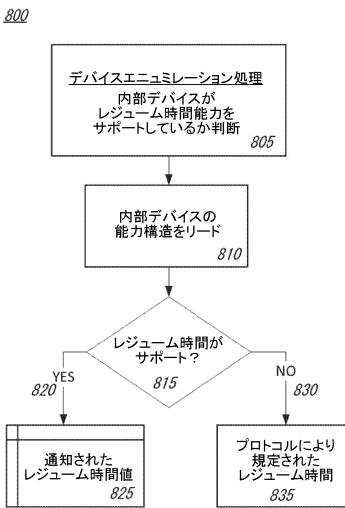

#### 【 0 0 6 0 】

図 8 に戻って、RCIE、ルートポート、ダウンストリームポート又は他のデバイスなどのデバイスが 1 以上のレジューム時間能力をサポートしているか判断するためのデバイスエニュミレーション処理 805 が、いくつかの実現形態において実行可能である。図 8 の具体例では、エニュミレーション（enumeration）処理は、デバイスに対応する能力構造を準備し（810）、カスタマイズされたレジューム又はリカバリ時間が通知及びサポートされているか判断する（815）ことが可能である。エニュミレーション処理 805 は、いくつかの例では、デバイスのリカバリを迅速化することを支援するため、デバイスのインタラプト能力がまた規定されているか判断できる。レジューム時間がサポートされていると判断された場合（820など）、（能力構造に指定されるなど）デバイスに固有の通知されたリカバリ値が特定できる（825）。その後、通知されたリカバリ値は、デバイスの電力状態遷移に関連してコンフィギュレーションアクセスを開始する際に、ソフトウェアコントローラによって従われる。あるいは、特別なレジューム時間がデバイスによりサポートされていないと判断された場合（830など）、ソフトウェアコントローラは、アーキテクチャを介し規定された標準的な最小リカバリ時間（10ms、100ms などの固定的な最小リカバリ時間など）を含む設定されたプロトコルにデフォルトのものとすることができます。30

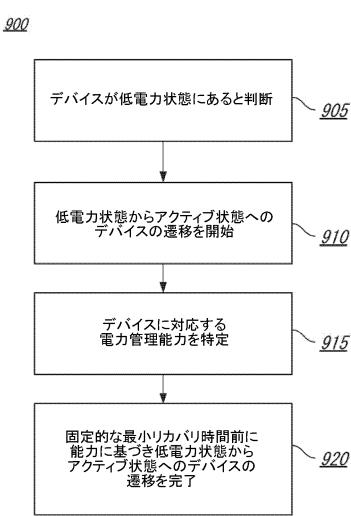

#### 【 0 0 6 1 】

図9は、少なくとも1つの実施例による処理セット900を示すフロー図である。図1のレジューム時間モジュール104などの装置又はその一部が、処理セット900を利用してもよい。当該装置は、図9の処理を実行するための手段を有してもよい。一実施例では、装置は、プロセッサにより実行されると、当該装置に処理セット900を実行させるよう構成されたコンピュータコードを有する図1のメモリ184及び/又はメモリ175などのメモリを有することによって変換される。

#### 【0062】

ブロック905において、デバイスは、低電力状態にあると決定できる（対応するレジスタなどから）。低電力状態からアクティブ状態へのデバイスの遷移は、例えば、少なくとも部分的にソフトウェアに基づくコントローラなどによって、ブロック910において開始できる。固定的な最小リカバリ時間は、インターフェースによる設定されたりカバリ時間などのシステム内の低電力状態からアクティブ状態への遷移について規定できる。デバイスの能力は、ブロック915においてデバイスの電力管理に対応して特定できる。当該能力は、デバイスについてサポートされるインタラプト機構と、固定的な最小リカバリ時間の代わりにデバイスにおいて適用されるべき通知された他のリカバリ時間とを含むことができる。いくつかのケースでは、双方の能力がデバイスについて有効となることができる。デバイスのアクティブ状態への遷移は、ブロック920において、例えば、特定された能力に対応するトリガにより開始されるデバイスのコンフィギュレーションを介し完了させることができる。例えば、通知されたリカバリ時間が適用可能であるか、又は可能な具体例及び実現形態のうち固定的な最小リカバリ時間の経過前に、デバイスのアクティブ状態への遷移の完了をトリガするため受信可能である。

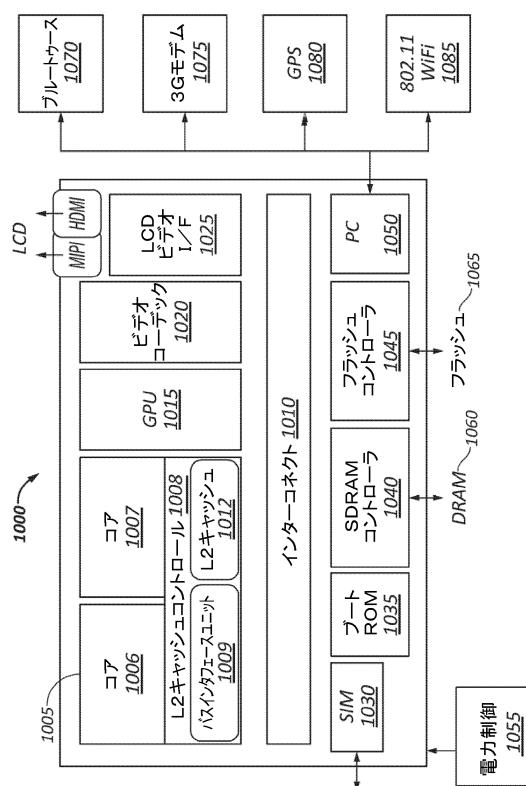

#### 【0063】

上述された原理は、各種インターフェースを含む何れか様々な異なるアーキテクチャに適用可能である。さらに、上記原理は、他の例のうちマルチプロセッササーバ、パーソナルコンピュータ、モバイル計算装置（スマートフォン、タブレットなど）を含む様々な異なるデバイスにおいて適用可能である。一例として、図10に戻って、SOC設計の実施例が示される。特定の例示的な具体例として、SOC1000はユーザ装置（UE）を有するコンピュータに含めることができる。一実施例では、UEは、携帯電話、スマートフォン、タブレット、ウルトラシンノートブック、ブロードバンドアダプタを備えたノートブック又は他の何れか同様の通信デバイスなど、エンドユーザーにより通信するのに利用される何れかのデバイスを表す。しばしば、UEは、GSM（登録商標）ネットワークの移動局（MS）に本来的に対応する基地局又はノードに接続する。

#### 【0064】

ここで、SOC1000は、2つのコア1006, 1007を有する。上記説明と同様に、コア1006, 1007は、Intel（登録商標）Architecture Core<sup>TM</sup>ベースプロセッサ、Advanced Micro Device, Inc. (AMD) プロセッサ、MIPSベースプロセッサ、ARMベースプロセッサ又はこれらのカスタマと共に、それらのライセンス又はアドプタなどのInstruction Set Architectureに準拠してもよい。コア1006, 1007は、システム1000の他のパートと通信するため、バスインターフェースユニット1009及びL2キャッシュ1012に関連付けられるキャッシュコントロール1008に接続される。インターフェース1010は、説明される発明の1以上の態様を実現可能な上述されたI/O S/F、AMBA又は他のインターフェースなどのオンチップインターフェースを含む。

#### 【0065】

インターフェース1010は、SOC1000を初期化及びブートするためコア1006, 1007により実行されるブートコードを保持するためのSIMカードのブートROM 1035とインターフェースをとるSIM(Subscriber Identity Module) 1030、外部メモリ(DRAM1060など)とインターフェースをとるためのSDRAMコントローラ1040、不揮発メモリ(フラッシュ1065など)とインターフェースをとるためのフラッシュコントローラ1045、周辺装置とインターフェースを

10

20

30

40

50

とるための周辺コントロール 1050 (S P I (S e r i a l P e r i p h e r a l I n t e r f a c e) など)、入力を表示及び受信するためのビデオコーデック 1020 及びビデオインターフェース 1025 (タッチ対応入力など)、グラフィック関連計算を実行する G P U 1015 などの他のコンポーネントとの通信チャネルを提供する。これらのインターフェースの何れもここに説明された本発明の態様を含むものであってもよい。

#### 【0066】

さらに、システムは、ブルートゥースモジュール 1070、3G モデム 1075、G P S 1085 及び W i F i 1085 などの通信用の周辺装置を示す。上述されるように、U E は、通信用のラジオを有することに留意されたい。この結果、これらの周辺通信モジュールの全てが必要であるとは限らない。しかしながら、U E のある形態では、外部通信用のラジオが含まれる。

10

#### 【0067】

上述された装置、方法及びシステムは、上述されるような何れかの電子デバイス又はシステムにより実現されてもよいことに留意されたい。具体例として、以下の図面はここに説明される本発明を利用するための一例となるシステムを提供する。以下のシステムがより詳細に説明されるとき、上記説明から複数の異なるインターフェースが開示、説明及び再訪される。また、容易に明らかなように、上述された進歩はこれらのインターフェース、ファブリック又はアーキテクチャの何れかに適用されてもよい。

#### 【0068】

本発明が限定数の実施例に関して説明されたが、当業者は、そこから多数の変更及び変形を理解するであろう。添付した請求項は本発明の真の趣旨及び範囲内に属するものとしてこれら全ての変更及び変形をカバーすることが意図される。

20

#### 【0069】

設計は、作成からシミュレーションを経て製造までの各種段階を経る。設計を表すデータは、複数の方法により当該設計を表すものであってもよい。まず、シミュレーションにおいて有用であるように、ハードウェアは、ハードウェア記述言語又は他の機能記述言語を用いて表現されてもよい。さらに、ロジック及び / 又はトランジスタゲートを備えた回路レベルモデルが、設計プロセスのいくつかの段階において生成されてもよい。さらに、ある段階における大部分の設計は、ハードウェアモデルにおける各種デバイスの物理的配置を表すデータのレベルに到達する。従来の半導体製造技術が利用される場合、ハードウェアモデルを表すデータは、集積回路を生成するため利用されるマスクのための異なるマスクレイヤ上の各種機能の有無を指定するデータであってもよい。当該設計の何れかの表現において、データは機械可読媒体の何れかの形式により格納されてもよい。メモリ又はディスクなどの磁気若しくは光ストレージは、情報を伝送するため変調又は生成される光波又は電波を介し伝送される情報を格納するための機械可読媒体であってもよい。コード又は設計を示す又は搬送する電気的な搬送波が送信されるとき、電気信号のコピー、バックファーリング又は再送が実行される程度まで、新たなコピーが生成される。従って、通信プロバイダ又はネットワークプロバイダは、本発明の実施例の技術を実現する搬送波に符号化された情報などの少なくとも一時的な有形な機械可読媒体を有する物に格納されてもよい。

30

#### 【0070】

ここで用いられるモジュールは、ハードウェア、ソフトウェア及び / 又はファームウェアの何れかの組み合わせを表す。一例として、モジュールは、マイクロコントローラにより実行されるよう構成されるコードを格納するための非一時的媒体に関連付けされるマイクロコントローラなどのハードウェアを含む。従って、一実施例では、モジュールという参照は、非一時的媒体に保持されるコードを認識及び / 又は実行するよう特に構成されるハードウェアを表す。さらに、他の実施例では、モジュールの使用は、所定の処理を実行するためマイクロコントローラにより実行されるよう特に構成されるコードを含む非一時的媒体を表す。推察できるように、さらなる他の実施例では、モジュールという用語（本例では）は、マイクロコントローラと非一時的媒体との組み合わせを表す。しばしば、一

40

50

般に分離するよう示されるモジュールの境界は、可変的であり、重複する可能性がある。例えば、第1及び第2モジュールは、いくつかの独立したハードウェア、ソフトウェア又はファームウェアを維持しながら、ハードウェア、ソフトウェア、ファームウェア又はこれらの組み合わせを共有してもよい。一実施例では、ロジックという用語の使用は、トランジスタ、レジスタ又はプログラマブルロジックデバイスなどの他のハードウェアを含む。

#### 【0071】

一実施例では、“～するため”又は“～するよう構成される”という用語の使用は、指定された又は決定されたタスクを実行するための装置、ハードウェア、ロジック又は要素を構成、組み立て、製造、販売の申し出、輸入及び／又は設計することを表す。本例では、動作していない装置又はその要素は、それが指定されたタスクを実行するよう設計、接続及び／又は相互接続される場合、指定されたタスクを実行するよう依然として“構成される”。純粹に例示的な具体例として、論理ゲートは、動作中に0又は1を提供する。クロックにイネーブル信号を提供するよう構成される論理ゲートは、1又は0を提供するすべての論理ゲートを含むものでない。代わりに、論理ゲートは、動作中に1又は0の出力がクロックをイネーブルにするという方法により接続されるものである。再び、“～するよう構成される”という用語の使用は処理を要求しないが、代わりに装置、ハードウェア及び／又は要素の潜在的な状態に着目し、潜在的な状態では、装置、ハードウェア及び／又は要素は、当該装置、ハードウェア及び／又は要素が動作しているとき、特定のタスクを実行するよう設計される。

10

#### 【0072】

さらに、一実施例では、“～できる”及び／又は“～するよう動作可能である”という用語の使用は、指定された方法により装置、ロジック、ハードウェア及び／又は要素の使用を可能にするように設計された装置、ロジック、ハードウェア及び／又は要素を表す。上述されるように、一実施例では、“～できる”又は“～するよう動作可能である”的使用は、装置、ロジック、ハードウェア及び／又は要素が動作していないが、指定された方法により装置の使用を可能にするように設計される装置、ロジック、ハードウェア及び／又は要素の潜在的な状態を表す。

20

#### 【0073】

ここで使用される値とは、数、状態、論理状態又はバイナリ論理状態の何れか既知の表現を含む。しばしば、論理レベル又は論理値の使用はまた、1及び0として参照され、単にバイナリ論理状態を表す。例えば、1は高論理レベルを表し、0は低論理レベルを表す。一実施例では、トランジスタやフラッシュセルなどのストレージセルは、単一の論理値又は複数の論理値を保持することが可能であってもよい。しかしながら、コンピュータシステムにおける他の値の表現が使用された。例えば、10進数の10はまた、1010のバイナリ値及び16進文字Aとして表現されてもよい。従って、値はコンピュータシステムに保持可能な情報の何れかの表現を含む。

30

#### 【0074】

さらに、状態は値又は値の一部により表現されてもよい。一例として、論理1などの第1の値はデフォルト又は初期状態を表し、論理0などの第2の値は非デフォルト状態を表してもよい。さらに、一実施例では、リセット及び設定という用語はそれぞれ、デフォルト及び更新値又は状態を表す。例えば、デフォルト値は、高論理値、すなわち、リセットを含み、更新値は、低論理値、すなわち、設定を含む。何れかの値の組み合わせは任意数の状態を表すのに利用されてもよいことに留意されたい。

40

#### 【0075】

上述された方法、ハードウェア、ソフトウェア、ファームウェア又はコードの実施例は、処理要素により実行可能な機械アクセス可能、機械可読、コンピュータアクセス可能又はコンピュータ可読媒体に格納される命令又はコードを介し実現されてもよい。非一時的機械アクセス可能／可読媒体は、コンピュータ又は電子システムなどの機械により可読な形態による情報を提供（すなわち、格納及び／又は送信）する何れかの機構を含む。例え

50

ば、非一時的機械アクセス可能媒体は、スタティックRAM(SRAM)又はダイナミックRAM(DRAM)などのRAM(Random Access Memory)、ROM、磁気若しくは光記憶媒体、フラッシュメモリデバイス、電子ストレージデバイス、光ストレージデバイス、音響ストレージデバイス、そこから情報を受信する非一時的媒体と区別されるべき一時的(伝搬)信号(搬送波、赤外線信号、デジタル信号など)から受信される情報を保持する他の形態のストレージデバイスを含む。

#### 【0076】

本発明の実施例を実行するようロジックをプログラムするのに利用される命令は、DRAM、キャッシュ、フラッシュメモリ又は他のストレージなどのシステムのメモリ内に格納されてもよい。さらに、命令はネットワークを介し又は他のコンピュータ可読媒体により配布可能である。従って、機械可読媒体は、機械(コンピュータなど)により可読な形態により情報を格納又は送信するための何れかの機構を含むが、フロッピー(登録商標)ディスクケット、光ディスク、CD、CD-ROM、光磁気ディスク、ROM、RAM、EPROM、EEPROM、磁気若しくは光カード、フラッシュメモリ、又は電気、光、音響若しくは他の形態の伝搬信号(搬送波、赤外線信号、デジタル信号など)を介しインターネットによる情報の伝送に利用される有形な機械可読ストレージに限定されるものでない。従って、コンピュータ可読媒体は、機械(コンピュータなど)により可読な形態により電子命令又は情報を格納又は送信するのに適した何れかのタイプの有形な機械可読媒体を含む。

#### 【0077】

以下の具体例は、本明細書による実施例に関する。1以上の実施例は、デバイスが低電力状態にあることを決定し、低電力状態からアクティブ状態への遷移について固定的な最小のリカバリ時間が規定される場合、低電力状態からアクティブ状態へのデバイスの遷移を開始し、低電力状態からアクティブ状態へのデバイスの遷移に対応するデバイスの能力を特定し、遷移が固定的な最小のリカバリ時間の経過前に完了されるべきである場合、当該能力に少なくとも部分的に基づき低電力状態からアクティブ状態へのデバイスの遷移を完了させるための装置、システム、機械可読ストレージ、機械可読媒体及び方法を提供するものであってもよい。

#### 【0078】

少なくとも一例では、当該能力はインタラプト能力を含み、インタラプトは、デバイスが遷移を完了させる準備ができているという通知である場合、デバイスから受信されるべきである。デバイスは、インタラプトについてモニタリング可能である。

#### 【0079】

1以上の具体例はさらに、インタラプトが規定されたリカバリ時間前に受信されない場合、デバイスについて規定されたリカバリ時間に従って完了されるべきであることを提供することができる。

#### 【0080】

少なくとも一例では、規定されたリカバリ時間は、固定的な最小リカバリ時間を含む。規定されたリカバリ時間は、デバイスに固有の通知されたリカバリ時間を含むことが可能である。

#### 【0081】

少なくとも一例では、当該能力は、デバイスに対して通知されたリカバリ時間を含み、通知されたリカバリ時間は、固定的な最小リカバリ時間より短い。

#### 【0082】

少なくとも一例では、通知されたリカバリ時間は、固定的な最小リカバリ時間の代わりに、低電力状態からアクティブ状態へのデバイスの遷移に適用可能である。

#### 【0083】

少なくとも一例では、固定的な最小リカバリ時間は、低電力状態からアクティブ状態への他のデバイスの遷移において当該他のデバイスに適用可能である。

#### 【0084】

10

20

30

40

50

少なくとも一例では、デバイスは、P C I eに準拠したデバイスを含む。低電力状態はD 3状態を含み、アクティブ状態はD 0状態を含む。

【0085】

少なくとも一例では、低電力状態からアクティブ状態へのデバイスの遷移の完了は、デバイスにコンフィギュレーションアクセスリクエストを送信することを含む。

【0086】

少なくとも一例では、デバイスは、ルートポート、ダウンストリームポート又はルートコンプレックスインテグレーテッドエンドポイント(R C I E)の少なくとも1つを含む。

【0087】

1以上の具体例はさらに、少なくとも1つのデバイスの電力管理能力を規定する電力管理能力構造を格納する機械可読媒体と、電力管理能力構造からデバイスの特定の能力を特定し、低電力状態からアクティブ状態への遷移に対して規定された固定的な最小リカバリ時間の経過前に遷移が完了されるべきである場合、特定の能力に少なくとも部分的に基づき低電力状態からアクティブ状態へのデバイスの遷移を完了させる電力管理コントローラとを提供することが可能である。

【0088】

少なくとも一例では、電力管理能力構造は、デバイスについて他のリカバリ時間が通知されているか規定する。

【0089】

少なくとも一例では、電力管理能力構造は、固定的な最小リカバリ時間より短いデバイスの他のリカバリ時間を規定する。

【0090】

少なくとも一例では、電力管理能力構造は、デバイスによってインタラプトがサポートされているか規定し、低電力状態からアクティブ状態へのデバイスの遷移が、デバイスからのインタラプトの受信に基づき完了される。

【0091】

少なくとも一例では、デバイスは、電力管理能力構造がデバイスがインタラプトをサポートしていることを示す場合、インタラプトについてモニタリングされる。

【0092】

少なくとも一例では、低電力状態からアクティブ状態へのデバイスの遷移の開始は、デバイスに電力を提供することを含む。

【0093】

本明細書を通じて“一実施例”又は“実施例”的参照は、当該実施例に関して説明された特定の機能、構造又は特性が本発明の少なくとも1つの実施例に含まれることを意味する。従って、本明細書を通じて各所における“一実施例では”又は“実施例では”という表現の出現は、必ずしも全てが同一の実施例を参照しているとは限らない。さらに、特定の特徴、構造又は特性は、1以上の実施例において何れか適切な方法により組み合わされてもよい。

【0094】

本明細書において、特定の実施例を参照して詳細な説明が与えられた。しかしながら、添付した請求項に提供される本発明の広範な趣旨及び範囲から逸脱することなく、各種変更及び改良が可能であることは明らかであろう。明細書及び図面は、限定的なものでなく例示的なものであるとみなされるべきである。さらに、実施例及び他の一例となる言語の使用は、同一の実施例又は具体例を必ずしも参照するものでなく、同一の実施例と共に異なる実施例を参照してもよい。

【0095】

以上、本発明の実施例について詳述したが、本発明は上述した特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

10

20

30

40

50

## 【符号の説明】

## 【0096】

- 100 プロセッサ

101, 102 コア

110 オンチップインターフェース

120 BTB I-TLB

125 復号化モジュール

130 アロケータリネーマユニット

135 リオーダ／リタイアメントユニット

140 スケジューラ実行ユニット

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 ロバート イー. ゴフ

アメリカ合衆国 97140 オレゴン州 シャーウッド サウスウェスト マウンテン クリーク ロード 23451

合議体

審判長 新川 圭二

審判官 高瀬 勤

審判官 山澤 宏

(56)参考文献 特開2011-34267 (JP, A)

特開2002-304237 (JP, A)

特開2007-290178 (JP, A)

特開2012-176611 (JP, A)

特開2006-221557 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F1/00