(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-72523

(P2005-72523A)

(43) 公開日 平成17年3月17日(2005.3.17)

(51) Int.CI.<sup>7</sup>H01L 25/10

H01L 25/11

H01L 25/18

F 1

H01L 25/14

Z

テーマコード(参考)

審査請求 未請求 請求項の数 17 O L (全 19 頁)

|           |                              |          |                                                   |

|-----------|------------------------------|----------|---------------------------------------------------|

| (21) 出願番号 | 特願2003-303974 (P2003-303974) | (71) 出願人 | 000005108<br>株式会社日立製作所<br>東京都千代田区丸の内一丁目6番6号       |

| (22) 出願日  | 平成15年8月28日 (2003.8.28)       | (71) 出願人 | 000100997<br>株式会社アキタ電子システムズ<br>秋田県河辺郡雄和町相川字後野85番地 |

|           |                              | (74) 代理人 | 100083552<br>弁理士 秋田 収喜                            |

|           |                              | (72) 発明者 | 加賀谷 豊<br>秋田県河辺郡雄和町相川字後野85番地                       |

|           |                              | (72) 発明者 | 株式会社アキタ電子システムズ内<br>草▲なぎ▼ 恵与<br>秋田県河辺郡雄和町相川字後野85番地 |

|           |                              |          | 株式会社アキタ電子システムズ内                                   |

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【要約】

【課題】 半導体チップの積層実装を行なう基板を共通化し、かつ信号の数の増加に対応する。

【解決手段】 半導体チップを搭載した基板を複数積層した半導体装置において、基板に形成されたリードの一端が半導体チップと接続されその他端が基板の接続端子となっており、前記リードの少なくとも一部は、接続端子近傍にて複数に分岐して、分岐した夫々のリードが異なる接続端子となっている。その製造方法において、前記基板に半導体チップを搭載する個片組み立てを行なう工程と、基板に半導体チップを搭載した状態で良品の選別を行なう工程と、選別された良品について、分岐したリードから所定のリードの導通を維持して各層の基板を個別化する工程と、個別化された基板を、所定の順に積層実装する工程とを有する。

この構成によれば、同一パターンの基板を共通化することが可能であり、スペースに余裕があるので、多くの信号を切り換えることができる。

【選択図】 図5

図5

**【特許請求の範囲】****【請求項 1】**

半導体チップを搭載した基板を複数積層した半導体装置において、

基板に形成されたリードの一端が半導体チップと接続されその他端が基板の接続端子となつてお

り、前記リードの少なくとも一部は、接続端子近傍にて複数に分岐して、分岐した夫々のリードが異なる接続端子となつてることを特徴とする半導体装置。

**【請求項 2】**

前記基板に形成されたリードは、積層される複数の基板全てに共通配線となる第1の配線と、前記積層される複数の基板の特定の層に共通となり、他の層では独立配線となる第2の配線と、前記積層される複数の基板全てに独立配線となる第3の配線とを有することを特徴とする請求項1に記載の半導体装置。 10

**【請求項 3】**

前記接続端子近傍にリード切断用の開口を設けたことを特徴とする請求項1又は2に記載の半導体装置。

**【請求項 4】**

前記分岐したリードでは、積層される各層によって異なるリードの導通を維持して各層の基板を個別化することを特徴とする請求項3に記載の半導体装置。

**【請求項 5】**

前記基板にはリード切断用の開口が対称に配置されていることを特徴とする請求項3に記載の半導体装置。 20

**【請求項 6】**

前記基板がポリイミド等を用いたフィルム状の絶縁性基体に金属膜のリードを形成したテープ基板であることを特徴とする請求項1又は2に記載の半導体装置。

**【請求項 7】**

前記基板がガラスファイバを混入させたエポキシ樹脂を用いた絶縁性基体に金属膜のリードを形成していることを特徴とする請求項1又は2に記載の半導体装置。

**【請求項 8】**

前記積層される複数の基板には、夫々同一の半導体チップが搭載されていることを特徴とする請求項1又は2に記載の半導体装置。

**【請求項 9】**

前記半導体チップがDRAMであり、複数に分岐するリードがデータ入出力コントロール信号線、データ入出力信号線であることを特徴とする請求項1又は2に記載の半導体装置。 30

**【請求項 10】**

前記リードの電源線を複数系統並設することを特徴とする請求項1又は2に記載の半導体装置。

**【請求項 11】**

前記開口部分では、開口上での配線の数を均等化するためにダミーリードを配置したことを特徴とする請求項3に記載の半導体装置。

**【請求項 12】**

前記開口で切断されるリードの切断部分の断面積が他の部分よりも小さいことを特徴とする請求項3に記載の半導体装置。 40

**【請求項 13】**

前記リードの切断を、テープ基板のインデックスとして用いることを特徴とする請求項10に記載の半導体装置。

**【請求項 14】**

半導体チップを搭載した基板を複数積層した半導体装置の製造方法において、

前記基板のリードは、一端が半導体チップと接続されその他端が基板の接続端子となつてお

り、前記リードの少なくとも一部は、接続端子近傍にて複数に分岐して、分岐した夫々のリードが異なる接続端子となっており、 50

この基板に半導体チップを搭載する個片組み立てを行なう工程と、

基板に半導体チップを搭載した状態で良品の選別を行なう工程と、

選別された良品について、分岐したリードから所定のリードの導通を維持して各層の基板を個別化する工程と、

個別化された基板を、所定の順に積層実装する工程とを有することを特徴とする半導体装置の製造方法。

【請求項 15】

前記接続端子近傍にリード切断用の開口を設け、この開口において前記複数の分岐リードの所定のリードを切断することを特徴とする請求項14に記載の半導体装置の製造方法。

10

【請求項 16】

前記分岐したリードでは、積層される各層によって異なる位置のリードの導通を維持して各層の基板を個別化することを特徴とする請求項14又は15に記載の半導体装置の製造方法。

【請求項 17】

前記開口における切断はレーザーにより行われることを特徴とする請求項15に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、半導体チップを搭載した基板を積層する半導体装置に適用して有効な技術に関するものである。

20

【背景技術】

【0002】

半導体装置の製造では、単結晶シリコン等のウェハに設けられた複数の素子形成領域に、半導体素子或いは配線パターンを一括して形成して所定の回路を構成し、隣接する素子形成領域間のスクライビング領域にてウェハを切断して、夫々の素子形成領域を個々の半導体チップとして分離するダイシングを行い、こうして分離された個々の半導体チップが、例えばベース基板に固定するボンディング等の実装工程及び樹脂封止等の封止工程を経て半導体装置として完成する。

30

【0003】

例えば、DRAM等の半導体記憶装置では、記憶容量の大容量化或いは所定容量の半導体記憶装置の省スペース化が求められており、こうした要求にこたえるために複数の半導体チップを单一の封止体に封止するSIP(System In Package)が考えられた。こうしたSIPでは、使用する複数の半導体チップがすべて良品KGD(Known Good Die)である必要があり、ペア・チップでは良品を選別する技術が充分に確立されていないことから、半導体チップを基板に取り付けた状態で選別試験を行ない、良品が取り付けられた基板のみを積層する方法が考えられた。

【0004】

このような基板としては、ポリイミド等を用いた絶縁性基体に金属膜のリードを形成したものがあり、リードはその一端が半導体チップのパッドと接続されその他端が基板の接続端子となっており、この接続端子に形成したバンプ電極によって各基板を接続している。半導体チップは接着層によって基板に固定され、リードとパッドとの接続部分は樹脂等を用いた封止材によって被覆されている。

40

【0005】

こうした積層実装で各半導体チップを接続する場合に、各半導体チップの端子の中で、例えばアドレス線のように夫々の半導体チップに共通の端子は、同一の配線パターンを用いて並列に接続することができるが、夫々の半導体チップごとに固有の端子は、夫々個別に配線を用意する必要があり、基板としては、各層ごとに異なる配線パターンのものを用意する必要がある。

50

【0006】

【特許文献1】特許公報第2695893号(第42図)

【0007】

このため、前記特許文献1には半導体チップと接続する部分のリードを複数設けて、適宜のリードを選択する技術が記載されている。

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、半導体チップの微細化の進展した近年では半導体チップ接続部分に複数のリードを配置するスペースを確保することは困難な場合が多い。半導体装置では、微細化の進展による大容量化に伴い、回路構成が複雑化・多様化しており、このため、積層実装を行なう場合に、個別に配線を用意する必要のある信号の数が増加している。

【0009】

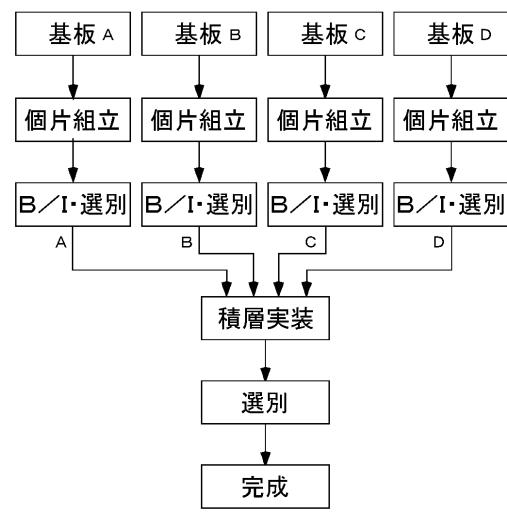

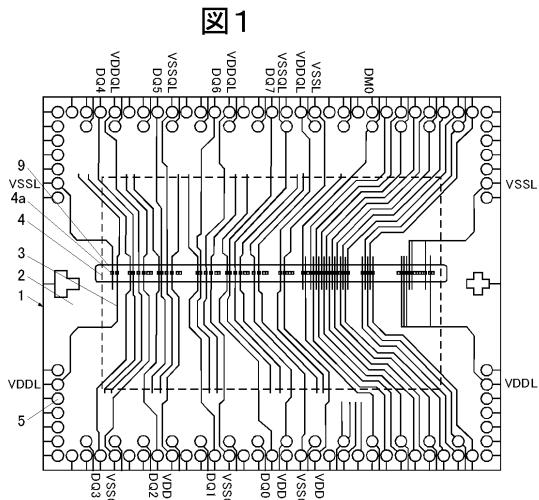

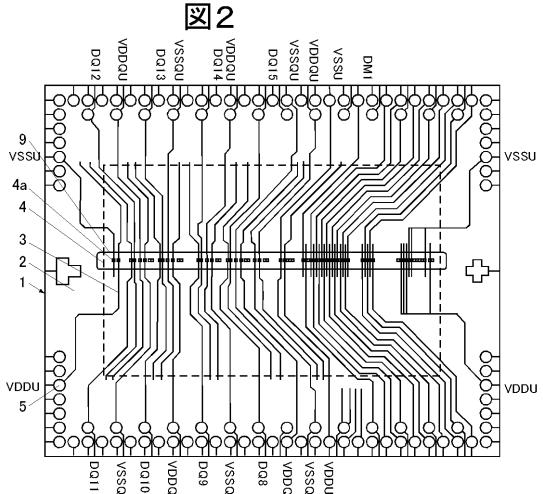

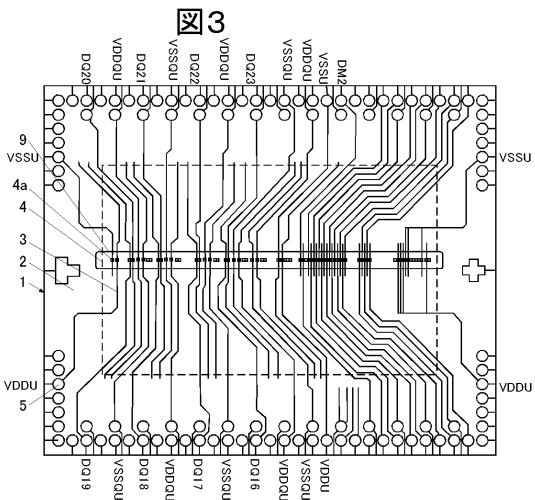

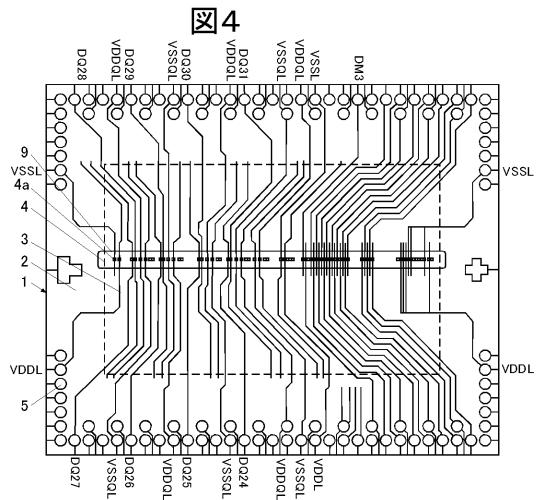

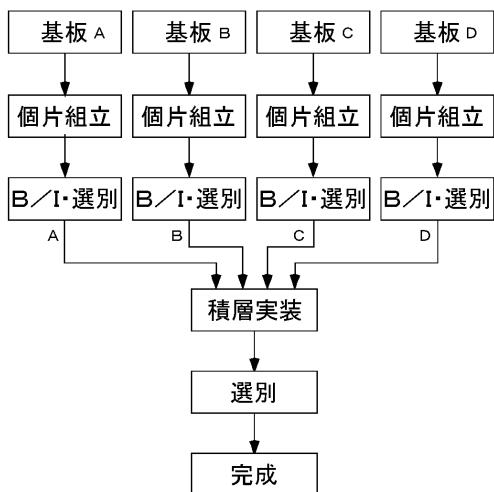

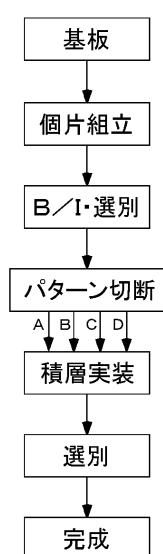

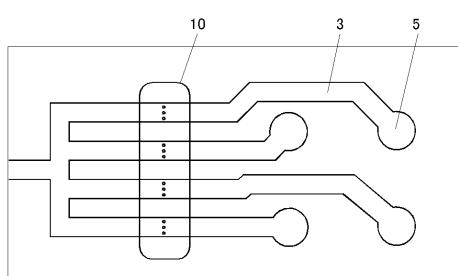

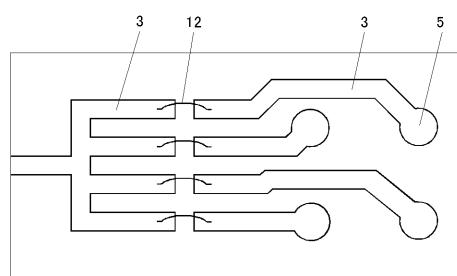

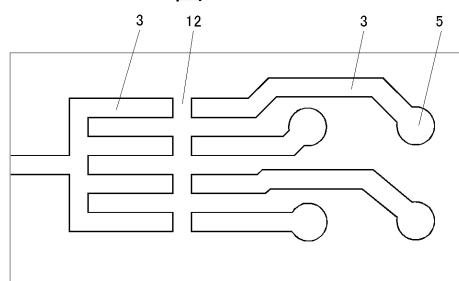

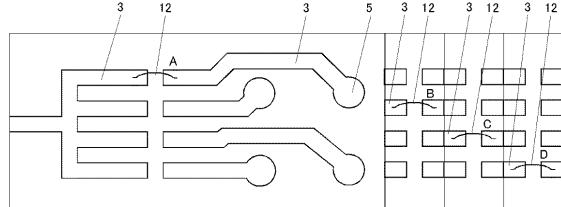

図1乃至図4は本発明者が事前に検討した先行技術である積層実装に用いられる各層のテープ基板を示す平面図である。これらのテープ基板1では、図示のようにパターンの異なる4種類のテープ基板1を用意している。図1乃至図4に示すテープ基板を用いた半導体装置の製造工程について、図5のフロー図を用いて説明する。

【0010】

各層のテープ基板1は、各層の基板A,B,C,Dの夫々について、先ず半導体チップを搭載する個片組み立てを行なった後に、バーンイン試験(B/I)・選別試験を行ない良品の選別を行なう。

【0011】

この試験の際に、例えばピン配置が異なるため、層の異なるテープ基板1(A,B,C,D)ごとに夫々の層についてプログラムを変更する必要があり、試験が煩雑になり、試験に要する時間も増大することになる。

【0012】

続いて選別された良品について、試験の前にパターン(A,B,C,D)ごとにテープ基板1が個別化されていたため、良品の選別の結果によっては、不良の発生が多かった特定の層のテープ基板1について数量が不足してしまうことがあり、その結果として、他の層のテープ基板1を有効に利用することができない場合が発生していた。

【0013】

選別されたテープ基板1は、所定の順に積層した後に、バンプ電極6を加熱溶融して互いに実装される。この後、半導体装置全体としての選別試験によって不良品を排除して、製品として完成する。

【0014】

本発明の課題は、このような信号の数の増加に対応し、半導体チップの積層実装を行なう基板を共通化することが可能な技術を提供することにある。

本発明の前記ならびにその他の課題と新規な特徴は、本明細書の記述及び添付図面によって明らかになるであろう。

【課題を解決するための手段】

【0015】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記のとおりである。

半導体チップを搭載した基板を複数積層した半導体装置において、基板に形成されたリードの一端が半導体チップと接続されその他端が基板の接続端子となっており、前記リードの少なくとも一部は、接続端子近傍にて複数に分岐して、分岐した夫々のリードが異なる接続端子となっている。

【0016】

また、半導体チップを搭載した基板を複数積層した半導体装置の製造方法において、前記基板のリードは、一端が半導体チップと接続されその他端が基板の接続端子となってお

10

20

30

40

50

り、前記リードの少なくとも一部は、接続端子近傍にて複数に分岐して、分岐した夫々のリードが異なる接続端子となっており、この基板に半導体チップを搭載する個片組み立てを行なう工程と、基板に半導体チップを搭載した状態で良品の選別を行なう工程と、選別された良品について、分岐したリードから所定のリードの導通を維持して各層の基板を個別化する工程と、個別化された基板を、所定の順に積層実装する工程とを有する。

上述した本発明によれば、テープ基板の接続端子の近傍で信号の切り換えを行なうので、スペースに余裕があり、多くの信号を切り換えることができる。加えて、リードを容易かつ確実に切断することが可能であり、同一の試験設定ですべてのテープ基板を試験することができるので、試験が容易になり、試験に要する時間も短縮する。

#### 【発明の効果】

10

#### 【0017】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記のとおりである。

(1) 本発明によれば、同一パターンのテープ基板を、接続端子近傍で分岐したリードを選択的に切断することによって回路を切り換えて積層実装の各層のテープ基板として用いることができるという効果がある。

(2) 本発明によれば、上記効果(1)により、テープ基板の接続端子の近傍で信号の切り換えを行なうので、スペースに余裕があり、多くの信号を切り換えることができるという効果がある。

(3) 本発明によれば、リード切断部分にあたるテープ基板に開口を設けてあるので、リードを容易かつ確実に切断することができるという効果がある。

(4) 本発明によれば、上記効果(1)により、形成されているリードが同一パターンとなっているため、同一の試験設定ですべてのテープ基板を試験することができるので、試験が容易になり、試験に要する時間も短縮するという効果がある。

(5) 本発明によれば、上記効果(1)により、選択される信号の数が増加・多様化に対応することが容易であるという効果がある。

(6) 本発明によれば、上記効果(4)により、選別された良品について、各層のテープ基板を個別化することができるので、層ごとにテープ基板の数量が不足することなく、テープ基板を有效地に利用することができるという効果がある。

#### 【発明を実施するための最良の形態】

30

#### 【0018】

以下、本発明の実施の形態を説明する。

なお、実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

#### 【0019】

##### (実施の形態1)

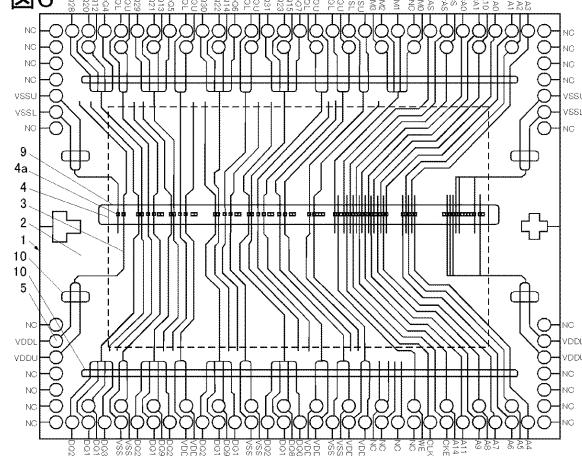

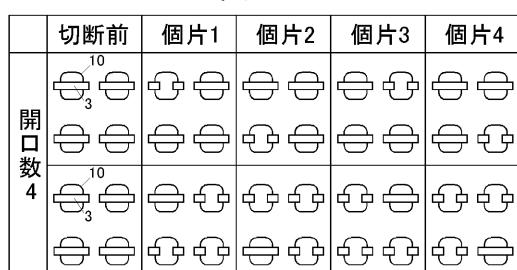

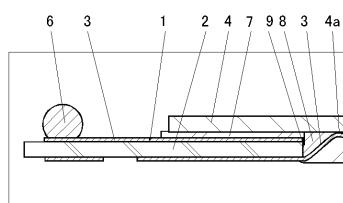

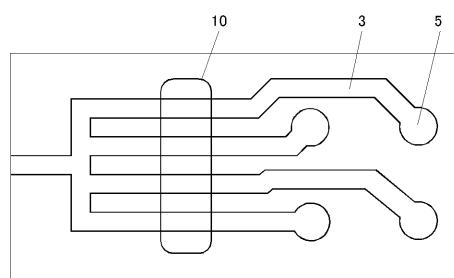

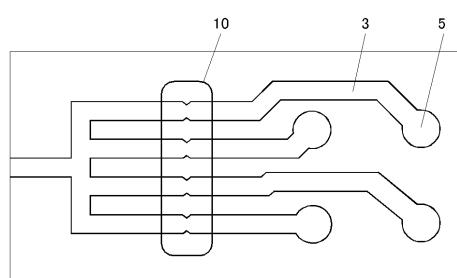

図6は、本発明の一実施の形態である半導体装置に用いられるテープ基板の半導体チップ搭載状態を示す平面図である。

テープ基板1は、ポリイミド等を用いたフィルム状の絶縁性基体2に金属膜のリード3を形成したものであり、リード3はその一端が半導体チップ4のパッド4aと接続されその他端がテープ基板1の接続端子5となっており、この接続端子5に形成したバンプ電極6によって各テープ基板を接続している。半導体チップ1は接着層7によってテープ基板1に固定され、リード3とパッド4aとの接続部分は樹脂等を用いた封止材8によって被覆されている。

#### 【0020】

40

このテープ基板は半導体チップの中央部分に列状にパッド4aを配置したセンターパッドの半導体チップ4に用いられるものであり、半導体チップ4のパッド4aに相当するテープ基板1の中央部に半導体チップ接続用の開口9が設けられ、この開口9部分でリード3の一端が半導体チップ4のパッド4aに接続され、リード3は、テープ基板1の中央から周辺部まで延びて、他端が接続端子となっている。

50

## 【0021】

このテープ基板1では、接続端子5近傍にて複数に分岐するリード3が設けられており、分岐した夫々のリード3が異なる接続端子5となっており、接続端子5近傍に設けた切断用の開口10にて分岐したリード3を容易に切断することができる。このため、分岐したリード3を選択的に切断することによって、積層構成される各層のテープ基板1を同一のテープ基板1から得ることができる。

## 【0022】

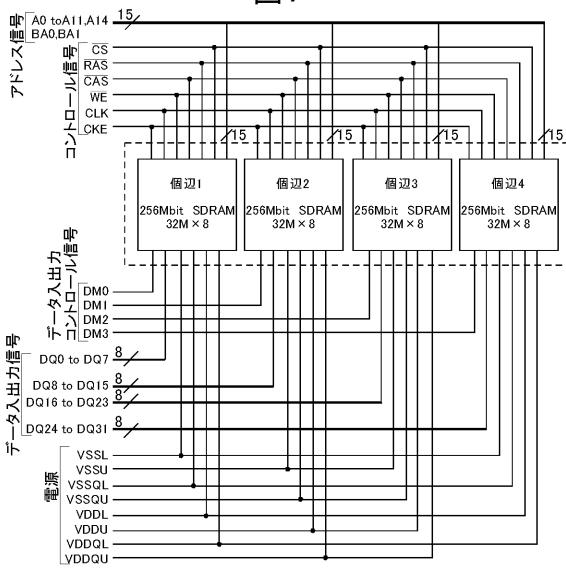

図7にロック構成を示すように本実施の形態の半導体装置は、256MbitのSDRAM半導体チップ4の同一個片を搭載したテープ基板1を4層に積層して32M-word×32bitシステム1バンクの1Gbit容量SDRAM半導体記憶装置を構成している。10

## 【0023】

積層状態となった各半導体チップ4の接続では、アドレス信号線(A0 to A11,A14,BA0,BA1)、コントロール信号線(CS,RAS,CAS,WE,CLK,CKE)は、各半導体チップに共通であり、各半導体チップ4が並列接続されているので、テープ基板1の配線パターンとしては同一のパターンを用いることができる。

## 【0024】

しかし、データ入出力コントロール信号線(DM0 to DM3)は、各半導体チップ4に固有の配線が必要であり、データ入出力信号線(DQ0 to DQ31)は各半導体チップ4に8本が個別に割り当てられ、合計で32本になっている。このため、積層されるそうによつて、データ入出力コントロール信号線、データ入出力信号線は半導体チップ4ごとに異なる接続端子5に半導体チップを接続する必要がある。20

## 【0025】

電源線については、1系統の配線に各半導体チップ4を共通接続することもできるが、本実施の形態ではノイズを低減させるために電源線を2系統(VSSL, VSSQL, VDDL, VDDQL)(VSSU, VSSQU, VDDU, VDDQU)設けて、2チップずつ夫々の系統に接続しているので、電源線については2チップずつ別の接続端子5と半導体チップ4とを接続する必要がある。なお、電源線については4本に分岐させて、各半導体チップ4に個別の配線と接続して更に配線を強化することも可能である。また、例えばクロック信号CLKを分岐させて配線を強化し、クロック信号を安定化させることも可能である。30

## 【0026】

このように、積層する各層のテープ基板1で異なる接続端子5に半導体チップ4の同一パッド4aを接続するために、本実施の形態の半導体装置では、テープ基板1の開口10にて分岐しているリード3を選択的に切断して、所定のリード3のみの導通を維持することによって、信号の切り換えを行なう。

## 【0027】

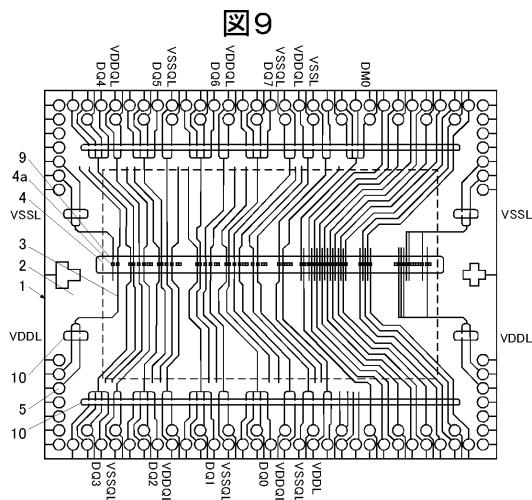

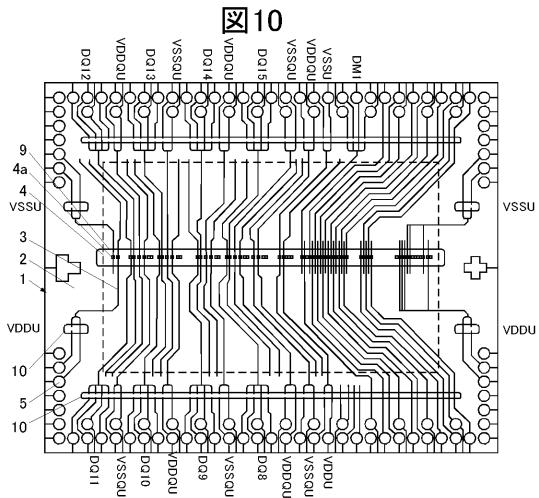

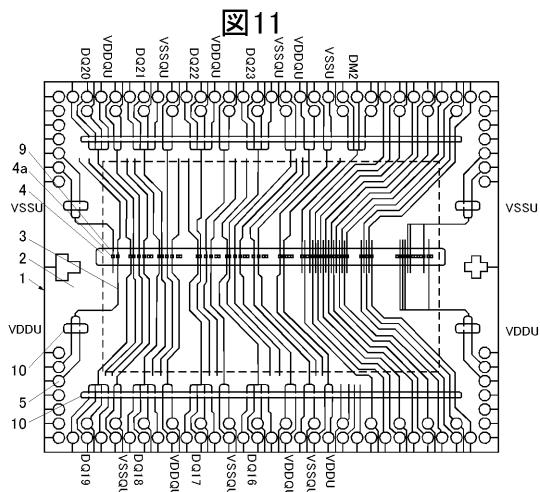

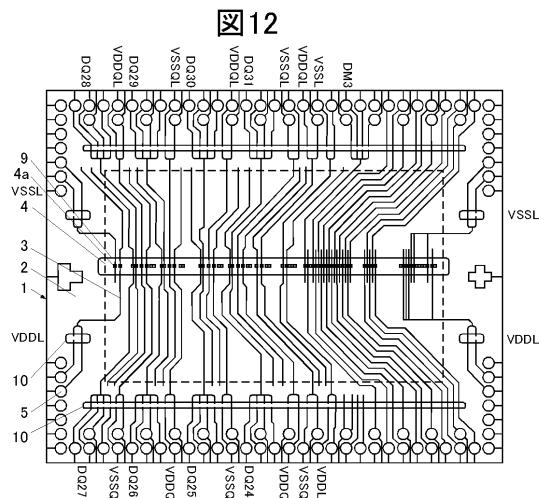

図8は、図7に示す例について、半導体チップ1個片ごとに切斷によって選択される信号を示しており、図9乃至図12は、図6に示すテープ基板1のリード3を切斷して個別化された各層のテープ基板1を示す平面図であり、各接続端子5には選択された信号を記載してある。40

## 【0028】

例えば、データ入出力コントロール信号線、データ入出力信号線については、図9乃至図12に示すテープ基板1では4本に分岐したリード3が夫々異なるリード3を残して切斷されており、その結果各層ごとに異なる接続端子5が半導体チップ4の同一パッド4aと接続されている。また、電源線については2本に分岐したリード3の何れかが切斷されており、その結果各層ごとに2系統の接続端子5を選択して半導体チップ4の同一パッド4aと接続されている。本実施の形態のテープ基板1では、テープ基板1の接続端子5の近傍で信号の切り換えを行なうので、スペースに余裕があり、多くの信号を切り換えることができる。

## 【0029】

10

20

30

40

50

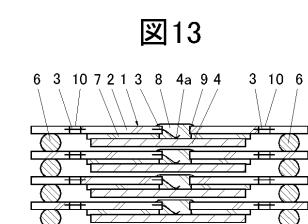

これら図9乃至図12に示す半導体チップを搭載したテープ基板を積層した状態の縦断面図を図13に示す

また、本実施の形態の半導体装置の製造工程では、図14にフロー図を示すように、同一パターンのテープ基板1について、先ず半導体チップを搭載する個片組み立てを行なった後に、バーンイン試験(B/I)・選別試験を行ない良品の選別を行なう。

#### 【0030】

この試験の際に、本実施の形態の半導体装置の製造では、パターン切断以前の1種類のテープ基板1について試験を行なうことにより、形成されているリード3が同一パターンとなっているため、同一のプログラム或いは試験設定ですべてのテープ基板1を試験することができるので、試験が簡素化され試験に要する時間も短縮することができる。

#### 【0031】

続いて、本実施の形態ではリード3を選択的に切断するパターン切断を行なって回路を切り換え、各層のテープ基板1(A,B,C,D)に個別化する。本実施の形態では良品を選別した後に各層のテープ基板1を個別化するので、層ごとにテープ基板1の数量が不足することではなく、テープ基板1を有効に利用することができる。また、リード3の切断部分に開口10を設けてあるので、小さなパンチ等を用いてリード3を容易かつ確実に切断することができる。

#### 【0032】

個別化されたテープ基板1は、図13に示すように、所定の順に積層した後に、バンプ電極6を加熱溶融して互いに実装される。この後、半導体装置全体としての選別試験によって不良品を排除して、製品として完成する。

#### 【0033】

個別化したテープ基板1は一連の工程で積層実装することもできるが、リード3を切断して個別化した状態で搬送或いは保管される場合も考えられる。そうした場合に、各層のテープ基板1を容易に識別することを求められる場合がある。そのために、リード3切断の工程を利用して、各層のテープ基板1を容易に識別することのできるインデックスを形成することが可能である。

#### 【0034】

図15乃至図18は、こうしたインデックスの例を示す部分平面図であり、インデックスは開口10を設けることができる場所であればどこでも配置することができるが、わかりやすい位置としてテープ基板1の角部等に設けることが望ましい。構成としては、半導体チップ4とは接続されない特定のリード3の切断状態によって各層のテープ基板1を識別するものである。

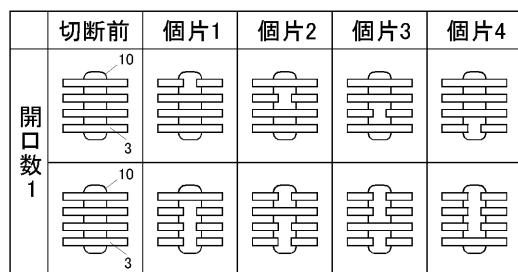

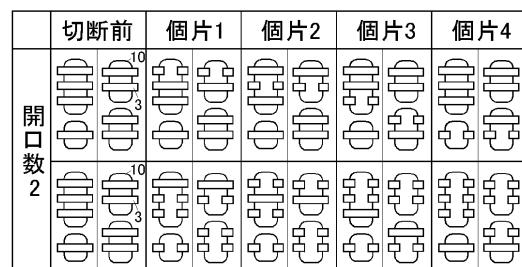

#### 【0035】

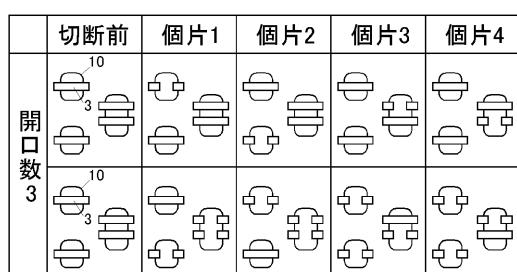

図15に示す例では、同一の開口10に4本のリード3を配置して、図中、上段に示す例では切断されたリード3の位置によって各層を識別し、下段に示す例では切断されなかったリード3の位置によって各層を識別する。この例では、4層のテープ基板1を4本のリード3で識別しているが、例えば2本のリード3によって夫々一方の切断及び双方の切断・非切断から4層のテープ基板1を識別することも可能であり、必ずしもテープ基板1の層数にリード3の数を一致させる必要はない。また、こうした各層の識別以外に、他の情報の表示として同様の方法を用いることも可能である。

#### 【0036】

図16乃至図18に示すのは、開口の数を2乃至4に変えて同様のインデックスを形成する場合を示しており、リード3を1箇所に4本収容する開口10を配置する余裕がテープ基板1にない場合等であっても、開口10を分割することによって、インデックスを配置する場所の自由度を高めることができる。

#### 【0037】

また、分岐したリード3の切斷を行なう部分としては、図19に斜線を付した部分に配置することが可能であるが、切斷後の分岐長を短くして特性を向上させるために、接続端子5の近傍に設けている。

## 【0038】

また、接続端子5の近傍では所定の接続端子5となるリード3を配置するためにスペースが予め用意されていることから、リード3を分岐させることによるスペースの増加を抑制することが可能となる。このため、信号を切り換える必要のあるリード3の数が増加しても、この増加に対応することができる。

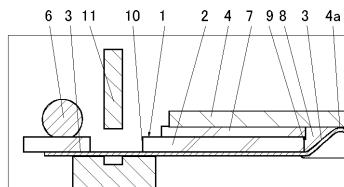

## 【0039】

なお、リード3の切断には、図20示すようにパンチ11を用いて容易に切断することができるが、それ以外に、例えば超音波を付加した加熱による切断ツールを用いてリード3を溶融切断することも可能である。

## 【0040】

他にエッティングによってリード3を部分的に一括除去することも可能であり、この場合には、テープ基板1に開口10が不要となり、図21及び図22に部分縦断面図を示すように、テープ基板1の基体2の両面にリード3を形成することが可能となる。この場合には、リード3の切断部分としては、図21に示すように半導体チップ4搭載面とした場合には図19に示す領域と同様になり、図22に示すようにその反対面とした場合には半導体チップ4搭載領域の反対面であってもよい。場合によっては、両面に切断部分を配置して、片面ずつ切断する或いは両面の切断を同時に行なうことも可能である。他にレーザ照射によってリード3を溶断することも考えられるが、この場合には開口10はあってもなくても適用することができる。

## 【0041】

図23は、切断部分を拡大して示す部分平面図である。このように通常は切断部分のリード3が他の部分のリード3と同じ幅に形成されているが、図24に示すように切断部分にV字状の切り込みを設ける、或いは図25に示すように複数の孔を列状にリード3を横断させて設けることによって、切断部分にてリード3の断面積を減少させて、リード3の切断をより確実かつ容易に行ない得る構成とすることができる。

## 【0042】

前述した説明では、所定のリード3以外のリード3を選択的に切断して、分岐したリード3から所定のリード3の導通を維持して各層のテープ基板1を個別化しているが、図26に部分拡大平面図を示すように、予め分岐しているリード3を全て切断状態として形成し、図27に部分拡大平面図を示すように、切断部分をボンディングワイヤ12によって導通させた状態で選別試験を行なった後に、図28に部分拡大平面図を示すように、選択的にボンディングワイヤ12を除去することによって各個片A, B, C, Dごとにテープ基板1を個別化することも可能である。

## 【0043】

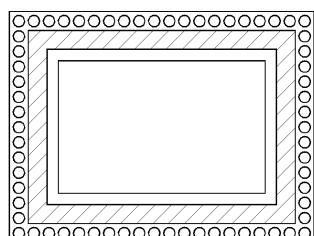

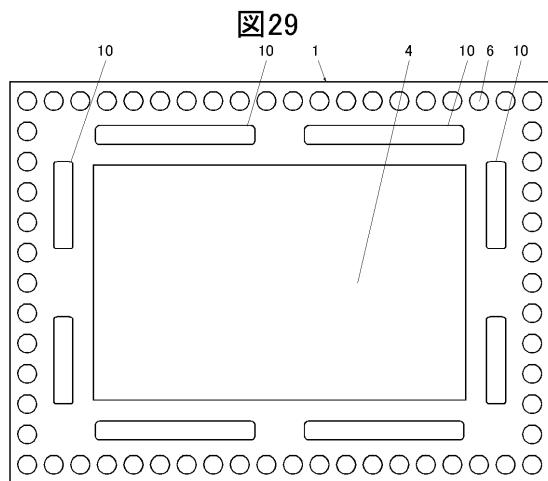

また、テープ基板1としてフィルム状の基体2を用いた場合には、テープ基板1が可撓性を有しているため変形が生じやすくなる。こうした変形を防止するために、図1に示すテープ基板1では開口10の配置を、テープ基板1全体として対称形としてあり、対称形に配置したことによりテープ基板1に加えられる力を平衡させて、テープ基板1の変形を抑制している。開口10を対称形に配置したテープ基板1の別の例を図29に示す。この例では、長辺に沿って配置された開口10が2分割されており、対称部に切断対象となるリード3がない場合であっても、ダミーの開口10を形成する。

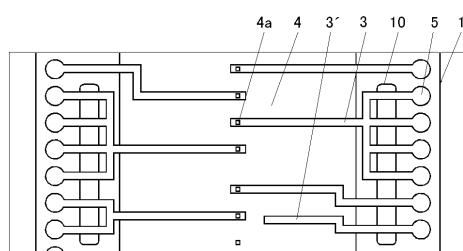

## 【0044】

こうした開口10部分では、対称位置のリード3の数によってパッケージ内で強度及び応力の平衡状態を確保してパッケージの反り等の不具合を防止する必要がある。このため、例えば図30に示すように、信号が割り当てられていないので半導体チップ4と接続しないため、リード3が不要な接続端子5であっても、ダミーリード3'を配置して開口10上での配線の数を均等化することが望ましい。

## 【0045】

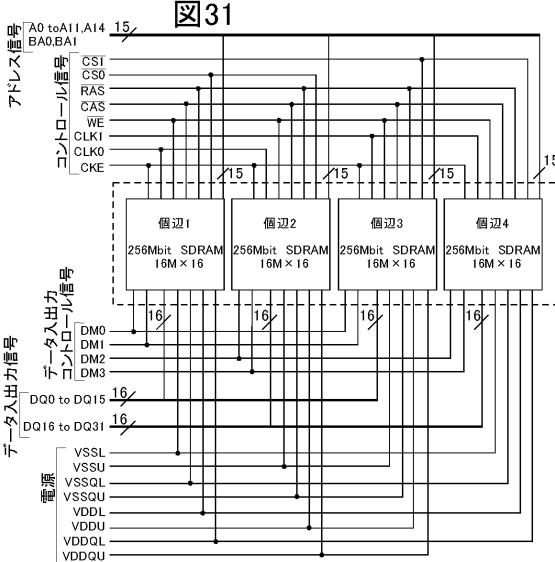

前述した説明では、256MbitのSDRAM半導体チップの個片を4層に積層して32M-word×32bitシステム1バンクの1Gbit容量SDRAM半導体記憶

10

20

30

40

50

装置を例としたが、図31に示すのは、同じく256MbitのSDRAM半導体チップの個片を4層に積層してこの例では16M-word×32bitシステム2バンクの1Gbit容量SDRAM半導体記憶装置を構成する場合のブロック構成図であり、図32は構成図に基づいて、切り換えのために選択される信号について、各リード3を明示したものである。

#### 【0046】

積層状態となった各半導体チップ4の接続では、アドレス信号線(A0 to A11,A14,BA0,BA1)、コントロール信号線(RAS,CAS,WE,CKE)は、各半導体チップに共通であり、各半導体チップ4が並列接続されているので、テープ基板1の配線パターンとしては同一のパターンを用いることができるが、コントロール信号線(CS,CLK)については、2チップずつ異なる系統に接続する必要がある。10

#### 【0047】

また、データ入出力コントロール信号線(DM0 to DM3)は、各半導体チップ4に固有の配線が必要であり、データ入出力信号線(DQ0 to DQ31)は各個片半導体チップ4に16本が2系統に割り当てられ、合計で32本になっている。このため、積層される層によって、データ入出力コントロール信号線、データ入出力信号線は半導体チップ4ごとに異なる接続端子5に半導体チップを接続する必要がある。

#### 【0048】

電源線については、1系統の配線に各半導体チップ4を共通接続することもできるが、本実施の形態ではノイズを低減するために電源線を2系統(VSSL, VSSQL, VDDL, VDDQL)(VSSU, VSSQU, VDDU, VDDQU)設けて、2チップずつ夫々の系統に接続しているので、電源線については2チップずつ別の接続端子5と半導体チップ4とを接続する必要がある。なお、電源線については4本に分岐させて、各半導体チップ4に個別の配線と接続して、更に配線を強化することも可能である。20

#### 【0049】

このように、同容量のSDRAMであっても、選択される信号の種類・数が異なっており、また、例えば積層する層数をより多層化することが考えられている。また、DRAMの他にも、半導体不揮発性記憶装置或いはSRAMの積層、半導体不揮発性記憶装置及びSRAMの積層等も検討されており、積層実装では更に選択される信号の数が増加・多様化することが考えられる。こうした場合にも、本実施の形態の半導体装置では信号の切り換えに要するスペースが少ないので、対応が容易である。30

#### 【0050】

##### (実施の形態2)

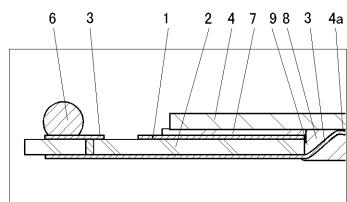

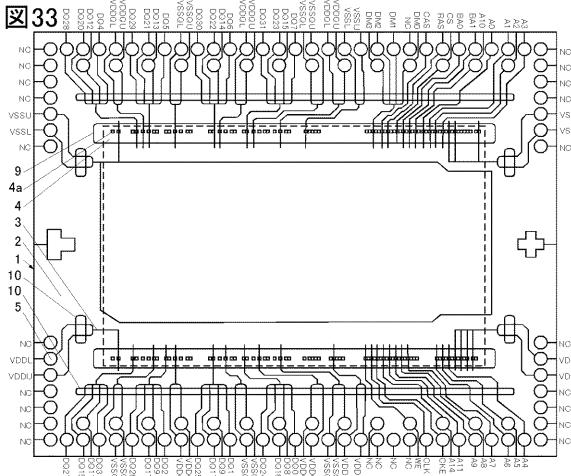

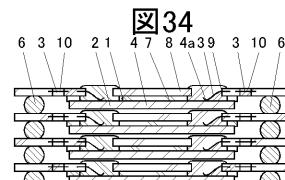

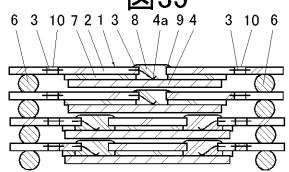

図33は、本発明の他の実施の形態である半導体装置に用いられるテープ基板の半導体チップ搭載状態を示す平面図であり、図34は半導体チップを搭載したテープ基板を積層した状態を示す縦断面図である。本実施の形態のテープ基板は半導体チップの周縁部分に列状にパッド4aを配置したコーナーパッドの半導体チップ4に用いられるものである点が前述した実施の形態とは異なっている。

#### 【0051】

テープ基板1は、ポリイミド等を用いたフィルム状の絶縁性基体2に金属膜のリード3を形成したものであり、リード3はその一端が半導体チップ4のパッド4aと接続されその他端がテープ基板1の接続端子5となっており、この接続端子5に形成したバンプ電極6によって各テープ基板を接続している。半導体チップ1は接着層7によってテープ基板1に固定され、リード3とパッド4aとの接続部分は樹脂等を用いた封止材8によって被覆されている。40

#### 【0052】

テープ基板1の半導体チップ4のパッド4aに相当する部分に半導体チップ接続用の開口9が設けられ、この開口9部分でリード3の一端が半導体チップ4のパッド4aに接続され、リード3は、ここから周辺部まで延びて、他端が接続端子となっている。

#### 【0053】

このテープ基板1では、接続端子5近傍にて複数に分岐するリード3が設けられており、分岐した夫々のリード3が異なる接続端子5となっており、接続端子5近傍に設けた切断用の開口10にて分岐したリード3を容易に切断することができる。このため、分岐したリード3を選択的に切断することによって、積層構成される各層のテープ基板1を同一のテープ基板1から得ることができる。

【0054】

このように、本発明はコーナーパッドの半導体チップ4の積層に適用することも可能であるが、更に、図35に示すようにセンターパッドの半導体チップとコーナーパッドの半導体チップとの積層を行なうことも可能である。

【0055】

以上、本発明を、前記実施の形態に基づき具体的に説明したが、本発明は、前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

【0056】

例えば、前述した説明では、可撓性のテープ基板を例にして本発明を説明したが、半導体チップを搭載する基板としては、ガラスファイバを混入させたエポキシ樹脂を用いた絶縁性基体に金属膜のリードを形成した基板等の可撓性を有していない基板を採用して本発明を実施することも可能である。

【図面の簡単な説明】

【0057】

【図1】本発明者が事前に検討した積層実装のための各層のテープ基板を示す平面図である。

【図2】本発明者が事前に検討した積層実装のための各層のテープ基板を示す平面図である。

【図3】本発明者が事前に検討した積層実装のための各層のテープ基板を示す平面図である。

【図4】本発明者が事前に検討した積層実装のための各層のテープ基板を示す平面図である。

【図5】図1乃至図4に示すテープ基板を用いた半導体装置の製造工程について説明するフロー図である。

【図6】本発明の一実施の形態である半導体装置に用いられるテープ基板の半導体チップ搭載状態を示す平面図である。

【図7】本発明の一実施の形態である半導体装置を示すブロック構成図である。

【図8】半導体チップ個片ごとに切断によって選択される信号を示す図である。

【図9】図6のテープ基板を個別化した各層のテープ基板を示す平面図である。

【図10】図6のテープ基板を個別化した各層のテープ基板を示す平面図である。

【図11】図6のテープ基板を個別化した各層のテープ基板を示す平面図である。

【図12】図6のテープ基板を個別化した各層のテープ基板を示す平面図である。

【図13】半導体チップを搭載したテープ基板を積層した状態を示す縦断面図である。

【図14】本発明の一実施の形態である半導体装置の製造工程について説明するフロー図である。

【図15】本発明の一実施の形態である半導体装置のインデックスを示す部分平面図である。

【図16】本発明の一実施の形態である半導体装置のインデックスを示す部分平面図である。

【図17】本発明の一実施の形態である半導体装置のインデックスを示す部分平面図である。

【図18】本発明の一実施の形態である半導体装置のインデックスを示す部分平面図である。

【図19】本発明の一実施の形態である半導体装置の切断部分の配置領域を示す平面図で

10

20

30

40

50

ある。

【図20】本発明の一実施の形態である半導体装置の切断状態を示す部分拡大縦断面図である。

【図21】本発明の一実施の形態である半導体装置の変形例の切断状態を示す部分拡大縦断面図である。

【図22】本発明の一実施の形態である半導体装置の変形例の切断状態を示す部分拡大縦断面図である。

【図23】本発明の一実施の形態である半導体装置の切断部分を示す部分拡大平面図である。

【図24】本発明の一実施の形態である半導体装置の変形例の切断部分を示す部分拡大平面図である。 10

【図25】本発明の一実施の形態である半導体装置の変形例の切断部分を示す部分拡大平面図である。

【図26】本発明の一実施の形態である半導体装置の切断部分の変形例を示す部分拡大平面図である。

【図27】本発明の一実施の形態である半導体装置の切断部分の変形例を示す部分拡大平面図である。

【図28】本発明の一実施の形態である半導体装置の切断部分の変形例を示す部分拡大平面図である。

【図29】本発明の一実施の形態である半導体装置に用いるテープ基板の開口配置を変えた例を示す平面図である。 20

【図30】本発明の一実施の形態である半導体装置ダミーリードを示す部分拡大平面図である。

【図31】本発明の一実施の形態の変形例である半導体装置を示すブロック構成図である。

【図32】半導体チップ個片ごとに切断によって選択される信号を示す図である。

【図33】本発明の他の実施の形態である半導体装置に用いられるテープ基板の半導体チップ搭載状態を示す平面図である。

【図34】半導体チップを搭載したテープ基板を積層した状態を示す縦断面図である。

【図35】半導体チップを搭載したテープ基板を積層した状態を示す縦断面図である。 30

#### 【符号の説明】

##### 【0058】

1 ... テープ基板

2 ... 基体

3 ... リード

3' ... ダミーリード

4 ... 半導体チップ

4a ... パッド

5 ... 接続端子

6 ... バンプ電極

7 ... 接着層

8 ... 封止材

9 ... 接続用の開口

10 ... 切断用の開口

11 ... パンチ

12 ... ボンディングワイヤ

40

【図1】

【図2】

【図3】

【図4】

【図5】

5

【図7】

义 7

【図6】

一

【 义 8 】

义 8

| 切断前接続信号<br>(共通仕様) | 切断により選択される信号 |       |       |       |

|-------------------|--------------|-------|-------|-------|

|                   | 個片1          | 個片2   | 個片3   | 個片4   |

| DQ0,8,16,24       | DQ0          | DQ8   | DQ16  | DQ24  |

| DQ1,9,17,25       | DQ1          | DQ9   | DQ17  | DQ25  |

| DQ2,10,18,26      | DQ2          | DQ10  | DQ18  | DQ26  |

| DQ3,11,19,27      | DQ3          | DQ11  | DQ19  | DQ27  |

| DQ4,12,20,28      | DQ4          | DQ12  | DQ20  | DQ28  |

| DQ5,13,21,29      | DQ5          | DQ13  | DQ21  | DQ29  |

| DQ6,14,22,30,     | DQ6          | DQ14  | DQ22  | DQ30  |

| DQ7,15,23,31,     | DQ7          | DQ15  | DQ23  | DQ31  |

| DM0,1,2,3         | DM0          | DM1   | DM2   | DM3   |

| VSSL,VSSU         | VSSL         | VSSU  | VSSU  | VSSL  |

| VSSQL,VSSQU       | VSSQL        | VSSQU | VSSQU | VSSQL |

| VDDL,VDDU         | VDDL         | VDDU  | VDDU  | VDDL  |

| VDDQL,VDDQU       | VDDQL        | VDDQU | VDDQU | VDDQL |

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

図24

【図25】

図25

【図27】

図27

【図26】

図26

【図28】

図28

【図29】

【図30】

図30

【図32】

| 切断前接続信号<br>(共通仕様) |       | 切断により選択される信号 |       |       |       |

|-------------------|-------|--------------|-------|-------|-------|

|                   |       | 個片1          | 個片2   | 個片3   | 個片4   |

| CS0,1             | CS0   | CS0          | CS0   | CS1   | CS1   |

| CLK0,1            | CLK0  | CLK0         | CLK1  | CLK1  |       |

| DQ0,16            | DQ0   | DQ16         | DQ0   | DQ16  |       |

| DQ1,17            | DQ1   | DQ17         | DQ1   | DQ17  |       |

| DQ2,18            | DQ2   | DQ18         | DQ2   | DQ18  |       |

| DQ3,19            | DQ3   | DQ19         | DQ3   | DQ19  |       |

| DQ4,20            | DQ4   | DQ20         | DQ4   | DQ20  |       |

| DQ5,21            | DQ5   | DQ21         | DQ5   | DQ21  |       |

| DQ6,22            | DQ6   | DQ22         | DQ6   | DQ22  |       |

| DQ7,23            | DQ7   | DQ23         | DQ7   | DQ23  |       |

| DQ8,24            | DQ8   | DQ24         | DQ8   | DQ24  |       |

| DQ9,25            | DQ9   | DQ25         | DQ9   | DQ25  |       |

| DQ10,26           | DQ10  | DQ26         | DQ10  | DQ26  |       |

| DQ11,27           | DQ11  | DQ27         | DQ11  | DQ27  |       |

| DQ12,28           | DQ12  | DQ28         | DQ12  | DQ28  |       |

| DQ13,29           | DQ13  | DQ29         | DQ13  | DQ29  |       |

| DQ14,30,          | DQ14  | DQ30         | DQ14  | DQ30  |       |

| DQ15,31           | DQ15  | DQ31         | DQ15  | DQ31  |       |

| DM0,2             | DM0   | DM2          | DM0   | DM2   |       |

| DM1,3             | DM1   | DM3          | DM1   | DM3   |       |

| VSSL,VSSU         | VSSL  | VSSU         | VSSL  | VSSU  |       |

| VSSQL,VSSQU       | VSSQL | VSSQU        | VSSQL | VSSQU |       |

| VDDL,VDDU         | VDDL  | VDDU         | VDDL  | VDDU  |       |

| VDDQL,VDDQU       | VDDQL | VDDQU        | VDDQL | VDDQU | VDDQL |

【図31】

【図33】

【図34】

【図35】

図35

---

フロントページの続き

(72)発明者 菊地 孝哉

秋田県河辺郡雄和町相川字後野 8 5 番地 株式会社アキタ電子システムズ内

(72)発明者 畠沢 秋彦

秋田県河辺郡雄和町相川字後野 8 5 番地 株式会社アキタ電子システムズ内