(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 695 34 968 T2 2007.02.08

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 702 406 B1

(21) Deutsches Aktenzeichen: 695 34 968.6

(96) Europäisches Aktenzeichen: 95 114 541.6

(96) Europäischer Anmeldetag: 15.09.1995

(97) Erstveröffentlichung durch das EPA: 20.03.1996

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 03.05.2006

(47) Veröffentlichungstag im Patentblatt: 08.02.2007

(51) Int Cl.<sup>8</sup>: H01L 23/48 (2006.01)

H01L 23/051 (2006.01)

H01L 25/065 (2006.01)

(30) Unionspriorität:

**24692794 15.09.1994 JP**

(84) Benannte Vertragsstaaten:

**CH, DE, FR, GB, LI, SE**

(73) Patentinhaber:

**Kabushiki Kaisha Toshiba, Kawasaki, Kanagawa,

JP**

(72) Erfinder:

**Hiyoshi, c/o Intellectual Property Div., Michiaki,

Minato-ku, Tokyo 105, JP; Muramatsu, c/o

Intellectual Property D., Hisayoshi, Minato-ku,

Tokyo 105, JP; Fujiwara, c/o Intellectual Property

Div., Takashi, Minato-ku, Tokyo 105, JP**

(74) Vertreter:

**HOFFMANN & EITLE, 81925 München**

(54) Bezeichnung: **Halbleiteranordnungen vom Druckkontaktyp**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung bezieht sich auf eine Halbleitervorrichtung vom Druckkontakttyp, insbesondere bezieht sie sich auf MOS-Gattertreibschaltvorrichtungen wie einen IGBT (Insulated Gate Bipolar Transistor) mit einer Mehrzahl von Halbleitersubstraten.

**[0002]** Konventionellerweise ist die Struktur der Druckkontakttyp-Halbleitervorrichtung nur eine gewesen, die ein einzelnes Halbleitersubstrat druckkontaktiert (hiernach bezeichnet als „Chip“). In der Druckkontakttypvorrichtung des Anodenkurztyp-GTO-(Gate Turn Off)-Thyristors schließt beispielsweise der Scheibentypchip, eine N-Typ-Emitterschicht, eine P-Typ-Basisschicht, eine N-Typ-Basisschicht und eine P-Typ-Emitterschicht von der Chipoberfläche, die die Katode ist, in Richtung der Rückseite des Chips, der die Anode ist, ein.

**[0003]** Ein N-Typ-Emitterbereich auf der Chipoberfläche wird als eine Mehrzahl von Mesas auf der P-Typ-Basisschicht gebildet. Diese N-Typ-Emitterbereiche weisen eine Aluminiumkatodenelektrode auf dem oberen Teil der Mesas auf und eine Mehrzahl von Gatterelektroden, die aus Aluminium bestehen, werden in der P-Typ-Basisschicht bereitgestellt, die durch die Mesa-Verarbeitung freigelegt werden. Auf der Rückseite des Chips werden eine Mehrzahl von P-Typ-Emitterbereichen mit einer planaren Struktur innerhalb der Oberfläche einer flachen N-Typ-Basissschicht gebildet, und der Anodenkurztyp-GTO-Thyristor wird gebildet durch Bereitstellen der Anodenelektrode, die aus Aluminium besteht, auf der gesamten Fläche davon, die sich über die N-Typbasissschicht und P-Typ-Emitterbereiche erstreckt. Die Seitenfläche des Chips ist zum Beispiel mit Siliconharz für den Isolationsschutz beschichtet.

**[0004]** Auf der Katodenelektrode auf dem oberen Teil der Mesas ist die äußere Katodenelektrode druckkontakteert, und auf der Anodenelektrode ist die äußere Anodenelektrode presskontakteert. Die oben erwähnte Druckkontakttypvorrichtung des Anodenkurztyp-GTO-Thyrisors ist offenbar in KOUKAI „Press-contact type semiconductor device“ HEI, 4-137561 (12. Mai 1992).

**[0005]** In der letzten Zeit ist ein IGBT in Erscheinung getreten als eine MOS-Gattertreibtyp-Schaltvorrichtung. Diese Vorrichtung ist durch einen Vorteil gekennzeichnet, dass sie einen Hochspannungs- und Hochstrombetrieb leicht macht, den der Bipolartransistor aufweist, und einen Vorteil, dass das Treiben leicht ist. Als die Schaltvorrichtung, die diesen IGBT verwendet, ist eine RC-(Reverse Conduction)-Typ-Schaltvorrichtung bekannt, die eine FRD (Free Wheel Diode) beinhaltet. Diese Vorrichtung ist eine, die eine FRD mit einem IGBT inversparallel ver-

bindet und in einer Modulstruktur verwendet wird. Dieses Modul ist zusammengesetzt durch Bilden eines Elektrodenmusters, das als gegebene Kollektorelektrode, Emittorelektrode, Emittersteuerungselektrode und Gatterelektrode auf dem Isolationssubstrat verwendet wird, und durch eine Lötbefestigung einer Mehrzahl von IGBT-Rückseitenkollektoren bzw. FRD-Chips auf dem Kollektorelektrodenmuster. Der Emitter auf der oberen Seite des Chips, eine Emitterssteuerung und entsprechende Elektroden des Gatters und die zugehörigen Elektrodenmuster auf dem Isolationssubstrat sind durch einen Bondingdraht entsprechend verbunden.

**[0006]** Die Oberfläche eines IGBT-Chips, die auf der Schaltvorrichtung dieser Modulstruktur befestigt ist, ist mit einem Passivierungssfilm wie einem Polyimid beschichtet, außer an dem Bondingfeld des Gatters und Emitters. Der quadratisch geformte Siliziumchip eines IGBT bildet die Kollektorelektrode des Metallmehrschichtfilms über die gesamte Oberfläche der Rückseite des Chips, um eine Lötzung zu vereinfachen.

**[0007]** Da zum Beispiel die Druckkontakttyp-Halbleitervorrichtung, die aus dem konventionellen GTO-Thyristor besteht, nur eine Struktur aufweist zum Druckkontakteieren eines Chips, bestehen Defekte, wie unten beschrieben:

(1) Ein Hochstrombetrieb des Elementes ist schwierig. Um nämlich die Strombemessung des Elementes zu erhöhen ist es notwendig geworden, die Chipgröße groß zu machen. Wenn jedoch die Chipgröße erhöht wird, werden derartige Probleme bewirkt, dass bei dem Hochgeschwindigkeitselement wie MOS-Gattertyp-Schaltungs-Vorrichtungen vom IGBT, die Möglichkeit erhöht wird, nicht wiederherstellbare Effekte zu enthalten, die eine Feinverarbeitung schwierig machen, um die Fehlerrate zu erhöhen.

(2) Eine hohe Funktionalisierung und hohe Wert-hinzufügungen sind schwierig. Wenn zum Beispiel die RC-Typ IGBT-Vorrichtung hergestellt wird, müssen zwei unterschiedliche Arten von Vorrichtungsstrukturen, IGBT und FRD auf einem Wafer hergestellt werden, wodurch der Herstellungsprozess kompliziert und die Produktion schwierig wird.

**[0008]** Wenn ferner die konventionelle Modultyp-Halbleitervorrichtung verwendet wird, um in einem Fahrzeug befestigt zu werden (für Traktionsanwendungen), werden Probleme wie unten beschrieben bewirkt:

(1) Eine Zuverlässigkeit des Leistungszyklus vom Bonding

Es wird gefordert, dass Halbleitervorrichtungen für Traktionsanwendungen haltbar sein müssen für die Leistungszyklen von 6 Millionen Zyklen bei einer Temperaturveränderung von 25°C, aber die

derzeitige Technologie kann nur eine Haltbarkeit von 3 Millionen Zyklen.

(2) Zuverlässigkeit für das thermische Schicksal der Lötschicht

Es wird gefordert, dass die Lötschicht haltbar sein muss, wie in dem Bonding, auf den Leistungszyklus von 75.000 Zyklen bei einer Temperaturveränderung von 70°C, aber die derzeitige Technologie kann nur eine Haltbarkeit von ungefähr 25.000 Zyklen.

(3) Eine Zuverlässigkeit zum Kühlen des Elementes

Konventionelle Modulyphalbleitervorrichtungen werden nur auf einer Seite der Kollektorseite gekühlt, und eine Kühlung von der Emitterelektrodenseite ist beinahe unmöglich. Daher muss der äußere Durchmesser des Elementes erhöht werden, um die Hitzeabfuhr zu erweitern. Zum Beispiel wird in dem RC-Typ-IGBT-Modul von 1200 A-2500 V Klasse der äußere Durchmesser 130 × 260 × 40 mm.

(4) Zuverlässigkeit für einen Hochtemperaturbetrieb

In Halbleitervorrichtungen für Traktionsanwendungen muss die Betriebstemperatur im Betrieb im Bereich vom -40°C–150°C sichergestellt werden, aber das Harz des Gehäusematerials ist bei derartige Temperaturen nicht haltbar.

(5) Zuverlässigkeit für einen Hochspannungsbetrieb

Da das Gehäusematerial ein Harz ist und leicht eine Kriechspur bewirkt, ist es nicht haltbar gegen einen Hochspannungsbetrieb.

(6) Zuverlässigkeit für ein Verdrahten

Da ein Verdrahten innerhalb des Moduls fein und kompliziert ist, bestehen derartige Probleme bezüglich einer Rauscherzeugung in dem Gatterschaltkreis infolge der Verdrahtungsinduktivität und eine Erzeugung von Spannungsspitzen zur Zeit einer Diodenwiederherstellung.

**[0009]** Relevanter Hintergrundstand der Technik ist beschrieben in EP-A-0 476 661 und US-A-5 267 687.

**[0010]** EP-A-0 476 661 des vorliegenden Anmelders beschreibt eine Druckkontakt-Halbleitervorrichtung mit einem monolithischen Halbleitersubstrat mit Halbleiterschichten, die aus einem Anodenkurzverschaltungstyp-GTO-Thyristor bestehen, mit Katoden und Gatterelektroden, die auf der oberen Oberfläche dessen gebildet sind, und einer Elektrode, die auf der unteren Oberfläche dessen gebildet ist. Das Substrat ist zwischen einem Paar von Elektrodenplatten gesandwiched, die wiederum zwischen einem Paar von äußeren Elektroden gesandwiched sind. Zusätzlich ist eine Weichmetallplatte zwischen der oberen Elektrodenplatte und der unteren Oberfläche des Halbleitersubstrates zwischen angeordnet. Die Seitenoberflächen des Substrates sind durch einen Passivierungsfilm beschichtet, der aus einem Silikonharz bei-

spielsweise gefertigt ist.

**[0011]** US-A-5 267 867 beschreibt eine Packung für mehrfach entfernbare integrierte Schaltkreise, wobei mehrfach integrierte Schaltkreischips auf einer oberen Oberfläche eines flexiblen Schaltkreisblattes angeordnet sind. Das flexible Schaltkreisblatt und die mehrfachen Halbleiterchips sind zwischen einem thermisch leitfähigen Deckel und einer festen Platte gesandwiched. Die Umgebung derartiger Chips ist umgeben von einem erhöhten Anpassungstemplate, das durch Ätzen eines Photoresists auf dem flexiblen Schaltkreisblatt gebildet wird. Die mehrfachen Chips sind dadurch fest an der Stelle gehalten. Elastische Felder, die zwischen dem flexiblen Schaltkreisblatt und der festen Platte angeordnet sind, übertragen einen Druck von der festen Platte auf das flexible Schaltkreisblatt, das dadurch in einen Presskontakt mit dem Chip gebracht wird, das auf der oberen Oberfläche dessen angeordnet sind. Da die erhöhten Anpassungstemplates integral mit dem flexiblen Schaltkreisblatt gebildet sind, sind die mehrfachen Chips nicht frei sich in einer Ebene parallel zu der Oberfläche des flexiblen Schaltkreisblattes zu bewegen und sind anstelle dessen in einem Array bzw. Feld angeordnet, mit Abständen zwischen den erhöhten Anpassungstemplates, die benachbarte Chips enthalten.

**[0012]** Die vorliegende Erfindung ist vor diesem Hintergrund erstellt worden. Es ist daher die Aufgabe der vorliegenden Erfindung planare Schaltungsvorrichtungen vom MOF-Gattertreib-Typ bereitzustellen, die eine hohe Zuverlässigkeit aufweisen und geeignet sind für Traktions- und industrielle Anwendungen, durch Angeben einer Druckkontaktestruktur auf der Mehrfachchiptyvorrichtung.

**[0013]** Die vorliegende Erfindung ist dadurch gekennzeichnet, dass ein Chiprahmen, der aus einem synthetischen Harz gefertigt ist, auf jeder Umgebung der mehrfachen Halbleiterchips befestigt wird, die MOS-Gattertreibtypchips enthalten, wobei jeder Chip in der gleichen Ebene angeordnet ist, um so gegen den Chiprahmen dessen zu grenzen, und diese presskontaktiert sind und gesichert sind durch die erste Elektrodenplatte und die zweite Elektrodenplatte. Ferner wird durch Regulieren der äußeren Umgebung der angeordneten Mehrfachhalbleiterchips unter Verwenden des äußeren Rahmens, der zwischen der ersten Elektrodenplatte und der zweiten Elektrodenplatte eingefügt wird, jeder Chip positioniert.

**[0014]** Gemäß der Erfindung wird eine Druckkontakttyp-Halbleitervorrichtung bereitgestellt gemäß Anspruch 1.

**[0015]** Ferner kann so dargestellt werden, dass zwischen der ersten Elektrodenplatte und der zweiten Elektrodenplatte ein äußerer Rahmen isolierenden

Harzes befestigt ist, derart, dass dieser äußere Rahmen einen kreisförmigen Körper aufweist, der die Seitenflächen der ersten und zweiten Elektrodenplatten einschließt, und einen Vorsprung, der sich von der inneren Wand zu der Innenseite dieses kreisförmigen Körpers erstreckt (zum Beispiel siehe **47** in [Fig. 1](#) und [Fig. 2](#)), wobei die Mehrfachhalbleitersubstrate auf der gleichen Ebene angeordnet sind, die durch diesen Vorsprung eingeschlossen wird, um die Chiprahmen aneinander angrenzend zu machen, nachfolgend druckkontakteert durch die erste und zweite Elektrodenplatte.

**[0016]** Zwischen der ersten Elektrodenplatte oder zweiten Elektrodenplatte, oder der ersten und zweiten Elektrodenplatte und dem Halbleitersubstrat, kann eine thermische Pufferplatte zwischengelegt sein. Oder eine dickeneinstellende Platte bestehend aus einem Weichmetallblatt kann zwischengelegt werden, um gegen die Druckkontakteebene der ersten Elektrodenplatte oder zweiten Elektrodenplatte oder der ersten und zweiten Elektrodenplatte anzugrenzen. Auf der Druckkontakteebene der ersten Elektrodenplatte oder zweiten Elektrodenplatte oder der ersten und zweiten Elektrodenplatte kann in der Umgebung des vorbestimmten Teils ein Graben gebildet sein, gegenüber dem Halbleitersubstrat, um die Beanspruchung zur Zeit einer Druckkontakteierung gleichmäßig auf den Chip anzuwenden. So wird ein Gatterelektrodenkontaktbereich in dem Teil der Emitteroberfläche des Halbleitersubstrates gebildet, wobei der Chiprahmen einen Erstreckungsteil aufweist, der sich von der oberen Kantenecke des Rahmens zu ihrem Inneren erstreckt, wobei der Erstreckungsteil den Gatterelektrodenkontaktbereich abdeckt, wo Tastköpfe, die mit der Gatterelektrode verbunden sind, bereitgestellt werden können.

**[0017]** Der Chiprahmen eines synthetischen Harzes, der auf der Umgebung der entsprechenden Chips befestigt ist, spielt eine Rolle als Positionierungsführung ebenso wie ein Schützen der Isolierung der Umgebung, um es möglich zu machen die Chips und die Druckkontakteplatte auf einer minimalen Größe zu fixieren. Der äußere Rahmen, der die äußere Umgebung des Chiprahmens einschließt, ordnet die Chiprahmen genau an und ermöglicht die Positionsbeziehung der Gatterelektrode genau zu bestimmen, und die Chips in einer hohen Dichte anzutragen. Ferner besteht die Dickeneinstellplatte aus einem Weichmetallblatt, mit einer Duktilität wie Silber, das zwischen dem Chip und der Elektrodenplatte eingefügt wird, was ermöglicht Chips mit unterschiedlichen Dicken gleichförmig mit Druck zu kontaktieren. Die thermische Pufferplatte gibt die thermische Beanspruchung der Halbleitervorrichtung frei und der auf der Druckkontakteebene gebildete Graben der Elektrodenplatte gibt die Beanspruchungskonzentrierung an die Chipumgebung frei. Der Erstreckungsbereich des Chiprahmens, der den Kontaktbereich der Gat-

terelektrode abdeckt, erleichtert die Verbindung mit dem Kontaktbereich der Gatterleitung, während der Kontaktbereich geschützt wird.

**[0018]** Diese Erfindung kann vollständiger aus der folgenden detaillierten Beschreibung verstanden werden, wenn sie zusammen mit den beigefügten Zeichnungen genommen wird, in denen

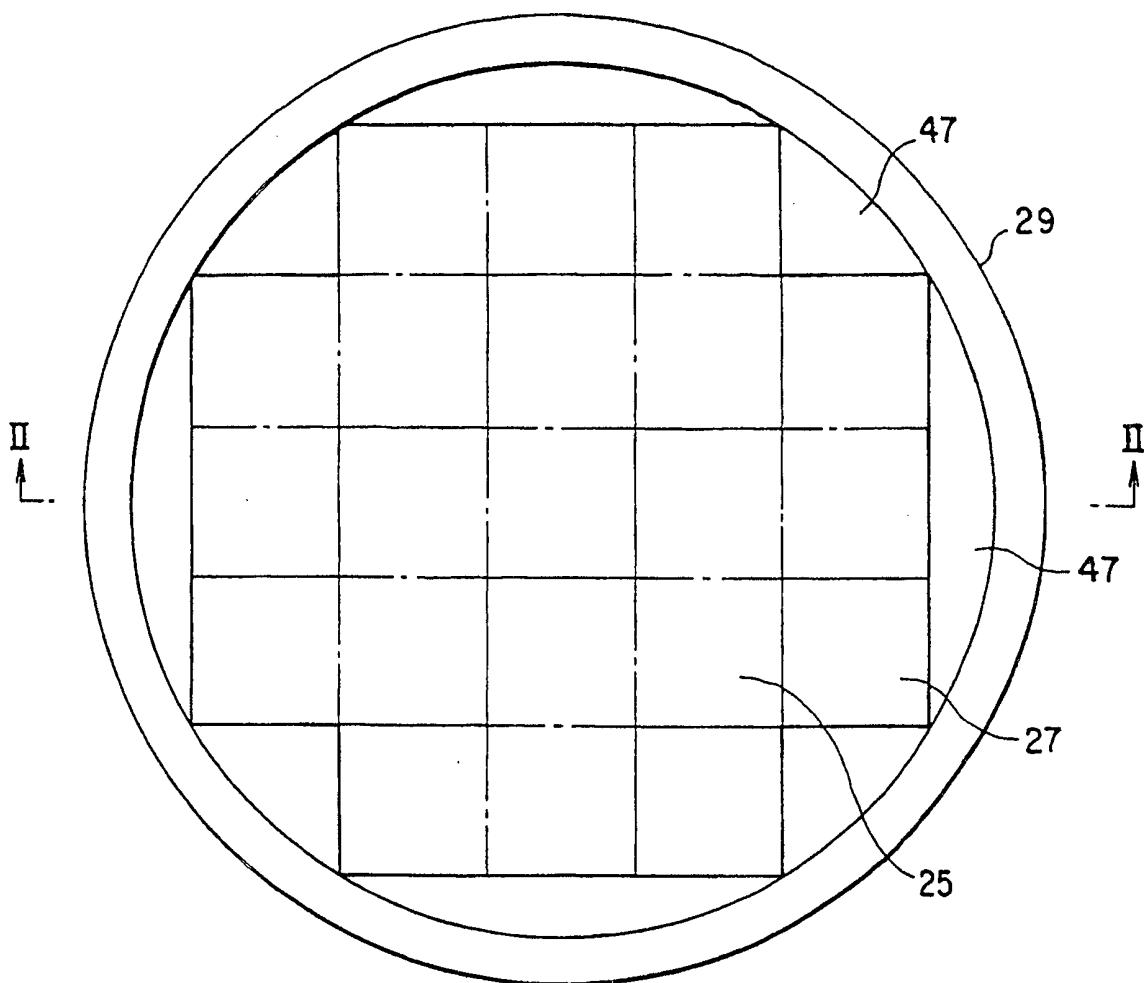

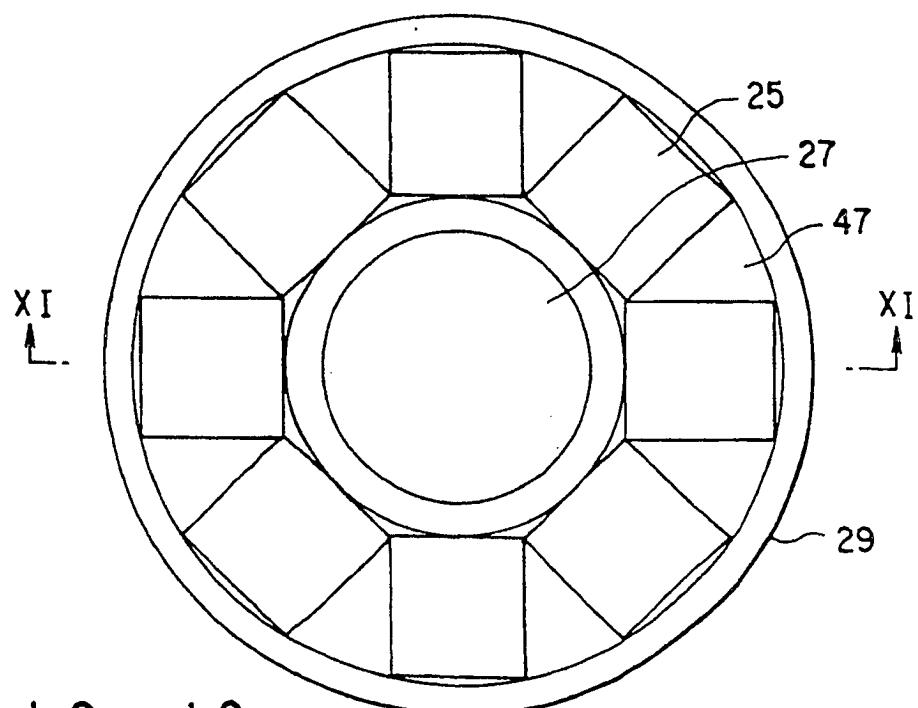

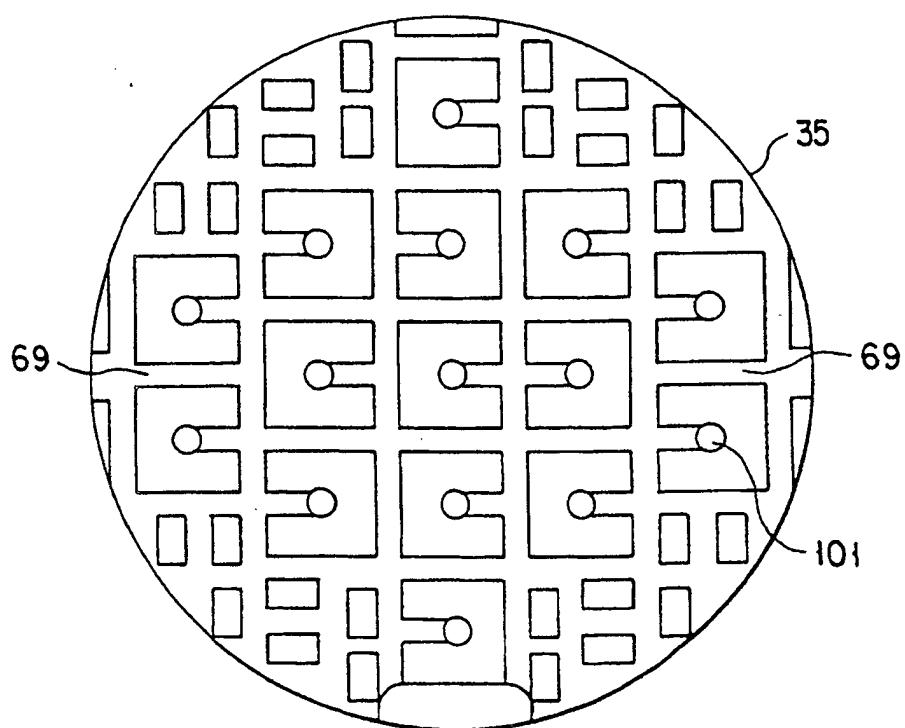

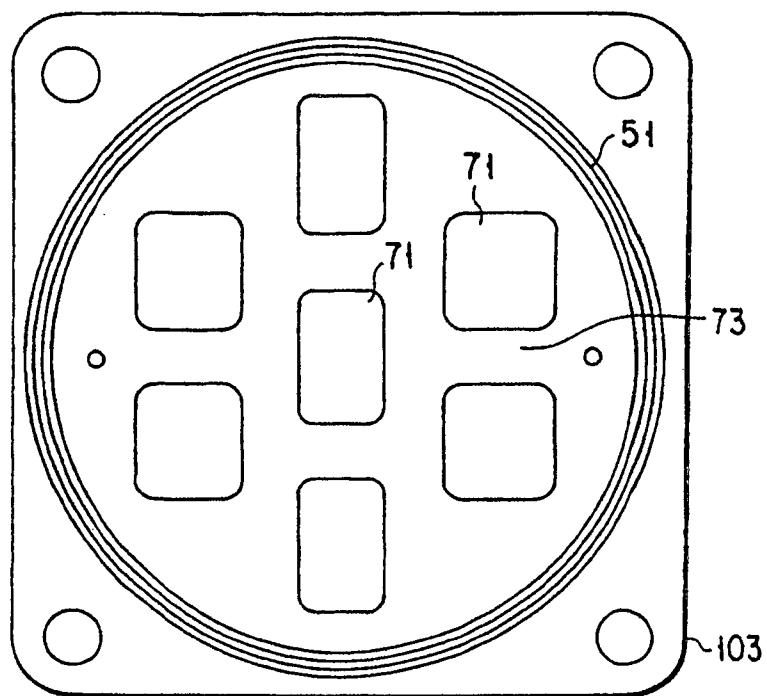

**[0019]** [Fig. 1](#) eine Aufsicht der Halbleitervorrichtung in der ersten Ausführungsform der vorliegenden Erfindung ist;

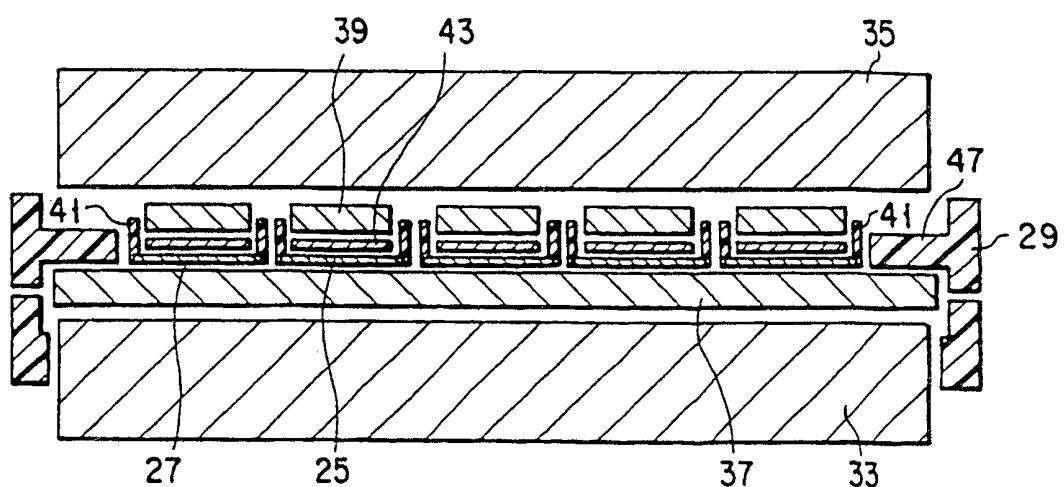

**[0020]** [Fig. 2](#) eine Schnittansicht eines Bereiches entlang der Linie II-II von [Fig. 1](#) ist;

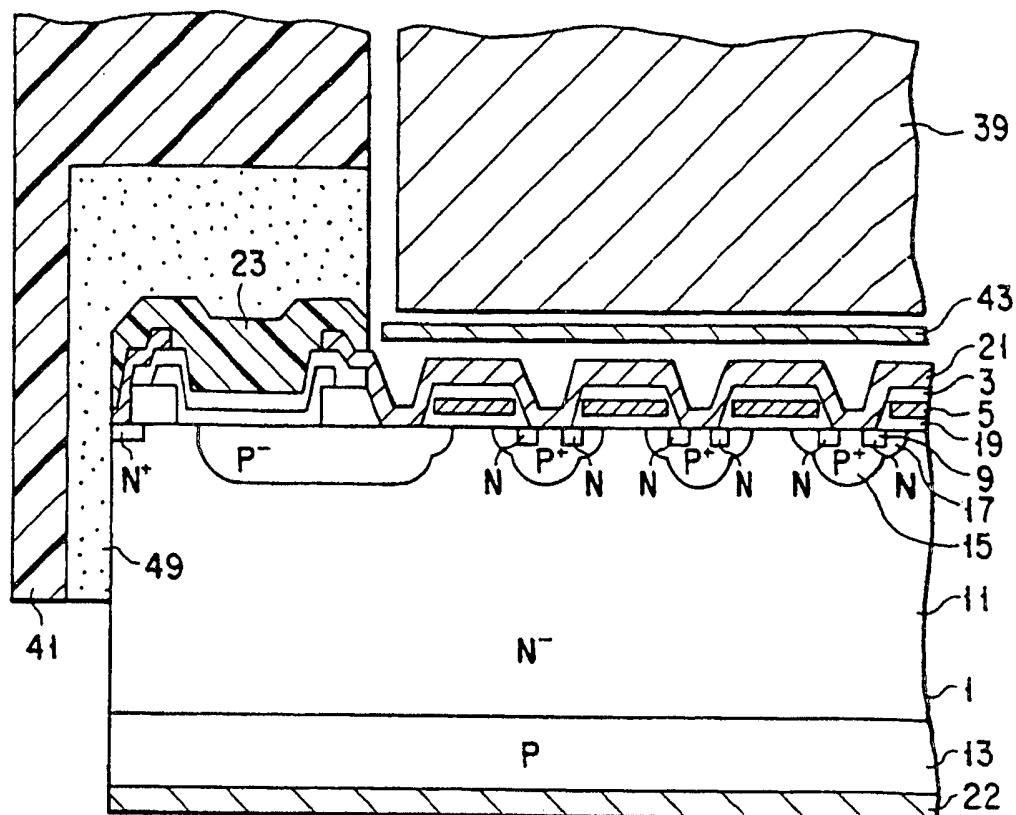

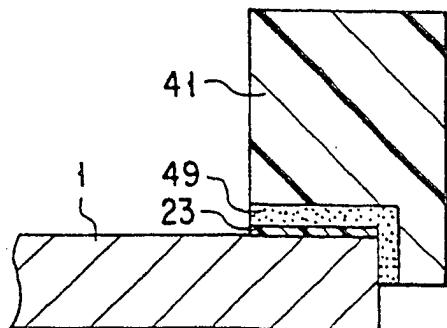

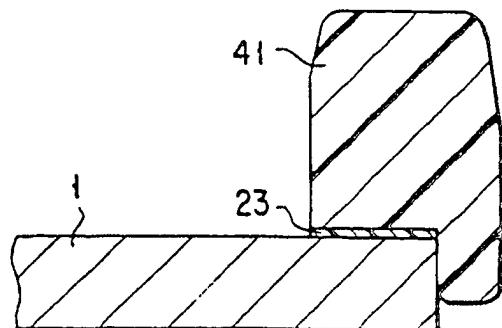

**[0021]** [Fig. 3](#) eine Schnittansicht des äußeren Bereiches des Halbleitersubstrates ist;

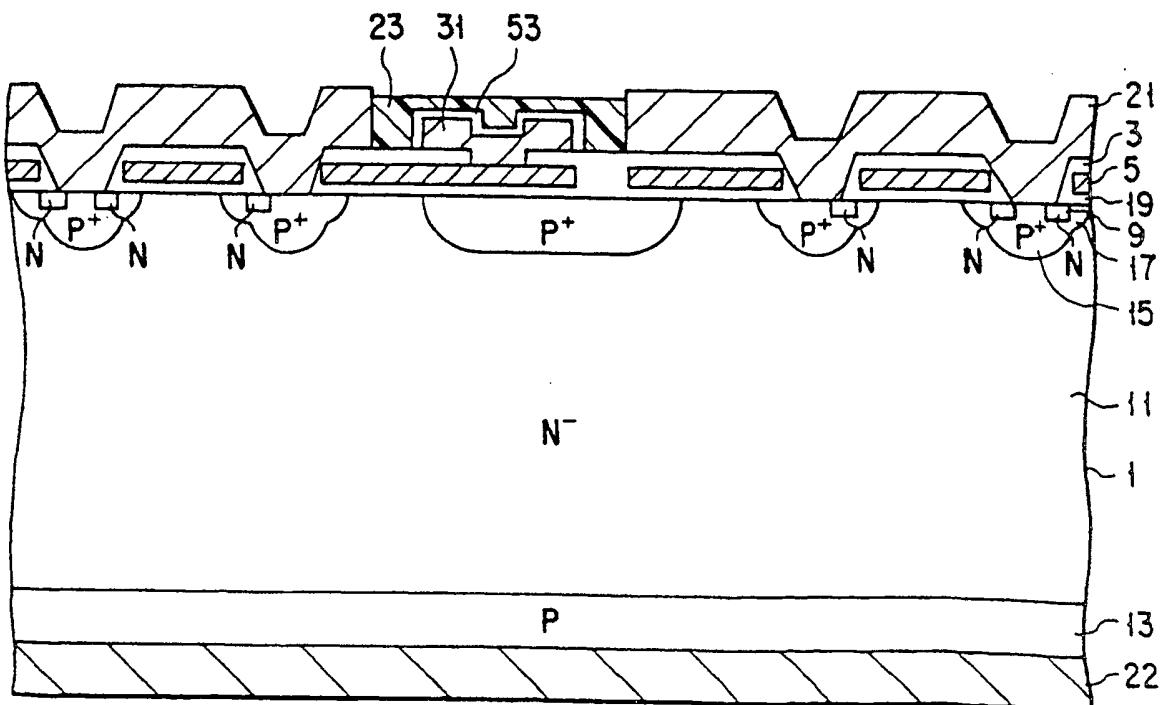

**[0022]** [Fig. 4](#) eine Schnittansicht des zentralen Bereiches des Halbleitersubstrates ist;

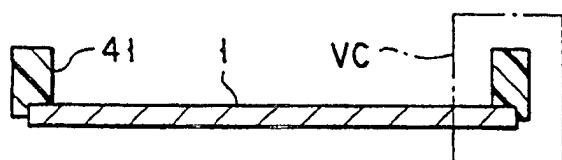

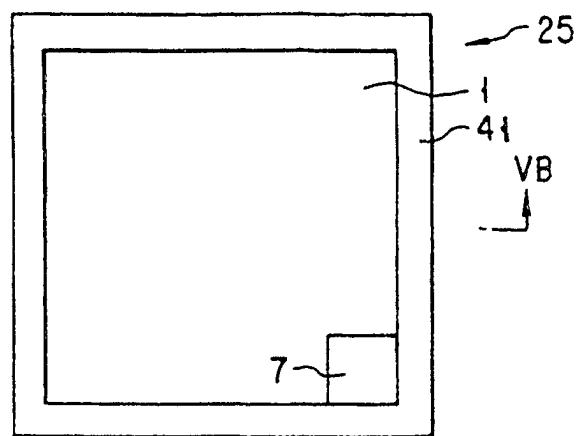

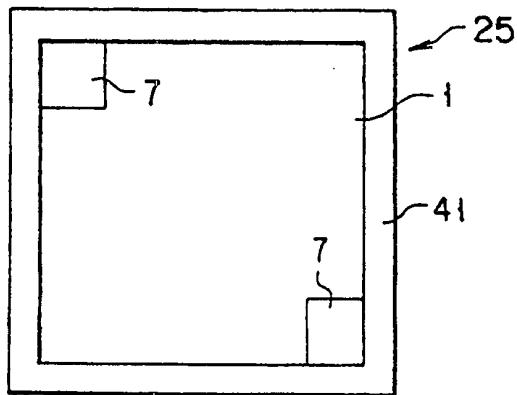

**[0023]** [Fig. 5A](#) eine erste Aufsicht des Halbleitersubstrates ist;

**[0024]** [Fig. 5B](#) eine Schnittansicht entlang der Linie VB-VB des Halbleitersubstrates ist;

**[0025]** [Fig. 5C](#) eine erste vergrößerte Schnittansicht des Bereiches VC von [Fig. 5B](#) ist;

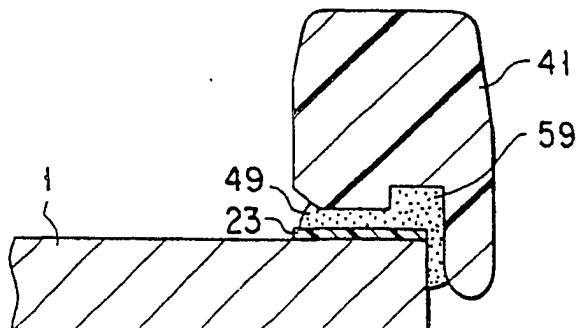

**[0026]** [Fig. 6](#) eine zweite vergrößerte Schnittansicht des Bereiches VC von [Fig. 5B](#) ist;

**[0027]** [Fig. 7](#) eine zweite vergrößerte Schnittansicht des Bereiches VC von [Fig. 5B](#) ist;

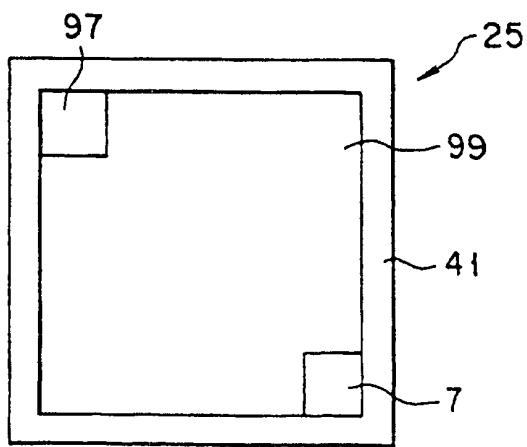

**[0028]** [Fig. 8A](#) eine zweite Aufsicht des Halbleitersubstrates ist;

**[0029]** [Fig. 8B](#) eine dritte Aufsicht des Halbleitersubstrates ist;

**[0030]** [Fig. 8C](#) eine vierte Aufsicht des Halbleitersubstrates ist;

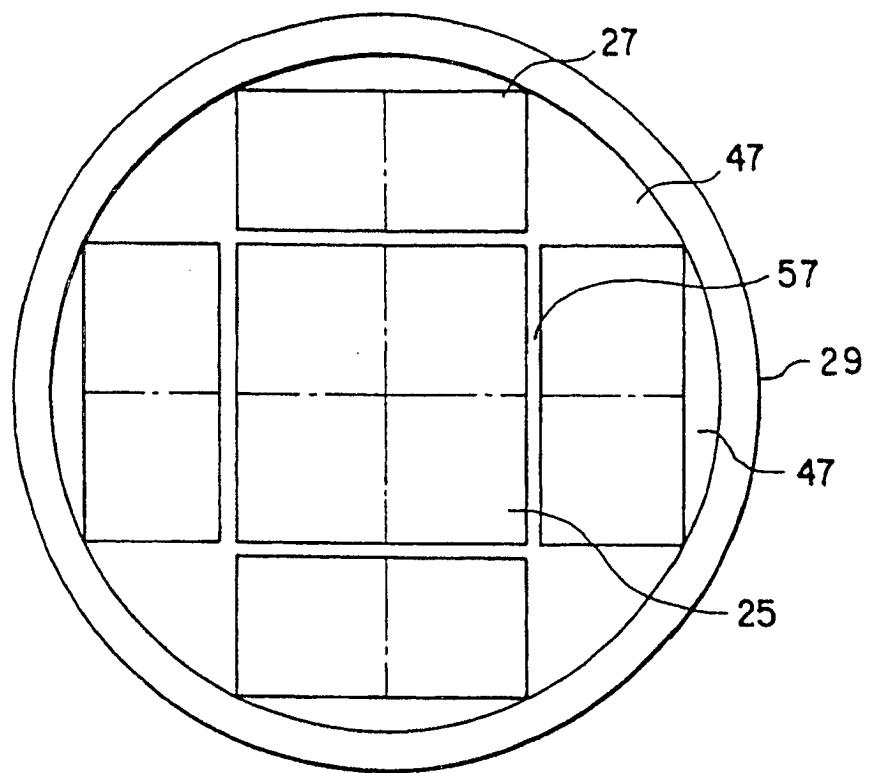

**[0031]** [Fig. 9](#) eine Aufsicht einer modifizierten Ausführungsform der Halbleitervorrichtung ist, die in [Fig. 1](#) gezeigt ist;

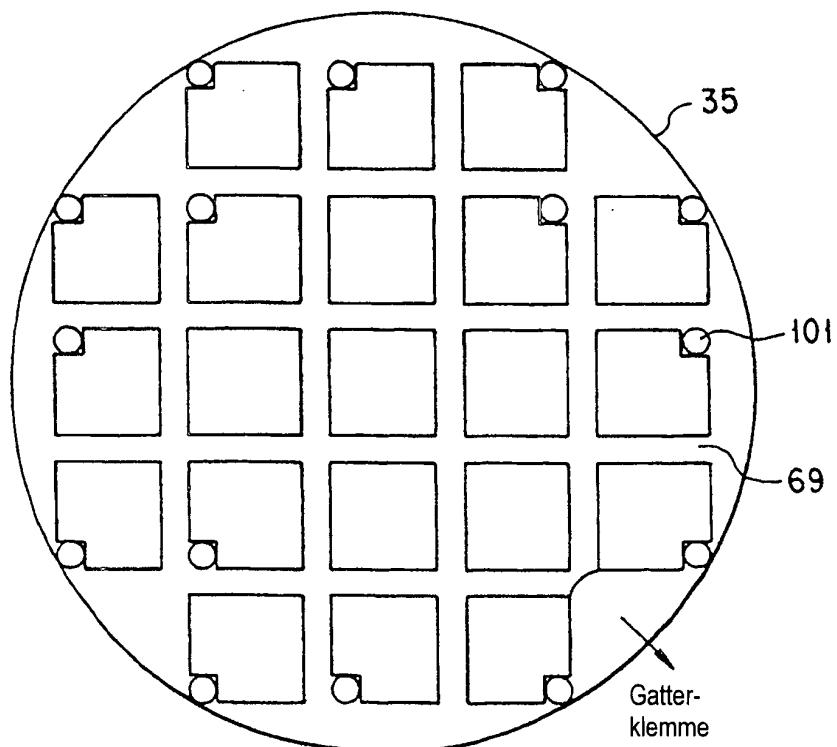

**[0032]** [Fig. 10](#) eine Aufsicht der Halbleitervorrichtung in der zweiten Ausführungsform der vorliegenden Erfindung ist;

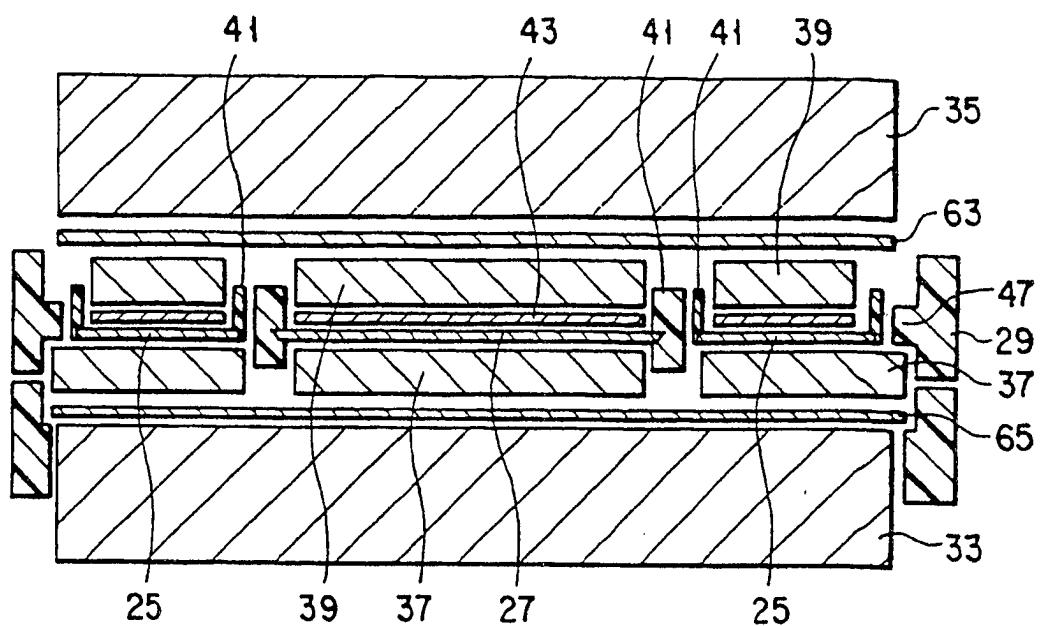

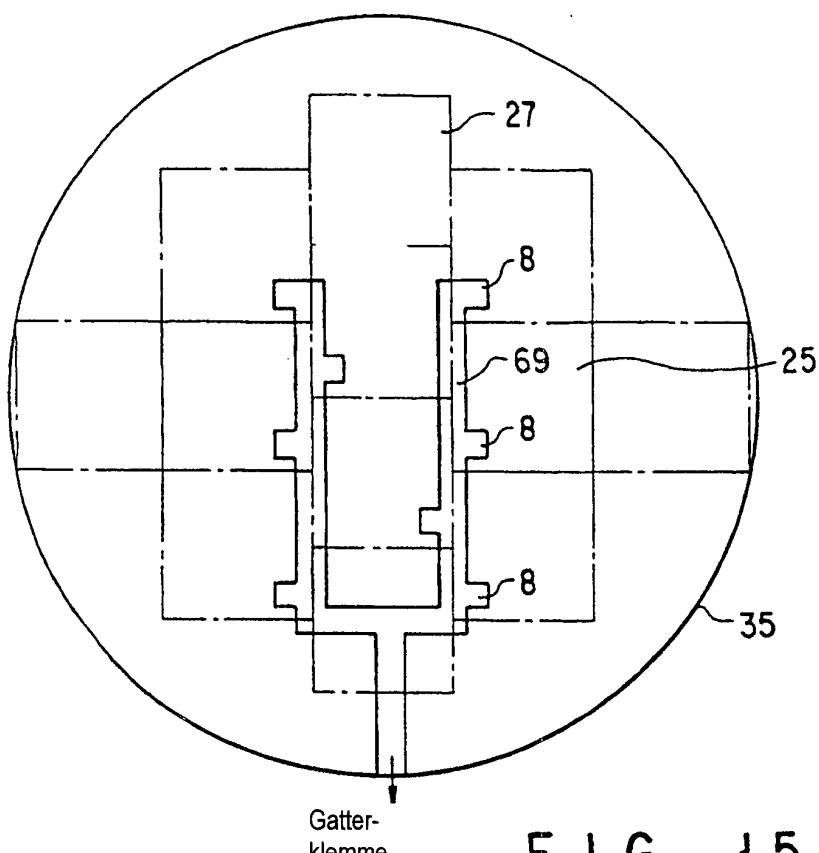

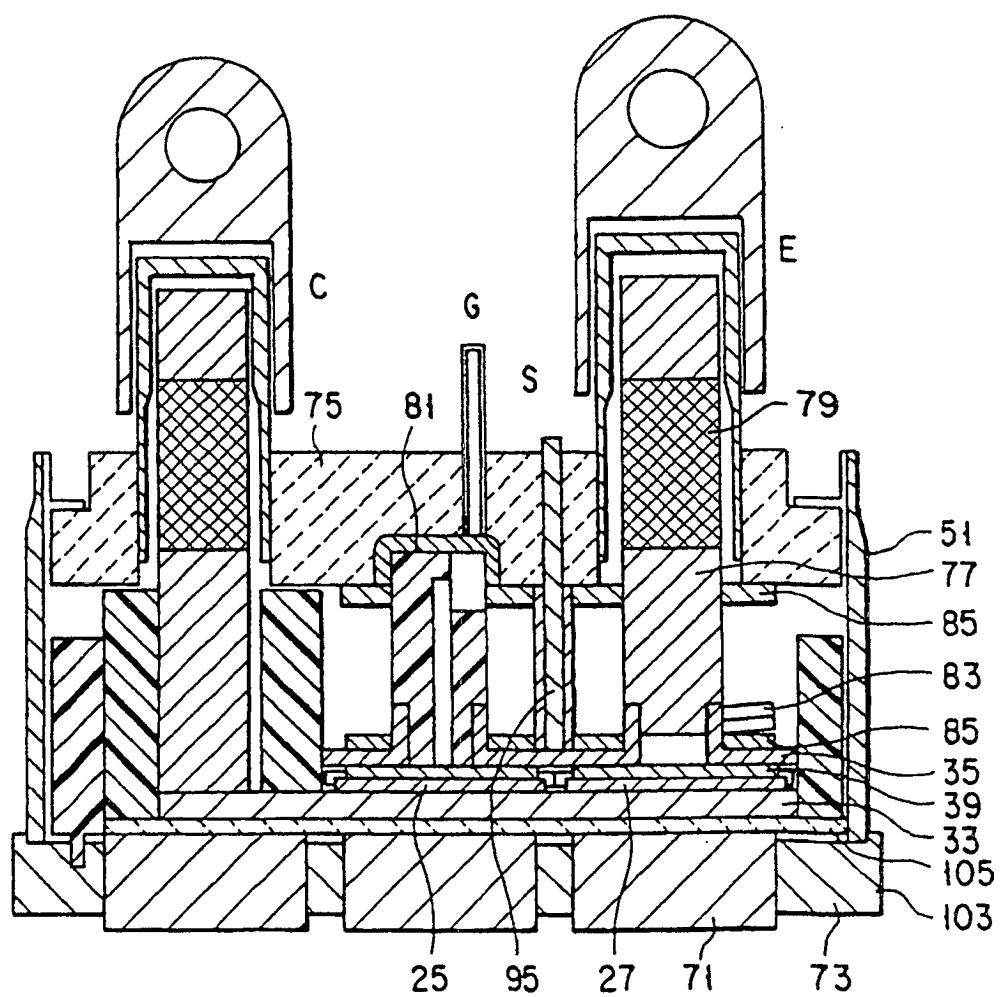

**[0033]** [Fig. 11](#) eine Schnittansicht eines Bereiches entlang der Linie XI-XI von [Fig. 10](#) ist;

**[0034]** [Fig. 12](#) eine Schnittansicht eines Bereiches in der dritten Ausführungsform ist;

[0035] [Fig. 13](#) eine Schnittansicht eines Bereiches in der vierten Ausführungsform ist;

[0036] [Fig. 14](#) eine erste Aufsicht einer Emitterelektrodenplatte ist;

[0037] [Fig. 15](#) eine zweite Aufsicht einer Emitterelektrodenplatte ist;

[0038] [Fig. 16](#) eine dritte Aufsicht einer Emitterelektrodenplatte ist;

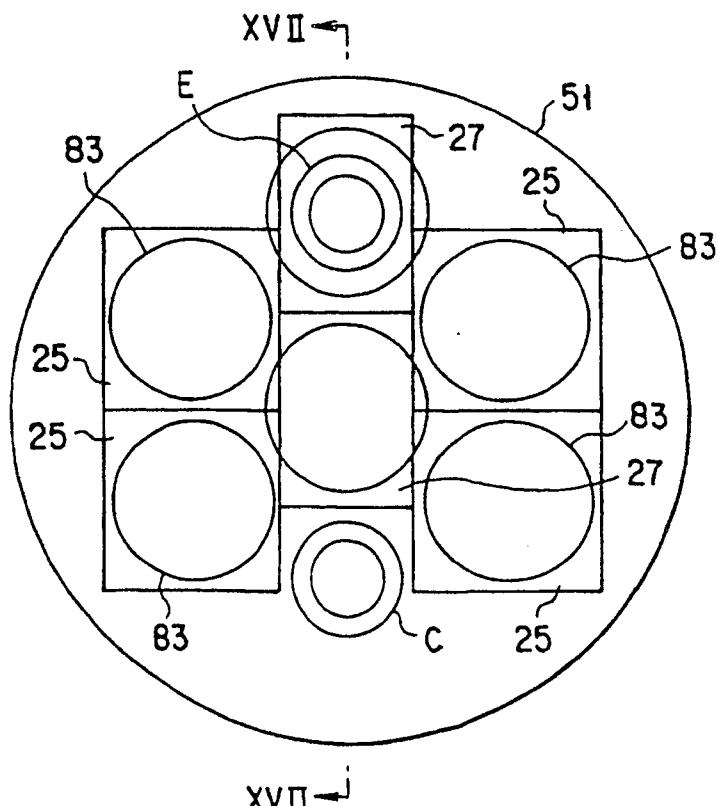

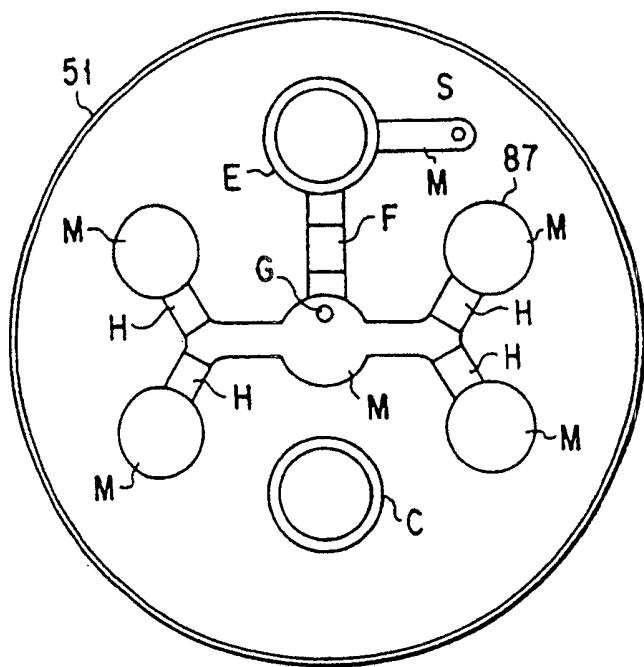

[0039] [Fig. 17](#) eine Schnittansicht der Halbleitervorrichtung in der fünften Ausführungsform ist;

[0040] [Fig. 18](#) eine Aufsicht der Basis der Halbleitervorrichtung ist, die in [Fig. 17](#) gezeigt ist;

[0041] [Fig. 19](#) eine Aufsicht der Chipanordnung der in [Fig. 17](#) gezeigten Halbleitervorrichtung ist;

[0042] [Fig. 20](#) eine Aufsicht der keramischen Kappe der in [Fig. 17](#) gezeigten Halbleitervorrichtung ist;

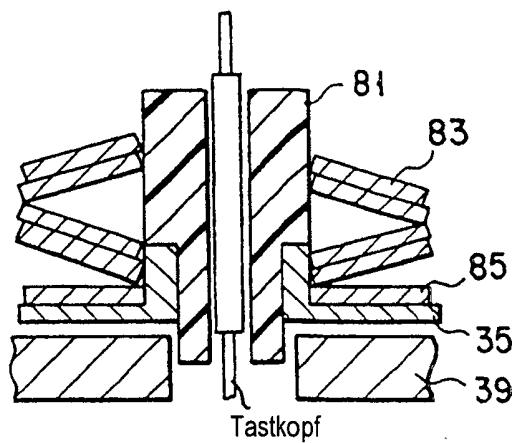

[0043] [Fig. 21](#) eine Schnittansicht der Plattenfeder der in [Fig. 17](#) gezeigten Halbleitervorrichtung ist;

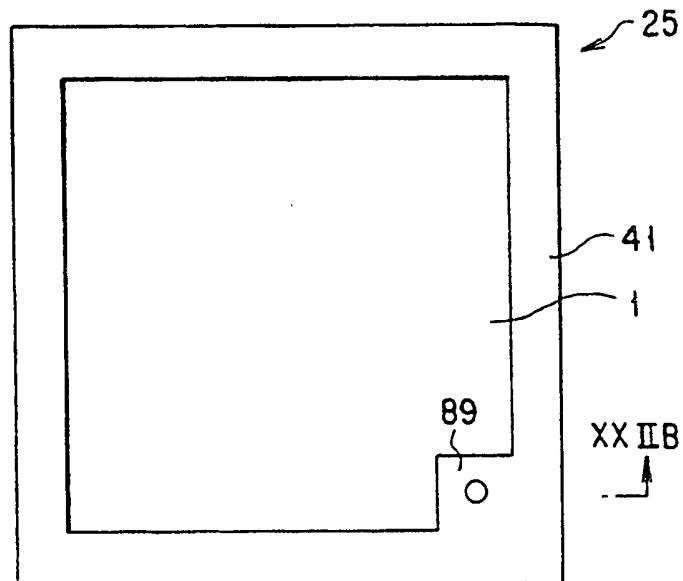

[0044] [Fig. 22A](#) eine fünfte Aufsicht des Halbleitersubstrates ist;

[0045] [Fig. 22B](#) eine Schnittansicht eines Bereiches entlang XXIIB-XXIIB von [Fig. 22A](#) ist;

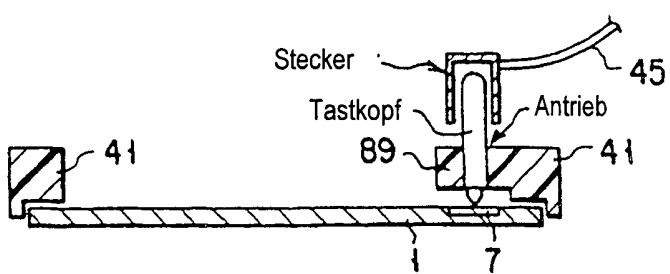

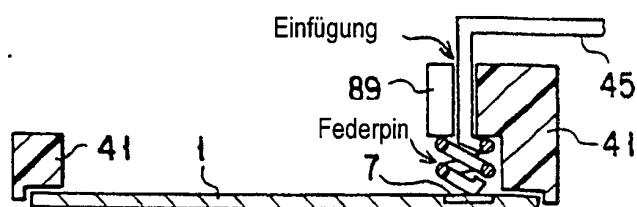

[0046] [Fig. 23A](#) eine sechste Aufsicht des Halbleitersubstrates ist;

[0047] [Fig. 23B](#) eine Schnittansicht eines Bereiches entlang XXIIB-XXIIB von [Fig. 23A](#) ist;

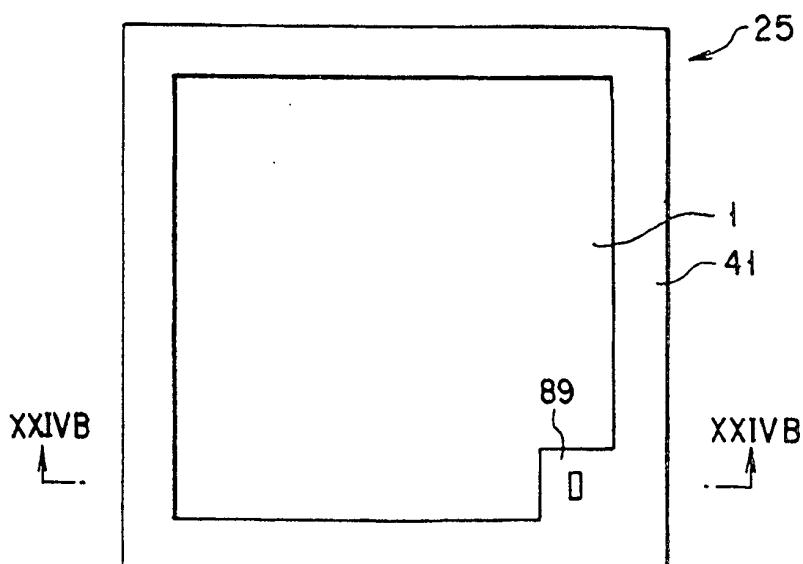

[0048] [Fig. 24A](#) eine siebte Aufsicht des Halbleitersubstrates ist;

[0049] [Fig. 24B](#) eine Schnittansicht eines Bereiches entlang XXIVB-XXIVB von [Fig. 24A](#) ist;

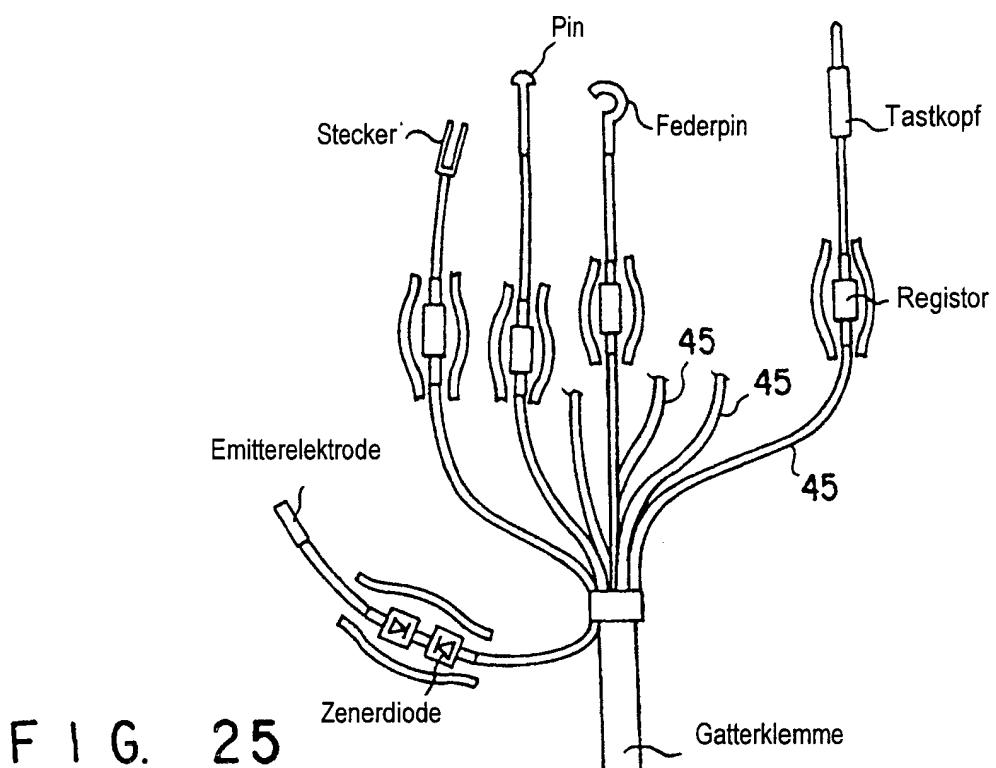

[0050] [Fig. 25](#) eine Ansicht verschiedener Gatterleitungen ist, die mit der Gatterklemme der Halbleitervorrichtung der vorliegenden Erfindung verbunden sind;

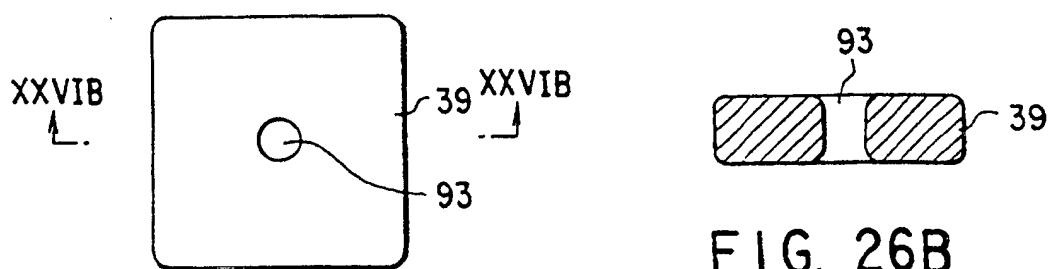

[0051] [Fig. 26A](#) eine Aufsicht der Pufferplatte ist, die für die Halbleitervorrichtung der vorliegenden Erfindung verwendet wird;

[0052] [Fig. 26B](#) eine Schnittansicht eines Bereiches entlang XXVIB-XXVIB von [Fig. 26A](#) ist;

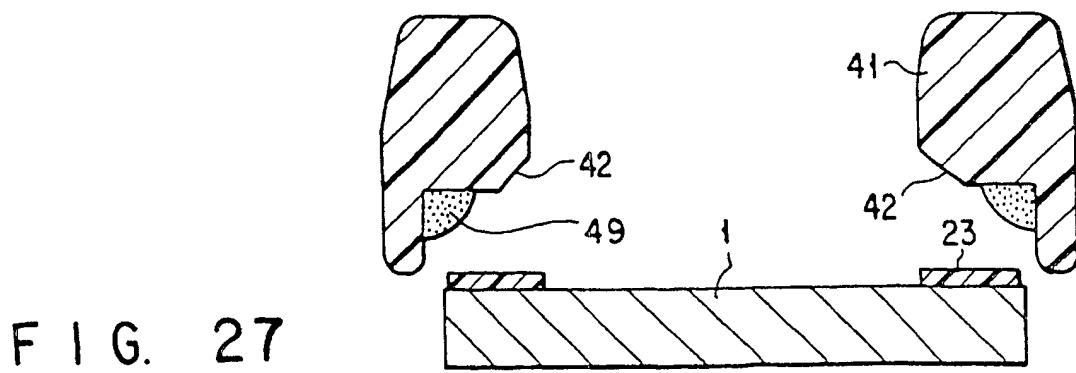

[0053] [Fig. 27](#) eine Schnittansicht ist, die eine Art darstellt, den Chiprahmen der Halbleitervorrichtung der vorliegenden Erfindung zu befestigen;

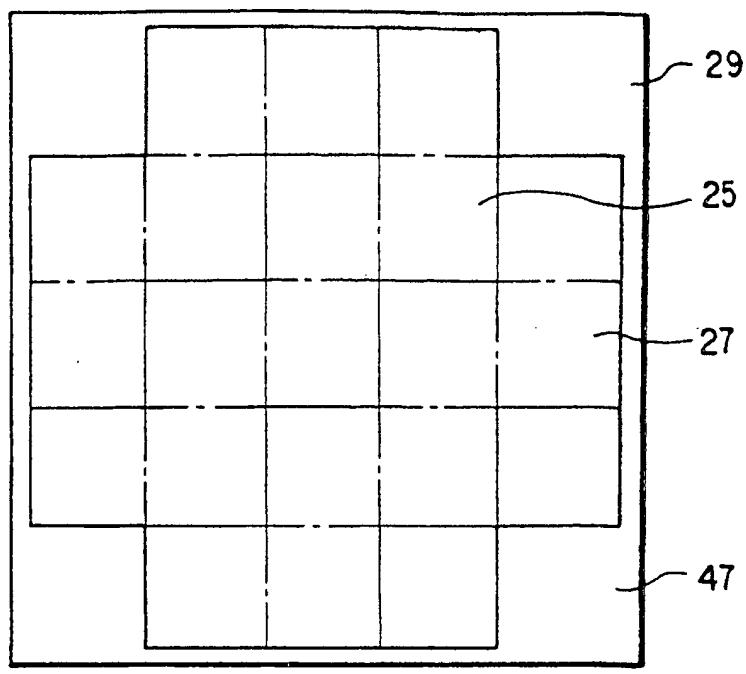

[0054] [Fig. 28](#) eine Aufsicht eines quadratisch geformten äußeren Rahmens der Halbleitervorrichtung der vorliegenden Erfindung ist;

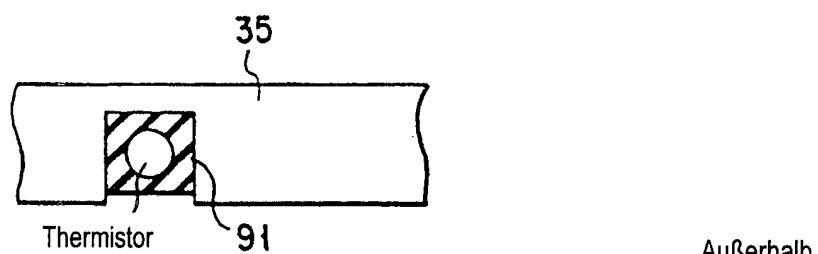

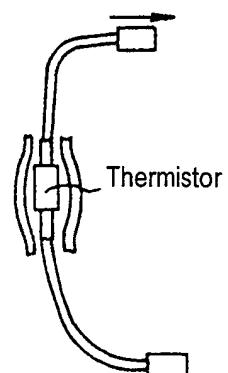

[0055] [Fig. 29A](#) eine erste Schnittansicht eines Thermistors ist, der auf dem Graben der Elektrodenplatte der vorliegenden Erfindung befestigt ist;

[0056] [Fig. 29B](#) eine zweite Schnittansicht eines Thermistors ist, der auf Graben der Elektrodenplatte der vorliegenden Erfindung befestigt ist; und

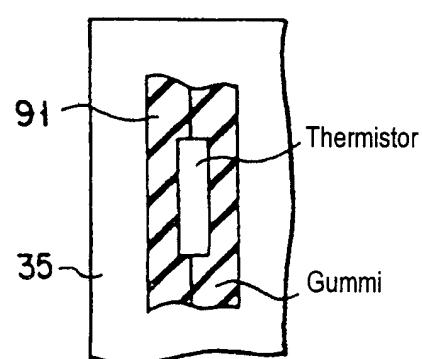

[0057] [Fig. 29C](#) ein Beispiel zum Befestigen des Thermistors auf der Gatterleitung ist.

[0058] Ausführungsformen der vorliegenden Erfindung werden nun mit Bezugnahme auf die beigefügten Zeichnungen beschrieben.

[0059] Die erste Ausführungsform wird mit Bezugnahme auf [Fig. 1](#) bis [Fig. 9](#) beschrieben. [Fig. 1](#) ist eine schematische Aufsicht der umgekehrten Leitungs-IGBT-Vorrichtung vom Druckkontaktyp, [Fig. 2](#) ist eine Schnittansicht des Bereiches entlang ihrer Linie II-II, [Fig. 5A](#), [Fig. 5B](#) und [Fig. 5C](#) sind Aufsichten und Schnittansichten des mit einem Chiprahmen befestigten IGBT-Chips, und [Fig. 6](#) bis [Fig. 9](#) sind modifizierte Ausführungsformen der entsprechenden Bereiche der vorliegenden Ausführungsform. Wie in [Fig. 1](#) gezeigt, besteht diese Vorrichtung aus neun IGBT-Chips **25** in dem zentralen Bereich und zwölf FRD-Chips **27** in dem Umgebungsbereich. Entsprechende Chips sind quadratische, aber der Sammeltörper, der sie sammelt, ist in die Kreisform presskontakteert. Diese Chipsammelkörper sind durch den äußeren Rahmen **29** eingeschlossen, der die äußere Umgebung dessen schützt und sie positioniert. Da die Ebenenform der Vorrichtung dieser Ausführungsform kreisförmig ist, wird der äußere Rahmen **29**, der den Chipsammelkörper einschließt, auch kreisförmig. Dieser äußere Rahmen wird als ein Ringrahmen bezeichnet. Wie in [Fig. 2](#) gezeigt, ist der Chipsammelkörper durch die Kollektorelektrodenplatte **33** presskontakteert, die die erste Elektrodenplatte ist, und die Emitterelektrodenplatte **35**, die die zweite Elektrodenplatte ist, aber zwischen der Elektrodenplatte und dem Chip sind thermische Pufferplatten **37** und **39** eingefügt, die zum Beispiel aus Molybdän bestehen.

[0060] Die thermische Kollektorpufferplatte **37** ist nämlich zwischen den IGBT-Chip **25** und FRD-Chip **27** eingefügt und die Kollektorelektrodenplatte **33** und eine thermische Emitterpufferplatte **39** ist zwischen diesen Chips **25** und **27** und die Emitterelektrodenplatte **35** eingefügt. Chips **25** und **27** sind auf der thermischen Kollektorpufferplatte **37** angeordnet und fixiert. Diese Chips sind auf der thermischen Kollektorpufferplatte **37** angeordnet und lassen keinen Platz dazwischen und sind

durch den Ringrahmen **29** befestigt, der derart führt, zum Einschließen von außen. Aus Siliconharz bestehende Chiprahmen **41** werden an die äußere Umgebung entsprechender Chips **25** und **27** angefügt. Ferner wird zwischen der thermischen Emitterpufferplatte **39** und den Chips **25**, **27** ein zum Beispiel aus Kupfer bestehender Weichmetallfilm **43** eingefügt, um den Kontaktzustand zu verbessern.

**[0061]** Der Ringrahmen **29** hat einen Vorsprung **47**, der von der inneren Wand in das Innere ragt und Chips positioniert, um die äußere Umgebung des angeordneten Chipsammelkörpers einzuschließen. Die Spitze des Vorsprungs **47** des Ringrahmens **49** grenzt gegen den Chiprahmen **41** der Chipumgebung und ist auf der thermischen Kollektorpufferplatte **37** platziert. Der Chiprahmen **41** hat eine Funktion zum Erleichtern der Positionierung, wenn der Chipsammelkörper gebildet wird, ebenso wie zum Verstärken einer Isolation des äußeren Bereiches.

**[0062]** In dieser Ausführungsform wird das Beispiel der umgekehrten Leitungs-IGBT-Vorrichtung vom Druckkontakttyp gezeigt, die mit einem IGBT-Element mit 9 Chips und einem FRD-Element mit 12 Chips bereitgestellt wird, aber durch Verwenden der gleichen Chips und Verändern der Anzahl und des Zuweisungsverhältnisses können Vorrichtungen mit verschiedenen Einordnungen bereitgestellt werden. Wie in dieser Ausführungsform kann durch Quadratischen machen des FRD-Elementes mit der gleichen Größe hinsichtlich des IGBT-Elementes die Produktivität durch Standardisierung der Chipauslegung verbessert werden, und der Freiheitsgrad der Zusammenfügungstechnik des Chiprahmens kann verbessert werden. Ferner wird dadurch, dass die innere Wand des Chiprahmens **41** zu einer Führung gemacht wird, die thermische Emitterpufferplatte **39** auf die Chips **25** und **27** gesetzt, wodurch das ganze kontaktiert wird.

**[0063]** Als nächstes wird mit Bezugnahme auf [Fig. 3](#) und [Fig. 4](#) der IGBT-Chip beschrieben. Beide Figuren sind Schnittansichten des IGBT-Chips. Die Emitteroberfläche, die auf der oberen Oberfläche des IGBT-Chips gebildet wird, ist mit einem Passivierungsfilm **23** abgedeckt, zum Beispiel Polyimid, außer für den Leistungsversorgungsbereich des Gatters, der die Steuerungselektrode und der Bereich ist, der gegen die thermische Emitterpufferplatte der Emitterelektrode trennt. Dieser Passivierungsfilm **23** ist auf der Chipumgebung gebildet, was bedeutet, dass er unter dem Chiprahmen **41** gebildet ist, der auf der Chipumgebung befestigt ist. [Fig. 3](#) zeigt die Struktur der Chipumgebung, und [Fig. 4](#) zeigt einen gegebenen Schnitt innerhalb des Chips.

**[0064]** Der quadratisch geformte Chip **1** schließt einen P-Typ-Kollektorbereich **13**, einen N-Basisbereich **11**, einen P+ Basisbereich **15**, einen P-Typ-Ba-

sisbereich **17** und einen N-Typ-Emitterbereich **9** ein. Ein P-Typ-Kollektorbereich **13** ist auf der Rückseite des Chips **1** gebildet, und auf dieser Rückseite ist eine Kollektorelektrode **22** aus zum Beispiel Aluminium auf der gesamten Oberfläche dessen gebildet. Ein P+ Basisbereich **15** und ein P-Typ-Basisbereich **17** sind in dem N-Basisbereich **11** gebildet, gegenüberliegend der oberen Oberfläche (hiernach bezeichnet als „Emitteroberfläche“) des Chips **1**. Der N-Typ-Emitterbereich **9** ist in dem P-Typ-Basisbereich **17** gebildet, gegenüberliegend der Emitteroberfläche des Chips **1**. Emitterelektrode **1** bestehend aus Aluminium wird auf dem N-Typ-Emitterbereich **9** gebildet, kurzgeschlossen mit dem P-Typ-Basisbereich **17**. Auf dem P-Typ-Basisbereich **17** und dem N-Basisbereich **11**, gesandwiched zwischen diesem P-Typ-Basisbereichen **17**, ist ein Polysiliziumgatter **5** über dem Gatteroxidfilm **19** gebildet. Polysiliziumgatter **5** ist mit einem Zwischenschichtisolierfilm **3** beschichtet, wie einem Siliziumdioxidfilm, und die Emitterelektrode **21** ist darauf angeordnet. Die mit dem Polysiliziumgatter **5** verbundene Gatterelektrode **31** besteht aus Aluminium und dergleichen und ist mit diesem Polysiliziumgatter **5** über eine Öffnung des zwischenlaminaren Films **3** (siehe [Fig. 4](#)) verbunden. Die Emitteroberfläche des Chips **1** ist mit einem Passivierungsfilm **23** wie Polyimid beschichtet, außer für den Kontaktierungsbereich **G** (nicht gezeigt) der Gatterelektrode **31** und dem Kontaktbereich der Emitterelektrode **21**. Daher ist der Bereich außer für den Kontaktbereich **G** der Gatterelektrode **31** mit einem Passivierungsfilm **23** beschichtet. Die Gatterelektrode **31** ist mit einem Siliziumdioxidfilm **53** beschichtet und geschützt, und der Passivierungsfilm **23** ist darauf gebildet.

**[0065]** Als nächstes wird der Weg zum Befestigen des Chiprahmens auf einem IGBT-Chip **25** mit Bezugnahme auf [Fig. 5](#) bis [8](#) beschrieben. [Fig. 5A](#) bis [Fig. 5C](#) zeigen die Aufsicht und die Schnittansicht und die teilweise vergrößerte Ansicht dessen des Chips mit einem darauf befestigten Chiprahmen. Der Chip **1** weist eine planare Hochspannungsstruktur auf, und die Form ist zum Beispiel quadratisch. Die Umgebung dessen ist mit einem Passivierungsfilm **23** aus Polyimidharz beschichtet. Auf dem Passivierungsfilm **23** aus Polyimid der Umgebung ist ein Chiprahmen **41**, der aus Silicon oder einem durch einen separaten Vorgang im Voraus gebildeten technischen Kunststoff besteht, mit einem Kleber **49** befestigt, wie einem Silicon oder Polyimid (siehe [Fig. 5C](#)). Dieser Chiprahmen **41** und der Kleber **49** decken die obere Oberfläche und Seitenflächen der Chipumgebung ab, aber erreichen nicht den rückseitigen Kollektor auf dem Chip. Ferner ist die Größe des Chiprahmens **41** derart, dass ein Abstand zum Verändern von Oberflächendurchschlägen gemäß der Bemessungsspannung von Chip **1** auftritt. Ein Standard ist ein Standard von 1 mm oder länger pro 1 KV. Er hat eine derartige Form zum Führen auf der Seiten-

fläche des Chips **1**, wie in [Fig. 5C](#) gezeigt, zum Positionieren zur Zeit der Anbringung des Chiprahmens **41** und des Chips **1**.

**[0066]** [Fig. 6](#) und [Fig. 7](#) zeigen die modifizierte Ausführungsform des Befestigungsverfahrens des Chiprahmens. In [Fig. 6](#) wird ein Graben **59** auf der Kontaktalebene des Chiprahmens **41** mit dem Kleber **49** bereitgestellt, um eine Kürzung des Klebers zu verhindern. Somit gelangt der Kleber in den Graben **59** zum Verbessern der Klebestärke. In [Fig. 7](#) ist der Chiprahmen **41** integral mit dem Chip durch Verwenden einer Gusstechnik von Siliconharz und dergleichen integral gebildet. Ferner wird in [Fig. 6](#) und [Fig. 7](#) ein leicht spitz zulaufender Winkel in dem oberen Bereich des Chiprahmens bereitgestellt und jeder Eckteil ist gerundet. Durch eine derartige Endbearbeitung kann der oben beschriebene Betrieb zum Anordnen des Chiprahmens durch Verwendung des Ringrahmes und zum Positionieren des Chipsammelkörpers sehr glatt durchgeführt werden.

**[0067]** In [Fig. 5A](#) ist die Gatterelektrode, die Bereich **G** kontaktiert, der auf der Emittéroberfläche auf Chip **1** bereitgestellt wird, als **7** auf dem Chip gezeigt, aber in dieser Ausführungsform ist **7** in jeder Ecke von vier Ecken auf dem Chip gebildet. Aber die Position dieses Kontaktbereiches muss nicht auf die Ecken beschränkt sein und kann in einem zentralen Bereich des Chips gebildet werden, wie in [Fig. 8A](#) gezeigt, oder kann mehr als ein oder zwei (mal) gebildet werden, wie in [Fig. 8B](#) gezeigt. Der Bereich, der verschieden ist von dem Gatterelektrodenkontaktbereich und dem Bereich, der mit dem Chiprahmen **41** in dem äußeren Bereich abgedeckt ist, wird der Kontaktbereich der Emitterelektrode, das bedeutet der Presskontaktebereich.

**[0068]** [Fig. 8C](#) ist eine Aufsicht des IGBT-Chips, der in einem anderen Beispiel verwendet wird. Auf der Emittéroberfläche ist die Emittersteuerungselektrode **97** an dem Eckbereich des Chips gebildet, ebenso der Kontaktbereich **7** der Gatterelektrode. Die Emittersteuerungselektrode **97** ist zu der Hauptemitterelektrode **99** auf dem Chip isoliert. Die Emittersteuerungselektrode **97** wird zum Erfassen des Überstroms bereitgestellt und in einem derartigen Bereichsverhältnis ausgelegt, dass ein Schwachstrom (in der Größenordnung von 10 mA bis 1 A) hinsichtlich der Hauptemitterelektrode **99** gegeben ist.

**[0069]** [Fig. 9](#) ist eine Modifizierung des Ringrahmens in dieser Ausführungsform. In der in [Fig. 1](#) gezeigten Ausführungsform besteht der äußere Rahmen **29** (der Ringrahmen in der Ausführungsform) aus dem Ringteil, der aus dem äußeren Bereich und dem Vorsprung **47** besteht, der aus der inneren Wand des Ringteils in Richtung der Innenseite heraussteht, aber ein Gitter **57** kann innerhalb des Ringrahmens gebildet werden, das integral mit dem Vorsprung **47**

verbunden ist. Wenn die Anzahl von Chips groß wird und die Summe jeder Dimensionstoleranz die Positionsgenauigkeit überschreitet, kann eine geeignete Einfügung eines derartigen Gitters beim Positionierungsbetrieb des Chipsammelkörpers zum Erhalten des besten Effektes helfen.

**[0070]** Als nächstes wird die zweite Ausführungsform mit Bezugnahme auf [Fig. 10](#) und [Fig. 11](#) beschrieben.

**[0071]** [Fig. 10](#) ist eine Aufsicht der zweiten Ausführungsform der umgekehrten Leitungs-IGBT-Vorrichtung vom Druckkontakte Typ, und [Fig. 11](#) ist eine Schnittansicht des Bereiches entlang der Linie XI-XI von [Fig. 10](#). In dieser Ausführungsform wird ein Chip mit einer schrägen Struktur in der Hybridzusammensetzung gebildet. Wie in [Fig. 10](#) gezeigt, ist ein runder FRD-Chip **27** in der Schrägstuktur und 8 quadratische IGBT-Chips **25** in der Umgebung dessen angeordnet. Dieser Chipsammelkörper positioniert jeden Chip des Sammelkörpers, um die äußere Umgebung dessen einzuschließen und ist in einem Kreisringrahmen **29** eingeschlossen, der die äußere Umgebung dessen schützt. Der Chipsammelkörper ist durch die Kollektorelektrodenplatte **33**, welches die erste Elektrodenplatte ist, und die Emittorelektrodenplatte **35**, welche die zweite Elektrodenplatte ist, presskontakteiert, wie in [Fig. 11](#) gezeigt ist. Zwischen der Elektrodenplatte und den Chips werden thermische Pufferplatten **37** und **39** eingefügt, die zum Beispiel aus Molybdän bestehen. Es wird nämlich eine thermische Kollektorpufferplatte **37** zwischen den IGBT-Chips **25** und dem FRD-Chip **27** und der Kollektorelektrodenplatte **33** eingefügt, und zwischen diesen Chips **25** und **27** und der Emittorelektrodenplatte werden thermische Emitterpufferplatten **39** eingefügt. Chips **25** und **27** sind auf der thermischen Kollektorpufferplatte **37** angeordnet und fixiert. Somit sind in der ersten Ausführungsform diese Chips auf der thermischen Kollektorpufferplatte in einer Linie angeordnet und lassen keinen Platz dazwischen, wobei in dieser Ausführungsform die thermische Kollektorpufferplatte **37** aus einem kreisförmigen Teil besteht, der den FRD-Chip **27** hält, und einem ringförmigen Teil, der die acht Chips hält, und die Emitterpufferplatte **39** besteht aus einer kreisförmigen Platte, die den FRD-Chip **27** abdeckt, und acht quadratischen Platten, die jeden IGBT-Chip **25** abdecken.

**[0072]** Der Ringrahmen **29** fixiert den Chipsammelkörper, um den Chipsammelkörper von außerhalb durch den Vorsprung **47** dessen einzuschließen. Chiprahmen **41** besteht aus einem Siliconharz und dergleichen und ist auf dem äußeren Bereich der entsprechenden Chips **25** und **27** befestigt. Ferner ist zwischen der thermischen Emitterpufferplatte **39** und Chips **25**, **27** ein Weichmetallfilm **23** wie Kupfer und dergleichen eingefügt, um den Kontaktzustand zu verbessern. Der Vorsprung **27** des Ringrahmens **29**

ist auf der thermischen Kollektorpufferplatte 37 platziert, mit der Spitze dessen gegen den Chiprahmen in der Chipumgebung angrenzend. Der Chiprahmen 41 hat Funktionen zum Verstärken der Isolation der Chipumgebung und zum Erleichtern der Anordnung, wie Positionieren der Zeit zum Bilden des Chipsammelkörpers.

**[0073]** Ferner wird in dieser Ausführungsform so gesteuert, dass die Chips einheitlich durch Verwenden einer Dicken-Einstellplatte einheitlich bzw gleichförmig presskontakteert werden, die zum Beispiel aus einem Silberblatt besteht. Es wird nämlich ein Silberblatt 63 zwischen die Emitterelektrodenplatte 35 und die thermische Emitterpufferplatte 39 auf der Emittersseite eingefügt, und ein Silberblatt 65 wird zwischen die Kollektorelektrodenplatte 33 und die thermische Kollektorpufferplatte 37 auf der Kollektorseite eingefügt. Somit werden Weichmetallblätter an der Außenseite der thermischen Pufferplatten als eine Dicken-Einstellplatte eingefügt, zum Einstellen der leichten Unterschiede der Dicke des Chips, der Weichmetallblätter und der thermischen Pufferplatten, und zum Durchführen einer gleichförmigen Druckkontakteierung.

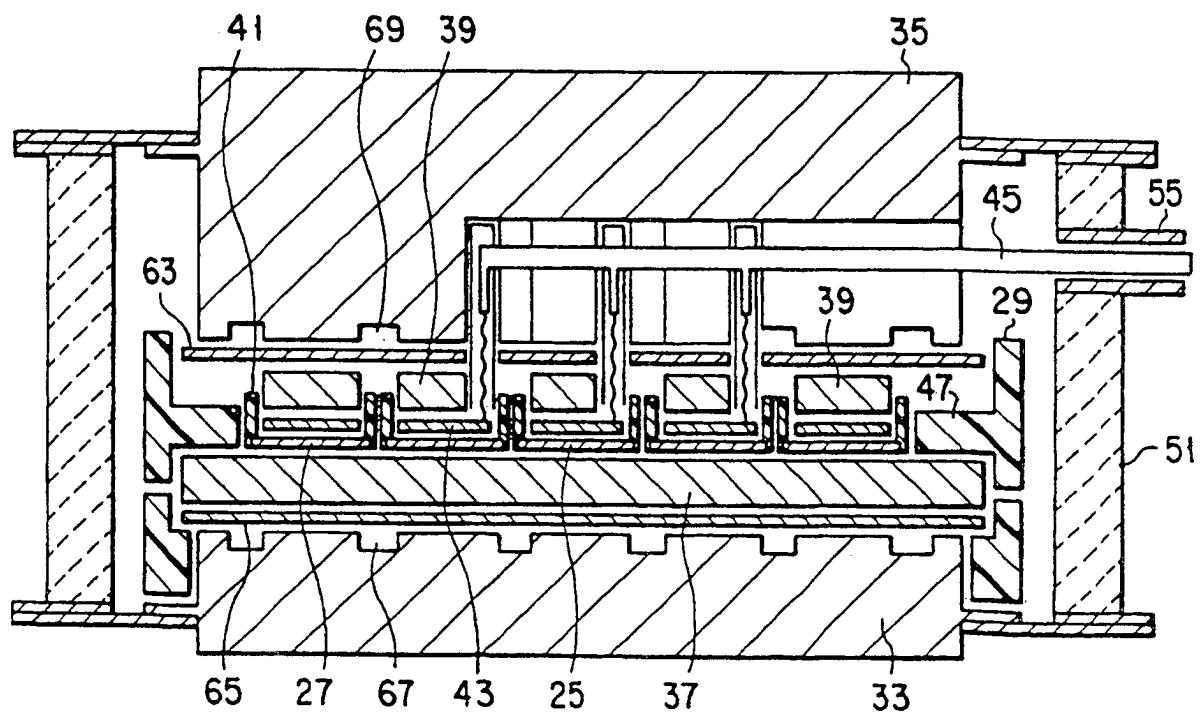

**[0074]** Als nächstes wird die dritte Ausführungsform mit Bezugnahme auf [Fig. 12](#) beschrieben.

**[0075]** [Fig. 12](#) ist eine Schnittansicht der dritten Ausführungsform der umgekehrten Leitungs-IG-BT-Vorrichtung vom Druckkontaktyp.

**[0076]** Eine Mehrzahl von quadratisch geformten IGBT-Chips 25 und FRD-Chips 27 sind entsprechend durch Chiprahmen 41 geschützt. Der Chipsammelkörper wird durch die Kollektorelektrodenplatte 33, die die erste Elektrodenplatte ist, und die Emitterelektrodenplatte 35, die die zweite Elektrodenplatte ist, presskontakteiert. Zwischen die Elektrodenplatte und die Chips werden thermische Pufferplatten 37 und 39 eingefügt, die zum Beispiel aus Molybdän bestehen. Es wird nämlich eine thermische Kollektorpufferplatte 37 zwischen die IGBT-Chips 25 und den FRD-Chips 27 und die Kollektorelektrodenplatte 33 eingefügt, und zwischen diesen Chips 25 und 27 und die Emitterelektrodenplatte werden thermische Emitterpufferplatten 39 eingefügt. Chips 25 und 27 sind auf der thermischen Kollektorpufferplatte 37 angeordnet und fixiert. Diese Chips sind auf der thermischen Kollektorpufferplatte in einer Linie angeordnet und lassen keinen Platz dazwischen, und die thermische Emitterpufferplatte 39 besteht aus einer quadratisch geformten Platte, die jeden Chip entsprechend presskontakteiert. Der Ringrahmen 29 fixiert den Chipsammelkörper, um den Chipsammelkörper von außerhalb durch den Vorsprung 47 dessen einzuschließen. Zwischen der thermischen Emitterpufferplatte 39 und Chips 25, 27 werden dünne Weichmetallfilme 43 wie Kupfer und dergleichen eingefügt, zum Ver-

bessern des Kontaktzustandes. Der Vorsprung 27 des Ringrahmens 29 wird auf der thermischen Kollektorpufferplatte 37 platziert mit der Spitze dessen angrenzend gegen den Chiprahmen 41 in der Chipumgebung. Der Chiprahmen 41 hat Funktionen zum Verstärken der Isolation auf der Chipumgebung und zum Erleichtern der Anordnung wie Positionierung zur Zeit des Bildens des Chipsammelkörpers.

**[0077]** Ferner wird in dieser Ausführungsform so gesteuert, dass die Chips gleichförmig durch Verwenden der Dicke-einstellplatte presskontakteiert werden, die zum Beispiel aus einem Silberblatt besteht. Es wird nämlich ein Silberblatt 63 zwischen die Emitterelektrodenplatte 35 und die thermische Emitterpufferplatte 39 auf der Emittersseite eingefügt, und ein Silberblatt wird zwischen die Kollektorelektrodenplatte 33 und die thermische Kollektorpufferplatte 37 auf der Kollektorseite eingefügt. Somit werden Weichmetallblätter an der Außenseite der thermischen Pufferplatten als eine Dicken-Einstellplatte eingefügt zum Einstellen der leichten Unterschiede in der Dicke des Chips, der Weichmetallblätter und der thermischen Pufferplatten, und zum Durchführen einer gleichförmigen Druckkontakteierung. Diese Pufferplatte hat auch eine Funktion zum Einstellen des Unterschiedes in der Dicke zwischen Chips in einem gewissen Ausmaß. Ferner sind in dieser Ausführungsform Gräben 67 und 69 auf der inneren Oberfläche gebildet, die den Chips der Kollektorelektrodenplatte und der Emitterelektrodenplatte 35 gegenüberliegen. Die Gräben sind so gebildet, dass sie zwischen den Chips angeordnet sind, unter Berücksichtigung der Größe der Chips. Der Bereich, der dem Chip der Emitterelektrodenplatte gegenüberliegt, die mit dem Rahmen eingeschlossen ist, weist eine Charakteristik auf, dass sie kleiner ist als der Bereich der thermischen Pufferplatte 39, die zwischen den Chips liegt. Somit kann die Belastungskonzentration der IGBT-Chips 25 und der FRD-Chips 27 auf die Chipumgebung verhindert werden, zu der Zeit einer Presskontakteierung, wodurch die Konzentration der Belastung auf den Chipumgebungsbereich freigegeben werden kann.

**[0078]** Die (nicht gezeigte) Gatterelektrode, ein Gatterleiter 45, wird durch eine Feder presskontakteiert. Ein Ende der Gatterleitung 45 wird nach außerhalb der äußeren Vorrichtung 51 durch den Metallgraben 55 geleitet, der mit der Seitenwand der zylindrischen äußeren Umgebungsvorrichtung 51 Silberverlötet ist. An dem Metallgraben 45 wird eine Dichtung bereitgestellt zum Abdichten der Chips 25 und 27 innerhalb der äußeren Umgebungsvorrichtung 51.

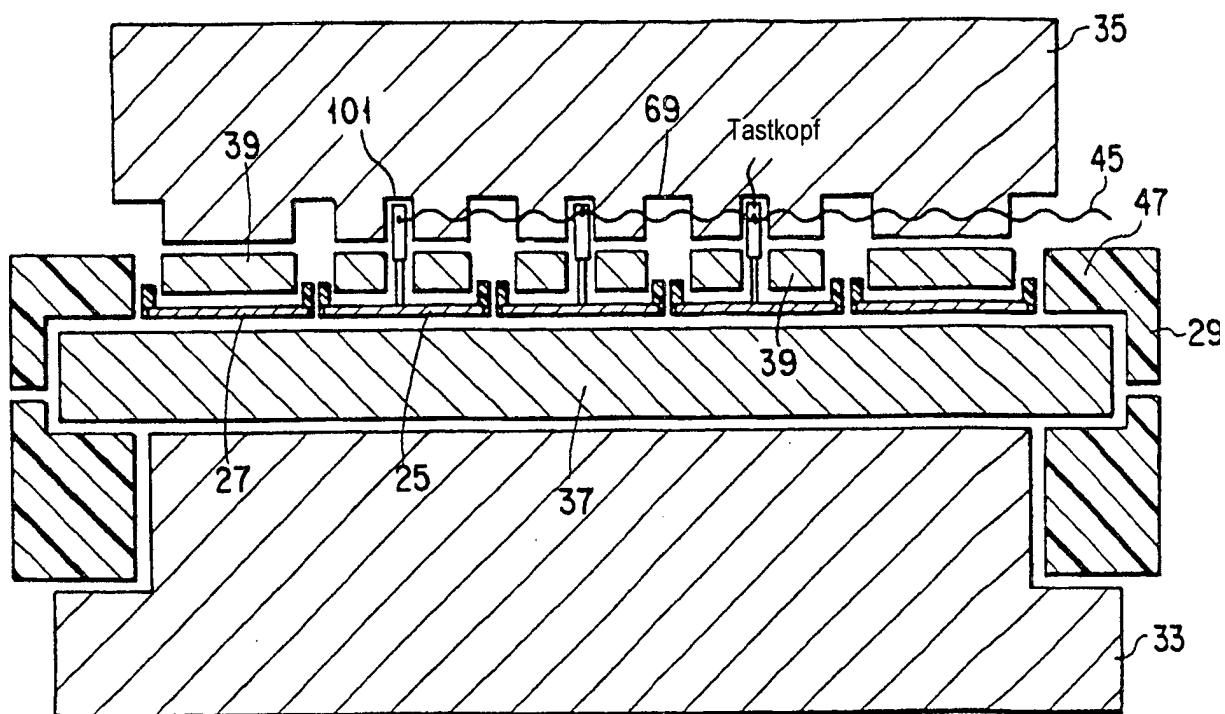

**[0079]** Als nächstes wird die vierte Ausführungsform mit Bezugnahme auf [Fig. 13](#) bis [Fig. 16](#) beschrieben.

**[0080]** So werden in der dritten Ausführungsform

durch die Gräben **67** und **69** in der Kollektorelektrodenplatte **33** und der Emittorelektrode eine Platte **35** bereitgestellt, wobei in dieser Ausführungsform, wie in der in [Fig. 13](#) gezeigten Ausführungsform, nur ein Graben **69** der Emittorelektrodenplatte bereitgestellt ist, und die Dicke der thermischen Kollektorpufferplatte **37** stark vergrößert wird. Wie oben beschrieben, werden, da die thermische Pufferplatte auch die Funktion hat zum Einstellen der Unterschiede in einer Dicke zwischen Chips durch Dickenmachen der dünne Kupferfilm **43** zum Verbessern des Kontaktzustandes der thermischen Emittorpufferplatte und des Chips, was in der dritten Ausführungsform erforderlich ist, und die Silberblätter **63** und **65**, die die Dicke zwischen der Emitt- und Kollektorelektrodenplatte und der thermischen Pufferplatte einstellen, entfernt, um die Struktur der Vorrichtung zu vereinfachen. In dieser Ausführungsform wird ein Gattertastkopf, der mit dem Gatterelektrodenbereich **101** des Grabens verbunden ist, mit dem Gatterelektrodenkontaktbereich **7** (siehe [Fig. 8A](#)) verbunden, der in dem zentralen Bereich des IGBT-Chips **25** bereitgestellt wird, der nach außerhalb durch den Graben **69** durch den Gatterleiter **45** geleitet wird, der mit dem Tastkopf verbunden ist.

**[0081]** [Fig. 14](#)–[Fig. 16](#) sind Modifizierungen der Emittorelektrodenplatte **35**, die Gräben **69** aufweist. In [Fig. 14](#) sind Gräben **69** längs und quer auf der inneren Oberfläche der Emittorelektrodenplatte gebildet und die Gatterleitung **45** kann in diese Gräben eingesetzt werden. Gemäß einer Notwendigkeit kann auch leicht eine hohe Funktionalität der Vorrichtung erhalten werden durch Einbetten anderer Leiter wie dem Emittsteuerungsleiter und dergleichen (siehe [Fig. 8C](#)) und dem Temperaturerfassungsthermistor und dergleichen. Somit werden in der Ausführungsform von [Fig. 14](#) ausreichende Gräben vorläufig gebildet und nur notwendige werden zum Verdrahten der Leitung verwendet. In den Gräben **69** sind Gatterelektrodenbereiche **101** zugehörig zu den Gatterelektrodenkontaktbereichen **7** auf den IGBT-Chips gebildet. Die Gatterelektrodenbereiche **101** werden nicht bezüglich der FRD-Chips verwendet. Die quadratisch geformten flachen Bereiche, die in diesen Gräben eingeschlossen sind, werden als die Presskontaktebene verwendet.

**[0082]** [Fig. 15](#) zeigt die Ausführungsform, in der die Gräben gebildet werden, im Gegensatz zu der Emittorelektrodenplatte nur in den Teilen, die zum Verdrahten der Leitung und dergleichen notwendig sind. Wenn eine Notwendigkeit zum Anordnen anderer Leiter und eines Thermistors bestehen, werden ferner Gräben für diese gebildet. **8** ist gegenüberliegend zum dem Gatterelektrodenkontaktbereich **7** auf dem Chip. In dieser Ausführungsform, wie in [Fig. 5A](#) gezeigt, ist ein Fall bereitgestellt, wo **7** an der Ecke des IGBT-Chips bereitgestellt wird.

**[0083]** [Fig. 16](#) ist eine andere Modifikation der Emittorelektrodenplatte. Wie in [Fig. 14](#) sind Gräben **69** längs und quer auf der inneren Oberfläche der Emittorelektrodenplatte gebildet, aber der Gatterelektrodenbereich des Grabens wird an der Ecke der Druckkontaktebene des IGBT-Chips bereitgestellt, und IGBT-Chips sind in dem äußeren Bereich der Elektrodenebene angeordnet und FRD-Chips sind in dem zentralen Bereich dessen angeordnet.

**[0084]** Wie oben beschrieben, sind, selbst wenn Gräben in der Emittorelektrodenplatte bereitgestellt werden, die zu der Hitzefreigabe des Chips beitragen, die Grabenteile gegenüberliegend zu dem Chiprahmen-bildenden Teil der Chipumgebung, und es trägt nicht dazu bei Hitze freizugeben, daher gibt es kaum den Einfluss auf die Hitzefreigabecharakteristik der gesamten Druckkontaktevorrichtung.

**[0085]** Die in [Fig. 14](#) bis [Fig. 16](#) gezeigte Emittorelektrodenplatte kann auf die dritte Ausführungsform angewendet werden, die von dieser Ausführungsform verschieden ist.

**[0086]** Als nächstes wird die fünfte Ausführungsform mit Bezugnahme auf [Fig. 17](#) bis [Fig. 21](#) beschrieben.

**[0087]** [Fig. 17](#) ist eine Schnittansicht einer umgekehrten Leitungs-IGBT-Halbleitervorrichtung vom Bolzentyp mit einer Nenngröße von 600 V–800 A, [Fig. 18](#) ist eine Aufsicht der Basis, die in der Halbleitervorrichtung verwendet wird, [Fig. 9](#) ist eine Aufsicht der Halbleitervorrichtung, die die Anordnung der Chips zeigt, [Fig. 20](#) ist eine Aufsicht, die die Innenseite der für die Halbleitervorrichtung verwendeten Keramikkappe zeigt, und [Fig. 21](#) ist eine Schnittansicht, die Verwendungszustand der Plattenfeder innerhalb der Vorrichtung zeigt.

**[0088]** In der Halbleitervorrichtung der vorliegenden Ausführungsform, die in [Fig. 17](#) gezeigt ist, ist ein isolierendes Substrat **105** aus Aluminiumnitrit und dergleichen an der Basis **103** befestigt, und eine Kollektorelektrodenplatte **33** bestehend aus Kupfer mit einer Dicke von ungefähr von 0,5 mm, die die erste Elektrodenplatte ist, ist mit **105** verbunden, und IGBT-Chip **25** und FRD-Chip **27** sind darauf platziert. Die Umgebung jedes Chips ist durch den Chiprahmen **41** aus Siliconharz und dergleichen geschützt, wie in [Fig. 18](#) gezeigt ist. Pufferplatten **39** aus Molybdän sind auf dem Chips platziert, und eine gemeinsame Emittorelektrodenplatte **35** mit einer Dicke von ungefähr 0,5 mm darauf presst alle Pufferplatten **39** der Chips. Eine zylindrische äußere Umgebungsvorrichtung **51**, die auf der Basis **103** platziert ist, schließt diese Chips ein und ist durch eine Keramikkappe **75** abgedichtet. Die äußere Emittorelektrode E, äußere Kollektorelektrode C und äußere Gatterelektrode G und äußere Emittsteuerungselektrode S

dieser Halbleitervorrichtung werden durch die Keramikkappe **75** gehalten. Die äußere Emitterelektrode **E** ist mit der Emitterelektrodenplatte **35** über den Emitterelektrodenanschlag **77**, der auf einem Chip unter den IGBT-Chips **25** und FRD-Chips **27** befestigt ist, und dem Litzen draht **79** verbunden.

**[0089]** Sowohl Seitenabtastköpfe als auch Federn, die in der Isolatorröhre **81** auf dem Chip platziert sind, vermindern die äußere Gatterelektrode **G** und die Gatterelektrode, die auf der Oberfläche von IGBT-Chips **25** gebildet ist. Eine Verbindung zwischen Gatterelektroden von IGBT-Chips **25** wird durch Verwenden des auf der inneren Oberfläche der Keramikkappe **75** gebildeten metallisierten Musters durchgeführt. Die Emitterelektrodenplatte **35** verbindet die Emittentsprechender Chips in einem. Die äußere Kollektorelektrode **C** ist elektrisch mit der gemeinsamen Kollektorelektrodenplatte **33** verbunden. Wie in der Aufsicht von [Fig. 19](#) gezeigt, wird in der vorliegenden Ausführungsform, da der zentrale Chip in [Fig. 17](#) ein FRD-Chip **27** ist, ein Tastkopf nicht in die in [Fig. 17](#) gezeigte Isolationsröhre eingefügt, und die Isolationsröhre wird hohl. Der Druckkontakt auf die Chips durch die Emitterelektrodenplatte **35** wird durch die Plattenfeder **83**, die auf jedem Chip über eine Unterlegscheibe befestigt ist, mit Energie versorgt. Die äußere Emittenteuerungselektrode **S** ist direkt verbunden mit der Emittenteuerungselektrode auf dem Chip, über einen Emittenteuerungsleiter **95** eines Tastkopfes und dergleichen, wodurch der parasitäre Widerstand vermindert werden kann. In dieser Figur sind die äußere Kollektorelektrode **C** und die äußere Emitterelektrode **E** verbunden durch Dichtungsschweißen oder Verlöten der entsprechenden äußeren Auslöseklemme. Diese äußeren Auslöseklemmen sind vertikal befestigt, aber sie können auch horizontal befestigt sein.

**[0090]** [Fig. 18](#) ist eine Aufsicht der Basis **103**. Die Basis **103** weist ein Befestigungsloch auf und besteht aus Halteteilen **71** aus Kupfer, die mit entsprechenden Chips beladen sind, und einem Gitterteil **73** aus Eisen, das diese Halteteile **71** hält. Da Kupfer leicht verformbar ist und sich infolge der inneren Druckkontaktkraft nach außen ausdehnt und dadurch die Druckkontaktkraft nicht angewendet wird oder die Einheitlichkeit beeinträchtigt wird, wird das Gitter **73** aus Eisen hinzugefügt, um es zu umgeben, wie in dieser Ausführungsform, um die Festigkeit der Basis zu erhöhen. Der Halteteil **71** aus Kupfer wird nur unter dem Chip angeordnet. Eine äußere Umgebungs vorrichtung **51** wird in der Umgebung der Basis **103** gebildet.

**[0091]** [Fig. 19](#) ist eine Aufsicht, die die Innenseite der äußeren Umgebungs vorrichtung **51** zeigt. [Fig. 17](#) ist eine Schnittansicht des Bereiches entlang der Linie XVII-XVII. Die darin angeordneten Chips bestehen aus vier IGBT-Chips **25** und zwei FRD-Chips **27**

in dem zentralen Bereich. Plattenfedern **83** zum Druckkontakteien des Chips sind auf den entsprechenden Chips gebildet. Die äußere Emitterelektrode **E** ist auf einem der RFD-Chips **27** gebildet. Und die äußere Kollektorelektrode **C** ist in einem gegebenen Raum gebildet.

**[0092]** [Fig. 20](#) ist eine Aufsicht, die die Oberfläche zeigt, die der Innenseite der äußeren Umgebungs vorrichtung **51** der Keramikkappe **75** gegenüberliegt, gezeigt in [Fig. 17](#). Ein metallisiertes Muster **87** der Gatterelektrode ist auf dieser Oberfläche gebildet. Freie Teile **F** und **H** werden gebildet, um einen Wider stand, einen Kondensator, eine Zener-Diode oder dergleichen durch Weichlöten oder Silberlöten an einigen Teilen in dem metallisierten Muster **87** zu verbinden. Wenn keine Notwendigkeit besteht diese Teile anzufügen, können diese freien Teile metallisiert werden. Dieses metallisierten Muster **87** verbinden Gattern von IGBT-Chips **25**. Mit dem freien Teil **F** ist zum Beispiel ein Kondensator und eine Zener-Diode verbunden. Mit dem freien Teil **H** ist zum Beispiel ein Widerstand verbunden. Somit kann durch Verwenden der inneren Fläche der Keramikkappe eine hohe Funktionalität der Vorrichtung leicht erhalten werden.

**[0093]** [Fig. 21](#) ist eine vergrößerte Ansicht, die die Struktur der Plattenfeder zeigt. Plattenfedern sind an jeden Chip angefügt, wodurch der Unterschied in dem Grad der Dicke für jeden Chip leicht durch ihren Hub eingestellt werden kann.

**[0094]** Als nächstes wird jeder strukturelle Teil oder seine Modifikation, der für die Ausführungsformen der Halbleitervorrichtung der vorliegenden Erfindung verwendet, im Detail mit Bezugnahme auf [Fig. 22](#) bis [29](#) beschrieben.

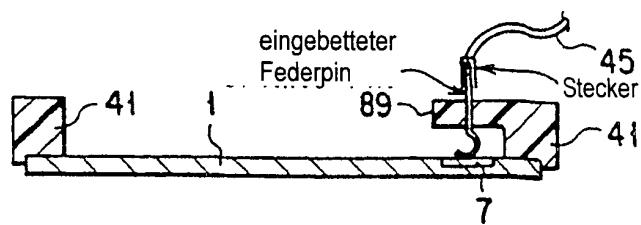

**[0095]** [Fig. 22](#) bis [24](#) sind Aufsichten und Schnittansichten von Modifikationen des Chiprahmens, der auf dem Chip befestigt ist. In diesen Figuren bestehen IGBT-Chips **25** aus einem Siliziumchip **1** und einem Chiprahmen **41**, der den Umgebungsbereich des Chips abdeckt und schützt. Die Oberfläche des Chips **1** weist einen Kontaktbereich **1** der Gatterelektrode und einen Druckkontaktbereich der Emitterelektrode auf, der von dem Chiprahmen freigelegt ist. In dieser Ausführungsform ist gekennzeichnet, dass der Chiprahmen **41** einen Erstreckungsteil **89** aufweist, und dieser Erstreckungsbereich **89** deckt den Kontaktbereich **7** der Gatterelektrode auf der Oberfläche des Chips ab. Durch die Existenz dieses Erstreckungsteils **89** weist der Chiprahmen **41** eine Funktion zum Halten der Gatterleitung **45** auf. [Fig. 22A](#) ist eine Aufsicht, bei der der kontaktierende Bereich der Spitze des Gatterleiters einen Stecker und einen Tastkopf umfasst, und [Fig. 22B](#) ist eine Schnittansicht entlang der Linie XXIIB–XXIIB dessen. Die Spitze des Tastkopfes ist mit dem Kontaktierungsbereich **7** der Gatterelektrode des Chips **1** durch einen kreisförmigen

Durchbruch in dem Erstreckungsteil **89** verbunden. In [Fig. 23B](#) umfasst der Kontaktierungsbereich der Spitze der Gatterleitung **45** einen Federpin, und der Gatterleiter **45** ist in der Kerbe des Erstreckungsteils **89** angepasst, und die Spitze des Federpins ist mit dem Kontaktierungsbereich **7** der Gatterelektrode verbunden. In [Fig. 24B](#) umfasst der Kontaktierungsbereich der Spitze des Gatterleiters **45** einen Stecker und einen eingebetteten Federpin, und dieser Federpin ist mit dem Kontaktierungsbereich **7** der Gatterelektrode auf der Oberfläche des Chips **1** verbunden durch den Durchbruch mit einem rechteckigen Abschnitt in dem Erstreckungsteil **89**, der in [Fig. 24A](#) gezeigt ist.

**[0096]** In [Fig. 25](#) ist kollektiv eine Struktur von verschiedenen Gatterleitern **45** gezeigt, die die Gatterklemme **G** nach außerhalb der Halbleitervorrichtung und der Gatterelektrode jedes IGBT-Chips leiten. Die Gatterklemme wird durch Kombinieren einer Mehrzahl von Gatterleitern **45** gebildet, die von einer Mehrzahl von Chips verbunden sind. Wie in [Fig. 25](#) gezeigt, kann ein Schwingungsverhinderungswiderstand mit dem Gatterleiter **45** verdrahtet sein. Der Widerstand wird vorzugsweise so nahe wie möglich in der Nähe des Chips angeordnet, um die L-Komponente zu vermindern. Ferner wird der Widerstand mit einer isolationsbeschichteten Röhre abgedeckt. Das Verbindungsverfahren des Gatterleiters **45** und der Gatterelektrode **7** des Chips schließen Verfahren ein, die in [Fig. 22–24](#) gezeigt sind. Ferner ist der Stecker an den Tastkopf, einen Federpin oder dergleichen der Gatterelektrode angepasst. Gemäß einer Notwendigkeit kann eine Zener-Diode mit einer Durchbruchspannung von ungefähr 30 V zum Verhindern einer Überspannung des Gatters zwischen dem Gatter und dem Emitter eingefügt werden. Oder ein Kondensator kann zwischen dem Gatter und dem Emitter eingefügt sein.

**[0097]** [Fig. 26A](#) ist eine Aufsicht der thermischen Emitterpufferplatte **39** und eine Schnittansicht entlang der Linie XXVIB–XXVIB dessen. Wie in diesen Figuren gezeigt, weist die für die thermische Emitterpufferplatte **39** verwendete Molybdänplatte eine Dicke von ungefähr 1–2 mm auf, und die vier Ecken sind mit einem Radius einer Krümmung  $R$  von ungefähr 0,2–1 mm verarbeitet. Diese Verarbeitung wird durch Lochen gefolgt durch Barrel Finishing durchgeführt, und die Belastungskonzentration auf die Eckenteile wird freigegeben. Da diese Pufferplatte **39** einen Gatterleiterdurchbruch **93** aufweist, der in dem zentralen Bereich dessen gebildet ist, wird es für den IGBT-Chip verwendet, in dem der Kontaktierungsbereich der Gatterelektrode in dem zentralen Bereich gebildet wird. Der Radius einer Krümmung  $R$  wird auf den Durchbruch **93** angewendet. Diese Verarbeitung hat den gleichen Effekt auf den dünnen weichen Metallfilm aus Kupfer und dergleichen.

**[0098]** Als nächstes wird die Befestigung des Chiprahmens auf dem Chip mit Bezugnahme auf [Fig. 27](#) beschrieben. Der Chiprahmen **41** ist an die Seitenfläche und die Oberfläche der Emittersseite von Chip **1** angefügt, und zu dieser Zeit wird die Ecke des niedrigeren Teils der inneren Seitenwand des anzufügenden Rahmes um ungefähr 0,2 mm abgesenkt. Ein Kleber **49** wird auf die Kontakt ebene des Chiprahmens **41** danach angewendet und beide werden angefügt. Durch eine derartige Verarbeitung kann ein Ausfressen des Klebers **49** auf das Muster auf der Chipoberfläche verhindert werden.

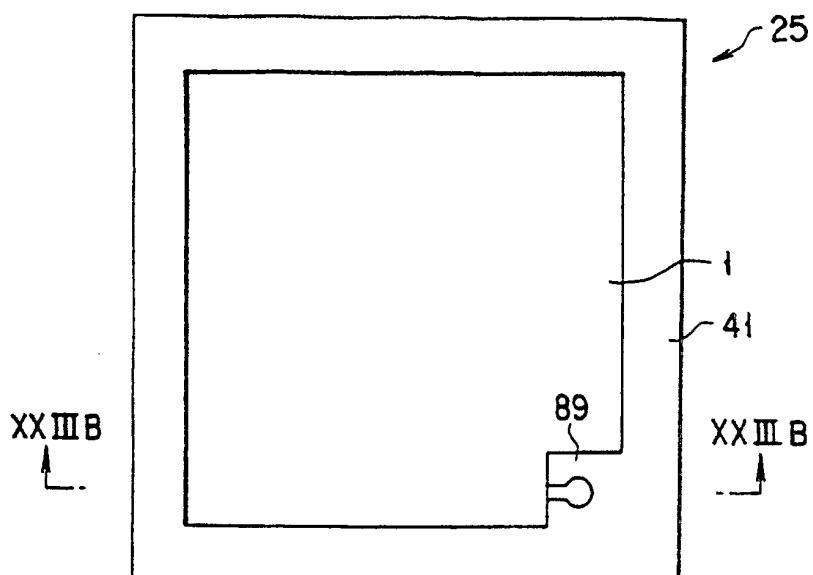

**[0099]** Der äußere Rahmen, der integral den Sammelkörper des Chips schützt, weist eine scheibenartige Form auf und wird als Ringrahmen bezeichnet, aber die vorliegende Erfindung ist nicht auf diese Form beschränkt. Wie in [Fig. 28](#) gezeigt, besteht eine Halbleitervorrichtung mit einer quadratischen Form und in diesem Fall wird auch der äußere Rahmen **29** quadratisch. Da der Chipsammelkörper bei nahe quadratisch ist, wird er kompakter als der mit einer kreisförmigen Form.

**[0100]** [Fig. 29A](#), [Fig. 29B](#) und [Fig. 29C](#) zeigen das Verfahren zum Anfügen eines Thermistors an den Graben der Elektrodenplatte zum Verdrahten der Gatterleitung. Der Thermistor wird für ein Erfassen der Temperatur auf dem Chip verwendet. Wenn die Elektrodenplatte in [Fig. 15](#) verwendet wird, wird ein ausschließlicher Rahmen **91** (nicht in [Fig. 15](#) gezeigt) vorbereitet, und wenn die Elektrodenplatte von [Fig. 14](#) und [Fig. 16](#) verwendet wird, wird der notwendige Graben ausgewählt. In [Fig. 29A](#) und [Fig. 29B](#) wird ein Graben **91** zum Bilden eines Schaltkreises für das Temperaturerfassungselement (Thermistor) in der Elektrodenplatte **35** gebildet, zum Beispiel in [Fig. 15](#) gezeigt, und wird durch einen Silikongummi durch Einbetten eines Thermistors befestigt.

**[0101]** Wie oben beschrieben, weist die Hochgeschwindigkeitsvorrichtung vom Multichip-Druckkontaktyp, in der verschiedene Arten von Mehrfachchips der vorliegenden Erfindung in einer hohen Dichte angeordnet sind, Charakteristiken auf, wie unten beschrieben:

- (1) Es wird erleichtert eine hohe Stromtragfähigkeit der Vorrichtung zu erhalten. Die hohe Stromtragfähigkeit der Vorrichtung wird durch die gleichen Chips erhalten.

- (2) Es wird erleichtert eine hohe Funktionalität und eine hohe Wertsteigerung der Vorrichtung zu erhalten. Eine Kombination von verschiedenen Chips wird möglich.

**[0102]** Ferner wird durch Erstellen der Halbleitervorrichtung vom Druckkontaktyp eine hohe Zuverlässigkeit möglich gemacht, die in einer Hochgeschwindigkeitsleistungsvorrichtung vom konventionellen Modultyp unmöglich gewesen ist, wie unten beschrie-

ben:

- (1) Eine Zuverlässigkeit für den Leistungszyklus und eine thermische Ermüdung durch Bondingfreiheit und eine Freiheit weicher Lötungen wird verbessert. Zum Beispiel wird es in der Halbleitervorrichtung für Traktionsanwendungen möglich, für Leistungszyklen von 6 Millionen Zyklen haltbar zu sein, und einen Temperaturzyklus gegen die thermische Ermüdung von 75.000 Zyklen.

- (2) Ein Kühlen beider Oberflächen wird möglich. Die Kühlmöglichkeit wird zweimal so hoch wie die der konventionellen Oberflächenkühlung, und der äußere Durchmesser des Chips kann auf ungefähr die Hälfte dessen vermindert werden. Umgekehrt wird der äußere Durchmesser des Chips des umgekehrten Leistungstyp-IGBT einer 1200 A-2500 V Klasse 120 mm oder kleiner, was ungefähr die Hälfte dessen des Modultyp-IGBT ist.

- (3) Eine Zuverlässigkeit für hohe Temperaturen und hohe Spannungsbetriebe wird verbessert. Eine keramische Packung, die die tatsächliche Leistung in dem Druckkontaktyp-Halbleiter für Traktionsanwendungen aufweist, kann verwendet werden.

- (4) Eine Verdrahtungsinduktivität wird vermindert. Die Induktivität zwischen Chips kann auf ein Minimum durch eine Druckkontakteierung unterdrückt werden.

**[0103]** Die Hochgeschwindigkeitsleistungsvorrichtung mit einer planaren Hochspannungsstruktur, wird möglich gemacht durch Befestigung eines Chiprahmens von synthetischem Harz an der Chipaußenseite bzw. -umgebung, die bei einem Druckkontakt in einer konventionellen Druckkontaktestruktur unmöglich gewesen ist. Ferner können durch Befestigen des Sammelkörpers des Chips durch einen äußeren Rahmen verschiedene Arten von Chips wie IGBT-Chips, FRD-Chips und dergleichen gesammelt druckkontakteiert werden. Weiterhin können Unterschiede zur Zeit eines gesammelten Druckkontaktees infolge des Unterschiedes der Chips und der Dicke von Teile unterdrückt werden, und ein gleichförmiger Druckkontakt wird durch Einfügen einer Dickeneinstellplatte möglich gemacht und durch ausreichend dickes Ausgestalten der Dicke der thermischen Pufferplatte. Weiterhin kann durch Bilden von Gräben auf der inneren Fläche der Emitter- oder Kollektorelektrodenplatte, die druckkontakteiert werden soll, zugehörig zu der äußeren Größe der Chips, verhindert werden, dass eine Biegekraft auf den Chip ausgeübt wird. Ferner wird durch Bereitstellen des Chiprahmens an einem Erstreckungsteil, der den Kontaktbereich der Gatterelektrode abdeckt, erleichtert, den Kontaktbereich zu schützen und den Gatterleiter mit dem Kontaktbereich zu verbinden.

#### Patentansprüche

##### 1. Druckkontakteotyp-Halbleitervorrichtung umfas-

send:

mehrere Halbleiterchips (1, 25, 27) eine erste Elektrodenplatte (33) und eine zweite Elektrodenplatte (35), wobei jeder der Halbleiterchips (1, 25, 27) von der oberen und unteren Seite von der ersten Elektrodenplatte (33) und der zweiten Elektrodenplatte (35) druckkontakteiert wird, **dadurch gekennzeichnet**, dass jeder der Halbleiterchips (1, 25, 27) eine Halbleiter-Leistungsvorrichtung enthält, wobei die jeweiligen Peripherien des Halbleiterchips (1, 25, 27) jeweils in einem jeweiligen Chiprahmen (41) aus Isolierharz eingeschlossen sind, wobei die Chiprahmen (41) an den jeweiligen Halbleiterchips (1, 25, 27) befestigt sind, so dass jeder der Halbleiterchips (1, 25, 27) gemeinsam mit dem jeweiligen Chiprahmen (41) daran befestigt eine Einheit bildet, wobei die Halbleiterchips (1, 25, 27) auf der gleichen Ebene angeordnet sind, so dass die Chiprahmen (41) aneinander stoßen, und die Halbleiterchips (1, 25, 27) gemeinsam von der oberen und der unteren Seite durch die erste Elektrodenplatte (33) und die zweite Elektrodenplatte (35) jeweils druckkontakteiert werden, so dass Hitze freigegeben wird, die von den Halbleiterchips (1, 25, 27) erzeugt wird.

2. Druckkontakteotyp-Halbleitervorrichtung nach Anspruch 1, wobei eine Rinne (67, 69) in Regionen auf mindestens einer der ersten und zweiten Elektrodenplatten (33, 35) ausgebildet ist, die den jeweiligen Peripherien jedes der mehreren Halbleiterchips (1, 25, 27) entgegengesetzt sind.

3. Druckkontakteotyp-Halbleitervorrichtung nach Anspruch 1 oder 2, wobei zwischen der ersten Elektrodenplatte (33) und der zweiten Elektrodenplatte (35) ein äußerer Rahmen (29) aus Isolierharz installiert ist, wobei der äußere Rahmen (29) eine periphere Region hat, die die Seitenflächen der ersten und zweiten Elektrodenplatte einschließt, und einen Vorsprung (47), der zwischen die erste und die zweite Elektrodenplatte (33, 35) eingefügt ist, um von einer Innenwand der peripheren Region vorzuragen und die Halbleiterchips (1, 25, 27) einzuschließen, die auf der gleichen Ebene angeordnet sind, so dass die Chiprahmen (41) gegeneinander stoßen.

4. Druckkontakteotyp-Halbleitervorrichtung nach Anspruch 2 oder 3, wobei jeder der Halbleiterchips (1, 25 oder 27) eine Kontaktzone (7) einer Elektrode auf der Oberfläche des Halbleiterchips (1, 25, 27) hat, und wobei die entsprechenden Chiprahmen (41) der Halbleiterchips (1, 25, 27) jeweils einen Erweiterungsabschnitt (89) haben, der sich über die Fläche des jeweiligen Halbleiterchips (1, 25, 27) nach innen erstreckt, wobei dieser Erweiterungsabschnitt die Kontaktzone (7) der Elektrode bedeckt.

5. Druckkontakte-Halbleitervorrichtung nach einem der Ansprüche 1 bis 4, wobei eine Wärmepufferplatte (**37** oder **39**) zwischen mindestens eine der ersten und der zweiten Halbleiterplatten (**33**, **35**) und den jeweils einen oder alle Halbleiterchips (**1**, **25** oder **27**) eingefügt ist.

6. Druckkontakte-Halbleitervorrichtung nach Anspruch 1 oder 5, wobei eine Stärkenjustierplatte (**63** oder **65**), die ein weiches Metallblech aufweist, eingefügt ist, um gegen die Druckkontakteebene mindestens einer der ersten und zweiten Elektrodenplatten (**33**, **35**) zu stoßen.

7. Druckkontakte-Halbleitervorrichtung nach einem der Ansprüche 1 bis 6, wobei die jeweiligen Chiprahmen (**41**) an den jeweiligen Halbleiterchips (**1**, **25**, **27**) haften, um die Nennspannung jedes der Halbleiterchips (**1**, **25**, **27**) zu erhöhen.

8. Druckkontakte-Halbleitervorrichtung nach einem der Ansprüche 1 bis 7, wobei die Halbleiterleistungsvorrichtung eine Freilaufdiode oder ein Isolierschicht-Bipolartransistor ist.

Es folgen 14 Blatt Zeichnungen

Anhängende Zeichnungen

F I G. 1

F I G. 2

F I G . 3

F I G . 4

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 6

FIG. 7

FIG. 8A

FIG. 8B

FIG. 8C

F I G. 9

F I G. 10

F I G. 11

F I G. 12

F I G. 13

F I G. 14

F I G. 15

F I G. 16

F I G. 17

F I G. 18

F I G. 19

FIG. 20

FIG. 21

FIG. 22A

FIG. 22B

FIG. 23A

FIG. 23B

FIG. 24A

FIG. 24B

FIG. 26A

FIG. 28

FIG. 29A

FIG. 29B

FIG. 29C