(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4729685号

(P4729685)

(45) 発行日 平成23年7月20日(2011.7.20)

(24) 登録日 平成23年4月28日(2011.4.28)

(51) Int.Cl.

F 1

H03H 17/02 (2006.01)

H03M 3/02 (2006.01)H03H 17/02 641 E

H03H 17/02 655 A

H03M 3/02

請求項の数 17 (全 17 頁)

|               |                               |           |                                             |

|---------------|-------------------------------|-----------|---------------------------------------------|

| (21) 出願番号     | 特願2001-525841 (P2001-525841)  | (73) 特許権者 | 510000633<br>エスティー・エリクソン、ソシエテ、アノニム          |

| (86) (22) 出願日 | 平成12年8月18日 (2000.8.18)        |           | スイス国プラン-レ-ズアト、シュマン、デュ、シャン-デ-フィュ、39          |

| (65) 公表番号     | 特表2003-510876 (P2003-510876A) | (74) 代理人  | 100117787<br>弁理士 勝沼 宏仁                      |

| (43) 公表日      | 平成15年3月18日 (2003.3.18)        | (72) 発明者  | マルチン、マシュマン<br>ドイツ連邦共和国ミュンヘン、シュパンジーシュトラーセ、77 |

| (86) 國際出願番号   | PCT/US2000/022826             |           |                                             |

| (87) 國際公開番号   | W02001/022582                 |           |                                             |

| (87) 國際公開日    | 平成13年3月29日 (2001.3.29)        |           |                                             |

| 審査請求日         | 平成19年8月16日 (2007.8.16)        |           |                                             |

| (31) 優先権主張番号  | 09/400,700                    |           |                                             |

| (32) 優先日      | 平成11年9月20日 (1999.9.20)        |           |                                             |

| (33) 優先権主張国   | 米国(US)                        |           |                                             |

審査官 関 知子

最終頁に続く

(54) 【発明の名称】プログラマブルシフタを使用する FIR フィルタ

## (57) 【特許請求の範囲】

## 【請求項 1】

少なくとも 1 つのフィルタ係数を含んだフィルタ関数を実現するように構成された回路装置であつて、

(a) 入力値、及び、前記フィルタ関数からのフィルタ係数を表す予めスケーリングされたフィルタ係数を受け取り、それらの積を出力するように構成された乗算器と、

(b) 前記乗算器から前記積を受け取るように結合され、前記予めスケーリングされたフィルタ係数と関連したシフト距離だけ前記積を右にシフトして、シフトされた積を生成するように構成されているプログラマブルシフタと、

を備え、

前記予めスケーリングされたフィルタ係数は、前記フィルタ関数からの前記フィルタ係数に対して、2に等しい桁移動子により、前記シフト距離の累乗にスケーリングされるものであり、前記フィルタ関数からの前記フィルタ係数に前記桁移動子を掛け、さらに整数値に丸めたものに等しいことを特徴とする回路装置。

## 【請求項 2】

前記予めスケーリングされたフィルタ係数は、前記フィルタ関数からの前記フィルタ係数に前記桁移動子を掛けて、整数値に丸め、さらに前記予めスケーリングされたフィルタ係数に関連した補正項を加えたものに等しいことを特徴とする請求項 1に記載の回路装置。

## 【請求項 3】

10

20

前記フィルタ関数は複数のフィルタ係数を含み、かつ、前記回路装置は、前記乗算器に結合された係数メモリをさらに備え、前記係数メモリは、複数の予めスケーリングされたフィルタ係数を格納するように構成され、各予めスケーリングされたフィルタ係数は、前記複数のフィルタ係数の1つを表すことを特徴とする請求項1に記載の回路装置。

【請求項4】

前記複数の予めスケーリングされたフィルタ係数の各々が共通の幅Wを有し、かつ、前記各予めスケーリングされたフィルタ係数は、等式

$$2^{W-1}-1 \quad | \quad \text{予めスケーリングされた} \text{ フィルタ係数 } | \quad 2^{W-2}$$

を満たすように構成されていることを特徴とする請求項3に記載の回路装置。

【請求項5】

前記複数の予めスケーリングされたフィルタ係数の各々は、シフト距離に関連し、前記回路装置は、

(a) 前記プログラマブルシフタに結合され、かつ、前記各予めスケーリングされたフィルタ係数に関連したシフト距離を格納するように構成されたシフトメモリと、

(b) 一連の入力値を格納するように構成された入力メモリと、

(c) 前記入力メモリ、前記係数メモリ及び前記シフトメモリにアクセスして、入力値と予めスケーリングされたフィルタ係数とを前記乗算器にそれぞれ出力し、シフト距離をプログラマブルシフタに出力して、複数のシフトされた積を生成するように構成された制御回路と、

をさらに備えていることを特徴とする請求項3に記載の回路装置。

【請求項6】

前記複数のシフトされた積を合計してフィルタ処理された出力を生成するように構成された合計回路をさらに備えていることを特徴とする請求項5に記載の回路装置。

【請求項7】

前記フィルタ関数からの前記複数のフィルタ係数は複数の対称的なフィルタ係数の対を含み、前記係数メモリ及び前記シフトメモリの各々は、各フィルタ係数の対の1つのフィルタ係数に関連した予めスケーリングされた係数及びシフト距離を格納するように構成されており、前記入力メモリが第1及び第2の出力ポートを含み、各出力ポートが前記複数の入力値の1つを出力するように構成されており、前記回路装置は、前記第1及び第2の出力ポートと前記乗算器との間に結合され、かつ、前記第1及び第2の出力ポートから出力される前記入力値を合計するように構成された加算器をさらに備え、前記制御回路は、さらに、前記入力メモリを制御して、フィルタ係数の対の両方のフィルタ係数に関連した入力値を前記入力メモリの前記第1及び第2の出力ポートから同時に出力するように構成されていることを特徴とする請求項5に記載の回路装置。

【請求項8】

前記フィルタ関数は、有限インパルス応答(FIR)フィルタ関数であることを特徴とする請求項1に記載の回路装置。

【請求項9】

前記乗算器は、Booth-Wallace乗算器を含むことを特徴とする請求項1に記載の回路装置。

【請求項10】

請求項1に記載の回路装置を備えていることを特徴とする集積回路装置。

【請求項11】

請求項1に記載の回路装置を備えていることを特徴とする電子装置。

【請求項12】

(a) 一連の入力値を格納するように構成された入力メモリと、

(b)  $n$ を整数のシフト距離とすると、各々が、 $2^n$ によりスケーリングされて整数値に丸められさらに関連した補正項を加えられた所定のフィルタ関数の理想的なFIRフィルタ係数に等しい複数の予めスケーリングされたフィルタ係数を格納するように構成された係数メモリと、

10

20

30

40

50

(c) 各々の予めスケーリングされたフィルタ係数に関連した前記シフト距離nを格納するように構成されたシフトメモリと、

(d) 前記入力メモリから入力値を受け取り、前記係数メモリから予めスケーリングされたフィルタ係数を受け取り、かつ、それらの積を出力するように構成された乗算器と、

(e) 前記乗算器からの前記積、及び、前記積が生成された前記予めスケーリングされたフィルタ係数に関連した前記シフト距離nを受け取り、前記積をnビットだけ右にシフトするように構成されたプログラマブルシフタと、

(f) 前記入力メモリ、前記係数メモリ及び前記シフトメモリにアクセスして、入力値及び予めスケーリングされた係数を前記乗算器に出力し、シフト距離を前記プログラマブルシフタに出力して、複数のシフトされた積を生成するように構成された制御回路と、

(g) 前記複数のシフトされた積を合計してフィルタ処理された出力を生成するように構成された合計回路と、

を備えていることを特徴とするデジタル有限インパルス応答(FIR)フィルタ回路装置。

#### 【請求項13】

前記複数の予めスケーリングされたフィルタ係数の各々が共通の幅Wを有し、かつ、前記各予めスケーリングされたフィルタ係数は、等式

$$2^{W-1}-1 \quad | \quad \text{予めスケーリングされたフィルタ係数} \quad | \quad 2^{W-2}$$

を満たすように構成されていることを特徴とする請求項16に記載の回路装置。

#### 【請求項14】

前記フィルタ関数からの前記複数のフィルタ係数は複数の対称的なフィルタ係数の対を含み、前記係数メモリ及び前記シフトメモリの各々は、各フィルタ係数の対の1つのフィルタ係数に関連した予めスケーリングされた係数及びシフト距離を格納するように構成されており、前記入力メモリが第1及び第2の出力ポートを含み、各出力ポートが前記複数の入力値の1つを出力するように構成されており、前記回路装置は、前記第1及び第2の出力ポートと前記乗算器との間に結合され、かつ、前記第1及び第2の出力ポートから出力される前記入力値を合計するように構成された加算器をさらに備え、前記制御回路は、さらに、前記入力メモリを制御して、フィルタ係数の対の両方のフィルタ係数に関連した入力値を前記入力メモリの前記第1及び第2の出力ポートから同時に出力するように構成されていることを特徴とする請求項12に記載の回路装置。

#### 【請求項15】

一連の入力値を処理してフィルタ関数を表すフィルタ処理された出力を生成する方法であって、

(a) 一連の入力値を受け取るステップと、

(b) シフトされた積ごとに、

(i) 前記一連の入力値からの入力値に、前記フィルタにより実現されるフィルタ関数からのフィルタ係数を表す予めスケーリングされたフィルタ係数を掛け、積を生成すること、及び、

(ii) 前記予めスケーリングされたフィルタ係数に関連したシフト距離だけ前記積を右にシフトして前記シフトされた積を生成すること、

を含む、複数のシフトされた積を生成するステップと、

(c) 前記複数のシフトされた積を合計して前記フィルタ処理された出力を生成するステップと、

を備え、

各予めスケーリングされたフィルタ係数は、前記フィルタ関数からの前記表されたフィルタ係数に対して、2に等しい桁移動子により、前記シフト距離の累乗にスケーリングされるものであり、

各予めスケーリングされたフィルタ係数は、前記フィルタ関数からの前記表されたフィルタ係数に前記桁移動子を掛け、さらに整数値に丸めたものに等しいことを特徴とする方法。

10

20

30

40

50

## 【請求項 16】

各予めスケーリングされたフィルタ係数は、前記フィルタ関数からの前記表されたフィルタ係数に前記桁移動子を掛けて、整数値に丸め、さらに前記予めスケーリングされたフィルタ係数に関連した補正項をえたものに等しいことを特徴とする請求項 15に記載の方法。

## 【請求項 17】

前記複数の予めスケーリングされたフィルタ係数の各々が共通の幅Wを有し、かつ、前記各予めスケーリングされたフィルタ係数は、等式

$$2^{W-1} - 1 \leq \text{予めスケーリングされたフィルタ係数} \leq 2^W - 2$$

を満たすように構成されていることを特徴とする請求項 15に記載の方法

10

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、概してデジタルフィルタに関し、より詳細には、有限インパルス応答（FIR）フィルタ及びそのハードウェアの実現に関する。

## 【0002】

## 【従来の技術】

有限インパルス応答（FIR）フィルタのようなデジタルフィルタは、いくつかの電子的な用途で使用されている。例えば、デジタルフィルタは、無線通信の用途、例えば、無線電話送受話器、無線ネットワークのハードウェアなどで広範に使用されて、入力無線信号をフィルタにかけ処理して、そこからデータストリームを回復する。一般的に、しかしそれに限られないが、デジタルフィルタは、他の制御回路及びデジタル信号処理回路とともに集積回路装置に実装される。

20

## 【0003】

デジタルフィルタは、比較的高速にデータを処理しなければならないことが多く、そのために多くの場合に、デジタルフィルタ内の内部遅延を最小にすることが望ましい。また、小型化に向けての絶え間のない努力を想定すれば、デジタルフィルタは、集積回路装置上において可能な限りコンパクトでかつ可能な限り小さなスペースを占めることが多くの場合に望ましい。さらに、無線電話送受話器のような携帯型の用途で使用されるときには、装置の全体的な電池寿命の延長を支援するために、デジタルフィルタの電力消費を最小限にすることが多くの場合に望ましい。

30

## 【0004】

1つの一般に使用される種類のデジタルフィルタは、有限インパルス応答（FIR）フィルタであり、そのフィルタの（時間領域における）挙動は、一般に次式で表される。

## 【0005】

## 【数1】

$$y[k] = \sum_{i=0}^{n-1} x[k-i] \times H[i] \quad (1)$$

ここで、nは係数の番号であり、x [ k ] はk番目の時間ステップにおける入力値であり、H [ i ] は符号付き整数 FIR フィルタ係数であり、さらに y [ k ] は k 番目の時間ステップにおけるフィルタのフィルタ処理された出力値である。

40

## 【0006】

そのような伝達関数をハードウェアで実現するために、一般に別個の乗算器段と加算器段とが利用されて、乗算器段は各入力値とフィルタ係数との積を生成するように構成されており、さらに加算器段は乗算器段により生成された積を合計してフィルタ処理された出力を生成するように構成されている。いくつかの用途では、並列回路を使用して各乗算を並列に行うように、乗算器段は構成されている。しかし、スペースが制約されるいくつかの用途では、そのような並列回路は大きすぎることが多い。他の方法では、単一の乗算器が使用されて、その単一乗算器に入力値と係数とを順次に供給して積を生成し、それが加

50

算器段で合計される。

【0007】

乗算器構造の最適化の進歩にもかかわらず（例えば、ブース・ウォレス（Booth-Wallace）乗算器の設計）、多くの場合に依然として乗算器段がFIRフィルタの中で最も大きくかつ最も遅い構成要素である。従って、フィルタ設計に関連した大きさ、電力消費及び遅延を減少させようとする試みは、フィルタの乗算器段の縮小に集中することが多い。

【0008】

乗算器の大きさを小さくする1つの方法は、理想的なフィルタ係数を表すために使用されるディジタル値の分解能（又は、ビット数）を減少させることである。しかし、分解能を減少させると、理想的なフィルタ係数を固定幅のディジタル値に丸めて変換することに起因する打切り誤差の増加のために、必ず、フィルタの応答（即ち、実際のフィルタ変換関数が、そのフィルタが目的として設計された理想的な伝達関数に一致する程度）もまた減少する。従って、係数の分解能を減少させることができる程度は、フィルタの必要な許容範囲で制限されることが多い。

10

【0009】

他の方法では、FIRフィルタ係数の操作により使用乗算器を無くそうとする。一例として、係数は2の整数乗に等しいことが要求され得るものであり、その結果、簡単で効率のよいシフトレジスタの設計を使用して乗算を行うようにすることができる。他の例として、加算器とシフトレジスタとの構成可能なブロックを使用して、基本的に各係数を2の整数乗の和として表し、それにより、入力値に対して複数のシフト動作を並列に行って係数と入力値との乗算を表すことができる（例えば、10の値を持つ係数の乗算は、8及び2と入力値との乗算にそれぞれ対応する2つのシフト動作の結果を互いに合計することで、実現し得る。

20

【0010】

【発明が解決しようとする課題】

しかし、これらの方法の各々では、係数の分解能が著しく減少して、適切なフィルタ応答を維持するために追加の係数が必要になることがある。その結果、追加の係数を処理するための追加の回路が必要になり、フィルタのスペース、電力消費及び遅延が増大する。さらに、そのような乗算器代替物の配置は、乗算器よりも難しくかつ複雑であることが多く、結果として生じる回路配置は効率のよいものではない。いくつかの乗算器設計は、コンパクトさ、低電力消費及び速度に対して高度に最適化されており、その結果、そのような代替構造の乗算器に優る利益は、あるとしても、無視できる程度である。さらに、そのような代替構造で得られる大きさ縮小の改良は、多くの場合に遅延の増大で埋め合わされて、いくつかの高速の用途に対してそのような構造は不適当になっている。

30

【0011】

従って、当技術分野では、従来の設計よりも小さなスペース、小さな電力でかつ遅延が少なくて望ましいフィルタ応答を実現する改良されたディジタルフィルタ設計が非常に必要とされている。

【0012】

【課題を解決するための手段】

40

本発明は、従来技術に関連したこれら及び他の問題に対処して、ディジタルフィルタの乗算器段が、乗算器の下流に結合されたプログラマブルシフタを使用して、所定のフィルタ機能を実現する「予めスケーリングされた」フィルタ係数と入力値との積をシフトする回路構成及び方法を提供する。適切な予めスケーリングされたフィルタ係数、及び、積をシフトすべき「シフト距離」の適切な選択によって、フィルタのディジタル実施に関連した打切り誤差を最小にすることが可能であり、同じ係数分解能を持った他のフィルタ実施に比べて改良されたフィルタ応答を提供し、又は、代替として、減少された係数分解能を用いて適切なフィルタ応答を維持することができるようになる。さらに、係数分解能を減少させた場合に、同等の従来設計よりも比較的小さなスペース、小さな電力消費、さらに少ない遅延のフィルタを実現することができる。

50

## 【0013】

いくつかの方法でフィルタ関数からの理想的なフィルタ係数を表すために、本発明に従った予めスケーリングされたフィルタ係数を使用することができる。予めスケーリングされたフィルタ係数に関連したシフト距離を桁移動子とする2の累乗に等しいスケーリング係数で、理想的なフィルタ係数をスケーリングすることにより、予めスケーリングされたフィルタ係数を、理想的なフィルタ係数から得ることができる。そのようなものとして、予めスケーリングされたフィルタ係数に固有なスケーリング動作は、プログラマブルシフタでシフト動作を行うことにより不要になる。

## 【0014】

また、理想的なフィルタ係数とスケーリング係数との積に対して行われる丸め操作によって、予めスケーリングされたフィルタ係数を、理想的なフィルタ係数から得ることができる。さらに、理想的なフィルタ係数と基準係数の丸められた積とに補正項を加えることによって、予めスケーリングされたフィルタ係数を、理想的なフィルタ係数から得ることができる。補正項を加えることで、スケーリング係数によるスケーリングで実現されるもの以上に、フィルタ応答の一層の改良を得ることができる。

## 【0015】

一般に、理解されるであろうが、本発明に従った様々な予めスケーリングされたフィルタ係数の表現を生成するために、いくつかの演算を実施することができる。従って、本発明はここで議論する特定の実施に限定されない。

## 【0016】

本発明を特徴付けるこれら及び他の利点及び特徴は、本明細書に添付され本明細書の他の部分を形成する特許請求の範囲に示される。しかし、本発明及びその使用により達成される利点及び目的をより適切に理解するために、図面及び本発明の例示的な実施形態が説明されている添付の記述内容を参照すべきである。

## 【0017】

## 【発明の実施の形態】

本発明に従った実施形態は、一般に、ハードウェア回路で有限インパルス応答(FIR)ディジタルフィルタを効率的に実施するために使用される。以下でより明らかになるように、フィルタ処理の品質にほとんど又は全く悪影響を及ぼすことなく、フィルタの大きさ、電力消費、及び遅延を最小にできる。

本発明をより適切に理解するために、以下で次の用語を使用する。

H[i] 理想的なフィルタ係数

h[i] 符号付き整数フィルタ係数

H\*[i] スケーリングされた理想的なフィルタ係数

h\*[i] 予めスケーリングされた符号付き整数フィルタ係数

n FIRフィルタ係数の番号

x[k] k番目のFIRフィルタ入力値

y[k] k番目のFIRフィルタ出力値

z\_k k番目の複素周波数点

R 所望の伝達関数と達成される伝達関数との間の偏差を決定する離散的(計算された)実伝達関数の点の数

S E 二乗誤差、離散的(Rの周波数点z\_kについて計算された)実伝達関数と離散化(同じRの周波数点z\_kについて計算された)理想的な(所望の)伝達関数との間の合計二乗差

s[i] FIRフィルタ動作時のシフト距離

c[i] 補正項

W 最終FIRフィルタ係数の分解能

T 丸められた結果が所望FIR係数範囲(-2^{W-1} h[i] × 2^T - 2^{W-1} - 1)に適合するように、理想的なFIRフィルタ係数に掛ける共通係数2^Tを決定する。

## 【0018】

10

20

30

40

50

さらに、そのようなフィルタの使用及び構成の背景にある原理を具体的に説明する前に、1つの従来のFIRフィルタ設計を簡単に説明する。

【0019】

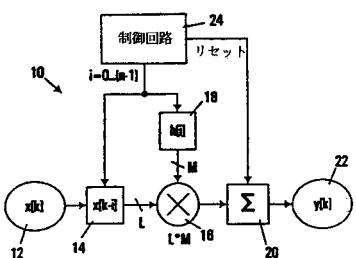

具体的には、図1は、上の式(1)で表される伝達関数を実現することができる1つの従来のFIRフィルタ設計10を示す。フィルタ10は、12で表されるような入力データ $x[k]$ を受け取り、最後のnの入力値が任意の与えられた時間ステップkでの計算に使用することができるよう、そのような入力データを入力メモリ14(例えば、ランダムアクセスメモリ、レジスタ又はラッチのバンク、又は他の形態の記憶装置)に格納する。入力メモリ14の出力は、乗算器16の1つの入力に供給される。その乗算器の他方の入力は係数メモリ18に結合され、その係数メモリ18には、フィルタ10で実現される伝達関数を表すフィルタ係数がその中に格納されている。乗算器16の出力は合計回路20に供給され、その合計回路20が乗算器で出力された値を累積し、時間ステップkの結果 $y[k]$ を出力22から出力する。

【0020】

制御回路24は各メモリ14、18に結合されて、各メモリ14、18に向けるべき一連のインデックス値iを供給して、適切な入力及び係数項を順次に乗算器16に出力する。その結果、乗算器は、入力値とフィルタ係数との適切な積を合計回路20に順次に出力する。制御回路24は、また、第1の項を乗算器16に供給する前に、リセット信号を合計回路20に出力するようにも構成される。その結果、総てのインデックス値 $0 \dots n-1$ がメモリ14、18に供給されると、合計回路が補正結果を出力22から出力する。

【0021】

入力データ $x[k]$ はLビット符号付き整数値で表され、各FIRフィルタ係数 $h[i]$ はMビット符号付き整数値(以下で、項 $h[i]$ で示す)で表されると想定すると、単一の出力値 $y[k]$ を計算するには、 $nL \times M$ の符号付き乗算及び $L \times M$ 乗算器が必要になる。上で議論したように、乗算器は比較的大きな機能ブロックであり、フィルタの全遅延の相当な部分を占めるだけでなく、フィルタで使用される全電力の相当な部分を消費することが多い。そのようなものとして、FIR乗算器に関連した遅延だけでなく、大きさも最小にすることが望ましい。乗算器のスペースの要求、電力消費及び遅延特性を最適化するいくつかの乗算器の設計が開発された。しかし、大きさ、電力消費及び遅延の減少は、乗算器に供給される各入力値の分解能の減少によって単純に起こり得るそれらの減少に一致しない可能性がある。

【0022】

各入力値と「予めスケーリングされた」フィルタ係数との積の結果に対して可変シフト動作が行われる乗算器段を使用することにより、本発明に従って、乗算器の大きさを縮小することができる。従って、変更されたフィルタの式は、次式のようになる。

【0023】

【数2】

$$y[k] = \sum_{i=0}^{n-1} \frac{x[k-i] \times h^*[i]}{2^{s[i]}} \quad (2)$$

ここで $h^*[i]$ は予めスケーリングされた符号付き整数係数であり、 $s[i]$ は予めスケーリングされた係数と入力値 $x[k-i]$ との積が右にシフトされる( $2^{s[i]}$ で割るのに等しい)可変シフト距離である。

【0024】

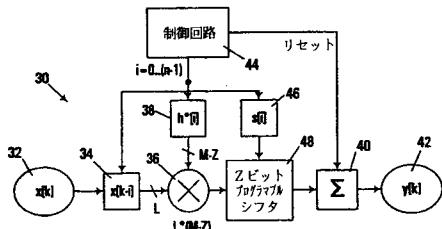

上記のフィルタの式を実現するために使用される可能性のあるフィルタ設計の1つの適当な表現は、図2にフィルタ30として図示する。フィルタ30は、図1のフィルタ10と類似しており、入力32、入力メモリ34、乗算器36、係数メモリ38、合計回路40、出力42及び制御回路44を使用している。しかし、フィルタ10とは異なって、フ

10

20

30

40

50

イルタ30は、予めスケーリングされた係数 $h^*[i]$ を係数メモリ38に格納し、さらに、各フィルタ係数に対するシフト距離 $s[i]$ を格納するシフトメモリ46、並びに、乗算器36の出力と合計回路40との間に置かれたプログラマブルシフタ48を使用する。シフトメモリ46は制御回路44からインデックス入力を受け取り、それに応答して、シフタ48が乗算器36の出力を右にシフトさせなければならないシフト距離を出力する。

#### 【0025】

以下で明らかになるように、予めスケーリングされた係数及び乗算後シフトの使用によって、より少ないビットに符号化されたフィルタ係数を用いて、より優れたフィルタ性能を得ることができる。そのビットは、図2でM-Zの幅を持つ予めスケーリングされた係数で表わされる（また、以下ではWとして示す）。その結果、乗算器36の大きさは、 $L \times (M - Z)$ 乗算器に縮小させることができて、大きさ、電力消費及び遅延が節約される。特定の設計に關したZの最適値の選択については、図5に關連して以下でより詳細に説明する。

#### 【0026】

本発明に従った予めスケーリングされた係数は、少なくとも、丸め及び打切りの前に $2^{s[i]}$ の値で関連した理想的な係数をスケーリングして丸め及び打切りの動作に起因する誤差を減少させることを取り入れている。さらに、いくつかの実施においては、最も大きな係数が許可され選ばれた係数の幅Wに適合するように、理想的な係数の総てを共通の係数 $2^T$ でスケーリングすることも必要となり得る。換言すると、共通スケーリング動作を行う際に使用するTの値は、次の式に従って設定しなければならない。

$$| \text{round}(\max(h[i]) \times 2^T) | = 2^{W-1} - 1 \quad (3)$$

具体的には、丸め及び打切りの前に、理想的な係数 $H[i]$ がスケーリングされて、次式のスケーリングされた理想的な係数 $H^*[i]$ が生成される可能性がある。

$$H^*[i] = H[i] \times 2^T \times 2^{s[i]} = 2^{W-1} - 1 \quad (4)$$

ここで共通スケーリング動作を行う必要がない場合、Tはゼロに等しくてもよい。

#### 【0027】

本発明に従った予めスケーリングされた係数の1つの実施では、次式に示すように、Wビット符号付き整数に丸められ打切られたスケーリングされた理想的な係数 $H^*[i]$ が使用される。

$$\begin{aligned} |h^*[i]| &= |\text{round}(H^*[i])| \\ &= |\text{round}(H[i] \times 2^T \times 2^{s[i]})| \\ &= 2^{W-1} - 1 \end{aligned} \quad (5)$$

予めスケーリングされた係数ごとにシフト距離を適切に選ぶことによって、フィルタ係数の符号付き整数表現の先頭のゼロを取り除いて、そのような係数の少数部分を予めスケーリングされた係数の中に入れることができる限りにおいて、利点が得られる。

#### 【0028】

本発明に従った予めスケーリングされた係数の他の実施では、追加の符号付き整数補正項 $c[i]$ が、次式で示すように、丸められ切り捨てられたスケーリングされた理想的な係数 $H^*[i]$ に加えられる。

$$h^*[i] = \text{round}(H[i] \times 2^T \times 2^{s[i]}) + c[i] \quad (6)$$

各予めスケーリングされた係数に対する適切な補正項 $c[i]$ の決定は、数学的なシミュレーション及び解析によろうが、又は直接的な経験プロセスによろうが、いくつかの方法で行われ得る。さらに、図5に關連して以下で議論するように、最適な補正項の決定は、最適なシフト距離及び係数（従って、乗算器）幅の減少の決定と組み合わされ得る。しかし、他の実施形態では、そのような最適値の選択は、互いに独立に行われ得る。

#### 【0029】

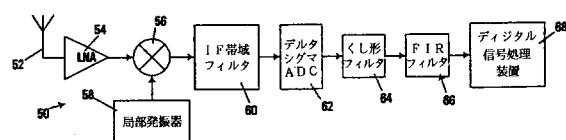

ここで図3に移ると、本発明に従ったFIRフィルタ設計の使用に適した1つの特定の環境は無線通信用途、例えば、無線電話のような無線通信装置50の受信経路であり、その一般的な構成は当技術分野で周知である。装置50はアンテナ52を含むものとして図

10

20

30

40

50

示されている。そのアンテナ 5 2 は無線信号を受信し、その信号を低雑音増幅器 5 4 に送り、その低雑音増幅器 5 4 の出力は、ミキサ 5 6 により局部発振器 5 8 からの中間周波( I F )信号と組み合わされ、I F 帯域フィルタ 6 0 を通してフィルタ処理されて、無線信号からアナログデータ信号を復調する。デルタシグマアナログディジタル変換器( A D C ) 6 2 が、そのアナログ信号を受け取り、デジタル信号を生成する。そのデジタル信号は、くし形フィルタ 6 4 に供給され、次に、デルタシグマ A D C で生成された高周波量子化雑音を除去する低域フィルタとして動作するデジタル F I R フィルタ 6 6 に供給される。フィルタ 6 6 の出力は、受け取られたデジタル信号を用途に適切な方法で処理するデジタル信号処理装置 6 8 に供給される。

## 【 0 0 3 0 】

10

しかし、理解されるであろうが、本発明に従った F I R フィルタは、F I R フィルタが一般に使用される無数の他の電子装置で使用され得る。例として、他の無線応用分野、高速信号処理応用分野などで使用される他の装置がある。従って、本発明はここで議論した特定の無線の用途に限定されない。

## 【 0 0 3 1 】

さらに、理解されるであろうが、F I R フィルタは 1 つ又は複数の集積回路装置に組み込まれ得るものであり、さらにそのような集積回路装置は、F I R フィルタの機能を実施するだけであることもあり、又は本発明に従った他の機能も実施する可能性がある。例えば、図 3 に示される例示的な用途では、F I R フィルタ 6 6 は、A D C 6 2 、くし形フィルタ 6 4 、デジタル信号処理装置 6 8 、及び他のデジタルハードウェア回路とともに单一集積回路装置に実装され得るということが予期されている。また、システムオンチップ( S O C )用途のような応用分野では、追加のアナログ回路、例えば、L N A 5 4 、ミキサ 5 6 及び I F 帯域フィルタ 6 0 もまた、同じ集積回路装置に組み込まれ得る。

20

## 【 0 0 3 2 】

さらに、認識すべきことであるが、ここでハードウェア定義プログラムと呼ぶ、デバイス上の回路配列の配置を定義する 1 つ又は複数のコンピュータデータファイルを使用して、集積回路装置は一般に設計製造される。そのプログラムは一般に、設計ツールによって公知の方法で生成され、その後製造時使用されて、半導体ウェハに適用される回路配列を定義する配置マスクを作成する。一般に、そのプログラムは、V H D L 、 v e r i l o g 、 E D I F などのハードウェア定義言語( H D L )を使用して、予め定義されたフォーマットで与えられる。このように、本発明は完全に機能する集積回路装置に実装された回路配列に関して以上及び以下に記載されており、当業者は理解するであろうが、本発明に従った回路配列は様々な形のプログラム製品として配布することができるし、また、本発明はその配布を実際に行うために使用される信号記録媒体の特定の種類に無関係に等しく適用される。信号記録媒体の例には、特に、揮発性及び不揮発性メモリ装置、フロッピーディスク、ハードディスクドライブ、C D R O M 、D V D のような記録可能型媒体、及びデジタル通信リンク及びアナログ通信リンクのような伝送型媒体が含まれるが、これらに限定されない。

30

## 【 0 0 3 3 】

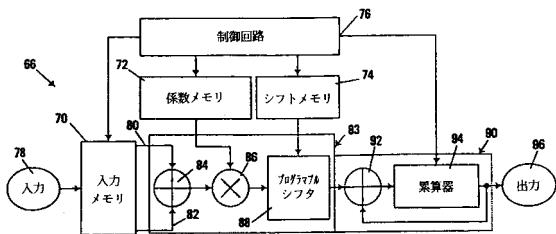

さて、図 4 は、制御回路 7 6 により制御される入力メモリ 7 0 、係数メモリ 7 2 及びシフトメモリ 7 4 を含んだ F I R フィルタ 6 6 の 1 つの適当な実施を示す。図示の実施形態では、メモリ 7 2 及び 7 4 は読み出し専用メモリ( R O M )であるが、他の実施形態では、様々な揮発性又は不揮発性ランダムアクセスメモリ( R A M )装置のようなリプログラマブルメモリが使用され得る。

40

## 【 0 0 3 4 】

フィルタ 6 6 は、対称的な F I R 関数を実現するように構成されており、各フィルタ係数は次式の条件を満たす。

## 【 0 0 3 5 】

$$h [ i ] = h [ ( n - 1 ) - i ] \quad ( 7 )$$

対称的なフィルタ係数を用い、分配の性質  $a b + a c = a ( b + c )$  に基づいて、乗算

50

の前に互いに加算すべき対称的な係数を入力値に掛けることが可能になる。従って、上の式(2)は次のように変更することができる。

【0036】

【数3】

$$y[k] = \sum_{i=0}^{\frac{n}{2}-1} \frac{(x[k-i] + x[k - ((n-1) - i)]) \times h^*[i]}{2^{s(i)}} \quad (8)$$

総てのフィルタ係数は対称的であるので、係数メモリ72及びシフトメモリ74は、それぞれ  $n/2$  の 予めスケーリングされた係数 及びシフト距離を格納する必要があるだけである ( $n$  は偶数であると仮定する)。さらに、入力メモリ70はマルチポートメモリとして構成される可能性があり、それぞれ、ポート80、82から2つの入力値 ( $x[k-i]$  及び  $x[k - ((n-1) - i)]$ ) を同時に出力することができる。また、入力メモリ70は、格納された値をポート80、82から出力するのと並行して、入力ポート78から受け取られた新しい入力値を格納することもできるのが望ましいこともある。

【0037】

ポート80、82から出力される入力値は、乗算器段83に供給され、その乗算器段は加算器84、乗算器86及びプログラマブルシフタ88を含む。加算器84は、係数メモリ72から出力される予めスケーリングされた係数 を乗算器86により掛ける前に、ポート80、82からの入力値を受け取り、合計する。合計された入力値と予めスケーリングされた係数との積は、次に、シフトメモリ74から出力されるシフト距離に基づいて、プログラマブルシフタ88によってシフトされる。

シフトされた積は、それから合計段90に供給される。その合計段90は、シフトされた積を累積レジスタ94に格納された現在合計と加算し、それから新しい現在合計を累積器レジスタ94に格納する。レジスタ94は、フィルタ計算の開始時に制御回路76からのリセット信号によりリセットされてもよく、フィルタ処理された出力値をフィルタの出力ポート96に出力する。理解されるであろうが、レジスタ94の出力は計算中に利用し得るようにしておく、又は、フィルタ処理された出力の計算の終了時にラッチ動作によってのみアクセスできるようにしてもよい。

【0038】

図示された実施形態の乗算器86は、Booth-Wallace乗算器として実現されており、その乗算器の使用及び構成は当技術分野で公知である。しかし、係数メモリ72から出力される予めスケーリングされたフィルタ係数 に必要な減少された分解能に基づいて、フィルタ性能を犠牲にすることなく、より小さな乗算器を使用することができる。さらに、他の乗算器構成を代替として使用することができる。

【0039】

動作に関して、制御回路76は、新しい入力値が入力ポート78で受け取られる各入力サイクルのための計算を行うように構成されている。各サイクル中に、制御回路76は、最初にレジスタ94をリセットし、ポート78で受け取られた新しい入力値を入力メモリ70に格納する。それから、制御回路76は  $n/2$  の制御信号をメモリ70、72及び74に順次に供給して、上の式(8)を実現するために、メモリが適切な入力値、予めスケーリングされた係数 及びシフト距離を出力するようにする。

【0040】

上の連続の動作を実施するのに適した制御回路及びメモリのアーキテクチャの設計は、この開示の恩恵を受ける当業者の能力内に十分にある。例えば、他のアーキテクチャが使用される可能性があるが、制御回路76は、フィルタの入力サイクルごとにインクリメントされる基準ポインタを利用して、入力メモリ70のための適切な制御信号を生成するように構成される可能性があり、その結果、入力メモリ70は論理的に円形配列として構成される。

10

20

30

40

50

## 【0041】

上記の対称的な構成を用いて、非対称な設計に優る重要な利点を実現することができる。性能の観点から、非対称設計の場合の  $n$  回の乗算に対して、 $n/2$  回の乗算を行う必要があるとすれば、フィルタ計算を半分の時間で行うことができる。さらに、設計の観点から、 $n/2$  のフィルタ計算とシフト距離だけを格納する必要があるので、各メモリ 72、74 の大きさが縮小され、従って、フィルタ全体の大きさが縮小される。しかし、理解すべきことであるが、他の実施形態では、例えば上で図 2 に示すように、係数の対称的な性質を利用する必要はない。

## 【0042】

上で言及したように、最適シフト距離及び 予めスケーリングされたフィルタ係数の決定 10 は、経験的又は数学計算方法を含むいくつつかの方法により行ってよい。さらに、そのような決定は、様々な用途で独立又は一括に行ってよい。

## 【0043】

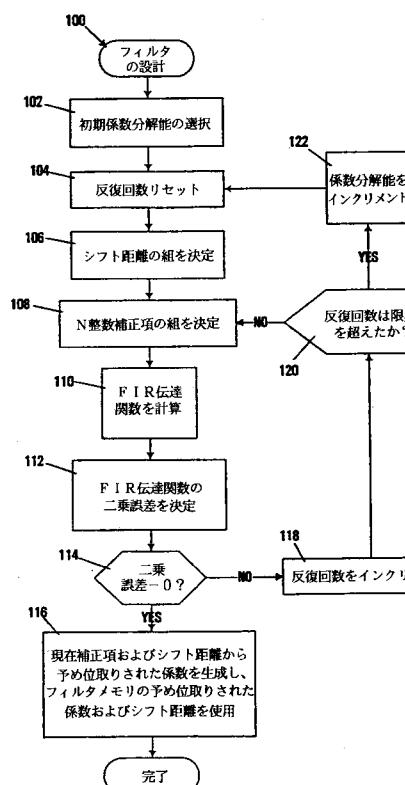

例えば、図 5 はフィルタ設計ルーチン 100 のプログラムの流れを示し、この設計ルーチンはフィルタの最適設計を決定するためにコンピュータにより実行するとよい。ルーチン 100 は、例えば、The Math Works, Inc. から販売されている MATLAB マトリックスペースの数学プログラムで使用するために実施されるようにしてもよい。

## 【0044】

ルーチン 100 は一般に、例えば浮動小数点表現で格納され、次式の要求を満たす  $n$  の理想的な FIR フィルタ係数  $h[i]$  (ここで、 $0 \leq i \leq n-1$ ) の組を含んだ、理想的 20 なフィルタ設計が行われた後で実行される。

## 【数 4】

$$\sum_{i=0}^{n-1} h[i] \cong 1 - |\epsilon|; \quad \epsilon \ll 1 \quad (9)$$

ルーチン 100 は、ブロック 102 で開始し、以下で  $W$  として識別される 予めスケーリングされたフィルタ係数の幅、又は分解能を試験するための初期値を選択する。例えば、係数分解能  $W$  の 1 つの適当な初期値は、FIR フィルタの出力ワード幅の半分であるが、他の初期値が選ばれてもよい。また、このときに、いくつかの実施形態では、最も大きな係数が選ばれた係数幅 (式 (3) に関連して上で説明した) に適合するように、総ての理想的なフィルタ係数に適用する共通 スケーリング係数  $2^T$  を決定することが必要となり得る。 30

## 【0045】

次に、ブロック 104 で、反復回数の値をゼロに初期設定する。このことは、最初の反復が  $W$  の初期値のために行われることを示す。さらに、また、分解能値  $R$  だけでなく反復制限を初期設定することが望ましいこともある。ここで反復制限は  $W$  の各値 (例えば、1000) に対して行うべき反復の最大数を表し、分解能値  $R$  は離散化伝達関数の分解能 (例えば、1024) を表す。

## 【0046】

次に、ブロック 106 で、1 組の最適シフト距離  $s[i]$  を決定する。例えば、次式の条件を満たす各シフト距離  $s[i]$  を選ぶことが望ましいことがある。

$$2^{W-1} - 3 \leq \text{round}(h[i] \times 2^T \times 2^s[i]) \leq 2^{W-2} \quad (10)$$

上限 ( $2^{W-1} - 3$ ) は、各補正項が 2 よりも小さい絶対値を持つという仮定に基づいて選ばれる。理解すべきことであるが、他のシフト距離選択方法が代替として使用される可能性がある。

## 【0047】

次に、ブロック 108 で、次式の条件を満たす 1 組の  $n$  個の整数補正項  $c[i]$  を決定する。

$$2^{W-1} - 1 \leq \text{round}(h[i] \times 2^T \times 2^s[i]) + c[i] \leq 2^{W-2} \quad (1) \quad 50$$

1 )

他の選択方法が使用される可能性があるが、例えば次式を使用して各補正項を選ぶことにより（Monte Carloシミュレーションとして知られている）、上の条件を満たす無差別な補正項をただ単に選ぶことが望ましいことがある。

$$c[i] = \text{round}(4 \times (\text{rand}() - 0.5)) \quad (12)$$

ここで `rand()` は、ゼロ以上でかつ 1 よりも小さい無差別な数を生成する関数である。

【0048】

次に、ブロック 110 で、選ばれたシフト距離と補正項に基づいてフィルタの伝達関数  $H^*(z_k)$  を計算する。それにより、伝達関数は次のようにになる。

【数5】

$$H^*(z_k) = \sum_{i=0}^{n-1} \frac{\text{round}(h[i] \times 2^T \times 2^{s[i]}) + c[i]}{2^{s[i]}} z_k^{-i} \quad (13)$$

ここで、

【数6】

$$z_k = \exp(j\pi \frac{k}{R}); \quad 0 \leq k < R \quad (14)$$

20

である。

$R$  の値は、一般に、 $H^*(z_k)$  伝達関数の細部総てが見えるほどに十分に大きく設定すべきである。例えば、 $R$  は  $10 \times n$  以上の大さな値に設定すべきであることがある。例えば、 $R = 1024$  である。

【0049】

伝達関数が作成されると、 $H^*(z_k)$  と要求された伝達関数との偏差を表す二乗誤差  $SE$  が計算される。特に、伝達関数は次式の条件を満たさなければならない。

【0050】

$$|H_{up}(z_k)| \leq |H^*(z_k)| \leq |H_{low}(z_k)| \quad (15)$$

ここで、 $H_{up}(z_k)$  及び  $H_{low}(z_k)$  は理想的な伝達関数の許容上限及び許容下限である。

30

【0051】

フィルタ設計に関連した誤差を計算するために他の方法が使用される可能性があるが、二乗誤差の近似を使用して誤差を計算する 1 つの方法を下に式 (16) 及び (17) により示す。

【0052】

【数7】

$$SE = \sum_{l=0}^{R-1} \min((H_{up}(z_l) - H^*(z_l))^2, (H_{low}(z_l) - H^*(z_l))^2) \times v_l \quad (16)$$

40

ここで、

【数8】

$$v_l = \begin{cases} 0 & \text{if } |H_{up}(z_k)| \geq |H^*(z_k)| \geq |H_{low}(z_k)| \\ 1 & \text{else} \end{cases} \quad (17)$$

である。

50

## 【0053】

次に、ブロック114で、二乗誤差値がゼロに等しいかどうかを決定する。即ち、現在フィルタ係数及びシフト距離の選択が理想的なフィルタの許容範囲内に完全にあるかどうかを決定する。範囲内にある場合、最適補正項、シフト距離及び係数分解能の設計は完成し、制御はブロック116に進んで、最適補正項及びシフト距離から予めスケーリングされたフィルタ係数を生成し、それから、フィルタメモリ内の現在の予めスケーリングされたフィルタ係数及びシフト距離を使用することができる。それで、ルーチン100は完了する。理解されるであろうが、次の式によって関連した補正項及びシフト距離から予めスケーリングされたフィルタ係数を生成することができる。

$$h^* [i] = \text{round}(h [i] \times 2^T \times 2^s [i]) + c [i] \quad (18) \quad \text{プロック114}$$

ク114に戻って、二乗誤差がゼロでない場合、制御はブロック118に進んで反復回数をインクリメントする。それから、制御はブロック120に進んで、反復回数が反復限界を超えたかどうかを決定する。超えていない場合、制御はブロック108に戻って、新しい組の整数補正項を決定する。しかし、超えている場合、制御はブロック122に進んで係数分解能Wをインクリメントし（共通因数指数Tをインクリメントするだけでなく）、それから、ブロック104に進んで反復回数をリセットし、新しい係数分解能に基づいて新しいシフト距離及び補正項を生成することに取り掛かる。そのようなものとして、係数分解能が順次にインクリメントされて、遂には、適当なフィルタ設計を示すゼロの二乗誤差を生成する適当な組の補正項及びシフト距離が見出される。

## 【0054】

上で計算された予めスケーリングされた係数及びシフト距離の実施には、Wビット幅の係数メモリ72及びL×W乗算器86（ここでLは入力値の幅である）が必要である。シフトメモリ74は、少なくとも最大シフト距離の底2の対数の幅を持たなければならない。ここで、最大シフト距離は、次式を使用して決定されるとい。

## 【0055】

## 【数9】

$$\text{最大シフト距離} = \text{round} \left( \frac{\log_{10} \left( \frac{2^{W-1} - 1}{2^T \times h[i_{\min}]} \right)}{\log_{10} 2} \right) \quad (19) \quad \text{30}$$

ここで、 $h[i_{\min}]$ はフィルタ設計の最小の理想的な係数である。

## 【0056】

予めスケーリングされたフィルタ係数及びシフト距離を生成する他の方法が代替として使用されてもよい。例えば、ルーチン100で必要な処理の量を減少させるために、乱数を使用しない方法が補正項を生成するために使用されてもよい。1つの適当な方法は、短時間アーニール（RTA）のアルゴリズムに依拠し、そのアルゴリズムに従って、ブロック112で生成された二乗誤差を使用して、1組の補正項が別の組の補正項よりもより適切な解につながるかどうかを決定する。いくつかのRTAアルゴリズムが代替として使用される可能性があり、そのようなアルゴリズムの使用及び構成は、本開示の恩恵を受ける当業者の能力内に十分にある。

## 【0057】

理解されるであろうが、本発明に従ったフィルタを設計するために、一般に、理想的な伝達関数が定義され、それから、フィルタのハードウェア実現のための最適な特性を決定するために、ルーチン100と同様なルーチンが実行される。

それから、実際のフィルタ実現の配置が、最適な特性を使用してメモリ及び乗算器の大きさを決定するように行われ、さらに、係数メモリ及びシフトメモリのROM具現物が使用される場合は、どのデータをメモリに表現するかを決定するように、最適な特性を使用し

10

20

30

40

50

て行われる。

【0058】

【実施例】

本発明に従ったフィルタに関連した電力、スペース及び遅延の減少例として、13ビット入力値を受け取るのに適し、かつ下記の対称浮動小数点（理想的な）係数を有する36タップFIR低域フィルタを考える。

【0059】

【表1】

表I：理想的な浮動小数点係数（1/36から18/19）

|             |             |            |              |             |             |

|-------------|-------------|------------|--------------|-------------|-------------|

| 28.199477   | -8.477851   | -45.563247 | -108.996583  | -127.805011 | -67.971068  |

| 87.600110   | 260.351015  | 328.894213 | 176.844236   | -194.887436 | -621.222760 |

| -806.838999 | -472.008357 | 483.348450 | 18866.984224 | 3238.921565 | 4093.000000 |

従来の丸めによって、これらの理想的な係数をただ単に13ビット整数値に切り捨てるとき、次の係数が得られた。

表II：従来の切捨て係数

|      |      |     |      |      |      |

|------|------|-----|------|------|------|

| 28   | -8   | -46 | -109 | -128 | -68  |

| 88   | 260  | 329 | 177  | -195 | -621 |

| -807 | -472 | 483 | 1867 | 3239 | 4093 |

そのときに、打切り誤差は次表のようになつた。

表III：従来の係数打切り誤差（1/36から18/19）

|               |           |           |           |           |           |

|---------------|-----------|-----------|-----------|-----------|-----------|

| -0.19947<br>7 | 0.477851  | -0.436753 | -0.003417 | -0.194989 | -0.028932 |

| 0.399890      | -0.351015 | 0.105787  | 0.155764  | -0.112564 | 0.222760  |

| -0.16100<br>1 | 0.008357  | -0.348450 | 0.015776  | 0.078435  | 0.000000  |

ここで説明したような、予めスケーリング、丸め、及び事後乗算シフトを使用すると（但し、補正項の使用を含まない）、実効フィルタ係数（依然として、13ビットの分解能）は次表のようになつた。

【0060】

【表2】

10

20

30

40

表IV：事後乗算の後の予め位取りされた係数

|             |             |            |             |             |             |

|-------------|-------------|------------|-------------|-------------|-------------|

| 28.203125   | -8.476562   | -45.562500 | -109.000000 | -127.812500 | -67.968750  |

| 87.593750   | 260.375000  | 328.875000 | 176.875000  | -194.875000 | -621.250000 |

| -806.750000 | -472.000000 | 483.375000 | 1867.000000 | 3239.000000 | 4093.000000 |

そのときに、打切り誤差は次表のように減少した。

表V：予め位取りされた係数の打切り誤差 (1/36から18/19)

|           |          |           |           |           |           |

|-----------|----------|-----------|-----------|-----------|-----------|

| 0.003648  | 0.001289 | 0.000747  | -0.003417 | -0.007489 | 0.002318  |

| -0.006360 | 0.023985 | -0.019213 | 0.030764  | 0.012436  | -0.027240 |

| 0.088999  | 0.008357 | 0.026550  | 0.015776  | 0.078435  | 0.000000  |

従って、表IIIと表Vとの間の打切り誤差の減少(%)は次表のようになつた。

表VI：打切り誤差の減少パーセント値

|      |      |      |      |      |      |

|------|------|------|------|------|------|

| 98.1 | 99.7 | 99.8 | 0    | 96.2 | 91.9 |

| 98.4 | 93   | 81   | 80.3 | 88.9 | 87.7 |

| 45   | 0    | 92.3 | 0    | 0    | 0    |

そのように、係数を予めスケーリングすることで、打切り誤差は大幅に減少した。この打切り誤差の減少は、所望の係数分解能の減少で埋め合わされたので、実効打切り誤差は基本的に従来設計と同じであったが、乗算器の大きさは実質的に縮小した。

#### 【0061】

設計をVHDLにより実施した後に、合成、配置し、さらにステップを経た後に、達成可能な面積及び電力消費量の減少は約17%であった。これは、乗算器が全FIRフィルタ面積の33%を占めるに過ぎないためであった。残りの66%は、フィルタのRAM(約60%)並びにROM及び制御回路(6%)が占めた。乗算器のゲート数の減少は相当に大きく、一実施形態では、ゲート数を1498ゲート(13×13、Wallace、条件付き合計)から823ゲート(13×7、Wallace、条件付き合計)に減少した。計算された遅延は、6.58ns(13×13)から5.58ns(13×7)に減少した。これは15%の減少に相当する。結果として、フィルタの全面積は17%だけ縮小し、達成可能な速度は15%だけ増加した(FIRフィルタの中で、乗算器が最も遅いブロックであると想定して)。

#### 【0062】

本発明の精神及び範囲から逸脱することなしに、説明した実施に対して他の修正を行うことができる。従って、本発明は、添付された特許請求の範囲の中に見出される。

#### 【図面の簡単な説明】

【図1】 有限インパルス応答(FIR)フィルタの従来の実施のブロック図である。

【図2】 本発明に従ったFIRフィルタのブロック図である。

【図3】 本発明に従ったFIRフィルタ実施を組み込んだ無線装置の受信経路内の主要な電子構成要素のブロック図である。

【図4】 図3のFIRフィルタのブロック図である。

【図5】 本発明に従ったFIRフィルタの最適フィルタパラメータを決定するのに適したフィルタ設計ルーチンのプログラムの流れを説明する流れ図である。

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 米国特許第05777914(US, A)

特開平06-061788(JP, A)

特開平03-211910(JP, A)

特開平02-281811(JP, A)

特開平04-049708(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03H 17/00 - 17/08

H03M 3/02