(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년11월10일

(11) 등록번호 10-1567994

(24) 등록일자 2015년11월04일

(51) 국제특허분류(Int. Cl.)

*H01L 29/12* (2006.01) *H01L 29/66* (2006.01)

*H01L 29/68* (2006.01) *H01L 29/778* (2006.01)

(21) 출원번호 10-2013-7011088

(22) 출원일자(국제) 2011년12월08일

심사청구일자 2014년10월31일

(85) 번역문제출일자 2013년04월29일

(65) 공개번호 10-2014-0027904

(43) 공개일자 2014년03월07일

(86) 국제출원번호 PCT/EP2011/072181

(87) 국제공개번호 WO 2012/080076

국제공개일자 2012년06월21일

(30) 우선권주장

12/970,744 2010년12월16일 미국(US)

(56) 선행기술조사문헌

JP4116722 B2

(73) 특허권자

테크니쉐 유니베르시타트 베를린

독일, 10623 베를린, 주니 135, 스트라쎄 테 17.

(72) 발명자

프로페셔 닥터 빌베르크, 디에터

독일 14089 베를린 하크렌데르 베그 28

젤러, 마틴

독일 45145 에센 클라우스탈리슈트라쎄 34

(뒷면에 계속)

(74) 대리인

특허법인에이아이피

전체 청구항 수 : 총 18 항

심사관 : 설관식

(54) 발명의 명칭 변형된 반도체 더블-헤테로구조체 및 양자점들을 포함하는 메모리 디바이스

**(57) 요약**

본 발명의 실시예는 2개의 외부 반도체 층들(120, 125) 사이에 끼인 내부 반도체 층(115)을 갖는 변형된 더블-헤테로구조체(110)를 포함하는 메모리에 관한 것으로, 내부 반도체 층의 격자 상수는 외부 반도체 층들의 격자 상수와 상이하고, 더블-헤테로구조체 내의 결과적인 격자 변형(strain)은 내부 반도체 층 내부에 적어도 하나의 양자점의 형성을 유도하며, 상기 적어도 하나의 양자점은 전하 캐리어들을 그 안에 저장할 수 있고, 격자 변형에 기인하여, 적어도 하나의 양자점은 1.15 eV 이상의 방출 장벽(E<sub>b</sub>)을 가지며, 1000 nm<sup>3</sup> 당 적어도 3개의 에너지 상태들의 에너지 상태 밀도(energy state density)를 제공하고, 상기 모든 적어도 3개의 에너지 상태들(186)은 50 meV 이하의 에너지 밴드(DeltaW<sub>b</sub>) 내에 위치된다.

**대표 도**

(72) 발명자

노보진, 토비아스

독일 13405 베를린 해켈슈트라쎄 1

마렌트, 안드레아스

독일 10965 베를린 피디신슈트라쎄 28

---

## 명세서

### 청구범위

#### 청구항 1

2개의 외부 반도체 층들 사이에 끼인 내부 반도체 층을 갖는 변형된 더블-헤테로구조체(double-heterostructure)를 포함하는 메모리로서,

- 상기 내부 반도체 층의 격자 상수(lattice constant)는 상기 외부 반도체 층들의 격자 상수와 상이하고, 상기 더블-헤테로구조체 내의 결과적인 격자 변형은 상기 내부 반도체 층 내부에 적어도 하나의 양자점(quantum dot)의 형성을 유도하며, 상기 적어도 하나의 양자점은 전하 캐리어(charge carrier)들을 그 안에 저장할 수 있고, 및

- 상기 격자 변형에 기인하여, 상기 적어도 하나의 양자점은 1.15 eV 이상의 방출 장벽(emission barrier)을 가지며,  $1000 \text{ nm}^3$  당 적어도 3개의 에너지 상태들의 에너지 상태 밀도(energy state density)를 제공하고, 모든 상기 적어도 3개의 에너지 상태들은 50 meV 이하의 에너지 밴드(energy band) 내에 위치되는, 메모리.

#### 청구항 2

청구항 1에 있어서,

상기 적어도 3개의 에너지 상태들의 각각은 2개의 전하 캐리어들을 저장할 수 있는, 메모리.

#### 청구항 3

청구항 2에 있어서,

상기 적어도 3개의 에너지 상태들의 각각은 정공(hole)들을 저장하며, 2개의 정공들을 저장할 수 있는, 메모리.

#### 청구항 4

청구항 1에 있어서,

상기 적어도 3개의 에너지 상태들은 정공들을 저장할 수 있으며, 상기 변형된 더블-헤테로구조체가 바이어스되지 않은 경우, 상기 적어도 3개의 에너지 상태들은 페르미-준위(Fermi-level) 위에 활성적으로(energetically) 위치되는, 메모리.

#### 청구항 5

청구항 1에 있어서,

상기 메모리는 적어도 하나의 양자점을 충전 또는 방전하기 위하여 정공들을 수송(transport)할 수 있는 2-차원 정공 가스층(2-dimensional hole gas layer)을 포함하는, 메모리.

#### 청구항 6

청구항 5에 있어서,

반도체 초격자(semiconductor superlattice)가 상기 2-차원 정공 가스층과 상기 적어도 하나의 양자점 사이에 배치되는 메모리.

#### 청구항 7

청구항 6에 있어서,

상기 반도체 초격자는, 각각이 적어도 하나의 에너지 상태를 제공하는, 적어도 2개의 양자 우물(quantum well)들을 포함하는, 메모리.

#### 청구항 8

청구항 7에 있어서,

상기 2개의 양자 우물들의 정공-에너지 상태들은, 상기 변형된 더블-헤테로구조체가 바이어스되지 않은 경우, 페르미-준위 위에 위치되는, 메모리.

### 청구항 9

청구항 7에 있어서,

상기 적어도 2개의 양자 우물들의 상기 에너지 상태들의 활성 위치(energetic position)들은, 변형된 더블-헤테로구조체가 바이어스되지 않은 경우, 서로 상이한, 메모리.

### 청구항 10

청구항 9에 있어서,

상기 적어도 2개의 양자 우물들의 상기 에너지 상태들은, 상기 변형된 더블-헤테로구조체에 외부 바이어스 전압을 인가함으로써, 서로에 대하여 그리고 적어도 하나의 양자점의 상기 에너지 상태들에 대하여 쉬프트(shift)될 수 있는, 메모리.

### 청구항 11

청구항 10에 있어서,

- 소거 전압(erase voltage)을 상기 변형된 더블-헤테로구조체에 인가함에 의해, 공진 터널링(resonance tunneling)에 기초하여 정공들이 상기 반도체 초격자를 통해 상기 적어도 하나의 양자점으로부터 터널링할 수 있도록, 상기 적어도 2개의 양자 우물들의 상기 에너지 상태들이 정렬(align)될 수 있고, 및

- 바이어스되지 않은 상태에서, 상기 적어도 2개의 양자 우물들의 상기 에너지 레벨들이 불일치(mismatch)하며, 정공들의 공진 터널링이 불가능해지는, 메모리.

### 청구항 12

청구항 11에 있어서,

상기 2-차원 정공 가스층은 상기 메모리의 전계효과 트랜지스터(field effect transistor)의 부분이며, 상기 전계효과 트랜지스터의 게이트 전극은 전압이 상기 변형된 더블-헤테로구조체로 인가될 수 있도록 하는, 메모리.

### 청구항 13

청구항 12에 있어서,

중간층(intermediate layer)이 상기 전계효과 트랜지스터의 상기 게이트 전극과 상기 변형된 더블-헤테로구조체 사이에 배치되며, 상기 중간층은 상기 변형된 더블-헤테로구조체의 인접한 상기 외부 반도체 층보다 더 작은 밴드갭(band gap)을 갖는, 메모리.

### 청구항 14

청구항 13에 있어서,

상기 메모리는, 상기 중간층 및 인접한 상기 외부 반도체 층 사이의 계면(interface)에서의 전도 밴드 불연속성(conduction band discontinuity)에 의해 특징화(characterize)되는, 메모리.

### 청구항 15

청구항 13에 있어서,

- 상기 전계효과 트랜지스터의 게이트 접촉(contact)은 오믹 접촉(ohmic contact)이며, 및

- 상기 중간층은 n-도핑되는, 메모리.

### 청구항 16

청구항 13에 있어서,

상기 전계효과 트랜지스터의 게이트 접촉은 쇼트키 접촉(Schottky contact)인, 메모리.

### 청구항 17

청구항 1에 있어서,

상기 내부 반도체 층 및 상기 2개의 외부 반도체 층은 각각 Ga(As, Sb) 및 (Al, Ga)As, 또는 각각 Ga(As, Sb) 및 GaP로 구성되는, 메모리.

### 청구항 18

청구항 1에 있어서,

상기 내부 반도체 층의 상기 양자점들이 규칙적인 어레이(regular array)로 배치되는, 메모리.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 메모리들에 관한 것으로서, 보다 구체적으로 반도체 메모리들에 관한 것이다.

### 배경 기술

[0002] 메모리들의 별개의 유형들은 플래시 메모리의 비휘발성[1] 및 동적 랜덤 액세스 메모리(DRAM)의 성능 및 내구성[2]의 이점을 결합할 것이다. 이러한 메모리 개념들의 거대한 다양성이, FeRAM, MRAM, PCRAM, 등[3]과 같은 상이한 처리방식들을 사용하여 제안되어 왔다. 전하기반(chargebased) 메모리들에 대하여 가장 유망한 옵션들 중 하나가 메모리 유닛들로서 자기-조직화(self-organized) 양자점들(quantum dots : QDs)에 기초하는 것이다. III-V QD 구조체들에 대한 메모리 동작이, 광학적으로[4-6] 또는 전기적으로 제어되는 전하 스토리지(storage)[7-9] 중 하나에 기초하여, 입증되었다.

### 발명의 내용

#### 해결하려는 과제

[0003] 본 발명의 목적은 고속 기입 및 소거 시간 및 높은 내구성과 함께 긴 저장 시간을 제공하는 메모리를 제공하는 것이다.

#### 과제의 해결 수단

[0004] 본 발명의 실시예는 2개의 외부 반도체 층들 사이에 끼인 내부 반도체 층을 갖는 변형된 더블-헤테로구조체(110)를 포함하는 메모리에 관한 것이다. 내부 반도체 층의 격자 상수는 외부 반도체 층들의 격자 상수와 상이하고, 더블-헤테로구조체 내의 결과적인 격자 변형은 내부 반도체 층 내부에 적어도 하나의 양자점의 형성을 유도한다. 상기 적어도 하나의 양자점은 전하 캐리어들을 그 안에 저장할 수 있다. 격자 변형에 기인하여, 적어도 하나의 양자점은 1.15 eV 이상의 방출 장벽(emission barrier)을 가지며,  $1000 \text{ nm}^3$  당 적어도 3개의 에너지 상태들의 에너지 상태 밀도(energy state density)를 제공하고, 모든 상기 적어도 3개의 에너지 상태들(186)은 50 meV 이하의 에너지 벤드(band) 내에 위치된다.

[0005] 바람직하게, 상기 적어도 3개의 에너지 상태들의 각각은 2개의 전하 캐리어들을 저장할 수 있다.

[0006] 상기 적어도 3개의 에너지 상태들의 각각은 바람직하게 정공(hole)들을 저장하며, 2개의 정공들을 저장할 수 있다. 구속된 정공(confined hole)들의 에너지 상태들은 전자들의 에너지 상태들보다 더 가깝게 이격(spaced)되며, 따라서 그들의 에너지 분포(energy distribution)에 관하여 전자들에 비하여 더 높은 캐리어 밀도를 보인다. 이와 같이, 정공들의 에너지 상태들은 전자들의 에너지 상태들보다 단위 체적(unit volume)당 더 많은 캐리어들을 저장할 수 있다. 이진 정보 단위(unit)당 더 많은 수의 저장된 캐리어들은 저장된 정보의 신뢰성을 증가시킨다.

[0007] 바람직한 실시예에 따르면, 상기 적어도 3개의 에너지 상태들은, 변형된 더블-헤테로구조체가 바이어스되지 않

은 경우, 페르미-준위(Fermi-level) 위에 활성적으로(energetically) 위치된다.

[0008] 메모리는 바람직하게 적어도 하나의 양자점을 충전 또는 방전하기 위하여 정공들을 수송할 수 있는 2-차원 정공 가스층(hole gas layer)을 포함한다.

[0009] 더 바람직한 실시예에 따르면, 반도체 초격자(supperlattice)가 상기 2-차원 정공 가스층과 상기 적어도 하나의 양자점 사이에 배치된다.

[0010] 상기 반도체 초격자는, 각각이 적어도 하나의 에너지 상태를 제공하는, 적어도 2개의 양자 우물(quantum well)들을 포함할 수 있다.

[0011] 2개의 양자 우물들의 정공-에너지 상태들은, 변형된 더블-헤테로구조체가 바이어스되지 않은 경우, 페르미-준위 위에 위치될 수 있다.

[0012] 적어도 2개의 양자 우물들의 에너지 상태들의 활성 위치(energetic position)들은, 변형된 더블-헤테로구조체가 바이어스되지 않은 경우, 바람직하게 서로 상이하다.

[0013] 적어도 2개의 양자 우물들의 에너지 상태들은 바람직하게, 변형된 더블-헤테로구조체에 외부 바이어스 전압을 인가함으로써, 서로에 대하여 그리고 적어도 하나의 양자점의 에너지 상태들에 대하여 쉬프트(shift)될 수 있다.

[0014] 소거 전압을 변형된 더블-헤테로구조체에 인가함에 의해, 공진 터널링(resonance tunneling)에 기초하여 정공들이 반도체 초격자를 통해 적어도 하나의 양자점으로부터 터널링 할 수 있도록, 적어도 2개의 양자 우물들의 에너지 상태들이 정렬(align)될 수 있다. 바이어스되지 않은 상태에서, 적어도 2개의 양자 우물들의 에너지 레벨들이 불일치(mismatch)할 수 있으며, 정공들의 공진 터널링이 불가능하게 될 수 있다. 이러한 실시예를 이용하면, 저장 상황(storage situation)으로부터 소거 상황으로 스위칭하기 위하여 매우 작은 소거 전압만이 요구된다. 전기장이 아주 약간만 증가되며, 이는 메모리 셀의 높은 내구성을 가져온다.

[0015] 2-차원 정공 가스층은 메모리의 전계효과 트랜지스터(field effect transistor)의 일부일 수 있으며, 상기 전계효과 트랜지스터의 게이트 전극은 전압이 변형된 더블-헤테로구조체로 인가될 수 있도록 한다.

[0016] 중간층(intermediate layer)이 전계효과 트랜지스터의 게이트 전극과 변형된 더블-헤테로구조체 사이에 배치되며, 상기 중간층은 변형된 더블-헤테로구조체의 인접한 외부 반도체 층보다 더 작은 밴드갭(bandgap)을 갖는다.

[0017] 전도 밴드 불연속성(conduction band discontinuity)은 중간층과 인접한 외부 반도체 층 사이의 계면(interface)에 위치될 수 있다. 이러한 전도 밴드 불연속성은, 변형된 더블-헤테로구조체가 바이어스될 때, 전자들이 변형된 더블-헤테로구조체에 도달하지 못하게 할 수 있다.

[0018] 전계효과 트랜지스터의 게이트 접촉(contact)은 오믹 접촉(ohmic contact)일 수 있으며, 중간층은 n-도핑될 수 있다.

[0019] 대안적으로 전계효과 트랜지스터의 게이트 접촉은 쇼트키 접촉(Schottky contact)일 수 있다.

[0020] 내부 반도체 층 및 2개의 외부 반도체 층은 각기 Ga(As, Sb) 및 (Al, Ga)As, 또는 각기 Ga(As, Sb) 및 GaP로 구성될 수 있다.

[0021] 내부 반도체 층의 양자점들은 어레이(array)로 배치될 수 있다.

### 도면의 간단한 설명

[0022] 본 발명의 이상에서 열거된 이점들 및 다른 이점들이 달성되는 방식이 용이하게 이해될 수 있도록 하기 위하여, 이상에서 간략하게 설명된 본 발명의 보다 구체적인 설명이 특정 실시예들 및 이러한 특정 실시예들에 예시되어 있는 첨부된 도면들을 참조하여 이루어질 것이다. 이러한 도면들이 단지 본 발명의 전형적인 실시예들을 도시하고 있고, 따라서 본 발명의 사상을 제한하는 것으로 간주되지 않아야 한다는 것이 이해되어야 하며, 본 발명이 첨부된 도면을 사용함으로써 추가적인 특정성 및 상세함을 가지고 기술되고 설명될 것이라는 것이 이해되어야 한다.

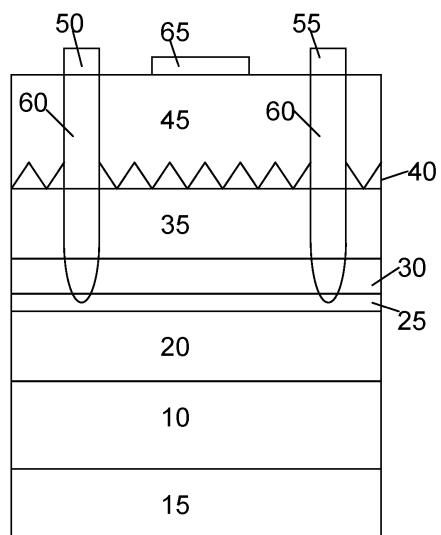

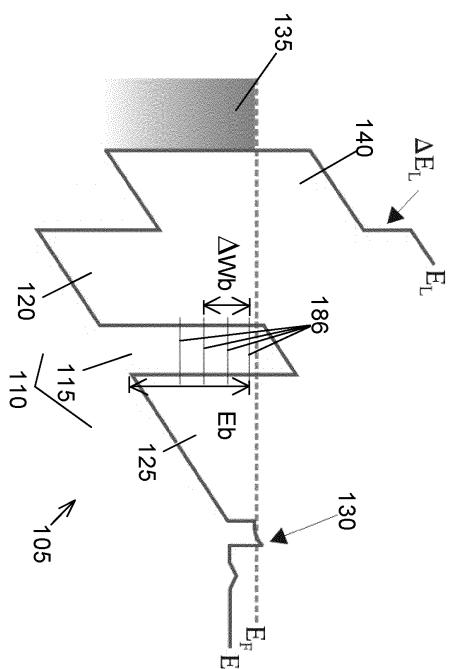

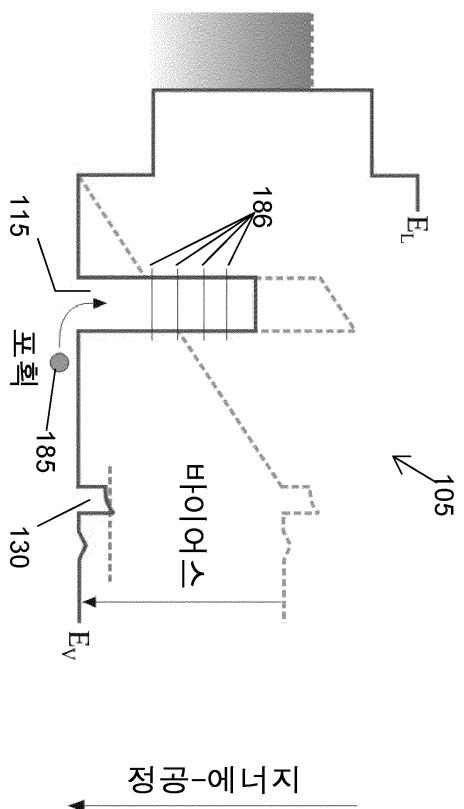

도 1은 본 발명에 따른 메모리의 제 1 실시예를 도시한다,

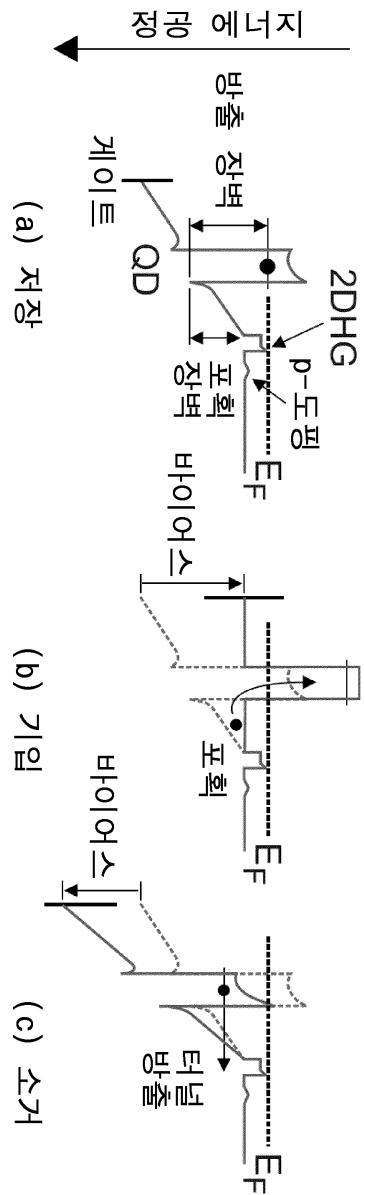

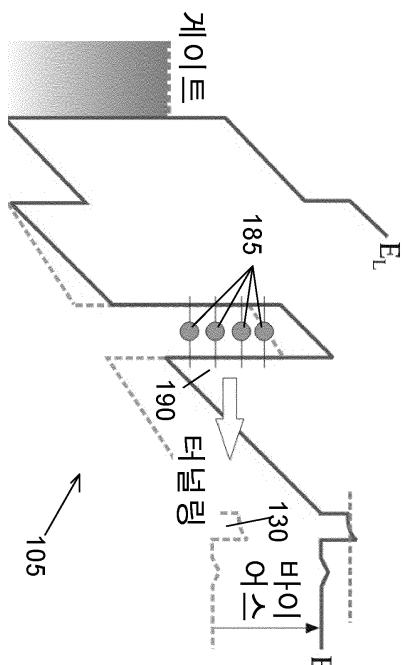

도 2는 도 1의 실시예의 (a) 저장, (b) 기입, (c) 소거 동작들의 개략적인 예시를 도시한다,

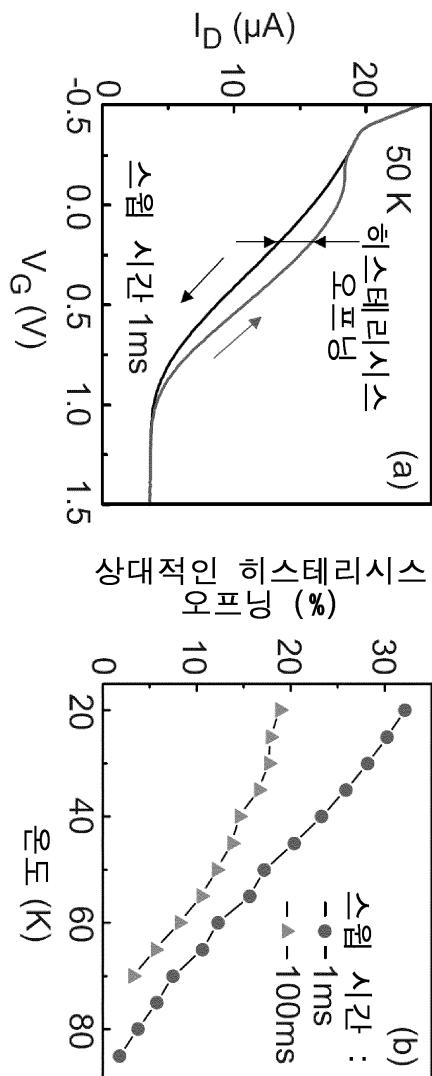

도 3은, 각기 (a) 50 K에서의 히스테리시스(hysteresis), 및 (b) 스윕 시간(sweep time) 1 및 100 ms에 대한 히스테리시스 오프닝(opening)의 온도 상관성(temperature dependence)을 도시한다,

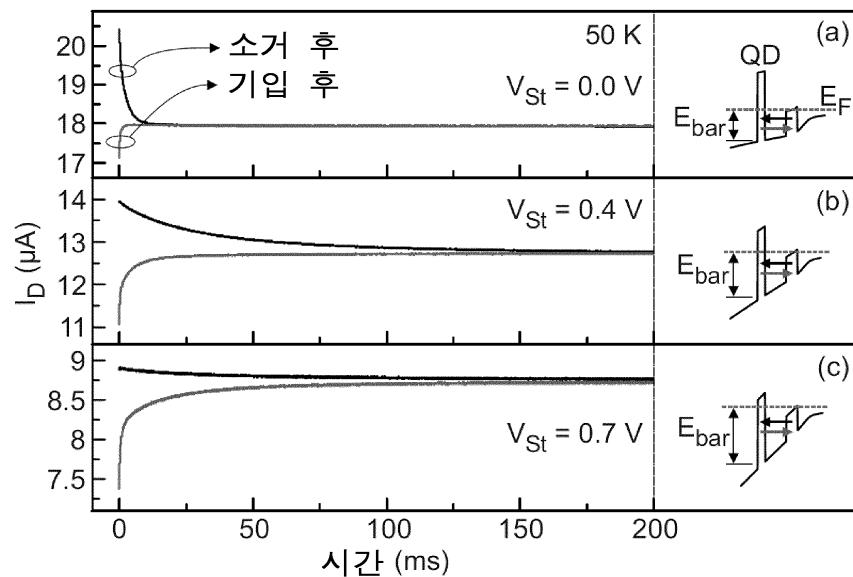

도 4는 50 k에서, (a) 0 V, (b) 0.4 V, 및 (c) 0.7 V의 저장 전압에서의 드레인 전류 트랜션트(transient)들을 도시하며, 여기에서 삽입도(insertion)들은 주어진 전압들에서의 가전자 밴드 프로파일(valence band profile)들을 도시한다,

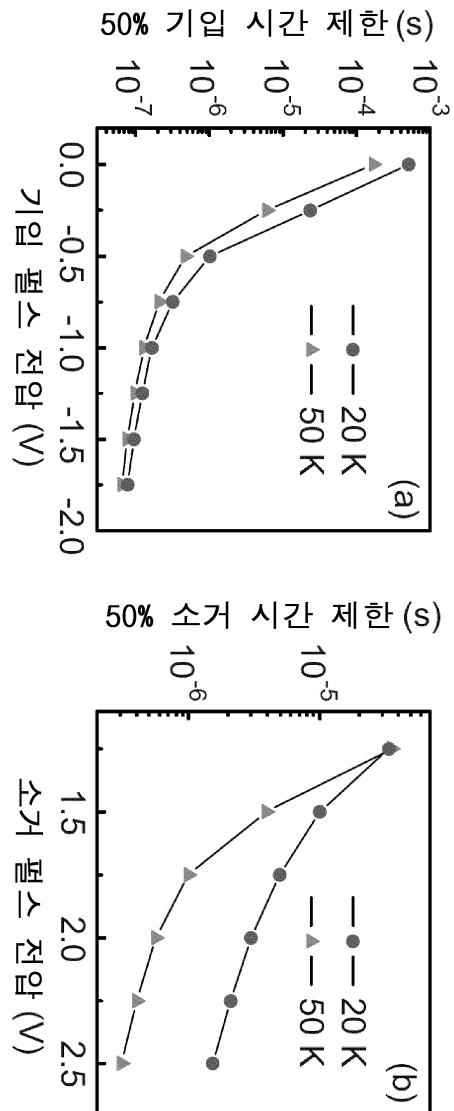

도 5는 웨尔斯 전압에 의존하는 (a) 기입 시간들 및 (b) 소거 시간들을 도시한다,

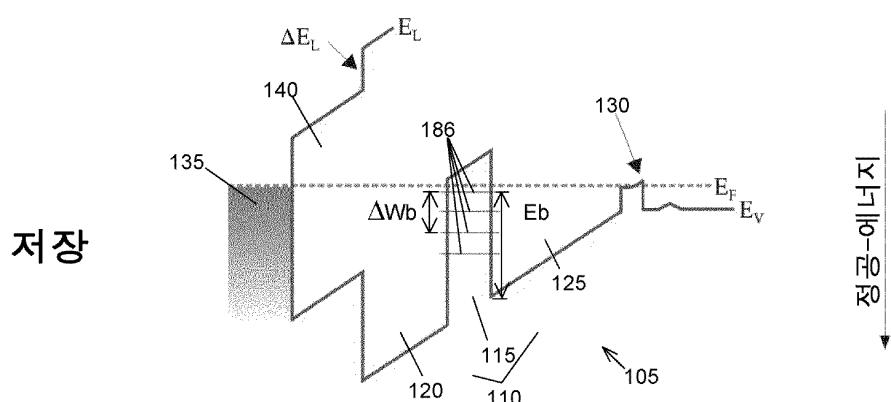

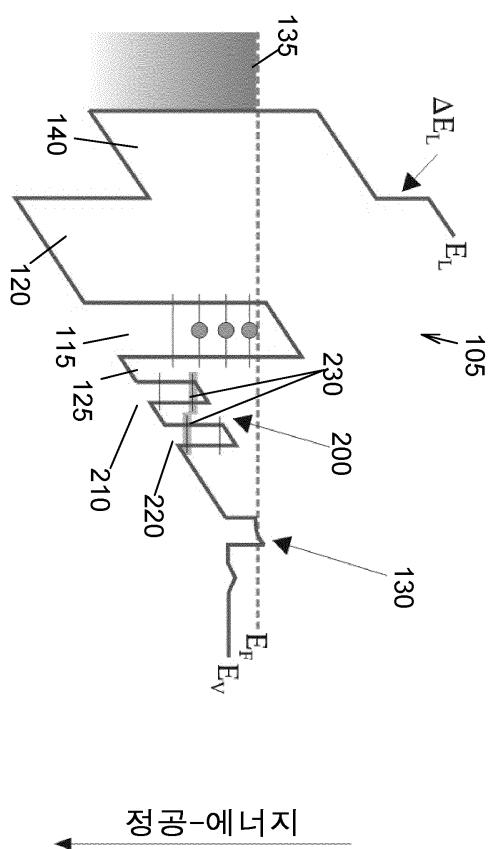

도 6은 바이어스되지 않은 상태의, 본 발명에 따른 메모리의 제 2 실시예를 도시한다,

도 7은 기입 동작 동안의 제 2 실시예를 도시한다,

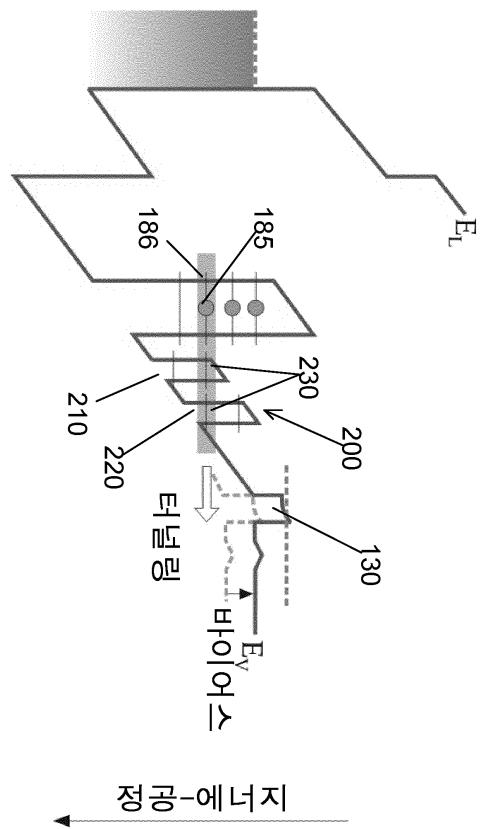

도 8은 소거 동작 동안의 제 2 실시예를 도시한다,

도 9는 바이어스되지 않은 상태의, 본 발명에 따른 메모리의 제 3 실시예를 도시한다,

도 10은 소거 동작 동안의 제 3 실시예를 도시한다, 및

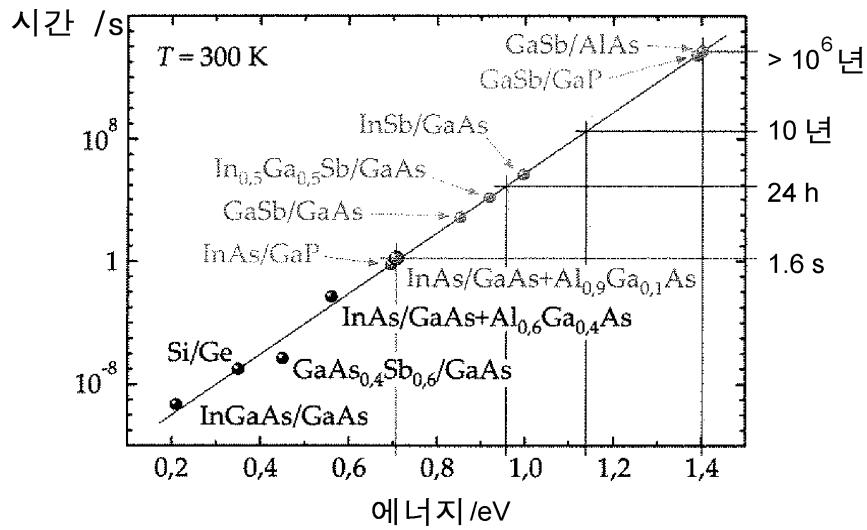

도 11은 다양한 재료 시스템들에 대한 탈성가능한 저장 시간들을 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0023] 본 발명의 바람직한 실시예들이 첨부된 도면들을 참조하여 최적으로 이해될 것이며, 동일하거나 또는 비슷한 부분들은 도면들에 걸쳐 동일한 참조부호들에 의해 지시된다. 본 명세서에 전반적으로 설명된 바와 같이, 본 발명이 넓은 범위에 걸쳐 변화할 수 있다는 것이 용이하게 이해될 것이다. 따라서, 본 발명의 예시적인 실시예들에 대한 다음의 상세한 설명은, 청구된 바와 같이, 본 발명의 범위를 제한하고자 하는 의도가 아니며, 단지 본 발명의 바람직한 실시예들을 대표할 뿐이다.

[0024] 이하에서 설명되는 실시예들은 정공들의 저장을 가능하게 하는 III-V 양자점들에 기초할 수 있다. 정공 저장은 확장성(scability) 및 저장 시간과 관련하여 상당한 이점들을 제공한다. QD 내의 구속된(confined) 정공들의 에너지 레벨들은 그들의 더 큰 유효 질량(effective mass)에 기인하여 전자들의 에너지 레벨들보다 더 가깝게 이격된다. 따라서, 전자들보다 적어도 10배(one order of magnitude) 많은 정공들이 주어진 부피(volume) 내에 저장될 수 있다. 또한, 정공-구속 유형-II 시스템(hole-confining type-II system)들(예를 들어, GaSb/AlGaAs QD들)은, 비휘발성 메모리에 대하여 기본 전제조건(prerequisite)인, 실온에서의 10년 이상의 저장 시간을 초래하는 큰 정공 국소화 에너지(hole localization energy)들을 제공한다.

[0025] 국소화 에너지들 및 그에 따른 QD의 바닥 상태(ground state)의 구속된 정공들의 방출 장벽(emission barrier)들이 상이한 III-V QD들에 대하여도 11에서 요약된다[10]. 열적 활성화 방출의 공통 레이트 방정식(common rate equation)에 의해 예측되는 바와 같이, 저장 시간은 국소화 에너지에 지수적으로 의존하는 것을 나타낸다. 약 50 meV의 국소화 에너지의 증가에 대하여 저장 시간은 10배만큼 증가한다. Ga(As, Sb)/(Al, Ga)As 및 Ga(As, Sb)/GaP에 기초한 메모리들이 10년 이상의 저장 시간에 도달하는 것이 확인될 수 있다.

[0026] 본 발명의 예시적인 제 1 실시예는 전자들 대신 정공들을 충전 캐리어들로서 사용하는 InAs/GaAs QD에 관한 것이다. 모니터링을 위하여, 공통적으로 사용되는 전자 채널들이 QD 층 아래에 임베디드(embedded) 2D 정공 가스(2D hole gas : 2DHG)에 의해 대체된다. 저장, 기입, 및 소거 시간들의 정적(static) 및 시간-분해 측정(time-resolved measurement)들이 정공-기반 QD-메모리 개념의 실현 가능성(feasibility)을 입증한다.

[0027] 도 1의 예시적인 실시예는 2DHG에 근접하여 단일 InAs/GaAs QD 층을 갖는 양자-우물 변조 도핑된(quantum-well modulation doped) 전계-효과 트랜지스터로 구성된다. 층 구조체의 개략적인 단면이 도 1에 도시되어 있다. 먼저 1 μm 두께의 도핑되지 않은 GaAs 베퍼층(10)이 도핑되지 않은 GaAs 기판(15) 상에 성장된다. 2DGH는 40 nm의 p-도핑된( $p=2 \times 10^{18} \text{ cm}^{-3}$ ) GaAs 층(20), 7 nm 두께의 도핑되지 않은 GaAs 스페이서(spacer) 층(25), 및 8 nm 두께의  $\text{In}_{0.25}\text{Ga}_{0.75}\text{As}$  양자 우물(30)로 형성된다. 계속해서, 20 nm의 GaAs 층(35)이 증착되었으며, 단일 InAs 층(40)(아주 적게(nominally) ~1.8 ML)이 뒤이어 졌다. 마지막으로, 구조체는 180 nm의 도핑되지 않은 GaAs 캡(cap)(45)에 의해 완성된다.

[0028] 혼태로구조체는 화학적 습식 에칭(chemical wet etching)(도 1(b)를 보라)을 사용하여  $310 \times 460 \mu\text{m}^2$ 의 활성 영역(active area)을 가지고 홀 바(Hall bar)들 내로 프로세싱된다.

[0029] 소스 및 드레인 영역들(50, 55)은 2DHG 아래에 오믹 접촉들을 형성하기 위하여 400 °C에서 3분간 어닐링(anneal)되는 Ni/Zn/Au 합금을 사용하여 금속화(metallize)된다. 게이트(65)는 쇼트키 접촉(Schottky contact)으로서 Ni/Au에 의해 형성된다. 게이트 전극(70)에서의 홀 측정들은 77 k에서 각기  $8 \times 10^{11} \text{ cm}^{-2}$  및  $4350 \text{ cm}^2/\text{Vs}$ 의 전하 캐리어 밀도 및 이동성(mobility)을 초래한다.

[0030] 도 2는 3개의 메모리 동작들: 저장, 기입, 및 소거에 대한 구조체의 가전자 밴드(valence band)를 개략적으로 도시한다. 저장 위치(도 2(a))에서, QD들 내의 홀들의 결합 전위(binding potential)는 논리적인 "1"을 저장하기 위하여 요구되는 방출 장벽을 나타낸다. 논리적인 "0"(비어있는 QD들로서 정의되는)을 저장하기 위하여 포획(capture) 장벽이 필요하며, 이는 쇼트키 접촉의 밴드-밴딩(band-bending)에 의해 형성된다.

[0031] 2개의 논리적 상태들 모두에 대한 저장 시간은 QD들의 방출 및 포획 프로세스들에 의해 제한된다. 구조체 내에서, 방출 및 포획 장벽들에 걸친 열 지원형 터널링(thermally assisted tunneling)이 방전 및 충전 프로세스들을 시작한다. 방출 및 포획 레이트(rate)들은 장벽 높이(즉, 국소화 에너지 및 포획 장벽 높이), 온도, 및 전기장에 의존한다. 논리적인 "1"을 기입하기 위하여 네거티브(negative) 바이어스가 게이트에 인가된다. 이는 밴드-밴딩에 의해 형성된 포획 장벽을 완전히 제거하며, 나노초에 이르는 고속 기입 시간이 실현될 수 있다. 따라서, QD-메모리 개념은, 기입 동작 동안 거의 0(zero)으로 감소될 수 있는, 큰 장벽 높이를 사용함으로써, 플레이시의  $\text{SiO}_2$  장벽들의 단점들을 해결한다. 기입 시간은 DRAM들의 기입 시간과 유사하며, 심지어 더 짧아지는 것도 가능하다.

[0032] 정보를 소거하기 위하여(도 2(c)), 터널 방출이 발생하도록 하기 위하여 포지티브(positive) 바이어스를 인가함에 의해, QD들의 위치에서의 전기장이 증가된다. 저장된 정보의 판독(read-out)은 QD 층 아래의 2DHG를 통해 이루어진다. QD들 내에 저장된 캐리어들은 2DHG 내의 이동성 및 전하 밀도를 감소시키고, 이는 QD들이 점유될(occupied) 때 2DHG의 더 낮은 전도도(conductance)를 가져온다. 2DHG의 전도도 상의 QD들 내에 저장된 정공들의 영향을 조사하기 위하여, 드레인 전류  $I_D$  대 게이트 전압  $V_G$ 가 100 mV의 고정된 드레인-소스 전압으로 어둠 속에서 측정되었다.

[0033] 도 3(a)는 50 K의 온도에서 측정된 히스테리시스(hysteresis)를 도시한다. 측정 사이클은 10 ms 길이의 충전 펄스( $V_G = -1 \text{ V}$ )로 시작하며, 이는 QD 상태들을 페르미 전위 밑으로 쉬프트하고, 이들을 2DHG로부터의 정공들로 충전한다(도 2(b)를 보라).

[0034] 이제 게이트 전압이 1.5 V로 스윕될 때, 드레인 전류는 2DHG가 약 1.1 V에서 핀치 오프(pinch off)될 때까지 감소한다. 다운 스윕(down sweep) 동안, 스윕 시간이 QD들 내의 정공 저장 시간보다 짧은 경우, QD들은 점유된 상태를 유지한다.

[0035]  $V_G = 1.5 \text{ V}$ 에서, QD 상태들은 페르미 준위보다 훨씬 위에 있으며(도 2(c)를 보라), 터널 방출은 QD들을 방전한다. 게이트 전압이 -1 V로 다시 스윕될 때, 뚜렷한 히스테리시스 오프닝(distinct hysteresis opening)을 초래하는 더 큰 전류가 관찰된다. 히스테리시스는 다운 스윕 동안, QD들 내에 저장된 정공들의 2DHG의 전도도 상의 영향으로부터 유래한다.

[0036] 충전된 QD들은 쿨롱 산란 중심(Coulomb scattering center)들로서 동작하며, 2DHG의 이동성을 감소시킨다. 또한, 가우스 법칙을 사용하면, QD들 내의 정공들의 수송(transfer)이 2DHG 내의 캐리어 밀도의 감소를 초래한다는 것이 예측된다. 더 낮아진 전하 캐리어 밀도 및 감소된 이동성 둘 다가 다운 스윕 동안 전도도를 감소시키며, 업 스윕(up sweep)에 비하여 더 낮은 전류 트레이스(current trace)를 초래한다. 업 스윕에 대하여 최대 히스테리시스 오프닝이 2개의 상이한 스윕 시간들에 대한 온도의 함수로써 도 3(b)에 도시된다. 1 ms의 스윕 시간을 사용하면, 히스테리시스 오프닝은 20 K에서 32%로부터 85 K에서 거의 0으로 떨어진다. 하강(descent)은 증가하는 온도와 함께 QD들의 감소되는 전하 캐리어 저장 시간에 있어 그것의 기원(origin)을 가지며, 즉, 더 높은 온도들에서 더 많은 정공들이 다운 스윕 동안 방출된다.

[0037] 참고문헌 [7]에서 딥 레벨(deep level)들에 기인한 고온 메모리 효과(high temperature memory effect)가 상이한 InAs QD-구조체에 대하여 보고된다. 여기에서, 이러한 고온 메모리 효과들의 결여는 딥 레벨들이 아니라 사실 QD들이 메모리 유닛들로서 동작한다는 것을 증명한다. 이러한 결론은, 1 ms의 스윕 시간에 대하여 85 K에서의 히스테리시스의 소멸에 따라서, QD 정공 바닥 상태에 대하여 90 k에서 5의 열 방출 시정수(time constant)가 초래된, 딥 레벨 트랜션트 분광학(spectroscopy)에 의한 유사한 InAs/GaAs QD들로부터의 정공 방출에 대한 이전

의 조사들에 의해 확인된다. 더 느려진 다운 스윕 동안 QD들 내에 저장된 더 많은 정공들이 방출되기 때문에, 100 ms의 스윕 시간은 1 ms에 비하여 히스테리시스 오프닝을 더 감소시킨다.

[0038] 증가된 최대 히스테리시스 오프닝이 더 큰 QD 밀도들 및/또는 복수의 QD 층들을 사용하여 예측된다. QD-메모리의 프로토타입(prototype)의 메모리 동작이, 최초에 점유되었거나 또는 빈(empty) QDs를 이용하여, 상이한 저장 전압들  $V_{st}$ 에서의 드레인 전류의 시간-분해 측정들에 의해 연구된다. QD들은, 각각 -0.8 또는 2 V의 게이트 전압을 인가함으로써 충전되거나 또는 방전된다.

[0039] 논리적인 "1" 또는 "0"의 이러한 초기화 후, 게이트 전압이 저장 전압으로 급격히 변화되며, 드레인 전류가 시간의 함수로써 측정된다.

[0040] 도 4는 3개의 상이한 저장 전압들(0, 0.4, 및 0.7 V)에 대한 50 K에서의 트랜션트들을 도시한다. 상단의 트랜션트는 최초에 빈 QD들 내로의 정공 포획을 나타내며, 이는 2DHG의 전도도의 감소를 초래하고, 따라서, 드레인 전류의 감소를 초래한다. 하단의 트랜션트는 완전히 점유된 QD들의 정공 방출을 나타내며, 따라서, 드레인 전류가 평형 상태(equilibrium state)까지 증가한다. 0 V로부터 0.4 V 및 추가적으로 0.7 V까지의 저장 전압의 변화는 복수의 효과들(도 4(a)-4(c))을 초래한다; 모든 트랜션트들의 시정수들이 증가하고, 포획 트랜션트의 크기(amplitude)가 감소되며, 및 방출 트랜션트의 크기가 증가된다. 이러한 효과들은, 포지티브 저장 전압을 구조체에 인가할 때, 포획 및 방출 프로세스들의 변화들에 의해 설명될 수 있다.

[0041] 도 4(a)-4(c)의 오른편에 3개의 저장 전압들에 대한 가전자 밴드 프로파일들이 도시된다. 트랜션트들의 크기들은 수송된 정공들의 양을 나타내며, 페르미 준위 아래의(포획에 대하여) 그리고 페르미 준위 위의(방출에 대하여) 레벨들의 수와 상관(correlate)된다. 더 큰 포지티브 저장 전압은 페르미 준위를 QD 바닥 상태를 향해 쉬프트하며, 따라서, 더 많은 정공들이 방출되고, 더 적은 정공들이 포획되며, 따라서 크기들이 변화한다.

[0042] 시정수들의 연장(prolongation)은 또한, 이것이 증가된 포획 및 방출 장벽 높이(도 4의  $E_{bar}$ )를 초래함에 따라, 페르미 준위 쉬프트와 관련된다.

[0043] 메모리 구조체의 기입 및 소거 시간들이 측정된다. 기입 및 소거 시간들을 결정하기 위하여, 시정수들의 연장된 기간에 걸쳐 QD들로부터의 방출 또는 QD들 내로의 포획을 연구할 수 있도록 하는 방법이 사용된다. 연속적으로 10 ns까지 감소되는 펄스 폭들로 기입/소거 펄스들을 인가한 후, 0.4 V의 저장 위치에서의 히스테리시스 오프닝이 측정된다. QD들의 임의의 충전/방전에 대하여 펄스 폭이 너무 짧을 때, 히스테리시스 오프닝이 소멸된다. 기입/소거 시간들은 펄스 폭으로서 정의되며, 여기에서 히스테리시스 오프닝은 최대 값의 50%로 떨어진다.

[0044] 도 5(a)는 20 및 50 K에서의 기입 펄스 전압에 의존하는 기입 시간을 도시한다. 더 많은 네거티브 기입 펄스는 기입 중 포획 장벽의 감소를 초래하며, 따라서, 기입 시간이 지수적으로 감소한다. **[0.5V]**보다 큰 기입 펄스들에 대하여, 기입 시간이 포화하기(saturate) 시작하며, -1.75 V의 기입 펄스에 대하여 80 ns에서 최소에 도달한다.

[0045] 이러한 포화는, 우리의 본 디바이스들의 RC 로우 패스(low pass)의 약 2 MHz의 기생 차단 주파수(parasitic cutoff frequency)에서 현재 그것의 기원을 갖는다. 더 큰 기생 차단 주파수들을 갖는 더 작은 디바이스들에 대하여 더 빠른 기입 시간들이 예상된다.

[0046] 소거 시간들이 도 5(b)에 도시된다. 2.5 V의 소거 펄스에 대하여 50 K에서 350 ns의 최소 소거 시간이 획득된다. 기입 및 소거 시간들의 온도 의존성은 다시 고온들에서의 증가된 열적 포획 및 방출 레이트들을 반영한다.

[0047] 요약하면, 예시적인 제 1 실시예는 전하 캐리어 저장을 위하여 InAs/GaAs QD들을 사용하는 정공 기반 메모리 디바이스에 관한 것이다. QD들의 충전 및 방전이 게이트 전압에 의해 명확하게 제어된다. 저장된 정보의 판독은, 32%까지 이르는 상대적인 히스테리시스 오프닝을 갖는, 2DHG를 사용한다. 80 ns까지의 기입 시간들 - 단지 전형적인 DRAM에 대한 것보다 8배 더 큰 인자만으로- 및 350 ns의 소거 시간들 - 전형적인 플래시 메모리들에 대한 것보다 10000배 빠른 -이 입증되었다. 이러한 결과들은 QD들이 메모리로서 동작한다는 가정을 지지한다.

[0048] 본 발명의 예시적인 제 2 실시예가 도 6-8을 참조하여 보다 구체적으로 설명될 것이다.

[0049] 도 6은 2개의 외부 반도체 층들(120 및 125) 사이에 끼인(sandwiched), Ga(As, sb)로 구성될 수 있는 내부 반도체 층(115)을 갖는 변형된 더블-헤테로구조체(110)를 포함하는 메모리(105)를 도시한다. 외부 반도체 층들

(120 및 125)은 (Al, Ga)As로 구성될 수 있다.

[0050] 내부 반도체 층(115)의 격자 상수가 외부 반도체 층들(120 및 125)의 격자 상수들과 상이하며, 그 결과 격자 변형(lattice strain)이 발생된다. 더블-헤테로구조체(110) 내의 결과적인 격자 변형은 내부 반도체 층 내에 적어도 하나의 양자점의 형성을 유도하며, 상기 적어도 하나의 양자점(quantum dot)은 그 안에 전하 캐리어들을 저장할 수 있는 적어도 3개의 에너지 상태들을 제공한다.

[0051] 격자 변형에 기인하여, 적어도 하나의 양자점은 1.15 eV 이상의 방출 장벽(emission barrier : Eb)을 갖고,  $1000 \text{ nm}^3$  당 적어도 3개의 에너지 상태들의 에너지 상태 밀도를 제공한다. 적어도 3개의 에너지 상태를 모두는 50 meV 이하의 에너지 벤드( $\Delta W_b$ ) 내에 위치된다. 에너지 벤드( $\Delta W_b$ )는, 상기 적어도 3개의 에너지 상태들의 각각이 2개의 정공들을 저장할 수 있도록, 제공된다.

[0052] 도 6은 바이어스되지 않은 상태의 메모리(105)를 도시한다. 정공들의 적어도 3개의 에너지 레벨들이 활성적으로(energetically) 페르미 준위(Ef)보다 위에 있다는 것이 확인될 수 있다.

[0053] 또한, 도 6은 적어도 하나의 양자점의 충전 또는 방전을 위하여 정공들을 수송할 수 있는 2-차원 정공 가스층(hole gas layer)(130)을 도시한다. 2-차원 정공 가스층(130)은 메모리의 전계효과 트랜지스터의 부분이다. 전계효과 트랜지스터의 게이트 전극(135)은 전압이 변형된 더블-헤테로-구조체(110)로 인가될 수 있도록 한다.

[0054] 도 6의 메모리는 전계효과 트랜지스터의 게이트 전극(135)과 변형된 더블-헤테로구조체(110) 사이에 배치되는 중간층(intermediate layer)(140)을 더 포함한다. 중간층(120)은 변형된 더블-헤테로구조체(110)의 인접한 외부 반도체 층(120)보다 더 작은 벤드 갭(band gap)을 갖는다. 더 작은 벤드 갭은 중간층(140)과 인접한 외부 반도체 층(120) 사이의 계면(interface)에서 전도 벤드 불연속성(conduction band discontinuity)( $\Delta E_L$ )을 제공한다. 전도 벤드 불연속성( $\Delta E_L$ )은, 포지티브 바이어스 전압이 인가되는 경우, 게이트(135)로부터 발원하는(Originating) 전자들이 외부 반도체 층(120) 내로 들어가지 못하도록 한다. 따라서, 전도 벤드 불연속성( $\Delta E_L$ )은 내부 반도체 층(115) 내의 전자들 및 정공들의 재결합을 방지한다.

[0055] 전계효과 트랜지스터의 게이트 접촉은 바람직하게 오믹 접촉(ohmic contact)이며, 중간층은 바람직하게 n-도핑된다.

[0056] 도 7은 기입-전압을 변형된 더블-헤테로구조체에 인가한 후의 도 6의 메모리(105)를 도시한다. 정공들(185)이 2-차원 정공 가스층(130)을 떠날 수 있고, 내부 반도체 층(115) 내에 위치된 양자점의 에너지 상태들(186) 내로 드롭(drop)할 수 있다는 것이 확인될 수 있다.

[0057] 도 8은 소거-전압을 변형된 더블-헤테로구조체에 인가한 후의 메모리(105)를 도시한다. 양자점의 에너지 상태들 내에 저장된 정공들(185)이 에너지 장벽(190)을 통해 터널링 할 수 있고, 2차원 정공 가스층(130)에 도달할 수 있다는 것이 확인될 수 있다.

[0058] 본 발명의 예시적인 제 3 실시예가 도 9 내지 10을 참조하여 더 상세하게 설명될 것이다.

[0059] 도 9는 2개의 외부 반도체 층들(120 및 125) 사이에 끼인 내부 반도체 층(115)을 갖는 변형된 더블-헤테로구조체(110)를 포함하는 메모리(105)를 도시한다. 중간층(140)은 전계효과 트랜지스터의 게이트 전극(135)과 변형된 더블-헤테로구조체(110) 사이에 배치된다. 또한, 메모리(105)는 내부 반도체 층(115) 내에 위치된 적어도 하나의 양자점의 충전 또는 방전을 위하여 정공들을 수송할 수 있는 2-차원 정공 가스층(130)을 포함한다. 이러한 범위에서, 예시적인 제 3 실시예는 도 6-8에 대하여 설명된 예시적인 제 2 실시예에 대응한다.

[0060] 제 2 실시예에 더하여, 제 3 실시예는 2차원 정공 가스층(130)과 외부 반도체 층(125) 사이에 배치된 반도체 초격자(semiconductor superlattice)(200)를 포함한다. 반도체 초격자(200)는 2개의 양자 우물(quantum well)들(210 및 220)을 포함한다. 각각의 양자 우물(210 및 220)은 적어도 하나의 에너지 상태(230)를 제공한다.

[0061] 도 9에 있어, 변형된 더블-헤테로구조체(110)는 바이어스되지 않는다. 양자 우물들(210 및 220)의 에너지 상태들(230)의 활성 위치(energetic position)들이 서로 상이하다. 에너지 상태들(230)의 불일치(mismatch)에 기인하여, 양자점 내의 에너지 상태들에 트랩(trap)된 정공들이 반도체 초격자(200)를 통해 터널링 할 수 없으며, 따라서 2-차원 정공 가스층(130)에 도달할 수 없다.

[0062] 도 10은 외부 소거 바이어스 전압을 변형된 더블-헤테로구조체에 인가한 후의 제 3 실시예를 도시한다. 바이어스 전압에 기인하여, 양자 우물들(210 및 220)의 에너지 상태들이 서로에 대하여, 그리고 적어도 하나의 양자점

의 에너지 상태들(186)에 대하여 쇠프트된다. 이러한 정렬(alignment)은 공진 터널링(resonant tunneling)에 기초하여 정공들(185)이 반도체 초격자(200)를 통해 터널링하는 것을 가능하게 한다. 정공들은 2차원 정공 가스 층(130)에 도달할 수 있으며, 적어도 하나의 양자점의 에너지 상태들은 비워진다.

[0063] 제 1 및 제 2 실시예에 있어, 소거 프로세서는 전체적인 방출 장벽을 통한 정공 터널링에 기초한다. 따라서, 소거 시간이 방출 장벽의 높이에 의존한다. 1.15 eV 이상의 방출 장벽에 대하여, MV/cm의 범위의 높은 전기장들이 고속 소거 시간들에 도달하기 위하여 요구된다[11]. 격자 내에 결함들이 발생될 수 있음에 따라, 이러한 높은 전기장들은 메모리 셀의 높은 전력 소모를 초래하며, 낮은 내구성을 초래한다. 제 3 실시예는 이러한 문제들을 해결한다. 제 3 실시예에 있어, 소거 프로세스는 초격자를 통한 공진 터널링에 의해 이루어진다. 공진 정공 터널링을 가능하도록 하는 양자 우물의 에너지 상태들을 정렬하기 위해 작은 전압만이 요구된다. 결과적으로 전기장이 아주 약간 증가된다. 그래서, 2가지 문제들- 높은 전력 소모 및 낮은 내구성-이 모두 해결된다. 빠른 소거 시간 및 높은 내구성과 함께 긴 저장 시간을 갖는 메모리가 실현 가능하다.

[0064] 도 11은 다양한 재료 시스템들에 대한 달성 가능한 저장 시간들을 도시한다. Ga(As, Sb)/(Al, Ga)As 및 Ga(As, Sb)/GaP에 기초한 메모리들이 10년 이상의 저장 시간에 도달할 수 있음이 확인될 수 있다.

#### [0065] 참조 문헌

- [0066] [1] P. Pavan, R. Bez, P. Olivo, and E. Zanoni, Proc. IEEE 85, 1248 (1997).

- [0067] [2] R. Waser, Nanoelectronics and Information Technology\_Wiley, Weinheim, 2003.

- [0068] [3] G. W. Burr, B. N. Kurdi, J. C. Scott, C. H. Lam, K. Gopalakrishnan, and R. S. Shenoy, IBM J. Res. Dev. 52, 449 (2008).

- [0069] [4] J. J. Finley, M. Skalitz, M. Arzberger, A. Zrenner, G. Boehm, and G. Abstreiter, Appl. Phys. Lett. 73, 2618\_1998\_.

- [0070] [5] K. Koike, K. Saitoh, S. Li, S. Sasa, M. Inoue, and M. Yano, Appl. Phys. Lett. 76, 1464 (2000).

- [0071] [6] H. Pettersson, L. Baath, N. Carlson, W. Seifert, and L. Samuelson, Appl. Phys. Lett. 79, 78 (2001).

- [0072] [7] C. Balocco, A. M. Song, and M. Missous, Appl. Phys. Lett. 85, 5911 (2004).

- [0073] [8] D. Nataraj, N. Ooike, J. Motohisa, and T. Fukui, Appl. Phys. Lett. 87, 193103 (2005).

- [0074] [9] C. R. Mueller, L. Worschech, J. Heinrich, S. Hoefling, and A. Forchel, Appl. Phys. Lett. 93, 063502 (2008).

- [0075] [10] A. Marent, M. Geller, A. Schliwa, D. Feise, K. Poetschke, and D. Bimberg, N. Akcay and N. Oencan, Appl. Phys. Lett. 91, 242109 (2007).

- [0076] [11] T. Nowozin, A. Marent, M. Geller, N. Akcay, N. Oencan, D. Bimberg, Appl. Phys. Lett. 94, 4, 042108 (2009)

#### **부호의 설명**

- [0077] 10 : 벼파총

- 15 : 기판

- 20 : 층

- 25 : 스페이서 층

- 30 : 양자 우물

- 35 : 층

- 40 : QD 층

- 45 : 캡

50 : 소스

55 : 드레인

60 : 오믹 접촉

65 : 게이트

105 : 메모리

110 : 변형된 더블-헤테로구조체

115 : 내부 반도체 층

120 : 외부 반도체 층

125 : 외부 반도체 층

130 : 2-차원 정공 가스층

135 : 게이트 전극

140 : 중간층

185 : 정공

186 : 에너지 상태

190 : 에너지 장벽

200 : 반도체 초격자

210 : 양자 우물

220 : 양자 우물

230 : 에너지 상태

$\Delta E_L$  : 전도 대역 불연속성

$E_F$  : 페르미 에너지

$E_V$  : 가전자 밴드

$E_L$  : 전도 밴드

$\Delta W_b$  : 에너지 밴드

도면

도면1

## 도면2

도면3

## 도면4

## 도면5

도면6

## 저장

도면7

## 기 입

정공-에너지

도면8

소거

정공-에너지

도면9

## 저장

도면10

## 소거

도면11