**Erfindungspatent für die Schweiz und Liechtenstein**

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

⑫ PATENTSCHRIFT A5

⑯1 Gesuchsnummer: 408/87

⑯3 Inhaber:

ANT Nachrichtentechnik GmbH, Backnang (DE)

⑯2 Anmeldungsdatum: 05.02.1987

⑯2 Erfinder:

Müller, Heiko (-Cajar), Grosserlach (DE)

⑯4 Patent erteilt: 29.12.1989

⑯5 Vertreter:

Kirker & Cie SA, Genève

⑯6 Patentschrift

veröffentlicht: 29.12.1989

⑯7 Verfahren und Schaltungsanordnung zur Ueberwachung eines Prozessorsystems.

⑯7 Die Erfinbung bezieht sich auf ein Verfahren zur Überwachung eines Prozessorsystems auf einen undefinierten Betriebszustand, wobei der ausser Normalbetrieb geratene Prozessor durch einen Rücksetzimpuls (RES) wieder in einen ordnungsgemässen Betriebszustand zurückgesetzt wird, wobei durch den Prozessor periodisch eine Überwachungsschaltung (watchdog) aufgerufen wird, durch welche die Erzeugung des Rücksetzimpulses dann angelassen wird, wenn der Aufruf durch den Prozessor nicht innerhalb einer vorgegebenen Zeit erfolgt, und ist dadurch gekennzeichnet, dass die laut Prozessorprogramm unbenutzten Adressen als verbotener Bereich deklariert werden, dass überwacht wird, ob sich die vom Prozessor angesprungenen Adressen im verbotenen Bereich befinden, und dass die Erzeugung eines Rücksetzimpulses dann angelassen wird, wenn vom Prozessor zu dem verbotenen Adressbereich zugegriffen wird.

### PATENTANSPRÜCHE

1. Verfahren zur Überwachung eines Prozessorsystems auf einen undefinierten Betriebszustand, wobei der ausser Normalbetrieb geratene Prozessor durch einen Rücksetzimpuls (RES) wieder in einem ordnungsgemässen Betriebszustand zurückgesetzt wird, wobei durch den Prozessor periodisch eine Überwachungsschaltung (watchdog) aufgerufen wird, durch welche die Erzeugung des Rücksetzimpulses dann angelassen wird, wenn der Aufruf durch den Prozessor nicht innerhalb einer vorgegebenen Zeit erfolgt, dadurch gekennzeichnet, dass die laut-Prozessorprogramm unbenutzten Adressen als verbotener Bereich (CSV) deklariert werden, dass überwacht wird, ob sich die vom Prozessor ( $\mu$ P) angesprungenen Adressen im verbotenen Bereich befinden, und dass die Erzeugung eines Rücksetzimpulses (RES) dann angelassen wird, wenn vom Prozessor ( $\mu$ P) zu dem verbotenen Adressbereich (CSV) zugegriffen wird.

2. Verfahren nach Anspruch 1, dadurch gekennzeichnet, dass unbenutzte Adressen im Speicher und/oder anderen peripheren Bausteinen verwendet werden.

3. Verfahren nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass als verbotene Adressen oder verbotene Adressbereiche Internadressen freier Ein- oder Ausgangskanäle, unbenutzte Wählleitungen zu integrierte Schaltungen und/oder freie Adressleitungen verwendet werden.

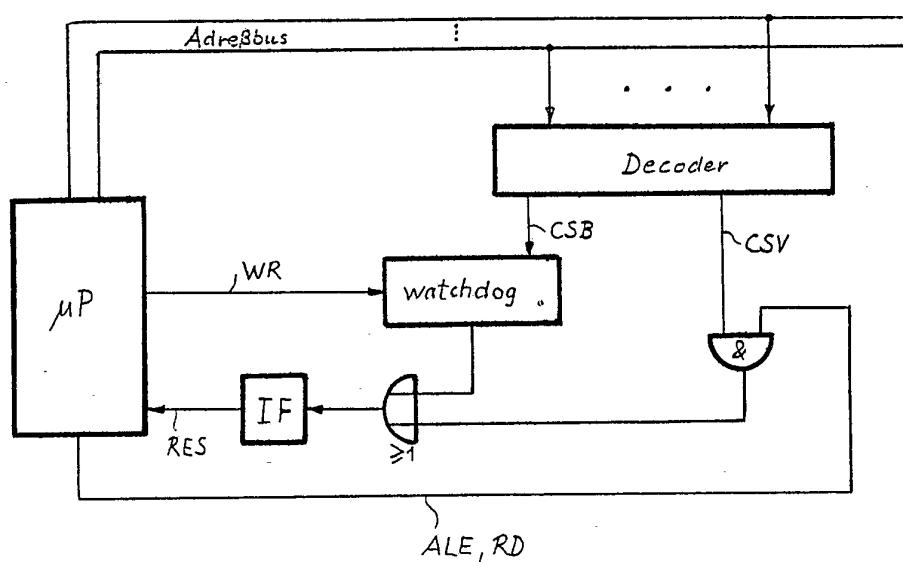

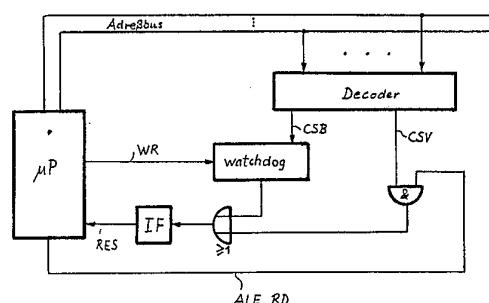

4. Schaltungsanordnung zur Durchführung des Verfahrens nach Anspruch 1, dadurch gekennzeichnet, dass ein UND-Glied (&) vorgesehen ist, dem als erstes Eingangssignal ein Prozessorsignal, das stabile Adressen anzeigt (ALE, RD, WR), und dem als zweites Eingangssignal das Ausgangssignal (CSV) eines Adressdecoders, welches den Zugriff auf unbenutzte Adressräume anzeigt, zugeführt wird und dass ein ODER-Glied ( $\geq 1$ ) vorgesehen ist, dem als Eingangssignale das Ausgangssignal des UND-Gliedes und das Ausgangssignal der Überwachungsschaltung (watchdog) zugeführt werden und dessen Ausgangssignal zur Erzeugung des Rücksetzimpulses (RES) benutzt wird.

### BESCHREIBUNG

Die Erfindung bezieht sich auf ein Verfahren zur Überwachung eines Prozessorsystems gemäss Oberbegriff des Anspruches 1.

Solche Verfahren sind bekannt.

Durch Umwelteinflüsse, beispielsweise durch elektromagnetische Einflüsse, Spannungseinbrüche, Spikes (Spannungsspitzen) auf Adress- oder Datenbus, können Prozessoren, insbesondere Mikroprozessoren, welche an exponierten Orten wie z.B. Orten mit hohen Energiedichten, in Schaltungen untergebracht sind, in undefinierte Betriebszustände gebracht werden, Betriebszustände, welche die Weiterführung des Programms nicht mehr gestatten und aus denen die (Mikro-)Prozessoren aus eigener Kraft nicht mehr herausfinden können. Deshalb werden üblicherweise Prozessoren mit einer Überwachungsschaltung (watchdog) ausgestattet, die den Prozessor überwacht und ihn, falls er in einen solchen undefinierten Betriebszustand fällt, wieder geordnet zurücksetzt.

Die bisher bekannten Systeme verwenden für die Überwachung eine Schaltung, die in bestimmten Abständen vom Prozessor getriggert werden muss. Bleibt diese Triggerung aus, so erhält der Prozessor einen Rücksetzimpuls (reset), der ihn wieder in einen definierten Ausgangs-Betriebszustand zurückführt. Üblicherweise benötigen insbesondere Mikroprozessorsysteme dafür einen längeren Rücksetzimpuls, der beispielsweise durch einen Mono-Flop oder durch einen Zähler realisiert wird.

Soll mit hoher Wahrscheinlichkeit ausgeschlossen werden,

dass diese Überwachungsschaltung unbeabsichtigt getriggert wird, so ist ein hoher Decodierungsaufwand für Adress- und Datenbus erforderlich, wenn ein bestimmtes Triggerwort definiert wurde.

- 5 Der vorliegenden Erfindung lag deshalb die Aufgabe zu grunde, die Prozessorüberwachung der eingangs genannten Art zu verbessern.

Diese Aufgabe wurde gelöst mit den kennzeichnenden Merkmalen des Anspruches 1.

- 10 Die abhängigen Ansprüche kennzeichnen optimale Ausgestaltungen des Verfahrens.

Die Erfindung weist die Vorteile einer erhöhten Störsicherheit von Prozessorsystemen und wesentlich geringeren Schaltungsaufwand gegenüber herkömmlichen Systemen auf.

- 15 Es folgt nun die Beschreibung der Erfindung anhand der Figur.

Die Figur zeigt ein Ausführungsbeispiel der Schaltungsanordnung zur Durchführung des erfindungsgemässen Verfahrens. Es ist links der Mikroprozessor  $\mu$ P mit seinem Adressbus erkennbar. Ferner ist eine herkömmliche Überwachungsschaltung Watchdog erkennbar, welche beispielsweise ein Mono-Flop oder ein Zähler ist. Diese Überwachungsschaltung wird über einen Decoder angesteuert, wenn auf eine ganz bestimmte definierte Busadresse CSB zugegriffen wird. Ein zusätzliches direktes Prozessorsignal, z.B. ein Schreibsignal WR, lässt die so angesteuerte Überwachungsschaltung in ihren Ausgangszustand übergehen. Innerhalb einer gewissen Zeit wird so bei normalem Prozessor-Betriebszustand die Überwachungsschaltung zurückgestellt. Erfolgt eine solche Rückstellung jedoch nicht, so wird über ein ODER-Glied  $\geq 1$  ein Impulsformer IF angesteuert, welcher beispielsweise ein Mono-Flop ist und das Rücksetzsignal RES für den Mikroprozessor erzeugt. Über den genannten Decoder ist außerdem ein UND-Glied & ansteuerbar, wenn auf unbenutzte, verbotene Adressen CSV, also Adressen, welche aufgrund des Prozessorprogramms nicht angesprochen werden, durch den Prozessor zugegriffen wird.

Als zweites Eingangssignal wird dem UND-Glied ein Prozessorsignal zugeführt, das stabile Adressen anzeigt, beispielsweise ALE (Adress latch enable) oder ein Lesesignal RD oder auch ein Schreibsignal WR. Wenn nun durch den genannten Decoder eine unbenutzte Adresse decodiert wird und zusätzlich das zuletzt genannte Prozessorsignal ansteht, so wird durch das UND-Glied & über das weiter obengenannte ODER-Glied  $\geq 1$  ebenfalls die Impulsformerstufe IF zur Erzeugung eines Rücksetzimpulses für den Prozessor angesteuert.

In manchen Mikroprozessor-Systemen stehen die obengenannten Signale nur als «aktiv low», also invertiert, zur Verfügung:  $\overline{WR}$ ,  $\overline{RD}$ ,  $\overline{ALE}$ ,  $\overline{CSB}$ ,  $\overline{CSV}$ ,  $\overline{RES}$ . In diesen Fällen sind die beiden Eingänge des UND-Gliedes & zusätzlich mit Inverterstufen zu versehen.

Der Vorteil der Schaltungsanordnung ist, dass der hohe Decodierungsaufwand für den Watchdog entfällt. Dieser muss nur noch ansprechen, wenn der Prozessor keine Busaktivitäten mehr entfaltet. In den anderen Fällen greift ein undefiniert laufender Prozessor nach den Gesetzen der Statistik auch auf unbenutzte Adressen zu, welche sozusagen als Fallen wirken und die Überwachung ansprechen lassen.

Als weitere Adressfallen können beispielsweise auch eine unbenutzte Chip-Select-Leitung, verknüpft mit einem der oben erwähnten Prozessorsignale, die stabile Adressen anzeigen, oder freie Ports benutzt werden, welche ebenso wie der Ausgang des Watchdogs über das genannte ODER-Gatter auf die Rücksetzimpulsstufe geführt werden. Um einen möglichst breiten Adressbereich als Falle einsetzen zu können, ist es vorteilhaft, eine Adressleitung für die Überwachung freizuhalten.