(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2015-534331

(P2015-534331A)

(43) 公表日 平成27年11月26日(2015.11.26)

(51) Int.Cl.

|            |           |

|------------|-----------|

| HO3H 11/04 | (2006.01) |

| HO3H 11/12 | (2006.01) |

| GO5B 13/02 | (2006.01) |

F 1

|      |       |

|------|-------|

| HO3H | 11/04 |

| HO3H | 11/12 |

| GO5B | 13/02 |

テーマコード(参考)

|   |       |

|---|-------|

| H | 5H004 |

| C | 5J098 |

| S |       |

審査請求 未請求 予備審査請求 未請求 (全 60 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2015-531158 (P2015-531158) |

| (86) (22) 出願日 | 平成25年9月4日 (2013.9.4)         |

| (85) 翻訳文提出日   | 平成27年5月1日 (2015.5.1)         |

| (86) 國際出願番号   | PCT/US2013/057996            |

| (87) 國際公開番号   | W02014/039517                |

| (87) 國際公開日    | 平成26年3月13日 (2014.3.13)       |

| (31) 優先権主張番号  | 61/779,390                   |

| (32) 優先日      | 平成25年3月13日 (2013.3.13)       |

| (33) 優先権主張国   | 米国(US)                       |

| (31) 優先権主張番号  | 61/697,049                   |

| (32) 優先日      | 平成24年9月5日 (2012.9.5)         |

| (33) 優先権主張国   | 米国(US)                       |

|          |                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------|

| (71) 出願人 | 510243344<br>ニューランズ・インコーポレーテッド<br>NEWLANS, INC.<br>アメリカ合衆国, マサチューセッツ州 01720, アクトン, スイート 215,<br>ナゴッグ パーク 43 |

| (74) 代理人 | 100087941<br>弁理士 杉本 修司                                                                                      |

| (74) 代理人 | 100086793<br>弁理士 野田 雅士                                                                                      |

| (74) 代理人 | 100112829<br>弁理士 堀 健郎                                                                                       |

| (74) 代理人 | 100144082<br>弁理士 林田 久美子                                                                                     |

最終頁に続く

(54) 【発明の名称】バイカッドのキャリブレーション

## (57) 【要約】

【課題】任意の所望のインパルス応答つまり伝達関数を指定可能な精度で実現するバイカッド回路のチューニング方法を提供する。

【解決手段】ロスパッドを、所定の周波数において目標のゲイン値を生成するようにチューニングする過程と、第1の積分器の位相を、所定の周波数において目標の位相にチューニングする過程と、第2の積分器の位相を、所定の周波数において目標の位相にチューニングする過程と、第1の積分器のゲインを、所定の周波数において目標のゲイン値にチューニングする過程と、第2の積分器のゲインを、所定の周波数において目標のゲイン値にチューニングする過程とを含む。

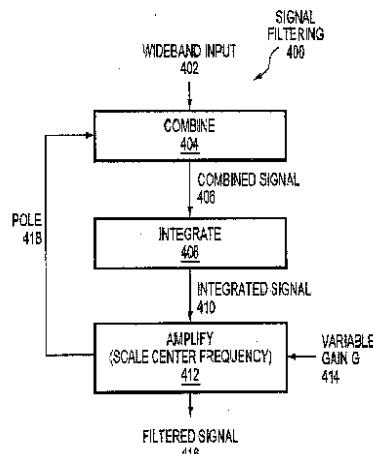

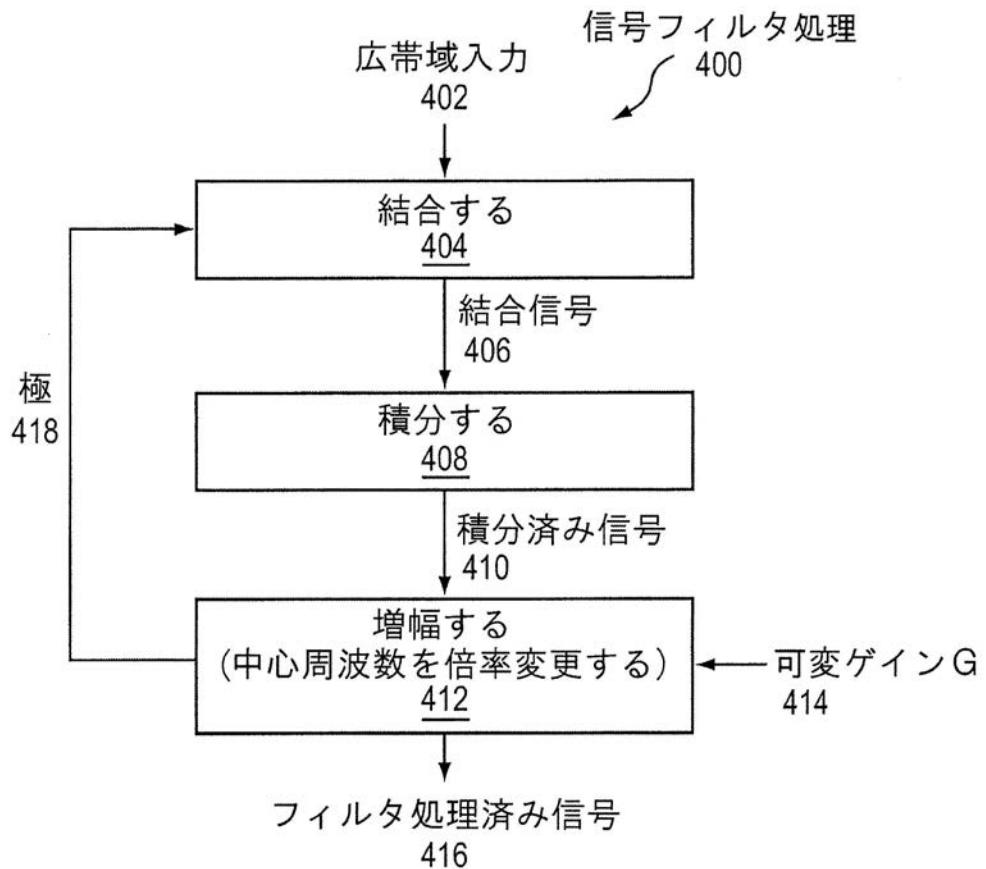

【選択図】図4

FIG. 4

## 【特許請求の範囲】

## 【請求項 1】

バイカッド回路のフィルタをチューニングする方法であって、

ロスパッドを、所定の周波数において目標のゲイン値を生成するようにチューニングする過程と、

第1の積分器の位相を、前記所定の周波数において目標の位相にチューニングする過程と、

第2の積分器の位相を、前記所定の周波数において前記目標の位相にチューニングする過程と、

前記第1の積分器のゲインを、前記所定の周波数において前記目標のゲイン値にチューニングする過程と、

前記第2の積分器のゲインを、前記所定の周波数において前記目標のゲイン値にチューニングする過程と、

を含む、チューニング方法。

## 【請求項 2】

請求項1に記載のチューニング方法において、さらに、

前記所定の周波数での前記目標のゲイン値を決定する過程、

を含む、チューニング方法。

## 【請求項 3】

請求項1に記載のチューニング方法において、前記ロスパッドをチューニングする過程が、当該ロスパッドの減衰値を調節することを含む、チューニング方法。

## 【請求項 4】

請求項1に記載のチューニング方法において、前記第1の積分器の位相をチューニングする過程が、当該第1の積分器の位相を制御する、当該第1の積分器の入力の位相値を調節することを含む、チューニング方法。

## 【請求項 5】

請求項1に記載のチューニング方法において、前記第1の積分器のゲインをチューニングする過程が、当該第1の積分器のゲインを制御する、当該第1の積分器の粗ゲイン値を調節すること、および、当該第1の積分器のゲインを制御する、当該第1の積分器の微ゲイン値を調節することを含む、チューニング方法。

## 【請求項 6】

請求項1に記載のチューニング方法において、前記第2の積分器の位相をチューニングする過程が、当該第2の積分器の位相を制御する、当該第2の積分器の入力の位相値を調節することを含む、チューニング方法。

## 【請求項 7】

請求項1に記載のチューニング方法において、前記第2の積分器のゲインをチューニングする過程が、当該第2の積分器のゲインを制御する、当該第2の積分器の粗ゲイン値を調節すること、および、当該第2の積分器のゲインを制御する、当該第2の積分器の微ゲイン値を調節することを含む、チューニング方法。

## 【請求項 8】

請求項1に記載のチューニング方法において、前記バイカッド回路が、ノッチフィルタとして動作するようにチューニングされる、チューニング方法。

## 【請求項 9】

請求項1に記載のチューニング方法において、前記バイカッド回路が、オールパスフィルタとして動作するようにチューニングされる、チューニング方法。

## 【発明の詳細な説明】

## 【関連出願】

## 【0001】

本願は、2012年9月5日付出願の米国仮特許出願第61/697,049号および2013年3月13日付出願の米国仮特許出願第61/779,390号の利益を主張する。これらの米国仮特許出願の全教

10

20

30

40

50

示内容は、参照をもって本明細書に取り入れたものとする。

【背景技術】

【0002】

信号帯域幅の増大およびデータレートの増加は、広帯域信号に伴う課題を解決するための新たな信号処理技術の開発に拍車を掛けた。信号帯域幅の増大により、異機種環境での超広帯域（UWB）技術ベースのアクティブ型無線周波数RF識別（RFID）も含め、新しい様々なアプリケーションが可能になった。また、信号帯域幅の増大は測距精度の向上につながるので、広帯域技術は、レーダ、画像処理およびその他の用途にとって特に魅力的な技術である。

【0003】

しかし、残念なことに、クロック速度、スイッチングおよび熱損失の根本的なスケーリング限界、ならびに障害回復の困難性から、デジタル論理は広帯域信号処理に向いていない。例えば、今日のDSP（デジタル信号処理）技術では、高精細度TV、ソフトウェア無線、コグニティブ無線、4G携帯サービス、ホワイトスペース、UWBベースのサービス、リアルタイムのGHz/THzの医用画像処理などの最先端のアプリケーションに必要な広帯域信号を処理できない。また、速度の向上および帯域幅処理能力の向上が所望されている以外にも、電力消費を抑えることが、数多くの信号処理アプリケーションにおいて多大な魅力および有用性を有する。例えば、モバイル機器では、その電力消費を抑えることが極めて重要視されている。これは、高速DSPは、携帯電話およびPDA（携帯情報端末）の電池寿命を大きく短縮するからである。

10

20

30

【0004】

広帯域アプリケーションでは、ナイキストレートが数Gsp（ギガサンプル/秒）範囲なので、比較的単純な信号処理しか実施できず、多くの場合、複雑なパイプライン処理やパラレル処理のアーキテクチャが必要となる。CMOSベースのデジタル信号処理構造の限界がもはやムーアの法則に従って伸びていないことを踏まえると、将来的にはDSP技術は、広帯域アプリケーションで要求される能力に恐らく到達しないであろう。事実、ディープサブミクロンCMOSのゲート幅は分子単位であり、これはトランジスタのサイズ（およびスイッチング速度）が根本的な限界に近付いていることを示唆している。換言すれば、トランジスタのサイズに反比例するトランジスタのスイッチング速度の現時点以上の高速化は不可能と考えられるため、DSP技術の帯域幅処理能力に向上の余地がない。

【0005】

一方、アナログ論理にも限界がある。アナログ回路を構成する各ブロックは、互いに完全に独立していないため、アナログ論理のブロックを1つでも変更したい場合、同じ回路内のその他のブロックを全て変更しなければならないこともある。また、プロセス技術の極めて高速な進歩により、あるアプリケーションに特化したデザインは、製造に移行する前に既に時代遅れとなる場合もある。さらに、アナログ回路は、完全に再構成できるものでも、また完全にプログラマブルではない。

【発明の概要】

【0006】

本発明の実施形態には、状態変数フィルタをチューニングする（調整する）方法が含まれる。そのような状態変数フィルタの例として、当該フィルタ内の積分器の出力に接続された可変ゲインブロックによって中心周波数をチューニングすることのできる状態変数フィルタが挙げられる。信号に対して複数の1次および2次の状態変数フィルタが並列に作用し、これらの出力を組み合わせてフィルタ処理済み出力を生成するようにしてよい。これらのフィルタは、アプリケーションに応じて、通過させたい信号又は除去したい信号をチューニングすることができる。そのようなアプリケーションの例として、アジャイルなフィルタリング（agile filtering）、スペクトル解析、干渉検出・除去、等化、中間周波数の直接伝達、および単側帯波変調・復調が挙げられるが、必ずしもこれらに限定されない。

40

【0007】

50

例示的な一実施形態として、バイカッド回路のフィルタ（状態変数フィルタ）をチューニングする方法は、ロスパッド（loss pad）を、所定の周波数において目標のゲイン値を生成するようにチューニングする過程を含む。第1の積分器の位相が、前記所定の周波数において目標の位相にチューニングされる。次に、第2の積分器の位相が、前記所定の周波数において前記目標の位相にチューニングされる。前記第1の積分器のゲインが、前記所定の周波数において目標のゲイン値にチューニングされる。最後に、前記第2の積分器のゲインが、前記所定の周波数において前記目標のゲイン値にチューニングされる。

【0008】

さらなる実施形態では、前記所定の周波数での前記目標のゲインが決定される。前記ロスパッドをチューニングする過程は、当該ロスパッドの減衰値を調節することを含んでもよい。前記第1の積分器の位相をチューニングする過程は、当該第1の積分器の位相を制御する、当該第1の積分器のゲインをチューニングする過程は、当該第1の積分器のゲインを制御する、当該第1の積分器の粗ゲイン値を調節すること、および、当該第1の積分器のゲインを制御する、当該第1の積分器の微ゲイン値を調節することを含んでもよい。前記第2の積分器の位相をチューニングする過程は、当該第2の積分器の位相を制御する、当該第2の積分器の入力の位相値を調節することを含んでもよい。前記第2の積分器のゲインをチューニングする過程は、当該第2の積分器のゲインを制御する、当該第2の積分器の粗ゲイン値を調節すること、および、当該第2の積分器のゲインを制御する、当該第2の積分器の微ゲイン値を調節することを含んでもよい。

10

20

30

40

【0009】

前述の内容は、添付の図面に示す本発明の例示的な実施形態についての以下の詳細な説明から明らかになる。なお、異なる図をとおして、同一の符号は同一の構成 / 構成要素を指すものとする。図面は必ずしも縮尺どおりではなく、本発明の例示的な実施形態を示すことに重点を置いている。

【図面の簡単な説明】

【0010】

【図1】1次の状態変数フィルタを示すブロック図である。

【図2A】2次の状態変数フィルタの制御正準形（control canonical form）を示すブロック図である。

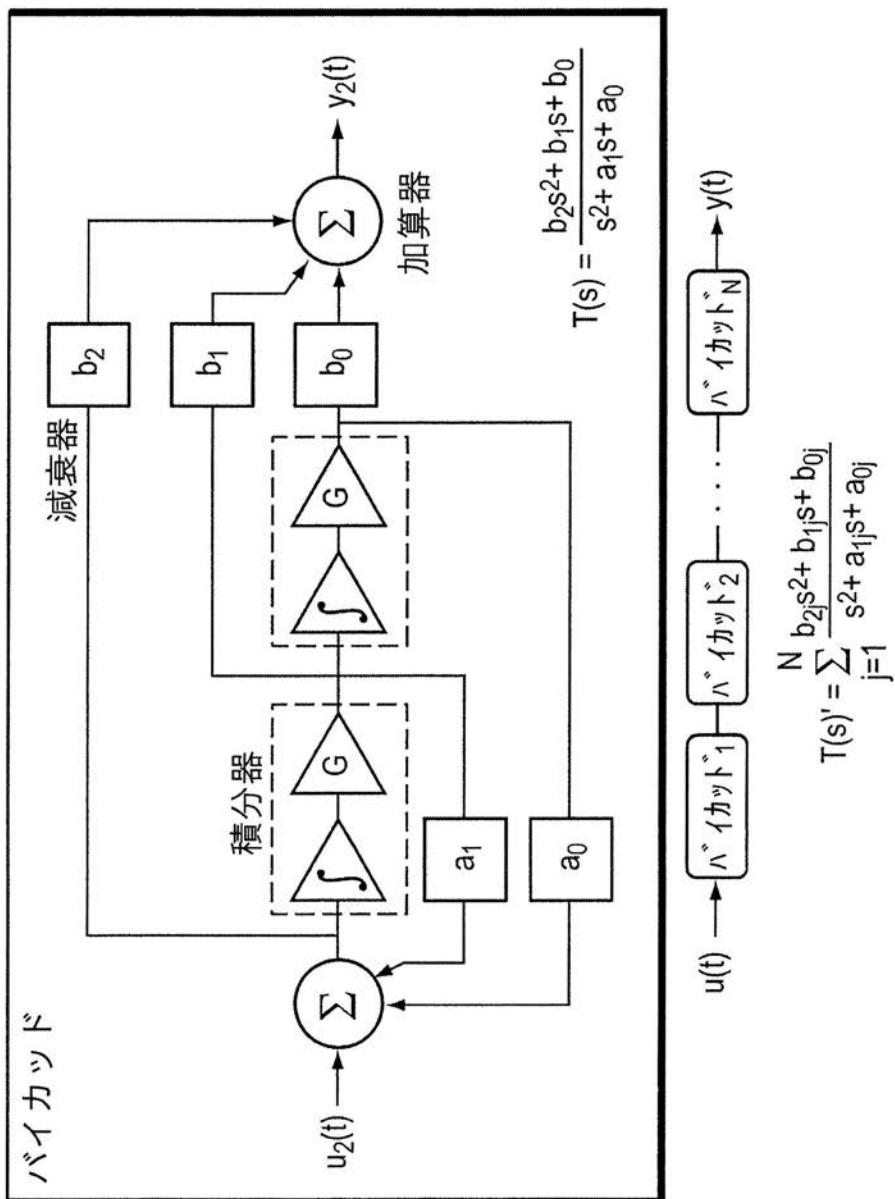

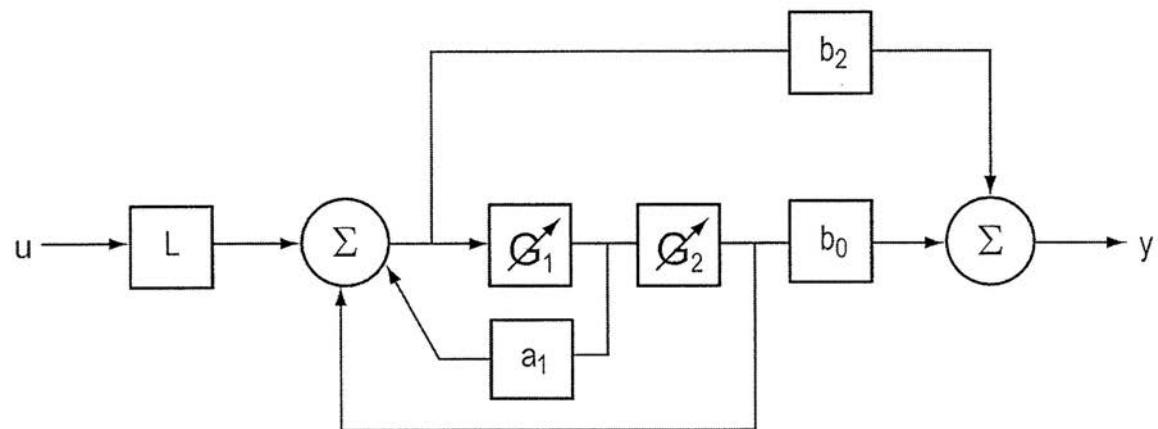

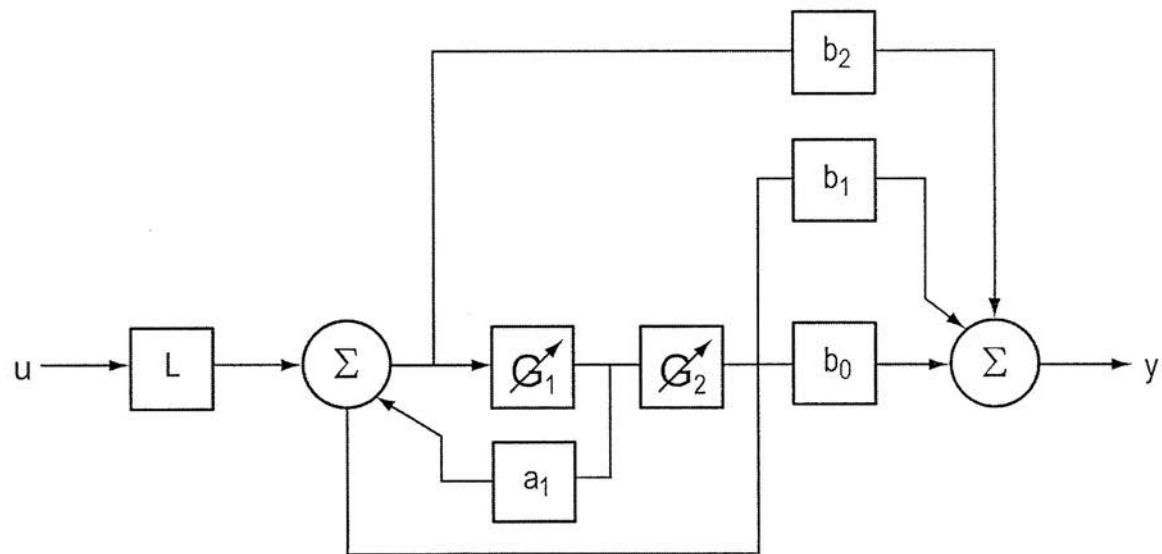

【図2B】本発明の実施形態を適用可能なバイカッド回路の構成を示すブロック図である。

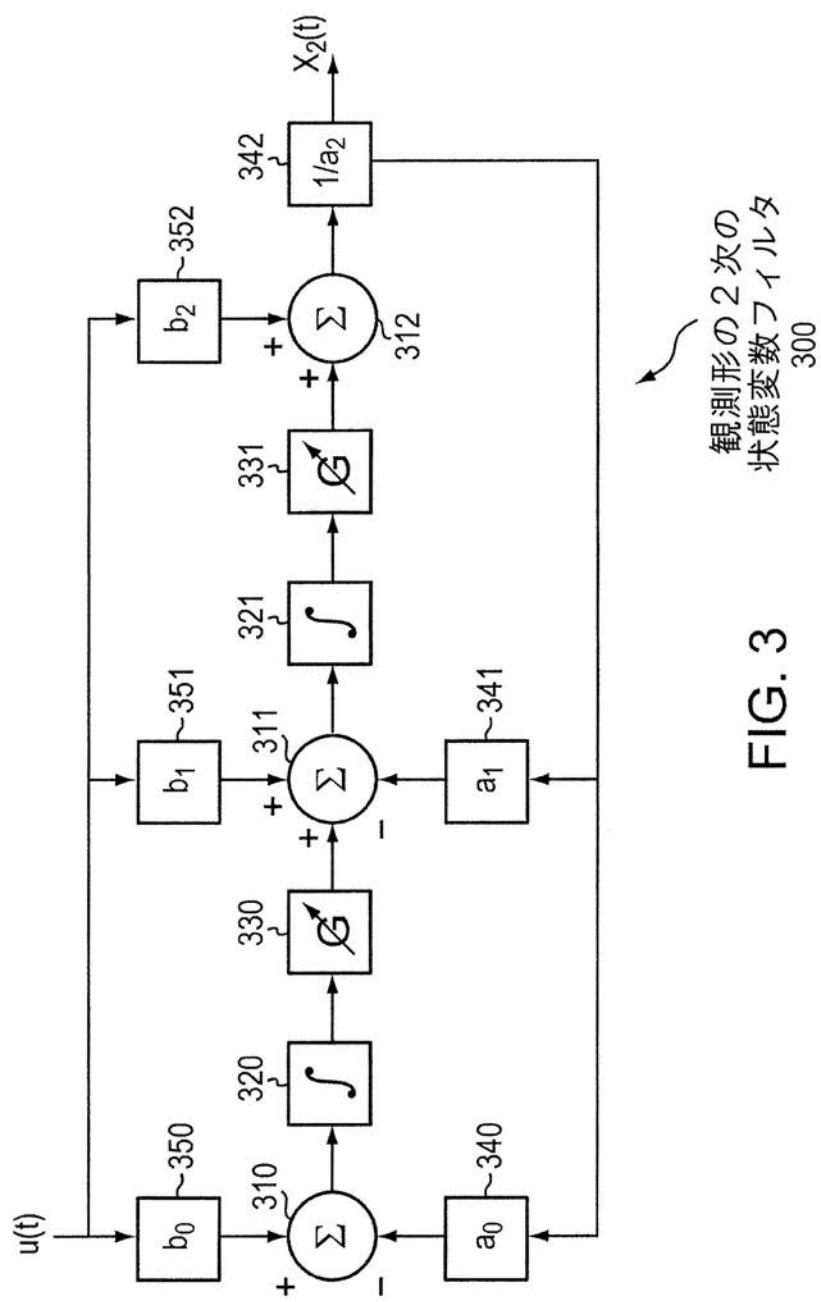

【図3】2次の状態変数フィルタの観測正準形（observer canonical form）を示すブロック図である。

【図4】本発明の原理に基づく信号フィルタ処理のフロー図である。

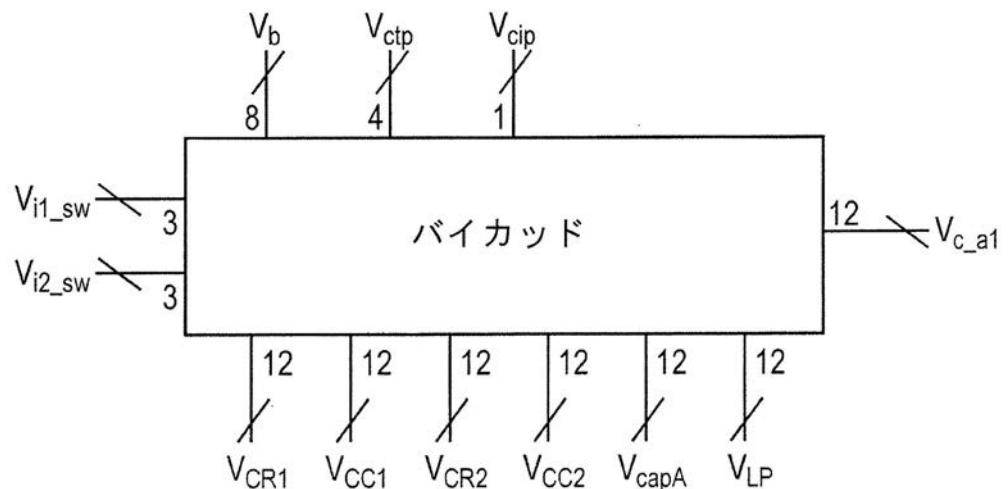

【図5A】状態変数フィルタの信号インターフェースを示すブロック図である。

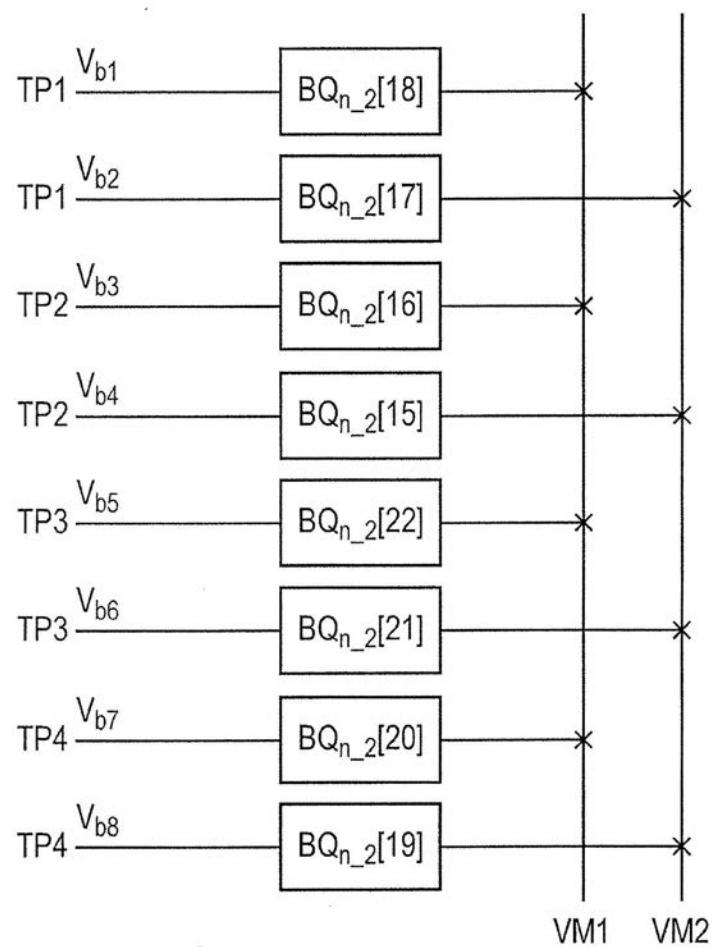

【図5B】状態変数フィルタのシリアルペリフェラルインターフェース（S P I）のデータ割当てを示すブロック図である。

【図5C】状態変数フィルタの動作を測定するテストポイント接続部を示すブロック図である。

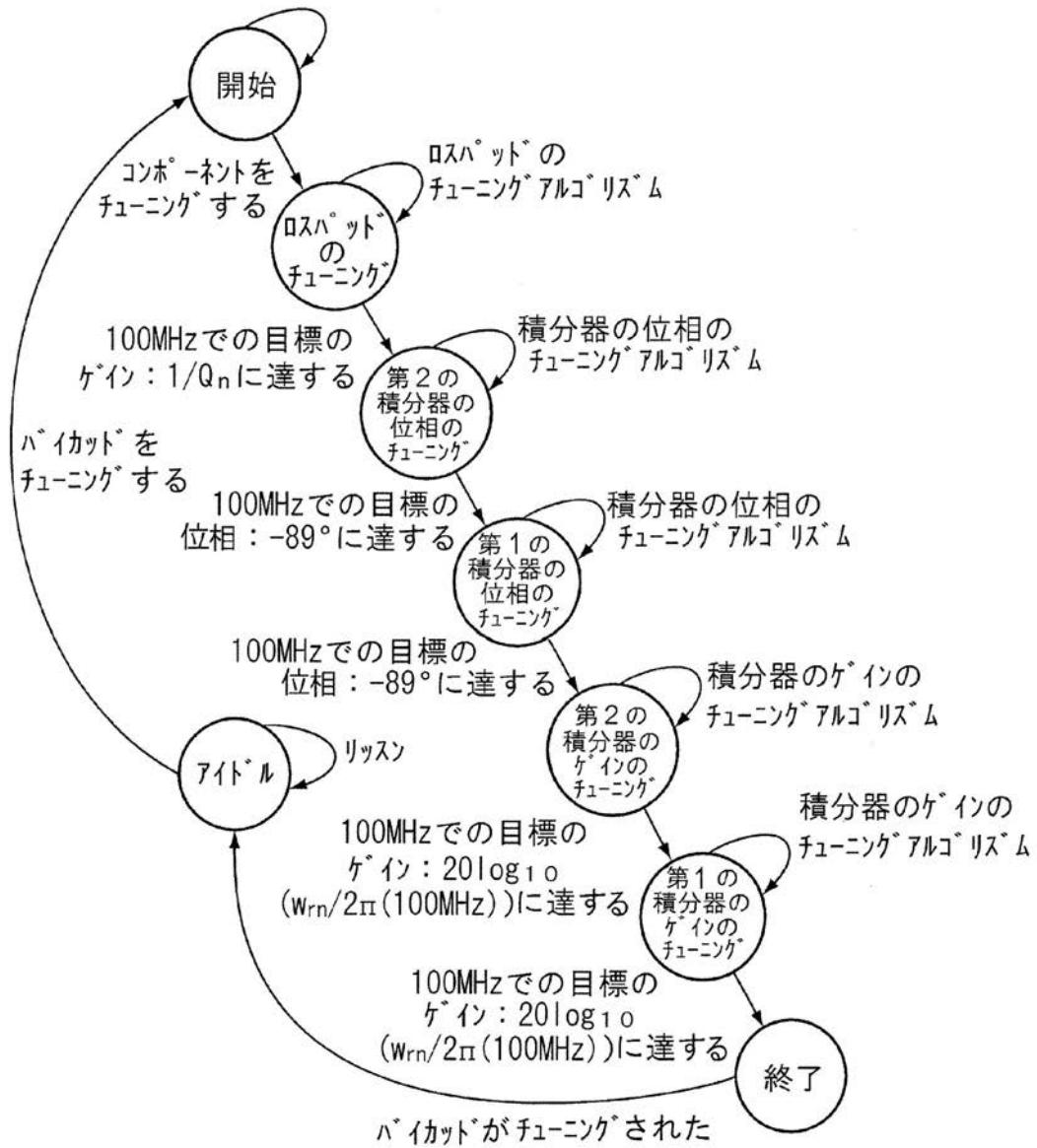

【図6】状態変数フィルタをチューニングするプロセスを示す状態遷移図（state diagram）である。

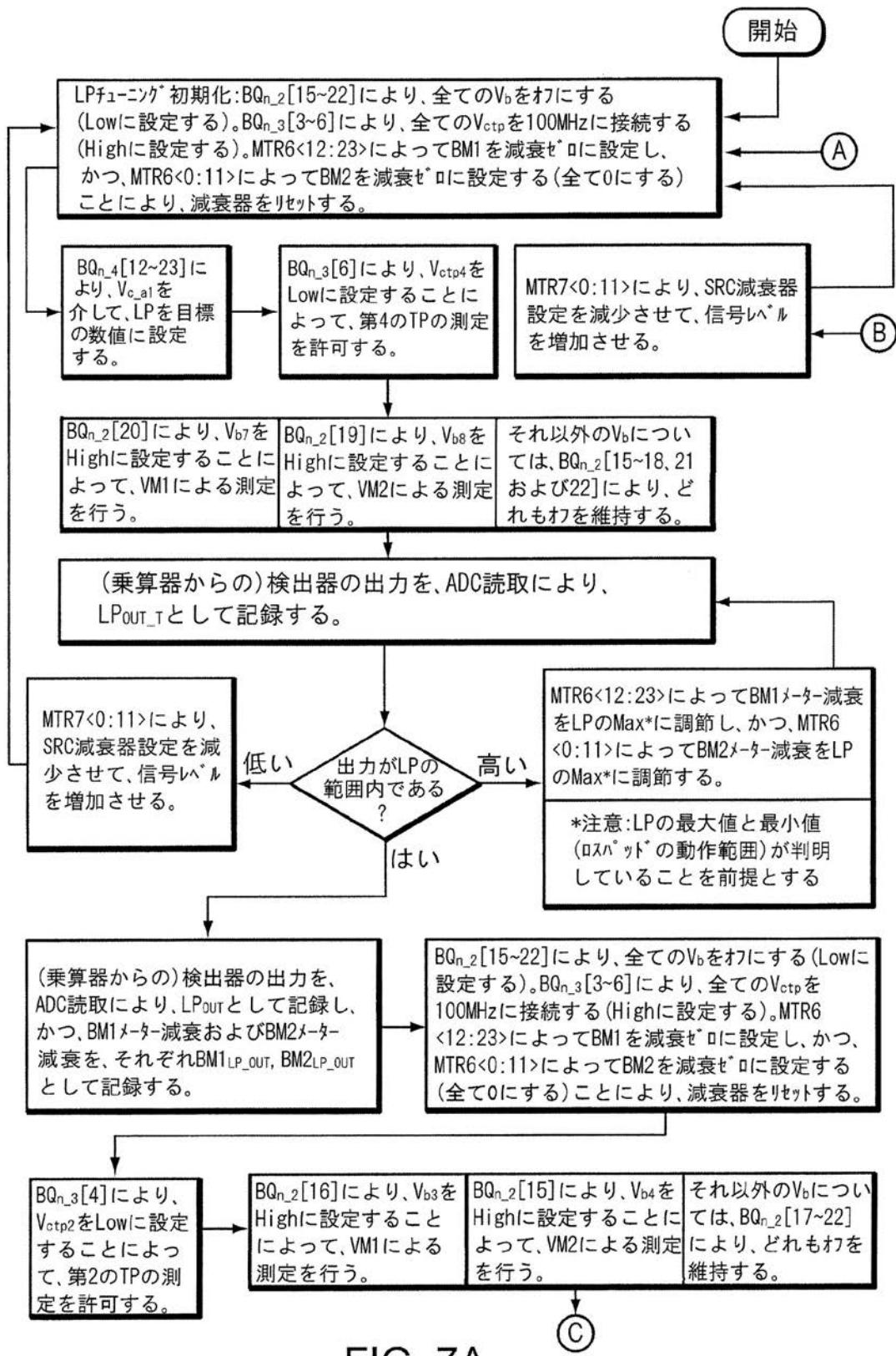

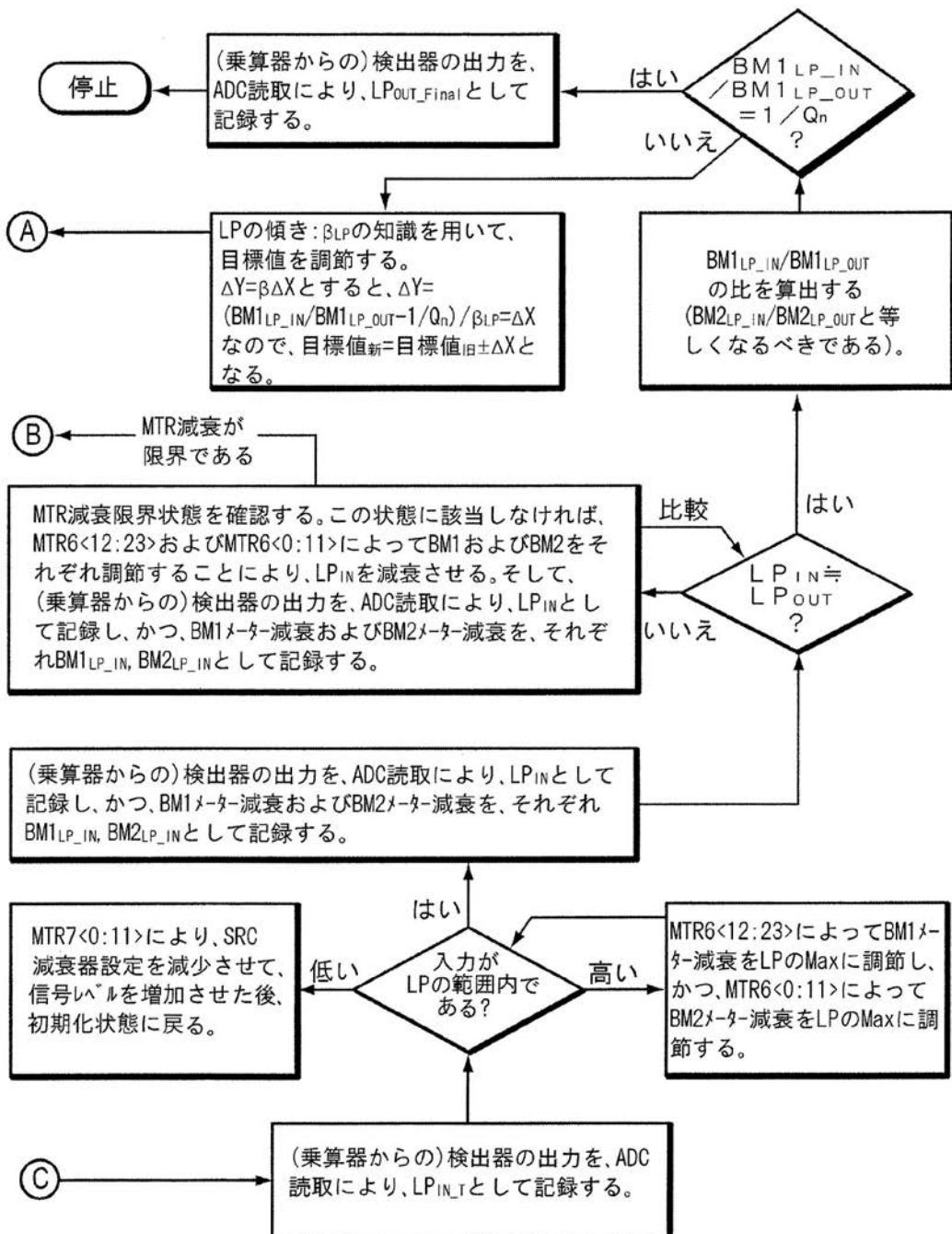

【図7A】ロスパッドをチューニングするプロセスのフロー図である。

【図7B】図7Aのフロー図の続きである。

【図7C】図7Aと図7Bとの関係を示す図である。

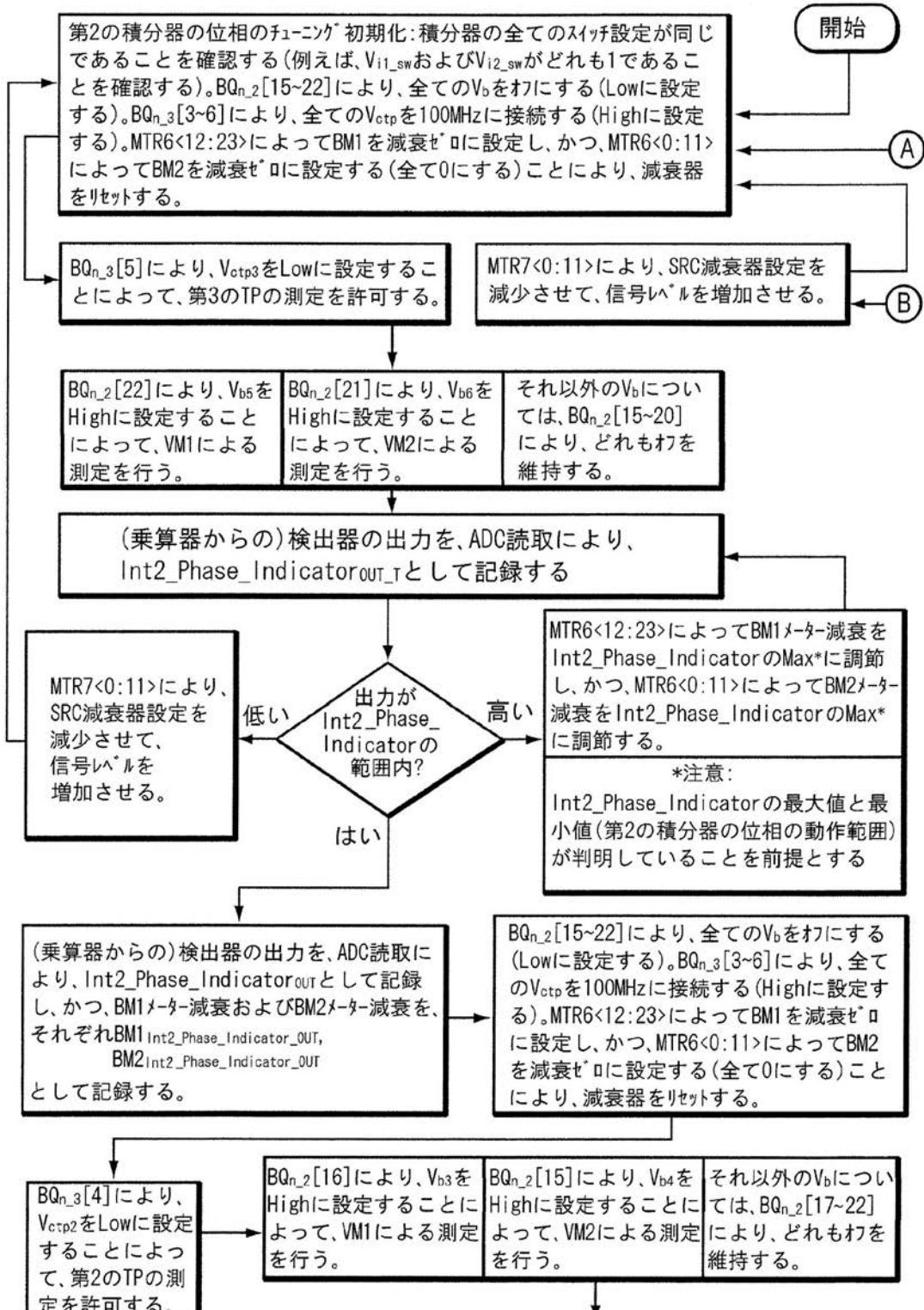

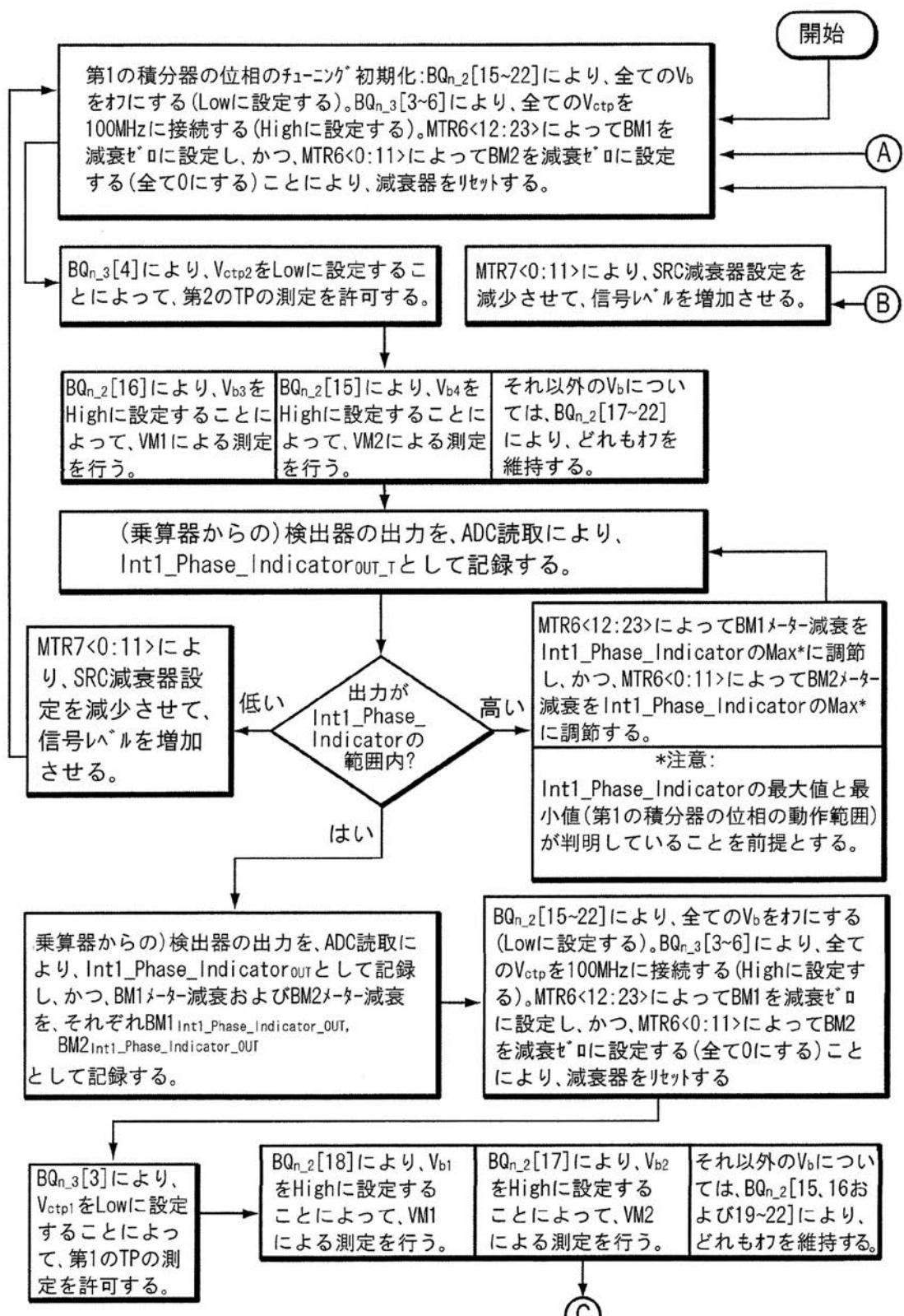

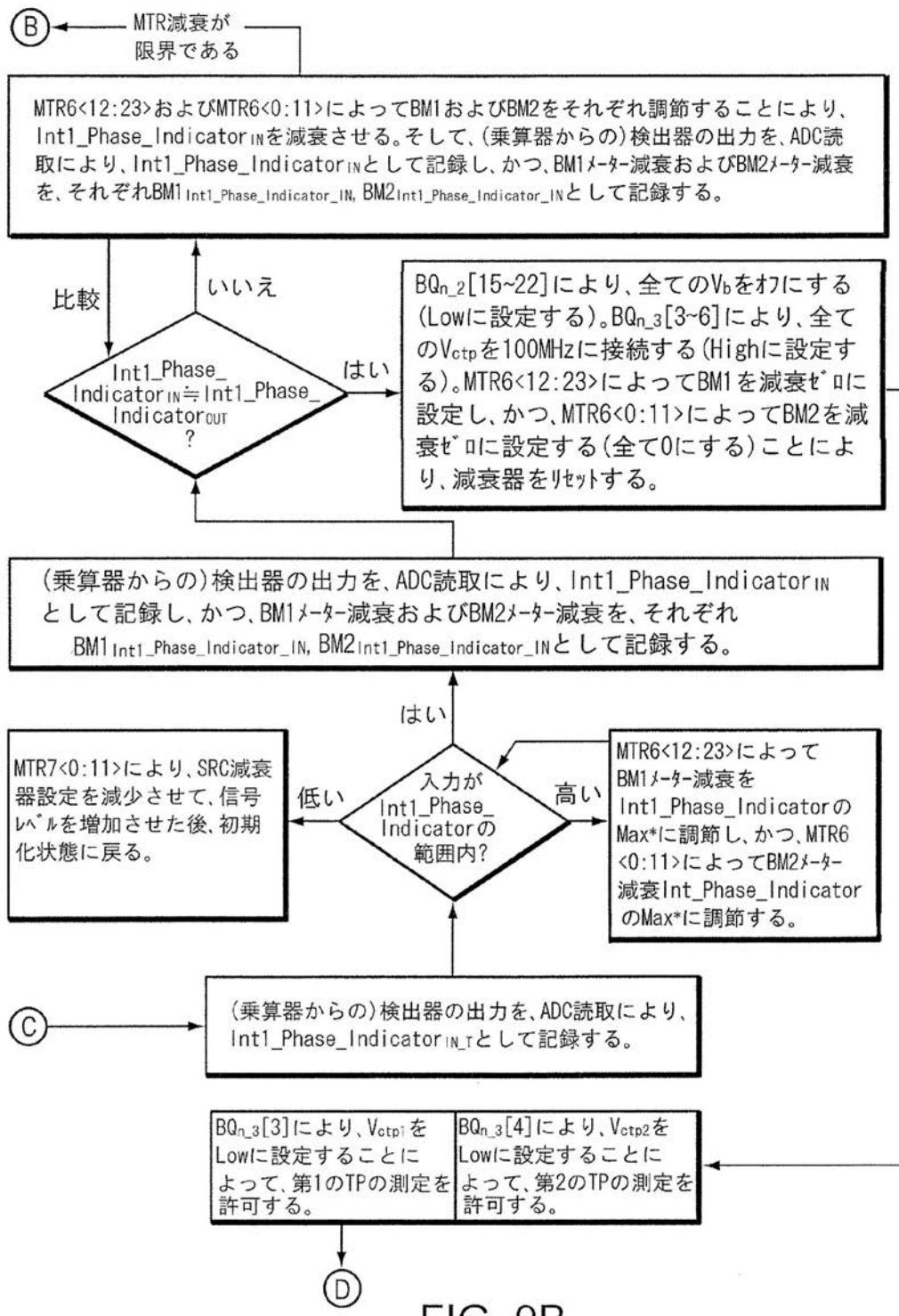

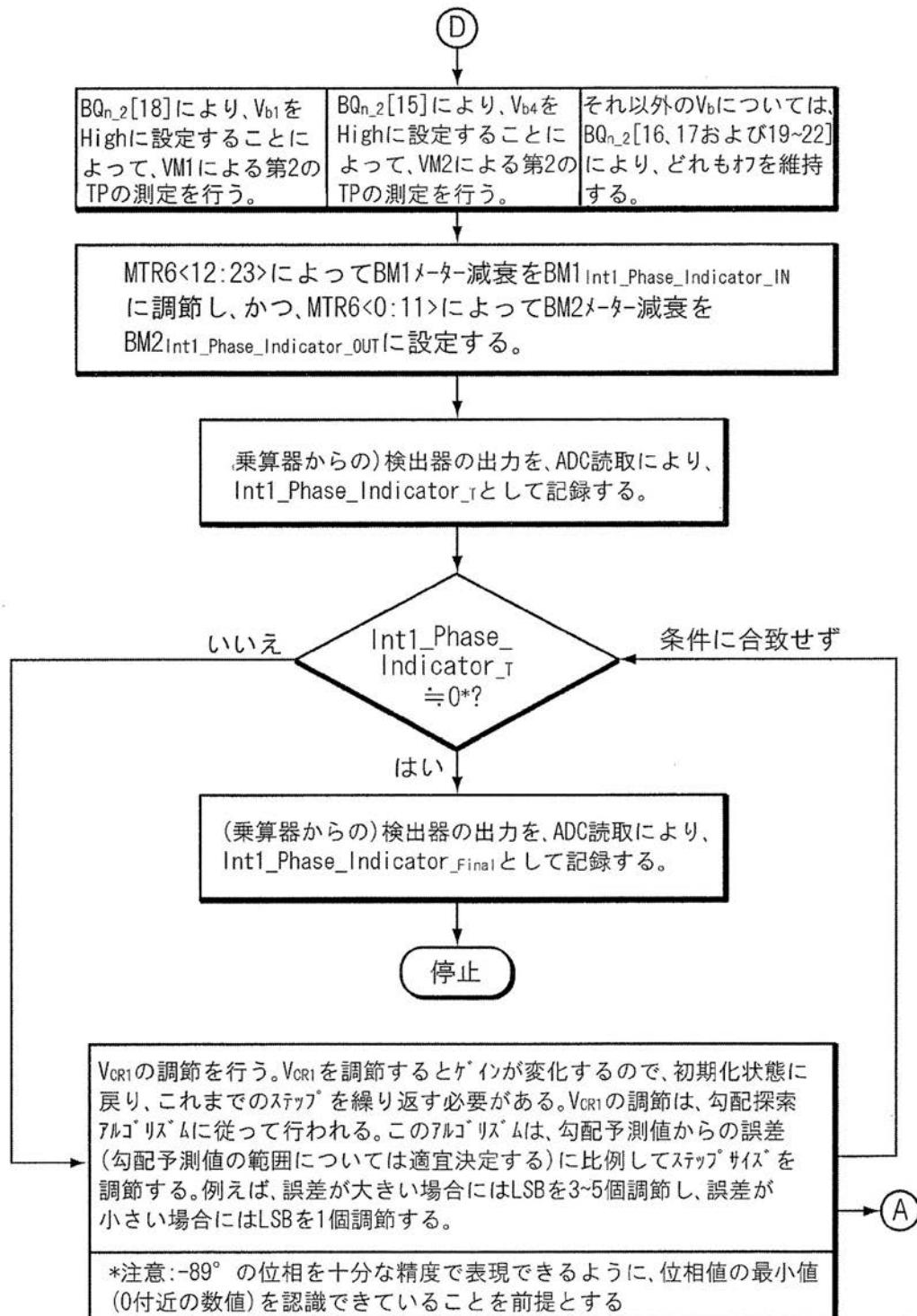

【図8A】積分器の位相をチューニングするプロセスのフロー図である。

【図8B】図8Aのフロー図の続きである。

【図8C】図8A及び図8Bの続きである。

【図8D】図8Aと図8Bと図8Cとの関係を示す図である。

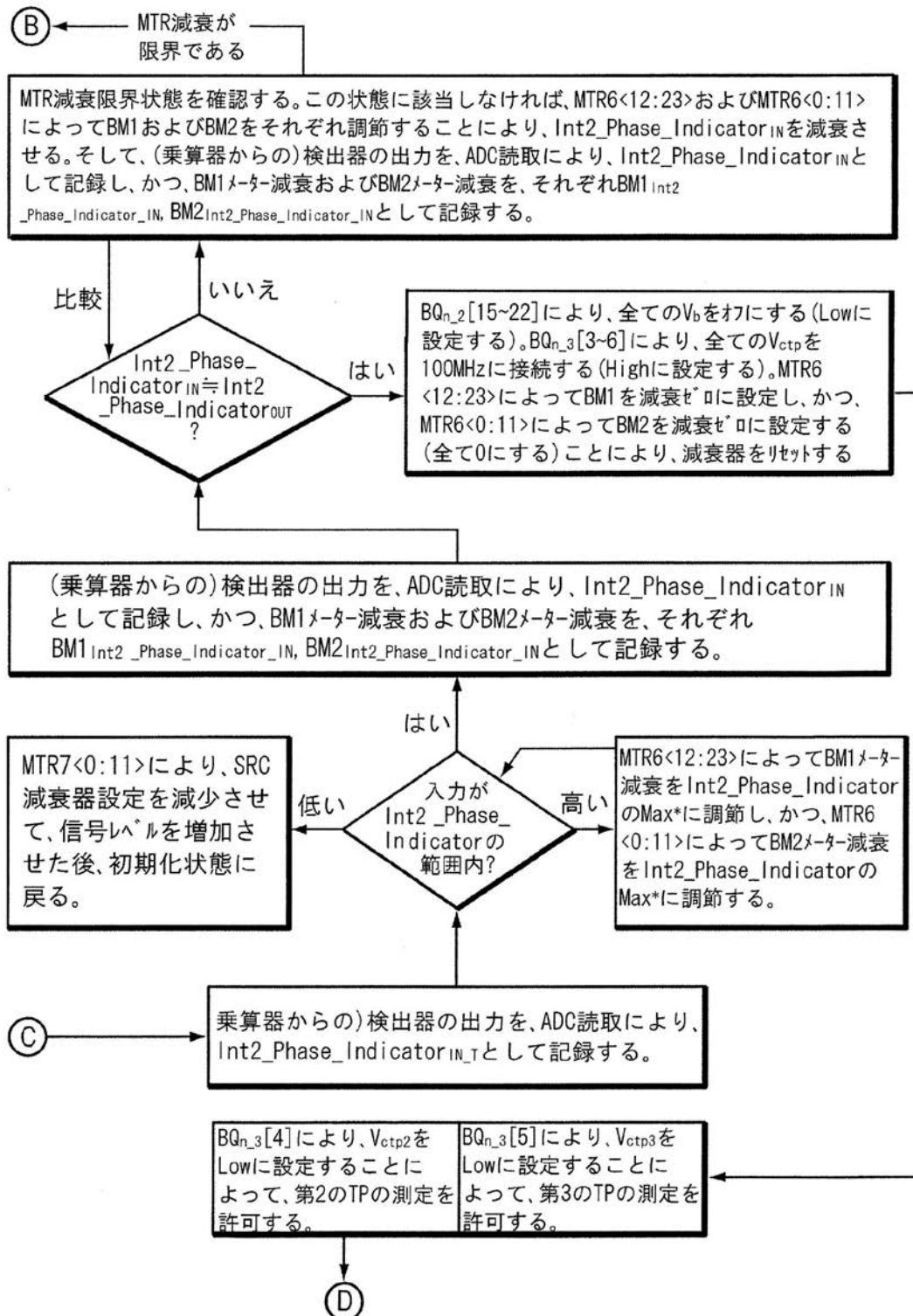

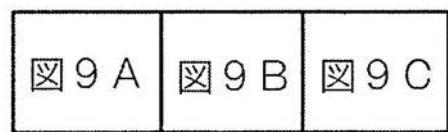

【図9A】さらなる積分器の位相をチューニングするプロセスのフロー図である。

50

【図 9 B】図 9 A のフロー図の続きである。

【図 9 C】図 9 A 及び図 9 B の続きである。

【図 9 D】図 9 A と図 9 B と図 9 Cとの関係を示す図である。

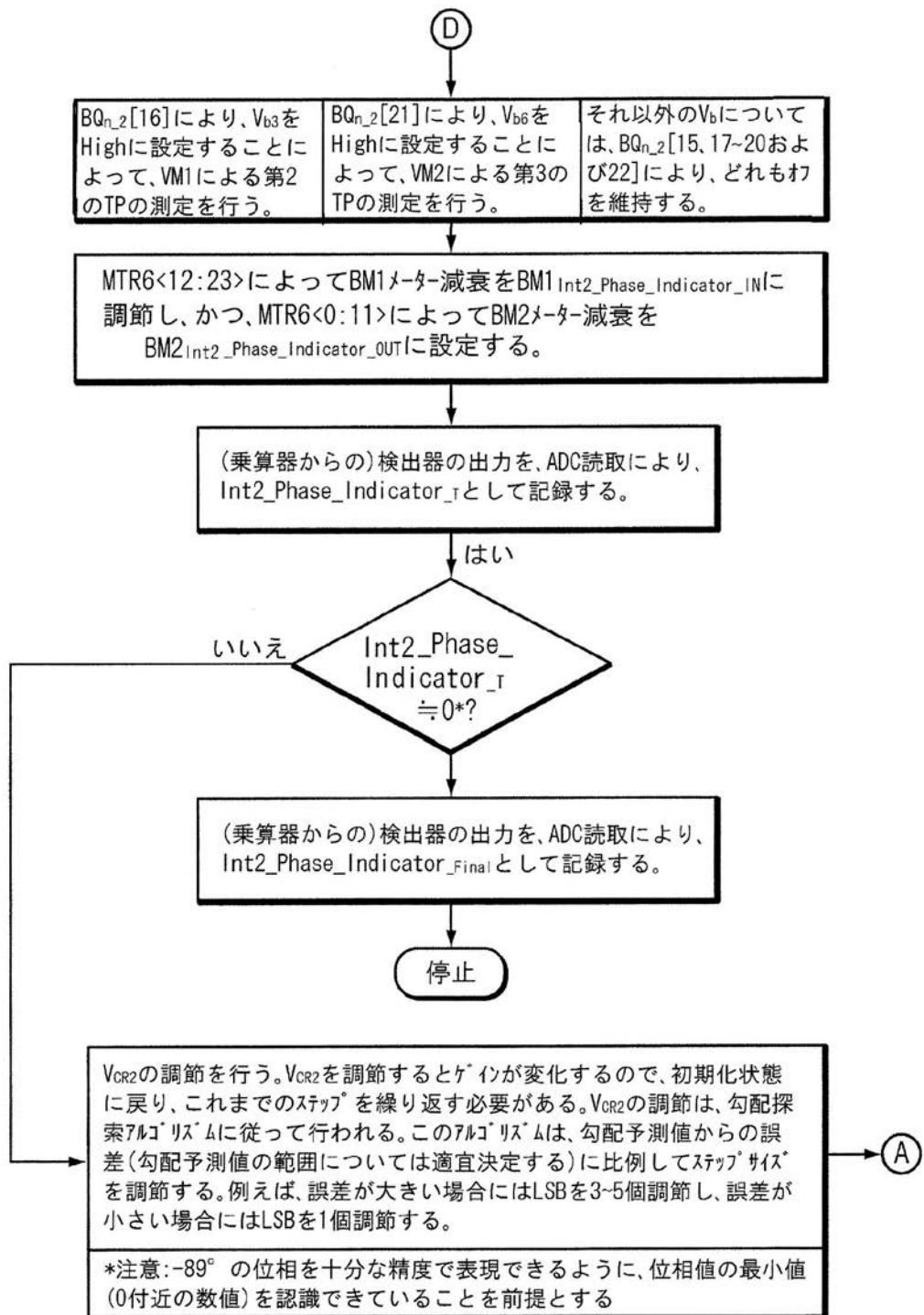

【図 10 A】積分器のゲインをチューニングするプロセスのフロー図である。

【図 10 B】図 10 A のフロー図の続きである。

【図 10 C】図 10 A と図 10 Bとの関係を示す図である。

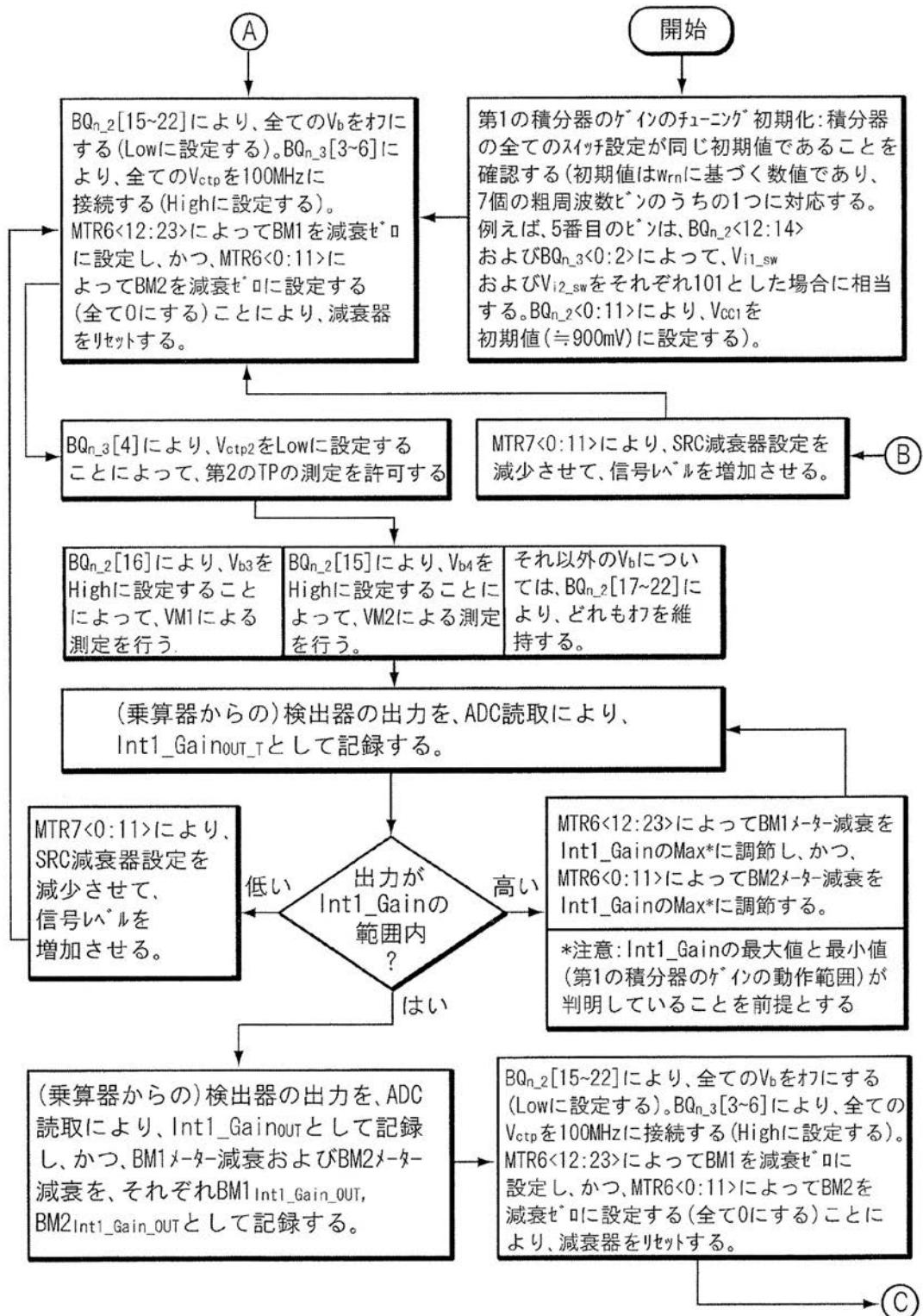

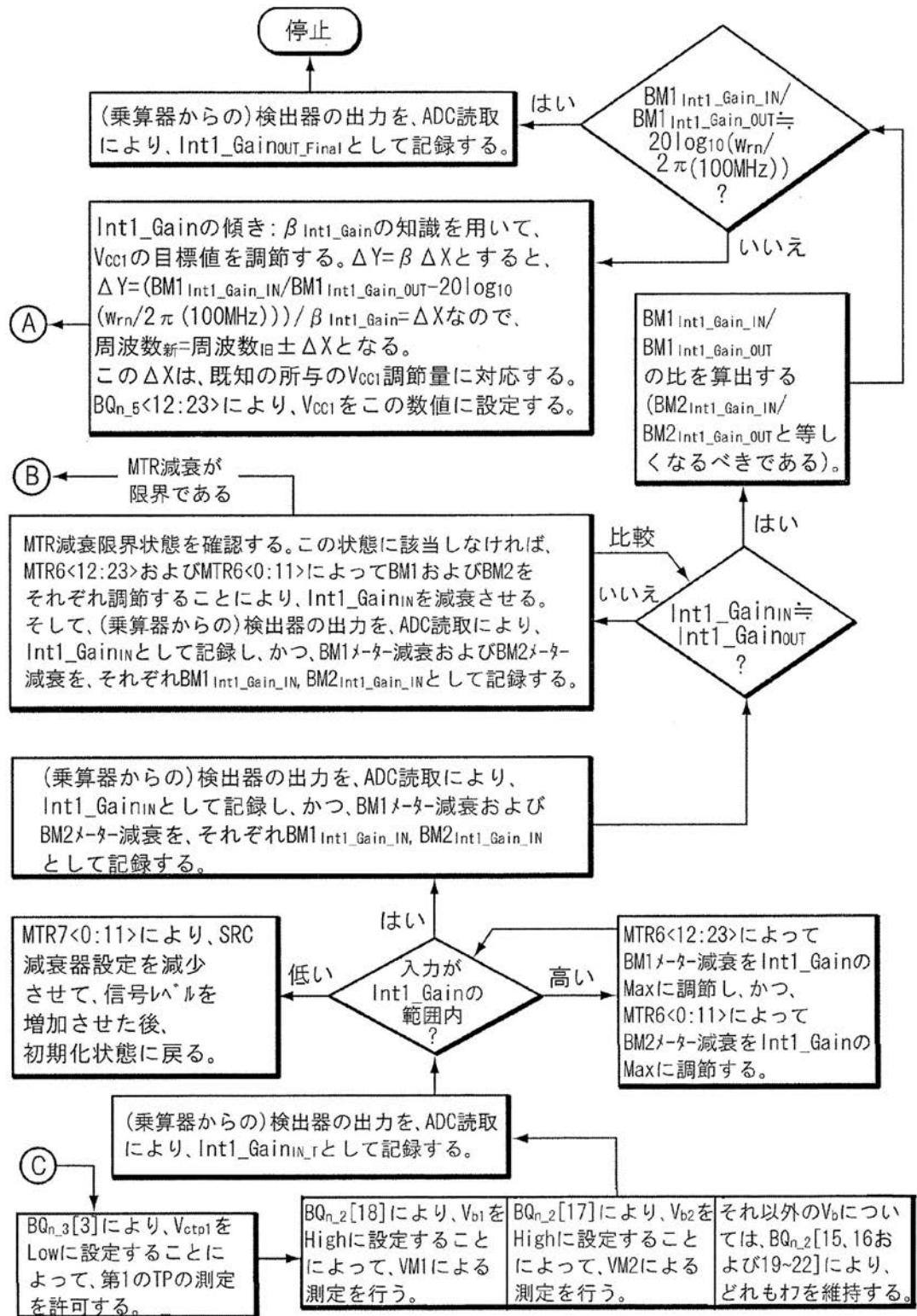

【図 11 A】さらなる積分器のゲインをチューニングするプロセスのフロー図である。

【図 11 B】図 11 A のフロー図の続きである。

【図 11 C】図 11 A と図 11 Bとの関係を示す図である。

【図 12 A】積分器の制御結果を示すグラフである。

【図 12 B】積分器の制御結果を示す他のグラフである。

【図 13】積分器のゲインをチューニングする回路の回路図である。

【図 14 A】積分器の粗チューニング（粗調整）の例を示すグラフである。

【図 14 B】積分器の粗チューニングの例を示す他のグラフである。

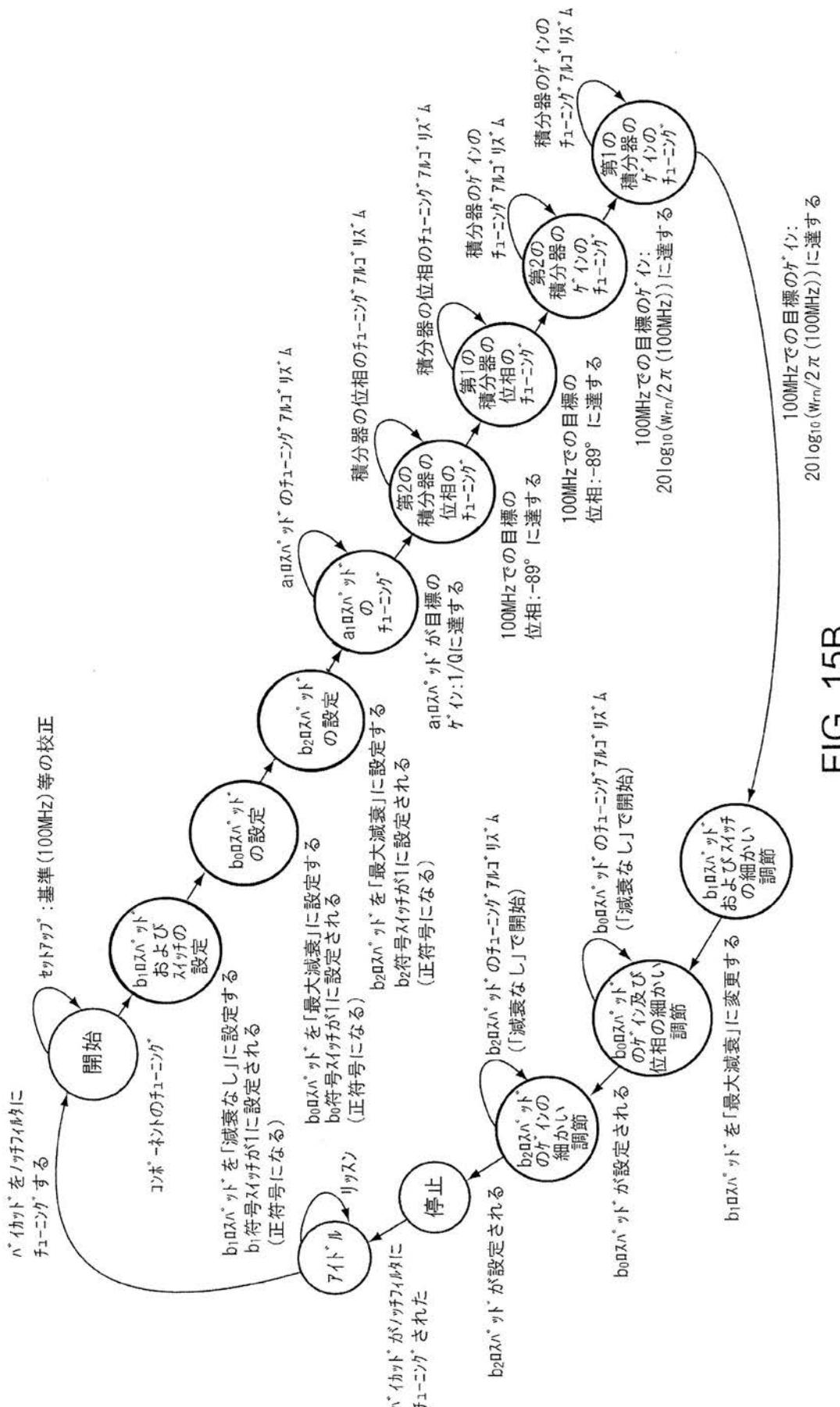

【図 15 A】状態変数フィルタをノッチフィルタとして動作させるチューニング例の回路図である。

【図 15 B】状態変数フィルタをノッチフィルタとして動作させるチューニング例のフロー図である。

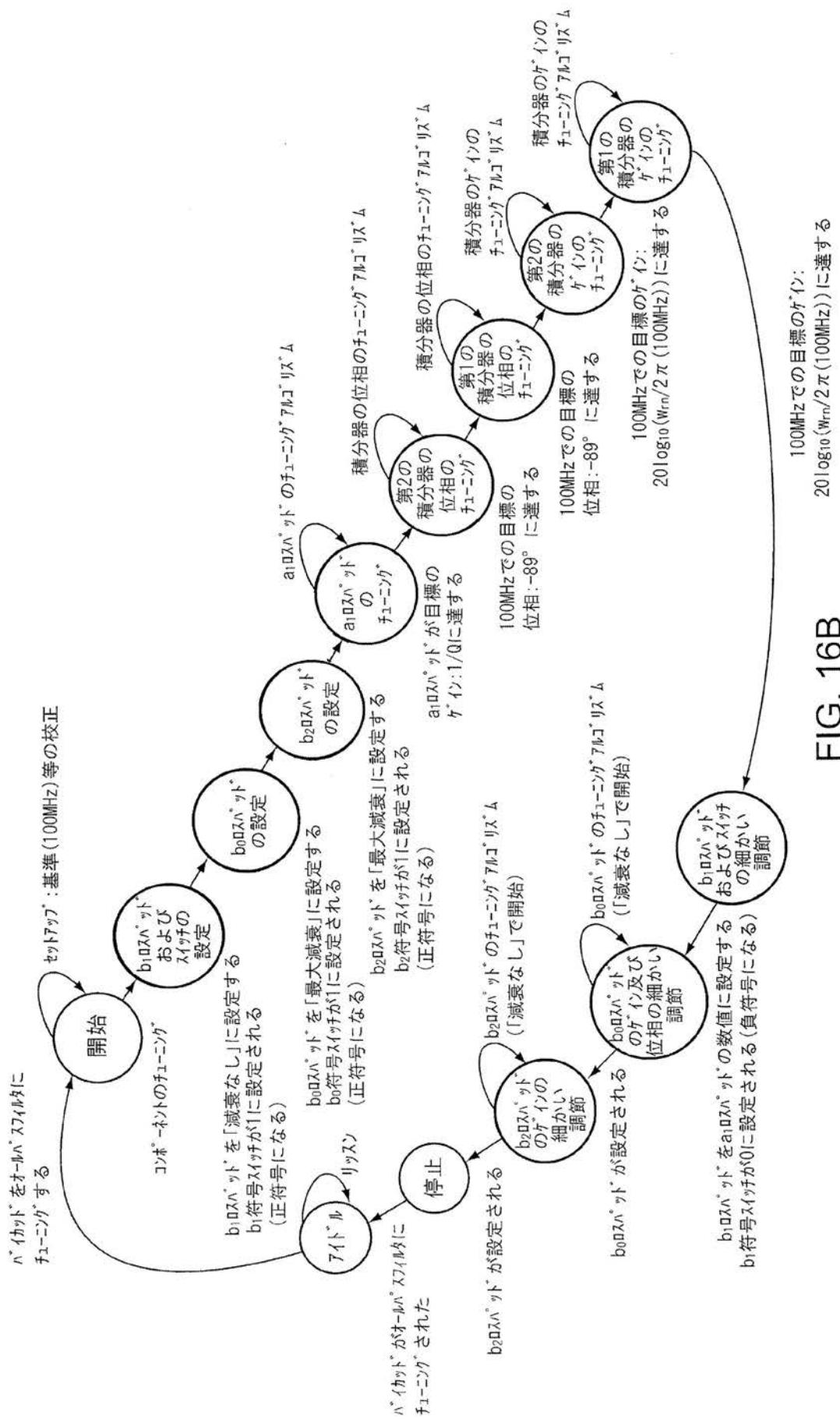

【図 16 A】状態変数フィルタをオールパスフィルタ（遅延フィルタ）として動作させるチューニング例の回路図である。

【図 16 B】状態変数フィルタをオールパスフィルタ（遅延フィルタ）として動作させるチューニング例のフロー図である。

【発明を実施するための形態】

【0011】

本発明の例示的な実施形態を以下に説明する。

【0012】

広い周波数帯域（例えば、3.7 ~ 10.0 GHz）にわたって細かく信号エネルギーを分散する広帯域および超広帯域（UWB）の通信システムが、多くの無線用途に有効であることは明らかである。広帯域通信の特質の多く（極限環境で作動する低電力システムにおいても、高精度の測距、材料透過、重畠（オーバーレイ）、および多重路フェージングに対する堅牢性）は、無線周波数識別（RFID）のような、難易度の高い軍用および商用用途に立ち向かう重大な課題に、まさに対処している。さらに、ベースバンドで作動する広帯域システムは、受信機においてダウンコンバートを必要とせず、必要とされる受信機を単純化している。

【0013】

重畠要求を満たすために、極めて広い周波数帯域にわたってエネルギーが細かく分散した広帯域システムの設計に関する課題は、通信システムの設計者には容易に明らかになる。具体的には、設計者は、一般に、オールデジタル（全帯域をデジタルにする）受信機、部分的または完全なレーキ（rake）受信機用のアナログ相関器、および基準送信受信機（transmitted reference receiver）の中から、極限の帯域幅（現在は7 GHzだが将来的により広くなる可能性がある）に倍率変更可能な受信機の設計を選択する。

【0014】

アナログ - デジタル（A / D）変換は、オールデジタル受信機の帯域幅およびダイナミックレンジ（分解能）を制限する。現在では、ベースバンドのUWB信号を適切にサンプリング可能な高忠実度のA / D変換器は、複雑すぎて、特にRFID用途に対してはかなりの電力を消費する。代替的なオールデジタルシステムは、低分解能のA / D変換器に依存しているが、良好に機能しない。アナログ相関器については、帯域幅が広くなるにつれて、効率的なエネルギー受信（エネルギー捕獲）に対するレーキフィンガの数が増えるため、チャネル推定の回路が複雑になり困難性も増す。基準送信受信機は、低速ないし中速度のデータ転送速度動作には好適であるが、これら動作は、UWB用途の受信機では広帯

域幅の遅延ラインを必要とする。

【0015】

ここで、本発明者らは、デジタル信号処理を強化し、このようなシステムの帯域幅処理能力を大幅に改善する、広帯域信号処理（WiSP）を開示する。この開示されたWiSPシステムおよび技術は、アナログ領域においてデジタル機能を実行して拡張することによって広帯域信号のための汎用的な信号処理を提供する。開示された本発明の実施形態は、任意の所望のインパルス応答つまり伝達関数を、指定可能な精度で実現するために、状態変数を使用したアーキテクチャを採用している。中心周波数を含む全てのフィルタパラメータは、低データ転送速度で動作するアルゴリズム、広帯域デジタル信号プロセッサ（DSP）、または、制御経路において動作する他の適切な制御要素を用いて制御および最適化できる。広帯域信号プロセッサは、帯域幅が10GHzを超える信号を含む、広帯域信号の処理を可能にするために、サブミクロンの相補型金属酸化物半導体（CMOS）構造で実現される。

10

【0016】

開示されたWiSPシステムおよび装置の実施形態には、広帯域フィルタ、アジャイルフィルタ、適応フィルタ、等化器、直接中間周波（IF）送信機（direct intermediate-frequency transmitter）、ならびに単側波帯変調器および復調器として、またはこれらの内部において用いられる、動的および再構成可能なフィルタが含まれる。本発明の原理に従って作製されたフィルタ、プロセッサ、等化器およびタップ付遅延ラインは、能動的RFID、レーダ、画像処理、ソフトウェア無線、コグニティブ無線、ベースバンドプロセッサ、計測器および無線高解像度マルチメディアインタフェーシングを含むがこれらに限定されるわけではない多種多様なアプリケーションで用いられてもよい。これらのコンポーネントおよびアプリケーションのリストは、全てを網羅したものではなく、むしろ、本発明の原理に基づいて製造または使用に適したコンポーネントおよびアプリケーションの代表例である。

20

【0017】

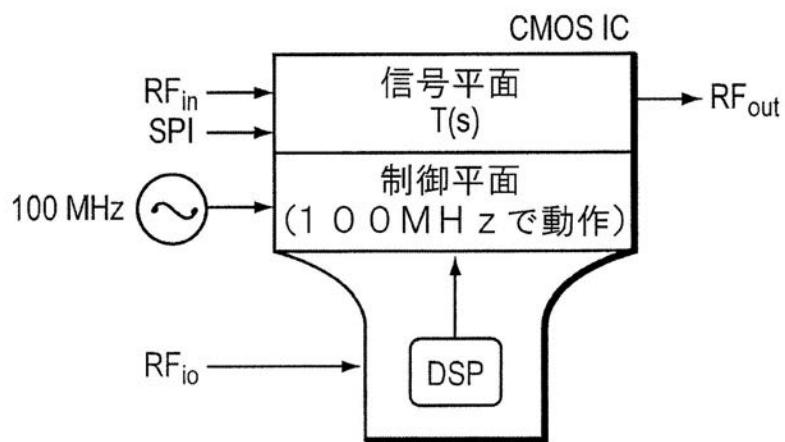

[アナログ信号処理用のフィルタ]

典型的な信号処理システムは2平面上で動作する。信号平面（S平面）では、信号は、フィルタおよび他の処理操作を用いて操作される。制御平面（C平面）では、信号処理動作がセットアップ（設定）されて操作される。例えば、適応等化システムでは、信号は、トランスバーサルフィルタを通過するが、フィルタの係数は、C平面によって制御される。今日では、これらの両方の機能はDSPによって実行される。デジタル信号処理の根底にある数学的基礎は、S平面理論、すなわち、サンプリング定理によって左右されるナイキストサンプリング速度における、またはそれを上回る、同期サンプリングに基づいている。言うまでもないが、このような機能を実行するシステムは、DSP、A/Dおよびデジタル-アナログ（D/A）技術の利用に依存している。

30

【0018】

ここで開示される実施形態では、S平面は、10+GHzの帯域幅を維持しながら、高度なアナログ信号処理（信号経路が全てアナログ）にかけられる。しかし、C平面は、従来のA/D、D/AおよびDSPアーキテクチャで実現される。本明細書で開示された実施形態は、これらのハイブリッドシステムに起因する少ないゲート数およびブロックアーキテクチャゆえに、今日の標準に比べて極めて低い電力消費となる。

40

【0019】

フィルタは、アナログ信号プロセッサに用いられる基礎的なコンポーネント（構成要素）である。これらフィルタは、周波数に対する信号の增幅および/または位相の特性を変更するため、S平面における信号処理が可能になる。フィルタは、特定の周波数範囲内の信号を通し、他の範囲内の信号を除去するために用いられる。帯域通過フィルタは、所与の帯域内にある周波数のみを通す。一方、ノッチフィルタまたは帯域除去フィルタは、特定の周波数を除去するが、その他の全ての周波数を乱すことなく通過させる。ローパスフィルタは遮断周波数よりも高い周波数を除去し、ハイパスフィルタは遮断周波数よりも低

50

い周波数を除去する。オールパスフィルタは、信号を減衰させずに、入力信号を位相シフトさせる。

【0020】

フィルタの周波数応答は伝達関数によって数学的に表すことができ、この伝達関数は、フィルタの出力信号と入力信号のラプラス変換の比である。理想的なフィルタは、矩形状の伝達関数、すなわち、通過帯域と阻止帯域との間における無限に急峻な境界と、通過帯域における一定のゲインとを伴う伝達関数を有する。さらに、理想的なフィルタは、信号に位相ひずみを導入することを避けるために、線形位相応答を有する。実際のフィルタは、理想的な応答を単に近似するものである。

【0021】

フィルタの次数は、フィルタの伝達関数の多項式展開の次数に等しい。従来のRFシステムでは、高次のフィルタが、低次のフィルタをカスケード接続（すなわち、直列接続）することによって構成されている。例えば、1次フィルタの出力を2次フィルタの入力に接続することによって、3次フィルタが構成されることができる。高次のフィルタは、典型的には、低次のフィルタに比べて通過帯域性能が改善されており、ロールオフ（阻止帯域における減衰）をより高速に行う。

【0022】

[フィルタの設計、実現および動作]

通常、フィルタを設計する場合、その目的は、特定の伝達関数またはインパルス応答を実現することである。有理関数による伝達関数は、以下の式になる。

【0023】

【数1】

$$T_{mn}(s) = \frac{b_m s^m + b_{m-1} s^{m-1} + \dots + b_0}{s^n + a_{n-1} s^{n-1} + \dots + a_0} \quad (1)$$

【0024】

但し、 $s = j\omega$  であり、単位は rad · Hz である。分子の解は、フィルタの零点であり、分母の解はフィルタの極である。この式では部分分数展開がなされ、次に逆ラプラス変換され、時間的関数を複素正弦波の総和として表わすことができる。

【0025】

【数2】

$$T_{mn}(s) = \sum_{i=1}^n \frac{R_i}{s - p_i} \Leftrightarrow y_{mn}(t) = \sum_{i=1}^n R_i e^{p_i t} \quad (2)$$

【0026】

この近似は、総和に追加の項を加えることによって、任意の精度の正確さを得ることができる。

【0027】

式(2)におけるように、複素正弦波の総和の形式のインパルス応答の式を展開するために、パデ近似、プロニー法または任意の他の適切な方法を採用して、 $y_{mn}(t)$  の  $R_i$  および  $p_i$  の値を決定することができる。 $y_{mn}(t)$  が分かると、状態変数法を用いることができる。式(3)で表される系は、式(2)からの  $y_{mn}(t)$  と同一形式の解、 $y(t)$  を有する。

【0028】

10

20

30

40

【数3】

$$\left\{ \begin{array}{l} \dot{\underline{\mathbf{x}}} = \begin{bmatrix} -p_1 & & & & \\ & -p_2 & & & \mathbf{0} \\ & & -p_3 & & \\ \mathbf{0} & & & \ddots & \\ & & & & -p_n \end{bmatrix} \underline{\mathbf{x}} + \begin{bmatrix} R_1 \\ R_2 \\ R_3 \\ \vdots \\ R_n \end{bmatrix} \mathbf{u} \\ y = [1 \ 1 \ 1 \ \cdots \ 1] \underline{\mathbf{x}} \end{array} \right. \quad (3)$$

10

【0029】

プロニー法またはパデ近似を適用することによって、 $R_i$  および  $p_i$  の値の一覧表が得られる。これらの値のうちいくつかは実数であり、いくつかは複素数である。複素極 / 留数のペアは、共役複素数のペアとして表され、以下のように組み合わさることができる。

【0030】

【数4】

20

$$\begin{aligned} T_p(s) &= \frac{R_i}{s - p_i} + \frac{R_i^*}{s - p_i^*} \\ &= \frac{2 \operatorname{Re}[R_i]s - 2 \operatorname{Re}[p_i R_i^*]}{s^2 - 2 \operatorname{Re}[p_i]s + |p_i|^2} = \frac{b_1 s + b_0}{s^2 + a_1 s + a_0} \end{aligned} \quad (4)$$

【0031】

但し、全てのフィルタ係数 (a および b) は実数である。これらの共役ペアは、以下に詳細に説明する、2次の制御正準形および観測正準形を用いてもたらされる。

30

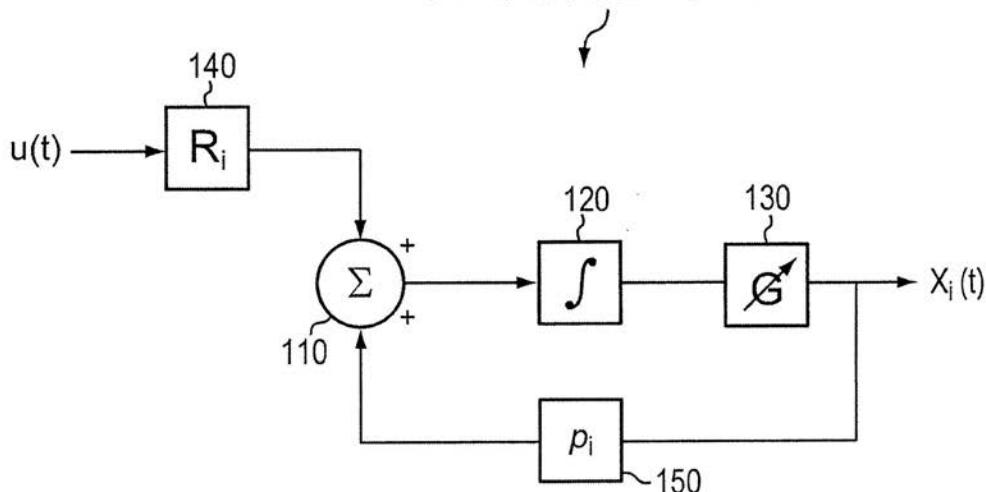

【0032】

図1は、式(2)および(3)に対する実数解を実現するために用いられる1次の状態変数フィルタ100を示している。1次の状態変数フィルタ100は、広帯域入力  $u(t)$  に作用して、フィルタ処理済み出力  $x_1(t)$  を生成する。留数ブロック140がその入力の留数  $R_i$  を決定し、この留数はフィルタ処理済み出力の極  $p_i$  と組み合わせる加算器110に送出される。加算器110は、留数と極の加算結果を積分器120に送る。従来の1次の状態変数フィルタとは異なり、この1次の状態変数フィルタ100は、積分器120の出力に作用する可変ゲインブロック130を含む。可変ゲインブロック130は、そのゲイン設定  $G$  に従って、積分済み信号を增幅または減衰して、フィルタ処理済み出力を生成する。可変ゲインブロック130に結合された極ブロック150が、フィルタ処理済み出力の極  $p_i$  を生成し、これが、加算器110にフィードバックされる。極ブロック150と留数ブロック140のパラメータを変更することによって（すなわち、フィルタのタップ重みを変えることによって）、フィルタの中心周波数および通過帯域幅を含むフィルタの伝達特性を変化させる。

40

【0033】

図1の1次の状態変数フィルタ100を再検討すると、可変ゲインブロック130の効果が極めて興味深いことがわかる。可変ゲインブロック130は、積分器120が前段に存在する場合には、信号を增幅するのではなく、周波数スケールとして機能する（これは、ラプラス領域における  $1/s$  に等しい）。可変ゲインブロック130は、フィルタ伝達

50

関数  $T(s)$  を  $T(s/G)$  に変換する。但し、 $G$  は、可変ゲインブロック 130 のゲインである。 $s = j\omega = j2\pi f$  であるため、 $1/G$  によって  $s$  を拡大または縮小（倍率変更）することによって、係数  $G$  で  $T(s)$  の周波数を実質的に拡大または縮小する。 $G$  を変えることで、フィルタの通過帯域の中心周波数を UWB 帯域全体にわたって調整できる。

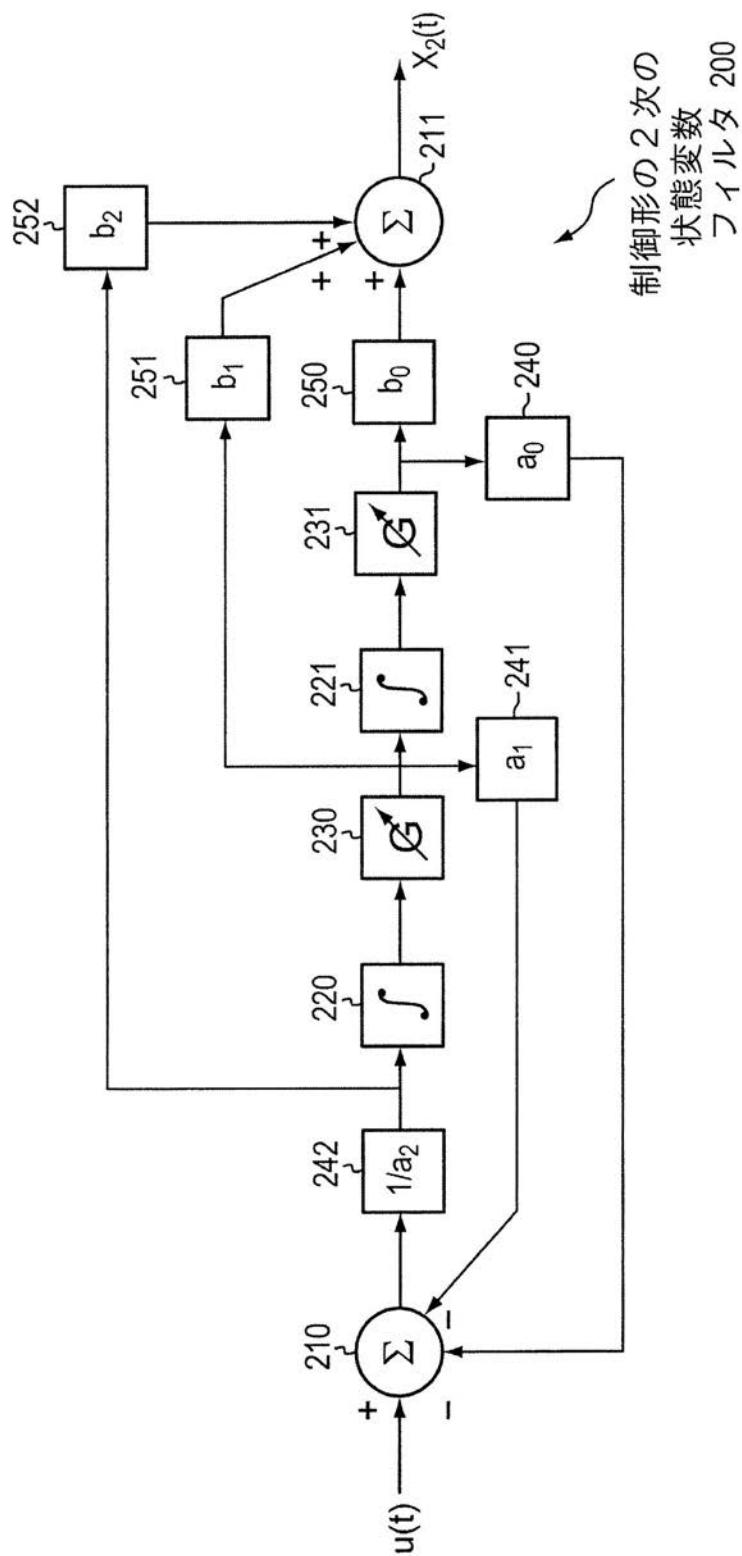

#### 【0034】

図 2A および図 3 は、それぞれ、式 (2) および (3) に対して 2 次の解を具現化する、制御正準形および観測正準形における 2 次の状態変数フィルタ 200 および 300 を示す。これら 2 つの正準形は、数学的には等価であるが、観測形 300 は、追加の加算器を必要とし、異なる構成の入力および出力を有する。図 1 の 1 次の状態変数フィルタ 100 と同様に、2 次のフィルタ 200, 300 は、フィルタの通過帯域の中心周波数を変化させる可変ゲインブロックを含む。2 次のフィルタ 200, 300 はまた、式 (4) の伝達関数の係数（すなわち、 $a_0, a_1, a_2, b_0, b_1$  および  $b_2$ ）を表す、タップ重みまたはフラクショナルゲイン（1 未満の分数ゲイン（fractional gain））ブロックも有する。可変ゲインブロックと同様に、フラクショナルゲインブロックは、対応する係数に従って信号を減衰または増幅する。典型的には、可変ゲインブロックとフラクショナルゲインブロックは、-1 以上 1 以下の正規範囲内の値に信号を増加または減少させる。

10

#### 【0035】

図 2 の制御形の 2 次の状態変数フィルタ 200 は、広帯域入力  $u(t)$  に作用して、フィルタ処理済み出力  $x_2(t)$  を生成する。加算器 210 が広帯域入力をフラクショナルゲインブロック 240, 241 からの出力と結合する。加算器 210 は、広帯域入力とフラクショナルゲインブロックの 2 つの出力との差を第 3 のフラクショナルゲインブロック 242 に渡す。この第 3 のフラクショナルゲインブロック 242 は、加算器の出力を  $1/a_2$  倍する。フラクショナルゲインブロック 242 は、この倍率変更された加算器の出力を積分器 220 とフラクショナルゲインブロック 252 に送る。フラクショナルゲインブロック 252 では、倍率変更された加算器の出力を  $b_2$  倍する。

20

#### 【0036】

積分器 220 は、倍率変更された信号を積分して、その積分済み信号を可変ゲインブロック 230 に送る。可変ゲインブロック 230 は、そのゲイン設定  $G_1$  に従って、渡された信号周波数を調整する。可変ゲインブロック 230 の出力が、第 2 の積分器 221 とフラクショナルゲインブロック 241, 251 とに送られる。フラクショナルゲインブロック 241 は可変ゲインブロック 230 からの出力を  $a_1$  倍し、フラクショナルゲインブロック 251 は可変ゲインブロック 230 からの出力を  $b_1$  倍する。第 2 の積分器 221 が信号を再度積分して、その結果である第 2 の積分済み信号を可変ゲインブロック 231 に送る。可変ゲインブロック 231 の出力はフラクショナルゲインブロック 240, 250 に送られ、フラクショナルゲインブロック 240 は可変ゲインブロック 231 からの出力を  $a_0$  倍し、フラクショナルゲインブロック 250 は可変ゲインブロック 231 からの出力を  $b_0$  倍する。加算器 211 がフラクショナルゲインブロック 250, 251 および 252 の出力を結合して、フィルタ処理済み出力を提供する。

30

#### 【0037】

図 2B に、図 2A を参照しながら説明したフィルタ 200 のような、状態変数フィルタ回路（以降では、「バイカッド回路」と称する場合もある）を複数直列に接続した構成を示す。バイカッドとは、2 次の状態変数構造のことを指す。2N 次の伝達関数  $T(s)$  は、N 個のバイカッドをカスケード接続することによって実現可能である。

40

#### 【0038】

図 2B に示す伝達関数は、単入力単出力 (SISO) のフィールドプログラマブルアナログアレイ (FPGA) を記述したものとも見なせる。つまり、減衰器の数値や積分器のゲイン値を変更することにより、適応フィルタの特性や遅延フィルタの特性を各種多様に実現することが可能である。このようにアナログ領域で様々な操作ができるこにより、エンジニアは、広帯域信号を処理するうえで強力なツールを手に入れたことになる。

50

## 【0039】

図3の観測形の2次の状態変数フィルタ300は、図2のフィルタ200とほぼ同一の方法で、広帯域入力 $u(t)$ に作用して、フィルタ処理済み出力 $x_2(t)$ を生成する。しかし、ここでは、フラクショナルゲインブロック350, 351, 352が、それぞれ、広帯域入力を $b_0$ ,  $b_1$ および $b_2$ 倍し、これら倍率変更後の出力を、それぞれ加算器310, 311, 312に送る。加算器310は、フラクショナルゲインブロック340からの倍率変更された出力を、フラクショナルゲインブロック350の出力と結合して(350の出力から差し引いて)、結合信号を提供する。

## 【0040】

積分器320は、加算器310からの信号を積分して、その積分器320からの積分済み信号を可変ゲインブロック330に送る。可変ゲインブロック330は、そのゲイン設定に従って、渡された信号周波数をチューニングする。第2の加算器311が、可変ゲインブロック330の出力を、フラクショナルゲインブロック341, 351からの出力と結合して、第2の結合出力を提供する。

10

## 【0041】

第2の積分器321が、第2の結合出力(第2の加算器311からの出力)を積分して、その第2の積分器321からの第2の積分済み信号を第2の可変ゲインブロック331に送る。第3の加算器312が、第2の可変ゲインブロックの出力をフラクショナルゲインブロック352の出力と結合して、第3の結合信号を提供する。フラクショナルゲインブロック342が第3の結合信号を $1/a_2$ 倍して、フィルタ処理済み出力を提供する。フィルタ処理済み出力は、フラクショナルゲインブロック340, 341に送られ、フラクショナルゲインブロック340はフィルタ処理済み出力を $a_0$ 倍し、フラクショナルゲインブロック341はフィルタ処理済み出力を $a_1$ 倍する。

20

## 【0042】

図1～図3の1次および2次の状態変数フィルタは、追加の積分器および可変ゲインブロックを適宜組み合わせまたは除去することによって、任意の次数に一般化できる。 $n$ 次の状態変数フィルタが、可変ゲインブロックを $n$ 個の積分器の各出力に結合することによって構成されることができる。高次の状態変数フィルタは、また、フィルタ全体の様々な箇所において、信号を倍率変更および結合するように構成された追加の機能的ゲインブロックおよび加算器を有してもよい。機能的ゲインブロックの倍率変更係数を0または1に設定する(フィルタの構成に応じて設定する)ことによって、フィルタ動作に対する機能的ゲインブロックの影響を、実質上抑えることもできる。また、図2Bを参照しながら説明したように、バイカッド回路を複数直列に接続し、具体的には $N$ 個のバイカッド回路をカスケード接続することにより、 $2N$ 次の伝達関数 $T(s)$ ’を実現することもできる。

30

## 【0043】

図4は、本発明の原理に従った基本的な信号フィルタ動作400を示したフロー図である。最初に、広帯域入力402が極418と結合されて(404)、結合信号406を生成する。ここで、極418は、信号フィルタ処理400を通して得られるフィルタ処理済み信号416から求められるものである。高次のフィルタ処理の場合、極418は、フィルタ処理済み信号416をフラクショナルゲイン係数によって倍率変更することによって得るようにしてもよい。結合信号406は積分されて(408)、積分済み信号410を生成し、積分済み信号410は、可変ゲイン414によって増幅されて(412)、フィルタ処理済み信号416を生成する。可変ゲイン414を変更することで、フィルタ処理済み信号416の中心周波数をシフトさせることができる。

40

## 【0044】

本発明の例示的な実施形態は、図1～図4を参照しながら説明したような状態変数フィルタ(以降では「バイカッドフィルタ」と称する場合もある)をチューニングする方法を提供する。本発明に適用可能な広帯域フィルタの実施形態については、「広帯域信号処理の方法、システムおよび装置」(米国特許出願第12/921,987号；国際出願第PCT/US2009/001512号)および「広帯域信号処理」(米国特許出願第13/666,269号；国際出願第PCT/US2

50

012/062965号)に詳細に記載されている。なお、これらの文献の全教示内容は、参照をもって本明細書に取り入れたものとする。以下で説明するチューニング手順を実行することにより、フィルタの性能を様々なかたちで向上させることができる。例えば、当該フィルタを集積回路で実現した場合に起こり得る精度低下を補償することができる。つまり、後述するチューニング手順により、当該手順を実行しない場合に比べて、より高い精度を達成することができる。

【0045】

図5Aは、状態変数フィルタの信号インターフェースを示すブロック図であり、データ信号平面と制御平面との2種類の平面を描いている。このインターフェースは、図1～図4を参照しながら説明したような状態変数フィルタのインターフェースとして実施されてもよい。制御平面は、信号平面との相互作用を介してフィルタをチューニングする。このようにして、バイカッドのカスケード構造(バイカッドフィルタ)をチューニングすることができる。この制御平面は、バイカッドの動作周波数範囲よりも低い周波数(例えば、100MHzなど)で動作し得る。この制御平面は、バイカッドの性能を向上させる測定メカニズムを提供する。具体的に述べると、この測定メカニズムは、バイカッドのサブコンポーネント(バイカッドの構成要素)(例えば、ロスパッド、積分器など)のゲイン及び位相の精密な設定を可能にすることにより、当該バイカッドの性能を向上させる。さらに具体的に述べると、測定結果が制御平面からADC(A/D変換器)に出力され、これがバイカッド内の回路値を変更して精度を高めるのに利用される。バイカッド内の数値の読み書きにはシリアルペリフェラルインターフェース(SPI)が使用される。バイカッドのSPIは、マスタであるマイクロプロセッサ/デジタル信号プロセッサ(μP/DS)に対するスレーブとして扱われ得る。

10

20

30

40

【0046】

バイカッド内には、回路値を変更するためのSPIアドレスが割り当てられている。一例として、8次の帯域通過フィルタの場合:

【0047】

a) フィルタに含まれる4個のバイカッドおよび校正用の1個のテストバイカッドからなる5個のバイカッドのそれぞれに設けられた、5つのSPIインターフェース;

b) 供給および測定用に組み合わされた、3つのSPIインターフェース(信号の供給と測定値の取得とを担う、制御平面内のバス);ならびに

c) モード特定用の1個のSPIインターフェース;

の合計29個のSPIインターフェースを有する。

【0048】

図5Bのブロック図および図5Cのブロック図には、例示的なバイカッド回路での、データ接続部およびテストポイント接続部が描かれている。これらの接続部は、図6～図16Bを参照しながら後述する例示的なチューニング手順で利用される。具体的に述べると、図5Bには、バイカッドに対するSPIデータ割当ての一例が描かれている。図5Cには、バイカッドの動作を測定するためのテストポイント接続部が描かれている。以下の表1～表5に、図5B及び図5Cのデータ接続部およびテストポイント接続部のレジストリ・アドレス構成の一例をまとめた:

【0049】

【表1-1】

表1：S P I アドレス割当て

| Reg<br>(レジスタ) | SPI レジスタアドレスビット |    |    |    |    |    |    | データビット及び説明   |

|---------------|-----------------|----|----|----|----|----|----|--------------|

|               | A6              | A5 | A4 | A3 | A2 | A1 | A0 |              |

| BQ1_1         | 0               | 0  | 0  | 0  | 0  | 0  | 0  | バイカッド1 レジスタ1 |

| BQ1_2         | 0               | 0  | 0  | 0  | 0  | 0  | 1  | バイカッド1 レジスタ2 |

| BQ1_3         | 0               | 0  | 0  | 0  | 0  | 1  | 0  | バイカッド1 レジスタ3 |

| BQ1_4         | 0               | 0  | 0  | 0  | 0  | 1  | 1  | バイカッド1 レジスタ4 |

| BQ1_5         | 0               | 0  | 0  | 0  | 1  | 0  | 0  | バイカッド1 レジスタ5 |

|               |                 |    |    |    |    |    |    |              |

| BQ2_1         | 0               | 0  | 0  | 1  | 0  | 0  | 0  | バイカッド2 レジスタ1 |

| BQ2_2         | 0               | 0  | 0  | 1  | 0  | 0  | 1  | バイカッド2 レジスタ2 |

| BQ2_3         | 0               | 0  | 0  | 1  | 0  | 1  | 0  | バイカッド2 レジスタ3 |

| BQ2_4         | 0               | 0  | 0  | 1  | 0  | 1  | 1  | バイカッド2 レジスタ4 |

| BQ2_5         | 0               | 0  | 0  | 1  | 1  | 0  | 0  | バイカッド2 レジスタ5 |

|               |                 |    |    |    |    |    |    |              |

| BQ3_1         | 0               | 0  | 1  | 0  | 0  | 0  | 0  | バイカッド3 レジスタ1 |

| BQ3_2         | 0               | 0  | 1  | 0  | 0  | 0  | 1  | バイカッド3 レジスタ2 |

| BQ3_3         | 0               | 0  | 1  | 0  | 0  | 1  | 0  | バイカッド3 レジスタ3 |

| BQ3_4         | 0               | 0  | 1  | 0  | 0  | 1  | 1  | バイカッド3 レジスタ4 |

| BQ3_5         | 0               | 0  | 1  | 0  | 1  | 0  | 0  | バイカッド3 レジスタ5 |

|               |                 |    |    |    |    |    |    |              |

10

20

30

40

【0050】

【表1-2】

表1 (続き) SPIアドレス割当て

| Reg<br>(レジスタ)      | SPI レジスタアドレスビット |    |    |    |    |    |    | データビット及び説明                            |

|--------------------|-----------------|----|----|----|----|----|----|---------------------------------------|

|                    | A6              | A5 | A4 | A3 | A2 | A1 | A0 |                                       |

| BQ4_1              | 0               | 0  | 1  | 1  | 0  | 0  | 0  | バイカッド4 レジスタ 1                         |

| BQ4_2              | 0               | 0  | 1  | 1  | 0  | 0  | 1  | バイカッド4 レジスタ 2                         |

| BQ4_3              | 0               | 0  | 1  | 1  | 0  | 1  | 0  | バイカッド4 レジスタ 3                         |

| BQ4_4              | 0               | 0  | 1  | 1  | 0  | 1  | 1  | バイカッド4 レジスタ 4                         |

| BQ4_5              | 0               | 0  | 1  | 1  | 1  | 0  | 0  | バイカッド4 レジスタ 5                         |

|                    |                 |    |    |    |    |    |    |                                       |

| BQ5_1              | 0               | 1  | 0  | 0  | 0  | 0  | 0  | テストバイカッド レジスタ 1                       |

| BQ5_2              | 0               | 1  | 0  | 0  | 0  | 0  | 1  | テストバイカッド レジスタ 2                       |

| BQ5_3              | 0               | 1  | 0  | 0  | 0  | 1  | 0  | テストバイカッド レジスタ 3                       |

| BQ5_4              | 0               | 1  | 0  | 0  | 0  | 1  | 1  | テストバイカッド レジスタ 4                       |

| BQ5_5              | 0               | 1  | 0  | 0  | 1  | 0  | 0  | テストバイカッド レジスタ 5                       |

|                    |                 |    |    |    |    |    |    |                                       |

| Mode ID<br>(モード特定) | 0               | 1  | 1  | 1  | 0  | 0  | 0  | モードを特定 (25 個のデータビットが、反映、変更などの情報を提供する) |

|                    |                 |    |    |    |    |    |    |                                       |

| MTR4               | 0               | 1  | 1  | 1  | 1  | 0  | 0  | メーターレジスタ 4                            |

|                    |                 |    |    |    |    |    |    |                                       |

| MTR6               | 0               | 1  | 1  | 1  | 1  | 1  | 0  | メーターレジスタ 6                            |

| MTR7               | 0               | 1  | 1  | 1  | 1  | 1  | 1  | メーターレジスタ 7                            |

【0051】

10

20

30

40

【表2】

表2：バイカッド用のS P Iデータ割当て

(アドレスビット：L S B = 0～M S B = 2 4)

| SPI               | データビット及び割当て                | データビット及び割当て                     | データビット及び割当て                | データビット及び割当て             | データビット及び割当て |

|-------------------|----------------------------|---------------------------------|----------------------------|-------------------------|-------------|

| BQ <sub>n_1</sub> | <0:11> = V <sub>CR1</sub>  | <12:23> = V <sub>CapA</sub>     | <24> = 未割当                 |                         |             |

| BQ <sub>n_2</sub> | <0:11> = V <sub>CC1</sub>  | <12:14> = V <sub>i1_SW</sub>    | <15:22> = V <sub>b</sub> * | <23> = V <sub>cip</sub> | <24> = 未割当  |

| BQ <sub>n_3</sub> | <0:2> = V <sub>i2_SW</sub> | <3:6> = V <sub>ctp1,2,3,4</sub> | <7:24> = 未割当               |                         |             |

| BQ <sub>n_4</sub> | <0:11> = V <sub>CR2</sub>  | <12:23> = V <sub>c_al</sub>     | <24> = 未割当                 |                         |             |

| BQ <sub>n_5</sub> | <0:11> = V <sub>LP</sub>   | <12:23> = V <sub>CC2</sub>      | <24> = 未割当                 |                         |             |

10

20

30

【0 0 5 2】

【表3】

表3：供給／測定用のS P Iデータ割当て

(アドレスビット：L S B = 0～M S B = 2 4)

| SPI              | データビット及び割当て               | データビット及び割当て               | データビット及び割当て   |

|------------------|---------------------------|---------------------------|---------------|

| MTR <sub>4</sub> | <0:11> = B <sub>s90</sub> | <12> = sel90              | <13:24> = 未割当 |

| MTR <sub>6</sub> | <0:11> = B <sub>m2</sub>  | <12:23> = B <sub>m1</sub> | <24> = selbyp |

| MTR <sub>7</sub> | <0:11> = B <sub>s</sub>   | <12> = seltbq             | <13:24> = 未割当 |

40

【0 0 5 3】

【表4】

表4 :  $V_b$ 制御

| 電圧/<br>スイッチ | SPI ビット          | アクティブ | 接続        | 機能                      |

|-------------|------------------|-------|-----------|-------------------------|

| $V_{b1}$    | $BQ_{n\_2} <18>$ | High  | TP1 に VM1 | 第1の積分器の入力               |

| $V_{b2}$    | $BQ_{n\_2} <17>$ | High  | TP1 に VM2 |                         |

| $V_{b3}$    | $BQ_{n\_2} <16>$ | High  | TP2 に VM1 | 第1の積分器の出力、<br>第2の積分器の入力 |

| $V_{b4}$    | $BQ_{n\_2} <15>$ | High  | TP2 に VM2 |                         |

| $V_{b5}$    | $BQ_{n\_2} <22>$ | High  | TP3 に VM1 | 第2の積分器の出力               |

| $V_{b6}$    | $BQ_{n\_2} <21>$ | High  | TP3 に VM2 |                         |

| $V_{b7}$    | $BQ_{n\_2} <20>$ | High  | TP4 に VM1 | ロスパッドの出力                |

| $V_{b8}$    | $BQ_{n\_2} <19>$ | High  | TP4 に VM2 |                         |

10

20

【0054】

【表5】

表5：スイッチおよび接続

| スイッチ       | SPI<br>ビット   | アクティブ        | 接続および機能                                                                                   |

|------------|--------------|--------------|-------------------------------------------------------------------------------------------|

| Vi1_sw[12] | BQ2<br><12>  | Low          | 第1の積分器ブロックにおける3個の粗チューニング用サブ積分器のうち、第1のサブ積分器を選択                                             |

| Vi1_sw[13] | BQ2<br><13>  | Low          | 第1の積分器ブロックにおける3個の粗チューニング用サブ積分器のうち、第2のサブ積分器を選択                                             |

| Vi1_sw[14] | BQ2<br><14>  | Low          | 第1の積分器ブロックにおける3個の粗チューニング用サブ積分器のうち、第3のサブ積分器を選択                                             |

| Vi2_sw[0]  | BQ3<br><0>   | Low          | 第2の積分器ブロックにおける3個の粗チューニング用サブ積分器のうち、第1のサブ積分器を選択                                             |

| Vi2_sw[1]  | BQ3<br><1>   | Low          | 第2の積分器ブロックにおける3個の粗チューニング用サブ積分器のうち、第2のサブ積分器を選択                                             |

| Vi2_sw[2]  | BQ3<br><2>   | Low          | 第2の積分器ブロックにおける3個の粗チューニング用サブ積分器のうち、第3のサブ積分器を選択                                             |

| Vcip       | BQ2<br><23>  | Low          | 制御平面からバイカッドに100MHz源を供給                                                                    |

| Vctp1      | BQ3<br><3>   | Low          | 各バイカッドの第1のテストポイントを選択                                                                      |

| Vctp2      | BQ3<br><4>   | Low          | 各バイカッドの第2のテストポイントを選択                                                                      |

| Vctp3      | BQ3<br><5>   | Low          | 各バイカッドの第3のテストポイントを選択                                                                      |

| Vctp4      | BQ3<br><6>   | Low          | 各バイカッドの第4のテストポイントを選択                                                                      |

| sel90      | MTR4<br><12> | High/<br>Low | 基準 (100 MHz 及び 90°) と VM2 (制御平面での測定用) とから1つ選択 (High = 基準 (100 MHz 及び 90°) 、 Low = VM2)    |

| Seltbq     | MTR7<br><12> | High/<br>Low | テストバイカッド出力の (制御平面での) 測定種類の選択 (High = TBQ <sup>2</sup> , Low = (TBQ - 3 dB) <sup>2</sup> ) |

| Selbyp     | MTR6<br><24> | High/<br>Low | 100 MHz 経路とテストバイカッド出力 (制御平面での測定用) とから1つ選択 (High = TBQ, Low = 100 MHz 経路)                  |

【0055】

一例として、バイカッド回路をチューニングするために接続されたSPIは、40MHzの周波数で動作し得る。シリアル高速I/Oインターフェースを用いた場合、制御平面は、最大で20Gbpsの速度で動作し得る。積分器およびロスパッドのセットアップ(設定)には、32ビットのワード(7ビットのアドレスレジスタおよび25ビットのデ-

10

20

30

40

50

タレジスタ)が使用され得る。一例である8次の帯域通過フィルタは、直列に接続された4個のバイカッドで構成され、各バイカッドは、2個の積分器および1個のロスパッドを有する。総セットアップ時間は、セットアップ・チューニング手順の具体的な内容によって変わる。

【0056】

[チューニング手順]

バイカッド回路をチューニングする手順を以下に説明する：

【0057】

a) 従来からの手法を用いて、所望の伝達関数を設計する。具体的に述べると、帯域通過フィルタを一例に挙げるならば、フィルタの種類、次数、中心周波数、帯域幅および通過帯域リップルを決定する。

10

【0058】

b) 前記伝達関数を、各バイカッド部分に因数分解する。8次の帯域通過フィルタを一例に挙げるならば、そのような因数分解は、以下のかたちを取ることになる：

【0059】

【数5】

$$\prod_{n=1}^4 \frac{k_n \frac{w_{r_n}}{Q_n} s}{s^2 + \frac{w_{r_n}}{Q_n} s + {w_{r_n}}^2}$$

20

【0060】

c) 「n」個のバイカッドのそれぞれについて、係数パラメータを決定する。上記の式において、係数パラメータはk、w<sub>r</sub>およびQである。

【0061】

d) 決定した係数パラメータを、バイカッドフィルタ回路で実現される前記伝達関数にマッピングする。先ほどの8次の帯域通過フィルタの例において、そのようなマッピングは、以下のかたちを取り得る：

30

【0062】

【数6】

$$\prod_{n=1}^4 \frac{L_n G_{1n} s}{s^2 + a_{1n} G_{1n} s + G_{1n} G_{2n}}$$

30

【0063】

e) 各バイカッドに、チューニングを実行する。以下では、図6を参照しながらチューニング手順の一例を説明する。図6の各ステップの詳細については、図7～図11を参照されたい。

40

【0064】

図6は、バイカッド回路を、一例として8次の帯域通過フィルタの構成にチューニングする方法を示す状態遷移図である。図示の手順は、当該フィルタを構成するように直列に接続された4個のバイカッドのそれぞれに対して、順次実行され得る。これ以外のフィルタの構成についても、バイカッドのサブコンポーネント(例えば、ロスパッド、積分器など)の位相および/またはゲインの精度をチューニングする際に、これと同様の手順を実行することができる。具体的な手順は、以下のとおりである：

50

## 【0065】

- 1)  $L_n = k_n / Q_n$  に設定する;

- 2)  $G_1 = G_2 = w_{rn}$  に設定する;

- 3)  $a_1 = 1 / Q_n$  に設定する;

- 4) 100 MHz での目標のゲインを、 $G_{100\text{MHz}} = 20 \log_{10}(w_{rn} / 2)$  (100 MHz) と決定する;

- 5) 100 MHz での目標の位相を -89° に設定する;

- 6) セットアップ: 乗算器およびその他のコンポーネントを校正する;

- 7) 前記  $a_1$  を制御するロスパッドをチューニングする;

- 8) 第2の積分器の位相をチューニングする;

- 9) 第1の積分器の位相をチューニングする;

- 10) 第2の積分器のゲインをチューニングする;

- 11) 第1の積分器のゲインをチューニングする。

10

## 【0066】

以下では、上記ステップ7)~11) (すなわち、ロスパッドのチューニングならびに第1および第2の積分器の位相 / ゲインのチューニング) の詳細について、図7~図11を参照しながら説明する。

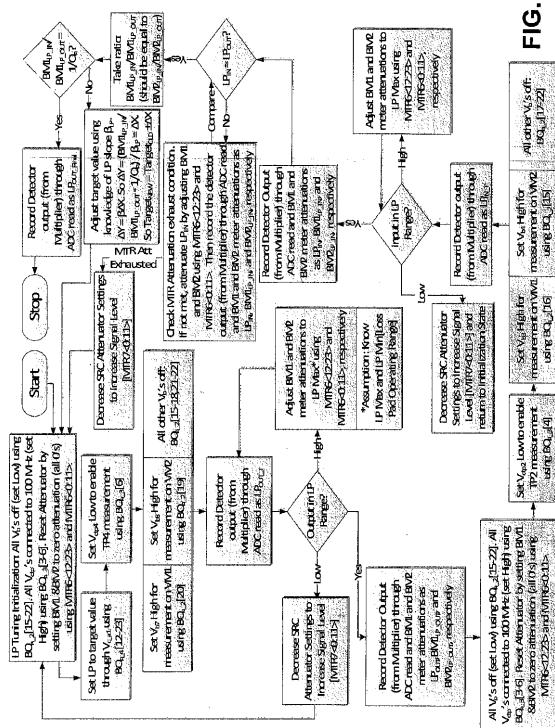

## 【0067】

図7は、図6のフィルタチューニング手順のうち、ロスパッドをチューニングするプロセスのフロー図である。

20

## 【0068】

1) LP (ロスパッド) チューニング初期化:  $BQ_n_2$  [15~22] により、全ての  $V_b$  をオフにする (Low に設定する)。  $BQ_n_3$  [3~6] により、全ての  $V_{ctp}$  を 100 MHz に接続する (High に設定する)。  $MTR6 < 12 : 23 >$  によって BM1 を減衰ゼロに設定し、かつ、  $MTR6 < 0 : 11 >$  によって BM2 を減衰ゼロに設定する (全て 0 にする) ことにより、減衰器をリセットする;

2)  $BQ_n_4$  [12~23] により、 $V_{cta_1}$  を介して、LP を目標の数値に設定する;

3)  $BQ_n_3$  [6] により、 $V_{ctp_4}$  を Low に設定することによって、第4の TP (テストポイント) の測定を許可する;

4)  $BQ_n_2$  [20] により、 $V_{b_7}$  を High に設定することによって、 VM1 による測定を行う;

5)  $BQ_n_2$  [19] により、 $V_{b_8}$  を High に設定することによって、 VM2 による測定を行う;

6) それ以外の  $V_b$  については、  $BQ_n_2$  [15~18, 21 および 22] により、どれもオフを維持する;

7) (乗算器からの) 検出器の出力を、ADC (A/D 変換器) 読取により、  $LP_{out\_T}$  として記録する;

8) 出力に応じて適宜調節を行う。出力が低ければ、  $MTR7 < 0 : 11 >$  により、 SRC 減衰器設定を減少させて、信号レベルを増加させる。出力が高ければ、  $MTR6 < 12 : 23 >$  によって BM1 メーター減衰を LP の Max \* に調節し、かつ、  $MTR6 < 0 : 11 >$  によって BM2 メーター減衰を LP の Max \* に調節する;

9) (乗算器からの) 検出器の出力を、ADC (A/D 変換器) 読取により、  $LP_{out\_T}$  として記録し、かつ、 BM1 メーター減衰および BM2 メーター減衰を、それぞれ BM1 LP\_out\_T, BM2 LP\_out\_T として記録する;

10)  $BQ_n_2$  [15~22] により、全ての  $V_b$  をオフにする (Low に設定する)。  $BQ_n_3$  [3~6] により、全ての  $V_{ctp}$  を 100 MHz に接続する (High に設定する)。  $MTR6 < 12 : 23 >$  によって BM1 を減衰ゼロに設定し、かつ、  $MTR6 < 0 : 11 >$  によって BM2 を減衰ゼロに設定する (全て 0 にする) ことにより、減衰器をリセットする;

40

50

11)  $BQ_{n\_3}$  [4] により、 $V_{c\_t\_p\_2}$  を Low に設定することによって、第 2 の TP の測定を許可する；

12)  $BQ_{n\_2}$  [16] により、 $V_{b\_3}$  を High に設定することによって、VM1 による測定を行う；

13)  $BQ_{n\_2}$  [15] により、 $V_{b\_4}$  を High に設定することによって、VM2 による測定を行う；

14) それ以外の  $V_b$  については、 $BQ_{n\_2}$  [17 ~ 22] により、どれもオフを維持する；

15) (乗算器からの) 検出器の出力を、ADC 読取により、 $LP_{IN\_T}$  として記録する；

16) 入力の測定値に応じて適宜調節を行う。入力が高ければ、 $MTR6 < 12 : 23 >$  によって BM1 メーター減衰を LP の Max に調節し、かつ、 $MTR6 < 0 : 11 >$  によって BM2 メーター減衰を LP の Max に調節する。入力が低ければ、 $MTR7 < 0 : 11 >$  により、SRC 減衰器設定を減少させて、信号レベルを増加させた後、初期化状態に戻る；

17) (乗算器からの) 検出器の出力を、ADC 読取により、 $LP_{IN}$  として記録し、かつ、BM1 メーター減衰および BM2 メーター減衰を、それぞれ  $BM1_{LP\_IN}$ ,  $BM2_{LP\_IN}$  として記録する；

18)  $LP_{IN}$   $LP_{OUT}$  である？ この確認の結果が否定である場合、MTR 減衰限界状態 (exhaust condition) を確認する。この状態に該当しなければ、 $MTR6 < 12 : 23 >$  および  $MTR6 < 0 : 11 >$  によって BM1 および BM2 をそれぞれ調節することにより、 $LP_{IN}$  を減衰させる。そして、(乗算器からの) 検出器の出力を、ADC 読取により、 $LP_{IN}$  として記録し、かつ、BM1 メーター減衰および BM2 メーター減衰を、それぞれ  $BM1_{LP\_IN}$ ,  $BM2_{LP\_IN}$  として記録する。 $LP_{IN}$   $LP_{OUT}$  となるまで、比較・調節を続ける；

19)  $BM1_{LP\_IN}$  /  $BM1_{LP\_OUT}$  の比を算出する ( $BM2_{LP\_IN}$  /  $BM2_{LP\_OUT}$  と等しくなるべきである)；

20)  $BM1_{LP\_IN}$  /  $BM1_{LP\_OUT} = 1 / Q_n$  である？ この確認の結果が否定である場合、LP の傾き： $LP$  の知識を用いて、目標値を調節する。 $Y = X$  とすると、 $Y = (BM1_{LP\_IN} / BM1_{LP\_OUT} - 1 / Q_n) / LP = X$  なので、目標値<sub>新</sub> = 目標値<sub>旧</sub> ± X となる。 $BM1_{LP\_IN}$  /  $BM1_{LP\_OUT} = 1 / Q_n$  となるまで、1) ~ 20) までのステップを繰り返す；

21) (乗算器からの) 検出器の出力を、ADC 読取により、 $LP_{OUT\_final}$  として記録する。

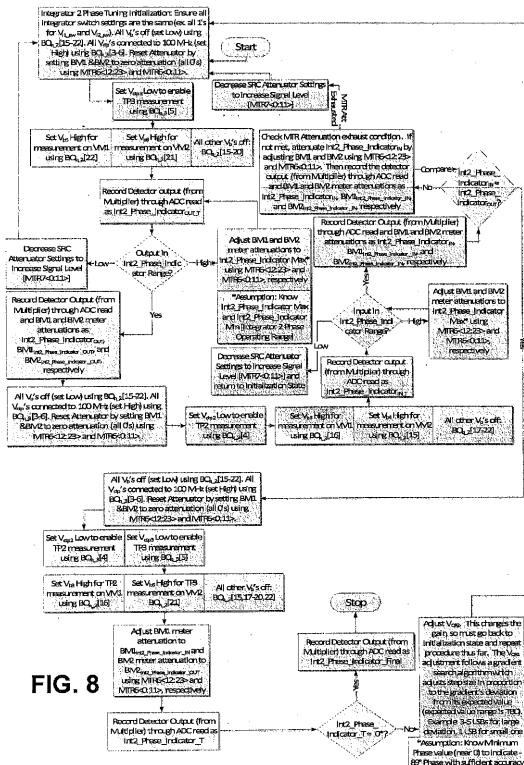

### 【0069】

図 8 は、図 6 のフィルタチューニング手順のうち、第 2 の積分器の位相をチューニングするプロセスのフロー図である。以下では、第 2 の積分器の位相のチューニングを説明する：

### 【0070】

1) 第 2 の積分器の位相のチューニング初期化：積分器の全てのスイッチ設定が同じであることを確認する（例えば、 $V_{i1\_sw}$  および  $V_{i2\_sw}$  がどれも 1 であることを確認する）。 $BQ_{n\_2}$  [15 ~ 22] により、全ての  $V_b$  をオフにする（Low に設定する）。 $BQ_{n\_3}$  [3 ~ 6] により、全ての  $V_{c\_t\_p}$  を 100 MHz に接続する（High に設定する）。 $MTR6 < 12 : 23 >$  によって BM1 を減衰ゼロに設定し、かつ、 $MTR6 < 0 : 11 >$  によって BM2 を減衰ゼロに設定する（全て 0 にする）ことにより、減衰器をリセットする；

2)  $BQ_{n\_3}$  [5] により、 $V_{c\_t\_p\_3}$  を Low に設定することによって、第 3 の TP の測定を許可する；

3)  $BQ_{n\_2}$  [22] により、 $V_{b\_5}$  を High に設定することによって、VM1 による測定を行う；

10

20

30

40

50

4)  $BQ_{n\_2}[21]$  により、 $V_{b_6}$  を  $High$  に設定することによって、 $VM2$  による測定を行う；

5) それ以外の  $V_b$  については、 $BQ_{n\_2}[15 \sim 20]$  により、どれもオフを維持する；

6) (乗算器からの) 検出器の出力を、ADC 読取により、 $Int2\_Phase\_Indicator_{out\_T}$  として記録する；

7) 出力が  $Int2\_Phase\_Indicator$  の範囲内である？ 出力が高ければ、 $MTR6 < 12 : 23 >$  によって  $BM1$  メーター減衰を  $Int2\_Phase\_Indicator$  の  $Max^*$  に調節し、かつ、 $MTR6 < 0 : 11 >$  によって  $BM2$  メーター減衰を  $Int2\_Phase\_Indicator$  の  $Max^*$  に調節する。出力が低ければ、 $MTR7 < 0 : 11 >$  により、SRC 減衰器設定を減少させて、信号レベルを増加させる；

8) (乗算器からの) 検出器の出力を、ADC 読取により、 $Int2\_Phase\_Indicator_{out}$  として記録し、かつ、 $BM1$  メーター減衰および  $BM2$  メーター減衰を、それぞれ  $BM1\_Int2\_Phase\_Indicator\_out$ ,  $BM2\_Int2\_Phase\_Indicator\_out$  として記録する；

9)  $BQ_{n\_2}[15 \sim 22]$  により、全ての  $V_b$  をオフにする ( $Low$  に設定する)。 $BQ_{n\_3}[3 \sim 6]$  により、全ての  $V_{ctp}$  を  $100MHz$  に接続する ( $High$  に設定する)。 $MTR6 < 12 : 23 >$  によって  $BM1$  を減衰ゼロに設定し、かつ、 $MTR6 < 0 : 11 >$  によって  $BM2$  を減衰ゼロに設定する (全て 0 にする) ことにより、減衰器をリセットする；

10)  $BQ_{n\_3}[4]$  により、 $V_{ctp_2}$  を  $Low$  に設定することによって、第 2 の TP の測定を許可する；

11)  $BQ_{n\_2}[16]$  により、 $V_{b_3}$  を  $High$  に設定することによって、 $VM1$  による測定を行う；

12)  $BQ_{n\_2}[15]$  により、 $V_{b_4}$  を  $High$  に設定することによって、 $VM2$  による測定を行う；

13) それ以外の  $V_b$  については、 $BQ_{n\_2}[17 \sim 22]$  により、どれもオフを維持する；

14) (乗算器からの) 検出器の出力を、ADC 読取により、 $Int2\_Phase\_Indicator_{IN\_T}$  として記録する；

15) 入力が  $Int2\_Phase\_Indicator$  の範囲内である？ 入力が低ければ、 $MTR7 < 0 : 11 >$  により、SRC 減衰器設定を減少させて、信号レベルを増加させた後、初期化状態に戻る。入力が高ければ、 $MTR6 < 12 : 23 >$  によって  $BM1$  メーター減衰を  $Int2\_Phase\_Indicator$  の  $Max^*$  に調節し、かつ、 $MTR6 < 0 : 11 >$  によって  $BM2$  メーター減衰を  $Int2\_Phase\_Indicator$  の  $Max^*$  に調節する；

16) (乗算器からの) 検出器の出力を、ADC 読取により、 $Int2\_Phase\_Indicator_{IN}$  として記録し、かつ、 $BM1$  メーター減衰および  $BM2$  メーター減衰を、それぞれ  $BM1\_Int2\_Phase\_Indicator\_IN$ ,  $BM2\_Int2\_Phase\_Indicator\_IN$  として記録する；

17)  $Int2\_Phase\_Indicator_{IN}$   $Int2\_Phase\_Indicator_{out}$  である？ この確認の結果が否定である場合、 $MTR$  減衰限界状態を確認する。この状態に該当しなければ、 $MTR6 < 12 : 23 >$  および  $MTR6 < 0 : 11 >$  によって  $BM1$  および  $BM2$  をそれぞれ調節することにより、 $Int2\_Phase\_Indicator_{IN}$  を減衰させる。そして、(乗算器からの) 検出器の出力を、ADC 読取により、 $Int2\_Phase\_Indicator_{IN}$  として記録し、かつ、 $BM1$  メーター減衰および  $BM2$  メーター減衰を、それぞれ  $BM1\_Int2\_Phase\_Indicator\_IN$ ,  $BM2\_Int2\_Phase\_Indicator\_IN$  として記録する。 $MTR7 < 0 : 11 >$  により、SRC 減衰器設定を減少させて、信号

10

20

30

40

50

レベルを増加させる。1) ~ 17)までのステップを繰り返す；

18) B Q<sub>n</sub>\_2 [15 ~ 22]により、全てのV<sub>b</sub>をオフにする(Lowに設定する)。B Q<sub>n</sub>\_3 [3 ~ 6]により、全てのV<sub>c<sub>t<sub>p</sub></sub></sub>を100MHzに接続する(Highに設定する)。MTR6 <12:23>によってBM1を減衰ゼロに設定し、かつ、MTR6 <0:11>によってBM2を減衰ゼロに設定する(全て0にする)ことにより、減衰器をリセットする；

19) B Q<sub>n</sub>\_3 [4]により、V<sub>c<sub>t<sub>p</sub></sub></sub>をLowに設定することによって、第2のTPの測定を許可する；

20) B Q<sub>n</sub>\_3 [5]により、V<sub>c<sub>t<sub>p</sub></sub></sub>をLowに設定することによって、第3のTPの測定を許可する；

21) B Q<sub>n</sub>\_2 [16]により、V<sub>b</sub>をHighに設定することによって、VM1による第2のTPの測定を行う；

22) B Q<sub>n</sub>\_2 [21]により、V<sub>b</sub>をHighに設定することによって、VM2による第3のTPの測定を行う；

23) それ以外のV<sub>b</sub>については、B Q<sub>n</sub>\_2 [15、17 ~ 20および22]により、どれもオフを維持する；

24) MTR6 <12:23>によってBM1メーター減衰をBM1\_In<sub>t</sub>2\_Phase<sub>se</sub>\_Indicator\_INに調節し、かつ、MTR6 <0:11>によってBM2メーター減衰をBM2\_In<sub>t</sub>2\_Phase<sub>se</sub>\_Indicator\_OUTに設定する；

25) (乗算器からの)検出器の出力を、ADC読取により、In<sub>t</sub>2\_Phase<sub>se</sub>\_Indicator\_Tとして記録する；

26) In<sub>t</sub>2\_Phase<sub>se</sub>\_Indicator\_T 0\*である？この確認の結果が否定である場合、V<sub>c<sub>R</sub></sub>の調節を行う。V<sub>c<sub>R</sub></sub>を調節するとゲインが変化するので、初期化状態に戻り、これまでのステップを繰り返す必要がある。V<sub>c<sub>R</sub></sub>の調節は、勾配探索アルゴリズムに従って行われる。具体的に述べると、このアルゴリズムは、勾配予測値からの誤差(勾配予測値の範囲については適宜決定する)に比例してステップサイズを調節する。例えば、ステップサイズは、誤差が大きい場合には3 ~ 5の LSB であり、誤差が小さい場合には1の LSB である。1) ~ 26)までのステップを繰り返す；

27) (乗算器からの)検出器の出力を、ADC読取により、In<sub>t</sub>2\_Phase<sub>se</sub>\_Indicator\_Finalとして記録する。

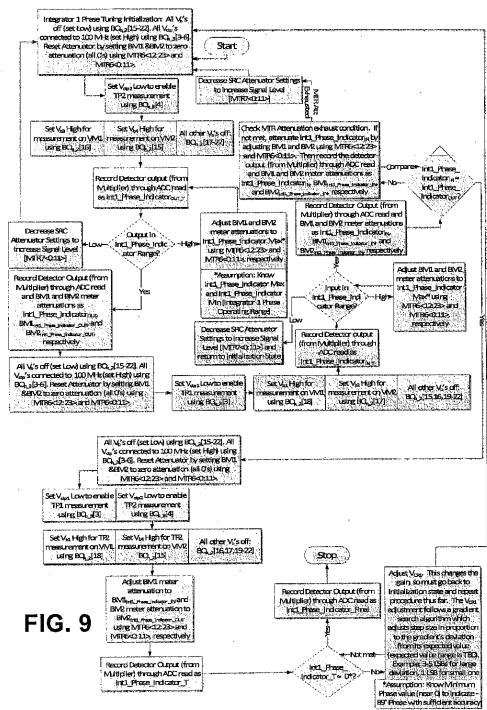

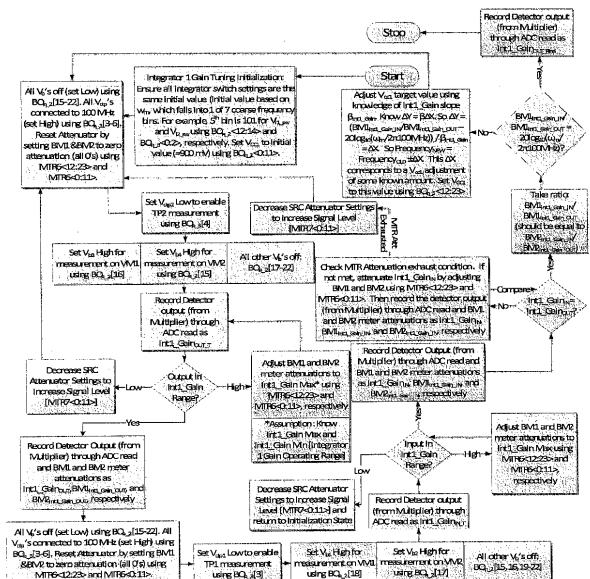

【0071】

図9は、図6のフィルタチューニング手順のうち、第1の積分器の位相をチューニングするプロセスのフロー図である。

【0072】

以下では、第1の積分器の位相のチューニングを説明する：

【0073】

1) 第1の積分器の位相のチューニング初期化：B Q<sub>n</sub>\_2 [15 ~ 22]により、全てのV<sub>b</sub>をオフにする(Lowに設定する)。B Q<sub>n</sub>\_3 [3 ~ 6]により、全てのV<sub>c<sub>t<sub>p</sub></sub></sub>を100MHzに接続する(Highに設定する)。MTR6 <12:23>によってBM1を減衰ゼロに設定し、かつ、MTR6 <0:11>によってBM2を減衰ゼロに設定する(全て0にする)ことにより、減衰器をリセットする；

2) B Q<sub>n</sub>\_3 [4]により、V<sub>c<sub>t<sub>p</sub></sub></sub>をLowに設定することによって、第2のTPの測定を許可する；

3) B Q<sub>n</sub>\_2 [16]により、V<sub>b</sub>をHighに設定することによって、VM1による測定を行う。B Q<sub>n</sub>\_2 [15]により、V<sub>b</sub>をHighに設定することによって、VM2による測定を行う。それ以外のV<sub>b</sub>については、B Q<sub>n</sub>\_2 [17 ~ 22]により、どれもオフを維持する；

4) (乗算器からの)検出器の出力を、ADC読取により、In<sub>t</sub>1\_Phase<sub>se</sub>\_Indicator\_out\_Tとして記録する；

5) 出力がIn<sub>t</sub>1\_Phase<sub>se</sub>\_Indicatorの範囲内である？出力が高け

10

20

30

40

50

れば、MTR6<12:23>によってBM1メーター減衰をInt1\_Phase\_IndicatorのMax\*に調節し、かつ、MTR6<0:11>によってBM2メーター減衰をInt1\_Phase\_IndicatorのMax\*に調節する。出力が低ければ、MTR7<0:11>により、SRC減衰器設定を減少させて、信号レベルを増加させた後、1)に戻る；

6) (乗算器からの)検出器の出力を、ADC読取により、Int1\_Phase\_Indicator\_outとして記録し、かつ、BM1メーター減衰およびBM2メーター減衰を、それぞれBM1\_Int1\_Phase\_Indicator\_out, BM2\_Int1\_Phase\_Indicator\_outとして記録する；

7) BQn\_2[15~22]により、全てのV<sub>b</sub>をオフにする(Lowに設定する)。BQn\_3[3~6]により、全てのV<sub>c<sub>tp</sub></sub>を100MHzに接続する(Highに設定する)。MTR6<12:23>によってBM1を減衰ゼロに設定し、かつ、MTR6<0:11>によってBM2を減衰ゼロに設定する(全て0にする)ことにより、減衰器をリセットする；

8) BQn\_3[3]により、V<sub>c<sub>tp</sub></sub>をLowに設定することによって、第1のTPの測定を許可する；

9) BQn\_2[18]により、V<sub>b</sub><sub>1</sub>をHighに設定することによって、VM1による測定を行う。BQn\_2[17]により、V<sub>b</sub><sub>2</sub>をHighに設定することによって、VM2による測定を行う。それ以外のV<sub>b</sub>については、BQn\_2[15, 16および19~22]により、どれもオフを維持する；

10) (乗算器からの)検出器の出力を、ADC読取により、Int1\_Phase\_Indicator\_IN-Tとして記録する；

11) 入力がInt1\_Phase\_Indicatorの範囲内である？入力が高ければ、MTR6<12:23>によってBM1メーター減衰をInt1\_Phase\_IndicatorのMax\*に調節し、かつ、MTR6<0:11>によってBM2メーター減衰をInt1\_Phase\_IndicatorのMax\*に調節し、再試行する。入力が低ければ、MTR7<0:11>により、SRC減衰器設定を減少させて、信号レベルを増加させた後、初期化状態に戻る；

12) (乗算器からの)検出器の出力を、ADC読取により、Int1\_Phase\_Indicator\_INとして記録し、かつ、BM1メーター減衰およびBM2メーター減衰を、それぞれBM1\_Int1\_Phase\_Indicator\_IN, BM2\_Int1\_Phase\_Indicator\_INとして記録する；

13) Int1\_Phase\_Indicator\_IN Int1\_Phase\_Indicator\_outである？この確認の結果が否定である場合、MTR減衰限界状態を確認する。この状態に該当しなければ、MTR6<12:23>およびMTR6<0:11>によってBM1およびBM2をそれぞれ調節することにより、Int1\_Phase\_Indicator\_INを減衰させる。そして、(乗算器からの)検出器の出力を、ADC読取により、Int1\_Phase\_Indicator\_INとして記録し、かつ、BM1メーター減衰およびBM2メーター減衰を、それぞれBM1\_Int1\_Phase\_Indicator\_IN, BM2\_Int1\_Phase\_Indicator\_INとして記録する。MTR7<0:11>により、SRC減衰器設定を減少させて、信号レベルを増加させる。1)に戻る；

14) BQn\_2[15~22]により、全てのV<sub>b</sub>をオフにする(Lowに設定する)。BQn\_3[3~6]により、全てのV<sub>c<sub>tp</sub></sub>を100MHzに接続する(Highに設定する)。MTR6<12:23>によってBM1を減衰ゼロに設定し、かつ、MTR6<0:11>によってBM2を減衰ゼロに設定する(全て0にする)ことにより、減衰器をリセットする；

15) BQn\_3[3]により、V<sub>c<sub>tp</sub></sub>をLowに設定することによって、第1のTPの測定を許可する。BQn\_3[4]により、V<sub>c<sub>tp</sub></sub>をLowに設定することによって、第2のTPの測定を許可する；

10

20

30

40

50

16)  $BQ_{n\_2}$  [18] により、 $V_{b_1}$ をHighに設定することによって、VM1による第2のTPの測定を行う。 $BQ_{n\_2}$  [15] により、 $V_{b_4}$ をHighに設定することによって、VM2による第2のTPの測定を行う。それ以外の $V_b$ については、 $BQ_{n\_2}$  [16、17および19～22] により、どれもオフを維持する；

17) MTR6 <12:23> によって BM1メーター減衰を  $BM1_{Int1\_Phase\_Indicator\_IN}$  に調節し、かつ、MTR6 <0:11> によって BM2メーター減衰を  $BM2_{Int1\_Phase\_Indicator\_OUT}$  に設定する；

18) (乗算器からの) 検出器の出力を、ADC読取により、 $Int1\_Phase\_Indicator\_T$  として記録する；

19)  $Int1\_Phase\_Indicator\_T$  0\* である？ この確認の結果が否定である場合、 $V_{CR1}$  の調節を行う。 $V_{CR1}$  を調節するとゲインが変化するので、初期化状態に戻り、これまでのステップを繰り返す必要がある。 $V_{CR1}$  の調節は、勾配探索アルゴリズムに従って行われる。具体的に述べると、このアルゴリズムは、勾配予測値からの誤差(勾配予測値の範囲については適宜決定する)に比例してステップサイズを調節する。例えば、ステップサイズは、誤差が大きい場合には3～5の LSB であり、誤差が小さい場合には1の LSB である。1) に戻る；

20) (乗算器からの) 検出器の出力を、ADC読取により、 $Int1\_Phase\_Indicator\_Final$  として記録する。

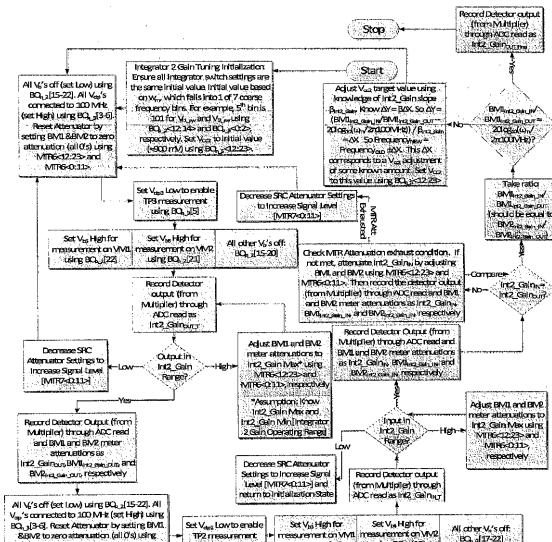

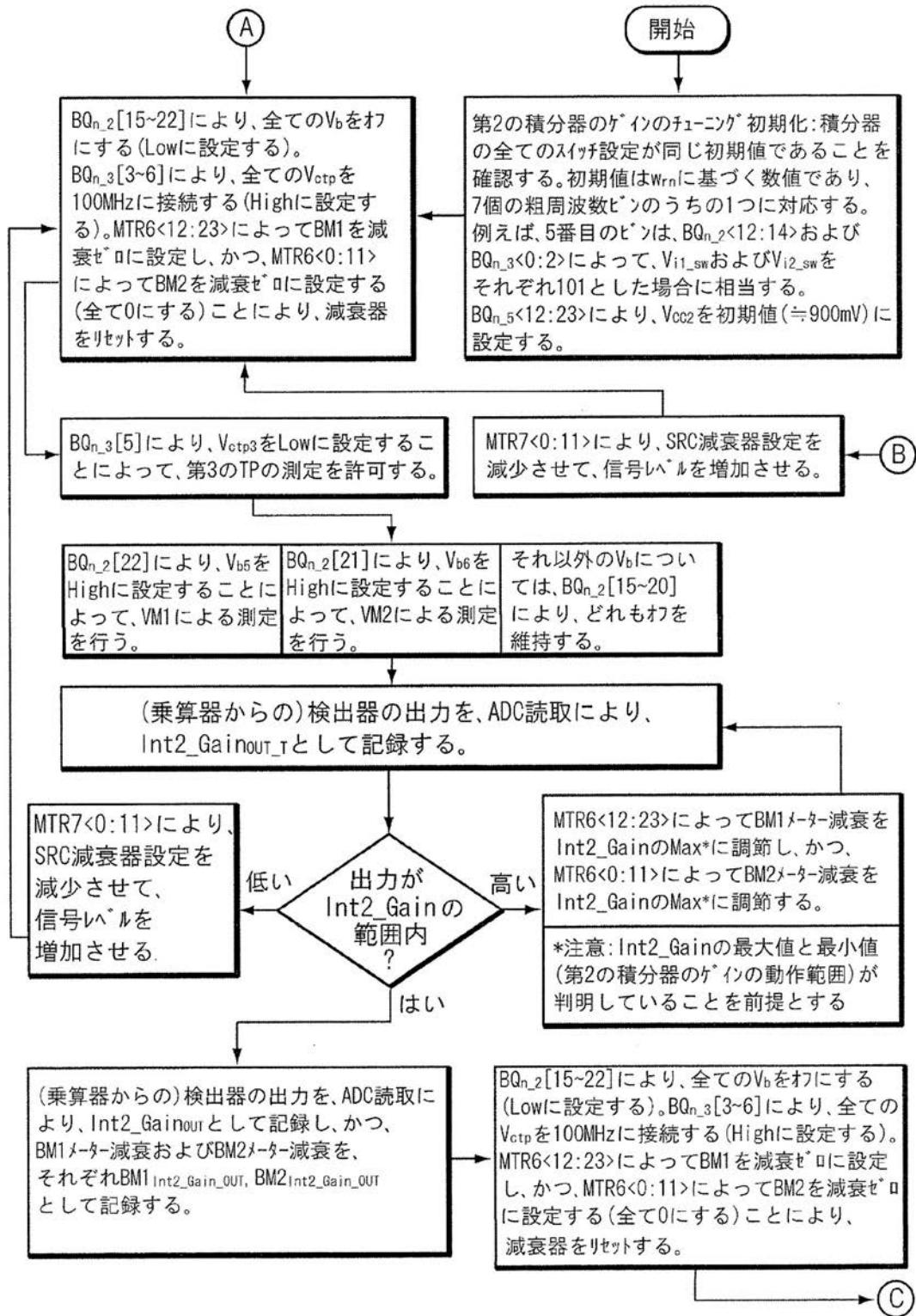

#### 【0074】

図10は、図6のフィルタチューニング手順のうち、第2の積分器のゲインをチューニングするプロセスのフロー図である。

#### 【0075】

以下では、第2の積分器のゲインのチューニングを説明する：

#### 【0076】

1) 第2の積分器のゲインのチューニング初期化：積分器の全てのスイッチ設定が同じ初期値であることを確認する。初期値は  $w_{rn}$  に基づく数値であり、7個の粗周波数BINのうちの1つに対応する。例えば、5番目のBINは、 $BQ_{n\_2}$  <12:14> および  $BQ_{n\_3}$  <0:2> によって、 $V_{i1\_sw}$  および  $V_{i2\_sw}$  をそれぞれ101とした場合に相当する。 $BQ_{n\_5}$  <12:23> により、 $V_{cc2}$  を初期値(900mV)に設定する；

2)  $BQ_{n\_2}$  [15～22] により、全ての $V_b$ をオフにする(Lowに設定する)。 $BQ_{n\_3}$  [3～6] により、全ての $V_{ctp}$ を100MHzに接続する(Highに設定する)。MTR6 <12:23> によって BM1を減衰ゼロに設定し、かつ、MTR6 <0:11> によって BM2を減衰ゼロに設定する(全て0にする)ことにより、減衰器をリセットする；

3)  $BQ_{n\_3}$  [5] により、 $V_{ctp3}$  を Low に設定することによって、第3のTPの測定を許可する；

4)  $BQ_{n\_2}$  [22] により、 $V_{b5}$  を High に設定することによって、VM1による測定を行う。 $BQ_{n\_2}$  [21] により、 $V_{b6}$  を High に設定することによって、VM2による測定を行う。それ以外の $V_b$ については、 $BQ_{n\_2}$  [15～20] により、どれもオフを維持する；

5) (乗算器からの) 検出器の出力を、ADC読取により、 $Int2\_Gain\_out\_T$  として記録する；

6) 出力が  $Int2\_Gain$  の範囲内である？ 出力が低ければ、MTR7 <0:1> により、SRC減衰器設定を減少させて、信号レベルを増加させた後、2) に戻る。出力が高ければ、MTR6 <12:23> によって BM1メーター減衰を  $Int2\_Gain$  の Max\* に調節し、かつ、MTR6 <0:11> によって BM2メーター減衰を  $Int2\_Gain$  の Max\* に調節し、再試行する；

7) (乗算器からの) 検出器の出力を、ADC読取により、 $Int2\_Gain\_out$  として記録し、かつ、BM1メーター減衰およびBM2メーター減衰を、それぞれ BM1

10

20

30

40

50

$I_{nt2\_Gain\_out}$ ,  $BM2_{nt2\_Gain\_out}$  として記録する;

8)  $BQn_2$  [15~22] により、全ての  $V_b$  をオフにする (Low に設定する)。

$BQn_3$  [3~6] により、全ての  $V_{ctp}$  を 100 MHz に接続する (High に設定する)。 $MTR6 < 12 : 23 >$  によって  $BM1$  を減衰ゼロに設定し、かつ、 $MTR6 < 0 : 11 >$  によって  $BM2$  を減衰ゼロに設定する (全て 0 にする) ことにより、減衰器をリセットする;

9)  $BQn_3$  [4] により、 $V_{ctp_2}$  を Low に設定することによって、第 2 の TP の測定を許可する;

10 10)  $BQn_2$  [16] により、 $V_{b_3}$  を High に設定することによって、 $VM1$  による測定を行う。 $BQn_2$  [15] により、 $V_{b_4}$  を High に設定することによって、 $VM2$  による測定を行う。それ以外の  $V_b$  については、 $BQn_2$  [17~22] により、どれもオフを維持する;

11) (乗算器からの) 検出器の出力を、ADC 読取により、 $I_{nt2\_Gain\_IN\_T}$  として記録する;

12) 入力が  $I_{nt2\_Gain}$  の範囲内である? 入力が低ければ、 $MTR7 < 0 : 11 >$  により、SRC 減衰器設定を減少させて、信号レベルを増加させた後、初期化状態に戻る。入力が高ければ、 $MTR6 < 12 : 23 >$  によって  $BM1$  メーター減衰を  $I_{nt2\_Gain}$  の Max に調節し、かつ、 $MTR6 < 0 : 11 >$  によって  $BM2$  メーター減衰を  $I_{nt2\_Gain}$  の Max に調節し、再試行する;

20 13) (乗算器からの) 検出器の出力を、ADC 読取により、 $I_{nt2\_Gain\_IN}$  として記録し、かつ、 $BM1$  メーター減衰および  $BM2$  メーター減衰を、それぞれ  $BM1_{nt2\_Gain\_IN}$ ,  $BM2_{nt2\_Gain\_IN}$  として記録する;

14)  $I_{nt2\_Gain\_IN}$  と  $I_{nt2\_Gain\_OUT}$  である? この確認の結果が否定である場合、 $MTR$  減衰限界状態を確認する。この状態に該当しなければ、 $MTR6 < 12 : 23 >$  および  $MTR6 < 0 : 11 >$  によって  $BM1$  および  $BM2$  をそれぞれ調節することにより、 $I_{nt2\_Gain\_IN}$  を減衰させる。そして、(乗算器からの) 検出器の出力を、ADC 読取により、 $I_{nt2\_Gain\_IN}$  として記録し、かつ、 $BM1$  メーター減衰および  $BM2$  メーター減衰を、それぞれ  $BM1_{nt2\_Gain\_IN}$ ,  $BM2_{nt2\_Gain\_IN}$  として記録し、再試行する [ $MTR$  減衰限界状態であれば、 $MTR7 < 0 : 11 >$  により、SRC 減衰器設定を減少させて、信号レベルを増加させた後、2) に戻る];

15)  $BM1_{nt2\_Gain\_IN} / BM1_{nt2\_Gain\_OUT}$  の比を算出する ( $BM2_{nt2\_Gain\_IN} / BM2_{nt2\_Gain\_OUT}$  と等しくなるべきである);

20 1 16)  $BM1_{nt2\_Gain\_IN} / BM1_{nt2\_Gain\_OUT}$  と  $log_{10}(w_{rn} / 2 (100 \text{ MHz}))$  である? この確認の結果が否定である場合、 $I_{nt2\_Gain}$  の傾き:  $I_{nt2\_Gain}$  の知識を用いて、 $V_{cc2}$  の目標値を調節する。 $Y = X$  とすると、 $Y = (BM1_{nt2\_Gain\_IN} / BM1_{nt2\_Gain\_OUT} - 20 \log_{10}(w_{rn} / 2 (100 \text{ MHz}))) / I_{nt2\_Gain} = X$  なので、周波数<sub>新</sub> = 周波数<sub>旧</sub> ±  $X$  となる。この  $X$  は、既知の所与の  $V_{cc2}$  調節量に対応する。 $BQn_5 < 12 : 23 >$  により、 $V_{cc2}$  をこの数値に設定する;

17) (乗算器からの) 検出器の出力を、ADC 読取により、 $I_{nt2\_Gain\_OUT\_T\_Final}$  として記録する。

【0077】

図 11 は、図 6 のフィルタチューニング手順のうち、第 1 の積分器のゲインをチューニングするプロセスのフロー図である。以下では、第 1 の積分器のゲインのチューニングを説明する:

【0078】

1) 第 1 の積分器のゲインのチューニング初期化: 積分器の全てのスイッチ設定が同じ

10

20

30

40

50

初期値であることを確認する（初期値は  $w_{r_n}$  に基づく数値であり、7個の粗周波数ピンのうちの1つに対応する。例えば、5番目のピンは、 $BQ_{n\_2} < 12 : 14 >$  および  $BQ_{n\_3} < 0 : 2 >$  によって、 $V_{i1\_sw}$  および  $V_{i2\_sw}$  をそれぞれ101とした場合に相当する。 $BQ_{n\_2} < 0 : 11 >$  により、 $V_{cc1}$  を初期値（900mV）に設定する）；

2)  $BQ_{n\_2} [15 \sim 22]$  により、全ての  $V_b$  をオフにする（ $Low$  に設定する）。 $BQ_{n\_3} [3 \sim 6]$  により、全ての  $V_{ctp}$  を 100MHz に接続する（ $High$  に設定する）。 $MTR6 < 12 : 23 >$  によって  $BM1$  を減衰ゼロに設定し、かつ、 $MTR6 < 0 : 11 >$  によって  $BM2$  を減衰ゼロに設定する（全て0にする）ことにより、減衰器をリセットする；

3)  $BQ_{n\_3} [4]$  により、 $V_{ctp2}$  を  $Low$  に設定することによって、第2のTPの測定を許可する；

4)  $BQ_{n\_2} [16]$  により、 $V_{b3}$  を  $High$  に設定することによって、 $VM1$  による測定を行う。 $BQ_{n\_2} [15]$  により、 $V_{b4}$  を  $High$  に設定することによって、 $VM2$  による測定を行う。それ以外の  $V_b$  については、 $BQ_{n\_2} [17 \sim 22]$  により、どれもオフを維持する；

5) (乗算器からの) 検出器の出力を、ADC読取により、 $Int1\_Gain_{out\_T}$  として記録する；

6) 出力が  $Int1\_Gain$  の範囲内である？ 出力が低ければ、 $MTR7 < 0 : 11 >$  により、SRC減衰器設定を減少させて、信号レベルを増加させた後、2) に戻る。出力が高ければ、 $MTR6 < 12 : 23 >$  によって  $BM1$  メーター減衰を  $Int1\_Gain$  の  $Max^*$  に調節し、かつ、 $MTR6 < 0 : 11 >$  によって  $BM2$  メーター減衰を  $Int1\_Gain$  の  $Max^*$  に調節し、再試行する；

7) (乗算器からの) 検出器の出力を、ADC読取により、 $Int1\_Gain_{out\_T}$  として記録し、かつ、 $BM1$  メーター減衰および  $BM2$  メーター減衰を、それぞれ  $BM1_{Int1\_Gain\_out\_T}$ ,  $BM2_{Int1\_Gain\_out\_T}$  として記録する；

8)  $BQ_{n\_2} [15 \sim 22]$  により、全ての  $V_b$  をオフにする（ $Low$  に設定する）。 $BQ_{n\_3} [3 \sim 6]$  により、全ての  $V_{ctp}$  を 100MHz に接続する（ $High$  に設定する）。 $MTR6 < 12 : 23 >$  によって  $BM1$  を減衰ゼロに設定し、かつ、 $MTR6 < 0 : 11 >$  によって  $BM2$  を減衰ゼロに設定する（全て0にする）ことにより、減衰器をリセットする；

9)  $BQ_{n\_3} [3]$  により、 $V_{ctp1}$  を  $Low$  に設定することによって、第1のTPの測定を許可する；

10)  $BQ_{n\_2} [18]$  により、 $V_{b1}$  を  $High$  に設定することによって、 $VM1$  による測定を行う。 $BQ_{n\_2} [17]$  により、 $V_{b2}$  を  $High$  に設定することによって、 $VM2$  による測定を行う。それ以外の  $V_b$  については、 $BQ_{n\_2} [15, 16$  および  $19 \sim 22]$  により、どれもオフを維持する；

11) (乗算器からの) 検出器の出力を、ADC読取により、 $Int1\_Gain_{IN\_T}$  として記録する；

12) 入力が  $Int1\_Gain$  の範囲内である？ 入力が低ければ、 $MTR7 < 0 : 11 >$  により、SRC減衰器設定を減少させて、信号レベルを増加させた後、初期化状態に戻る。 $MTR6 < 12 : 23 >$  によって  $BM1$  メーター減衰を  $Int1\_Gain$  の  $Max$  に調節し、かつ、 $MTR6 < 0 : 11 >$  によって  $BM2$  メーター減衰を  $Int1\_Gain$  の  $Max$  に調節し、再試行する；

13) (乗算器からの) 検出器の出力を、ADC読取により、 $Int1\_Gain_{IN}$  として記録し、かつ、 $BM1$  メーター減衰および  $BM2$  メーター減衰を、それぞれ  $BM1_{Int1\_Gain\_IN}$ ,  $BM2_{Int1\_Gain\_IN}$  として記録する；

14)  $Int1\_Gain_{IN}$  が  $Int1\_Gain_{out\_T}$  である？ この確認の結果が否定である場合、MTR減衰限界状態を確認する。この状態に該当しなければ、 $MTR6 < 12 : 23 >$  および  $MTR6 < 0 : 11 >$  によって  $BM1$  および  $BM2$  をそれぞれ調

節することにより、 $\text{Int1\_Gain}_{IN}$ を減衰させる。そして、(乗算器からの)検出器の出力を、ADC読取により、 $\text{Int1\_Gain}_{IN}$ として記録し、かつ、BM1メーター減衰およびBM2メーター減衰を、それぞれ $\text{BM1}_{\text{Int1\_Gain\_IN}}$ 、 $\text{BM2}_{\text{Int1\_Gain\_IN}}$ として記録し、再試行する [MTR減衰限界状態であれば、MTR7 < 0 : 11>により、SRC減衰器設定を減少させて、信号レベルを増加させた後、2)に戻る] ;

15)  $\text{BM1}_{\text{Int1\_Gain\_IN}} / \text{BM1}_{\text{Int1\_Gain\_OUT}}$  の比を算出する ( $\text{BM2}_{\text{Int1\_Gain\_IN}} / \text{BM2}_{\text{Int1\_Gain\_OUT}}$  と等しくなるべきである) ;

16)  $\text{BM1}_{\text{Int1\_Gain\_IN}} / \text{BM1}_{\text{Int1\_Gain\_OUT}}$  201<sup>10</sup>  $\log_{10}(\text{wrn} / 2 (100\text{MHz}))$  である? この確認の結果が否定である場合、 $\text{Int1\_Gain}$ の傾き： $\text{Int1\_Gain}$ の知識を用いて、 $V_{CC1}$ の目標値を調節する。 $Y = X$  とすると、 $Y = (\text{BM1}_{\text{Int1\_Gain\_IN}} / \text{BM1}_{\text{Int1\_Gain\_OUT}} - 201 \log_{10}(\text{wrn} / 2 (100\text{MHz}))) / \text{Int1\_Gain} = X$  なので、周波数<sub>新</sub> = 周波数<sub>旧</sub> ± X となる。この X は、既知の所与の  $V_{CC1}$  調節量に対応する。 $\text{BQn\_2} < 0 : 11>$  により、 $V_{CC1}$ をこの数値に設定する;

17) (乗算器からの)検出器の出力を、ADC読取により、 $\text{Int1\_Gain}_{OUT\_FINAL}$ として記録する。

【0079】<sup>20</sup>

#### [積分器およびロスパッドの制御]

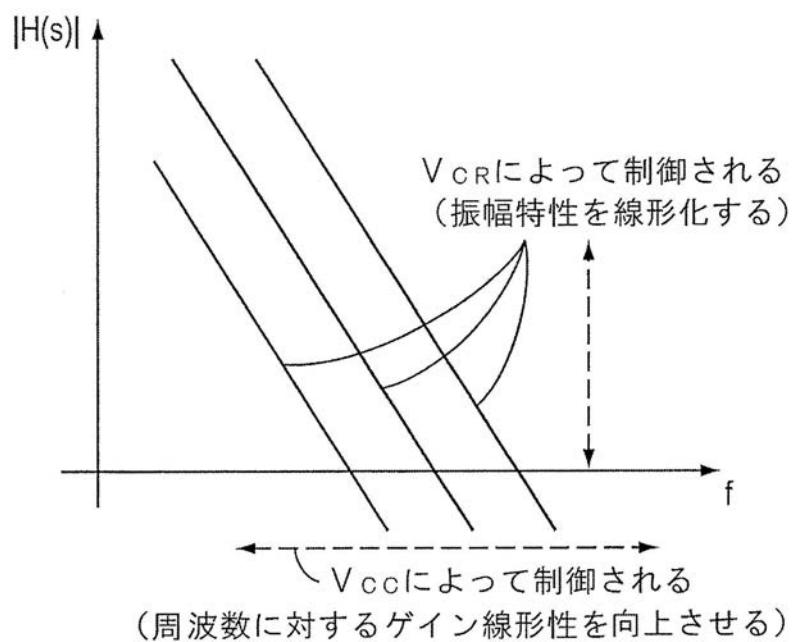

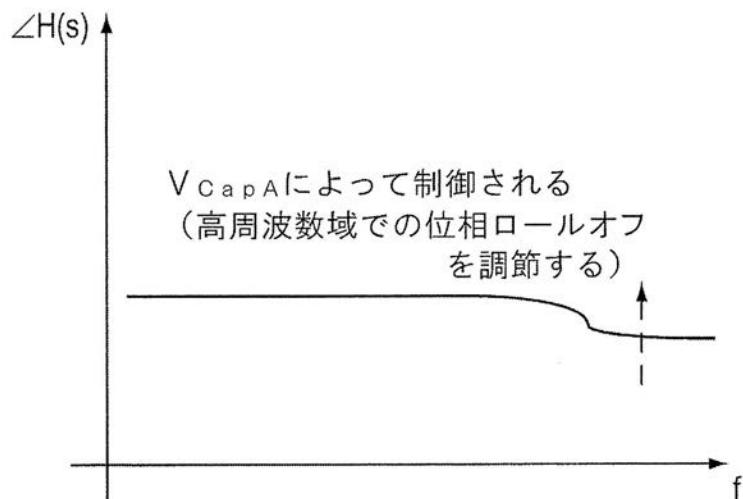

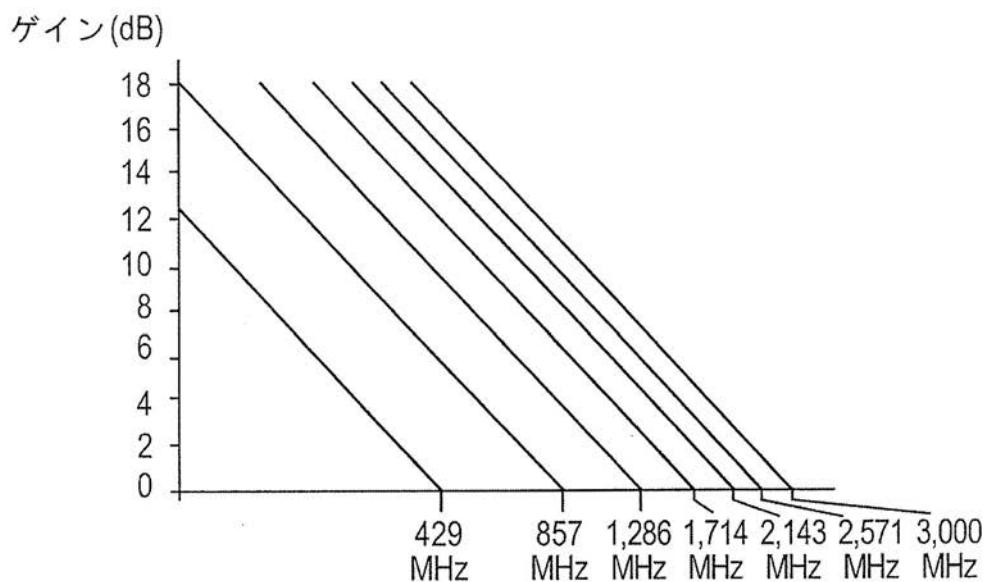

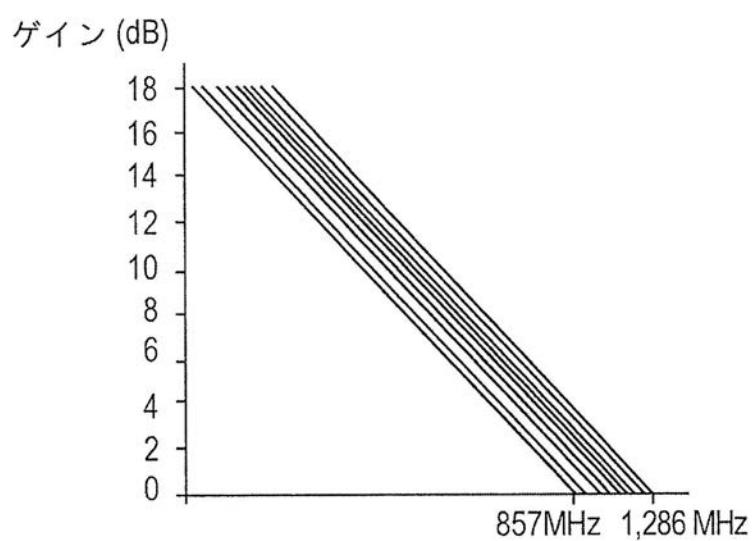

図12A及び図12Bは、積分器の制御および当該制御による出力を示すグラフである。上記例の8次の帯域通過フィルタでは、 $V_{CR1}$ 、 $V_{CR2}$ 、 $V_{CapA}$ 、 $V_{i1\_sw}$ 、 $V_{i2\_sw}$ 、 $V_{CC1}$ および $V_{CC2}$ が、積分器の位相及びゲインのチューニングに関わる主なピンである。まず、位相応答が目標の -89° 位相シフトにチューニングされるように、 $V_{CR1}$ および $V_{CR2}$ を(動作周波数しだいでは、 $V_{CapA}$ も)設定する。次に、ゲインが目標値にチューニングされるように、 $V_{i1\_sw}$ 、 $V_{i2\_sw}$ 、 $V_{CC1}$ および $V_{CC2}$ を設定する。これらのピンは、対応するビットにより、位相値及びゲイン値を制御する。

【0080】<sup>30</sup>

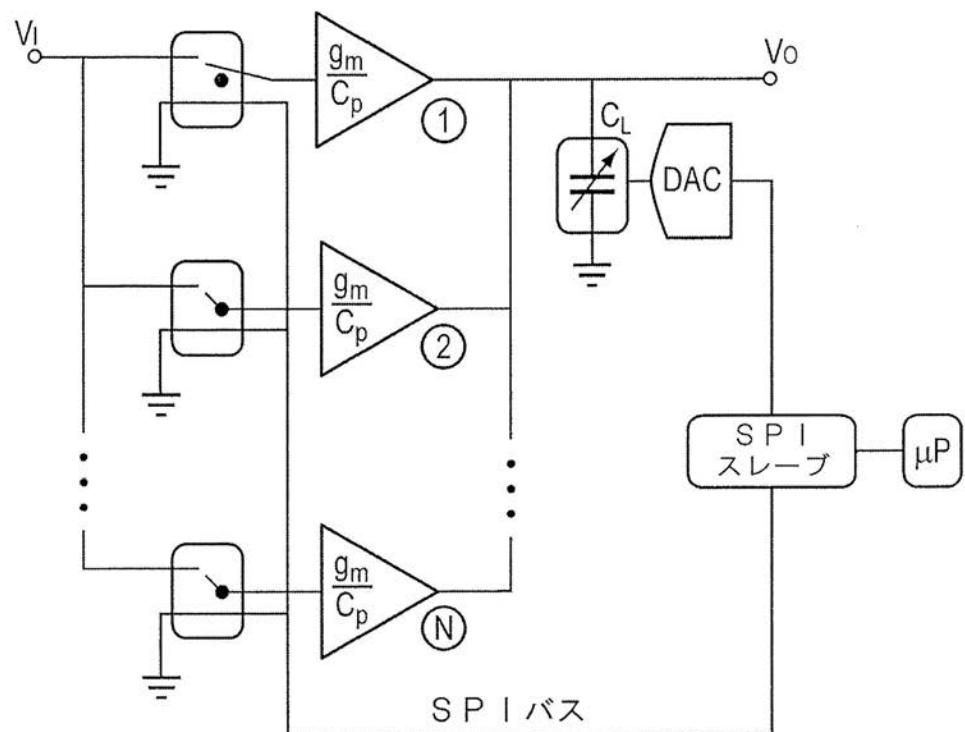

図13は、積分器のゲインをチューニングする回路の回路図である。図5Bにおいて、入力  $V_{i1\_sw} / V_{i2\_sw}$  は左側でスイッチに接続されており、ゲインの粗チューニングを制御する。また、入力  $V_{CC1} / V_{CC2}$  は、図13の  $C_L$  を介して、ゲインの微チューニング(微調整)を制御する。図14Aのグラフ及び図14Bのグラフに、粗チューニング値の例を示す。

【0081】

図5Bにおいて、ロスパッドの制御ならびに積分器の位相及びゲインの制御を行う入力は、以下のように割り当てられ得る:

【0082】

1) ピン  $V_{CR1}$  は第1の積分器の位相の調節を制御し、ピン  $V_{CR2}$  は第2の積分器の位相の調節を制御する。これらのピンは、それぞれの12個のビットにより、位相値を制御する;

2) ピン  $V_{CapA}$  は、必要な場合に、第1および第2の積分器の位相の微調節を制御する。このピンは、その12個のビットにより、位相値を制御する。このピンを使用するか否かは動作周波数範囲に依存し、具体的には、動作周波数が所与の閾値(例えば、1.5GHz)を超える場合にのみ必要とされる;

3) スイッチ  $V_{i1\_sw}$  は第1の積分器のゲインの粗調節を制御し、スイッチ  $V_{i2\_sw}$  は第2の積分器のゲインの粗調節を制御する(演繹的情報からのルックアップを用いて、7段階の粗調節が可能である)。これらのスイッチは、それぞれの3個のビットにより、ルックアップテーブルのどの数値を使用するかを制御する;

10

20

30

40

50

4) ピン  $V_{c\_c\_1}$  は第1の積分器のゲインの微調節を制御し、ピン  $V_{c\_c\_2}$  は第2の積分器のゲインの微調節を制御する。これらのピンは、それぞれの12個のビットにより、ゲイン値を制御する。また、これら  $V_{c\_c\_1}$  及び  $V_{c\_c\_2}$  は、典型的に約900mVに設定される；

5)  $V_{c\_a\_1}$  は、前記  $a_1$  を制御するロスパッドの減衰調節を制御する。

【0083】

[ノッチフィルタの場合のバイカッド]

図15Aは、状態変数フィルタをノッチフィルタとして動作させるチューニング例の回路図であり、図15Bは、そのフロー図である。図15Aには、前記チューニング手順により実現可能な伝達関数の演算が記載されている。図15Bの状態遷移図は、状態変数フィルタをノッチフィルタとして動作させる際の、経験的に定まるチューニング手順を表したものである。具体的に述べると、図6の状態マシンを介して帯域通過フィルタを構築した後、係数「 $b$ 」を調節する。詳細には、 $b_1$  ロスパッドを「最大減衰」に変更すると共に、 $b_0$  および  $b_2$  を最大減衰から「減衰なし」に調節する。これらの調節で所望のノッチフィルタが得られない場合には、 $b_0$  ロスパッドのゲイン及び位相ならびに  $b_2$  ロスパッドのゲインをさらに細かく調節することが考えられる。

10

【0084】

[オールパスフィルタ(遅延ライン)の場合のバイカッド]

図16Aは、状態変数フィルタをオールパスフィルタ(遅延フィルタ)として動作させるチューニング例の回路図であり、図16Bは、その状態遷移図である。図16Aには、前記チューニング手順により実現可能な伝達関数の演算が記載されている。図16Bの状態遷移図は、状態変数フィルタをオールパスフィルタ(遅延フィルタ)として動作させる際の、経験的に定まるチューニング手順を表したものである。具体的に述べると、図6の状態マシンを介して帯域通過フィルタを構築した後、係数「 $b$ 」を調節する。詳細には、 $b_1$  ロスパッドを  $a_1$  ロスパッドの数値に設定することにより、 $b_1$  が正の数値から負の数値に切り替わる。これに加えて、 $b_0$  ロスパッドおよび  $b_2$  ロスパッドを最大減衰から「減衰なし」に調節する。これらの調節で所望のオールパスフィルタが得られない場合には、 $b_0$  ロスパッドのゲイン及び位相ならびに  $b_2$  ロスパッドのゲインをさらに細かく調節することが考えられる。

20

【0085】

本発明を例示的な実施形態を参照しながら具体的に図示・説明したが、当業者であれば、添付の特許請求の範囲に包含される本発明の範囲から逸脱することなく、形態および細部の様々な変更が可能であることを理解するであろう。

30

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

【図 1】

## 1 次の状態変数フィルタ 100

FIG. 1

【図 2 A】

FIG. 2A

【図 2 B】

FIG. 2B

【図 3】

FIG. 3

観測形の2次の

状態変数フィルタ

300

【図 4】

FIG. 4

【図 5 A】

FIG. 5A

【図 5 B】

FIG. 5B

【図 5 C】

FIG. 5C

【図 6】

## セットアップ：乗算器等の校正

FIG. 6

【図 7A】

FIG. 7A

【図 7 B】

【 図 8 A 】

FIG. 8A

【図 8 B】

FIG. 8B

【図 8 C】

FIG. 8C

【図 8 D】

FIG. 8

【図 9 A】

FIG. 9A

【図 9B】

FIG. 9B

【図 9C】

FIG. 9C

【図 9 D】

FIG. 9

【図 10A】

FIG. 10A

【図 10B】

FIG. 10B

【図 10 C】

FIG. 10

【図 11A】

FIG. 11A

【図 11B】

FIG. 11B

【図 11 C】

FIG. 11

【図 12 A】

FIG. 12A

【図 12B】

FIG. 12B

【図 13】

FIG. 13

【図 1 4 A】

FIG. 14A

【図 1 4 B】

FIG. 14B

【図 15A】

計算内容

$$G = \omega_r$$

$$a_1 = 1/Q$$

$$b_2 = 1$$

一般的な伝達関数との違い

$$a_0 = 1 \quad Q_n = Q_d$$

$$b_1 = 0 \quad \omega_m = \omega_{rd}$$

$$G_1 = G_2$$

$$T(s) = \frac{L [s_2 b_2 + G_1 G_2 b_0]}{s^2 + a_1 G_1 s + G_1 G_2}$$

FIG. 15A

【図15B】

FIG. 15B

【図 16 A】

計算内容

$$G = \omega_r$$

$$a_1 = 1/Q$$

$$b_2 = 1$$

一般的な伝達関数との違い

$$a_0 = 1$$

$$Q_n = Q_d$$

$$\omega_{rn} = \omega_{rd}$$

$$G_1 = G_2$$

$$T(s) = \frac{L [s^2 - a_1 G_1 s + G_1 G_2]}{s^2 + a_1 G_1 s + G_1 G_2}$$

FIG. 16A

【図16B】

FIG. 16B

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                 | International application No.<br>PCT/US2013/057996                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br><b>H03H 11/12(2006.01)i, H03H 11/04(2006.01)i</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                                                                                            |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                 |                                                                                            |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>H03H 11/12; H03H 17/02; H03H 7/30; G01V 3/10; H03H 21/00; G01V 3/08; H03H 11/04                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                                                                                            |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched<br>Korean utility models and applications for utility models<br>Japanese utility models and applications for utility models                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                                                                                            |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>eKOMPASS(KIPO internal) & keywords: biquad circuit, integrator, phase, gain, frequency                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                 |                                                                                            |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |                                                                                            |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Citation of document, with indication, where appropriate, of the relevant passages                              | Relevant to claim No.                                                                      |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 7733950 B2 (HYUNG-JONG KO) 08 June 2010<br>See column 8, line 54 – column 15, line 10; and figures 2-9.      | 1-9                                                                                        |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 2003-0155922 A1 (JOHN M. ROYLE et al.) 21 August 2003<br>See paragraphs [0023]–[0063]; and figures 1-4.      | 1-9                                                                                        |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | JP 07-240664 A (FUJITSU LTD.) 12 September 1995<br>See paragraphs [0018]–[0046]; and figures 2-6.               | 1-9                                                                                        |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EP 0579875 A1 (ALCATEL N.V. et al.) 26 January 1994<br>See page 6, line 29 – page 12, line 27; and figures 1-4. | 1-9                                                                                        |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | JP 07-058596 A (ASAHI KASEI MICRO SYST. KK.) 03 March 1995<br>See paragraphs [0045]–[0051]; and figures 11, 12. | 1-9                                                                                        |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                 | <input checked="" type="checkbox"/> See patent family annex.                               |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"U" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                                 |                                                                                            |

| Date of the actual completion of the international search<br>24 December 2013 (24.12.2013)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 | Date of mailing of the international search report<br><b>26 December 2013 (26.12.2013)</b> |

| Name and mailing address of the ISA/KR<br><br>Korean Intellectual Property Office<br>189 Cheongsa-ro, Seo-gu, Daejeon Metropolitan City,<br>302-701, Republic of Korea<br>Facsimile No. +82-42-472-7140                                                                                                                                                                                                                                                                                                                             |                                                                                                                 | Authorized officer<br>KIM, Do Weon<br>Telephone No. +82-42-481-5560                        |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No.

**PCT/US2013/057996**

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                                                              | Publication date                                                                                             |

|----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| US 7733950 B2                          | 08/06/2010       | CN 1822498 A<br>CN 1822498 B<br>JP 04809677 B2<br>JP 2006-191621 A<br>KR 10-0660848 B1<br>KR 10-2006-0075125 A<br>TW I294224 B<br>US 2006-0140263 A1 | 23/08/2006<br>06/07/2011<br>09/11/2011<br>20/07/2006<br>26/12/2006<br>04/07/2006<br>01/03/2008<br>29/06/2006 |

| US 2003-0155922 A1                     | 21/08/2003       | AT 514107 T<br>AU 2003-215717 A1<br>EP 1474709 A1<br>EP 1474709 B1<br>US 6617856 B1<br>WO 03-069374 A1                                               | 15/07/2011<br>04/09/2003<br>10/11/2004<br>22/06/2011<br>09/09/2003<br>21/08/2003                             |

| JP 07-240664 A                         | 12/09/1995       | JP 03232856 B2                                                                                                                                       | 26/11/2001                                                                                                   |

| EP 0579875 A1                          | 26/01/1994       | DE 69222161 D1<br>DE 69222161 T2<br>EP 0579875 B1<br>ES 2108082 T3<br>FI 933311 A0<br>JP 06-164313 A<br>US 05471168 A                                | 16/10/1997<br>26/02/1998<br>10/09/1997<br>16/12/1997<br>22/07/1993<br>10/06/1994<br>28/11/1995               |

| JP 07-058596 A                         | 03/03/1995       | None                                                                                                                                                 |                                                                                                              |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,H,R,HU,ID,IL,IN,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ

(74)代理人 100154771

弁理士 中田 健一

(72)発明者 グブタ・デヴ・ヴィ

アメリカ合衆国, マサチューセッツ州 01742, コンコード, マッティソン ドライブ 35

6

F ターム(参考) 5H004 HA14 HB14 KA32 KB03 KB04 MA11

5J098 AB07 AB25 AB26 AB34 AC02 AD24 CA06 CA08