(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6435787号

(P6435787)

(45) 発行日 平成30年12月12日(2018.12.12)

(24) 登録日 平成30年11月22日(2018.11.22)

(51) Int.Cl.

F 1

|             |              |                  |      |      |

|-------------|--------------|------------------|------|------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/36 |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G09G | 3/20 |

| <b>H03M</b> | <b>1/66</b>  | <b>(2006.01)</b> | G09G | 3/20 |

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

請求項の数 10 (全 35 頁) 最終頁に続く

(21) 出願番号

特願2014-226884 (P2014-226884)

(22) 出願日

平成26年11月7日(2014.11.7)

(65) 公開番号

特開2016-90881 (P2016-90881A)

(43) 公開日

平成28年5月23日(2016.5.23)

審査請求日

平成29年11月6日(2017.11.6)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 森田 晶

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】 ドライバー及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の基準電圧から階調データに対応する基準電圧を選択し、前記選択された基準電圧を出力ノードから出力するD/A変換回路と、

入力ノードが前記D/A変換回路の出力ノードに接続され、出力ノードがデータ電圧出力端子に接続され、前記入力ノードから入力される電圧を増幅し、前記増幅した電圧を前記階調データに対応するデータ電圧として前記データ電圧出力端子に出力する電圧駆動回路と、

第1～第n(nは2以上の自然数)の第1のキャパシターを有し、前記第1～第nの第1のキャパシターのそれぞれの一端が、前記D/A変換回路の出力ノードと前記電圧駆動回路の入力ノードの間に接続された第1のキャパシター回路と、

前記階調データに対応する第1～第nの第1のキャパシター駆動電圧を出力する第1～第nの第1のキャパシター駆動用ノードを備え、前記第1～第nの第1のキャパシター駆動用ノードのそれぞれが、前記第1のキャパシター回路の前記第1～第nの第1のキャパシターの対応する他端に接続された第1のキャパシター駆動回路と、

第1～第n(nは2以上の自然数)の第2のキャパシターを有し、前記第1～第nの第2のキャパシターのそれぞれの一端が、前記データ電圧出力端子に接続された第2のキャパシター回路と、

前記階調データに対応する第1～第nの第2のキャパシター駆動電圧を出力する第1～第nの第2のキャパシター駆動用ノードを備え、前記第1～第nの第2のキャパシター駆

10

20

動用ノードのそれぞれが、前記第2のキャパシター回路の前記第1～第nの第2のキャパシターの対応する他端に接続された第2のキャパシター駆動回路と、

を含むことを特徴とするドライバー。

【請求項2】

請求項1において、

前記電圧駆動回路は、

前記第2のキャパシター駆動回路から出力された第1～第nの第2のキャパシター駆動電圧が、前記第2のキャパシター回路を介して、前記データ電圧出力端子に出力された後に、前記出力ノードから前記データ電圧を前記データ電圧出力端子に出力する電圧駆動を行うことを特徴とするドライバー。 10

【請求項3】

請求項2において、

前記第1～第nの第1のキャパシターの第iの第1のキャパシター(iはn以下の自然数)の容量は、前記第1～第nの第2のキャパシターの第iのキャパシターの容量よりも小さいことを特徴とするドライバー。

【請求項4】

請求項1乃至3のいずれかにおいて、

前記第1のキャパシター回路は、

前記電圧駆動回路の前記入力ノードと前記第1～第nの第1のキャパシターの前記一端との間に設けられるスイッチ回路を有することを特徴とするドライバー。 20

【請求項5】

請求項4において、

前記スイッチ回路は、

前記電圧駆動回路が前記データ電圧を前記データ電圧出力端子に出力する前に、オンからオフになることを特徴とするドライバー。

【請求項6】

請求項5において、

前記電圧駆動回路は、

前記データ電圧を出力するアンプ回路と、

前記アンプ回路の出力と前記データ電圧出力端子との間に設けられる電圧駆動用スイッチ回路と、 30

を有し、

前記第1のキャパシター回路の前記スイッチ回路は、

前記電圧駆動用スイッチ回路がオフからオンになる前に、オンからオフになることを特徴とするドライバー。

【請求項7】

請求項1乃至6のいずれかにおいて、

前記電圧駆動回路は、

反転増幅回路であることを特徴とするドライバー。

【請求項8】

請求項7において、

前記第1のキャパシター駆動回路は、

前記階調データの論理反転データに対応する前記第1～第nの第1のキャパシター駆動電圧を出力することを特徴とするドライバー。 40

【請求項9】

請求項2又は3において、

前記データ電圧出力端子に接続された可変容量回路を含み、

前記可変容量回路の容量と電気光学パネル側容量を加算した容量と、前記第2のキャパシター回路の容量とが、所与の容量比関係になるように、前記可変容量回路の容量が設定されていることを特徴とするドライバー。 50

**【請求項 10】**

請求項 1 乃至 9 のいずれかに記載されたドライバーを含むことを特徴とする電子機器。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、ドライバー及び電子機器等に関する。

**【背景技術】****【0002】**

プロジェクターや情報処理装置、携帯型情報端末等の種々の電子機器において表示装置（例えば液晶表示装置）が用いられている。このような表示装置では高精細化が進んでおり、それに伴ってドライバーが1つの画素を駆動する時間が短くなっている。例えば、電気光学パネル（例えば液晶表示パネル）を駆動する手法として相展開駆動がある。この駆動手法では、例えば1回に8本のソース線を駆動し、それを160回繰り返して1280本のソース線を駆動する。WXGA（1280×768画素）のパネルを駆動する場合、上記160回の駆動（即ち水平走査線1本の駆動）を768回繰り返すことになる。リフレッシュレートを60Hzとすると、単純計算で1画素あたりの駆動時間は約135ナノ秒である。実際には、画素を駆動しない期間（例えばブランкиング期間等）があるため、1画素あたりの駆動時間は約70ナノ秒程度と更に短くなる。10

**【先行技術文献】****【特許文献】**

20

**【0003】**

【特許文献1】特開2000-341125号公報

【特許文献2】特開2001-156641号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

上記のような画素の駆動時間の短縮にともなって、アンプ回路によって時間内にデータ電圧の書き込みを終えることが困難になりつつある。このような課題を解決する駆動手法として、キャパシターの電荷再分配により電気光学パネルを駆動する手法（以下、容量駆動と呼ぶ）が考えられる。例えば、特許文献1、2には、キャパシターの電荷再分配をD/A変換を利用した技術が開示されている。D/A変換回路では、駆動側の容量と負荷側の容量が共にICに内蔵されており、それらの容量の間で電荷再分配が生じる。例えば、このようなD/A変換回路の負荷側の容量をIC外部の電気光学パネルの容量に置き換え、ドライバーとして用いたとする。この場合、ドライバー側の容量と電気光学パネル側の容量との間で電荷再分配が行われる。30

**【0005】**

このように電荷再分配を用いる容量駆動では、自在に電荷を供給できるアンプ回路に比べてデータ電圧の精度が低下するという課題がある。このような課題を解決する駆動手法として、容量駆動による高速な駆動を開始した後に更にアンプ回路により高精度なデータ電圧を出力する手法（以下、電圧駆動と呼ぶ）が考えられる。この場合、階調データに対応した電圧をアンプ回路に出力するD/A変換回路が設けられる。40

**【0006】**

しかしながら、D/A変換回路の出力（アンプ回路の入力）が、階調データに対応した電圧にセトリングする時間が長い場合、それを受けたアンプ回路の出力がデータ電圧にセトリングする時間が長くなるという課題がある。そのため、画素の書き込み時間内に高精度なデータ電圧を書き込めない可能性がある。

**【0007】**

本発明の幾つかの態様によれば、電圧駆動においてアンプ回路の出力のセトリング時間を短縮することが可能なドライバー及び電子機器等を提供できる。

**【課題を解決するための手段】**

50

## 【0008】

本発明の一態様は、入力ノードの電圧を増幅し、前記増幅した電圧をデータ電圧としてデータ電圧出力端子に出力する電圧駆動回路と、複数の基準電圧から階調データに対応する基準電圧を選択し、前記選択された基準電圧を前記電圧駆動回路の前記入力ノードに出力するD/A変換回路と、前記階調データに対応する第1～第nの補助用キャパシター駆動電圧（nは2以上の自然数）を第1～第nの補助用キャパシター駆動用ノードに出力する補助用キャパシター駆動回路と、前記電圧駆動回路の前記入力ノードと前記第1～第nの補助用キャパシター駆動用ノードとの間に設けられる第1～第nの補助用キャパシターを有する補助用キャパシター回路と、を含むドライバーに関係する。

## 【0009】

10

本発明の一態様によれば、補助用キャパシター駆動回路が第1～第nの補助用キャパシター駆動電圧を出力して第1～第nの補助用キャパシターを駆動し、それにより第1～第nの補助用キャパシターと電圧駆動回路の入力ノードの寄生容量との間で電荷再分配が行われ、階調データに対応する電圧が電圧駆動回路の入力ノードに設定される。これにより、電圧駆動回路の入力を高速にセトリングでき、電圧駆動においてアンプ回路の出力のセトリング時間を短縮することが可能となる。

## 【0010】

また本発明の一態様では、前記階調データに対応する第1～第nのキャパシター駆動電圧を第1～第nのキャパシター駆動用ノードに出力するキャパシター駆動回路と、前記第1～第nのキャパシター駆動用ノードと前記データ電圧出力端子との間に設けられる第1～第nのキャパシターを有するキャパシター回路と、を含み、前記電圧駆動回路は、前記キャパシター駆動回路と前記キャパシター回路により電気光学パネルを駆動する容量駆動が開始された後に、前記データ電圧を前記データ電圧出力端子に出力する電圧駆動を行ってもよい。

20

## 【0011】

このようにすれば、容量駆動を先に開始することで高速にデータ電圧にセトリングさせることが可能であり、その後に電圧駆動を行うことで、容量駆動よりも高精度にデータ電圧を出力することが可能となる。これにより、容量駆動による高速な駆動と電圧駆動による高精度な駆動を両立できる。

## 【0012】

30

また本発明の一態様では、前記第1～第nの補助用キャパシターの第iの補助用キャパシター（iはn以下の自然数）の容量は、前記第1～第nのキャパシターの第iのキャパシターの容量よりも小さくてもよい。

## 【0013】

電気光学パネル側容量に比べて電圧駆動回路の入力ノードの寄生抵抗（例えばアンプ回路の入力ゲート容量や入力ノードの配線容量等）は小さい。そのため、容量駆動のキャパシター回路に比べて補助用キャパシター回路の容量を小さくできる。これにより、電荷再分配のCR時定数が小さくなるので、電圧駆動回路の入力電圧を補助用電圧設定回路により高速に駆動できる。

## 【0014】

40

また本発明の一態様では、前記補助用キャパシター回路は、前記電圧駆動回路の前記入力ノードと前記第1～第nの補助用キャパシターとの間に設けられるスイッチ回路を有してもよい。

## 【0015】

D/A変換回路の出力から見ると、補助用キャパシター回路は負荷容量として見えるため、D/A変換回路の出力のCR時定数が増える。この点、本発明の一態様によれば、スイッチ回路をオフすることで電圧駆動回路の入力ノードから補助用キャパシター回路を遮断できる。これにより、電圧駆動回路の入力電圧がD/A変換回路の出力電圧にセトリングする時間を増加させることなく、補助用電圧設定回路による高速なセトリングが可能となる。

50

**【 0 0 1 6 】**

また本発明の一態様では、前記スイッチ回路は、前記電圧駆動回路が前記データ電圧を前記データ電圧出力端子に出力する電圧駆動を開始する前に、オンからオフになってもよい。

**【 0 0 1 7 】**

このようにすれば、スイッチ回路をオンにして補助用電圧設定回路により高速に駆動し、その後にスイッチ回路をオフにすることでD/A変換回路により電圧駆動回路の入力ノードに正確な電圧を供給できる。そして、スイッチ回路をオフにした後に電圧駆動を開始することで、D/A変換回路による正確な電圧により電圧駆動を行うことができる。

**【 0 0 1 8 】**

また本発明の一態様では、前記電圧駆動回路は、前記データ電圧を出力するアンプ回路と、前記アンプ回路の出力と前記データ電圧出力端子との間に設けられる電圧駆動用スイッチ回路と、を有し、前記補助用キャパシター回路の前記スイッチ回路は、前記電圧駆動用スイッチ回路がオフからオンになる前に、オンからオフになってもよい。

**【 0 0 1 9 】**

アンプ回路による駆動よりも容量駆動の方が高速であるため、電圧駆動と容量駆動を同時に使うと、アンプ回路の出力に引っ張られてデータ電圧への漸近が遅くなる。この点、本発明の一態様によれば、電圧駆動用スイッチ回路を設けたことで、アンプ回路の出力とデータ電圧出力端子を遮断して、高速な容量駆動によりデータ電圧を出力することが可能になる。そして、電圧駆動用スイッチ回路がオフからオンになる前に、補助用キャパシターレベルのスイッチ回路がオンからオフになることで、電圧駆動を開始する前に補助用キャパシター回路をD/A変換回路の出力から遮断できる。

**【 0 0 2 0 】**

また本発明の一態様では、前記電圧駆動回路は、反転增幅回路であってもよい。

**【 0 0 2 1 】**

反転增幅回路ではサミングノードの電圧が一定の電圧に固定されるので、出力レンジの端でも差動対の入力電圧が変化しない。そのため、ボルテージフォロア等の非反転増幅回路に比べて出力レンジの広い範囲において良好な特性（例えばセトリング時間）を得やすい。

**【 0 0 2 2 】**

また本発明の一態様では、前記補助用キャパシター駆動回路は、前記階調データの論理反転データに対応する前記第1～第nの補助用キャパシター駆動電圧を出力してもよい。

**【 0 0 2 3 】**

このようにすれば、補助用電圧設定回路が反転出力を行う（容量駆動の出力範囲を所与の基準電圧に対して反転した電圧範囲を出力する）ので、反転增幅回路を用いて電圧駆動を行うことができる。

**【 0 0 2 4 】**

また本発明の一態様では、前記データ電圧出力端子と基準電圧のノードとの間に設けられる可変容量回路を含み、前記可変容量回路の容量と電気光学パネル側容量を加算した容量と、前記キャパシター回路の容量とが、所与の容量比関係になるように、前記可変容量回路の容量が設定されていてもよい。

**【 0 0 2 5 】**

このようにすれば、電気光学パネル側容量が異なる場合であっても、それに応じて可変容量回路の容量を調整することによって所与の容量比関係が実現され、その容量比関係に対応した所望のデータ電圧の範囲を実現できる。即ち、種々の接続環境（例えば、ドライバーに接続される電気光学パネルの機種や、ドライバーが実装されるプリント基板の設計等）において汎用可能な容量駆動を実現できる。

**【 0 0 2 6 】**

また本発明の他の態様は、上記のいずれかに記載されたドライバーを含む電子機器に関係する。

10

20

30

40

50

## 【図面の簡単な説明】

## 【0027】

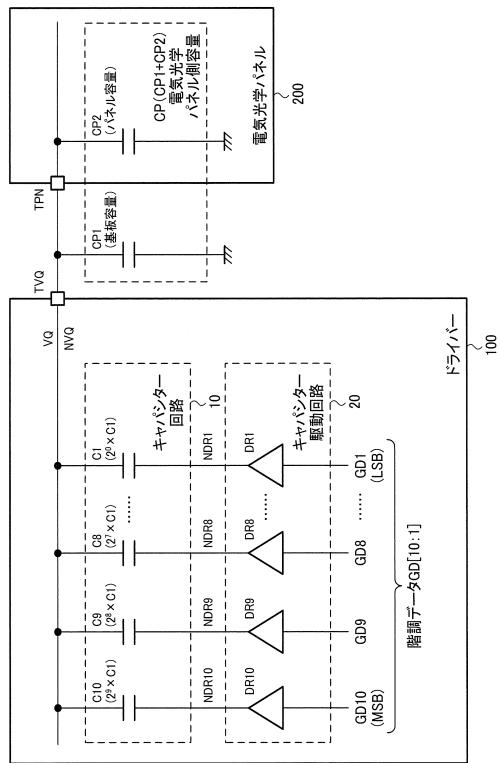

【図1】ドライバーの第1構成例。

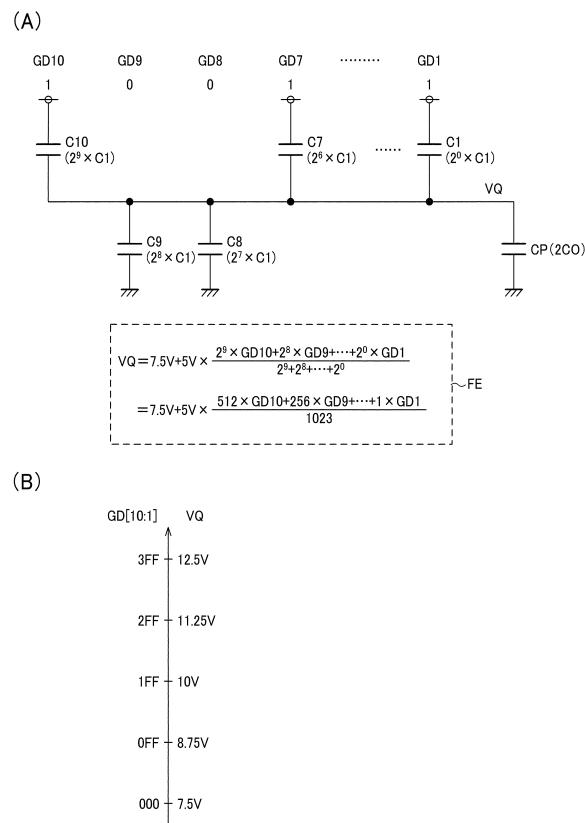

【図2】図2(A)、図2(B)は、階調データに対応するデータ電圧の説明図。

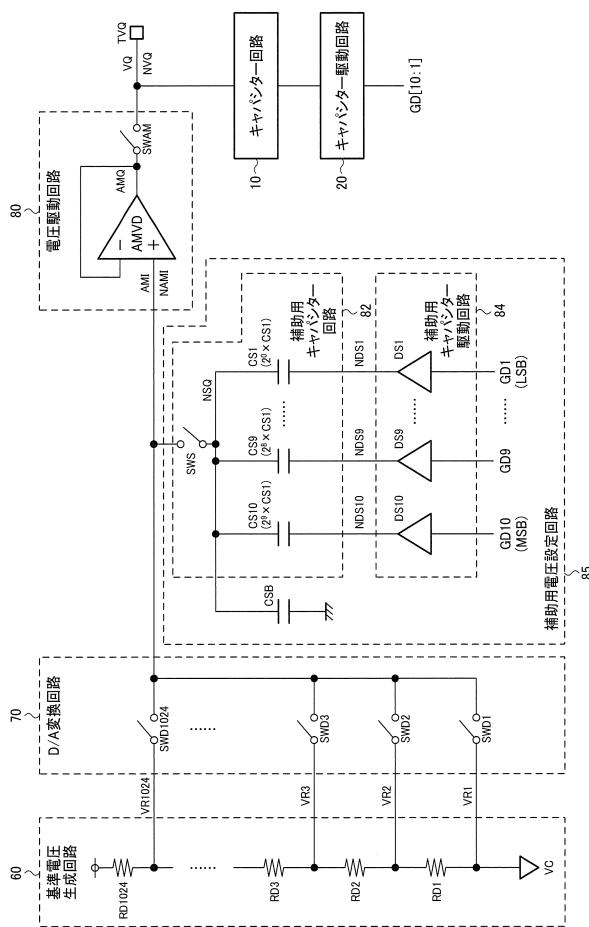

【図3】ドライバーの第2構成例。

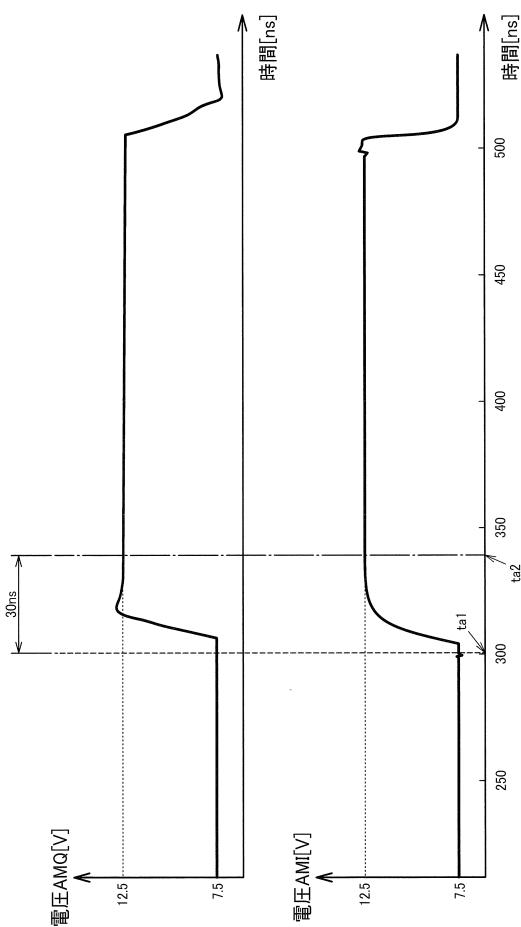

【図4】比較例のシミュレーション結果。

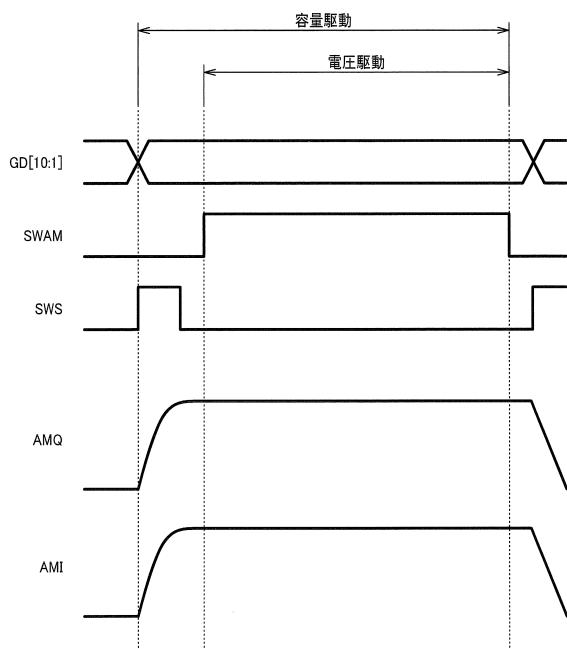

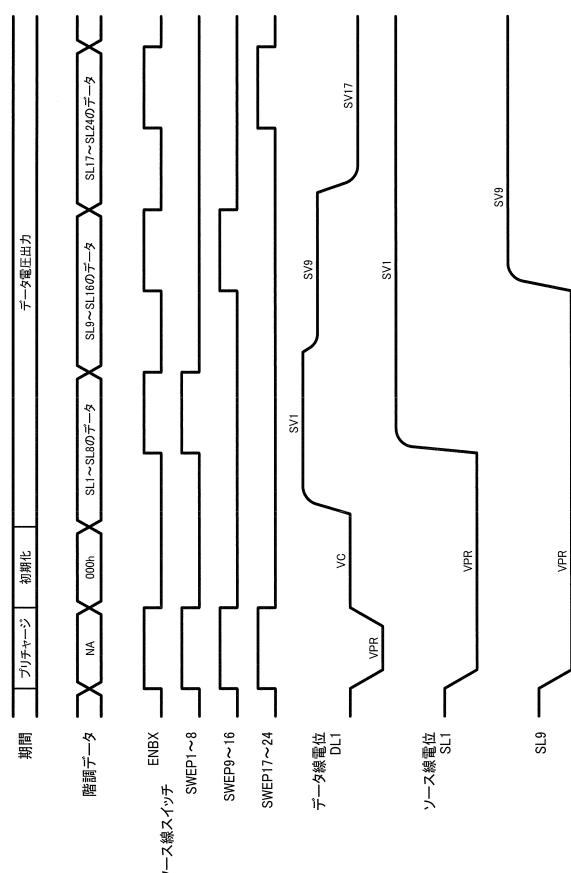

【図5】第2構成例の補助用電圧設定回路についての動作タイミングチャート。

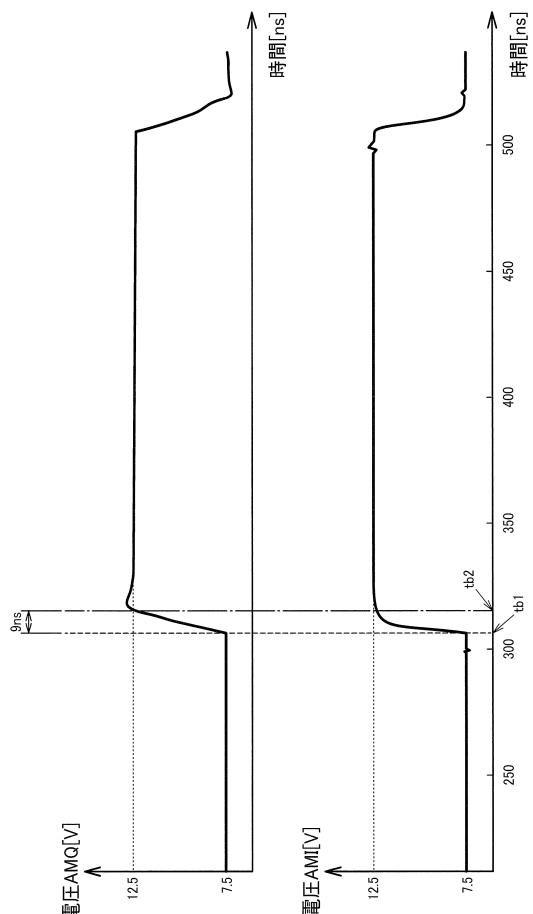

【図6】第2構成例のシミュレーション結果。

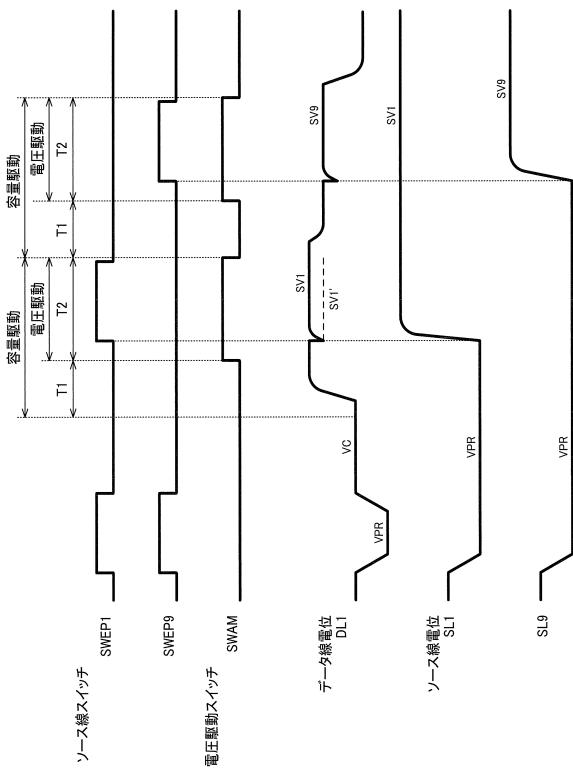

【図7】第2構成例の電圧駆動回路についての動作タイミングチャート。

【図8】ドライバーの変形構成例。

10

【図9】図9(A)～図9(C)は、第1構成例におけるデータ電圧の説明図。

【図10】ドライバーの第3構成例。

【図11】図11(A)～図11(C)は、第3構成例におけるデータ電圧の説明図。

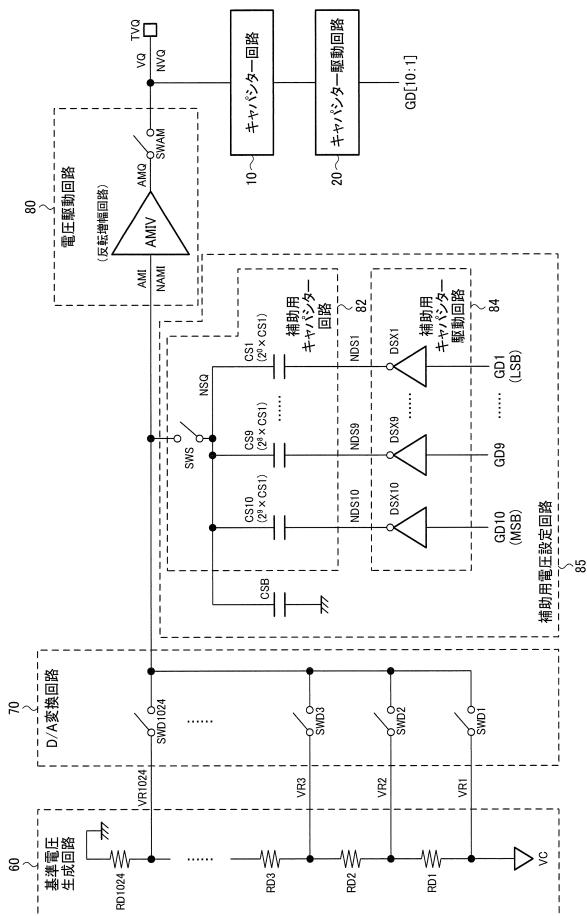

【図12】ドライバーの詳細な構成例。

【図13】検出回路の詳細な構成例。

【図14】可変容量回路の容量を設定する処理のフローチャート。

【図15】図15(A)、図15(B)は、可変容量回路の容量を設定する処理の説明図。

【図16】ドライバーの第2の詳細な構成例。

20

【図17】第2の詳細な構成例の動作タイミングチャート。

【図18】第2の詳細な構成例の動作タイミングチャート。

【図19】ドライバーの第3の詳細な構成例と、電気光学パネルの詳細な構成例と、ドライバーと電気光学パネルの接続構成例。

【図20】ドライバーと電気光学パネルの動作タイミングチャート。

【図21】電子機器の構成例。

## 【発明を実施するための形態】

## 【0028】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

30

## 【0029】

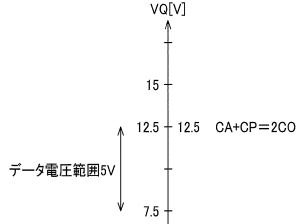

## 1. ドライバーの第1構成例

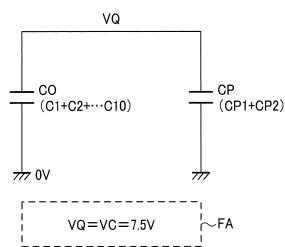

図1に、本実施形態のドライバーの第1構成例を示す。このドライバー100は、キャパシタ回路10、キャパシタ駆動回路20、データ電圧出力端子TVQを含む。なお以下では、キャパシターの容量値を表す符号として、そのキャパシターの符号と同一の符号を用いる。

## 【0030】

ドライバー100は、例えば集積回路装置(IC)により構成される。集積回路装置は、例えばシリコン基板に回路が形成されたICチップ、或はICチップがパッケージに収納された装置に対応する。ドライバー100の端子(データ電圧出力端子TVQ等)は、ICチップのパッド或はパッケージの端子に対応する。

40

## 【0031】

キャパシタ回路10は、第1～第nのキャパシターC1～Cn(nは2以上の自然数)を含む。またキャパシタ駆動回路20は、第1～第nの駆動部DR1～DRnを含む。なお以下では、n=10の場合を例にとって説明するが、nは2以上の自然数であればよい。例えばnは、階調データのビット数と同数に設定すればよい。

## 【0032】

キャパシタC1～C10の第iのキャパシター(iはn=10以下の自然数)の一端は、キャパシタ駆動ノードNDRiに接続され、第iのキャパシターの他端は、データ電圧出力ノードNVQに接続される。データ電圧出力ノードNVQはデータ電圧出力端子

50

T V Q に接続されるノードである。キャパシター C 1 ~ C 1 0 は、2 の累乗で重み付けされた容量値を有している。具体的には第 i のキャパシター C i の容量値は  $2^{(i-1)} \times C_1$  である。

#### 【 0 0 3 3 】

第 1 ~ 第 1 0 の駆動部 D R 1 ~ D R 1 0 の第 i の駆動部 D R i の入力ノードには、階調データ G D [ 1 0 : 1 ] の第 i のビット G D i が入力される。第 i の駆動部 D R i の出力ノードは、第 i のキャパシター駆動ノード N D R i である。階調データ G D [ 1 0 : 1 ] は第 1 ~ 第 1 0 のビット G D 1 ~ G D 1 0 ( 第 1 ~ 第 n のビット ) で構成され、ビット G D 1 が L S B に対応し、ビット G D 1 0 が M S B に対応する。

#### 【 0 0 3 4 】

第 i の駆動部 D R i は、ビット G D i が第 1 論理レベルの場合に第 1 電圧レベルを出力し、ビット G D i が第 2 論理レベルの場合に第 2 電圧レベルを出力する。例えば、第 1 論理レベルは “ 0 ” ( ローレベル ) 、第 2 論理レベルは “ 1 ” ( ハイレベル ) 、第 1 電圧レベルは低電位側電源 V S S の電圧 ( 例えは 0 V ) 、第 2 電圧レベルは高電位側電源 V D D の電圧 ( 例えは 1 5 V ) である。例えば、第 i の駆動部 D R i は、入力された論理レベル ( 例えはロジック電源の 3 V ) を駆動部 D R i の出力電圧レベル ( 例えは 1 5 V ) にレベルシフトするレベルシフターや、そのレベルシフターの出力をバッファリングするバッファー回路で構成される。

#### 【 0 0 3 5 】

以上のように、キャパシター C 1 ~ C 1 0 の容量値は、階調データ G D [ 1 0 : 1 ] のビット G D 1 ~ G D 1 0 の桁に応じた 2 の累乗で重み付けされている。そして、駆動部 D R 1 ~ D R 1 0 が、ビット G D 1 ~ G D 1 0 に応じて 0 V 又は 1 5 V を出力することで、その電圧によりキャパシター C 1 ~ C 1 0 が駆動される。この駆動によってキャパシター C 1 ~ C 1 0 と電気光学パネル側容量 C P との間で電荷再分配が生じ、その結果としてデータ電圧出力端子 T V Q にデータ電圧が出力される。

#### 【 0 0 3 6 】

電気光学パネル側容量 C P は、データ電圧出力端子 T V Q から見える容量の合計である。例えは、電気光学パネル側容量 C P は、プリント基板の寄生容量である基板容量 C P 1 と、電気光学パネル 2 0 0 内の寄生容量や画素容量であるパネル容量 C P 2 と、を加算したものである。

#### 【 0 0 3 7 】

具体的には、ドライバー 1 0 0 は集積回路装置としてリジッド基板に実装され、そのリジッド基板にフレキシブル基板が接続され、そのフレキシブル基板に電気光学パネル 2 0 0 が接続される。このリジッド基板やフレキシブル基板には、ドライバー 1 0 0 のデータ電圧出力端子 T V Q と電気光学パネル 2 0 0 のデータ電圧入力端子 T P N とを接続する配線が設けられている。この配線の寄生容量が基板容量 C P 1 である。また図 1 9 で後述するように、電気光学パネル 2 0 0 には、データ電圧入力端子 T P N に接続されたデータ線と、ソース線と、データ線をソース線に接続するスイッチ素子と、ソース線に接続される画素回路と、が設けられる。スイッチ素子は例えは T F T ( Thin Film Transistor ) で構成され、ソース・ゲート間に寄生容量がある。データ線には多数のスイッチ素子が接続されるため、データ線には多数のスイッチ素子の寄生容量が付く。また、データ線やソース線とパネル基板との間に寄生容量が存在する。また、液晶表示パネルでは液晶の画素に容量がある。これらを加算したものがパネル容量 C P 2 である。

#### 【 0 0 3 8 】

電気光学パネル側容量 C P は、例えは 5 0 p F ~ 1 2 0 p F である。後述するように、キャパシターアクション 1 0 の容量 C O ( キャパシター C 1 ~ C 1 0 の容量の合計 ) と電気光学パネル側容量 C P の比を 1 : 2 にするため、キャパシターアクション 1 0 の容量 C O は 2 5 p F ~ 6 0 p F となる。集積回路に内蔵する容量としては大きいが、例えは M I M ( Metal Insulation Metal ) キャパシターを縦に 2 ~ 3 段積み上げる断面構造にすることで、キャパシターアクション 1 0 の容量 C O を実現できる。

10

20

30

40

50

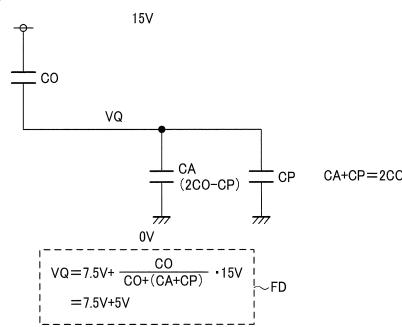

## 【0039】

## 2. データ電圧

次に、階調データGD[10:1]に対してドライバー100が出力するデータ電圧について説明する。ここでは、キャパシター回路10の容量CO(=C1+C2+...+C10)がCP/2に設定されているとする。

## 【0040】

図2(A)に示すように、第*i*のビットGD*i*が“0”的場合には駆動部DR*i*は0Vを出力し、第*i*のビットGD*i*が“1”的場合には駆動部DR*i*は15Vを出力する。図2(A)には、GD[10:1] = “1001111111b”(末尾のbは“”内の数が2進数であることを示す)の場合を例に示している。

10

## 【0041】

まず、駆動の前に初期化を行う。即ち、GD[10:1] = “0000000000b”に設定して駆動部DR1～DR10に0Vを出力させ、電圧VQ = VC = 7.5Vを設定する。VC = 7.5Vは初期化電圧である。

## 【0042】

この初期化においてデータ電圧出力ノードNVQに蓄積された電荷は、以後の駆動時にも保存されるので、電荷保存から図2(A)の式FEが求められる。式FEにおいて符号GD*i*はビットGD*i*の値(“0”又は“1”)を表すものとする。式FEの右辺第2項を見ると、階調データGD[10:1]が1024階調のデータ電圧(5V × 0 / 1023、5V × 1 / 1023、5V × 2 / 1023、...、5V × 1023 / 1023)に変換されることが分かる。図2(B)には、一例として階調データGD[10:1]の上位3ビットを変化させたときのデータ電圧(出力電圧VQ)を示す。

20

## 【0043】

なお、以上では正極性駆動を例にとって説明したが、本実施形態では負極性駆動を行ってもよい。また正極性駆動と負極性駆動を交互に行う反転駆動を行ってもよい。負極性駆動では、初期化においてキャパシター駆動回路20の駆動部DR1～DR10の出力を全て15Vに設定し、出力電圧VQ = VC = 7.5Vを設定する。そして、階調データGD[10:1]の各ビットの論理レベルを反転(“0”を“1”に、“1”を“0”に)してキャパシター駆動回路20に入力し、容量駆動を行う。この場合、階調データGD[10:1] = “000h”(末尾のhは“”内の数が16進数であることを示す)に対してVQ = 7.5Vが出力され、階調データGD[10:1] = “3FFh”に対してVQ = 2.5Vが出力され、データ電圧範囲は7.5V～2.5Vとなる。

30

## 【0044】

以上のようにして、キャパシター回路10の容量COと電気光学パネル側容量CPとの間で電荷再分配させ、容量駆動を行うことで、階調データGD[10:1]に対応するデータ電圧を出力できる。電荷再分配により駆動を行うことで、フィードバック制御により電圧をセトリングさせるアンプ駆動に比べて高速なセトリングが可能となる。

## 【0045】

## 3. 比較例

さて、電気光学パネル200の駆動では、画像を表示する前にソース線にプリチャージ電圧を書き込むプリチャージ駆動が行われる。これは、全てのソース線を一旦同じ電圧にしてから表示用の駆動を開始して表示画質を向上させるためである。容量駆動では、このプリチャージ駆動のために、データ電圧出力ノードNVQの電荷の保存が崩れてデータ電圧に誤差が生じるという課題がある。この点について以下に説明する。

40

## 【0046】

まず、図19と図7を用いて、電気光学パネル200の構成とその駆動手法について簡単に説明する。

## 【0047】

以下、データ線DL1とソース線SL1を例に説明する。図19に示すように、電気光学パネル200のデータ線DL1は、ドライバー100のデータ線駆動回路DD1に駆動

50

される。データ線駆動回路 D D 1 は、図 1 のキャパシター回路 1 0 とキャパシター駆動回路 2 0 に対応する。データ線 D L 1 はスイッチ素子 S W E P 1 介してソース線 S L 1 に接続されている。

#### 【 0 0 4 8 】

図 7 に示すように、まずスイッチ素子 S W E P 1 がオンになり、データ線駆動回路 D D 1 がプリチャージ電圧 V P R を出力し、データ線 D L 1 とソース線 S L 1 がプリチャージ電圧 V P R に設定される。次に、スイッチ素子 S W E P 1 がオフになってデータ線駆動回路 D D 1 が初期化電圧 V C を出力し、データ線 D L 1 がプリチャージ電圧 V P R に設定される。次に、データ線駆動回路 D D 1 が容量駆動を開始し、データ線 D L 1 がデータ電圧 S V 1 で駆動される。次に、スイッチ素子 S W E P 1 がオンになってデータ線 D L 1 とソース線 S L 1 が接続され、ソース線 S L 1 にデータ電圧 S V 1 が書き込まれる。

10

#### 【 0 0 4 9 】

第 1 構成例で説明したように、データ線 D L 1 ( データ電圧出力ノード N V Q ) を初期化電圧 V C で初期化した後は、データ線 D L 1 の電荷が保存され、初期化電圧 V C を基準としたデータ電圧が出力される。しかしながら、スイッチ素子 S W E P 1 がオンになってデータ線 D L 1 とソース線 S L 1 が接続されるとき、ソース線 S L 1 はプリチャージ電圧 V P R なので ( データ線 D L 1 のソース電圧 S V 1 と異なるため ) 、データ線 D L 1 の電荷の保存が崩れてしまう。そのため、データ線 D L 1 の電圧は S V 1 からずれて S V 1 ' となり、所望のソース電圧 S V 1 に対して誤差が生じる。

20

#### 【 0 0 5 0 】

そこで本実施形態のドライバー 1 0 0 は、図 3 で後述するように基準電圧生成回路 6 0 と D / A 変換回路 7 0 と電圧駆動回路 8 0 を含む。そして、キャパシター回路 1 0 による容量駆動を行って出力電圧 V Q がデータ電圧に近づいた後に、電圧駆動回路 8 0 のアンプ回路 A M V D による電圧駆動を行う。D / A 変換回路 7 0 は階調データ G D [ 1 0 : 1 ] を D / A 変換して出力し、それを受けたアンプ回路 A M V D がデータ電圧を出力する。図 7 に示すように、電圧駆動の開始はソース線 S L 1 のスイッチ素子 S W E P 1 がオンになる前である。

20

#### 【 0 0 5 1 】

このように容量駆動により高速にデータ電圧に近づけた後にアンプ回路 A M V D による駆動を行うことで、容量駆動のみの場合に比べて高精度にデータ電圧を出力できる。即ち、上述のようにスイッチ素子 S W E P 1 がオンすることでデータ線 D L 1 の電圧に誤差が生じる ( S V 1 ' ) が、アンプ回路 A M V D が電圧 S V 1 を出力することで、その誤差を解消して正確な電圧 S V 1 に戻すことができる。

30

#### 【 0 0 5 2 】

しかしながら、アンプ回路 A M V D はフィードバックによって出力電圧 A M Q を制御しているため、入力電圧 A M I のセトリングに時間がかかると、それに伴って出力電圧 A M Q のセトリング時間も延びてしまう。具体的には、基準電圧生成回路 6 0 は抵抗素子 R D 1 ~ R D 1 0 2 4 の抵抗分割によって基準電圧 V R 1 ~ V R 1 0 2 4 を生成しており、そのうちの 1 つが D / A 変換回路 7 0 により選択される。そのため、基準電圧生成回路 6 0 の抵抗とアンプ回路 A M V D の入力ノード N A M I の寄生容量とで R C の時定数が決定され、その時定数で入力ノード N A M I の電圧がセトリングすることになる。入力ノード N A M I には、アンプ回路 A M V D の入力ゲート容量や、D / A 変換回路 7 0 のスイッチ素子 S W D 1 ~ S W D 1 0 2 4 のゲート - ソース ( 又はゲート - ドレイン ) 間の容量などが寄生している。

40

#### 【 0 0 5 3 】

また、図 16 等で後述するように、基準電圧生成回路 6 0 には複数の D / A 変換回路 ( D A A M 1 、 D A A M 2 など ) 及びアンプ回路 ( A M V D 1 、 A M V D 2 など ) が接続されている。D / A 変換回路は、基準電圧生成回路 6 0 の抵抗分圧のタップとアンプ回路の入力ノードとをスイッチ素子で接続するため、各 D / A 変換回路の出力が基準電圧生成回路 6 0 を介して相互にカップリングした状態となっている。そのため、ある D / A 変換回

50

路の出力（アンプ回路の入力）がセトリングしていない場合、それが他のD/A変換回路の出力にも影響してクロストークを生じてしまう。このような点からもD/A変換回路の出力（アンプ回路の入力）を高速にセトリングさせることは重要である。

#### 【0054】

図4に、本実施形態のドライバーの比較例におけるD/A変換回路の出力(AMI)及びアンプ回路の出力(AMQ)のシミュレーション結果を示す。比較例の構成は、後述する図3の構成例において本実施形態の補助用電圧設定回路85を含まない構成である。

#### 【0055】

図4には、初期化電圧 $V_C = 7.5V$ からデータ電圧の最大値 $12.5V$ に上昇させるときのシミュレーション結果を示す。時間 $t_{a1}$ においてD/A変換回路70がD/A変換結果である $12.5V$ をアンプ回路AMVDの入力ノードNAMIに出力し始める。そうすると、アンプ回路AMVDの入力電圧AMIが上昇していき、時間 $t_{a2}$ で入力電圧AMIが $12.5V$ に達する。時間 $t_{a2}$ は、例えばRCの時定数に対して6に相当する。 $t_{a2} - t_{a1}$ は約 $30\text{ns}$ であり、アンプ回路AMVDの出力電圧AMQが $12.5V$ に正確にセトリングするためには、 $30\text{ns}$ よりも更に時間がかかることになる。WXGAでは画素の書き込み時間は $70\text{ns}$ なので、セトリング可能であっても $30\text{ns}$ は長い上、WXGAよりも高精細化するためには問題点となる。

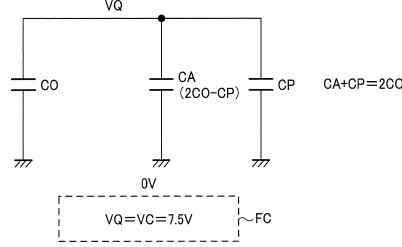

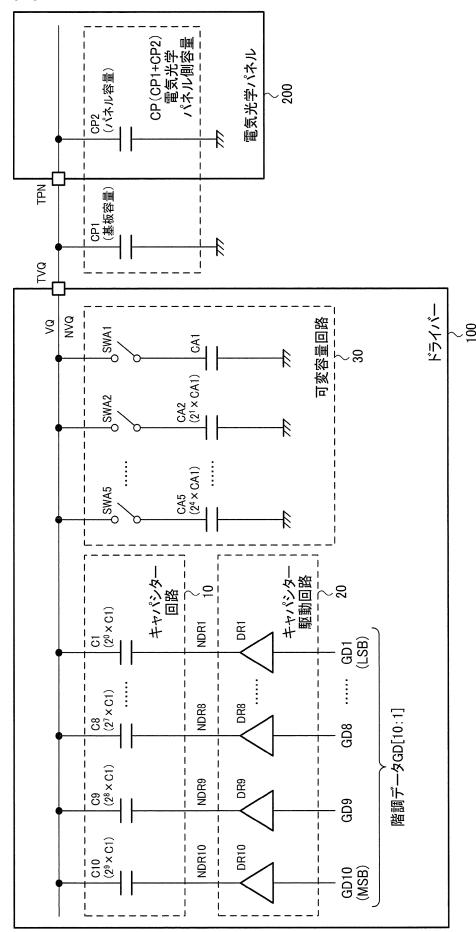

#### 【0056】

##### 4. ドライバーの第2構成例

図3に、上記のような課題を解決できる本実施形態のドライバーの第2構成例を示す。このドライバー100は、キャパシタ回路10、キャパシタ駆動回路20、基準電圧生成回路60、D/A変換回路70(電圧選択回路)、電圧駆動回路80、補助用電圧設定回路85、データ電圧出力端子TVQを含む。なお、既に説明した構成要素と同一の構成要素には同一の符号を付し、その構成要素については適宜説明を省略する。

#### 【0057】

補助用電圧設定回路85は、データ電圧(データ電圧出力端子TVQの電圧)に対応する電圧を電圧駆動回路80の入力ノードNAMIに設定する回路である。具体的には、補助用電圧設定回路85は、補助用キャパシタ回路82と、補助用キャパシタ駆動回路84と、バランス用キャパシタCSBと、を含む。

#### 【0058】

補助用キャパシタ回路82は、第1～第10の補助用キャパシタCS1～CS10(広義には第1～第nの補助用キャパシタCS1～CSn)と、スイッチ回路SWSと、を含む。また補助用キャパシタ駆動回路84は、第1～第10の補助用駆動部DS1～DS10(広義には第1～第nの補助用駆動部DS1～DSn)を含む。

#### 【0059】

補助用キャパシタCS1～CS10の第iの補助用キャパシタCSI(iはn=1以下の自然数)の一端は、補助用キャパシタ駆動ノードNDSiに接続され、第iの補助用キャパシタCSIの他端はノードNSQに接続される。補助用キャパシタCS1～CS10は、2の累乗で重み付けされた容量値を有している。具体的には第iの補助用キャパシタCSIの容量値は $2^{(i-1)} \times CS_1$ である。

#### 【0060】

第1～第10の補助用駆動部DS1～DS10の第iの補助用駆動部DSiの入力ノードには、階調データGD[10:1]の第iのビットGDiが入力される。第iの補助用駆動部DSiの出力ノードは、第iの補助用キャパシタ駆動ノードNDSiである。

#### 【0061】

第iの補助用駆動部DSiは、ビットGDiが第1論理レベル“0”的時に第1電圧レベル(0V)を出力し、ビットGDiが第2論理レベル“1”的時に第2電圧レベル(15V)を出力する。例えば、第iの補助用駆動部DSiは、入力された論理レベル(例えばロジック電源の3V)を補助用駆動部DSiの出力電圧レベル(例えば15V)にレベルシフトするレベルシフターや、そのレベルシフターの出力をバッファリングするバ

10

20

30

40

50

ツファーリ回路で構成される。

#### 【0062】

スイッチ回路SWSは、補助用キャパシターCS1～CS10が接続されるノードNSQと電圧駆動回路80の入力ノードNAMIとの間に設けられる。スイッチ回路SWSがオンした場合にはノードNSQとノードNAMIが接続される。スイッチ回路SWSのオン・オフ制御信号は、例えば図12の制御回路40から供給される。スイッチ回路SWAMは、例えば1つのスイッチ素子で構成されてもよいし、或いは複数のスイッチ素子を含む回路（例えばトランスマルチплекс等）で構成されてもよい。或いは、補助用キャパシターCS1～CS10がノードNSQに共通接続されるのではなく、補助用キャパシターCS1～CS10の各キャパシターとノードNAMIとの間にそれぞれスイッチ素子が設けられてもよい。10

#### 【0063】

バランス用キャパシターCSBは、その一端がノードNSQに接続され、他端が低電位側電源VSSのノードに接続される。バランス用キャパシターCSBの容量と電圧駆動回路80の入力ノードNAMIの寄生容量との加算値をCSB'とする場合、例えば $CSB' = 2CSO$  ( $CSO = CS1 + CS2 + \dots + CS10$ )となるように、バランス用キャパシターCSBの容量が設定される。これにより、図2(A)で説明した容量駆動と同じ原理で階調データGD[10:1]に対応する電圧(7.5V～12.5V)がノードNAMIに出力される。ノードNAMIの寄生容量は、例えばプロセスパラメーターやレイアウト（配線長など）等から見積もればよい。或いは、シミュレーション結果に基づいて見積もればよい。20

#### 【0064】

なお、最終的にはD/A変換回路70が電圧駆動回路80の入力電圧AMIを決めるので、補助用電圧設定回路85の出力とD/A変換回路70の出力は厳密に一致している必要はない。そのため、 $CSB' = 2CSO$ の関係も、おおよそ成り立つればよい。

#### 【0065】

基準電圧生成回路60は、階調データの各値に対応する基準電圧（階調電圧）を生成する回路である。例えば、10ビットの階調データGD[10:1]に対応して1024階調の基準電圧VR1～VR1024を生成する。

#### 【0066】

具体的には、基準電圧生成回路60は、高電位側電源と初期化電圧VC（コモン電圧）のノードとの間に直列接続された第1～第1024の抵抗素子RD1～RF1024を含む。そして、抵抗素子RD1～RF1024のタップから、電圧分割により得られた第1～第1024の基準電圧VR1～VR1024を出力する。30

#### 【0067】

D/A変換回路70は、基準電圧生成回路60からの複数の基準電圧の中から、階調データGD[10:1]に対応する基準電圧を選択する回路である。選択された基準電圧は電圧駆動回路80の入力ノードNAMIに入力電圧AMIとして出力される。

#### 【0068】

具体的には、D/A変換回路70は、基準電圧VR1～VR1024が一端に供給される第1～第1024のスイッチ素子SWD1～SWD1024を含む。スイッチ素子SWD1～SWD1024の他端は共通接続されている。スイッチ素子SWD1～SWD1024のうち、いずれか1つが階調データGD[10:1]に対応してオンになり、そのスイッチ素子に供給される基準電圧が電圧AMIとして出力される。スイッチ素子SWD1～SWD1024のオン・オフ制御信号は、例えば図12の制御回路40から供給される。或いは、D/A変換回路70が階調データGD[10:1]をデコードするデコーダーを有し、制御回路40からデコーダーに階調データGD[10:1]が入力されてもよい。40

#### 【0069】

なお、D/A変換回路70の構成は図3に限定されない。例えば、スイッチ素子を多段

に設けて勝ち抜き方式での選択を行うトーナメント方式であってもよい。トーナメント方式では、例えば 16 個の基準電圧から 1 つ選択するセレクターを 2 段 ( $16 \times 16 = 256$ ) 重ね、それにより選択された 4 個の基準電圧から 1 つ選択するセレクター ( $256 \times 4 = 1024$ ) を 3 段目に設ける。

#### 【0070】

電圧駆動回路 80 は、D/A 変換回路 70 からの電圧 A M I を增幅し、その増幅した電圧をデータ電圧出力端子 T V Q へ出力する（電圧駆動）。電圧駆動回路 80 は、アンプ回路 A M V D、電圧駆動用スイッチ回路 S W A M を含む。

#### 【0071】

アンプ回路 A M V D は演算增幅回路を有し、その演算增幅回路は例えばボルテージフォロアに構成される。そのボルテージフォロアの入力には、D/A 変換回路 70 からの電圧 A M I が入力される。10

#### 【0072】

電圧駆動用スイッチ回路 S W A M は、アンプ回路 A M V D の出力とデータ電圧出力ノード N V Q の接続・遮断を行う回路である。電圧駆動用スイッチ回路 S W A M は、例えば 1 つのスイッチ素子で構成されてもよいし、或いは複数のスイッチ素子を含む回路で構成されてもよい。電圧駆動用スイッチ回路 S W A M のオン・オフ制御信号は、例えば図 12 の制御回路 40（不図示のタイミングコントローラー）から供給される。

#### 【0073】

##### 5. 第 2 構成例の動作

20

図 5 に、上記ドライバーの第 2 構成例の補助用電圧設定回路についての動作タイミングチャートを示す。なおスイッチ回路 S W S、S W A S は、ハイレベルでオンを表し、ローレベルでオフを表すものとする。

#### 【0074】

図 5 に示すように、キャパシター駆動回路 20 に階調データ G D [ 10 : 1 ] が入力されるとキャパシター回路 10 による容量駆動が開始される。この容量駆動の開始時において、補助用キャパシター駆動回路 84 に階調データ G D [ 10 : 1 ] が入力され、スイッチ回路 S W S がオンになる。これにより、補助用キャパシター回路 82 とバランス用キャパシター C S B とノード N A M I の寄生容量との間で電荷再分配が生じ、アンプ回路 A M V D の入力ノード N A M I の電圧 A M I がデータ電圧に急速に漸近する。30

#### 【0075】

容量駆動の開始時には、D/A 変換回路 70 も D/A 変換結果の出力を開始する。即ち、補助用電圧設定回路 85 により電圧 A M I をデータ電圧に急速に漸近させると共に、D/A 変換回路 70 が高精度なデータ電圧を出力する。スイッチ回路 S W S がオフになると、D/A 変換回路 70 の出力から補助用キャパシター回路 82 やバランス用キャパシター C S B が見えなくなるので、最終的に電圧 A M I は D/A 変換回路 70 が出力する高精度なデータ電圧となる。補助用電圧設定回路 85 により電圧 A M I はデータ電圧に接近しているので、D/A 変換回路 70 により正確なデータ電圧にセトリングするまでの時間は短くて済む。スイッチ回路 S W S がオンからオフになった後、電圧駆動用スイッチ回路 S W A M がオフからオンになり、電圧駆動が開始される。40

#### 【0076】

なお、スイッチ回路 S W S のオン期間は、補助用電圧設定回路 85 により電圧 A M I が十分にデータ電圧に接近する期間に設定しておけばよい。例えば、補助用電圧設定回路 85 により電圧 A M I が急峻に変化する期間だけスイッチ回路 S W S をオンさせておいてよいし、その変化の時定数に基づいて（例えば時定数の数倍等の）オン期間を設定してもよい。

#### 【0077】

図 6 に、本実施形態における D/A 変換回路の出力（A M I）及びアンプ回路の出力（A M Q）のシミュレーション結果を示す。図 6 には、初期化電圧 V C = 7.5 V からデータ電圧の最大値 12.5 V に上昇させるときのシミュレーション結果を示す。50

## 【0078】

時間  $t_{b1}$  において補助用電圧設定回路 85（と D/A 変換回路 70）が電圧 12.5 V をアンプ回路 AMVD の入力ノード NAMI に出力し始め、アンプ回路 AMVD の入力電圧 AMI が急速に上昇する。時間  $t_{b1}$  から約 9 ns 後の時間  $t_{b2}$  には、入力電圧 AMI が 12.5 V に達する。図 4 で説明した比較例では 12.5 V に達するまで 30 ns かかっており、本実施形態では、その時間を約 1/3 に短縮できている。このようにアンプ回路 AMVD の入力電圧 AMI が早くセトリングすることで、その分だけアンプ回路 AMVD の出力電圧 AMQ を早くセトリングさせることができることが可能となり、画素の書き込み時間内に正確なデータ電圧を出力できる。

## 【0079】

10

次に、電圧駆動回路 80 の動作について説明する。図 7 に、ドライバーの第 2 構成例の電圧駆動回路についての動作タイミングチャートを示す。以下では、図 19 に示すデータ線 DL1、スイッチ素子 SWEP1、ソース線 SL1、SL9 を例にとって説明する。

## 【0080】

まず、プリチャージ駆動と初期化電圧 VC による初期化を行ふ。次に、容量駆動を開始してデータ線 DL1 をデータ電圧 SV1 で駆動する。容量駆動を開始してから期間 T1 が経過した後に電圧駆動回路 80 のスイッチ回路 SWAM をオンにして、アンプ回路 AMVD がデータ電圧 SV1 と同じ電圧でデータ線 DL1 を駆動する。次に、スイッチ素子 SWEP1 がオン（スイッチ回路 SWAM のオンと同時でもよい）になり、データ線 DL1 にソース線 SL1 が接続される。上述したようにデータ線 DL1 の電圧が SV1' になるが、電圧駆動回路 80 によりデータ電圧 SV1 が供給されるので、ソース線 SL1 にはデータ電圧 SV1 が書き込まれる。

20

## 【0081】

次に、スイッチ素子 SWEP1 がオフになり、その後に電圧駆動回路 80 のスイッチ回路 SWAM がオフになる。スイッチ回路 SWAM がオンしている期間を、電圧駆動を行う期間 T2 とする。

## 【0082】

30

ソース線 SL9 についても上記と同様にして駆動される。即ち、電圧駆動の期間 T2 が終了した後に容量駆動が開始され、データ線 DL1 にデータ電圧 SV9 が出力される。期間 T1 が経過した後、スイッチ回路 SWAM がオンになり、アンプ回路 AMVD がデータ電圧 SV9 と同じ電圧でデータ線 DL1 を駆動する。次に、スイッチ素子 SWEP9 がオンになり、ソース線にデータ電圧 SV9 が書き込まれる。

## 【0083】

このように電圧駆動回路 80 が電圧駆動を行うことで、容量駆動のみを用いる場合に比べて、ソース線 SL1、SL9 に書き込まれるデータ電圧 SV1、SV9 の誤差を小さくできる。

## 【0084】

## 6. ドライバーの変形例

以上の実施形態では電圧駆動回路 80 がボルテージフォロア（広義には非反転増幅回路）で構成される場合を例に説明したが、電圧駆動回路 80 の構成はこれに限定されない。例えば、以下のような変形実施が可能である。

40

## 【0085】

図 8 に、本実施形態のドライバーの変形構成例を示す。このドライバー 100 は、キャパシター回路 10、キャパシター駆動回路 20、基準電圧生成回路 60、D/A 変換回路 70（電圧選択回路）、電圧駆動回路 80、補助用電圧設定回路 85、データ電圧出力端子 TVQ を含む。なお、既に説明した構成要素と同一の構成要素には同一の符号を付し、その構成要素については適宜説明を省略する。

## 【0086】

電圧駆動回路 80 は、反転増幅回路 AMIV、電圧駆動用スイッチ回路 SWAM を含む。反転増幅回路 AMIV は、入力電圧 AMI を反転増幅（ $AMIV = VC - AMI$  とした

50

場合、例えば  $A M Q = V C + A M Q$  を出力する回路である。例えば、反転増幅回路  $A M I V$  は、正極入力端子に基準電圧（例えばコモン電圧  $V C$ ）が入力される演算増幅回路と、反転増幅回路  $A M I V$  の入力ノード  $N A M I$  と演算増幅回路の負極入力端子との間に設けられる入力キャパシターと、演算増幅回路の出力端子と演算増幅回路の負極入力端子との間に設けられる帰還キャパシターと、で構成される。

#### 【0087】

補助用電圧設定回路 85 は、補助用キャパシターリード回路 82 と、補助用キャパシターリード回路 84 と、バランス用キャパシターカソード CSB と、を含む。補助用キャパシターリード回路 84 は、反転バッファーである第 1 ~ 第 10 の補助用駆動部  $D S X 1 \sim D S X 10$  を含む。即ち、第  $i$  の補助用駆動部  $D S i$  は、ビット  $G D i$  が第 1 論理レベル “0” の場合に第 2 電圧レベル (15V) を出力し、ビット  $G D i$  が第 2 論理レベル “1” の場合に第 1 電圧レベル (0V) を出力する。10

#### 【0088】

なお、第 1 ~ 第 10 の補助用駆動部  $D S X 1 \sim D S X 10$  を非反転バッファーで構成し、階調データ  $G D [10 : 1]$  のビット  $G D 1 \sim G D 10$  の論理レベルを反転して第 1 ~ 第 10 の補助用駆動部  $D S X 1 \sim D S X 10$  に入力してもよい。

#### 【0089】

基準電圧生成回路 60 は、初期化電圧  $V C$  (コモン電圧) のノードと低電位側電源  $V S S$  のノードとの間を抵抗分割する抵抗素子  $R D 1 \sim R D 1024$  を有する。抵抗分割により得られる基準電圧  $V R 1 \sim V R 1024$  の電圧範囲は 7.5V ~ 2.5V である。20

#### 【0090】

補助用電圧設定回路 85 と D/A 変換回路 70 は、階調データ  $G D [10 : 1] = "000h"$  に対して 7.5V を出力し、階調データ  $G D [10 : 1] = "3FFh"$  に対して 2.5V を出力する。例えば反転増幅回路  $A M I V$  のゲインを “-1” とすると、補助用電圧設定回路 85 と D/A 変換回路 70 の出力電圧範囲 7.5V ~ 2.5V に対して、反転増幅回路  $A M I V$  の出力電圧範囲は 7.5V ~ 12.5V となる。

#### 【0091】

以上の実施形態によれば、ドライバー 100 は電圧駆動回路 80 と D/A 変換回路 70 と補助用キャパシターリード回路 84 と補助用キャパシターリード回路 82 とを含む。電圧駆動回路 80 は、入力ノード  $N A M I$  の電圧  $A M I$  を増幅し、その増幅した電圧をデータ電圧としてデータ電圧出力端子  $T V Q$  に出力する。D/A 変換回路 70 は、複数の基準電圧  $V R 1 \sim V R 1024$  から階調データ  $G D [10 : 1]$  に対応する基準電圧を選択し、その選択された基準電圧を電圧駆動回路 80 の入力ノード  $N A M I$  に出力する。補助用キャパシターリード回路 84 は、階調データ  $G D [10 : 1]$  に対応する第 1 ~ 第 10 の補助用キャパシターリード電圧を第 1 ~ 第 10 の補助用キャパシターリード用ノード  $N D S 1 \sim N D S 10$  に出力する。補助用キャパシターリード回路 82 は、電圧駆動回路 80 の入力ノード  $N A M I$  と第 1 ~ 第 10 の補助用キャパシターリード用ノード  $N D S 1 \sim N D S 10$  との間に設けられる第 1 ~ 第 10 の補助用キャパシターカソード  $C S 1 \sim C S 10$  を有する。30

#### 【0092】

さて、比較例で説明したように、D/A 変換回路 70 の出力電圧のセトリング時間は、基準電圧生成回路 60 の抵抗と入力ノード  $N A M I$  の寄生抵抗との  $C R$  時定数でおおよそ決まる。このセトリング時間を短くするには、基準電圧生成回路 60 の抵抗値を下げる必要があるが、抵抗値を下げるヒューダー抵抗を流れる電流が増加し、消費電流が増えるという課題がある。また、基準電圧生成回路 60 の抵抗値を下げすぎると、配線抵抗による電圧ドロップが大きくなり、例えば基準電圧生成回路 60 を介したチャンネル間のクロストークが発生する等の課題がある。40

#### 【0093】

この点、本実施形態によれば、補助用キャパシターリード回路 82 と入力ノード  $N A M I$  の寄生抵抗（とバランス用キャパシターカソード  $C S B$ ）との間の電荷再分配により、電圧駆動回路 80 の入力ノード  $N A M I$  の電圧  $A M I$  を D/A 変換回路 70 の出力電圧に高速に近づける50

ことが可能となる。電荷再分配のセトリング時間は C R 時定数でおおよそ決まるが、例えばスイッチ回路 S W S のオン抵抗を小さくしておくことで、セトリング時間を短くできる。基準電圧生成回路 6 0 の抵抗を小さくすると消費電流の増加等の問題があるが、スイッチ回路 S W S のオン抵抗を小さくしても消費電流の増加等の問題はないので、D / A 変換回路 7 0 よりも高速なセトリングを実現できる。

#### 【 0 0 9 4 】

また本実施形態では、ドライバー 1 0 0 はキャパシター駆動回路 2 0 とキャパシター回路 1 0 と電圧駆動回路 8 0 を含む。キャパシター駆動回路 2 0 は、階調データ G D [ 1 0 : 1 ] に対応する第 1 ~ 第 1 0 のキャパシター駆動電圧 ( 0 V 又は 1 5 V ) を第 1 ~ 第 1 0 のキャパシター駆動用ノード N D R 1 ~ N D R 1 0 に出力する。キャパシター回路 1 0 は、第 1 ~ 第 1 0 のキャパシター駆動用ノード N D R 1 ~ N D R 1 0 とデータ電圧出力端子 T V Q との間に設けられる第 1 ~ 第 1 0 のキャパシター C 1 ~ C 1 0 を有する。そして電圧駆動回路 8 0 は、キャパシター駆動回路 2 0 とキャパシター回路 1 0 により電気光学パネル 2 0 0 を駆動する容量駆動が開始された後に、階調データ G D [ 1 0 : 1 ] に対応するデータ電圧をデータ電圧出力端子 T V Q に出力する電圧駆動を行う。

#### 【 0 0 9 5 】

さて、比較例で説明したように、容量駆動ではキャパシター間の電荷再分配によってデータ電圧を出力するため、電荷を自由に供給できるアンプ回路に比べてデータ電圧の精度が低くなる場合がある。例えば、上述したようにプリチャージされたソース線がデータ線に接続されることでデータ電圧に誤差が発生する。

#### 【 0 0 9 6 】

この点、本実施形態によれば、容量駆動が開始された後に電圧駆動回路 8 0 によりデータ電圧を出力するため、高精度なデータ電圧の出力が可能となる。即ち、容量駆動によって出力電圧 V Q を高速にデータ電圧に漸近させると共に、その後に電圧駆動を行うことによって高精度なデータ電圧で画素の書き込みを行うことができる。

#### 【 0 0 9 7 】

上述したように、電気光学パネル 2 0 0 のデータ線とソース線が接続された際にはデータ電圧出力ノード N V Q の電荷が（厳密には）保存しなくなるが、電圧駆動によって電荷が供給されるため、最終的には電荷が保存した状態に戻すことができる。即ち、ソース線が接続される前には電荷が保存しており、そのときデータ電圧出力ノード N V Q は電圧 S V 1 である。ソース線 S L 1 の接続によってデータ線 D L 1 の電圧が S V 1 ' となった後、その電圧を S V 1 に戻すことによって、電荷がソース線を接続する前の状態に戻り、以後も電荷が保存された状態として容量駆動を行うことができる。

#### 【 0 0 9 8 】

このとき、電圧駆動回路 8 0 が供給する電荷はソース線 1 本分なので、基板容量やデータ線の容量を駆動する場合に比べて、供給する電荷は少ない。即ち、容量駆動を用いずに最初からアンプ回路で駆動する場合に比べて、電荷の供給能力を下げることが可能である。そのため、高速なセトリングが必要な高精細な電気光学パネル 2 0 0 であっても、消費電力を抑制できる。

#### 【 0 0 9 9 】

以上のように、容量駆動を用いることで高速なセトリングが可能となり、アンプ回路だけで駆動する場合に比べて、より高精細な電気光学パネル 2 0 0 を駆動することができる。また、容量駆動と電圧駆動を組み合わせることで、消費電力を抑制しつつ高精度なデータ電圧で画素を駆動することが可能となる。このとき、電圧駆動回路 8 0 の入力電圧 A M I ( D / A 変換回路 7 0 の出力電圧 ) のセトリング時間が電圧駆動のセトリング時間に影響を与えるが、補助用電圧設定回路 8 5 を設けたことで入力電圧 A M I を高速にセトリングできる。

#### 【 0 1 0 0 】

また本実施形態では、第 1 ~ 第 1 0 の補助用キャパシター C S 1 ~ C S 1 0 の第 i の補助用キャパシター C S i の容量は、第 1 ~ 第 1 0 のキャパシター C 1 ~ C 1 0 の第 i のキ

10

20

30

40

50

ヤパシター C i の容量よりも小さい。

**【 0 1 0 1 】**

電気光学パネル側容量 C P は例えば 50 pF ~ 120 pF と非常に大きいが、それに比べてアンプ回路 A M V D の入力ノード N A M I の寄生抵抗（アンプ回路 A M V D の入力ゲート容量、ノード N A M I の配線容量等）は小さい。駆動側の容量と被駆動側の容量との比は 1 : 2 なので、被駆動側の容量が小さい補助用キャパシター回路 8 2 の容量を小さくできる。これにより、電荷再分配の C R 時定数が小さくなるので、アンプ回路 A M V D の入力電圧 A M I を補助用電圧設定回路 8 5 により高速に駆動できる。

**【 0 1 0 2 】**

また本実施形態では、補助用キャパシター回路 8 2 は、電圧駆動回路 8 0 の入力ノード N A M I と第 1 ~ 第 10 の補助用キャパシター C S 1 ~ C S 10 との間に設けられるスイッチ回路 S W S を有する。10

**【 0 1 0 3 】**

D / A 変換回路 7 0 の出力から見ると、補助用キャパシター回路 8 2 （とバランス用キャパシター C S B ）は負荷容量として見えるため、D / A 変換回路 7 0 の出力の C R 時定数が増える。そのため、補助用電圧設定回路 8 5 が出力する電圧と D / A 変換回路 7 0 が出力する電圧が微妙に異なる場合、アンプ回路 A M V D の入力電圧 A M I が D / A 変換回路 7 0 の出力にセトリングする時間が増えてしまう。

**【 0 1 0 4 】**

この点、本実施形態によれば、スイッチ回路 S W S をオフすることでアンプ回路 A M V D の入力ノード N A M I から補助用キャパシター回路 8 2 （とバランス用キャパシター C S B ）を遮断できる。これにより、アンプ回路 A M V D の入力電圧 A M I が D / A 変換回路 7 0 の出力にセトリングする時間を増加させることなく、補助用電圧設定回路 8 5 による高速なセトリングが可能となる。20

**【 0 1 0 5 】**

また本実施形態では、スイッチ回路 S W S は、電圧駆動回路 8 0 がデータ電圧をデータ電圧出力端子 T V Q に出力する電圧駆動を開始する前に、オンからオフになる。

**【 0 1 0 6 】**

このようにすれば、まずスイッチ回路 S W S をオンにして補助用電圧設定回路 8 5 により入力ノード N A M I を高速に駆動し、その後にスイッチ回路 S W S をオフにすることで補助用電圧設定回路 8 5 による C R 時定数の増加を避け、D / A 変換回路 7 0 により入力ノード N A M I に正確な電圧を供給できる。そして、スイッチ回路 S W S をオフにした後にアンプ回路 A M V D による電圧駆動を開始することで、D / A 変換回路 7 0 による正確な電圧により電圧駆動を行うことができる。30

**【 0 1 0 7 】**

また本実施形態では、電圧駆動回路 8 0 は、データ電圧を出力するアンプ回路 A M V D と、アンプ回路 A M V D の出力とデータ電圧出力端子 T V Q との間に設けられるスイッチ回路 S W A M と、を有する。そして、補助用キャパシター回路 8 2 のスイッチ回路 S W S は、電圧駆動用スイッチ回路 S W A M がオフからオンになる前に、オンからオフになる。

**【 0 1 0 8 】**

アンプ回路 A M V D による駆動よりも容量駆動の方が高速であるため、電圧駆動と容量駆動を同時に行うと、アンプ回路 A M V D の出力に引っ張られてデータ電圧への漸近が遅くなる。この点、本実施形態によれば、スイッチ回路 S W A M を設けたことで、アンプ回路 A M V D の出力とデータ電圧出力端子 T V Q を遮断することが可能となる。即ち、第 1 期間（図 7 の T 1 ）においてスイッチ回路 S W A M をオフにして容量駆動によりデータ電圧に近い電圧まで高速に近づけた後に、第 2 期間（図 7 の T 2 ）においてスイッチ回路 S W A M をオンにしてアンプ回路 A M V D の高精度な出力をデータ電圧出力端子 T V Q に接続できる。これにより、高速な容量駆動と高精度なアンプ駆動を両立できる。

**【 0 1 0 9 】**

そして、電圧駆動用スイッチ回路 S W A M がオフからオンになる前に、補助用キャパシ40

50

ター回路 8 2 のスイッチ回路 S W S がオンからオフになることで、電圧駆動を開始する前に補助用キャパシター回路 8 2 を D / A 変換回路 7 0 の出力から遮断できる。

#### 【 0 1 1 0 】

また変形構成例で説明したように、電圧駆動回路 8 0 は反転増幅回路であってもよい。この場合、補助用キャパシター駆動回路 8 4 は、階調データ G D [ 1 0 : 1 ] の論理反転データ（各ビットの“ 0 ”を“ 1 ”に、“ 1 ”を“ 0 ”に反転したデータ）に対応する第 1 ~ 第 1 0 の補助用キャパシター駆動電圧を出力する。

#### 【 0 1 1 1 】

このようにすれば、補助用電圧設定回路 8 5 が反転出力を行う（容量駆動の出力範囲 7 . 5 V ~ 1 2 . 5 V を電圧 V C = 7 . 5 V に対して反転した電圧範囲 7 . 5 V ~ 2 . 5 V を出力する）ので、反転増幅回路を用いて電圧駆動を行うことができる。10

#### 【 0 1 1 2 】

反転増幅回路ではサミングノードの電圧（演算増幅回路の差動対の入力電圧）が一定の電圧（例えば電圧 V C ）に固定される。即ち、出力レンジの端（例えば 1 2 . 5 V ）でも差動対の入力電圧が変化しないので、ボルテージフォロア等の非反転増幅回路に比べて出力レンジの広い範囲において良好な特性（例えばセトリング時間）を得やすい。

#### 【 0 1 1 3 】

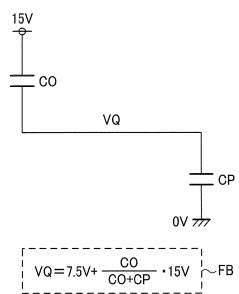

##### 7 . ドライバーの第 3 構成例

次に、図 1 で説明した第 1 構成例におけるデータ電圧について再考する。図 2 ( A ) では、キャパシター回路 1 0 の容量 C O と電気光学パネル側容量 C P の比が 1 : 2 に設定されていることを前提としていたが、ここでは比が 1 : 2 でない場合も含めてデータ電圧の最大値を考える。以下で説明するように、種々の電気光学パネル 2 0 0 に対して汎用のドライバー 1 0 0 を作ろうとすると、比を 1 : 2 に保てなくなり、一定のデータ電圧範囲を出力できないという課題がある。20

#### 【 0 1 1 4 】

図 9 ( A ) に示すように、まずキャパシター回路 1 0 の初期化を行う。即ち、階調データ G D [ 1 0 : 1 ] = “ 0 0 0 h ”（末尾の h は“ ” 内の数が 1 6 進数であることを示す）を設定して駆動部 D R 1 ~ D R 1 0 の全ての出力を 0 V に設定する。また図 9 ( A ) の式 F A に示すように電圧 V Q = V C = 7 . 5 V を設定する。この初期化においてキャパシター回路 1 0 の容量 C O と電気光学パネル側容量 C P に蓄積された電荷の総量は、以降のデータ電圧出力において保存される。これにより、初期化電圧 V C ( コモン電圧 ) を基準としたデータ電圧が出力されることになる。30

#### 【 0 1 1 5 】

図 9 ( B ) に示すように、データ電圧の最大値が出力されるのは、階調データ G D [ 1 0 : 1 ] = “ 3 F F h ” を設定して駆動部 D R 1 ~ D R 1 0 の全ての出力を 1 5 V に設定した場合である。このときのデータ電圧は電荷保存の法則から求めることができ、図 9 ( B ) の式 F B に示す値となる。

#### 【 0 1 1 6 】

図 9 ( C ) に示すように、所望のデータ電圧範囲が例えば 5 V であるとする。初期化電圧 V C = 7 . 5 V が基準なので、最大値は 1 2 . 5 V である。このデータ電圧が実現されるのは、式 F B から C O / ( C O + C P ) = 1 / 3 の場合である。即ち、電気光学パネル側容量 C P に対して、キャパシター回路 1 0 の容量 C O = C P / 2 ( 即ち、 C P = 2 C O ) に設定しておけばよい。ある特定の電気光学パネル 2 0 0 と実装基板に対しては、このように C O = C P / 2 に設計することで、 5 V のデータ電圧範囲を実現できる。40

#### 【 0 1 1 7 】

しかしながら、電気光学パネル側容量 C P は電気光学パネル 2 0 0 の種類や実装基板の設計に応じて 5 0 p F ~ 1 2 0 p F 程度の幅をもっている。また同一種類の電気光学パネル 2 0 0 及び実装基板であっても、複数の電気光学パネルを接続する場合には（例えばプロジェクトでは R 、 G 、 B の 3 つの電気光学パネルを接続する）、各電気光学パネルとドライバーの接続配線の長さが異なるため、基板容量 C P 1 が同一になるとは限らない。50

**【0118】**

例えば、ある電気光学パネル200と実装基板に対してキャパシター回路10の容量COをCP = 2COとなるように設計したとする。このキャパシター回路10に対して別種の電気光学パネルや実装基板を接続した場合、CP = CO / 2や、CP = 5COとなる可能性がある。CP = CO / 2の場合、図9(C)に示すように、データ電圧の最大値が17.5Vになり、電源電圧15Vを超えてしまう。この場合、データ電圧の範囲だけでなくドライバー100や電気光学パネル200の耐圧の観点からも問題がある。また、CP = 5COの場合、データ電圧の最大値が10Vとなり、十分なデータ電圧範囲が得られない。

**【0119】**

10

このように、キャパシター回路10の容量COを電気光学パネル側容量CPに応じて設定した場合、その電気光学パネル200や実装基板に対してドライバー100が専用設計になってしまいという課題がある。即ち、電気光学パネル200の種類や実装基板の設計が変わるたびに、それ専用のドライバー100を設計し直さなければならない。

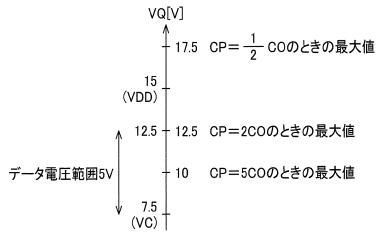

**【0120】**

図10に、上記のような課題を解決できる本実施形態のドライバーの第3構成例を示す。このドライバー100は、キャパシター回路10、キャパシター駆動回路20、可変容量回路30を含む。なお、既に説明した構成要素と同一の構成要素には同一の符号を付し、その構成要素については適宜説明を省略する。

**【0121】**

20

可変容量回路30は、データ電圧出力ノードNVQに接続される容量であり、その容量値を可変に設定できる回路である。具体的には、可変容量回路30は、第1～第mのスイッチ素子SWA1～SWAm(mは2以上の自然数)、第1～第mの調整用キャパシターカA1～カAmを含む。なお以下ではm=6の場合を例に説明する。

**【0122】**

第1～第6のスイッチ素子SWA1～SWA6は、例えばP型又はN型のMOSトランジスター、或はP型MOSトランジスターとN型MOSトランジスターを組み合わせたトランスファーゲートで構成される。スイッチ素子SWA1～SWA6の第sのスイッチ素子SWAs(sはm=6以下の自然数)の一端は、データ電圧出力ノードNVQに接続される。

**【0123】**

第1～第6の調整用キャパシターカA1～カA6は、2の累乗で重み付けされた容量値を有している。具体的には調整用キャパシターカA1～カA6の第sの調整用キャパシターカAsの容量値は $2^{(s-1)} \times CA_1$ である。第sの調整用キャパシターカAsの一端は、第sのスイッチ素子SWAsの他端に接続される。第sの調整用キャパシターカAsの他端は、低電位側電源(広義には、基準電圧のノード)に接続される。

**【0124】**

例えれば、CA1 = 1 pFに設定した場合、スイッチ素子SWA1のみがオンした状態では可変容量回路30の容量は1 pFであり、スイッチ素子SWA1～SWA6の全てがオンした状態では可変容量回路30の容量は63 pF (= 1 pF + 2 pF + ⋯ + 32 pF)である。容量値が2の累乗で重み付けされているため、スイッチ素子SWA1～SWA6のオン・オフ状態に応じて1 pF～63 pFの間で1 pF(CA1)ステップで、可変容量回路30の容量を設定することができる。

**【0125】****8. 第3構成例におけるデータ電圧**

本実施形態のドライバー100が出力するデータ電圧について説明する。ここではデータ電圧の範囲(データ電圧の最大値)について説明する。

**【0126】**

図11(A)に示すように、まずキャパシター回路10の初期化を行う。即ち、駆動部DR1～DR10の全ての出力を0Vに設定し、電圧VQ=VC=7.5V(式FC)を

10

20

30

40

50

設定する。この初期化においてキャパシター回路 10 の容量 CO と可変容量回路の容量 CA と電気光学パネル側容量 CP に蓄積された電荷の総量は、以降のデータ電圧出力において保存される。

#### 【 0 1 2 7 】

図 1 1 ( B ) に示すように、データ電圧の最大値が出力されるのは、駆動部 DR 1 ~ DR 10 の全ての出力を 15 V に設定した場合である。このときのデータ電圧は図 1 1 ( B ) の式 FD に示す値となる。

#### 【 0 1 2 8 】

図 1 1 ( C ) に示すように、所望のデータ電圧範囲が例えば 5 V であるとする。データ電圧の最大値 12.5 V が実現されるのは、式 FD から  $CO / (CO + (CA + CP)) = 1/3$  、即ち  $CA + CP = 2CO$  の場合である。<sup>10</sup> CA は可変容量回路の容量なので、自在に設定可能であり、与えられた CP に対して  $CA = 2CO - CP$  に設定することができる。即ち、ドライバー 100 に接続する電気光学パネル 200 の種類や、実装基板の設計がどのようなものであっても、データ電圧の範囲をいつも 7.5 V ~ 12.5 V に設定することが可能となる。

#### 【 0 1 2 9 】

以上の第 3 構成例によれば、ドライバー 100 は可変容量回路 30 を含む。可変容量回路 30 は、データ電圧出力端子 TVQ と基準電圧（低電位側電源の電圧、0 V）のノードとの間に設けられる。そして、可変容量回路 30 の容量 CA と電気光学パネル側容量 CP を加算した容量 CA + CP （以下、被駆動側の容量と呼ぶ）と、キャパシター回路 10 の容量 CO （以下、駆動側の容量と呼ぶ）とが、所与の容量比関係（例えば  $CO : (CA + CP) = 1 : 2$  ）になるように、可変容量回路 30 の容量 CA が設定されている。<sup>20</sup>

#### 【 0 1 3 0 】

ここで、可変容量回路 30 の容量 CA は、可変容量回路 30 の可変の容量に対して設定された容量値である。図 1 0 の例では、スイッチ素子 SWA 1 ~ SWA 6 のうちオンになっているスイッチ素子に接続された調整用キャパシターの容量を合計したものである。また、電気光学パネル側容量 CP は、データ電圧出力端子 TVQ に対して外部に接続される容量（寄生容量、回路素子の容量）である。図 1 0 の例では、基板容量 CP 1 とパネル容量 CP 2 である。また、キャパシター回路 10 の容量 CO は、キャパシター C 1 ~ C 10 の容量を合計したものである。<sup>30</sup>

#### 【 0 1 3 1 】

また、所与の容量比関係とは、駆動側の容量 CO と被駆動側の容量 CA + CP との比の関係である。これは、各容量の値が測定されている（明確に容量値が決定されている）場合の容量比に限定されない。例えば、所与の階調データ GD [ 10 : 1 ] に対する出力電圧 VQ から推定される容量比であってもよい。電気光学パネル側容量 CP は通常、事前に測定値が得られているものではないので、そのままでは可変容量回路 30 の容量 CA を決定できない。そのため、図 1 4 で後述するように、例えば階調データ GD [ 10 : 1 ] の中央値 “200 h” に対して  $VQ = 10 V$  が出力されるように可変容量回路 30 の容量 CA を決定する。この場合、結果的に容量比  $CO : (CA + CP) = 1 : 2$  になっていると推定され、この比と容量 CA から容量 CP を推定できる（推定できるが、容量 CP は知らないくてよい）。<sup>40</sup>

#### 【 0 1 3 2 】

さて、図 1 等で説明した第 1 構成例では、ドライバー 100 の接続環境（実装基板の設計や電気光学パネル 200 の種類）が変わると、その度に設計変更が必要であるという課題があった。

#### 【 0 1 3 3 】

この点、第 3 構成例によれば、可変容量回路 30 を設けることで、ドライバー 100 の接続環境に依存しない汎用のドライバー 100 を実現できる。即ち、電気光学パネル側容量 CP が異なる場合であっても、それに応じて可変容量回路 30 の容量 CA を調整することによって、所与の容量比関係（例えば  $CO : (CA + CP) = 1 : 2$  ）を実現できる。<sup>50</sup>

この容量比関係によってデータ電圧の範囲（図11（A）～図11（C）の例では7.5V～12.5V）が決まるので、接続環境に依存しないデータ電圧の範囲を実現できる。

#### 【0134】

また、本実施形態では、キャパシター駆動回路20は、階調データGD[10:1]の第1～第10のビットGD1～GD10に基づいて、前記第1～第10のキャパシター駆動電圧の各駆動電圧として第1電圧レベル(0V)又は第2電圧レベル(15V)を出力する。そして、所与の容量比関係は、第1電圧レベルと第2電圧レベルの電圧差(15V)と、データ電圧出力端子TVQに出力されるデータ電圧(出力電圧VQ)との間の電圧関係によって決定される。

#### 【0135】

例えば、図11（A）～図11（C）の例では、データ電圧出力端子TVQに出力されるデータ電圧の範囲が5V(7.5V～12.5V)である。この場合、第1電圧レベルと第2電圧レベルの電圧差(15V)とデータ電圧の範囲(5V)との間の電圧関係が実現されるように所与の容量比関係が決定される。即ち、容量COと容量CA+CPによる分圧(電圧分割)によって15Vが5Vに分圧される容量比CO:(CA+CP)=1:2が、所与の容量比関係となる。

#### 【0136】

このようにすれば、第1電圧レベルと第2電圧レベルの電圧差(15V)と、データ電圧出力端子TVQに出力されるデータ電圧(範囲5V)との間の電圧関係から、所与の容量比関係CO:(CA+CP)=1:2を決定できる。逆に、所与の容量比関係が実現されているか否かは、電圧関係を調べれば判定できることになる。即ち、電気光学パネル側容量CPが分かっていなくても、電圧関係から容量比CO:(CA+CP)=1:2を実現する可変容量回路30の容量CAを決定できることになる（例えば図14のフロー）。

#### 【0137】

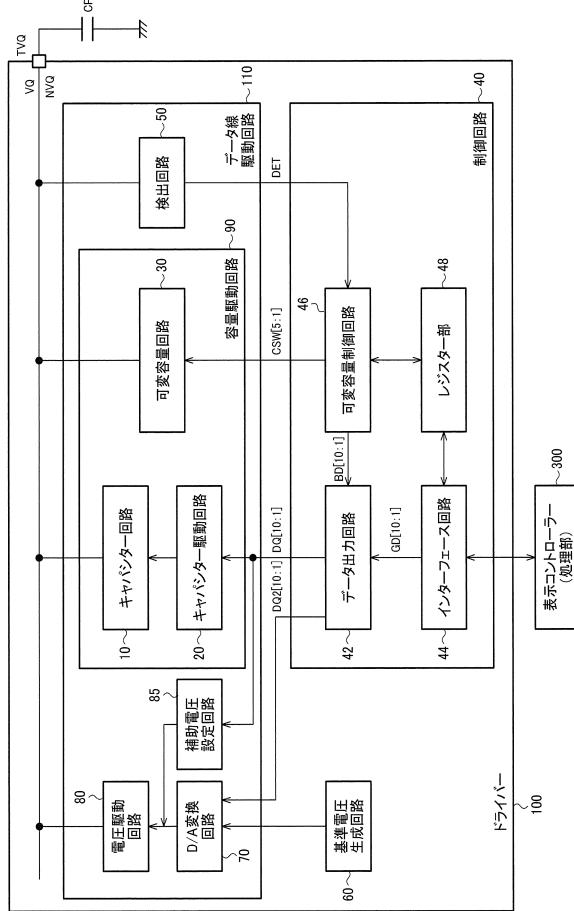

##### 9. ドライバーの詳細な構成例

図12に、本実施形態のドライバーの詳細な構成例を示す。このドライバー100は、データ線駆動回路110、基準電圧生成回路60、制御回路40を含む。データ線駆動回路110は、補助用電圧設定回路85、D/A変換回路70、電圧駆動回路80、容量駆動回路90、検出回路50を含む。容量駆動回路90は、キャパシターリード回路10、キャパシタ駆動回路20、可変容量回路30を含む。制御回路40は、データ出力回路42、インターフェース回路44、可変容量制御回路46、レジスター部48を含む。なお、既に説明した構成要素と同一の構成要素には同一の符号を付し、その構成要素については適宜説明を省略する。

#### 【0138】

データ線駆動回路110は、1つのデータ電圧出力端子TVQに対応して1つ設けられる。ドライバー100は複数のデータ線駆動回路と複数のデータ電圧出力端子を含むが、図12では1つだけ図示している。基準電圧生成回路60は、複数のデータ線駆動回路（複数のD/A変換回路）に対して共通に設けられる。

#### 【0139】

インターフェース回路44は、ドライバー100を制御する表示コントローラー300（広義には、処理部）とドライバー100との間のインターフェース処理を行う。例えば、LVDS（Low Voltage Differential Signaling）等のシリアル通信によるインターフェース処理を行う。この場合、インターフェース回路44は、シリアル信号を入出力するI/O回路と、制御データや画像データをシリアル／パラレル変換するシリアル／パラレル変換回路と、を含む。また、表示コントローラー300から入力されてパラレルデータに変換された画像データをラッチするラインラッチを含む。ラインラッチは、例えば1度に1本の水平走査線に対応する画像データをラッチする。

#### 【0140】

データ出力回路42は、水平走査線に対応する画像データの中から、キャパシタ駆動回路20と補助用キャパシタ駆動回路84へ出力する階調データGD[10:1]を取

10

20

30

40

50

り出し、データD Q [ 1 0 : 1 ]として出力する。また、その階調データG D [ 1 0 : 1 ]をデータD Q 2 [ 1 0 : 1 ]としてD / A変換回路7 0へ出力する。データ出力回路4 2は、例えば、電気光学パネル2 0 0の駆動タイミングを制御するタイミングコントローラーと、水平走査線に対応する画像データから階調データG D [ 1 0 : 1 ]を選択する選択回路と、選択された階調データG D [ 1 0 : 1 ]をデータD Q [ 1 0 : 1 ]としてラッチする出力ラッチと、選択された階調データG D [ 1 0 : 1 ]をデータD Q 2 [ 1 0 : 1 ]としてラッチする出力ラッチと、を含む。図19等で後述する相展開駆動を行う場合、出力ラッチは、1度に8画素分(データ線D L 1～D L 8の本数分)の階調データG D [ 1 0 : 1 ]をラッチする。この場合、タイミングコントローラーは、相展開駆動の駆動タイミングに合わせて選択回路や出力ラッチの動作タイミングを制御する。また、インターフェース回路4 4によって受信された画像データに基づいて水平同期信号や垂直同期信号を生成してもよい。また、電気光学パネル2 0 0のスイッチ素子(S W E P 1等)のオン・オフを制御するための信号(E N B X)や、ゲート駆動(電気光学パネル2 0 0の水平走査線の選択)を制御する信号を、電気光学パネル2 0 0に対して出力してもよい。

#### 【0141】

検出回路5 0は、データ電圧出力ノードN V Qの電圧V Qを検出する。具体的には、所与の検出電圧と電圧V Qとを比較し、その結果を検出信号D E Tとして出力する。例えば、電圧V Qが検出電圧以上である場合にはD E T = “1”を出力し、電圧V Qが検出電圧より小さい場合にはD E T = “0”を出力する。

#### 【0142】

可変容量制御回路4 6は、検出信号D E Tに基づいて可変容量回路3 0の容量を設定する。この設定処理のフローは図14で後述する。可変容量制御回路4 6は、可変容量回路3 0の制御信号として設定値C S W [ 6 : 1 ]を出力する。この設定値C S W [ 6 : 1 ]は第1～第6のビットC S W 6～C S W 1(第1～第mのビット)で構成される。ビットC S W s(sはm = 6以下の自然数)は、可変容量回路3 0のスイッチ素子S W A sに入力される。例えばビットC S W s = “0”的場合にはスイッチ素子S W A sがオフになり、ビットC S W s = “1”的場合にはスイッチ素子S W A sがオンになる。設定処理を行う場合、可変容量制御回路4 6は検出用データB D [ 1 0 : 1 ]を出力する。そして、データ出力回路4 2は検出用データB D [ 1 0 : 1 ]を出力データD Q [ 1 0 : 1 ]としてキャパシター駆動回路2 0へ出力する。

#### 【0143】

レジスター部4 8は、設定処理により設定された可変容量回路3 0の設定値C S W [ 6 : 1 ]を記憶する。レジスター部4 8はインターフェース回路4 4を介して表示コントローラー3 0 0からアクセス可能に構成される。即ち、表示コントローラー3 0 0はレジスター部4 8から設定値C S W [ 6 : 1 ]を読み出すことができる。或は、表示コントローラー3 0 0がレジスター部4 8に設定値C S W [ 6 : 1 ]を書き込む構成としてもよい。

#### 【0144】

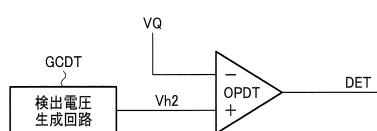

図13に、検出回路5 0の詳細な構成例を示す。検出回路5 0は、検出電圧V h 2を生成する検出電圧生成回路G C D Tと、データ電圧出力ノードN V Qの電圧V Qと検出電圧V h 2とを比較するコンパレーターO P D Tと、を有する。

#### 【0145】

検出電圧生成回路G C D Tは、例えば抵抗素子による電圧分割回路等により予め決められた検出電圧V h 2を出力する。或は、レジスター設定等により可変の検出電圧V h 2を出力してもよい。この場合、検出電圧生成回路G C D Tは、レジスター設定値をD / A変換するD / A変換回路であってもよい。

#### 【0146】

##### 10. 可変容量回路の容量を設定する処理

図14に、可変容量回路3 0の容量を設定する処理のフローチャートを示す。この処理は、例えばドライバー1 0 0に電源を投入した際の立ち上げ時(初期化処理)において行

10

20

30

40

50

う。

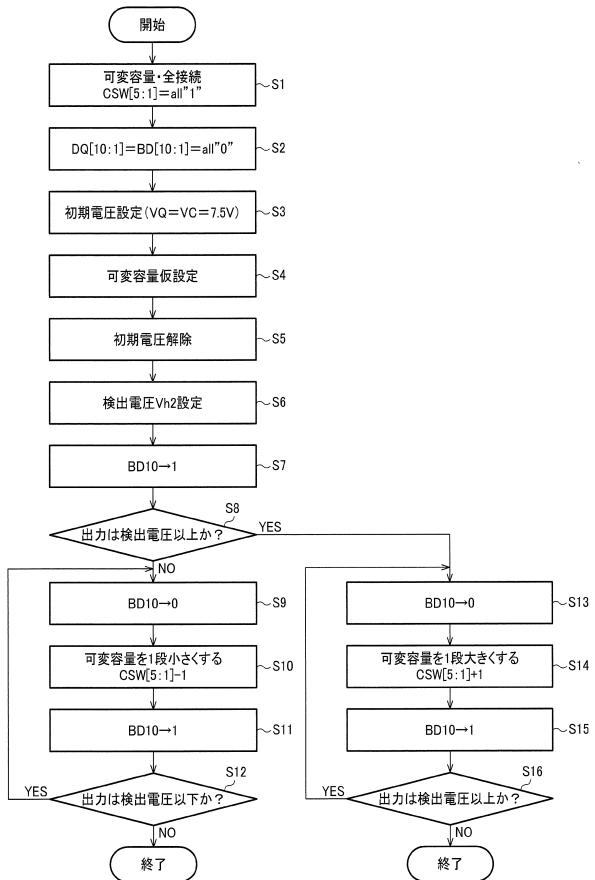

#### 【0147】

図14に示すように、処理を開始すると、設定値CSW[6:1] = “3Fh”を出力し、可変容量回路30のスイッチ素子SWA1～SWA6を全てオンにする(ステップS1)。次に、検出用データBD[10:1] = “000h”を出力し、キャパシター駆動回路20の駆動部DR1～DR10の出力を全て0Vに設定する(ステップS2)。次に、出力電圧VQを初期化電圧VC = 7.5Vに設定する(ステップS3)。この初期化電圧VCは、図16で後述するように例えば外部から端子TVCを介して供給される。

#### 【0148】

次に、可変容量回路30の容量を仮設定する(ステップS4)。例えば、設定値CSW[6:1] = “1Fh”を設定する。この場合、スイッチ素子SWA6がオフ、スイッチ素子SWA5～SWA1がオンになるので、容量は最大値の半分になる。次に、出力電圧VQへの初期化電圧VCの供給を解除する(ステップS5)。次に、検出電圧Vh2を所望の電圧に設定する(ステップS6)。例えば、検出電圧Vh2 = 10Vを設定する。

#### 【0149】

次に、検出用データBD[10:1]のMSBをBD10 = “0”からBD10 = “1”に変化させる(ステップS7)。次に、出力電圧VQが検出電圧Vh2 = 10V以上であるか否かを検出する(ステップS8)。

#### 【0150】

ステップS8において出力電圧VQが検出電圧Vh2 = 10Vより小さい場合、ビットBD10 = “0”に戻す(ステップS9)。次に、設定値CSW[6:1] = “1Fh”を“-1”して“1Eh”とし、可変容量回路30の容量を1段階小さくする(ステップS10)。次に、ビットBD10 = “1”を設定する(ステップS11)。次に、出力電圧VQが検出電圧Vh2 = 10V以下であるか否かを検出する(ステップS12)。出力電圧VQが検出電圧Vh2 = 10V以下である場合にはステップS9に戻り、出力電圧VQが検出電圧Vh2 = 10Vより大きい場合には処理を終了する。

#### 【0151】

ステップS8において出力電圧VQが検出電圧Vh2 = 10V以上である場合、ビットBD10 = “0”に戻す(ステップS13)。次に、設定値CSW[6:1] = “1Fh”を“+1”して“20h”とし、可変容量回路30の容量を1段階大きくする(ステップS14)。次に、ビットBD10 = “1”を設定する(ステップS15)。次に、出力電圧VQが検出電圧Vh2 = 10V以上であるか否かを検出する(ステップS16)。出力電圧VQが検出電圧Vh2 = 10V以上である場合にはステップS13に戻り、出力電圧VQが検出電圧Vh2 = 10Vより小さい場合には処理を終了する。

#### 【0152】

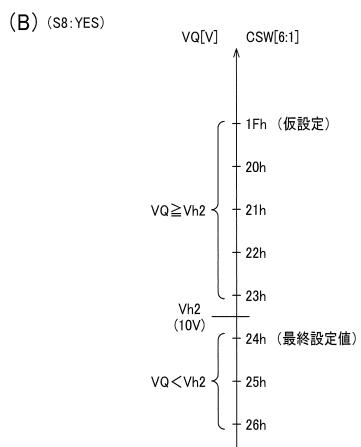

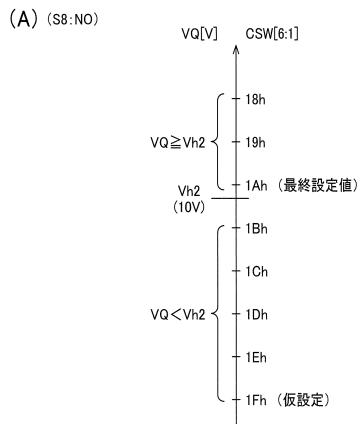

図15(A)、図15(B)に、上記のステップS8～S16により設定値CSW[6:1]が決定される様子を模式的に示す。

#### 【0153】

上記のフローでは検出用データBD[10:1]のMSBをBD10 = “1”に設定し、そのときの出力電圧VQと検出電圧Vh2 = 10Vを比較している。BD[10:1] = “200h”は階調データ範囲“000h”～“3FFFh”的中央値であり、検出電圧Vh2 = 10Vはデータ電圧範囲7.5V～12.5Vの中央値である。即ち、BD10 = “1”にしたときに出力電圧VQが検出電圧Vh2 = 10Vに一致していれば、正しい(所望の)データ電圧が得られていることになる。

#### 【0154】

図15(A)に示すように、仮設定値CSW[6:1] = “1Fh”においてステップS8で“NO”であった場合、VQ < Vh2である。この場合、出力電圧VQを上昇させる必要がある。図11(B)の式FDから可変容量回路30の容量CAを小さくすれば出力電圧VQが上昇することが分かるので、設定値CSW[6:1]を“1”ずつ小さくしていく。そして、最初にVQ = Vh2となる設定値CSW[6:1] = “1Ah”で停止

10

20

30

40

50

する。これにより、検出電圧  $V_{h2}$  に直近の出力電圧  $V_Q$  が得られる設定値  $C_{SW[6:1]}$  を決定できる。

#### 【0155】

図15(B)に示すように、仮設定値  $C_{SW[6:1]} = "1Fh"$ においてステップS8で“YES”であった場合、 $V_Q < V_{h2}$ である。この場合、出力電圧  $V_Q$ を下降させる必要がある。図11(B)の式FDから可変容量回路30の容量CAを大きくすれば出力電圧  $V_Q$  が上昇することが分かるので、設定値  $C_{SW[6:1]}$  を “1”ずつ大きくしていく。そして、最初に  $V_Q < V_{h2}$ となる設定値  $C_{SW[6:1]} = "24h"$ で停止する。これにより、検出電圧  $V_{h2}$  に直近の出力電圧  $V_Q$  が得られる設定値  $C_{SW[6:1]}$  を決定できる。

10

#### 【0156】

以上の処理により得られた設定値  $C_{SW[6:1]}$  を、最終的な設定値  $C_{SW[6:1]}$ として決定し、その設定値  $C_{SW[6:1]}$  をレジスター部48に書き込む。容量駆動により電気光学パネル200を駆動する際には、レジスター部48に記憶された設定値  $C_{SW[6:1]}$  で可変容量回路30の容量が設定される。

#### 【0157】

なお、本実施形態では可変容量回路30の設定値  $C_{SW[6:1]}$  をレジスター部48に記憶させる場合を例に説明したが、これに限定されるものでない。例えば、設定値  $C_{SW[6:1]}$  をRAM等のメモリーに記憶させてもよいし、ヒューズ(例えば、製造時にレーザー等で切断して設定値を設定する)により設定値  $C_{SW[6:1]}$  を設定してもよい。

20

#### 【0158】

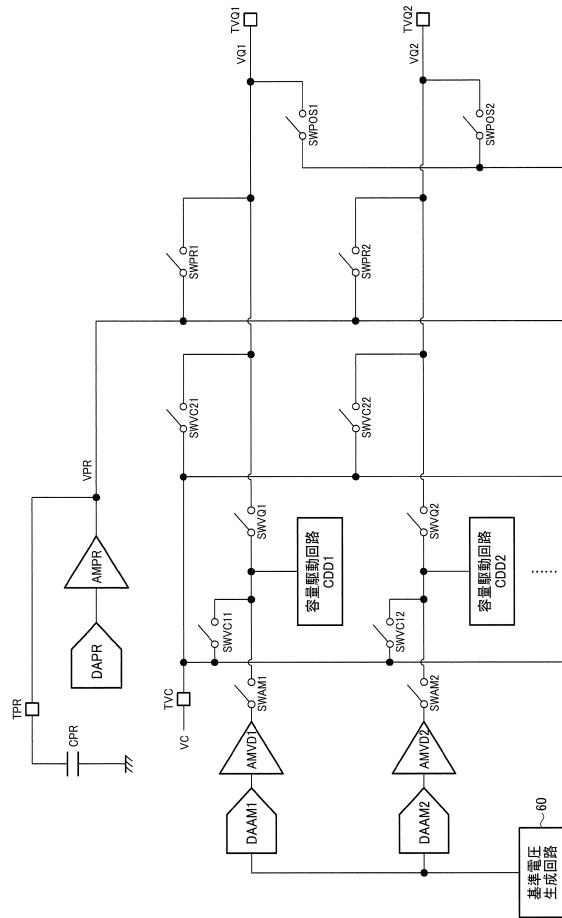

##### 11. ドライバーの第2の詳細な構成例

図16に、本実施形態のドライバー100の第2の詳細な構成例を示す。なお、ここでは補助用電圧設定回路85の図示を省略している。

#### 【0159】

このドライバー100は、アンプ回路AMVD1、AMVD2、D/A変換回路DAAA

M1、DAAM2、スイッチ回路SWAM1、SWAM2、基準電圧生成回路60、プリ

チャージ用端子TPR、初期化電圧用端子TVC(コモン電圧用端子)、データ電圧出力

端子TVQ1、TVQ2、プリチャージ用D/A変換回路DAPR、プリチャージ用アン

プ回路AMP R、容量駆動回路CDD1、CDD2、プリチャージ用スイッチ素子SWP

R1、SWPR2、初期化用スイッチ素子SWVC11、SWVC12、SWVC21、

SWVC22、出力用スイッチ素子SWVQ1、SWVQ2、ポストチャージ用スイッチ

素子SWPOS1、SWPOS2を含む。

30

#### 【0160】

容量駆動回路CDD1とD/A変換回路DAAM1とアンプ回路AMVD1とスイッチ

回路SWAM1は、図12のデータ線駆動回路110に対応している。同様に、容量駆動

回路CDD2とD/A変換回路DAAM2とアンプ回路AMVD2とスイッチ回路SWA

M2は、図12のデータ線駆動回路110に対応している。図16では、2つのみ記載し

ているが、実際にはドライバー100は電気光学パネル200のデータ線と同数(又は同

数以上)のデータ線駆動回路を有する。同様に、データ電圧出力端子や、各種スイッチ素

子も、データ線駆動回路と同数含まれる。

40

#### 【0161】

初期化電圧用端子TVCには、例えば外部の電源回路等から初期化電圧VC(コモン電

圧)が供給される。

#### 【0162】

なお、初期化電圧VCを供給する手法は初期化電圧用端子TVCに限定されない。例え

ば、ドライバー100は、初期化電圧VCを出力する初期化電圧用アンプ回路を含んでも

よい。

#### 【0163】

50

プリチャージ用端子 T P R は、プリチャージ用アンプ回路 A M P R の出力に接続される。プリチャージ用 D / A 変換回路 D A P R がプリチャージの設定値（例えばレジスター値）を D / A 変換してプリチャージ電圧 V P R を生成し、そのプリチャージ電圧 V P R でプリチャージ用アンプ回路 A M P R がプリチャージ用端子 T P R を駆動する。プリチャージ電圧 V P R は、例えば初期化電圧 V C よりも低い電圧（負極性駆動のデータ電圧範囲 7 . 5 V ~ 2 . 5 V の範囲内）である。

#### 【 0 1 6 4 】

プリチャージ用端子 T P R には、外部のプリチャージ用キャパシター C P R が接続されている。プリチャージ用キャパシター C P R は、プリチャージ電圧 V P R に対応する電荷を蓄積しており、プリチャージ時にデータ線に対して電荷を供給する。このプリチャージ用キャパシター C P R を設けることでプリチャージ電圧 V P R を平滑化できるので、プリチャージ用アンプ回路 A M P R の電荷供給能力を下げることができる。即ち、プリチャージを行うとプリチャージ用キャパシター C P R が電荷を放出するが、その後のプリチャージを行うまでの間に、プリチャージ用アンプ回路 A M P R がプリチャージ用キャパシター C P R の電荷を補充できればよい。

#### 【 0 1 6 5 】

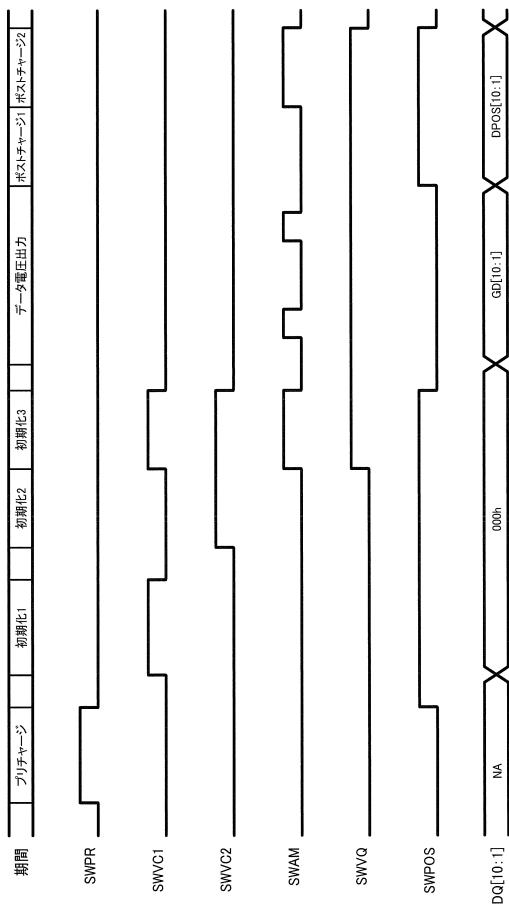

図 17 に、ドライバー 100 の第 2 の詳細な構成例の動作タイミングチャートを示す。図 17 では、スイッチ素子の符号末尾の数字を省略している。例えば “ S W P R ” はプリチャージ用スイッチ素子 S W P R 1、S W P R 2 を表す。スイッチ素子のタイミングチャートにおいてハイレベルはスイッチ素子のオン状態を表し、ローレベルはスイッチ素子のオフ状態を表す。

#### 【 0 1 6 6 】

図 17 に示すように、電気光学パネル 200 の駆動はプリチャージ、初期化、データ電圧出力、ポストチャージの順に行う。この一連の動作は、例えば 1 つの水平走査期間に行う。

#### 【 0 1 6 7 】

プリチャージ期間では、プリチャージ用スイッチ素子 S W P R 1、S W P R 2 がオンになり、データ電圧出力端子 T V Q 1、T V Q 2 からプリチャージ電圧 V P R が出力される。

#### 【 0 1 6 8 】

初期化期間は第 1 ~ 第 3 の初期化期間に分かれている。この第 1 ~ 第 3 の初期化期間では D Q [ 1 0 : 1 ] = “ 0 0 0 h ” ( D Q 2 [ 1 0 : 1 ] = “ 0 0 0 h ” ) に設定されており、キャパシター駆動回路 20 の駆動部 D R 1 ~ D R 1 0 は全て 0 V を出力している。またアンプ回路 A M V D 1、A M V D 2 は初期化電圧 V C を出力している。

#### 【 0 1 6 9 】

第 1 の初期化期間では、初期化用スイッチ素子 S W V C 1 1、S W V C 1 2 がオンになり、容量駆動回路 C D D 1、C D D 2 の出力（キャパシター C 1 ~ C 1 0 の一端）が初期化電圧 V C に設定される。これにより、キャパシター回路 1 0 と可変容量回路 3 0 の電荷が初期化される。また、ポストチャージ用スイッチ素子 S W P O S 1、S W P O S 2 がオンになり、データ電圧出力端子 T V Q 1、T V Q 2 が共通接続される。

#### 【 0 1 7 0 】

第 2 の初期化期間では、初期化用スイッチ素子 S W V C 2 1、S W V C 2 2 とポストチャージ用スイッチ素子 S W P O S 1、S W P O S 2 がオンになり、データ電圧出力端子 T V Q 1、T V Q 2 から初期化電圧 V C が出力される。これにより、電気光学パネル側容量 C P の電荷が初期化される。

#### 【 0 1 7 1 】

第 3 の初期化期間では、出力用スイッチ素子 S W V Q 1、S W V Q 2 とスイッチ回路 S W A M 1、S W A M 2 がオンになり、アンプ回路 A M V D 1 の出力と容量駆動回路 C D D 1 の出力とデータ電圧出力端子 T V Q 1 が接続され、アンプ回路 A M V D 2 の出力と容量駆動回路 C D D 2 の出力とデータ電圧出力端子 T V Q 2 が接続される。また、初期化用ス

10

20

30

40

50

イッチ素子 SWVC11、SWVC12、SWVC21、SWVC22とポストチャージ用スイッチ素子 SWPOS1、SWPOS2がオンになり、データ電圧出力端子 TVQ1、TVQ2から初期化電圧 VCが出力される。

#### 【0172】

データ電圧出力期間では、 $DQ[10:1] = GD[10:1]$  ( $DQ2[10:1] = GD[10:1]$ )に設定されている。そして、出力用スイッチ素子 SWVQ1、SWVQ2がオンになり、階調データ  $GD[10:1]$  に対応したデータ電圧がデータ電圧出力端子 TVQ1、TVQ2から出力される。データ電圧出力期間の詳細は後述する。

#### 【0173】

ポストチャージ期間は第1のポストチャージ期間、第2のポストチャージ期間に分かれている。第1のポストチャージ期間、第2のポストチャージ期間では、 $DQ[10:1] = DPoS[10:1]$  ( $DQ2[10:1] = DPoS[10:1]$ )に設定されている。 $DPoS[10:1]$  はポストチャージ用データである。

#### 【0174】

第1のポストチャージ期間では、出力用スイッチ素子 SWVQ1、SWVQ2とポストチャージ用スイッチ素子 SWPOS1、SWPOS2がオンになり、ポストチャージ用データ  $DPoS[10:1]$  に対応したデータ電圧がデータ電圧出力端子 TVQ1、TVQ2から出力される。

#### 【0175】

第2のポストチャージ期間では、更にスイッチ回路 SWAM1、SWAM2がオンになり、アンプ回路 AMVD1、AMVD2が、ポストチャージ用データ  $DPoS[10:1]$  に対応したデータ電圧をデータ電圧出力端子 TVQ1、TVQへ出力する。

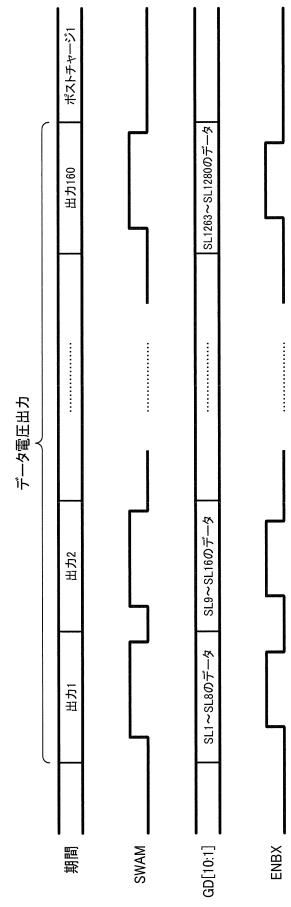

#### 【0176】

図18に、データ電圧出力期間における動作タイミングチャートを示す。データ電圧出力期間は第1～第160の出力期間に分かれている。なお、電気光学パネル200が図19に示す構成である場合を例に説明する。

#### 【0177】

第1の出力期間では、階調データ  $GD[10:1]$  としてソース線 SL1～SL8に対応する階調データを出力する。例えば、データ出力回路42の出力ラッチに階調データがラッチされたタイミングが容量駆動の開始タイミングである。ソース線 SL1～SL8に対応する階調データをラッチした後にスイッチ回路 SWAM1、SWAM2がオンになり、アンプ回路 AMVD1、AMVD2が階調データに対応したデータ電圧を出力する。

#### 【0178】

スイッチ回路 SWAM1、SWAM2がオンになっている期間（電圧駆動の期間）に信号 ENBXがオン（アクティブ）になり、電気光学パネル200のソース線 SL1～SL8が駆動される。信号 ENBXは、電気光学パネル200のデータ線とソース線を接続するスイッチ素子をオン・オフ制御するための制御信号である。

#### 【0179】

スイッチ回路 SWAM1、SWAM2がオフになった後、次の第2の出力期間に移行する。第2の出力期間では、階調データ  $GD[10:1]$  としてソース線 SL9～SL16に対応する階調データを出力する。次に、スイッチ回路 SWAM1、SWAM2がオンになり、信号 ENBXがオン（アクティブ）になり、電気光学パネル200のソース線 SL9～SL16が駆動される。以降、第3～第160の出力期間において同様の動作を行い、第1のポストチャージ期間に移行する。

#### 【0180】

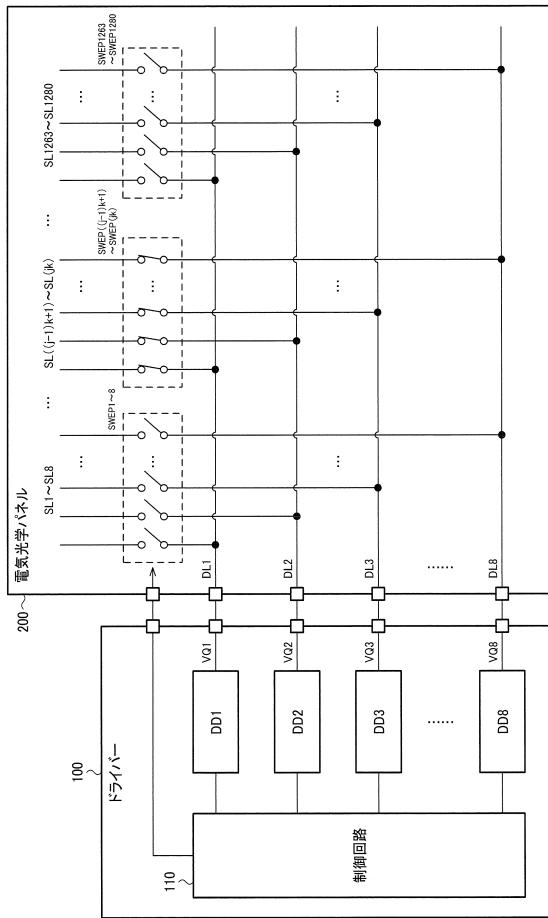

##### 12. 相展開駆動の手法

次に、電気光学パネル200の駆動手法について説明する。以下では相展開駆動を例にとって説明するが、本実施形態のドライバー100が行う駆動手法は相展開駆動に限定されない。

#### 【0181】

10

20

30

40

50

図19に、ドライバーの第3の詳細な構成例と、電気光学パネルの詳細な構成例と、ドライバーと電気光学パネルの接続構成例を示す。

#### 【0182】

ドライバー100は、制御回路40、第1～第kのデータ線駆動回路DD1～DDk(kは2以上の自然数)を含む。データ線駆動回路DD1～DDkは、それぞれ図12のデータ線駆動回路110に対応する。なお以下ではk=8の場合を例に説明する。

#### 【0183】

制御回路40は、データ線駆動回路DD1～DD8の各データ線駆動回路に対して、対応する階調データを出力する。また制御回路40は、制御信号(例えば図20のENBX等)を電気光学パネル200に出力する。

10

#### 【0184】

データ線駆動回路DD1～DD8は、階調データをデータ電圧に変換し、そのデータ電圧を出力電圧VQ1～VQ8として電気光学パネル200のデータ線DL1～DL8へ出力する。

#### 【0185】

電気光学パネル200は、データ線DL1～DL8(第1～第kのデータ線)、スイッチ素子SWEP1～SWEP(tk)、ソース線SL1～SL(tk)を含む。tは2以上の自然数であり、以下ではt=160(即ちtk=160×8=1280(WXGA))の場合を例に説明する。

#### 【0186】

スイッチ素子SWEP1～SWEP1280のうちスイッチ素子SWEP((j-1)×k+1)～SWEP(j×k)の一端は、データ線DL1～DL8に接続される。jはt=160以下の自然数である。例えばj=1の場合にはスイッチ素子SWEP1～SWEP8である。

20

#### 【0187】

スイッチ素子SWEP1～SWEP1280は、例えばTFT(Thin Film Transistor)等で構成され、ドライバー100からの制御信号に基づいて制御される。例えば、電気光学パネル200は不図示のスイッチ制御回路を含み、そのスイッチ制御回路がENBX等の制御信号に基づいてスイッチ素子SWEP1～SWEP1280のオン・オフを制御する。

30

#### 【0188】

図20に、図19のドライバー100と電気光学パネル200の動作タイミングチャートを示す。

#### 【0189】

プリチャージ期間では、信号ENBXがハイレベルになり、スイッチ素子SWEP1～SWEP1280が全てオンになる。そして、ソース線SL1～SL1280の全てがプリチャージ電圧VPRに設定される。

#### 【0190】

初期化期間では、信号ENBXがローレベルになり、スイッチ素子SWEP1～SWEP1280が全てオフになる。そして、データ線DL1～DL8が初期化電圧VC=7.5Vに設定される。ソース線SL1～SL1280はプリチャージ電圧VPRのままである。

40

#### 【0191】

データ電圧出力期間の第1の出力期間では、ソース線SL1～SL8に対応する階調データがデータ線駆動回路DD1～DD8に入力される。そして、キャパシター回路10とキャパシター駆動回路20による容量駆動と電圧駆動回路80による電圧駆動が行われ、データ線DL1～DL8がデータ電圧SV1～SV8で駆動される。容量駆動と電圧駆動の開始後、信号ENBXがハイレベルになり、スイッチ素子SWEP1～SWEP8がオンになる。そして、ソース線SL1～SL8がデータ電圧SV1～SV8で駆動される。このとき、不図示のゲートドライバーにより1本のゲート線(水平走査線)が選択されて

50

おり、その選択されたゲート線とデータ線 D L 1 ~ D L 8 に接続される画素回路にデータ電圧 S V 1 ~ S V 8 が書き込まれる。なお図 20 には例としてデータ線 D L 1 、ソース線 S L 1 の電位を示す。

#### 【 0 1 9 2 】

第 2 出力期間では、ソース線 S L 9 ~ S L 1 6 に対応する階調データがデータ線駆動回路 D D 1 ~ D D 8 に入力される。そして、キャパシター回路 1 0 とキャパシター駆動回路 2 0 による容量駆動と電圧駆動回路 8 0 による電圧駆動が行われ、データ線 D L 1 ~ D L 8 がデータ電圧 S V 9 ~ S V 1 6 で駆動される。容量駆動と電圧駆動の開始後、信号 E N B X がハイレベルになり、スイッチ素子 S W E P 9 ~ S W E P 1 6 がオンになる。そして、ソース線 S L 9 ~ S L 1 6 がデータ電圧 S V 9 ~ S V 1 6 で駆動される。このとき、選択されたゲート線とデータ線 D L 9 ~ D L 1 6 に接続される画素回路にデータ電圧 S V 9 ~ S V 1 6 が書き込まれる。なお図 20 には例としてデータ線 D L 1 、ソース線 S L 9 の電位を示す。10

#### 【 0 1 9 3 】

以降、同様にして第 3 出力期間、第 4 出力期間、・・・、第 1 6 0 出力期間においてソース線 S L 1 7 ~ S L 2 4 、 S L 2 5 ~ S L 3 2 、・・・、 S L 1 2 6 3 ~ S L 1 2 8 0 が駆動され、ポストチャージ期間に移行する。

#### 【 0 1 9 4 】

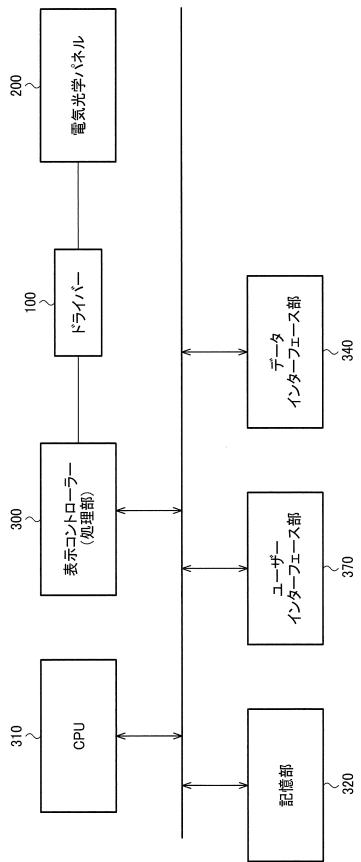

##### 1 3 . 電子機器

図 21 に、本実施形態のドライバー 1 0 0 を適用できる電子機器の構成例を示す。本実施形態の電子機器として、例えばプロジェクターや、テレビジョン装置、情報処理装置（コンピューター）、携帯型情報端末、カーナビゲーションシステム、携帯型ゲーム端末等の、表示装置を搭載する種々の電子機器を想定できる。20

#### 【 0 1 9 5 】

図 21 に示す電子機器は、ドライバー 1 0 0 、電気光学パネル 2 0 0 、表示コントローラー 3 0 0 （第 1 処理部）、 C P U 3 1 0 （第 2 処理部）、記憶部 3 2 0 、ユーザーインターフェース部 3 3 0 、データインターフェース部 3 4 0 を含む。

#### 【 0 1 9 6 】

電気光学パネル 2 0 0 は例えばマトリックス型の液晶表示パネルである。或は、電気光学パネル 2 0 0 は自発光素子を用いた E L (Electro-Luminescence) 表示パネルであってもよい。ユーザーインターフェース部 3 3 0 は、ユーザーからの種々の操作を受け付けるインターフェース部である。例えば、ボタンやマウス、キーボード、電気光学パネル 2 0 0 に装着されたタッチパネル等で構成される。データインターフェース部 3 4 0 は、画像データや制御データの入出力を行うインターフェース部である。例えば U S B 等の有線通信インターフェースや、或は無線 L A N 等の無線通信インターフェースである。記憶部 3 2 0 は、データインターフェース部 3 4 0 から入力された画像データを記憶する。或は、記憶部 3 2 0 は、 C P U 3 1 0 や表示コントローラー 3 0 0 のワーキングメモリーとして機能する。 C P U 3 1 0 は、電子機器の各部の制御処理や種々のデータ処理を行う。表示コントローラー 3 0 0 はドライバー 1 0 0 の制御処理を行う。例えば、表示コントローラー 3 0 0 は、データインターフェース部 3 4 0 や記憶部 3 2 0 から転送された画像データを、ドライバー 1 0 0 が受け付け可能な形式に変換し、その変換された画像データをドライバー 1 0 0 へ出力する。ドライバー 1 0 0 は、表示コントローラー 3 0 0 から転送された画像データに基づいて電気光学パネル 2 0 0 を駆動する。3040

#### 【 0 1 9 7 】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語（第 1 論理レベル、第 2 論理レベル）と共に記載された用語（ローレベル、ハイレベル）は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また50

本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。またキャパシタ一回路、キャパシター駆動回路、可変容量回路、検出回路、制御回路、基準電圧生成回路、D/A変換回路、電圧駆動回路、補助用電圧設定回路、ドライバー、電気光学パネル、電子機器の構成・動作等も、本実施形態で説明したものに限定されず、種々の変形実施が可能である。

【符号の説明】

【0198】

10 10 キャパシタ一回路、20 キャパシター駆動回路、30 可変容量回路、

40 制御回路、42 データ出力回路、44 インターフェース回路、

46 可変容量制御回路、48 レジスター部、50 検出回路、

60 基準電圧生成回路、70 D/A変換回路、80 電圧駆動回路、

82 補助用キャパシタ一回路、84 補助用キャパシター駆動回路、

85 補助用電圧設定回路、90 容量駆動回路、100 ドライバー、

110 データ線駆動回路、200 電気光学パネル、

300 表示コントローラー、310 CPU、320 記憶部、

330 ユーザーインターフェース部、340 データインターフェース部、

AMIV 反転增幅回路、AMVD アンプ回路、

AMP R プリチャージ用アンプ回路、C1 キャパシター、

CA 可変容量回路の容量、CA1 調整用キャパシター、

CDD1 容量駆動回路、CO キャパシタ一回路の容量、

CP 電気光学パネル側容量、CPR プリチャージ用キャパシター、

CSB バランス用キャパシター、DAAM1 D/A変換回路、

DL1 データ線、DR1 駆動部、GD1 ビット、

GD[10:1] 階調データ、GS1, GSX1 補助用駆動部、

NDR1 キャパシタ一駆動ノード、NDS1 補助用キャパシタ一駆動ノード、

SL1 ソース線、SWA1 スイッチ素子、SWAM 電圧駆動用スイッチ回路、

SWEP1 スイッチ素子、SWS スイッチ回路、TPR プリチャージ用端子、

TVC 初期化電圧用端子、TVQ データ電圧出力端子、

VC 初期化電圧、Vh2 検出電圧、VPR プリチャージ電圧

20

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【 図 6 】

【図7】

【 四 8 】

【図9】

### (A) 初期化

(B) 最大データ電圧

(c)

【図11】

### (A) 初期化

(B) 最大データ電圧

(c)

【図10】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図20】

【図 2 1】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G      3/20      6 1 2 F

G 0 2 F      1/133     5 7 5

H 0 3 M      1/66        B

(56)参考文献 特開平05-145421(JP,A)

特開2004-252419(JP,A)

特開2000-165243(JP,A)

特表2008-533513(JP,A)

特開2001-100712(JP,A)

特開2011-130440(JP,A)

特開2008-304896(JP,A)

米国特許出願公開第2012/0218235(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G      3 / 0 0   -   3 / 3 8

G 0 2 F      1 / 1 3 3

H 0 3 M      1 / 6 6