(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4906238号

(P4906238)

(45) 発行日 平成24年3月28日(2012.3.28)

(24) 登録日 平成24年1月20日(2012.1.20)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 27/06   | (2006.01) | HO1L 27/06 | 311B |

| HO1L 27/04   | (2006.01) | HO1L 27/04 | H    |

| HO1L 21/822  | (2006.01) | HO1L 27/08 | 321H |

| HO1L 21/8238 | (2006.01) |            |      |

| HO1L 27/092  | (2006.01) |            |      |

請求項の数 1 (全 8 頁)

(21) 出願番号 特願2004-110006 (P2004-110006)

(22) 出願日 平成16年4月2日 (2004.4.2)

(65) 公開番号 特開2004-327976 (P2004-327976A)

(43) 公開日 平成16年11月18日 (2004.11.18)

審査請求日 平成19年1月16日 (2007.1.16)

審判番号 不服2010-18247 (P2010-18247/J1)

審判請求日 平成22年8月12日 (2010.8.12)

(31) 優先権主張番号 特願2003-107830 (P2003-107830)

(32) 優先日 平成15年4月11日 (2003.4.11)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74) 代理人 100150441

弁理士 松本 洋一

(72) 発明者 菊坂 浩志

東京都品川区大崎一丁目11番2号 富士

電機デバイステクノロジー株式会社内

(72) 発明者 藤平 龍彦

東京都品川区大崎一丁目11番2号 富士

電機デバイステクノロジー株式会社内

(72) 発明者 木内 伸

東京都品川区大崎一丁目11番2号 富士

電機デバイステクノロジー株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の半導体基板のおもて面側に、第2導電型の第1の領域と、該第2導電型の第1の領域内に第1導電型の第1の領域と第2の領域を形成して横型のトランジスタを構成し、

同一の半導体基板のおもて面側に、前記第2導電型の第1の領域とは離間してかつ面積が小さな第2導電型の第2の領域と、該第2導電型の第2の領域内に、第2導電型の第2の領域より高濃度の第2導電型の第3の領域を形成して縦型のダイオードを構成し、

前記第2導電型の第3の領域と前記第1導電型の第1の領域とを接続するとともに、前記半導体基板の裏面と前記第1導電型の第2の領域とを接続することで、前記縦型のダイオードを前記横型のトランジスタのサージ吸収素子とし、

前記横型のトランジスタの降伏動作時の抵抗より前記サージ吸収素子の降伏動作時の抵抗が小さく、かつ、前記トランジスタの二次降伏電流より前記サージ吸収素子の二次降伏電流が大きいことを特徴とする半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、高ESD (Electro Static Discharge: 静電放電) 耐量およびEMC (Electro Magnetic Compatibility)

)を含む高ノイズ耐量を具えたトランジスタを有する半導体装置に関する。

【背景技術】

【0002】

従来より、高ESD耐量およびEMC( Electro Magnetic Compatibility )を含む高ノイズ耐量が要求される自動車電装器および各種産業機器、モータコントロール、OA(オフィスオートメーション)機器、モバイル(携帯)機器または家庭電化機器等において、複数のパワー半導体素子(スイッチ素子)と駆動制御回路等とを同一チップ上に集積した統合型のインテリジェントスイッチデバイスが用いられている。

統合型インテリジェントスイッチデバイスは、サージ電圧やノイズからデバイス内の各素子を保護するため同一半導体基板上にサージ吸収素子が形成されている(例えば、特許文献1参照)。

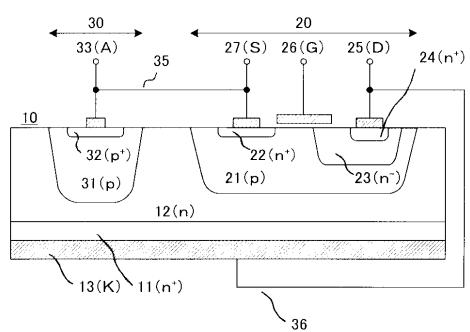

図3は、横型のMOSFETとサージ吸収素子としての縦型のダイオードを同一半導体基板上に形成した構成を示す断面図である。図3に示すように、横型パワーMOSFET20とサージ吸収素子としての縦型ダイオード30とが半導体基板10上に形成されている。

【0003】

半導体基板10は高濃度のn層11上の低濃度n層12からなり、低濃度n層12の表面領域にpウエル21, 31が形成され、pウエル21内に横型のMOSFET20が形成され、pウエル31内に縦型のダイオード30が形成されている。

pウエル31の表面は高濃度p層32を介してアノード電極33が接続され、アノード電極33はpウエル21の表面の高濃度n層22を介して接続される横型MOSFET20のソース電極27と配線35によって接続されている。25, 26はそれぞれ横型MOSFET20のドレイン電極、ゲート電極である。

半導体基板10の裏面に形成された電極13は、ダイオード30のカソード電極となり、pウエル21の表面の高濃度n層24を介して接続される横型MOSFET20のドレイン電極25に配線36によって接続される。

【0004】

図3の構成において、横型MOSFET20のドレイン電極にESDやサージが印加されると、このESDやサージのエネルギーを縦型ダイオード30が吸収して、横型MOSFET20を保護する。

【特許文献1】特開平3-49257号公報(第3図など)

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上述したデバイスを、ESD耐量、サージ・ノイズ耐量の要求が厳しい自動車用途に用いる場合には、10kV~15kV(試験条件150pF, 150V)の非常に高いESD耐量が要求され、特にパワー半導体素子においては実力耐量25kV以上の高いESD耐量が要求される。

MOSFET等を備えたパワーICでは上記の要求が満たせない場合には、コンデンサ、ダイオード、抵抗等の素子をディスクリート部品の外付け対応する必要があり、部品点数の増加、組立等の作業工数の増加、コストの増加等の課題がある。

これに対して図3に示す構成を採用することにより、外付け部品の削減を図ることができる。

【0006】

しかしながら、上記の要求を満たすサージ吸収素子は、所望のサージ吸収能力を満たすためにその能力に余裕を持たせて形成されるため、チップ面積が大きくなる。

複数の素子を1チップに集積し、高耐圧化、微細化を図ってチップ面積を縮小しようとする中でサージ吸収素子の面積が増大するのは、チップ面積を縮小してコストを圧縮するうえでの大きな問題である。

10

20

30

40

50

本発明は、上記問題点に鑑みてなされたものであって、過剰なサージ吸収能力を必要とせず、より小さいチップ面積で必要な高ESD耐量および高サージ耐量を備えた横型MOSFETを有する半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

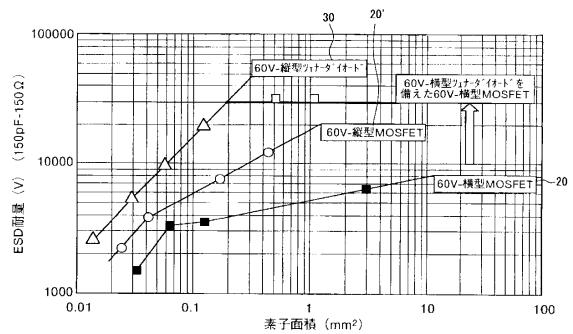

上記目的を達成するため、本発明者らは鋭意研究をおこなった。その内容について説明する。本発明者らは、60V定格の横型MOSFET20、縦型MOSFET20'および縦型ツエナーダイオード30の素子領域面積に対するESD耐量を求める実験をおこなった。その結果を図4に示す。なお、基板、プロセス条件および素子の降伏電圧は同一である。また、ESD耐量の測定条件として、主に日本国内における自動車用途で用いられる150pF-150の条件を用いて実施した。この自動車用途で要求されるESD耐量は10kV~15kV以上であり、特に前記MOSFET20, 20'に要求される実力耐量は25kV以上である。

従来、上述した要求を満たせない場合には、外付けディスクリート部品として保護コンデンサ、ダイオードおよび抵抗等を追加することによって、前記MOSFET20, 20'等を備えたパワーIC等が実用化されている。その代わり、コストが増大するという不利益がある。図4からわかるように、MOSFET20, 20'を用いて上述したESD耐量要求を満たすためには、素子面積が十分大きい必要がある。特に、横型MOSFET20では、10kVのESD耐量を達成するためには、10mm<sup>2</sup>を超える大きな面積が必要である。それに対して、縦型ツエナーダイオード30では、パッド電極レベルの0.2mm<sup>2</sup>の小さな素子面積で30kVのESD耐量を達成することができる。

【0008】

横型MOSFET20においては、微細化が進み、それによって単位面積あたりのオン抵抗が下がり、60V定格では1m<sup>-1</sup>cm<sup>2</sup>まで発展してきている。現在、自動車用途でもっとも多い数百m<sup>-1</sup>のオン抵抗領域では、横型MOSFET20の素子面積は数mm<sup>2</sup>程度で十分である。今後、ますますパワーICに搭載される素子面積が小さくなるため、ESD耐量は下がる傾向にある。今回、本発明者らは、横型MOSFET20、縦型MOSFET20'および縦型ツエナーダイオード30の素子面積に対するESD耐量の関係を、データとして同じ尺度で定量化した。それによって、横型MOSFET20、縦型MOSFET20'および縦型ツエナーダイオード30について、ESD耐量の傾向と問題を定量的に扱うことができるようになった。

【0009】

上記の点を踏まえ、本発明においては、第1導電型の半導体基板のおもて面側に、第2導電型の第1の領域と、該第2導電型の第1の領域内に第1導電型の第1の領域と第2の領域を形成して横型のトランジスタを構成し、同一の半導体基板のおもて面側に、前記第2導電型の第1の領域とは離間してかつ面積が小さな第2導電型の第2の領域と、該第2導電型の第2の領域内に、第2導電型の第2の領域より高濃度の第2導電型の第3の領域を形成して縦型のダイオードを構成し、前記第2導電型の第3の領域と前記第1導電型の第1の領域とを接続するとともに、前記半導体基板の裏面と前記第1導電型の第2の領域とを接続することで、前記縦型のダイオードを前記横型のトランジスタのサージ吸収素子とし、前記横型のトランジスタの降伏動作時の抵抗より前記サージ吸収素子の降伏動作時の抵抗が小さく、かつ、前記トランジスタの二次降伏電流より前記サージ吸収素子の二次降伏電流が大きいことを特徴とする。

【発明の効果】

【0010】

本発明によれば、通常MOSFET動作にはなんら影響を与えず、ESDやサージ等の吸収能力を損なうことなく、十分小さい面積で高ESD耐量および高サージ耐量を有する半導体装置を得ることができる。したがって、半導体装置の微細集積化に伴うESD耐量およびサージ・ノイズ耐量の低下を抑制し、チップ面積の大幅な増加を招くことなく、より低コストな半導体基板を用いて高ESD耐量および高サージ・ノイズ耐量を有する、よ

10

20

30

40

50

り低価格の統合型のパワーICおよび統合型の通信IC等を実現することができる

【発明を実施するための最良の形態】

【0011】

本発明の実施の形態にかかる半導体装置は、横型MOSFETと縦型サージ吸収素子としてのツエナーダイオードとを、特別な素子分離構造を形成せずに、同一半導体基板上に形成し、横型MOSFETのドレイン電極またはソース電極と縦型ツエナーダイオードの表面電極とを金属電極配線により電気的に接続した構成となっている。

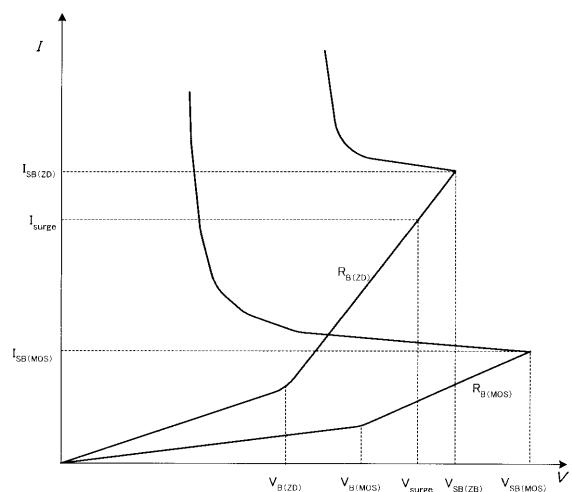

図1は、トランジスタとしての横型MOSFET20とサージ吸収素子としてのツエナーダイオード30のI-V特性を示す図である。

先ず、横型MOSFET20の降伏動作時の抵抗( $R_{B(MOS)}$ )は降伏動作時の傾き( $dI/dV$ )であり、縦型ツエナーダイオード30の降伏動作時の抵抗( $R_{B(ZD)}$ )との間に(1)式の関係を満たし、

(数1)

$$(R_{B(ZD)}) < (R_{B(MOS)}) \dots (1)$$

同時に横型MOSFET20の二次降伏電流( $I_{SB(MOS)}$ )と縦型ツエナーダイオード30の二次降伏電流( $I_{SB(ZD)}$ )との間に(2)式の関係を満たすものとする(条件1)。

(数2)

$$(I_{SB(ZD)}) > (I_{SB(MOS)}) \dots (2)$$

【0012】

さらに、上記(1),(2)式の関係に加えて、横型MOSFET20の降伏電圧( $V_{B(MOS)}$ )と縦型ツエナーダイオードの降伏電圧( $V_{B(ZD)}$ )との間に(3)式の関係を満たすものとする(条件2)。

(数3)

$$(V_{B(ZD)}) < (V_{B(MOS)}) \dots (3)$$

さらに、上記(1),(2)式の関係に加えて、横型MOSFET20の二次降伏電圧( $V_{SB(MOS)}$ )と縦型ツエナーダイオードの二次降伏電圧( $V_{SB(ZD)}$ )との間に(4)式の関係を満たすものとする(条件3)。

(数4)

$$(V_{SB(ZD)}) < (V_{SB(MOS)}) \dots (4)$$

【0013】

また、上記(1),(2)式の関係に加えて、所望のESD及びサージ・ノイズ耐量における縦型ツエナーダイオード30に流れるサージ電流( $I_{surge}$ )とし、縦型ツエナーダイオード30の二次降伏電流( $I_{SB(ZD)}$ )との間に(5)式の関係を満たすものとする(条件5)。

(数5)

$$(I_{surge}) < (I_{SB(ZD)}) \dots (5)$$

【0014】

ここで、サージ電流( $I_{surge}$ )は、例えば、試験条件150pF, 150Vにおいて25kVのサージ電圧を想定したときに流れる電流であり、後述の図2における経路Fには約100Aの電流が瞬間に流れる。測定条件は、素子の仕様により任意に設定されるものであり、サージ電圧も素子の特性に応じて任意に設定される。

なお縦型ツエナーダイオード30と横型MOSFET20とが上記の関係を満たすためには、両素子が形成される半導体基板の抵抗率を0.3~1.0cmとすればよい。また、特に半導体基板の裏面に半導体層を設けるとよく、例えばこの裏面半導体層の抵抗率を0.1cm以下とすればよい。

また、縦型ツエナーダイオードの降伏電圧( $V_{B(ZD)}$ )を所望値に定めるためには、縦型ツエナーダイオード30が形成されるウエル領域と半導体基板裏面の半導体層との間で、パンチスルーやリーチスルーや起こることを条件とし、前記ウエル層の接合深さ及び不純物濃度と、半導体基板の抵抗率および厚さを決定すればよい。

10

20

30

40

50

## 【0015】

例えば、図3の構成において、 $0.95 \text{ cm}$ の低濃度n層12上に不純物を $2.7 \times 10^{14} \text{ cm}^{-2}$ でイオン注入してpウエル31を形成する。

そして、上記の条件1～条件5をすべて充足するものとする。

## 〔実施例〕

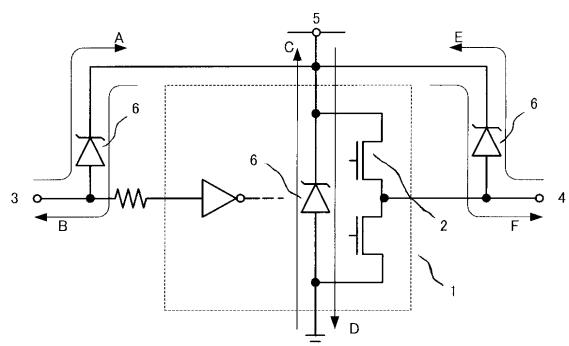

次に、図2を用いて実施例を説明する。図2は本発明の実施例を示す図であり、1は複数のMOSFET2から構成されるICであって入力端子3、出力端子4、電源端子5を備えている。

## 【0016】

IC1にサージ電圧が印加されると、矢印A～Fに示す経路でサージ電流が流れる。このようなサージ電圧からIC1即ちIC1を構成するMOSFET2を保護するために、入力端子3～電源端子5間、出力端子4～電源端子5間、電源端子5～接地間にツェナーダイオード6を設けている。

このとき、ツェナーダイオード6とMOSFET2との間は、上述した(条件1)～(条件5)の関係を満たすものとする。

上記の関係を満たすとき、ツェナーダイオード6とMOSFET2の動作波形は図1に示すI-V特性となる。ESD等のサージが印加されると、ツェナーダイオード6とMOSFET2には $V_{surge}$ の電圧が印加され、ツェナーダイオード6には $I_{surge}$ の電流が流れる。このとき、上述した条件を満たしていれば、MOSFET2に印加されるサージ電圧 $V_{surge}$ は、MOSFET2の二次降伏電圧 $V_{SB(MOS)}$ を上回ることがなく、MOSFET2をESD等のサージによる破壊から確実に保護することができる。

## 【0017】

このように構成することにより、サージ吸収素子のサイズを最適化でき、統合型のインテリジェントスイッチデバイスのチップサイズを縮小することができる。

なお、図2では各経路にツェナーダイオードを配置しているが、サージ電圧が印加されるモードが特定できる場合には、少なくともその端子間にサージ吸収素子を配置すればよく、他の個所への配置は省略できる。サージ吸収素子の配置を省略することによりチップサイズの一層の小型化を図ることができる。

上記の実施の形態および実施例では横型のMOSFETとサージ吸収素子として縦型のツェナーダイオードを例に説明をしたがこれに限るものではなく、上記の条件1～条件5を充足する素子を採用することができる。

## 【図面の簡単な説明】

## 【0018】

【図1】横型MOSFETとツェナーダイオードI-V特性を示す図である。

【図2】本発明の実施例の構成を示す断面図である。

【図3】従来の統合型のインテリジェントスイッチデバイスの構成を示す断面図である。

【図4】60V定格の横型MOSFET、縦型MOSFET、縦型ツェナーダイオードおよび高ESD耐量を備えた横型MOSFETについて、素子面積に対するESD耐量の実験結果を示す特性図である。

## 【符号の説明】

## 【0019】

- 1 IC

- 2 MOSFET

- 3 入力端子

- 4 出力端子

- 5 電源端子

- 6 ツェナーダイオード

- 11 高濃度n層(半導体基板)

- 12 低濃度n層(半導体基板)

- 13 裏面電極(カソード電極)

10

20

30

40

50

- 2 0 サージ吸収素子(縦型ダイオード)

2 1 , 3 1 p ウェル

2 2 , 2 4 n 型高濃度層

2 3 n ベース

2 5 ドレイン電極

2 6 ゲート電極

2 7 ソース電極

3 2 p 型高濃度層

3 3 アノード電極

3 5 , 3 6 配線

10

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

- (72)発明者 篠谷 由成

東京都品川区大崎一丁目11番2号 富士電機デバイステクノロジー株式会社内

- (72)発明者 市村 武

東京都品川区大崎一丁目11番2号 富士電機デバイステクノロジー株式会社内

- (72)発明者 八重澤 直樹

東京都品川区大崎一丁目11番2号 富士電機デバイステクノロジー株式会社内

- (72)発明者 斎藤 龍

東京都品川区大崎一丁目11番2号 富士電機デバイステクノロジー株式会社内

- (72)発明者 古畑 昌一

東京都品川区大崎一丁目11番2号 富士電機デバイステクノロジー株式会社内

- (72)発明者 原田 祐一

神奈川県横須賀市長坂二丁目2番1号 富士電機アドバンストテクノロジー株式会社内

合議体

審判長 北島 健次

審判官 小川 将之

審判官 恩田 春香

- (56)参考文献 特開平05-136348 (JP, A)

特開平09-223748 (JP, A)

特開平01-276673 (JP, A)

特開2000-133799 (JP, A)

特開2002-057335 (JP, A)

特開平02-000369 (JP, A)

特開2000-286391 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822, 27/04