(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6572738号

(P6572738)

(45) 発行日 令和1年9月11日(2019.9.11)

(24) 登録日 令和1年8月23日(2019.8.23)

(51) Int.Cl.

F 1

**G09F** 9/30 (2006.01)

**G09G** 3/3233 (2016.01)

**G09G** 3/20 (2006.01)

**H01L** 51/50 (2006.01)

GO9F 9/30 338

GO9G 3/3233

GO9G 3/20 680H

GO9G 3/20 624B

GO9G 3/20 611D

請求項の数 8 (全 47 頁) 最終頁に続く

(21) 出願番号

特願2015-215231 (P2015-215231)

(22) 出願日

平成27年10月30日(2015.10.30)

(65) 公開番号

特開2017-83800 (P2017-83800A)

(43) 公開日

平成29年5月18日(2017.5.18)

審査請求日

平成30年10月3日(2018.10.3)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100125689

弁理士 大林 章

(74) 代理人 100128598

弁理士 高田 聖一

(74) 代理人 100121108

弁理士 高橋 太朗

(72) 発明者 太田 人嗣

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72) 発明者 野澤 陵一

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

最終頁に続く

(54) 【発明の名称】電気光学装置、電子機器、及び電気光学装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の導電層と、

第2の導電層と、

第3の導電層と、

前記第2の導電層に接続された第4の導電層と、前記第3の導電層と前記第4の導電層との間の誘電体膜とを有する第1容量と、

前記第2の導電層と前記第3の導電層とを、導通状態又は非導通状態にする第1トランジスターと、

前記第3の導電層と前記第1の導電層とに対応して設けられた画素回路と、を有し、

前記画素回路は、

駆動トランジスターと、

前記第3の導電層と、前記駆動トランジスターのゲートとの間に接続された第2トランジスターと、

前記駆動トランジスターの電流端と、前記駆動トランジスターのゲートとを導通させるための第3トランジスターと、

前記駆動トランジスターを介して供給される電流の大きさに応じた輝度で発光する発光素子と、

前記駆動トランジスターの前記電流端と、前記発光素子との間に接続された第4トランジスターと、を含み、

10

20

前記第1トランジスターと前記第2の導電層との接続位置は、前記画素回路の平面視において、前記駆動トランジスターの前記電流端と前記第3トランジスターとの接続位置よりも、前記第4トランジスターと前記発光素子との接続位置に近い、

ことを特徴とする電気光学装置。

【請求項2】

前記接続位置のそれぞれは、一の前記画素回路における電源線と、当該一の画素回路の隣の行の前記画素回路における電源線との間に配置される、

ことを特徴とする請求項1に記載の電気光学装置。

【請求項3】

前記発光素子にリセット電位を供給するリセット電位供給線と、前記発光素子との間に接続された第5トランジスターとをさらに含み、 10

前記第1トランジスターと前記第2の導電層との接続位置は、前記第5トランジスターのゲートに接続される制御線と、前記第1トランジスターのゲートに接続される制御線との間に配置される、

ことを特徴とする請求項1または請求項2に記載の電気光学装置。

【請求項4】

前記発光素子にリセット電位を供給するリセット電位供給線と、前記発光素子との間に接続された第5トランジスターとをさらに含み、

前記第4トランジスターと前記発光素子との接続位置は、前記第5トランジスターのゲートに接続される制御線と、前記第4トランジスターのゲートに接続される制御線との間に配置される、 20

ことを特徴とする請求項1乃至請求項3のいずれか一項に記載の電気光学装置。

【請求項5】

前記第2の導電層には、二以上の前記第3の導電層が、それぞれ前記第1容量を介して接続され、前記第3の導電層を介して同一の前記第2の導電層に接続された前記画素回路の集合を画素列とし、前記画素列に含まれる前記画素回路の個数よりも少ない個数の前記画素回路を一つのブロックとすると、前記第3の導電層は、各ブロックに対して設けられてなる、

ことを特徴とする請求項1乃至請求項4のいずれか一項に記載の電気光学装置。

【請求項6】

前記第1容量は、前記第3の導電層ごとに設けられている、

ことを特徴とする請求項5に記載の電気光学装置。 30

【請求項7】

走査線と、

第1データ転送線と、

第2データ転送線と、

前記第1データ転送線に接続された第1電極と、前記第2データ転送線と前記第1電極との間の誘電体膜とを有する第1容量と、

前記第1データ転送線と前記第2データ転送線とを、導通状態又は非導通状態にする第1トランジスターと、 40

前記第2データ転送線と前記走査線とに対応して設けられた画素回路と、を有し、

前記画素回路は、

駆動トランジスターと、

前記第2データ転送線と、前記駆動トランジスターのゲートとの間に接続された第2トランジスターと、

前記駆動トランジスターの電流端と、前記駆動トランジスターのゲートとを導通させるための第3トランジスターと、

前記駆動トランジスターを介して供給される電流の大きさに応じた輝度で発光する発光素子と、

前記駆動トランジスターの前記電流端と、前記発光素子との間に接続された第4トラン

ジスターと、を含み、

前記第1トランジスターと前記第1データ転送線との接続位置は、前記画素回路の平面視において、前記駆動トランジスターの前記電流端と前記第3トランジスターとの接続位置よりも、前記第4トランジスターと前記発光素子との接続位置に近い、

ことを特徴とする電気光学装置。

**【請求項8】**

請求項1乃至請求項7のいずれかに記載の電気光学装置を備える、

ことを特徴とする電子機器。

**【発明の詳細な説明】**

**【技術分野】**

10

**【0001】**

本発明は、電気光学装置、電子機器、及び電気光学装置の駆動方法に関する。

**【背景技術】**

**【0002】**

近年、有機発光ダイオード（以下、OLED（Organic Light Emitting Diode）という）素子などの発光素子を用いた電気光学装置が各種提案されている。この電気光学装置の一般的な構成では、走査線とデータ線との交差に対応して、発光素子やトランジスターなどを含む画素回路が、表示すべき画像の画素に対応して設けられる。

このような構成において、画素の階調レベルに応じた電位のデータ信号が駆動トランジスターのゲートに印加されると、駆動トランジスターは、ゲート・ソース間の電圧に応じた電流を発光素子に供給する。これにより、当該発光素子は、階調レベルに応じた輝度で発光する。

20

**【0003】**

トランジスターを発光強度の調節に用いる駆動方式では、各画素に設けられたトランジスターの閾値電圧がばらつくと、発光素子に流れる電流がばらつくため、表示画像の画質が低下してしまう。従って、画質の低下を防ぐためには、トランジスターの閾値電圧のばらつきを補償する必要がある。そこで、トランジスターのゲート電圧を閾値電圧に調整するため、トランジスターのゲートとドレインまたはソースとの間に補償用トランジスターを設けると共に、トランジスターのゲートとデータ線との間にカッピング容量を設けた装置が提案されている（例えば特許文献1参照）。

30

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献1】特開2008-191247号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

しかしながら、特許文献1の装置においては、カッピング容量の電極のうちトランジスターのゲートに接続された電極が、発光期間中にフローティング状態となるため、データ線の電位変動の影響を受ける。その結果、トランジスターのゲート電圧を閾値電圧に維持することができず、表示不具合が生じる虞があった。

40

本発明は上述した事情に鑑みてなされたものであり、その目的は、データ信号が供給される素子の電位変動の影響を抑制し、表示品位を向上することである。

**【課題を解決するための手段】**

**【0006】**

上記目的を達成するために、本発明の一態様に係る電気光学装置は、第1の導電層と、第2の導電層と、第3の導電層と、前記第2の導電層に接続された第4の導電層と、前記第3の導電層と前記第4の導電層との間の誘電体膜とを有する第1容量と、前記第2の導電層と前記第3の導電層とを、導通状態又は非導通状態にする第1トランジスターと、前記第3の導電層と前記第1の導電層とに対応して設けられた画素回路と、を有し、前記画

50

素回路は、駆動トランジスターと、前記第3の導電層と、前記駆動トランジスターのゲートとの間に接続された第2トランジスターと、前記駆動トランジスターの電流端と、前記駆動トランジスターのゲートとを導通させるための第3トランジスターと、前記駆動トランジスターを介して供給される電流の大きさに応じた輝度で発光する発光素子と、前記駆動トランジスターの前記電流端と前記発光素子との間に接続された第4トランジスターと、を含み、前記第1トランジスターと前記第2の導電層との接続位置は、前記画素回路の平面視において、前記駆動トランジスターの前記電流端と前記第3トランジスターとの接続位置よりも、前記第4トランジスターと前記発光素子との接続位置に近い、ことを特徴とする。

## 【0007】

10

この態様によれば、画素回路は、第3の導電層の一例としての第2データ転送線と、第1の導電層の一例としての走査線とに対応して設けられる。第2の導電層の一例としての第1データ転送線は複数の画素回路に対して共通に設けられるが、第2データ転送線を介して同一の第1データ転送線に接続された画素回路の集合を画素列とし、この画素列に含まれる画素回路の個数よりも少ない個数の画素回路を一つのブロックとすると、第2データ転送線は、各ブロックに対して設けられる。このような画素回路において、第1データ転送線と第2データ転送線とを導通状態又は非導通状態にする第1トランジスターと、第1データ転送線との接続位置をAとした場合、接続位置Aは、駆動トランジスター及び第3トランジスターとの関係で以下のように説明される。まず、駆動トランジスターの電流端と、駆動トランジスターの電流端とゲートを導通させるための第3トランジスターとの接続位置をBとする。次に、第4トランジスターと発光素子との接続位置をCとする。この場合、本発明の前記態様は、画素回路の平面視において、接続位置Aが、接続位置Bよりも接続位置Cに近くなっている。第1データ転送線には、振幅の大きいデータ信号が供給されるが、第1データ転送線と第1トランジスターとの接続位置である接続位置Aは、駆動トランジスターと第3トランジスターとの接続位置である接続位置Bよりも、第4トランジスターと発光素子との接続位置である接続位置Cに近い。したがって、振幅の大きい信号が第1データ転送線に供給されても、駆動トランジスターのゲートが、振幅の大きい信号の電位変動から受ける影響が少なくなり、表示品位が向上することになる。

20

## 【0008】

30

本発明の他の態様に係る電気光学装置は、前記接続位置のそれぞれは、一の前記画素回路における電源線と、当該一の画素回路の隣の行の前記画素回路における電源線との間に配置される、ことを特徴とする。この態様によれば、一の画素回路における接続位置Aと、当該一の画素回路の隣の行の他の画素回路における接続位置Bとの間に電源線が存在するので、当該電源線がシールドとなり、駆動トランジスターのゲートが、当該振幅の大きい信号の電位変動から受ける影響が少なくなる。その結果、表示品位が向上することになる。

## 【0009】

40

本発明の他の態様に係る電気光学装置は、前記発光素子にリセット電位を供給するリセット電位供給線と、前記発光素子との間に接続された第5トランジスターとをさらに含み、前記第1トランジスターと前記第2の導電層との接続位置は、前記第5トランジスターのゲートに接続される制御線と、前記第1トランジスターのゲートに接続される制御線との間に配置される、ことを特徴とする。この態様によれば、第1トランジスターと第1データ転送線との接続位置は、第5トランジスターのゲートに接続される制御線と、第1トランジスターのゲートに接続される制御線とにより挟まれているので、これらの制御線がシールドとなり、駆動トランジスターのゲートが、振幅の大きい信号の電位変動から受ける影響が少なくなる。その結果、表示品位が向上することになる。

## 【0010】

本発明の他の態様に係る電気光学装置は、前記発光素子にリセット電位を供給するリセット電位供給線と、前記発光素子との間に接続された第5トランジスターとをさらに含み、

50

前記第4トランジスターと前記発光素子との接続位置は、前記第5トランジスターのゲートに接続される制御線と、前記第4トランジスターのゲートに接続される制御線との間に配置される、ことを特徴とする。この態様によれば、接続位置Cは、第5トランジスターのゲートに接続される制御線と、第4トランジスターのゲートに接続される制御線により挟まれているので、これらの制御線がシールドとなり、発光素子への電流を供給する箇所が、振幅の大きい信号の電位変動から受ける影響が少なくなる。その結果、表示品位が向上することになる。

## 【0011】

本発明の他の態様に係る電気光学装置は、前記第2の導電層には、少なくとも一つの前記第3の導電層が、前記第1容量を介して接続され、前記第3の導電層を介して同一の前記第2の導電層に接続された所定数の前記画素回路の集合を画素列とし、前記画素列に含まれる前記画素回路の個数以下の個数の前記画素回路を一つのブロックとすると、前記第3の導電層は、各ブロックに対して設けられてなる、ことを特徴とする。この態様によれば、第3の導電層の一例としての第2データ転送線と、第1容量の一例としての転送容量を共通化することができる。

10

## 【0012】

本発明の他の態様に係る電気光学装置は、前記第1容量は、前記第3の導電層ごとに設けられている、ことを特徴とする。この態様によれば、第1データ転送線に振幅の大きいデータ信号が供給される場合でも、各駆動トランジスターのゲートに接続される各第2データ転送線への電位変動の影響を抑えることができる。

20

## 【0013】

上記目的を達成するために、本発明の一態様に係る電子機器は、前記各態様のいずれかに係る電気光学装置を備えることを特徴とする。この態様によれば、前記各態様のいずれかに係る電気光学装置を備える電子機器が提供される。

## 【図面の簡単な説明】

## 【0014】

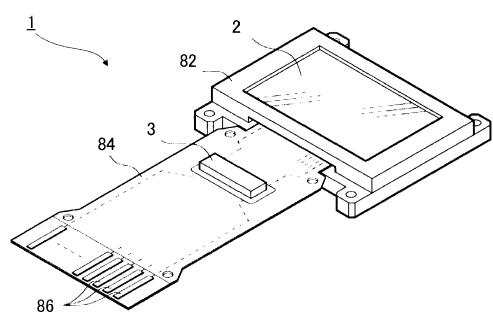

【図1】本発明の第1実施形態に係る電気光学装置の構成を示す斜視図である。

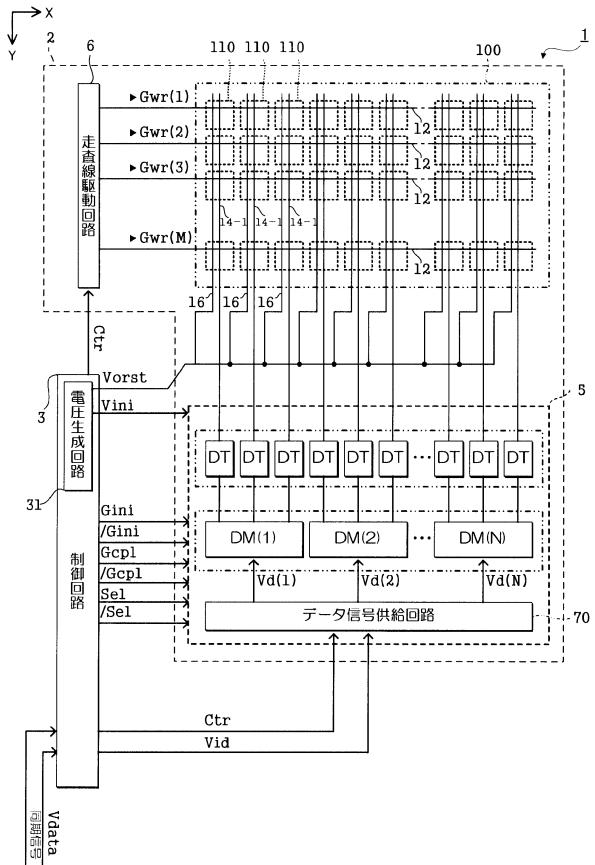

【図2】同電気光学装置の構成を示すブロック図である。

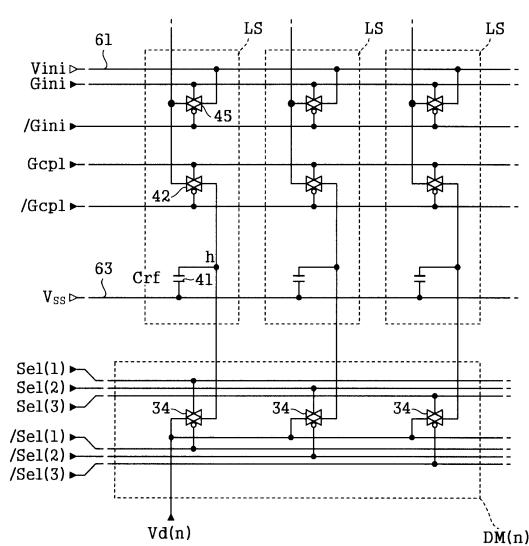

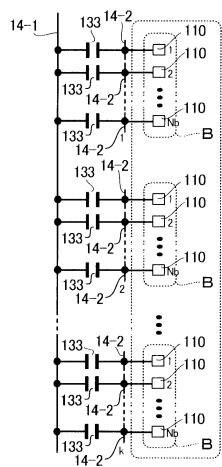

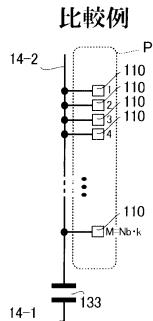

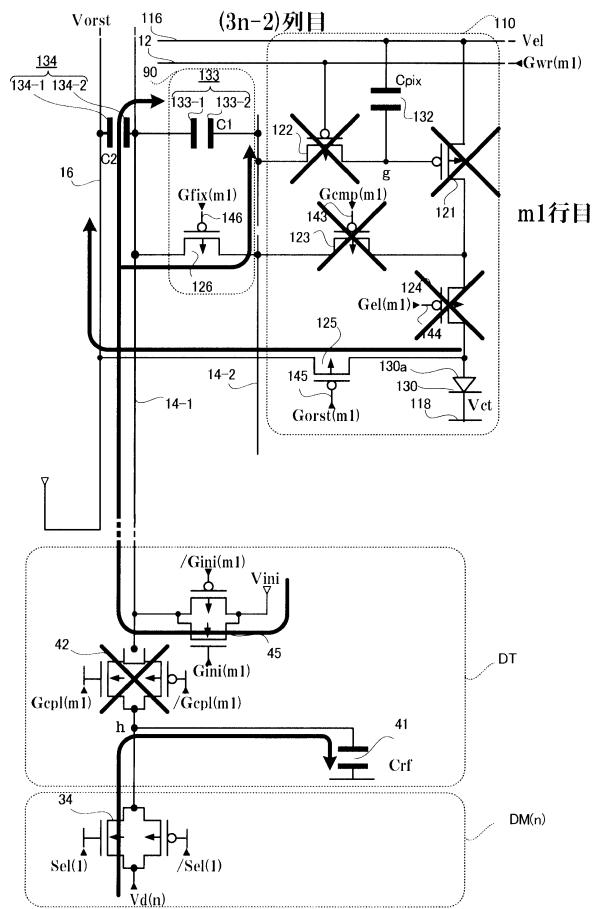

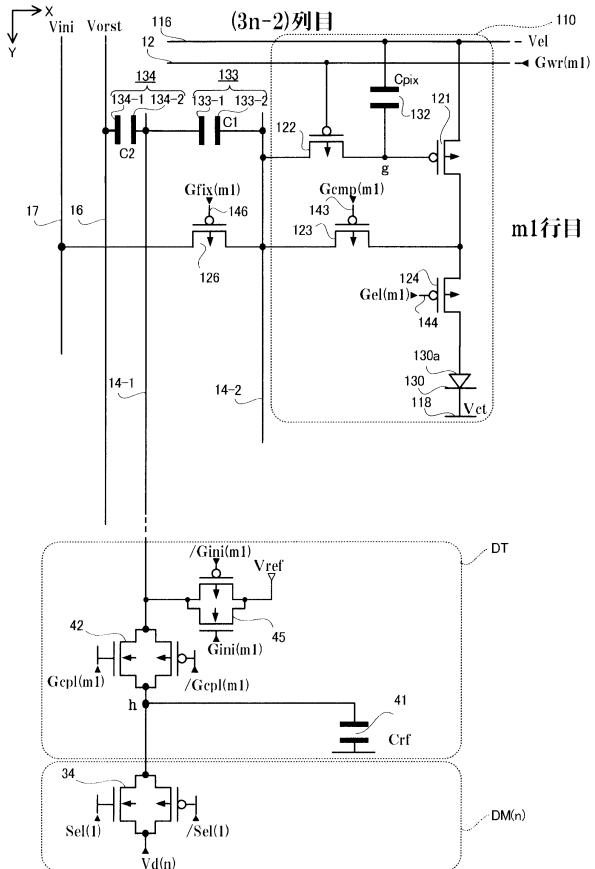

【図3】同電気光学装置のデマルチプレクサとデータ転送回路との構成を説明するための回路図である。

30

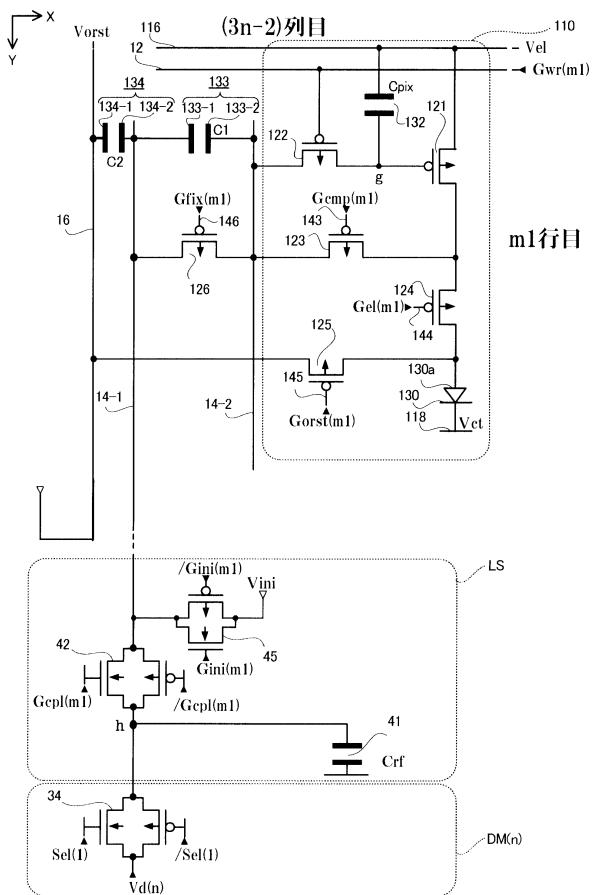

【図4】同電気光学装置の画素回路の構成を示す回路図である。

【図5】同電気光学装置に特有の構成を説明する図である。

【図6】比較例として示す従来の構成を説明する図である。

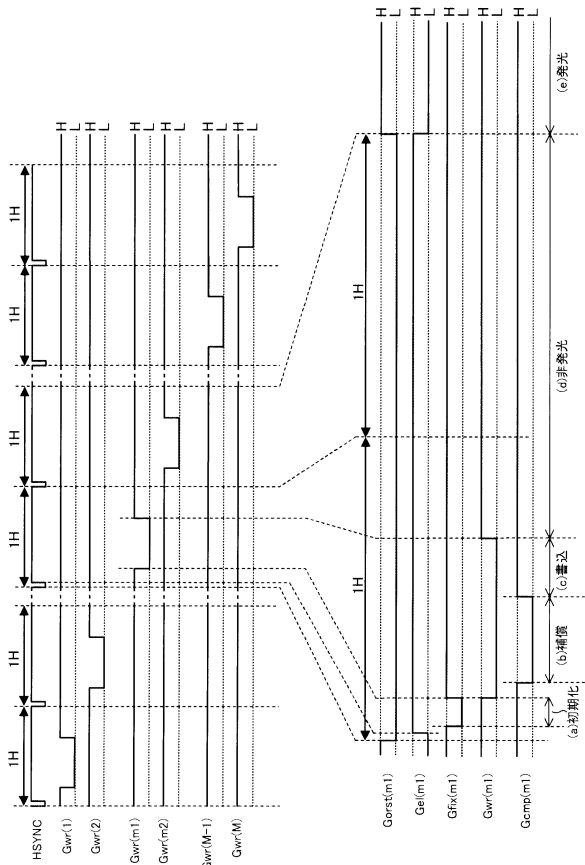

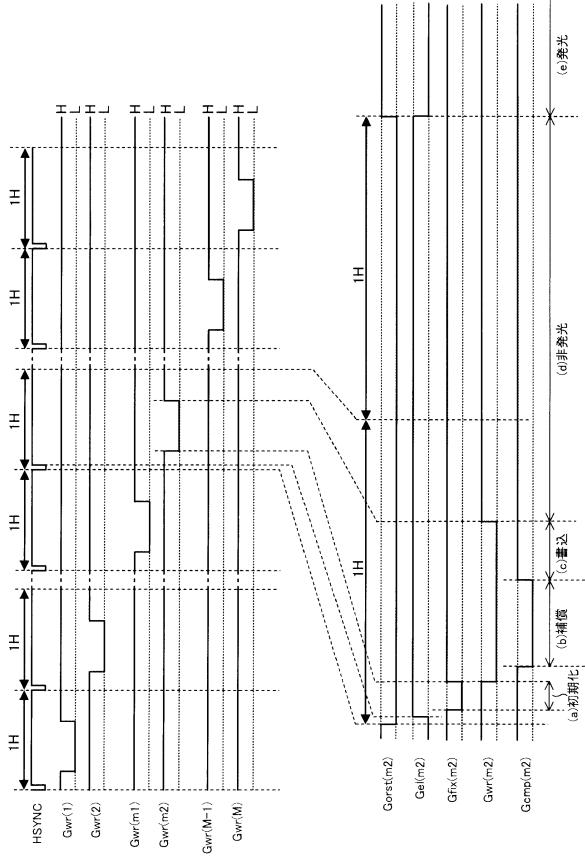

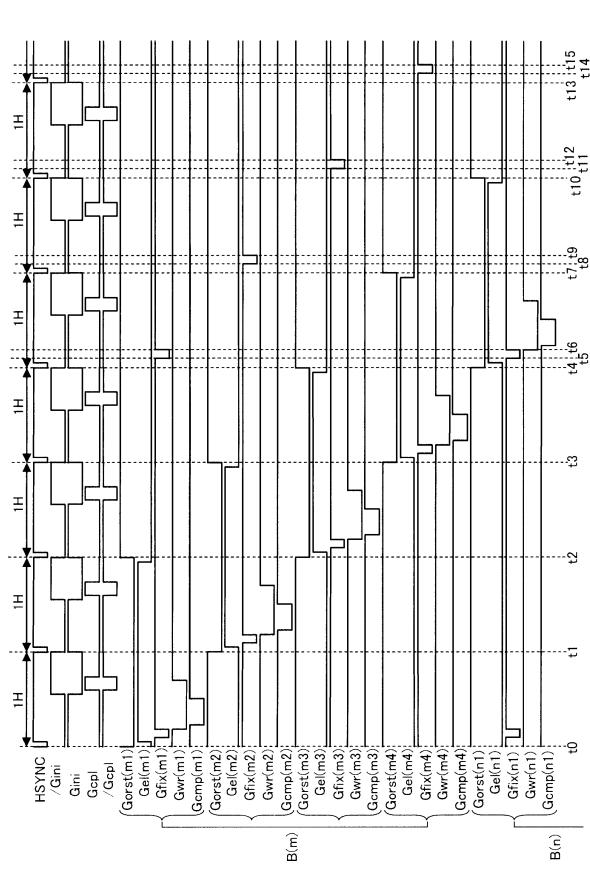

【図7】同電気光学装置の動作を示すタイミングチャートである。

【図8】同電気光学装置の動作説明図である。

【図9】同電気光学装置の動作を示すタイミングチャートである。

【図10】同電気光学装置の動作説明図である。

【図11】同電気光学装置の動作説明図である。

【図12】同電気光学装置の動作説明図である。

【図13】同電気光学装置の動作を示すタイミングチャートである。

40

【図14】同電気光学装置の動作説明図である。

【図15】基板上に形成される各要素の説明図である。

【図16】基板上に形成される各要素の説明図である。

【図17】発光装置の断面図である。

【図18】本発明の第2実施形態に係る電気光学装置の基板上に形成される各要素の説明図である。

【図19】基板上に形成される各要素の説明図である。

【図20】発光装置の断面図である。

【図21】基板上に形成される各要素の説明図である。

【図22】基板上に形成される各要素の説明図である。

50

【図23】本発明の第3実施形態に係る電気光学装置の画素回路の構成を示す回路図である。

【図24】基板上に形成される各要素の説明図である。

【図25】基板上に形成される各要素の説明図である。

【図26】発光装置の断面図である。

【図27】本発明の第4実施形態に係る電気光学装置の画素回路の構成を示す回路図である。

【図28】基板上に形成される各要素の説明図である。

【図29】基板上に形成される各要素の説明図である。

【図30】発光装置の断面図である。

10

【図31】変形例に係る画素回路の構成を示す回路図である。

【図32】変形例に係る画素回路の構成を示す回路図である。

【図33】変形例に係る画素回路の第1データ転送線、転送容量、第2データ転送線及び画素回路の関係を示す図である。

【図34】HMDの外観構成を示す図である。

【図35】HMDの光学構成を示す図である。

【発明を実施するための形態】

【0015】

<第1実施形態>

図1は、本発明の第1実施形態に係る電気光学装置1の構成を示す斜視図である。電気光学装置1は、例えばヘッドマウント・ディスプレイにおいて画像を表示するマイクロ・ディスプレイである。

20

図1に示すように、電気光学装置1は、表示パネル2と、表示パネル2の動作を制御する制御回路3とを備える。表示パネル2は、複数の画素回路と、当該画素回路を駆動する駆動回路とを備える。本実施形態において、表示パネル2が備える複数の画素回路及び駆動回路は、シリコン基板に形成され、画素回路には、発光素子の一例であるOLEDが用いられる。また、表示パネル2は、例えば、表示部で開口する枠状のケース82に収納されるとともに、FPC(Flexible Printed Circuits)基板84の一端が接続される。

FPC基板84には、半導体チップの制御回路3が、COF(Chip On Film)技術によって実装されるとともに、複数の端子86が設けられて、図示省略された上位回路に接続される。

30

【0016】

図2は、実施形態に係る電気光学装置1の構成を示すブロック図である。上述のとおり、電気光学装置1は、表示パネル2と、制御回路3とを備える。

制御回路3には、図示省略された上位回路よりデジタルの画像データVdataが同期信号に同期して供給される。ここで、画像データVdataとは、表示パネル2(厳密には、後述する表示部100)で表示すべき画像の画素の階調レベルを例えば8ビットで規定するデータである。また、同期信号とは、垂直同期信号、水平同期信号、及び、ドットクロック信号を含む信号である。

【0017】

40

制御回路3は、同期信号に基づいて、各種制御信号を生成し、これを表示パネル2に対して供給する。具体的には、制御回路3は、表示パネル2に対して、制御信号Ctrと、正論理の制御信号Giniと、これと論理反転の関係にある負論理の制御信号/Giniと、正論理の制御信号Gcplと、これと論理反転の関係にある負論理の制御信号/Gcplと、制御信号Sel(1)、Sel(2)、Sel(3)と、これらの信号に対して論理反転の関係にある制御信号/Sel(1)、/Sel(2)、/Sel(3)と、を供給する。

ここで、制御信号Ctrとは、パルス信号や、クロック信号、イネーブル信号など、複数の信号を含む信号である。

なお、制御信号Sel(1)、Sel(2)、Sel(3)を、制御信号Selと総称し、制御信号/Sel(1)、/Sel(2)、/Sel(3)を、制御信号/Selと総称する場合がある。

50

また、制御回路3は電圧生成回路31を含む。電圧生成回路31は、表示パネル2に対して、各種電位を供給する。具体的には、制御回路3は、表示パネル2に対してリセット電位V<sub>orst</sub>及び初期電位V<sub>ini</sub>等を供給する。

#### 【0018】

さらに、制御回路3は、画像データV<sub>data</sub>に基づいて、アナログの画像信号V<sub>id</sub>を生成する。具体的には、制御回路3には、画像信号V<sub>id</sub>の示す電位、及び、表示パネル2が備える発光素子（後述するOLED130）の輝度を対応付けて記憶したルックアップテーブルが設けられる。そして、制御回路3は、当該ルックアップテーブルを参照することで、画像データV<sub>data</sub>に規定される発光素子の輝度に対応した電位を示す画像信号V<sub>id</sub>を生成し、これを表示パネル2に対して供給する。

10

#### 【0019】

図2に示すように、表示パネル2は、表示部100と、これを駆動する駆動回路（データ転送線駆動回路5及び走査線駆動回路6）とを備える。

表示部100には、表示すべき画像の画素に対応した画素回路110がマトリクス状に配列されている。詳細には、表示部100において、M行の走査線12が図において横方向（X方向）に延在して設けられ、また、3列毎にグループ化された（3N）列の第1データ転送線14-1が図において縦方向（Y方向）に延在し、かつ、各走査線12と互いに電気的な絶縁を保って設けられている。

なお、図面の煩雑化を避けるために図2においては図示していないが、各々の第1データ転送線14-1に対しては、第2データ転送線14-2が電気的に接続可能に且つ縦方向（Y方向）に延在して設けられている（例えば図4参照）。そして、M行の走査線12と、（3N）列の第2データ転送線14-2とに対応して画素回路110が設けられている。このため、本実施形態において画素回路110は、縦M行×横（3N）列でマトリクス状に配列されている。

20

#### 【0020】

ここで、M、Nは、いずれも自然数である。走査線12及び画素回路110のマトリクスのうち、行（ロウ）を区別するために、図において上から順に1、2、3、…、（M-1）M行と呼ぶ場合がある。同様に第1データ転送線14-1及び画素回路110のマトリクスの列（カラム）を区別するために、図において左から順に1、2、3、…、（3N-1）、（3N）列と呼ぶ場合がある。

30

ここで、第1データ転送線14-1のグループを一般化して説明するために、1以上の任意の整数をnと表すと、左から数えてn番目のグループには、（3n-2）列目、（3n-1）列目及び（3n）列目の第1データ転送線14-1が属している、ということになる。

#### 【0021】

なお、同一行の走査線12と、同一グループに属する3列の第2データ転送線14-2とに対応した3つの画素回路110は、それぞれR（赤）、G（緑）、B（青）の画素に対応して、これらの3画素が表示すべきカラー画像の1ドットを表現する。すなわち、本実施形態では、RGBに対応したOLEDの発光によって1ドットのカラーを加法混色で表現する構成となっている。

40

#### 【0022】

また、図2に示すように、表示部100において、（3N）列の給電線（リセット電位供給線）16が、縦方向に延在し、かつ、各走査線12と互いに電気的な絶縁を保って設けられる。各給電線16には、所定のリセット電位V<sub>orst</sub>が共通に給電されている。ここで、給電線16の列を区別するために、図において左から順に1、2、3、…、（3N）列目の給電線16と呼ぶ場合がある。1列目～（3N）列目の給電線16の各々は、1列目～（3N）列目の第1データ転送線14-1（第2データ転送線14-2）の各々に対応して設けられる。

#### 【0023】

走査線駆動回路6は、1個のフレームの期間内にM本の走査線12を1行毎に順番に走

50

査するための走査信号  $G_{wr}$  を、制御信号  $C_{tr}$  に従って生成する。ここで、1、2、3、…、M行目の走査線 1 2 に供給される走査信号  $G_{wr}$  を、それぞれ  $G_{wr}(1)$ 、 $G_{wr}(2)$ 、 $G_{wr}(3)$ 、…、 $G_{wr}(M-1)$ 、 $G_{wr}(M)$  と表記している。

なお、走査線駆動回路 6 は、走査信号  $G_{wr}(1)$  ~  $G_{wr}(M)$  のほかにも、当該走査信号  $G_{wr}$  に同期した各種制御信号を行毎に生成して表示部 1 0 0 に供給するが、図 2 においては図示を省略している。また、フレームの期間とは、電気光学装置 1 が 1 カット（コマ）分の画像を表示するのに要する期間をいい、例えば同期信号に含まれる垂直同期信号の周波数が 1 2 0 H z であれば、その 1 周期分の 8 . 3 ミリ秒の期間である。

#### 【 0 0 2 4 】

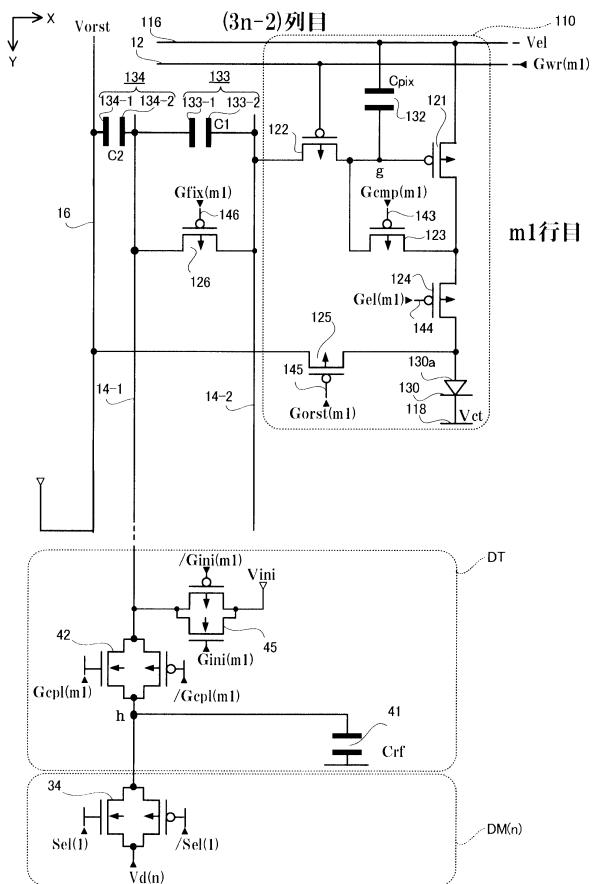

データ転送線駆動回路 5 は、( 3 N ) 列の第 1 データ転送線 1 4 - 1 の各々と 1 対 1 に 10 対応して設けられる ( 3 N ) 個のデータ転送回路 D T、各グループを構成する 3 列の第 1 データ転送線 1 4 - 1 毎に設けられる N 個のデマルチプレクサ D M、及び、データ信号供給回路 7 0 を備える。

#### 【 0 0 2 5 】

データ信号供給回路 7 0 は、制御回路 3 より供給される画像信号  $V_{id}$  と制御信号  $C_{tr}$  とに基づいて、データ信号  $V_d(1)$ 、 $V_d(2)$ 、…、 $V_d(N)$  を生成する。すなわち、データ信号供給回路 7 0 は、データ信号  $V_d(1)$ 、 $V_d(2)$ 、…、 $V_d(N)$  を時分割多重した画像信号  $V_{id}$  に基づいて、データ信号  $V_d(1)$ 、 $V_d(2)$ 、…、 $V_d(N)$  を生成する。そして、データ信号供給回路 7 0 は、データ信号  $V_d(1)$ 、 $V_d(2)$ 、…、 $V_d(N)$  を、1、2、…、N 番目のグループに対応するデマルチプレクサ D M に対して、それぞれ供給する。 20

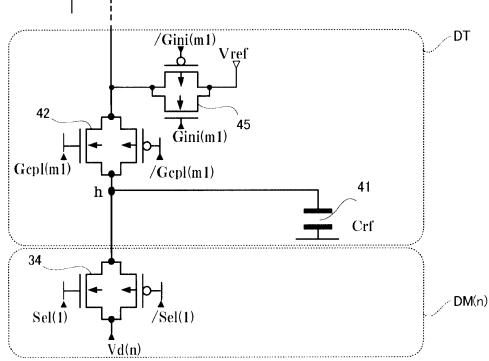

#### 【 0 0 2 6 】

図 3 は、デマルチプレクサ D M とデータ転送回路 D T との構成を説明するための回路図である。なお、図 3 は、n 番目のグループに属するデマルチプレクサ D M と、当該デマルチプレクサ D M に接続された 3 個のデータ転送回路 D T とを、代表的に表している。なお、以下では、n 番目のグループに属するデマルチプレクサ D M を、D M(n) と表記する場合がある。

#### 【 0 0 2 7 】

以下では、図 2 に加えて図 3 を参照しながら、デマルチプレクサ D M 及びデータ転送回路 D T の構成について説明する。

図 3 に示すように、デマルチプレクサ D M は、列毎に設けられたトランスマッショングート 3 4 の集合体であり、各グループを構成する 3 列に、データ信号を順番に供給するものである。ここで、n 番目のグループに属する ( 3 n - 2 )、( 3 n - 1 )、( 3 n ) 列に対応したトランスマッショングート 3 4 の入力端は互いに共通接続されて、その共通端子にそれぞれデータ信号  $V_d(n)$  が供給される。n 番目のグループにおいて左端列である ( 3 n - 2 ) 列に設けられたトランスマッショングート 3 4 は、制御信号  $S_{el}(1)$  が H レベルであるとき ( 制御信号 /  $S_{el}(1)$  が L レベルであるとき ) にオン ( 導通 ) する。同様に、n 番目のグループにおいて中央列である ( 3 n - 1 ) 列に設けられたトランスマッショングート 3 4 は、制御信号  $S_{el}(2)$  が H レベルであるとき ( 制御信号 /  $S_{el}(2)$  が L レベルであるとき ) にオンし、n 番目のグループにおいて右端列である ( 3 n ) 列に設けられたトランスマッショングート 3 4 は、制御信号  $S_{el}(3)$  が H レベルであるとき ( 制御信号 /  $S_{el}(3)$  が L レベルであるとき ) にオンする。 40

#### 【 0 0 2 8 】

データ転送回路 D T は、保持容量 ( 第 3 容量 ) 4 1、トランスマッショングート 4 5、及び、トランスマッショングート 4 2 の組を列毎に有し、後述する初期化期間および補償期間において各列のトランスマッショングート 3 4 の出力端から出力されるデータ信号の電位を保持容量 ( 第 3 容量 ) 4 1 に蓄積し、後述する書き期間において保持容量 ( 第 3 容量 ) 4 1 に蓄積されたデータ信号の電位を、転送容量 1 3 3 に転送する回路である。

#### 【 0 0 2 9 】

各列のトランスマッショングート 4 5 のソース又はドレインは、第 1 データ転送線 1 4 - 1 に電気的に接続される。また、制御回路 3 は、各列のトランスマッショングート 4 5 50

のゲートに対して、制御信号 / Giniを共通に供給する。トランスマッショングート4 5は、第1データ転送線1 4 - 1と、初期電位Viniの供給線とを、制御信号 / GiniがLレベルのときに電気的に接続し、制御信号 / GiniがHレベルのときに電気的に非接続とする。なお、初期電位Viniの供給線6 1には、制御回路3から所定の初期電位Viniが供給される。

#### 【0030】

保持容量4 1は2つの電極を有する。保持容量4 1の一方の電極は、ノードhを介してトランスマッショングート4 2の入力端に電気的に接続される。また、トランスマッショングート4 2の出力端は、第1データ転送線1 4 - 1に電気的に接続される。

制御回路3は、各列のトランスマッショングート4 2に対して、制御信号Gcpl及び制御信号 / Gcplを共通に供給する。このため、各列のトランスマッショングート4 2は、制御信号GcplがHレベルであるとき（制御信号 / GcplがLレベルであるとき）に一斉にオンする。

#### 【0031】

各列の保持容量4 1の一方の電極は、ノードhを介して、トランスマッショングート3 4の出力端、及び、トランスマッショングート4 2の入力端に電気的に接続される。そして、トランスマッショングート3 4がオンした際、保持容量4 1の一方の電極には、トランスマッショングート3 4の出力端を介してデータ信号Vd(n)が供給される。すなわち、保持容量4 1は、一方の電極にデータ信号Vd(n)が供給される。

また、各列の保持容量4 1の他方の電極は、固定電位である電位Vssが供給される給電線6 3に共通に接続される。ここで、電位Vssは、論理信号である走査信号や制御信号のLレベルに相当するものであってもよい。なお、保持容量4 1の容量値をCrfとする。

#### 【0032】

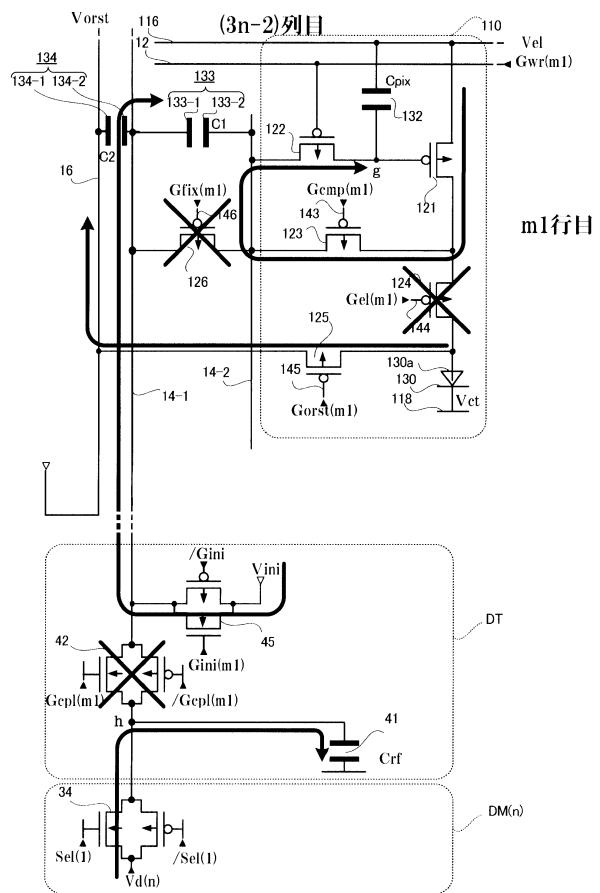

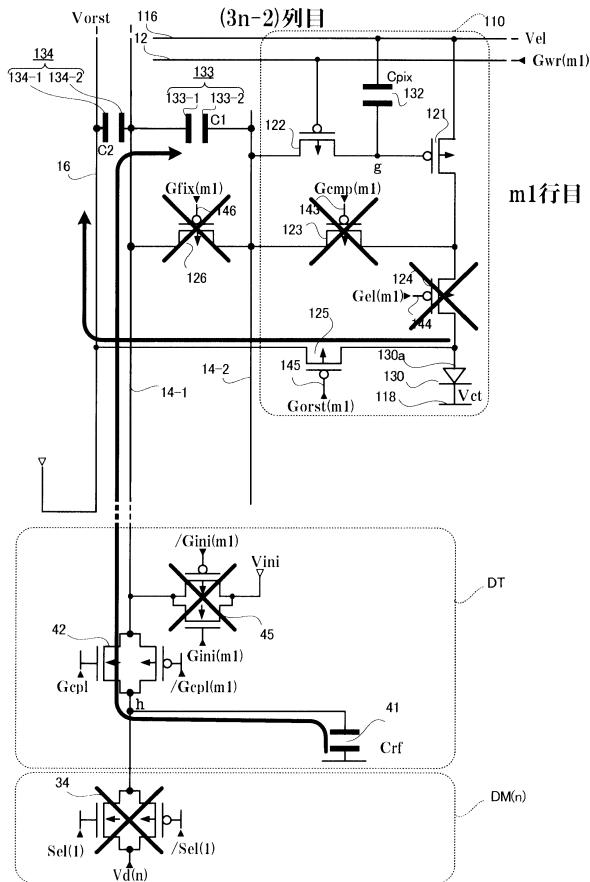

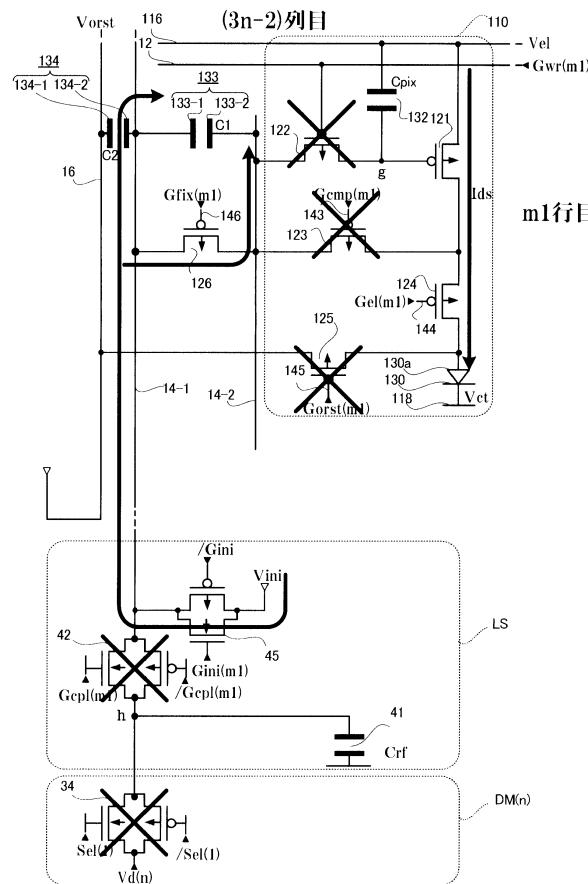

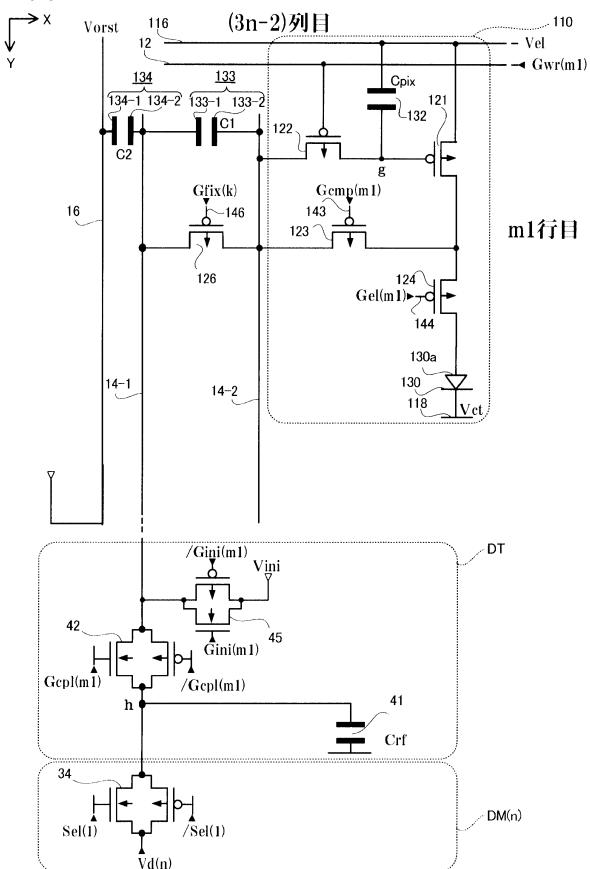

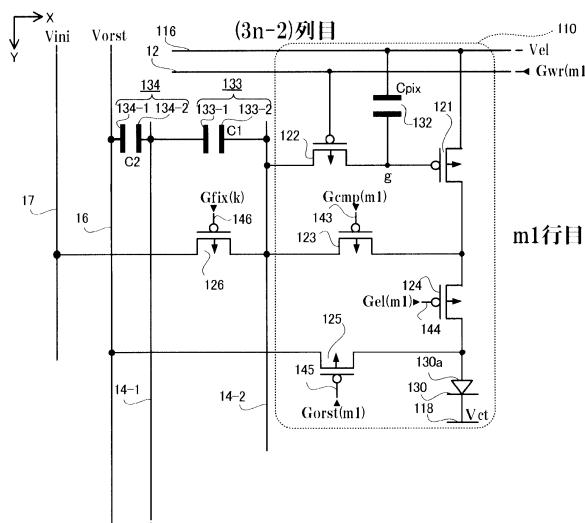

図4を参照して、画素回路1 1 0等について説明する。画素回路1 1 0が配列する行を一般的に示すために、1以上M以下の任意の整数をmと表す。また、1以上M以下であって、連続する任意の整数をm 1、m 2と表す。すなわち、mは、m 1やm 2を包含する一般化した概念である。

各画素回路1 1 0については電気的にみれば互いに同一構成なので、ここでは、m行目に位置し、且つ、n番目のグループのうち左端列の(3n - 2)列目に位置する、m行(3n - 2)列の画素回路1 1 0を例にとって説明する。

#### 【0033】

図4に示されるように、第1データ転送線1 4 - 1には転送容量（第1容量）1 3 3の第1電極1 3 3 - 1と、第1トランジスター1 2 6のソース又はドレインの一方とが電気的に接続されている。また、転送容量1 3 3の第2電極1 3 3 - 2と、第1トランジスター1 2 6のソース又はドレインの他方とは、第2データ転送線1 4 - 2に電気的に接続されている。

つまり、第1データ転送線1 4 - 1と第2データ転送線1 4 - 2との間には、転送容量1 3 3と第1トランジスター1 2 6とが並列に接続される。

また、画素回路1 1 0は、第2データ転送線1 4 - 2に対して接続される。すなわち、画素回路1 1 0には、第1データ転送線1 4 - 1及び第2データ転送線1 4 - 2を介して、指定階調に応じた階調電位が供給される。

#### 【0034】

本実施形態においては、一本の第2データ転送線1 4 - 2に対して1個の画素回路1 1 0が電気的に接続される。

但し、本発明はこのような構成に限定されるものではなく、一本の第2データ転送線1 4 - 2に対してNb個の画素回路1 1 0を電気的に接続してもよい。つまり、複数個の画素回路1 1 0が、一本の第2データ転送線1 4 - 2と、一つの転送容量1 3 3と、第1トランジスター1 2 6とを共用するようにしてもよい。

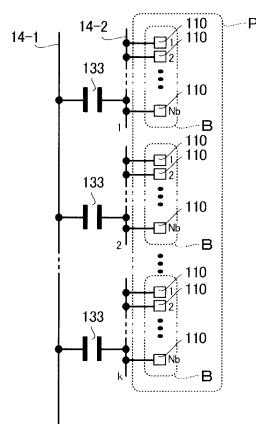

#### 【0035】

図5は、本実施形態に特有の構成を説明する図である。本実施形態では、第1データ転

10

20

30

40

50

送線 14-1 には、図 5 に示すように二以上の第 2 データ転送線 14-2 が、それぞれ転送容量 133 を介して接続される。

ここで、第 2 データ転送線 14-2 と転送容量 133 を介して、同一の第 1 データ転送線 14-1 に接続された画素回路 110 の集合を「画素列」と称する（図 5 における画素列 P）。また、所定数の画素回路 110 の集合を「ブロック」と称する（図 5 におけるブロック B）。

図 5 に示すように、画素列 P は複数のブロック B を含み、各ブロック B は複数の画素回路 110 を含む。つまり、本実施形態においては、第 2 データ転送線 14-2 は、画素列 P に含まれる画素回路 110 の個数と等しい個数の画素回路 110 に対して設けられている。

これに対して、従来の構成は図 6 に示すものである。図 6 は、比較例として示す従来の構成を説明する図である。同図に示すように、従来の構成では、第 2 データ転送線 14-2 が画素列 P に対して設けられ、その端部に転送容量 133 と第 1 データ転送線 14-1 とが設けられている。つまり、従来の構成では、一の画素列 P（に含まれる全ての画素回路 110）に対して、一本の第 1 データ転送線 14-1 と一本の第 2 データ転送線 14-2 とが設けられている。この点が、図 5 を参照して説明した本実施形態に特有の構成、すなわち第 2 データ転送線 14-2 が画素列 P を構成するブロック B 単位で分割されて複数設けられている点と明確に相違する。

#### 【0036】

ところで、下記の（式 1）で示されるように、表示部 100 における画素回路 110 の全行数 M を、一本の第 2 データ転送線 14-2 に接続された画素回路 110 の行数 Nb で除した値を K とする。換言すれば、第 2 データ転送線 14-2 は、M を Nb で除した値である K 本に分割され、1 本の第 2 データ転送線 14-2 には Nb 個の画素回路 110 が接続されてなるとする。

#### 【数 1】

$$K = \frac{M}{Nb} \quad \dots \text{ (式 1)}$$

#### 【0037】

本実施形態では、一本の第 1 データ転送線 14-1 に対して、K (K 2) × Nb 本の第 2 データ転送線 14-2 が設けられている。換言すれば、一の画素列 P は、K 個のブロック B を備える。また、第 1 データ転送線 14-1 は、M 行分 (M 個) の画素回路 110 に対応して設けられ、第 2 データ転送線 14-2 は、Nb 行分 (Nb 個) の画素回路 110 に対応して設けられる。従って、第 2 データ転送線 14-2 は第 1 データ転送線 14-1 と比較して短い。

本実施形態では、Nb の値は 1 である。なお、1 以上 K 以下の任意の整数として、k を用いる。

以降、1 行目から数えて m 番目の行における各画素回路 110 に対応する第 1 トランジスター 126 は、1 行目から数えて m 番目の第 1 トランジスター 126 であるとし、制御信号 G fix(m) が供給されるとする。

#### 【0038】

画素回路 110 は、P チャネル MOS 型のトランジスター 121 ~ 125 と、OLED 130 と、画素容量 132 と、を含む。m 行目の画素回路 110 には、走査信号 G wr(m)、制御信号 G cmp(m)、G el(m)、G orst(m) が供給される。ここで、走査信号 G wr(m)、制御信号 G cmp(m)、G el(m)、G orst(m) は、それぞれ m 行目に対応して走査線駆動回路 6 によって供給されるものである。

#### 【0039】

10

20

30

40

50

なお、図2では図示省略したが、図4に示すように表示パネル2(表示部100)には、横方向(X方向)に延在するM行の制御線143(第1制御線)、横方向に延在するM行の制御線144(第2制御線)、横方向に延在するM行の制御線145(第3制御線)、横方向に延在するK行の制御線146(第4制御線)が設けられる。

#### 【0040】

そして、走査線駆動回路6は、m行目の制御線143に対して制御信号G<sub>cmp(m)</sub>を供給し、m行目の制御線144に対して制御信号G<sub>el(m)</sub>を供給し、m行目の制御線145に対して制御信号G<sub>orst(m)</sub>を供給し、m行目の制御線146に対して制御信号G<sub>fix(m)</sub>を供給する。

すなわち、走査線駆動回路6は、m行目に位置する画素回路に対して、走査信号G<sub>wr(m)</sub>、制御信号G<sub>el(m)</sub>、G<sub>cmp(m)</sub>、G<sub>orst(m)</sub>を、それぞれ、m行目の走査線12、制御線143、144、145を介して供給する。また、m行目に位置する第1トランジスター126に対して制御信号G<sub>fix(m)</sub>を、m行目の制御線146を介して供給する。

10

以下では、走査線12、制御線143、制御線144、制御線145、及び制御線146を、「制御線」と総称する場合がある。すなわち、本実施形態に係る表示パネル2には、各行に走査線12を含む4本の制御線が設けられると共に、1行ごとに1本の制御線146が設けられる。

#### 【0041】

画素容量132、及び転送容量133は、それぞれ2つの電極を有する。転送容量133は、第1電極133-1と第2電極133-2とを含む静電容量である。

20

第2トランジスター122は、ゲートがm行目の走査線12に電気的に接続され、ソース又はドレインの一方が、第2データ転送線14-2に電気的に接続されている。また、第2トランジスター122は、ソースまたはドレインの他方が、駆動トランジスター121のゲートと、画素容量132の一方の電極とに、それぞれ電気的に接続されている。すなわち、第2トランジスター122は、駆動トランジスター121のゲートと転送容量133の第2電極133-2との間に電気的に接続されている。そして、第2トランジスター122は、駆動トランジスター121のゲートと、(3n-2)列目の第2データ転送線14-2に接続された転送容量133の第2電極133-2との間の電気的な接続を制御するトランジスターとして機能する。

#### 【0042】

駆動トランジスター121は、そのソースが給電線116に電気的に接続され、そのドレインは、第3トランジスター123のソースまたはドレインの一方と、第4トランジスター124のソースとに電気的に接続されている。

ここで、給電線116には、画素回路110において電源の高位側となる電位V<sub>el</sub>が給電される。この駆動トランジスター121は、駆動トランジスター121のゲート及びソース間の電圧に応じた電流を流す駆動トランジスターとして機能する。

第3トランジスター123は、ゲートが制御線143に電気的に接続され、制御信号G<sub>cmp(m)</sub>が供給される。この第3トランジスター123は、駆動トランジスター121のゲートとドレインとの間の電気的な接続を制御するスイッチングトランジスターとして機能する。よって、第3トランジスター123は、第2トランジスター122を介して駆動トランジスター121のゲート及びドレインの間を導通させるためのトランジスターである。なお、第3トランジスター123のソース及びドレインの一方と駆動トランジスター121のゲートとの間には第2トランジスター122が接続されているが、第3トランジスター123のソース及びドレインの一方は、駆動トランジスター121のゲートに電気的に接続されているとも解釈され得る。

40

#### 【0043】

第4トランジスター124は、ゲートが制御線144に電気的に接続され、制御信号G<sub>el(m)</sub>が供給される。また、第4トランジスター124は、ドレインが第5トランジスター125のソースとOLED130のアノード130aとにそれぞれ電気的に接続されている。この第4トランジスター124は、駆動トランジスター121のドレインと、OL

50

ED130のアノードとの間の電気的な接続を制御する、スイッチングトランジスターとして機能する。さらに、駆動トランジスター121のドレインとOLED130のアノードとの間には第4トランジスター124が接続されているが、駆動トランジスター121のドレインは、OLED130のアノードに電気的に接続されているとも解釈され得る。

第5トランジスター125は、ゲートが制御線145に電気的に接続され、制御信号G<sub>orst(m)</sub>が供給される。また、第5トランジスター125のドレインは(3n-2)列目の給電線16に電気的に接続されてリセット電位V<sub>orst</sub>に保たれている。この第5トランジスター125は、給電線16と、OLED130のアノード130aとの間の電気的な接続を制御するスイッチングトランジスターとして機能する。

【0044】

10

第1トランジスター126は、ゲートが制御線146に電気的に接続され、制御信号G<sub>fix(k)</sub>が供給される。また、第1トランジスター126は、ソース又はドレインの一方が、第2データ転送線14-2と電気的に接続され、第2データ転送線14-2を介して転送容量133の第2電極133-2及び第3トランジスター123のソース又はドレインの他方に電気的に接続されている。また、第1トランジスター126は、ソース又はドレインの他方が、(3n-2)列目の第1データ転送線14-1と電気的に接続されている。

この第1トランジスター126は、主として、第1データ転送線14-1と第2データ転送線14-2との間の電気的な接続を制御するスイッチングトランジスターとして機能する。

20

ここで、第1トランジスター126及び転送容量133は、同一の第2データ転送線14-2に接続されているNb個の画素回路110によって共用される。本実施形態では、図4に示すように、1本の同一の第2データ転送線14-2には各行目の画素回路110が接続される。

【0045】

30

なお、本実施形態において表示パネル2はシリコン基板に形成されるので、トランジスター121～126の基板電位については電位V<sub>el</sub>としている。また、上記におけるトランジスター121～126のソース、ドレインは、トランジスター121～126のチャネル型、電位の関係に応じて入れ替わってもよい。また、トランジスターは薄膜トランジスターであっても電界効果トランジスターであってもよい。

【0046】

画素容量132は、一方の電極が駆動トランジスター121のゲートgに電気的に接続され、他方の電極が給電線116に電気的に接続される。このため、画素容量132は、駆動トランジスター121のゲート・ソース間の電圧を保持する保持容量として機能する。なお、画素容量132の容量値をC<sub>pix</sub>と表記する。

なお、画素容量132としては、駆動トランジスター121のゲートgに寄生する容量を用いても良いし、シリコン基板において互いに異なる導電層で絶縁層を挟持することによって形成される容量を用いても良い。

【0047】

40

転送容量133は、第1電極133-1が第1データ転送線14-1及びトランスマッシュショングート42を介して保持容量41の一方の電極に電気的に接続される。また、転送容量133は、第2電極133-2が第2データ転送線14-2及び第2トランジスター122を介して駆動トランジスター121のゲートgに電気的に接続される。このため、転送容量133は、後述する補償期間において、ゲートgの電位を、第1データ転送線14-1及び第1電極133-1の電位の変化量に対して、転送容量133と保持容量41との容量比を乗じた値だけレベルシフトさせる転送容量として機能する。詳しくは後述する。なお、転送容量133の容量値をC<sub>1</sub>と表記する。

【0048】

また、本実施形態においては、リセット電位V<sub>orst</sub>が供給される給電線16と、第1データ転送線14-1との間には、シールド容量134が設けられている。転送容量133

50

は、第1電極134-1と第2電極134-2とを含む静電容量である。シールド容量134は、第1データ転送線14-1をシールドするシールド容量として機能する。なお、シールド容量134の容量値をC2と表記する。

【0049】

OLED130のアノード130aは、画素回路110毎に個別に設けられる画素電極である。これに対して、OLED130のカソードは、画素回路110のすべてにわたって共通に設けられる共通電極118であり、画素回路110において電源の低位側となる電位Vctに保たれている。OLED130は、上記シリコン基板において、アノード130aと光透過性を有するカソードとで白色有機EL層を挟持した素子である。そして、OLED130の出射側(カソード側)にはRGBのいずれかに対応したカラーフィルターが重ねられる。なお、白色有機EL層を挟んで配置される2つの反射層間の光学距離を調整してキャビティ構造を形成し、OLED130から発せられる光の波長を設定してもよい。この場合、カラーフィルターを有していてもよいし、有さなくてもよい。

【0050】

このようなOLED130において、アノード130aからカソードに電流が流れる、アノード130aから注入された正孔とカソードから注入された電子とが有機EL層で再結合して励起子が生成され、白色光が発生する。このときに発生した白色光は、シリコン基板(アノード130a)とは反対側のカソードを透過し、カラーフィルターによる着色を経て、観察者側に視認される構成となっている。

【0051】

図7を参照して電気光学装置1の動作について説明する。図7は、電気光学装置1における各部の動作を説明するためのタイミングチャートである。この図に示されるように、走査線駆動回路6は、走査信号Gwr(1)～Gwr(M)を順次Lレベルに切り替えて、1フレームの期間において1～M行目の走査線12を1水平走査期間(H)毎に順番に走査する。

1水平走査期間(H)での動作は、各行の画素回路110にわたって共通である。そこで以下については、m1行目が水平走査される水平走査期間において、特にm1行(3n-2)列の画素回路110について着目して動作を説明する。

【0052】

本実施形態ではm1行目の水平走査期間は、大別すると、図7において(a)で示される初期化期間と、(b)で示される補償期間と、(c)で示される書き込み期間と、(d)で示される非発光期間とに分けられる。また、次の水平走査期間は、(d)で示される非発光期間が継続し、さらに次の水平走査期間は、(e)で示される発光期間となり、1フレームの期間経過後に再びm1行目の水平走査期間に至る。このため、時間の順でいえば、初期化期間 補償期間 書込み期間 非発光期間 発光期間というサイクルの繰り返しとなる。

【0053】

図8は、発光期間における画素回路110などの動作を説明する図である。なお、図8においては、動作説明で重要となる電流経路を太線で示し、オフ状態のトランジスター又はトランスマッショングート上には太線で「X」印を付している(以下の図9、図10、図11、及び図14においても同様である)。

【0054】

<初期化期間>

図7に示されるように、m1行目の初期化期間では、走査信号Gwr(m1)はHレベルであり、制御信号Gel(m1)はHレベルであり、制御信号Gcmp(m1)はHレベルであり、制御信号Gfix(m1)はLレベルである。制御信号Gorst(m1)はLレベルである。

このため、図8に示されるように、m1行(3n-2)列の画素回路110においては第5トランジスター125、第1トランジスター126がオンする一方、駆動トランジスター121、第2トランジスター122、第3トランジスター123、第4トランジスター124がオフする。これにより、OLED130に供給される電流の経路が遮断されるので、OLED130は、オフ(非発光)状態となる。

10

20

30

40

50

## 【0055】

図8に示されるように、第5トランジスタートランジスター125がオンすることにより、OLED130のアノード130aと給電線16とが電気的に接続され、アノード130aの電位がリセット電位V<sub>rst</sub>に設定される

## 【0056】

ここで、初期化期間においてデータ転送回路DTでは、制御信号/G<sub>ini</sub>がLレベルになり、制御信号G<sub>ini</sub>がHレベルになるので図8に示されるようにトランスマッシュゲート45がオンし、制御信号G<sub>cpl</sub>がLレベルになり、制御信号/G<sub>cpl</sub>がHレベルになるので図8に示されるようにトランスマッシュゲート42がオフする。また、制御信号G<sub>fix(k)</sub>はLレベルであるため、第1トランジスター126がオンしている。このため、図8に示されるように転送容量133の第1電極133-1に接続された第1データ転送線14-1が初期電位V<sub>ini</sub>に設定されると共に、第1データ転送線14-1と第2データ転送線14-2とが電気的に接続され、転送容量133の第2電極133-2も初期電位V<sub>ini</sub>に設定される。これにより、転送容量133が初期化される。

## 【0057】

また、初期化期間におけるデマルチプレクサDM(n)では、制御信号Sel(1)がHレベルになり、制御信号/Sel(1)がLレベルになるので、図8に示されるようにトランスマッシュゲート34がオンする。これにより、容量値C<sub>rf</sub>の保持容量41に階調電位が書き込まれる。

## 【0058】

ところで、本実施形態では、m1行(3n-2)列の画素回路110が接続されている第2データ転送線14-2と、m2行(3n-2)列の画素回路110が接続されている第2データ転送線14-2とは別になっている。従って、m1行目の初期化期間には制御信号G<sub>fix(m1)</sub>によって制御される第1トランジスター126が用いられ、図9に示されるようにm2行目の初期化期間には制御信号G<sub>fix(m2)</sub>によって制御される第1トランジスター126が用いられる。

## 【0059】

## &lt;補償期間&gt;

初期化期間を終えると補償期間が開始する。m1行目の補償期間では、走査信号G<sub>wr(m1)</sub>はLレベルであり、制御信号G<sub>el(m1)</sub>はHレベルであり、制御信号G<sub>cmp(m1)</sub>はLレベルであり、制御信号G<sub>fix(m1)</sub>はHレベルである。制御信号G<sub>rst(m1)</sub>はLレベルである。

このため、図10に示されるように、m1行(3n-2)列の画素回路110においては第2トランジスター122、第3トランジスター123、第5トランジスター125がオンする一方、第4トランジスター124、第1トランジスター126がオフする。このとき、駆動トランジスター121のゲートgは、第2トランジスター122と第3トランジスター123とを介して自身のドレインに接続(ダイオード接続)され、駆動トランジスター121にはドレイン電流が流れゲートgを充電する。

すなわち、駆動トランジスター121のドレインとゲートgとは、第2データ転送線14-2に接続され、駆動トランジスター121の閾値電圧をV<sub>th</sub>とすると、駆動トランジスター121のゲートgの電位V<sub>g</sub>は、(V<sub>el</sub> - V<sub>th</sub>)に漸近していく。

## 【0060】

ここで、補償期間のデータ転送回路DTにおいては、制御信号/G<sub>ini</sub>がLレベルになり、制御信号G<sub>ini</sub>がHレベルになるので、図10に示されるようにトランスマッシュゲート45がオンし、制御信号G<sub>cpl</sub>がLレベルになり、制御信号/G<sub>cpl</sub>がHレベルになるので、トランスマッシュゲート42がオフする。このとき、上述したように従来の構成と比較して第2データ転送線14-2が短いため、第2データ転送線14-2に付随する寄生容量への充電又は放電に要する時間が短縮され、補償期間自体が短縮される。

## 【0061】

また、補償期間におけるデマルチプレクサDM(n)では、制御信号Sel(1)がHレベル

10

20

30

40

50

ルになり、制御信号 / Sel(1)が L レベルになるので、図 10 に示されるようにトランスマッショングート 3 4 がオンする。これにより、容量値 Crf の保持容量 4 1 に階調電位が書き込まれる。

#### 【 0 0 6 2 】

なお、第 4 トランジスター 1 2 4 はオフしているため、駆動トランジスター 1 2 1 のドレインは O LED 1 3 0 と電気的に非接続である。また、初期化期間と同様、第 5 トランジスター 1 2 5 がオンすることによって、O LED 1 3 0 のアノード 1 3 0 a と給電線 1 6 とが電気的に接続され、アノード 1 3 0 a の電位がリセット電位 Vorst に設定される。

#### 【 0 0 6 3 】

< 書込期間 > 10

補償期間を終えると、書込期間が開始する。m 1 行目の書込期間では、走査信号 Gwr(m 1) が L レベルであり、制御信号 Gel(m1) は H レベルであり、制御信号 G cmp(m1) は H レベルであり、制御信号 G fix(m1) は H レベルである。制御信号 Gorst(m1) は L レベルである。

このため、図 11 に示されるように、m 1 行 ( 3 n - 2 ) 列の画素回路 1 1 0 においてはトランジスター 1 2 2 、 1 2 5 がオンする一方、トランジスター 1 2 3 、 1 2 4 、 1 2 6 がオフする。

#### 【 0 0 6 4 】

ここで、書込期間のデータ転送回路 D T においては、制御信号 / Gini が H レベルになるので、図 11 に示されるようにトランスマッショングート 4 5 がオフし、制御信号 Gcp 1 が H レベルになるので、図 11 に示されるようにトランスマッショングート 4 2 がオンする。このため、第 1 データ転送線 1 4 - 1 及び第 1 電極 1 3 3 - 1 への初期電位 Vini の供給が解除されると共に、第 1 データ転送線 1 4 - 1 及び第 1 電極 1 3 3 - 1 に対して容量値 Crf の保持容量 4 1 の一方の電極が接続され、当該第 1 電極 1 3 3 - 1 に階調電位が供給される。そして、階調電位がレベルシフトされた信号が、駆動トランジスター 1 2 1 のゲートに供給され、画素容量 1 3 2 に書き込まれる。このように、本実施形態においては、データ転送回路 D T のトランスマッショングート 4 2 および保持容量 4 1 、並びに転送容量 1 3 3 を用いて階調電位のレベルシフトが行われる。

なお、書込期間におけるデマルチプレクサ DM ( n ) では、制御信号 Sel(1) が L レベルになるので、図 11 に示されるようにトランスマッショングート 3 4 がオフする。 30

#### 【 0 0 6 5 】

なお、第 4 トランジスター 1 2 4 はオフしているため、駆動トランジスター 1 2 1 のドレインは O LED 1 3 0 と電気的に非接続である。また、初期化期間と同様、第 5 トランジスター 1 2 5 がオンすることによって、O LED 1 3 0 のアノード 1 3 0 a と給電線 1 6 とが電気的に接続され、アノード 1 3 0 a の電位がリセット電位 Vorst に初期化される。

#### 【 0 0 6 6 】

なお、m 行目の書込期間が開始されるまで（初期化期間、補償期間の間）に、制御回路 3 は、n 番目のグループといえば、データ信号 Vd(n) を順番に、m 行 ( 3 n - 2 ) 列、m 行 ( 3 n - 1 ) 列、m 行 ( 3 n ) 列の画素の階調レベルに応じた電位に切り替える。 40

一方、制御回路 3 は、データ信号の電位の切り替えに合わせて制御信号 Sel(1) 、 Sel(2) 、 Sel(3) を順番に排他的に H レベルとする。制御回路 3 は、図示は省略しているが、制御信号 Sel(1) 、 Sel(2) 、 Sel(3) とは論理反転の関係にある制御信号 / Sel(1) 、 / Sel(2) 、 / Sel(3) についても出力している。これによって、デマルチプレクサ DM では、各グループにおいてトランスマッショングート 3 4 がそれぞれ左端列、中央列、右端列の順番でオンする。

#### 【 0 0 6 7 】

ところで、左端列のトランスマッショングート 3 4 が制御信号 Sel(1) 、 / Sel(1) によってオンしたとき、第 1 データ転送線 1 4 - 1 及び第 1 電極 1 3 3 - 1 の電位の変化量を V とすると、第 2 データ転送線 1 4 - 2 及び駆動トランジスター 1 2 1 のゲート g の電 50

位の変化量  $V_g$  は、下記（式2）で表せる。但し、転送容量 133 の容量値  $C_1$  は画素回路 110 の行数に比例して容量値を調整可能であり、1行当たりの容量  $C_1a$  とする。また、1行当たりの第2データ転送線 14-2 に付随する寄生容量の容量値を  $C_3a$  とする。また、上述したように、一本の第2データ転送線 14-2 に接続された画素回路 110 の行数を  $Nb$  と表す。

【数2】

$$\Delta V_g = \frac{Nb \cdot C_1a}{Nb \cdot C_1a + Nb \cdot C_3a + C_{pix}} \Delta V \cdots \text{(式2)}$$

10

ここで  $V$  と  $V_g$  の比を、下記の（式3）で示すように圧縮率  $R$  とする。

【数3】

$$R = \frac{Nb \cdot C_1a}{Nb \cdot C_1a + Nb \cdot C_3a + C_{pix}} \cdots \text{(式3)}$$

20

つまり、書込期間における駆動トランジスター 121 のゲート  $g$  の電位  $V_g$  は、補償期間における電位  $V_g$  から、第1データ転送線 14-1 及び第1電極 133-1 の電位の変化量  $V$  に対して、 $R$  を乗じた値だけレベルシフトした（データ圧縮された）値となる。この書込期間を終えると、後述する発光期間が開始する。

【0068】

上述した（式2）に示される関係から、一本の第2データ転送線 14-2 に対して接続する画素回路 110 の個数  $Nb$  が多いほど（1 ブロック内に含まれる画素回路 110 の個数  $Nb$  が多いほど）、 $V_g$  と  $V$  とは近い値になる。換言すれば、 $Nb$  の値が大きいほど、（式4）に示す  $R$  は 1 に近づく。

30

ここで、第2データ転送線 14-2 に接続する画素回路 110 の個数  $Nb$ （1 ブロック内に含まれる画素回路 110 の個数  $Nb$ ）は、補償動作の完了に要する時間と、データ圧縮の圧縮率と、を鑑みて決定することが好ましい。以下、具体的に説明する。

まず、補償動作の完了に要する時間について説明する。補償期間を終えた時点の駆動トランジスター 121 のゲート  $g$  の電位  $V_g$ （補償点）が、階調電圧の中間階調に設定されていることが好ましいところ、 $Nb$  の値が小さいほど、駆動トランジスター 121 のゲート  $g$  に付随する寄生容量が小さくなるため、補償時間が極端に短くなってしまい、結果として走査信号  $G_{wr}(m)$  の立上がり（立下り）におけるなまりの影響を受けて、走査信号  $G_w(m)$  を供給する側と供給される側とで補償時間が異なってしまう虞がある。この場合、当該虞をなくす程度に駆動能力の高い走査線駆動回路 6 が必要となってしまう。

40

また、データ圧縮の圧縮率については、（式2）に示されるように、 $Nb$  の値が小さいほど圧縮率が大きくなり、逆に  $Nb$  の値が大きいほど圧縮率は小さくなる。

従って、補償動作の完了に要する時間と、データ圧縮の圧縮率とを鑑みて、 $Nb$  の値を適切な値に決定することが好ましい。例えば全行数  $M$  が 720 行の場合、 $Nb$  を 90 個とし、総ブロック数  $K$  を 8 個としてもよい。

【0069】

<非発光期間>

図7のタイミングチャートに示されるように、走査信号  $G_{wr}(m1)$  が L レベルから H レベルに立ち上がり、書込期間を終えると、1 水平走査期間（H）の残りの期間及び次の 1 水

50

平走査期間 (H) は、非発光期間となる。非発光期間においては、全てのトランジスターがオフとなり、制御信号 Gorst(m1) は L レベルである。

【0070】

<発光期間>

非発光期間を終えると、発光期間が開始する。図 7 のタイミングチャートに示されるように、m1 行目の発光期間では、走査信号 Gwr(m1) が H レベルであり、制御信号 Gel(m1) は L レベルであり、制御信号 Gcmp(m1) は H レベルであり、制御信号 Gfix(k) は H レベルである。制御信号 Gorst(m1) は H レベルである。

このため、図 12 に示されるように m1 行 (3n - 2) 列の画素回路 110 においては、第 4 トランジスター 124 がオンする一方、第 2 トランジスター 122、第 3 トランジスター 123、第 5 トランジスター 125、第 1 トランジスター 126 がオフする。これにより、駆動トランジスター 121 は、画素容量 132 によって保持された電圧、すなわちゲート・ソース間の電圧 Vgs に応じた駆動電流 Ids を、OLED130 に供給する。つまり、OLED130 は、駆動トランジスター 121 によって各画素の指定階調に応じた階調電位に応じた電流が供給され、当該電流に応じた輝度で発光する。

【0071】

ここで、発光期間においてデータ転送回路 DT では、制御信号 /Gini が H レベルになり、制御信号 Gini が L レベルになるので図 12 に示されるようにトランスマッシュゲート 45 がオフし、制御信号 Gcp1 が L レベルになり、制御信号 /Gcp1 が H レベルになるので、トランスマッシュゲート 42 がオフする。また、発光期間におけるデマルチプレクサ DM(n) では、制御信号 Sel(1) が L レベルになり、制御信号 /Sel(1) が H レベルになるので、トランスマッシュゲート 34 がオフする。

【0072】

なお、m1 行目の発光期間は、m1 行目以外が水平走査されている期間であるから、トランスマッシュゲート 34、トランスマッシュゲート 42、トランスマッシュゲート 45 はこれらの行の動作に合わせてオン又はオフするので、第 1 データ転送線 14-1 及び第 2 データ転送線 14-2 の電位は適宜変動する。特に、第 1 トランジスター 126、第 2 トランジスター 122、及び第 3 トランジスター 123 がオフの場合には、第 2 データ転送線 14-2 は、フローティングの状態となり、電位が変動し易い。

【0073】

そこで、本実施形態においては、一つのブロック B における発光期間に、第 1 トランジスター 126 をオンさせることにより、第 1 データ転送線 14-1 と第 2 データ転送線 14-2 を導通状態にして、第 2 データ転送線 14-2 に初期電位 Vini を供給する期間を設ける。

m1 行目や m2 行目等の画素回路 110 が属するブロックをブロック B(m) とすると、ブロック B(m) の次のブロックであるブロック B(n) における初期化期間は、ブロック B(m) においては発光期間である。本実施形態では、例えば、前記ブロック B(m) の次のブロック (n) を一のブロックとし、前記ブロック B(m) を他のブロックとすると、一のブロックであるブロック B(n) における初期化期間であって、他のブロックであるブロック B(m) における発光期間に、第 1 トランジスター 126 をオンさせて第 1 データ転送線 14-1 と第 2 データ転送線 14-2 を導通状態にして、第 2 データ転送線 14-2 に初期電位 Vini を供給する。

【0074】

図 13 に示されるように、時刻 t1 から時刻 t4 までの期間では、ブロック B(m) において初期化期間、補償期間、書き期間の処理が実行される。

時刻 t5 から時刻 t6 では、ブロック B(m) の次のブロックであるブロック B(n) において初期化期間の処理が実行されるが、この期間はブロック B(m) においては発光期間である。しかし、本実施形態においては、ブロック B(n) において初期化期間の処理が実行される際に、ブロック B(m) を始めとして他のブロック B において、制御信号 Gfix を L レベルにする。その結果、図 14 に示すように、第 1 トランジスター 126 が

10

20

30

40

50

オンし、ブロック B ( m ) を始めとして他のブロック B において、第 1 データ転送線 14 - 1 と第 2 データ転送線 14 - 2 とが導通状態となって、第 2 データ転送線 14 - 2 に初期電位  $V_{ini}$  が供給されることになる。

【 0 0 7 5 】

以下、同様にして、ブロック B ( n ) において初期化期間の処理が実行される時刻  $t_8$  から時刻  $t_9$  までの期間、時刻  $t_{11}$  から時刻  $t_{12}$  までの期間、及び時刻  $t_{14}$  から時刻  $t_{15}$  までの期間では、ブロック B ( m ) を始めとして他のブロック B において、制御信号  $G_{fix}$  を L レベルにする。その結果、図 14 に示すように、第 1 トランジスター 12 6 がオンし、ブロック B ( m ) を始めとして他のブロック B において、第 1 データ転送線 14 - 1 と第 2 データ転送線 14 - 2 とが導通状態となって、第 2 データ転送線 14 - 2 に初期電位  $V_{ini}$  が供給されることになる。

10

【 0 0 7 6 】

以上のように、本実施形態によれば、発光期間中にフローティングノードになる第 2 トランジスター 12 2 の転送容量 13 3 側の第 2 データ転送線 14 - 2 を、他のブロックで初期化期間の処理が行われる期間において固定電位の初期電位  $V_{ini}$  に設定するので、第 2 データ転送線 14 - 2 の電位が電源電圧に近づくことを抑えることができる。その結果、第 2 トランジスター 12 2 がオンすることなく、画素容量 13 2 において電圧が保持され、表示の不具合を発生させることがない。

【 0 0 7 7 】

< 構造 >

20

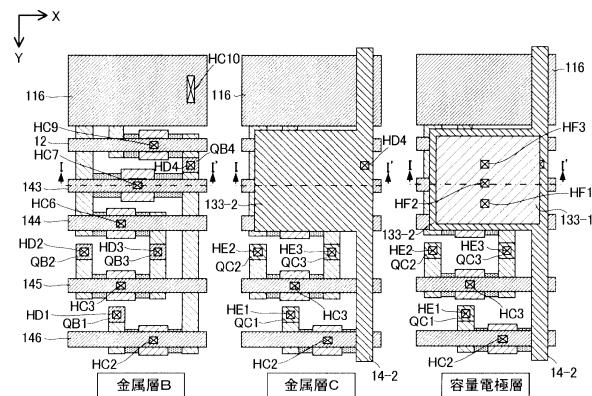

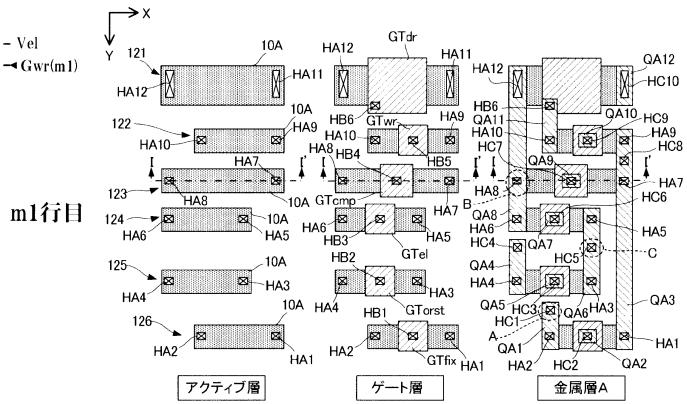

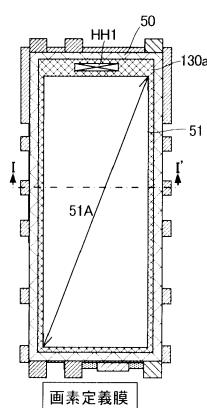

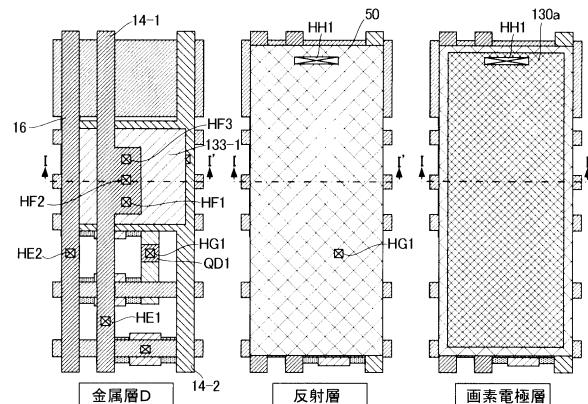

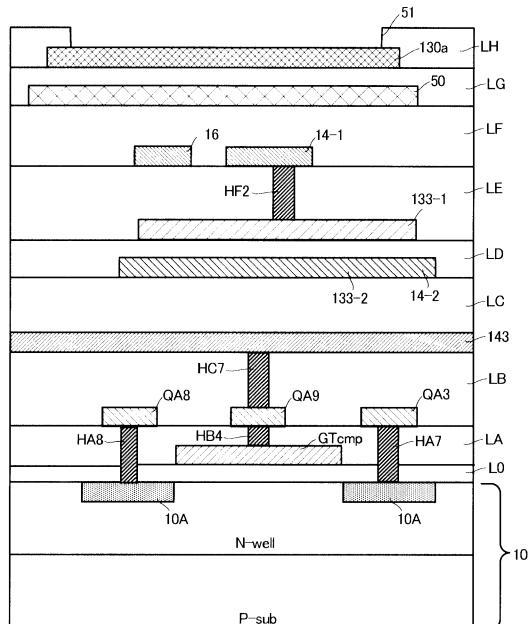

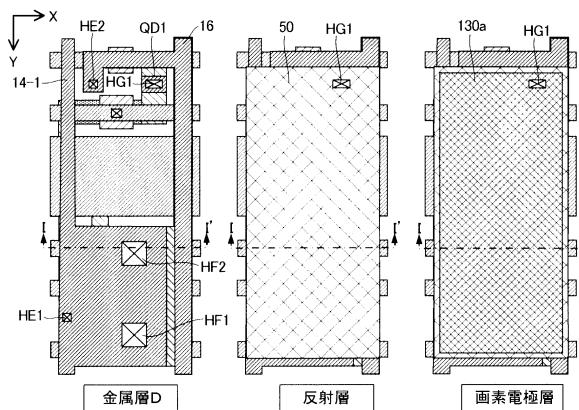

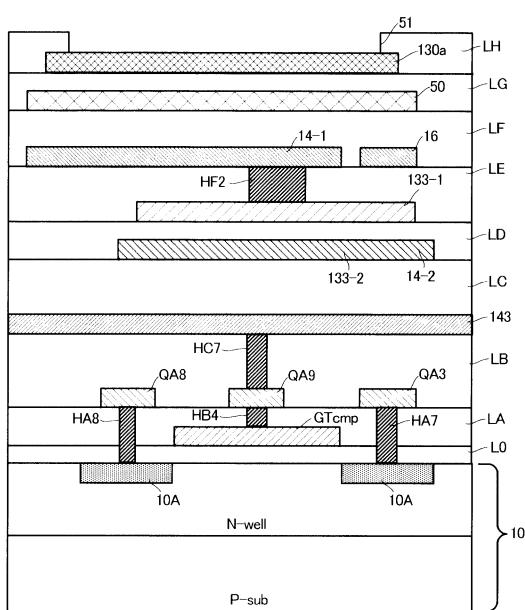

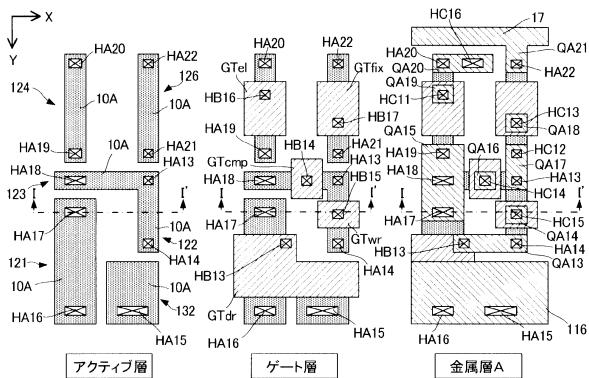

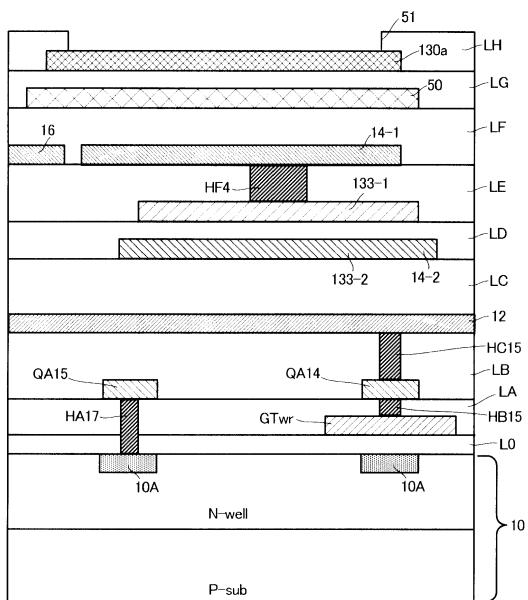

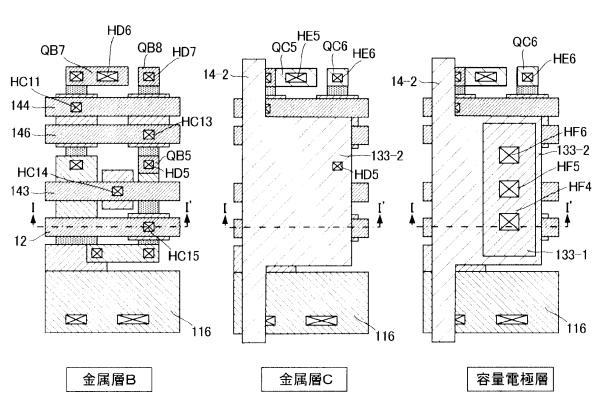

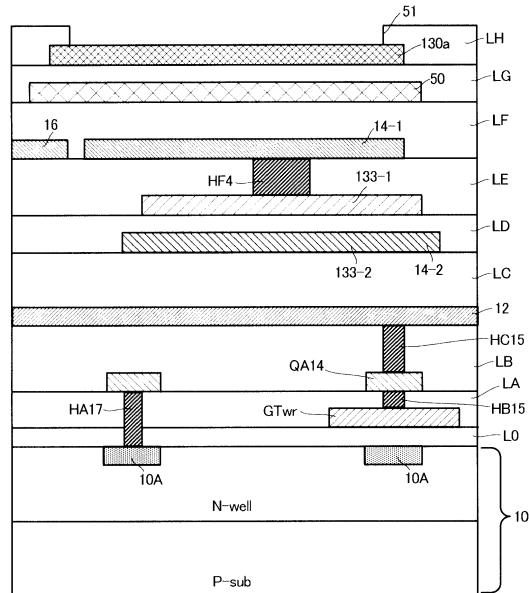

次に、本実施形態における電気光学装置 1 の具体的な構造を以下に詳述する。なお、以下の説明で参照する各図面では、説明の便宜のために、各要素の寸法や縮尺を実際の電気光学装置 1 とは相違させている。図 15 及び図 16 は、電気光学装置 1 の各要素を形成する各段階での基板 10 の表面の様子を画素回路 110 の 1 個分に着目して図示した平面図である。図 17 は、電気光学装置 1 の断面図である。図 15 及び図 16 の I - I' 線を含む断面に対応した断面図が図 17 に相当する。なお、図 15 及び図 16 の平面図であるが、各要素の視覚的な把握を容易化する観点から、図 17 と共に各要素に図 17 と同様のハッチングが便宜的に付加されている。

【 0 0 7 8 】

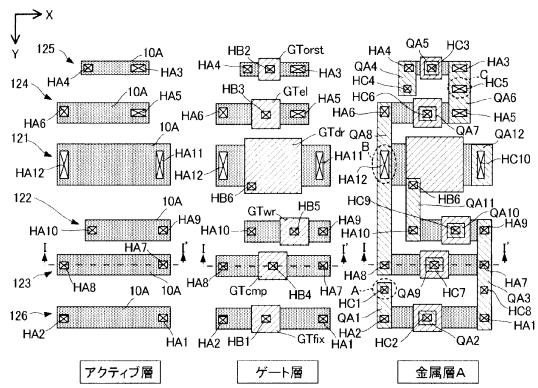

図 15 のアクティブ層を示す部分及び図 17 から理解される通り、珪素等の半導体材料で形成された基板 10 の表面には、画素回路 110 の各トランジスター 12 1, 12 2, 12 3, 12 4, 12 5, 12 6 の能動領域 10 A ( ソース / ドレイン領域 ) が形成される。能動領域 10 A にはイオンが注入される。画素回路 110 の各トランジスター 12 1, 12 2, 12 3, 12 4, 12 5, 12 6 のアクティブ層はソース領域とドレイン領域との間に存在し、能動領域 10 A とは別種類のイオンが注入されるが、便宜的に能動領域 10 A と一体に記載している。

30

図 15 のゲート層を示す部分及び図 17 から理解される通り、能動領域 10 A が形成された基板 10 の表面は絶縁膜 L 0 ( ゲート絶縁膜 ) で被覆され、各トランジスター 12 1, 12 2, 12 3, 12 4, 12 5, 12 6 のゲート層 G T ( G Tdr, G Twr, G Tcmp, G Tel, G Torst, G Tf fix ) が絶縁膜 L 0 の面上に形成される。各トランジスター 12 1, 12 2, 12 3, 12 4, 12 5, 12 6 のゲート層 G T は、絶縁膜 L 0 を挟んでアクティブ層に対向する。

40

【 0 0 7 9 】

図 17 から理解される通り、各トランジスター 12 1, 12 2, 12 3, 12 4, 12 5, 12 6 のゲート層 G T が形成された絶縁膜 L 0 の面上には、複数の絶縁層 L ( L A ~ L H ) と複数の導電層 ( 配線層 ) とを交互に積層した多層配線層が形成される。各絶縁層 L は、例えば珪素化合物 ( 典型的には窒化珪素や酸化珪素 ) 等の絶縁性の無機材料で形成される。なお、以下の説明では、導電層 ( 単層または複数層 ) の選択的な除去により複数の要素が同一工程で一括的に形成される関係を「同層から形成される」と表記する。

【 0 0 8 0 】

10

20

30

40

50

絶縁層 L A は、各トランジスター 121, 122, 123, 124, 125, 126 のゲート層 G T が形成された絶縁膜 L 0 の面上に形成される。図 15 の金属層 A を示す部分及び図 17 から理解される通り、絶縁層 L A の面上には、複数の中継電極 Q A ( Q A 1 ~ Q 12 ) が形成される。

【0081】

図 15 の金属層 A を示す部分及び図 17 から理解される通り、中継電極 Q A 1 は、絶縁膜 L 0 と絶縁層 L A とを貫通する導通孔 H A 2 を介して第 1 トランジスター 126 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。中継電極 Q A 2 は、絶縁層 L A を貫通する導通孔 H B 1 を介して第 1 トランジスター 126 のゲート層 G T fix に導通する。中継電極 Q A 3 は、絶縁膜 L 0 と絶縁層 L A とを貫通する導通孔 H A 1 を介して第 1 トランジスター 126 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。また、中継電極 Q A 3 は、絶縁膜 L 0 と絶縁層 L A とを貫通する導通孔 H A 7 を介して第 3 トランジスター 123 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。さらに、中継電極 Q A 3 は、絶縁膜 L 0 と絶縁層 L A とを貫通する導通孔 H A 9 を介して第 2 トランジスター 122 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。以上のように、中継電極 Q A 3 はソース電極であり、第 1 トランジスター 126 のドレイン領域またはソース領域を形成する能動領域 10 A 、第 3 トランジスター 123 のドレイン領域またはソース領域を形成する能動領域 10 A 、及び第 2 トランジスター 122 のドレイン領域またはソース領域を形成する能動領域 10 A に直接接して形成される電極である。

【0082】

中継電極 Q A 4 は、絶縁膜 L 0 と絶縁層 L A とを貫通する導通孔 H A 4 を介して第 5 トランジスター 125 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。中継電極 Q A 5 は、絶縁層 L A を貫通する導通孔 H B 2 を介して第 5 トランジスター 125 のゲート層 G T orst に導通する。中継電極 Q A 6 は、絶縁層 L A と絶縁膜 L 0 とを貫通する導通孔 H A 3 を介して第 5 トランジスター 125 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。

【0083】

また、中継電極 Q A 6 は、絶縁層 L A と絶縁膜 L 0 とを貫通する導通孔 H A 5 を介して第 4 トランジスター 124 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。中継電極 Q A 7 は、絶縁層 L A を貫通する導通孔 H B 3 を介して第 4 トランジスター 124 のゲート層 G T el に導通する。中継電極 Q A 8 は、絶縁層 L A と絶縁膜 L 0 とを貫通する導通孔 H A 6 を介して第 4 トランジスター 124 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。また、中継電極 Q A 8 は、絶縁層 L A と絶縁膜 L 0 とを貫通する導通孔 H A 8 を介して第 3 トランジスター 123 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。さらに、中継電極 Q A 8 は、絶縁層 L A と絶縁膜 L 0 とを貫通する導通孔 H A 12 を介して駆動トランジスター 121 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。以上のように、中継電極 Q A 6 はソース電極であり、第 4 トランジスター 124 のドレイン領域またはソース領域を形成する能動領域 10 A に直接接して形成される電極である。また、中継電極 Q A 8 もソース電極であり、第 4 トランジスター 124 のドレイン領域またはソース領域を形成する能動領域 10 A 、第 3 トランジスター 123 のドレイン領域またはソース領域を形成する能動領域 10 A 、及び駆動トランジスター 121 のドレイン領域またはソース領域を形成する能動領域 10 A に直接接して形成される電極である。

【0084】

中継電極 Q A 9 は、絶縁層 L A を貫通する導通孔 H B 4 を介して第 3 トランジスター 123 のゲート層 G T cmp に導通する。中継電極 Q A 10 は、絶縁層 L A を貫通する導通孔 H B 5 を介して第 2 トランジスター 122 のゲート層 G T wr に導通する。中継電極 Q A 11 は、絶縁層 L A と絶縁膜 L 0 とを貫通する導通孔 H A 10 を介して第 2 トランジスター 122 のドレイン領域またはソース領域を形成する能動領域 10 A に導通する。また、中

10

20

30

40

50

継電極 Q A 1 1 は、絶縁層 L A を貫通する導通孔 H B 6 を介して駆動トランジスター 1 2 1 のゲート層 G T dr に導通する。中継電極 Q A 1 2 は、絶縁層 L A と絶縁膜 L 0 とを貫通する導通孔 H A 1 1 を介して駆動トランジスター 1 2 1 のドレイン領域またはソース領域を形成する能動領域 1 0 A に導通する。

【 0 0 8 5 】

絶縁層 L B は、複数の中継電極 Q A ( Q A 1 , Q A 2 , Q A 3 , Q A 4 , Q A 5 , Q A 6 , Q A 7 , Q A 8 , Q A 9 , Q A 1 0 , Q A 1 1 , Q A 1 2 ) が形成された絶縁層 L A の面上に形成される。図 1 5 の金属層 B を示す部分及び図 1 7 から理解される通り、絶縁層 L B の面上には、走査線 1 2 、給電線 1 1 6 、複数の制御線 1 4 3 ~ 1 4 6 、及び複数の中継電極 Q B ( Q B 1 , Q B 2 , Q B 3 , Q B 4 ) が形成される。 10

図 1 5 の金属層 B を示す部分及び図 1 7 から理解される通り、第 1 の導電線の一例としての走査線 1 2 は、絶縁層 L B を貫通する導通孔 H C 9 を介して第 2 トランジスター 1 2 2 のゲート層 G T wr に導通する。走査線 1 2 は、複数の画素回路 1 1 0 にわたり第 2 トランジスター 1 2 2 のチャネル長の方向 ( X 方向 ) に沿って延在する。

【 0 0 8 6 】

給電線 1 1 6 は、多層配線層内の配線 ( 図示略 ) を介して、高位側の電源電位 V e 1 が供給される実装端子に導通する。給電線 1 1 6 は、例えば銀やアルミニウムを含有する導電材料で例えば 1 0 0 nm 程度の膜厚に形成される。給電線 1 1 6 は、絶縁層 L B を貫通する導通孔 H C 1 0 を介して駆動トランジスター 1 2 1 のドレイン領域またはソース領域を形成する能動領域 1 0 A に導通する。給電線 1 1 6 は、複数の画素回路 1 1 0 にわたり駆動トランジスター 1 2 1 のチャネル長の方向 ( X 方向 ) に沿って延在する。給電線 1 1 6 は、絶縁層 L C により、後述する転送容量 1 3 3 の第 2 電極 1 3 3 - 2 からは電気的に絶縁される。 20

制御線 1 4 3 は、図 1 5 の金属層 B を示す部分及び図 1 7 から理解される通り、絶縁層 L B を貫通する導通孔 H C 7 と、中継電極 Q A 9 と、絶縁層 L A を貫通する H B 4 とを介して第 3 トランジスター 1 2 3 のゲート層 G T cmp に導通する。また、制御線 1 4 3 は、第 3 トランジスター 1 2 3 のチャネル長の方向 ( X 方向 ) に沿って延在する。

【 0 0 8 7 】

制御線 1 4 4 は、図 1 5 の金属層 B を示す部分及び図 1 7 から理解される通り、絶縁層 L B を貫通する導通孔 H C 6 と、中継電極 Q A 7 と、絶縁層 L A を貫通する H B 3 とを介して第 4 トランジスター 1 2 4 のゲート層 G T el に導通する。また、制御線 1 4 4 は、第 4 トランジスター 1 2 4 のチャネル長の方向 ( X 方向 ) に沿って延在する。 30

制御線 1 4 5 は、絶縁層 L B を貫通する導通孔 H C 3 と、中継電極 Q A 5 と、絶縁層 L A を貫通する H B 2 とを介して第 5 トランジスター 1 2 5 のゲート層 G T orst に導通する。また、制御線 1 4 5 は、第 5 トランジスター 1 2 5 のチャネル長の方向 ( X 方向 ) に沿って延在する。

制御線 1 4 6 は、絶縁層 L B を貫通する導通孔 H C 2 と、中継電極 Q A 2 と、絶縁層 L A を貫通する H B 1 とを介して第 1 トランジスター 1 2 6 のゲート層 G T fix に導通する。また、制御線 1 4 6 は、第 1 トランジスター 1 2 6 のチャネル長の方向 ( X 方向 ) に沿って延在する。 40

【 0 0 8 8 】

中継電極 Q B 1 は、図 1 5 の金属層 B 及び金属層 A の部分から理解される通り、絶縁層 L B を貫通する導通孔 H C 1 を介して中継電極 Q A 1 に導通される。中継電極 Q B 2 は、絶縁層 L B を貫通する導通孔 H C 4 を介して中継電極 Q A 4 に導通される。中継電極 Q B 3 は、絶縁層 L B を貫通する導通孔 H C 5 を介して中継電極 Q A 6 に導通される。中継電極 Q B 4 は、絶縁層 L B を貫通する導通孔 H C 8 を介して中継電極 Q A 3 に導通される。

【 0 0 8 9 】

絶縁層 L C は、走査線 1 2 と、複数の制御線 1 4 3 ~ 1 4 6 と、複数の中継電極 Q B ( Q B 1 , Q B 2 , Q B 3 , Q B 4 ) とが形成された絶縁層 L B の面上に形成される。図 1 5 の金属層 C の部分及び図 1 7 から理解される通り、絶縁層 L C の面上には、第 2 データ 50

転送線 14-2 と、転送容量 133 の第 2 電極 133-2 と、複数の中継電極 QC (QC1, QC2, QC3) とが形成される。

第 3 の導電層の一例としての第 2 データ転送線 14-2 は、複数の画素回路 110 にわたり Y 方向に沿って延在する。第 2 データ転送線 14-2 は、絶縁層 LC を貫通する導通孔 HD4 と、中継電極 QB4 と、絶縁層 LB を貫通する導通孔 HC8 と、中継電極 QA3 とを介して、第 2 トランジスター 122 のドレイン領域またはソース領域を形成する能動領域 10A に導通される。また、第 2 データ転送線 14-2 は、第 3 トランジスター 123 のドレイン領域またはソース領域を形成する能動領域 10A と、第 1 トランジスター 126 のドレイン領域またはソース領域を形成する能動領域 10A とに導通される。

転送容量 (第 1 容量) 133 の第 5 の導電層の一例としての第 2 電極 133-2 は、画素回路 110 において、走査線 12、制御線 143、及び制御線 144 を覆う矩形の電極であり、第 2 データ転送線 14-2 と一体に形成される。

#### 【0090】

図 15 及び図 17 から理解される通り、中継電極 QC1 は、絶縁層 LC を貫通する導通孔 HD1 を介して中継電極 QB1 に導通される。中継電極 QC2 は、絶縁層 LC を貫通する導通孔 HD2 を介して中継電極 QB2 に導通される。中継電極 QC3 は、絶縁層 LC を貫通する導通孔 HD3 を介して中継電極 QB3 に導通される。

#### 【0091】

絶縁層 LD は、第 2 データ転送線 14-2 と、転送容量 133 の第 2 電極 133-2 と、複数の中継電極 QC (QC1, QC2, QC3) とが形成された絶縁層 LC の面上に形成される。図 15 の容量電極層の部分及び図 17 から理解される通り、絶縁層 LD の面上には、転送容量 133 の第 1 電極 133-1 が形成される。

転送容量 (第 1 容量) 133 の第 4 の導電層の一例としての第 1 電極 133-1 は、絶縁層 LD を介して第 2 電極 133-2 と対向する矩形の容量電極である。第 1 電極 133-1 は、絶縁層 LD を介して第 2 電極 133-2 と対向する。このように、転送容量 133 は、金属である第 1 電極 133-1 と、絶縁層 LD と、金属である第 2 電極 133-2 とから構成され、MIM (Metal-Insulator-Metal) 構造を有している。したがって、転送容量 133 は、大容量化が容易である。また、転送容量 133 は、画素回路 110 の表示領域内に形成されるので、電気光学装置の小型化を図ることができる。

#### 【0092】

絶縁層 LE は、転送容量 133 の第 1 電極 133-1 が形成された絶縁層 LD の面上に形成される。図 16 の金属層 D の部分及び図 17 から理解される通り、絶縁層 LE の面上には、第 1 データ転送線 14-1 と、給電線 16 と、中継電極 QD1 が形成される。

第 2 の導電層の一例としての第 1 データ転送線 14-1 は、複数の画素回路 110 にわたり Y 方向に沿って延在する。第 1 データ転送線 14-1 は、絶縁層 LE を貫通する導通孔 HF1, HF2, HF3 を介して、転送容量 133 の第 1 電極 133-1 に導通される。また、第 1 データ転送線 14-1 は、絶縁層 LE 及び絶縁層 LD を貫通する導通孔 HE1 と、中継電極 QC1 と、絶縁層 LC を貫通する導通孔 HD1 と、中継電極 QB1 と、絶縁層 LB を貫通する導通孔 HC1 と、中継電極 QA1 と、絶縁層 LA 及び絶縁膜 L0 を貫通する導通孔 HA2 とを介して、第 1 トランジスター 126 のドレイン領域またはソース領域を形成する能動領域 10A とに導通される。

#### 【0093】

第 6 の導電層としての給電線 16 は、複数の画素回路 110 にわたり Y 方向に沿って延在する。給電線 16 は、絶縁層 LE 及び絶縁層 LD を貫通する導通孔 HE2 と、中継電極 QC2 と、絶縁層 LC を貫通する導通孔 HD2 と、中継電極 QB2 と、絶縁層 LB を貫通する導通孔 HC4 と、中継電極 QA4 と、絶縁層 LA 及び絶縁膜 L0 を貫通する導通孔 HA4 とを介して、第 5 トランジスター 125 のドレイン領域またはソース領域を形成する能動領域 10A とに導通される。中継電極 QD1 は、絶縁層 LE を貫通する導通孔 HE3 を介して、中継電極 QC3 に導通される。

また、給電線 16 は、第 1 データ転送線 14-1 と同層に形成され、絶縁層 LF を介し

10

20

30

40

50

て、第1データ転送線14-1との間に所定の間隙を有して配置される。このようにしてシールド容量(第2容量)134が形成され、第1データ転送線14-1はシールド線としての給電線16によってシールドされることになる。

#### 【0094】

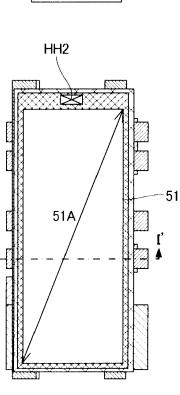

絶縁層LFは、第1データ転送14-1と、給電線16と、中継電極QD1とが形成された絶縁層LEの面上に形成される。図16の反射層の部分及び図17から理解される通り、絶縁層LFの面上には、反射層50が形成される。反射層50は、画素回路110毎に個別に形成されている。反射層50は、例えば銀やアルミニウムを含有する光反射性の導電材料で例えば100nm程度の膜厚に形成される。図16の反射層の部分及び図17から理解されるように、反射層50は、絶縁層LFを貫通する導通孔HG1を介して中継電極QD1に導通する。中継電極QD1は、導通孔HE3、中継電極QC3、導通孔HD3、中継電極QB3、導通孔HC5、中継電極QA6、導通孔HA5、及び導通孔HA3を介して、第4トランジスター124のドレイン領域またはソース領域、及び第5トランジスター124のドレイン領域またはソース領域と導通される。

#### 【0095】

反射層50が形成された絶縁層LFの面上には、図17に示される通り、光路調整層LGが形成される。光路調整層LGは、各画素回路110の共振構造の共振波長(すなわち表示色)を規定する光透過性の膜体である。表示色が同じ画素では、共振構造の共振波長は略同じであり、表示色が異なる画素では、共振構造の共振波長は異なるように設定される。

10

#### 【0096】

図16の画素電極層の部分及び図17に示される通り、光路調整層LGの面上には、画素回路110毎のアノード130aが形成される。アノード130aは、例えばITO(Indium Tin Oxide)等の光透過性の導電材料で形成される。アノード130aは、光路調整層LGを貫通する導通孔HH1を介して、反射層50と導通する。したがって、アノード130aは、反射層50を介して第4トランジスター124のドレイン領域またはソース領域、及び第5トランジスター124のドレイン領域またはソース領域と導通する。

#### 【0097】

アノード130aが形成された光路調整層LGの面上には、図16の画素定義膜の部分及び図17に例示される通り、基板10の全域にわたり画素定義膜51が形成される。画素定義膜51は、例えば珪素化合物(典型的には窒化珪素や酸化珪素)等の絶縁性の無機材料で形成される。図16の画素定義膜の部分から理解される通り、画素定義膜51には、各アノード130aに対応する開口部51Aが形成される。画素定義膜51のうち開口部51Aの内周縁の近傍の領域はアノード130aの周縁に重なる。すなわち、開口部51Aの内周縁は平面視でアノード130aの周縁の内側に位置する。各開口部51Aは、平面形状(矩形状)やサイズが共通し、かつ、X方向およびY方向の各々にわたり共通のピッチで行列状に配列する。以上の説明から理解される通り、画素定義膜51は平面視で格子状に形成される。尚、開口部51Aの平面形状やサイズは、表示色が同じであれば同じであり、表示色が異なる場合は異なるようにしてもよい。また、開口部51Aのピッチは、表示色が同じ開口部同士では同じであり、表示色が異なる開口部間では異なるようにしてもよい。

20

#### 【0098】

その他にも、詳細な説明は省略するが、アノード130aの上層には、発光機能層、OLED130のカソード、及び封止体が積層され、以上の各要素が形成された基板10の表面には封止基板(図示略)が例えば接着剤で接合される。封止基板は、基板10上の各要素を保護するための光透過性の板状部材(例えばガラス基板)である。なお、封止基板の表面または封止体の表面に画素回路110毎にカラーフィルターを形成することも可能である。

30

#### 【0099】

また、図示を省略するが、画素回路110には別の電源線層としての共通電極118が

40

50

形成される。共通電極 118 は、多層配線層内の配線（図示略）を介して、低位側の電源電位  $V_{ct}$  が供給される実装端子に導通する。給電線 116 及び低位側の電源電位  $V_{ct}$  が供給される共通電極 118 は、例えば銀やアルミニウムを含有する導電材料で例えば 100 nm 程度の膜厚に形成される。共通電極 118 は、アノード 130a と導通する。

#### 【0100】

上述したように、駆動トランジスター 121 のゲート  $g$  に供給する電位  $V_g$  のデータ圧縮率を高めるためには、転送容量（第 1 容量）133 を大きくすることが望ましいが、本実施形態によれば、転送容量 133 を、それぞれ異なる層に形成された第 1 電極 133-1 と、第 2 電極 133-2 と、これらの電極の間の絶縁層 LD とにより形成し、MIM (Metal-Insulator-Metal) 構造を探るため、チップ面積の増大を防ぎつつ、転送容量 133 の大容量化が可能である。また、転送容量 133 は、第 2 トランジスター 122 及び第 3 トランジスター 123 のソース電極が形成される層よりも上層に形成されるので、画素回路 110 の表示領域内に形成されることになり、チップ面積の増大を防ぐことができる。

また、シールド容量（第 2 容量）134 については、絶縁層 LF を介して、第 1 データ転送線 14-1 とシールド線としての給電線 16 とを所定の間隙で配置することによって形成する。したがって、シールド容量 134 は、2 本の平行な配線によって形成されるので、Y 方向において所定の長さを有することになり、所定の容量を確保することができる。また、シールド容量 134 についても画素回路 110 の表示領域内に形成されるので、チップ面積の増大を防ぐことができる。

#### 【0101】

本実施例では、画素回路 110 ごとに転送容量 133 を形成したが、第 2 データ転送線 14-2 ごとに転送容量 133 を形成するようにしてもよい。チップ面積の増大をさらに防ぐことができる。

#### 【0102】

図 15 ないし図 17 から理解されるように、本実施形態においては、供給される信号の振幅が大きい第 1 データ転送線 14-1 は、圧縮された信号が供給される第 2 データ信号線 14-2 よりも上層に形成されている。つまり、駆動トランジスター 121 のゲートに対する、第 1 データ転送線 14-1 に供給される振幅の大きい信号の影響が軽減され、駆動トランジスター 121 のゲートの電位の変動を抑制して、表示品位を向上させることができる。

#### 【0103】

また、図 15 及び図 17 から理解されるように、本実施形態においては、第 2 データ転送線 14-2 は、駆動トランジスター 121、第 1 トランジスター 126、第 2 トランジスター 122、及び第 3 トランジスター 123 のソース電極が形成される層よりも上層に形成される。したがって、チップ面積の増大を防ぐことができる。

さらに、図 15 及び図 17 から理解されるように、駆動トランジスター 121 の第 2 電流端に接続される電源線としての給電線 116 は、第 2 データ転送線 14-2 よりも下層に形成されるので、給電線 116 がシールドとして機能し、駆動トランジスター 121 のゲートの電位の変動をより一層効果的に抑制して、表示品位を向上させることができる。

また、図 15 から理解されるように、駆動トランジスター 121 は電源線としての給電線 116 に覆われているので、給電線 116 がシールドとして機能し、駆動トランジスター 121 のゲートの電位の変動をより一層効果的に抑制して、表示品位を向上させることができる。

#### 【0104】

図 15 ないし図 17 から理解されるように、転送容量 133 の第 1 電極 133-1 と第 2 電極 133-2 は、第 1 データ転送線 14-1 が形成される層とは異なる層に形成されている。したがって、小さな面積である程度の容量を確保するために絶縁層を薄くした場合でも、短絡を発生せずに均一な層間を有する転送容量 133 を形成することができる。

#### 【0105】

図 15 の金属層 A の部分に示すように、第 1 トランジスター 126 と第 1 データ転送線

10

20

30

40

50

14-1との接続位置を点線の楕円Aで示し、駆動トランジスター121の第1電流端と第3トランジスター123との接続位置を点線の楕円Bで示す。また、第4トランジスター124と発光素子としてのOLED130との接続位置を点線の楕円Cで示す。このように示すと、画素回路の平面視においては、第1トランジスター126と第1データ転送線14-1との接続位置を示す点線の楕円Aは、駆動トランジスター121の第1電流端と第3トランジスター123との接続位置を示す点線の楕円Bよりも、第4トランジスター124と発光素子としてのOLED130との接続位置を示す点線の楕円Cに近くなるように設定されている。

【0106】

第1データ転送線14-1には振幅の高い信号が供給され、第1トランジスター126と第1データ転送線14-1の接続位置（楕円A）には、ノイズが発生する可能性がある。しかし、第1トランジスター126と第1データ転送線14-1の接続位置（楕円A）は、画素回路の平面視において、第4トランジスター124と発光素子としてのOLED130との接続位置（楕円C）よりも、駆動トランジスター121の第1電流端と第3トランジスター123との接続位置（楕円B）から遠い位置に設定されている。したがって、第1トランジスター126と第1データ転送線14-1の接続位置（楕円A）にノイズが発生したとしても、駆動トランジスター121に対するノイズの影響を抑えることができ、表示品位を向上させることができる。

【0107】

また、第1トランジスター126と第1データ転送線14-1の接続位置（楕円A）、駆動トランジスター121の第1電流端と第3トランジスター123との接続位置（楕円B）、及び第4トランジスター124と発光素子としてのOLED130との接続位置（楕円C）のそれぞれは、当該画素回路110における電源線としての給電線116と、Y方向に隣り合うブロックの画素回路110における電源線としての給電線116との間に配置されることになる。したがって、給電線116がシールドとなり、ノイズの影響を低減することができる。

【0108】

また、図15に示すように、第1トランジスター126と第1データ転送線14-1の接続位置（楕円A）は、リセット電位供給線としての給電線16に接続される第5トランジスター125のゲート層G<sub>Torst</sub>に接続される制御線145と、第1トランジスター126のゲート層G<sub>fix</sub>に接続される制御線146との間に配置される。したがって、第1データ転送線14-1に振幅の高い信号が供給されてノイズが発生したとしても、制御線145と制御線146がシールドとして機能し、駆動トランジスター121に対するノイズの影響を低減することができる。

【0109】

また、図15に示すように、第4トランジスター124と発光素子としてのOLED130との接続位置（楕円C）は、リセット電位供給線としての給電線16に接続される第5トランジスター125のゲート層G<sub>Torst</sub>に接続される制御線145と、第4トランジスター124のゲート層G<sub>Tel</sub>に接続される制御線144との間に配置される。したがって、第1データ転送線14-1に振幅の高い信号が供給されてノイズが発生したとしても、制御線145と制御線144がシールドとして機能し、駆動トランジスター121に対するノイズの影響を低減することができる。

【0110】

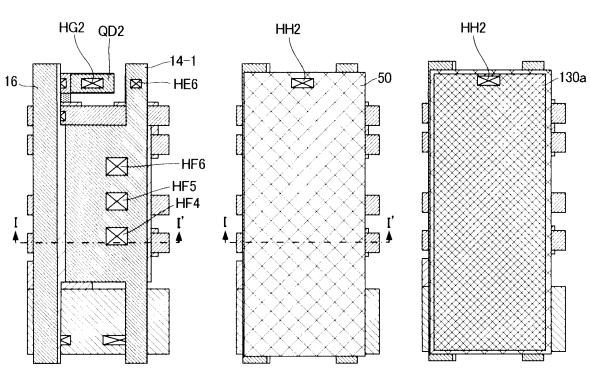

<第2実施形態>

次に、本発明の第2実施形態について添付図面の図18ないし図20を参照しつつ説明する。なお、第1実施形態との共通箇所については、同一符号を付して説明を省略する。

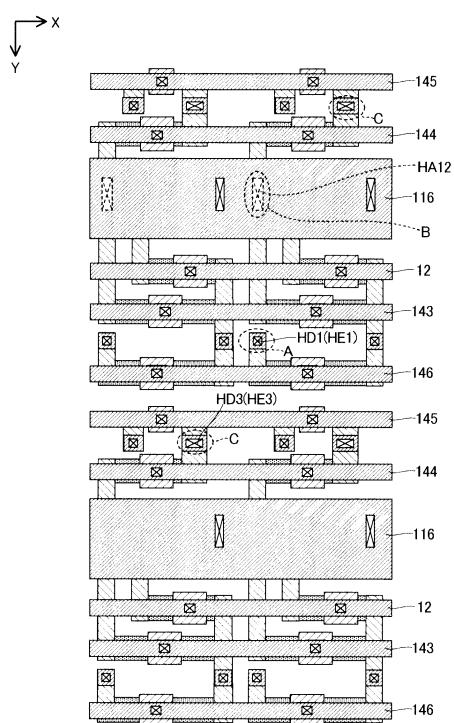

本実施形態の回路は、図4に示す第1実施形態の回路と同様である。本実施形態は、図18ないし図20に示すように、各トランジスターの平面視上の配置が第1実施形態と異なっている。但し、各配線の層上の位置関係は第1実施形態と同様である。

【0111】

10

20

30

40

50

本実施形態においても、図18及び図20から理解されるように、転送容量（第1容量）133は、金属である第1電極133-1と、絶縁層LDと、金属である第1電極133-2とから形成され、MIM(Metal-Insulator-Metal)構造により形成される。したがって、転送容量133の大容量化が可能であり、駆動トランジスター121のゲートgに供給する電位Vgのデータ圧縮率を高めることができる。また、転送容量133は、第2トランジスター122及び第3トランジスター123のソース電極が形成される層よりも上層に形成されるので、画素回路110の表示領域内に形成されることになり、チップ面積の増大を防ぐことができる。

#### 【0112】

図19及び図20から理解されるように、シールド容量（第2容量）134については、絶縁層LFを介して、第1データ転送線14-1とシールド線としての給電線16とを所定の間隙で配置することによって形成する。したがって、シールド容量134は、2本の平行な配線によって形成されるので、Y方向において所定の長さを有することになり、所定の容量を確保することができる。また、シールド容量134についても画素回路110の表示領域内に形成されるので、チップ面積の増大を防ぐことができる。

#### 【0113】

本実施例においても、画素回路110ごとに転送容量133を形成したが、第2データ転送線14-2ごとに転送容量133を形成するようにしてもよい。チップ面積の増大をさらに防ぐことができる。

#### 【0114】

図18ないし図20から理解されるように、本実施形態においては、供給される信号の振幅が大きい第1データ転送線14-1は、圧縮された信号が供給される第2データ信号線14-2よりも上層に形成されている。つまり、駆動トランジスター121のゲートに対する、第1データ転送線14-1に供給される振幅の大きい信号の影響が軽減され、駆動トランジスター121のゲートの電位の変動を抑制して、表示品位を向上させることができる。

#### 【0115】

また、図18及び図20から理解されるように、本実施形態においては、第2データ転送線14-2は、駆動トランジスター121、第1トランジスター126、第2トランジスター122、及び第3トランジスター123のソース電極が形成される層よりも上層に形成される。したがって、チップ面積の増大を防ぐことができる。

図18に示す中継電極QA3はソース電極であり、第1トランジスター126のドレイン領域またはソース領域を形成する能動領域10A、第3トランジスター123のドレイン領域またはソース領域を形成する能動領域10A、及び第2トランジスター122のドレイン領域またはソース領域を形成する能動領域10Aに直接接して形成される電極である。

また、図18に示す中継電極QA8もソース電極であり、第4トランジスター124のドレイン領域またはソース領域を形成する能動領域10A、第3トランジスター123のドレイン領域またはソース領域を形成する能動領域10A、及び駆動トランジスター121のドレイン領域またはソース領域を形成する能動領域10Aに直接接して形成される電極である。

さらに、図18に示す中継電極QA11もソース電極であり、第2トランジスター122のドレイン領域またはソース領域を形成する能動領域10Aに直接接して形成される電極である。

さらに、図18及び図20から理解されるように、駆動トランジスター121の第2電流端に接続される電源線としての給電線116は、第2データ転送線14-2よりも下層に形成されるので、給電線116がシールドとして機能し、駆動トランジスター121のゲートの電位の変動をより一層効果的に抑制して、表示品位を向上させることができる。

また、図18から理解されるように、駆動トランジスター121は電源線としての給電線116に覆われているので、給電線116がシールドとして機能し、駆動トランジスター

10

20

30

40

50

– 1 2 1 のゲートの電位の変動をより一層効果的に抑制して、表示品位を向上させることができる。

【 0 1 1 6 】

図 1 8 ないし図 2 0 から理解されるように、転送容量 1 3 3 の第 1 電極 1 3 3 - 1 と第 2 電極 1 3 3 - 2 は、第 1 データ転送線 1 4 - 1 が形成される層とは異なる層に形成されている。したがって、小さな面積である程度の容量を確保するために絶縁層を薄くした場合でも、短絡を発生せずに均一な層間を有する転送容量 1 3 3 を形成することができる。

【 0 1 1 7 】

図 1 8 の金属層 A の部分に示すように、第 1 トランジスター 1 2 6 と第 1 データ転送線 1 4 - 1 との接続位置を点線の楕円 A で示し、駆動トランジスター 1 2 1 の第 1 電流端と第 3 トランジスター 1 2 3 との接続位置を点線の楕円 B で示す。また、第 4 トランジスター 1 2 4 と発光素子としての O L E D 1 3 0 との接続位置を点線の楕円 C で示す。このように示すと、一つの画素回路 1 1 0 内で見た場合には、第 1 トランジスター 1 2 6 と第 1 データ転送線 1 4 - 1 との接続位置を示す点線の楕円 A は、第 4 トランジスター 1 2 4 と発光素子としての O L E D 1 3 0 との接続位置を示す点線の楕円 C よりも、駆動トランジスター 1 2 1 の第 1 電流端と第 3 トランジスター 1 2 3 との接続位置を示す点線の楕円 B に近くなっている。

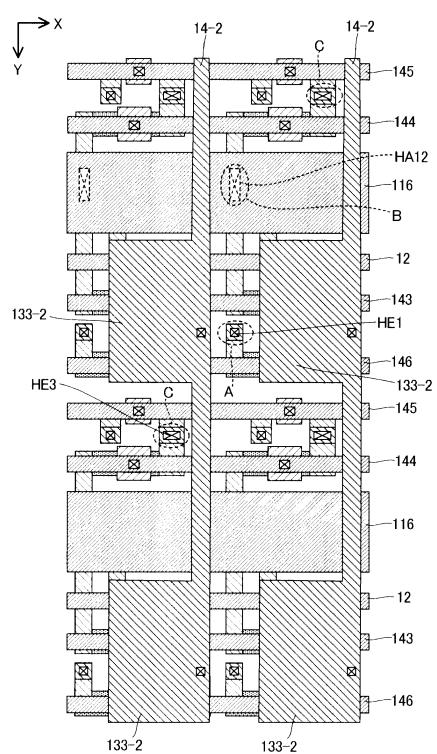

【 0 1 1 8 】

しかしながら、図 2 1 及び図 2 2 に示すように、Y 方向及び X 方向に隣り合う異なる画素回路 1 1 0 間で見た場合には、第 1 トランジスター 1 2 6 と第 1 データ転送線 1 4 - 1 との接続位置を示す点線の楕円 A は、駆動トランジスター 1 2 1 の第 1 電流端と第 3 トランジスター 1 2 3 との接続位置を示す点線の楕円 B よりも、第 4 トランジスター 1 2 4 と発光素子としての O L E D 1 3 0 との接続位置を示す点線の楕円 C に近くなっている。

【 0 1 1 9 】

したがって、第 1 データ転送線 1 4 - 1 には振幅の高い信号が供給され、第 1 トランジスター 1 2 6 と第 1 データ転送線 1 4 - 1 の接続位置（楕円 A ）にノイズが発生したとしても、駆動トランジスター 1 2 1 に対するノイズの影響を抑えることができ、表示品位を向上させることができる。

【 0 1 2 0 】

また、図 2 1 及び図 2 2 に示すように、Y 方向及び X 方向に隣り合う異なる画素回路 1 1 0 間で見た場合には、第 1 トランジスター 1 2 6 と第 1 データ転送線 1 4 - 1 との接続位置を点線の楕円 A は、第 5 トランジスター 1 2 5 のゲートに接続される制御線 1 4 5 と、駆動トランジスター 1 2 6 のゲートに接続される走査線 1 2 との間に配置される。したがって、駆動トランジスター 1 2 6 のゲートは、制御線 1 4 5 と走査線 1 2 との間に配置されることになり、制御線 1 4 5 と走査線 1 2 とによりシールドされる。その結果、第 1 データ転送線 1 4 - 1 には振幅の高い信号が供給され、第 1 トランジスター 1 2 6 と第 1 データ転送線 1 4 - 1 の接続位置（楕円 A ）にノイズが発生したとしても、駆動トランジスター 1 2 1 に対するノイズの影響を抑えることができ、表示品位を向上させることができる。

【 0 1 2 1 】

また、図 1 8 に示すように、第 1 トランジスター 1 2 6 と第 1 データ転送線 1 4 - 1 の接続位置（楕円 A ）、駆動トランジスター 1 2 1 の第 1 電流端と第 3 トランジスター 1 2 3 との接続位置（楕円 B ）、及び第 4 トランジスター 1 2 4 と発光素子としての O L E D 1 3 0 との接続位置（楕円 C ）のそれぞれは、当該画素回路 1 1 0 における電源線としての給電線 1 1 6 と、Y 方向に隣り合うブロックの画素回路 1 1 0 における電源線としての給電線 1 1 6 との間に配置されることになる。したがって、給電線 1 1 6 がシールドとなり、ノイズの影響を低減することができる。

【 0 1 2 2 】

また、図 1 8 に示すように、第 1 トランジスター 1 2 6 と第 1 データ転送線 1 4 - 1 の接続位置（楕円 A ）は第 3 トランジスター 1 2 3 のゲート層 G T cmp に接続される制御線

10

20

30

40

50

143と、第1トランジスター126のゲート層G<sub>Tfix</sub>に接続される制御線146との間に配置される。したがって、第1データ転送線14-1に振幅の高い信号が供給されてノイズが発生したとしても、制御線143と制御線146がシールドとして機能し、駆動トランジスター121に対するノイズの影響を低減することができる。

【0123】

また、図18に示すように、第4トランジスター124と発光素子としてのOLED130との接続位置（楕円C）は、リセット電位供給線としての給電線16に接続される第5トランジスター125のゲート層G<sub>Torst</sub>に接続される制御線145と、第4トランジスター124のゲート層G<sub>Tel</sub>に接続される制御線144との間に配置される。したがって、第1データ転送線14-1に振幅の高い信号が供給されてノイズが発生したとしても、制御線145と制御線144がシールドとして機能し、駆動トランジスター121に対するノイズの影響を低減することができる。10

【0124】

<第3実施形態>

次に、本発明の第3実施形態について添付図面の図23ないし図26を参照しつつ説明する。上述した各実施形態においては、6個のトランジスターを用いたが、本実施形態では、5個のトランジスターを用いる。

【0125】

<回路図>

図23に示すように、本実施形態においては、第5トランジスター125が設けられていない構成が、上述した各実施形態と異なっている。また、第1トランジスター126のドレインまたはソースには、初期電位V<sub>ini</sub>が供給される給電線17が接続されている。また、第1データ転送線14-1には、トランスマッショングート45を介して、第1データ転送線14-1を初期化する電圧V<sub>ref</sub>が供給される。電圧V<sub>ref</sub>は、初期電位V<sub>ini</sub>と同じであってもよい。

本実施形態における動作は、上述した各実施形態と同様であり、発光期間中にフローティングノードになる第2トランジスター122の転送容量133側の第2データ転送線14-2を、他のブロックで初期化期間の処理が行われる期間において固定電位の初期電位V<sub>ini</sub>に設定するので、第2データ転送線14-2の電位が電源電圧に近づくことを抑えることができる。その結果、第2トランジスター122がオンすることなく、画素容量132において電圧が保持され、表示の不具合を発生させることがない。20

【0126】

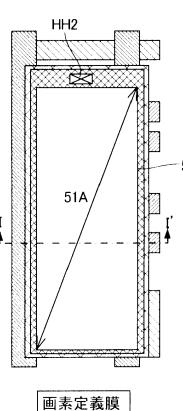

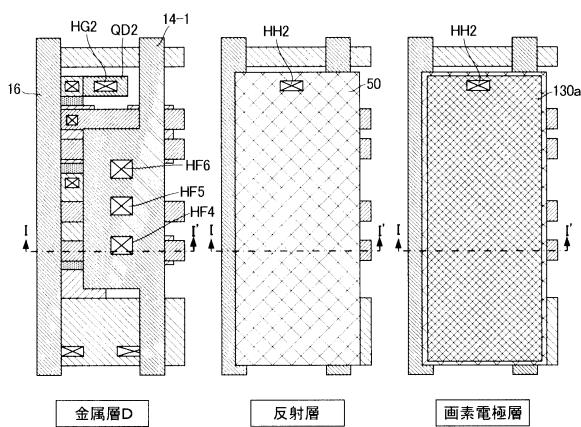

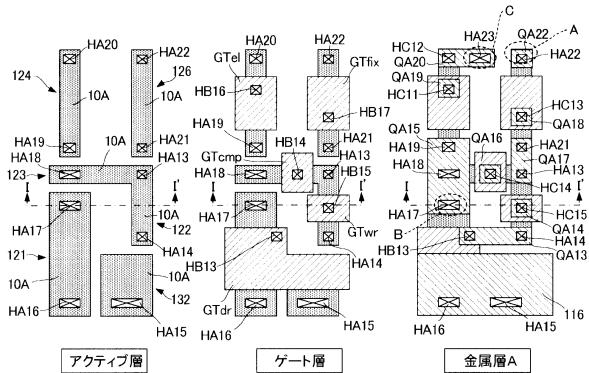

<構造>

次に、第3実施形態の電気光学装置1の具体的な構造を以下に詳述する。なお、以下の説明で参照する各図面では、説明の便宜のために、各要素の寸法や縮尺を実際の電気光学装置1とは相違させている。図24及び図25は、電気光学装置1の各要素を形成する各段階での基板10の表面の様子を画素回路110の1個分に着目して図示した平面図である。図26は、電気光学装置1の断面図である。図24及び図25のI-I'線を含む断面に対応した断面図が図26に相当する。なお、図24及び図25は平面図であるが、各要素の視覚的な把握を容易化する観点から、図26と共に各要素に図26と同様のハッチングが便宜的に付加されている。40

【0127】

図26及び図24のアクティブ層の部分から理解される通り、珪素等の半導体材料で形成された基板10の表面には、画素回路110の各トランジスター121, 122, 123, 124, 126の能動領域10A（ソース/ドレイン領域）が形成される。能動領域10Aにはイオンが注入される。画素回路110の各トランジスター121, 122, 123, 124, 126のアクティブ層はソース領域とドレイン領域との間に存在し、能動領域10Aとは別種類のイオンが注入されるが、便宜的に能動領域10Aと一緒に記載している。また、本実施形態においては、画素容量132を構成する領域においても能動領域10Aが形成され、能動領域10Aには不純物が注入されて電源に接続される。そして50

、能動領域 10 A を一方の電極とし、絶縁層を介して形成された容量電極を他方の電極とするいわゆるMOS容量を構成する。また、画素容量 132 を構成する領域における能動領域 10 A は電源電位部としても機能する。図 24 のアクティブ層の部分から理解される通り、第3トランジスター 123 の能動領域 10 A は導通孔 HA13 が設けられた部分において、第2トランジスター 122 の能動領域 10 A とつながっている。したがって、第3トランジスター 123 の電流端は、第2トランジスター 122 の電流端としても機能する。図 24 のゲート層の部分及び図 26 から理解される通り、能動領域 10 A が形成された基板 10 の表面は絶縁膜 L0 (ゲート絶縁膜) で被覆され、各トランジスター 121, 122, 123, 124, 126 のゲート層 GT (GTdr, GTwr, GTcmp, GTel, GTfix) が絶縁膜 L0 の面上に形成される。各トランジスター 121, 122, 123, 124, 126 のゲート層 GT は、絶縁膜 L0 を挟んでアクティブ層に対向する。

10

また、図 24 のゲート層の部分に例示される通り、駆動トランジスター 121 のゲート層 GTdr は、容量素子を構成する領域に形成された能動領域 10 A まで延びて形成され、画素容量 132 を構成している。

#### 【0128】

図 26 から理解される通り、各トランジスター 121, 122, 123, 124, 126 のゲート層 GT 及び画素容量 132 が形成された絶縁膜 L0 の面上には、複数の絶縁層 L (LA ~ LH) と複数の導電層 (配線層) とを交互に積層した多層配線層が形成される。各絶縁層 L は、例えば珪素化合物 (典型的には窒化珪素や酸化珪素) 等の絶縁性の無機材料で形成される。なお、以下の説明では、導電層 (単層または複数層) の選択的な除去により複数の要素が同一工程で一括的に形成される関係を「同層から形成される」と表記する。

20

#### 【0129】

絶縁層 LA は、各トランジスター 121, 122, 123, 124, 126 のゲート層 GT が形成された絶縁膜 L0 の面上に形成される。図 24 の金属層 A の部分及び図 26 から理解される通り、絶縁層 LA の面上には、給電線 116 と、複数の中継電極 QA (QA13, QA14, QA15, QA16, QA17, QA18, QA19, QA20, QA21) とが同層から形成される。

また、図 24 から理解されるように、本実施形態においては、第2データ転送線 14-2 は、駆動トランジスター 121、第1トランジスター 126、第2トランジスター 122、及び第3トランジスター 123 のソース電極が形成される層よりも上層に形成される。したがって、チップ面積の増大を防ぐことができる。

30

図 24 に示す中継電極 QA13 はソース電極であり、第2トランジスター 122 のドレイン領域またはソース領域を形成する能動領域 10 A に直接接して形成される電極である。

また、図 24 に示す中継電極 QA15 もソース電極であり、第3トランジスター 123 のドレイン領域またはソース領域を形成する能動領域 10 A、第4トランジスター 124 のドレイン領域またはソース領域を形成する能動領域 10 A、及び駆動トランジスター 121 のドレイン領域またはソース領域を形成する能動領域 10 A に直接接して形成される電極である。

40

さらに、図 24 に示す中継電極 QA17 もソース電極であり、第3トランジスター 123 のドレイン領域またはソース領域を形成する能動領域 10 A、第2トランジスター 122 のドレイン領域またはソース領域を形成する能動領域 10 A、及び第1トランジスター 126 のドレイン領域またはソース領域を形成する能動領域 10 A に直接接して形成される電極である。

図 24 の金属層 A の部分及び図 26 から理解される通り、給電線 116 は、絶縁層 LA と絶縁膜 L0 とを貫通する導通孔 HA16 を介して駆動トランジスター 121 のソース領域またはドレイン領域を形成する能動領域 10 A に導通する。また、給電線 116 は、絶縁層 LA と絶縁膜 L0 とを貫通する導通孔 HA15 を介して画素容量 132 を形成する能動領域 10 A に導通する。給電線 116 は、複数の画素回路 110 にわたり駆動トランジ

50

スター 121 のチャネル幅の方向 (X 方向) に沿って延在する。給電線 116 は、多層配線層内の配線 (図示略) を介して、高位側の電源電位 V<sub>e1</sub> が供給される実装端子に導通する。なお、図示を省略するが、画素回路 110 の周辺領域内にも別の電源線層が形成される。この電源線層は、多層配線層内の配線 (図示略) を介して、低位側の電源電位 V<sub>c1</sub> が供給される実装端子に導通する。給電線 116 及び低位側の電源電位 V<sub>c1</sub> が供給される電源線層は、例えば銀やアルミニウムを含有する導電材料で例えば 100 nm 程度の膜厚に形成される。

【 0130 】

駆動トランジスター 121 のゲート層 G<sub>Tdr</sub> は、中継電極 Q<sub>A13</sub> と、絶縁層 L<sub>A</sub> を貫通する導通孔 H<sub>B13</sub> と、絶縁層 L<sub>A</sub> と絶縁膜 L<sub>0</sub> とを貫通する導通孔 H<sub>A14</sub> とを介して、第 2 トランジスター 122 のソース領域またはドレイン領域を形成する能動領域 10A に導通する。

10

【 0131 】

駆動トランジスター 121 と第 3 トランジスター 123 及び第 4 トランジスター 124 との導通部、第 3 トランジスター 123 と第 6 トランジスター 126 との導通部のそれには、中継電極 Q<sub>A15</sub>、中継電極 Q<sub>A17</sub> が、給電線 116 と同層に形成される。また、第 2 トランジスター 122 のゲート層 G<sub>Twr</sub>、第 3 トランジスター 123 のゲート層 G<sub>Tcmp</sub>、第 4 トランジスター 124 のゲート層 G<sub>Tel</sub>、及び第 6 トランジスターのゲート層 G<sub>Tfix</sub> の導通部には、中継電極 Q<sub>A14</sub>、中継電極 Q<sub>A16</sub>、中継電極 Q<sub>A19</sub>、及び中継電極 Q<sub>A18</sub> が、給電線 116 と同層に形成される。さらに、第 4 トランジスター 124 のソース領域またはドレイン領域の導通部、及び第 1 トランジスター 126 のソース領域またはドレイン領域の導通部には、中継電極 Q<sub>A20</sub>、及び中継電極 Q<sub>A21</sub> が、給電線 116 と同層に形成される。

20

【 0132 】

図 24 の金属層 A の部分、及び図 26 から理解される通り、中継電極 Q<sub>A15</sub> は、絶縁膜 L<sub>0</sub> と絶縁層 L<sub>A</sub> とを貫通する導通孔 H<sub>A17</sub> を介して駆動トランジスター 121 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。また、中継電極 Q<sub>A15</sub> は、絶縁膜 L<sub>0</sub> と絶縁層 L<sub>A</sub> とを貫通する導通孔 H<sub>A18</sub> を介して、第 3 トランジスター 123 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。さらに、中継電極 Q<sub>A15</sub> は、絶縁膜 L<sub>0</sub> と絶縁層 L<sub>A</sub> とを貫通する導通孔 H<sub>A19</sub> を介して第 4 トランジスター 124 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。

30

【 0133 】

中継電極 Q<sub>A17</sub> は、絶縁膜 L<sub>0</sub> と絶縁層 L<sub>A</sub> を貫通する導通孔 H<sub>A13</sub> を介して、第 2 トランジスター 122 と第 3 トランジスター 122 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。また、中継電極 Q<sub>A17</sub> は、絶縁膜 L<sub>0</sub> と絶縁層 L<sub>A</sub> を貫通する導通孔 H<sub>A21</sub> を介して、第 1 トランジスター 121 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。

【 0134 】

中継電極 Q<sub>A20</sub> は、絶縁膜 L<sub>0</sub> と絶縁層 L<sub>A</sub> を貫通する導通孔 H<sub>A20</sub> を介して、第 4 トランジスター 124 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。中継電極 Q<sub>A21</sub> は、絶縁膜 L<sub>0</sub> と絶縁層 L<sub>A</sub> を貫通する導通孔 H<sub>A22</sub> を介して、第 1 トランジスター 126 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。また、中継電極 Q<sub>A21</sub> は、初期電位が供給される給電線 17 と接続される。

40

【 0135 】

絶縁層 L<sub>B</sub> は、給電線 116 と、複数の中継電極 Q<sub>A</sub> (Q<sub>A13</sub>, Q<sub>A14</sub>, Q<sub>A15</sub>, Q<sub>A16</sub>, Q<sub>A17</sub>, Q<sub>A18</sub>, Q<sub>A19</sub>, Q<sub>A20</sub>, Q<sub>A21</sub>) とが形成された絶縁層 L<sub>A</sub> の面上に形成される。図 24 の金属層 B の部分及び図 26 から理解される通り、絶縁層 L<sub>B</sub> の面上には、走査線 12 と、第 3 トランジスター 123 の制御線 143 と、第 4

50

トランジスター 124 の制御線 144 と、第 1 トランジスター 126 の制御線 146 と、複数の中継電極 QB ( QB5, QB6 ) とが同層から形成される。

【 0136 】

図 24 の金属層 B の部分及び図 26 から理解される通り、第 1 の導電層の一例としての走査線 12 は、画素回路 110 毎に絶縁層 LB に形成された導通孔 HC15 を介して中継電極 QA14 に導通する。したがって、図 24 及び図 26 から理解される通り、走査線 12 は、絶縁層 LB を貫通する導通孔 HC15 と、中継電極 QA14 と、絶縁層 LA を貫通する導通孔 HB15 とを介して第 2 トランジスター 121 のゲート層 GTwr に導通する。走査線 12 は、複数の画素回路 110 にわたり X 方向に直線状に延在し、絶縁層 LC により第 1 容量 133 及び第 2 データ転送線 14-2 からは電気的に絶縁される。

10

【 0137 】

図 24 から理解される通り、制御線 143 は、画素回路 110 毎に絶縁層 LB に形成された導通孔 HC14 を介して中継電極 QA16 に導通する。したがって、図 24 ないし図 26 から理解される通り、制御線 143 は、絶縁層 LB を貫通する導通孔 HC14 と、中継電極 QA16 と、絶縁層 LA を貫通する導通孔 HB14 とを介して第 3 トランジスター 123 のゲート層 GTcmp に導通する。制御線 143 は、複数の画素回路 110 にわたり X 方向に直線状に延在し、絶縁層 LC により第 1 容量 133 及び第 2 データ転送線 14-2 からは電気的に絶縁される。

【 0138 】

図 24 から理解される通り、制御線 144 は、画素回路 110 每に絶縁層 LB に形成された導通孔 HC11 を介して中継電極 QA19 に導通する。したがって、図 24 ないし図 26 から理解される通り、制御線 144 は、絶縁層 LB を貫通する導通孔 HC11 と、中継電極 QA19 と、絶縁層 LA を貫通する導通孔 HB16 とを介して第 4 トランジスター 124 のゲート層 GTel に導通する。制御線 144 は、複数の画素回路 110 にわたり X 方向に直線状に延在し、絶縁層 LC により第 1 容量 133 及び第 2 データ転送線 14-2 からは電気的に絶縁される。

20

【 0139 】

図 24 から理解される通り、制御線 146 は、画素回路 110 毎に絶縁層 LB に形成された導通孔 HC13 を介して中継電極 QA18 に導通する。したがって、図 24 ないし図 26 から理解される通り、制御線 146 は、絶縁層 LB を貫通する導通孔 HC13 と、中継電極 QA18 と、絶縁層 LA を貫通する導通孔 HB17 とを介して第 1 トランジスター 126 のゲート層 GTfix に導通する。制御線 146 は、複数の画素回路 110 にわたり X 方向に直線状に延在し、絶縁層 LC により第 1 容量 133 及び第 2 データ転送線 14-2 からは電気的に絶縁される。

30

【 0140 】

中継電極 QB5 は、画素回路 110 毎に絶縁層 LB に形成された導通孔 HC12 を介して中継電極 QA17 に導通する。したがって、図 24 ないし図 26 から理解される通り、中継電極 QB5 は、絶縁層 LB を貫通する導通孔 HC12 と、中継電極 QA17 と、絶縁膜 L0 および絶縁層 LA を貫通する導通孔 HA21 を介して第 1 トランジスター 126 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。

40

【 0141 】

中継電極 QB6 は、画素回路 110 毎に絶縁層 LB に形成された導通孔 HC16 を介して中継電極 QA20 に導通する。したがって、図 24 ないし図 26 から理解される通り、中継電極 QB6 は、絶縁層 LB を貫通する導通孔 HC16 と、中継電極 QA20 と、絶縁膜 L0 および絶縁層 LA を貫通する導通孔 HA20 を介して第 4 トランジスター 124 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。

【 0142 】

絶縁層 LC は、走査線 12 と、第 3 トランジスター 123 の制御線 143 と、第 4 トランジスター 124 の制御線 144 と、第 1 トランジスター 126 の制御線 146 と、複数の中継電極 QB ( QB5, QB6 ) とが形成された絶縁層 LB の面上に形成される。図 2

50

4 及び図 2 6 から理解される通り、絶縁層 L C の面上には、第 2 データ転送線 14 - 2 と、当該第 2 データ転送線 14 - 2 と一緒に形成された転送容量 133 の第 2 電極 133 - 2 と、中継電極 Q C 4 とが同層から形成される。

#### 【 0 1 4 3 】

第 3 の導電層の一例としての第 2 データ転送線 14 - 2 は、複数の画素回路 110 にわたり Y 方向に沿って延在する。第 2 データ転送線 14 - 2 は、絶縁層 L C を貫通する導通孔 H D 5 と、中継電極 Q B 5 と、絶縁層 L B を貫通する導通孔 H C 12 と、中継電極 Q A 17 と、絶縁膜 L 0 および絶縁層 L A を貫通する導通孔 H A 21 を介して、第 1 ワンジスター 126 のドレイン領域またはソース領域を形成する能動領域 10A に導通される。また、第 2 データ転送線 14 - 2 は、絶縁層 L C を貫通する導通孔 H D 5 と、中継電極 Q B 5 と、絶縁層 L B を貫通する導通孔 H C 12 と、中継電極 Q A 17 と、絶縁膜 L 0 および絶縁層 L A を貫通する導通孔 H A 13 を介して、第 3 ワンジスター 123 及び第 2 ワンジスター 122 のドレイン領域またはソース領域を形成する能動領域 10A に導通する。

10

転送容量 133 (第 1 容量) の第 5 の導電層の一例としての第 2 電極 133 - 2 は、画素回路 110 において、走査線 12、制御線 143、及び制御線 146 を覆う矩形の電極であり、第 2 データ転送線 14 - 2 と一緒に形成される。

#### 【 0 1 4 4 】

絶縁層 L D は、第 2 データ転送線 14 - 2 と、転送容量 133 の第 2 電極 133 - 2 と、中継電極 Q C 4 とが形成された絶縁層 L C の面上に形成される。図 2 4 の容量電極層の部分及び図 2 6 から理解される通り、絶縁層 L D の面上には、転送容量 133 の第 1 電極 133 - 1 が形成される。

20

転送容量 133 (第 1 容量) の第 4 の導電層の一例としての第 1 電極 133 - 1 は、絶縁層 L D を介して第 2 電極 133 - 2 と対向する矩形の容量電極である。第 1 電極 133 - 1 は、絶縁層 L D を介して第 2 電極 133 - 2 と対向する。このように、転送容量 133 は、MIM (Metal-Insulator-Metal) 構造により形成されるので、大容量化が可能となっている。

#### 【 0 1 4 5 】

絶縁層 L E は、転送容量 133 の第 1 電極 133 - 1 が形成された絶縁層 L D の面上に形成される。図 2 5 の金属層 D の部分及び図 2 6 から理解される通り、絶縁層 L E の面上には、第 1 データ転送線 14 - 1 と、給電線 16 と、中継電極 Q D 2 が形成される。

30

第 2 の導電層の一例としての第 1 データ転送線 14 - 1 は、複数の画素回路 110 にわたり Y 方向に沿って延在する。第 1 データ転送線 14 - 1 は、絶縁層 L E を貫通する導通孔 H F 4, H F 5, H F 6 を介して、転送容量 133 の第 1 電極 133 - 1 に導通される。

。

#### 【 0 1 4 6 】

第 6 の導電層の一例としての給電線 16 は、複数の画素回路 110 にわたり Y 方向に沿って延在する。給電線 16 は、第 1 データ転送線 14 - 1 と同層に形成され、絶縁層 L F を介して、第 1 データ転送線 14 - 1 との間に所定の間隙を有して配置される。このようにしてシールド容量 134 が形成され、第 1 データ転送線 14 - 1 は給電線 16 によってシールドされることになる。

40

#### 【 0 1 4 7 】

中継電極 Q D 2 は、絶縁層 L E 及び絶縁層 L D を貫通する導通孔 H E 4 を介して中継電極 Q C 4 に導通する。したがって、中継電極 Q D 2 は、絶縁層 L E 及び絶縁層 L D を貫通する導通孔 H E 4 と、中継電極 Q C 4 と、絶縁層 L C を貫通する導通孔 H D 6 と、中継電極 Q B 6 と、絶縁層 L B を貫通する導通孔 H C 16 と、中継電極 Q A 20 と、絶縁膜 L 0 と絶縁層 L A を貫通する導通孔 H A 20 とを介して、第 4 ワンジスター 124 のドレイン領域またはソース領域を形成する能動領域 10A とに導通する。

#### 【 0 1 4 8 】

絶縁層 L F は、第 1 データ転送線 14 - 1 と、給電線 16 と、中継電極 Q D 2 とが形成

50

された絶縁層 L E の面上に形成される。図 2 5 の反射層の部分及び図 2 6 から理解される通り、絶縁層 L F の面上には、反射層 5 0 が形成される。反射層 5 0 は、画素回路 1 1 0 毎に個別に形成されている。反射層 5 0 は、例えば銀やアルミニウムを含有する光反射性の導電材料で例えば 1 0 0 nm 程度の膜厚に形成される。図 2 5 及び図 2 6 から理解されるように、反射層 5 0 は、絶縁層 L F を貫通する導通孔 H G 2 を介して中継電極 Q D 2 に導通する。したがって、反射層 5 0 は、中継電極 Q D 2 を介して第 4 トランジスター 1 2 4 のドレイン領域またはソース領域を形成する能動領域 1 0 A と導通する。

#### 【 0 1 4 9 】

反射層 5 0 が形成された絶縁層 L F の面上には、図 2 6 に示される通り、光路調整層 L G が形成される。光路調整層 L G は、各画素回路 1 1 0 の共振構造の共振波長（すなわち表示色）を規定する光透過性の膜体である。表示色が同じ画素では、共振構造の共振波長は略同じであり、表示色が異なる画素では、共振構造の共振波長は異なるように設定される。

#### 【 0 1 5 0 】

図 2 5 の画素電極層の部分及び図 2 6 に示される通り、光路調整層 L G の面上には、画素回路 1 1 0 毎のアノード 1 3 0 a が形成される。アノード 1 3 0 a は、例えば I T O (Indium Tin Oxide) 等の光透過性の導電材料で形成される。アノード 1 3 0 a は、光路調整層 L G を貫通する導通孔 H H 2 を介して、反射層 5 0 と導通する。したがって、アノード 1 3 0 a は、反射層 5 0 を介して第 4 トランジスター 1 2 4 のドレイン領域またはソース領域のドレイン領域またはソース領域を形成する能動領域 1 0 A と導通する。

#### 【 0 1 5 1 】

アノード 1 3 0 a が形成された光路調整層 L G の面上には、図 2 6 の画素定義膜の部分及び図 2 6 に例示される通り、基板 1 0 の全域にわたり画素定義膜 5 1 が形成される。画素定義膜 5 1 は、例えば珪素化合物（典型的には窒化珪素や酸化珪素）等の絶縁性の無機材料で形成される。図 2 5 の画素定義膜の部分から理解される通り、画素定義膜 5 1 には、各アノード 1 3 0 a に対応する開口部 5 1 A が形成される。画素定義膜 5 1 のうち開口部 5 1 A の内周縁の近傍の領域はアノード 1 3 0 a の周縁に重なる。すなわち、開口部 5 1 A の内周縁は平面視でアノード 1 3 0 a の周縁の内側に位置する。各開口部 5 1 A は、平面形状（矩形状）やサイズが共通し、かつ、X 方向および Y 方向の各々にわたり共通のピッチで行列状に配列する。以上の説明から理解される通り、画素定義膜 5 1 は平面視で格子状に形成される。尚、開口部 5 1 A の平面形状やサイズは、表示色が同じであれば同じであり、表示色が異なる場合は異なるようにしてもよい。また、開口部 5 1 A のピッチは、表示色が同じ開口部同士では同じであり、表示色が異なる開口部間では異なるようにしてもよい。

#### 【 0 1 5 2 】

その他にも、詳細な説明は省略するが、アノード 1 3 0 a の上層には、発光機能層、 O L E D 1 3 0 のカソード、及び封止体が積層され、以上の各要素が形成された基板 1 0 の表面には封止基板（図示略）が例えば接着剤で接合される。封止基板は、基板 1 0 上の各要素を保護するための光透過性の板状部材（例えばガラス基板）である。なお、封止基板の表面または封止体の表面に画素回路 1 1 0 毎にカラーフィルターを形成することも可能である。

#### 【 0 1 5 3 】

また、図示を省略するが、画素回路 1 1 0 には別の電源線層としての共通電極 1 1 8 が形成される。共通電極 1 1 8 は、多層配線層内の配線（図示略）を介して、低位側の電源電位 V c t が供給される実装端子に導通する。給電線 1 1 6 及び低位側の電源電位 V c t が供給される共通電極 1 1 8 は、例えば銀やアルミニウムを含有する導電材料で例えば 1 0 0 nm 程度の膜厚に形成される。共通電極 1 1 8 は、アノード 1 3 0 a と導通する。

#### 【 0 1 5 4 】

駆動トランジスター 1 2 1 のゲート g に供給する電位 V g のデータ圧縮率を高めるためには、転送容量（第 1 容量）1 3 3 を大きくすることが望ましいが、本実施形態によれば

10

20

30

40

50

、転送容量 133 を MIM (Metal-Insulator-Metal) 構造により形成するため、転送容量 133 の大容量化が可能である。また、転送容量 133 は、第 2 トランジスター 122 及び第 3 トランジスター 123 のソース線が形成される層よりも上層に形成されるので、画素回路 110 の表示領域内に形成されることになり、チップ面積の増大を防ぐことができる。

また、シールド容量 (第 2 容量) 134 については、絶縁層 LF を介して、第 1 データ転送線 14-1 とシールド電極としての給電線 16 とを所定の間隙で配置することによって形成する。したがって、シールド容量 134 は、2 本の平行な配線によって形成されるので、Y 方向において所定の長さを有することになり、所定の容量を確保することができる。また、シールド容量 134 についても画素回路 110 の表示領域内に形成されるので、チップ面積の増大を防ぐことができる。10

#### 【0155】

本実施例では、画素回路 110 ごとに転送容量 133 を形成したが、第 2 データ転送線 14-2 ごとに転送容量 133 を形成するようにしてもよい。チップ面積の増大をさらに防ぐことができる。

#### 【0156】

図 24 ないし図 26 から理解されるように、本実施形態においては、供給される信号の振幅が大きい第 1 データ転送線 14-1 は、圧縮された信号が供給される第 2 データ信号線 14-2 よりも上層に形成されている。つまり、駆動トランジスター 121 のゲートに対する、第 1 データ転送線 14-1 に供給される振幅の大きい信号の影響が軽減され、駆動トランジスター 121 のゲートの電位の変動を抑制して、表示品位を向上させることができる。20

#### 【0157】

また、図 24 及び図 26 から理解されるように、本実施形態においては、第 2 データ転送線 14-2 は、駆動トランジスター 121、第 1 トランジスター 126、第 2 トランジスター 122、及び第 3 トランジスター 123 のソース電極が形成される層よりも上層に形成される。したがって、チップ面積の増大を防ぐことができる。

さらに、図 24 及び図 26 から理解されるように、駆動トランジスター 121 の第 2 電流端に接続される電源線としての給電線 116 は、第 2 データ転送線 14-2 よりも下層に形成されるので、給電線 116 がシールドとして機能し、駆動トランジスター 121 のゲートの電位の変動をより一層効果的に抑制して、表示品位を向上させることができる。30

また、図 24 から理解されるように、駆動トランジスター 121 は電源線としての給電線 116 に覆われているので、給電線 116 がシールドとして機能し、駆動トランジスター 121 のゲートの電位の変動をより一層効果的に抑制して、表示品位を向上させることができる。

#### 【0158】

図 24 ないし図 26 から理解されるように、転送容量 133 の第 1 電極 133-1 と第 2 電極 133-2 は、第 1 データ転送線 14-1 が形成される層とは異なる層に形成されている。したがって、小さな面積である程度の容量を確保するために絶縁層を薄くした場合でも、短絡を発生せずに均一な層間を有する転送容量 133 を形成することができる。40

#### 【0159】

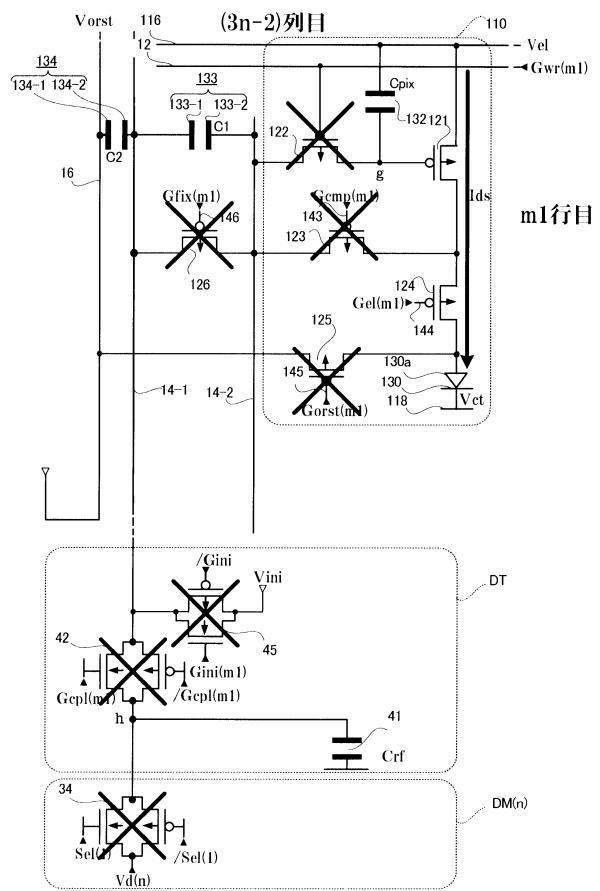

##### <第 4 実施形態>

次に、本発明の第 4 実施形態について添付図面の図 27 ないし図 30 を参照しつつ説明する。なお、第 3 実施形態との共通箇所については、同一符号を付して説明を省略する。

#### 【0160】

##### <回路図>

本実施形態の回路は、図 27 に示すように、第 3 実施形態と同様に 5 個のトランジスターで構成されるが、給電線 17 は設けられていない。その代わりに、第 1 トランジスター 126 のドレインまたはソースは、第 1 データ転送線 14-1 に接続され、第 1 データ転送線 14-1 には、トランスマッショングート 45 を介して、初期電位  $V_{ini}$  が供給され50

る。その他の構成は、第3実施形態と同様である。

本実施形態における動作は、上述した各実施形態と同様であり、発光期間中にフロー・ティングノードになる第2トランジスター122の転送容量133側の第2データ転送線14-2を、他のブロックで初期化期間の処理が行われる期間において固定電位の初期電位V<sub>ini</sub>に設定するので、第2データ転送線14-2の電位が電源電位に近づくことを抑えることができる。その結果、第2トランジスター122がオンすることができなく、画素容量132において電圧が保持され、表示の不具合を発生させることができない。

#### 【0161】

##### <構造>

本実施形態においては、図28に示すように、第2データ転送線14-2の配置と形状が第3実施形態と異なっている。また、第1トランジスター126のドレインまたはソースを構成するノード領域10Aは、導通孔HA22、中継電極QA22、導通孔HD7、中継電極QB8を介して、第1データ転送線14-1と接続される。その他の構造は、第3実施形態と同様である。

#### 【0162】

駆動トランジスター121のゲートgに供給する電位V<sub>g</sub>のデータ圧縮率を高めるためには、転送容量(第1容量)133を大きくすることが望ましいが、本実施形態によれば、転送容量133をMLM(Metal-Insulator-Metal)構造により形成するため、転送容量133の大容量化が可能である。また、転送容量133は、第2トランジスター122及び第3トランジスター123のソース電極が形成される層よりも上層に形成されるので、画素回路110の表示領域内に形成されることになり、チップ面積の増大を防ぐことができる。

図28に示す中継電極QA13はソース電極であり、第2トランジスター122のドレイン領域またはソース領域を形成する能動領域10Aに直接接して形成される電極である。

また、図28に示す中継電極QA15もソース電極であり、第3トランジスター123のドレイン領域またはソース領域を形成する能動領域10A、第4トランジスター124のドレイン領域またはソース領域を形成する能動領域10A、及び駆動トランジスター121のドレイン領域またはソース領域を形成する能動領域10Aに直接接して形成される電極である。

さらに、図28に示す中継電極QA17もソース電極であり、第3トランジスター123のドレイン領域またはソース領域を形成する能動領域10A、第2トランジスター122のドレイン領域またはソース領域を形成する能動領域10A、及び第1トランジスター126のドレイン領域またはソース領域を形成する能動領域10Aに直接接して形成される電極である。

また、シールド容量(第2容量)134については、絶縁層LFを介して、第1データ転送線14-1とシールド線としての給電線16とを所定の間隙で配置することによって形成する。したがって、シールド容量134は、2本の平行な配線によって形成されるので、Y方向において所定の長さを有することになり、所定の容量を確保することができる。また、シールド容量134についても画素回路110の表示領域内に形成されるので、チップ面積の増大を防ぐことができる。

#### 【0163】

本実施例では、画素回路110ごとに転送容量133を形成したが、第2データ転送線14-2ごとに転送容量133を形成するようにしてもよい。チップ面積の増大をさらに防ぐことができる。

#### 【0164】

図28ないし図30から理解されるように、本実施形態においては、供給される信号の振幅が大きい第1データ転送線14-1は、圧縮された信号が供給される第2データ信号線14-2よりも上層に形成されている。つまり、駆動トランジスター121のゲートに対する、第1データ転送線14-1に供給される振幅の大きい信号の影響が軽減され、駆

10

20

30

40

50

動トランジスター 121 のゲートの電位の変動を抑制して、表示品位を向上させることができる。

【 0165 】

また、図 28 及び図 30 から理解されるように、本実施形態においては、第 2 データ転送線 14-2 は、駆動トランジスター 121、第 1 トランジスター 126、第 2 トランジスター 122、及び第 3 トランジスター 123 のソース電極が形成される層よりも上層に形成される。したがって、チップ面積の増大を防ぐことができる。

さらに、図 28 及び図 30 から理解されるように、駆動トランジスター 121 の第 2 電流端に接続される電源線としての給電線 116 は、第 2 データ転送線 14-2 よりも下層に形成されるので、給電線 116 がシールドとして機能し、駆動トランジスター 121 のゲートの電位の変動をより一層効果的に抑制して、表示品位を向上させることができる。10

また、図 28 から理解されるように、駆動トランジスター 121 は電源線としての給電線 116 に覆われているので、給電線 116 がシールドとして機能し、駆動トランジスター 121 のゲートの電位の変動をより一層効果的に抑制して、表示品位を向上させることができる。

【 0166 】

図 28 ないし図 30 から理解されるように、転送容量 133 の第 1 電極 133-1 と第 2 電極 133-2 は、第 1 データ転送線 14-1 が形成される層とは異なる層に形成されている。したがって、小さな面積である程度の容量を確保するために絶縁層を薄くした場合でも、短絡を発生せずに均一な層間を有する転送容量 133 を形成することができる。20

【 0167 】

図 28 の金属層 A の部分に示すように、第 1 トランジスター 126 と第 1 データ転送線 14-1 との接続位置を点線の楕円 A で示し、駆動トランジスター 121 の第 1 電流端と第 3 トランジスター 123 との接続位置を点線の楕円 B で示す。また、第 4 トランジスター 124 と発光素子としての OLED 130 との接続位置を点線の楕円 C で示す。このように示すと、一つの画素回路 110 内で見た場合には、第 1 トランジスター 126 と第 1 データ転送線 14-1 との接続位置を点線の楕円 A は、駆動トランジスター 121 の第 1 電流端と第 3 トランジスター 123 との接続位置を点線の楕円 B よりも、第 4 トランジスター 124 と発光素子としての OLED 130 との接続位置を点線の楕円 C に近くなっている。30

したがって、第 1 データ転送線 14-1 には振幅の高い信号が供給され、第 1 トランジスター 126 と第 1 データ転送線 14-1 の接続位置（楕円 A）にノイズが発生したとしても、駆動トランジスター 121 に対するノイズの影響を抑えることができ、表示品位を向上させることができる。

【 0168 】

また、図 28 に示すように、第 1 トランジスター 126 と第 1 データ転送線 14-1 の接続位置（楕円 A）、駆動トランジスター 121 の第 1 電流端と第 3 トランジスター 123 との接続位置（楕円 B）、及び第 4 トランジスター 124 と発光素子としての OLED 130 との接続位置（楕円 C）のそれぞれは、当該画素回路 110 における電源線としての給電線 116 と、Y 方向に隣り合うブロックの画素回路 110 における電源線としての給電線 116 との間に配置されることになる。したがって、給電線 116 がシールドとなり、ノイズの影響を低減することができる。40

【 0169 】

<変形例 >

本発明は、上述した実施形態に限定されるものではなく、例えば次に述べるような各種の変形が可能である。また、次に述べる変形の態様は、任意に選択された一または複数を、適宜に組み合わせることもできる。

<変形例 1 >

上述した実施形態では、各画素回路 110 において第 3 トランジスター 123 は、駆動トランジスター 121 のドレインと第 2 データ転送線 14-2 との間に接続されているが50

、図31に示すように駆動トランジスター121のドレインとゲートgとの間に接続されてもよい。

【0170】

<変形例2>

第1実施形態においては、第1データ転送線14-1に対して、トランスマッショングート45を介して初期電位V<sub>ini</sub>を供給し、第1トランジスター126をオンすることにより、第2データ転送線14-2に初期電位V<sub>ini</sub>を供給した。しかし、図32に示すように、初期電位V<sub>ini</sub>を供給する給電線17を設け、第1トランジスター126のドレインまたはソースと、給電線17を接続するようにしてもよい。この場合には、第1トランジスター126をオンすることにより、給電線17から第2データ転送線14-2に初期電位V<sub>ini</sub>が供給されることになる。

【0171】

<変形例3>

上述した実施形態の回路図では、第1トランジスター126と転送容量133とを画素回路110ごとに一対一対応で設けているが、図33に示すように、第1トランジスター126と転送容量133とをNb個の画素回路110に対して各一個の割合で設けてよい。

【0172】

<変形例4>

上述した実施形態では、第1データ転送線14-1を3列毎にグループ化するとともに、各グループにおいて第1データ転送線14-1を順番に選択して、データ信号を供給する構成としたが、グループを構成するデータ線数は、「2」以上「3n」以下の所定数であればよい。例えば、グループを構成するデータ線数は、「2」であっても良いし、「4」以上であっても良い。

また、グループ化せずに、すなわちデマルチプレクサDMを用いないで各列の第1データ転送線14-1にデータ信号を一斉に線順次で供給する構成でも良い。

【0173】

<変形例5>

上述した実施形態では、トランジスター121～126をPチャネル型で統一したが、Nチャネル型で統一しても良い。また、Pチャネル型及びNチャネル型を適宜組み合わせても良い。

例えば、トランジスター121～126をNチャネル型で統一する場合、上述した実施形態における、データ信号V<sub>d(n)</sub>とは、正負が逆転した電位を、各画素回路110に供給すればよい。また、この場合、トランジスター121～126のソース及びドレインは、上述した実施形態及び変形例とは逆転した関係となる。

<変形例6>

上述した実施形態及び変形例では、電気光学素子として発光素子であるOLEDを例示したが、例えば無機発光ダイオードやLED(Light Emitting Diode)など、電流に応じた輝度で発光するものであれば良い。

【0174】

<応用例>

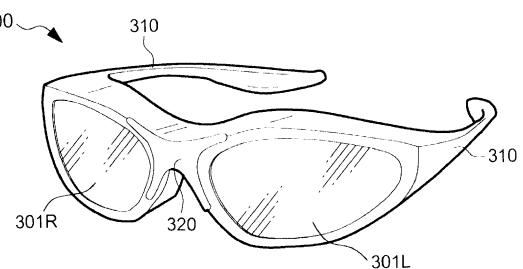

次に、実施形態等や応用例に係る電気光学装置1を適用した電子機器について説明する。電気光学装置1は、画素が小サイズで高精細な表示な用途に向いている。そこで、電子機器として、ヘッドマウント・ディスプレイを例に挙げて説明する。

【0175】

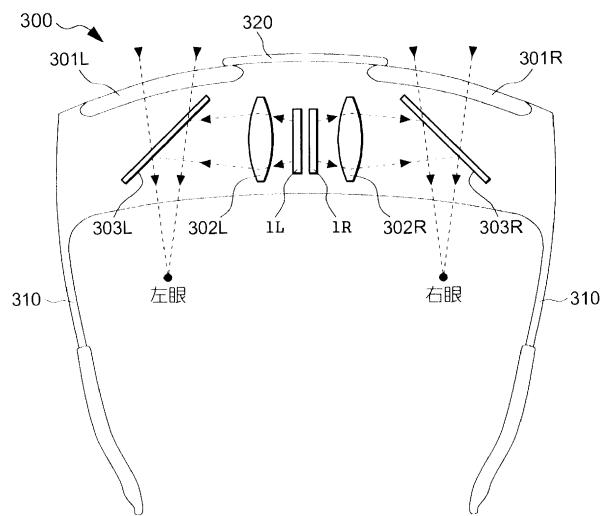

図34は、ヘッドマウント・ディスプレイの外観を示す図であり、図35は、その光学的な構成を示す図である。

まず、図34に示されるように、ヘッドマウント・ディスプレイ300は、外観的には、一般的な眼鏡と同様にテンプル310や、ブリッジ320、レンズ301L、301Rを有する。また、ヘッドマウント・ディスプレイ300は、図35に示されるように、ブ

10

20

30

40

50

リッジ 320 近傍であってレンズ 301L、301R の奥側（図において下側）には、左眼用の電気光学装置 1L と右眼用の電気光学装置 1R とが設けられる。

電気光学装置 1L の画像表示面は、図 35において左側となるように配置している。これによって電気光学装置 1L による表示画像は、光学レンズ 302L を介して図において 9 時の方向に出射する。ハーフミラー 303L は、電気光学装置 1L による表示画像を 6 時の方向に反射させる一方で、12 時の方向から入射した光を透過させる。

電気光学装置 1R の画像表示面は、電気光学装置 1L とは反対の右側となるように配置している。これによって電気光学装置 1R による表示画像は、光学レンズ 302R を介して図において 3 時の方向に出射する。ハーフミラー 303R は、電気光学装置 1R による表示画像を 6 時方向に反射させる一方で、12 時の方向から入射した光を透過させる。 10

#### 【0176】

この構成において、ヘッドマウント・ディスプレイ 300 の装着者は、電気光学装置 1L、1R による表示画像を、外の様子と重ね合わせたシースルーハーフミラー状態で観察することができる。

また、このヘッドマウント・ディスプレイ 300 において、視差を伴う両眼画像のうち、左眼用画像を電気光学装置 1L に表示させ、右眼用画像を電気光学装置 1R に表示させると、装着者に対し、表示された画像があたかも奥行きや立体感を持つかのように知覚させることができる（3D 表示）。

#### 【0177】

なお、電気光学装置 1 については、ヘッドマウント・ディスプレイ 300 のほかにも、ビデオカメラやレンズ交換式のデジタルカメラなどにおける電子式ビューファインダーにも適用可能である。 20

#### 【符号の説明】

#### 【0178】

1、1L、1R … 電気光学装置、2 … 表示パネル、3 … 制御回路、5 … データ線駆動回路、6 … 走査線駆動回路、12 … 走査線、14-1 … 第 1 データ転送線、14-2 … 第 2 データ転送線、16 … 給電線、31 … 電圧生成回路、34 … トランスマッショングート、41 … 保持容量、42 … トランスマッショングート、45 … トランスマッショングート、70 … データ信号供給回路、100 … 表示部、110 … 画素回路、116 … 給電線、118 … 共通電極、121、122、123、124、125、126 … トランジスター、130 … OLED、130a … アノード、132 … 画素容量、133 … 転送容量、143、144、145、146 … 制御線、300 … ディスプレイ、301L、301R … レンズ、302L、302R … 光学レンズ、303L、303R … ハーフミラー、310 … テンプル、320 … ブリッジ、DM … デマルチブレクサ、DT … データ転送回路。 30

【図1】

【図2】

【図3】

【図4】

【 図 5 】

【図6】

【図8】

【図7】

【図9】

【図10】

### 【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【 図 1 9 】

### 【図20】

### 【図21】

## 【図22】

【図23】

【図24】

【図25】

## 【図26】

【図27】

【図28】

【図29】

【図30】

【 図 3 1 】

### 【図3-2】

### 【図33】

〔 囮 3 4 〕

【図35】

---

フロントページの続き

(51)Int.Cl.

| F I     |       |         |   |

|---------|-------|---------|---|

| G 0 9 G | 3/20  | 6 1 1 J |   |

| G 0 9 F | 9/30  | 3 6 5   |   |

| H 0 5 B | 33/14 |         | A |

審査官 中村 直行

(56)参考文献 特開2013-213979 (JP, A)

特開2001-156641 (JP, A)

特開2010-243610 (JP, A)

特開2014-029423 (JP, A)

特開2015-043030 (JP, A)

特開2011-008053 (JP, A)

特開2010-243611 (JP, A)

米国特許出願公開第2013/0120338 (US, A1)

米国特許出願公開第2014/0312326 (US, A1)

韓国公開特許第10-2013-0055450 (KR, A)

(58)調査した分野(Int.Cl., DB名)

|         |           |   |           |

|---------|-----------|---|-----------|

| G 0 9 F | 9 / 0 0   | - | 9 / 4 6   |

| G 0 9 G | 3 / 0 0   | - | 3 / 3 8   |

| H 0 1 L | 5 1 / 5 0 |   |           |

| H 0 1 L | 2 7 / 3 2 |   |           |

| H 0 5 B | 3 3 / 0 0 | - | 3 3 / 2 8 |