RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 480 481**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 80 07913**

(54) Dispositif pour la mémorisation d'états logiques de processus.

(51) Classification internationale (Int. Cl.<sup>3</sup>). G 11 C 7/00; G 06 F 13/00; G 11 C 9/04.

(22) Date de dépôt..... 9 avril 1980.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 42 du 16-10-1981.

(71) Déposant : COMPAGNIE INTERNATIONALE POUR L'INFORMATIQUE CII-HONEYWELL BULL

(dite : CII-HB), résidant en France.

(72) Invention de : Michel Ugon et Robert Jean Louis Anthime Hervé.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Georges Lincot, Compagnie Internationale pour l'Informatique CII-Honeywell Bull,

94, av. Gambetta, 75960 Paris Cedex 20.

- 1 -

"DISPOSITIF POUR LA MEMORISATION D'ETATS LOGIQUES DE PROCESSUS"

La présente invention concerne un dispositif électronique permettant de mémoriser les états logiques de processus au cours de leur déroulement dans le temps.

5

Il est connu des mémoires à accès protégé dont le but principal est de mémoriser des informations confidentielles ou secrètes. L'accès dans ces mémoires est contrôlé par des logiques spécialisées qui 10 s'interposent entre celles-ci et le milieu extérieur. Un exemple de réalisation d'une logique d'accès est décrit dans la demande de brevet n° 77.26.107 déposée au nom de la demanderesse. Dans cette demande la logique d'accès est constituée d'un microprocesseur, 15 l'accès est obtenu sur présentation d'un mot de passe correct.

Dans beaucoup d'applications, il est nécessaire de mémoriser le nombre d'erreurs, le nombre d'accès ou 20 d'apparition d'évènements illégaux. Dans les exemples de réalisation les plus connus, la façon habituelle d'enregistrer de tels évènements consiste à les enregistrer dans une mémoire permanente ou de les compter à l'aide de compteurs spécialisés utilisant une

- 2 -

mémoire effaçable électriquement. Une description de ces dispositifs est donnée dans la demande de brevet n° 79.17.171 déposée également au nom de la demanderesse.

5

Cette méthode présente au moins trois inconvénients. En premier lieu, elle nécessite une occupation de la mémoire importante, en deuxième lieu la capacité de comptage est limitée à la capacité maximale du compteur 10 et ne peut être modifiée même s'il reste de la place disponible dans la mémoire, et enfin le nombre d'évènements enregistrés dans les mémoires permanentes ne peut être ni diminué, ni annulé.

15 Le but de la présente invention est d'éliminer ces inconvénients en supprimant les différentes zones de comptage décrites dans les deux demandes précitées et en leur substituant une mémoire permanente ou non, désignée ci-après par "mémoire d'états" dans laquelle 20 toute la capacité de la mémoire peut être utilisée et où le passage d'un état de processus à un autre s'effectue par simple examen de la mémoire d'états.

25 Le dispositif de mémorisation d'états logiques selon l'invention est caractérisé en ce qu'il comprend des moyens pour mémoriser dans une "mémoire d'états", irréversible ou non, des suites de configurations binaires correspondant à chaque état logique, la longueur des configurations variant en fonction des 30 types d'états que peuvent prendre un processus et étant d'autant plus courte qu'elle correspond à des états pouvant être les plus fréquemment rencontrés. Selon un mode préféré de réalisation de l'invention tous les états successifs que peut prendre un processus sont

- 3 -

écrits et analysés par les moyens de mémorisation dans la mémoire d'états à travers une "fenêtre glissante d'écriture-lecture" ayant une longueur fixe et dont l'adresse de début est située à un nombre entier de positions binaires prédéterminées. Cette fenêtre est positionnée en outre dans la mémoire d'états, de façon que tous les chiffres binaires la précédant soient dans le même état et que tous ceux qui la suivent, soient dans l'état opposé, les chiffres binaires situés à l'intérieur de la fenêtre elle-même pouvant revêtir n'importe quelle combinaison. Dans le mode préféré de réalisation de l'invention la fenêtre est divisée en différents champs. La position des champs étant d'autant plus proche du début de la fenêtre qu'ils correspondent à des états pouvant se réaliser les plus fréquemment de façon à réduire les configurations binaires utiles.

L'invention sera mieux comprise à l'aide de la description faite au regard des dessins qui va suivre.

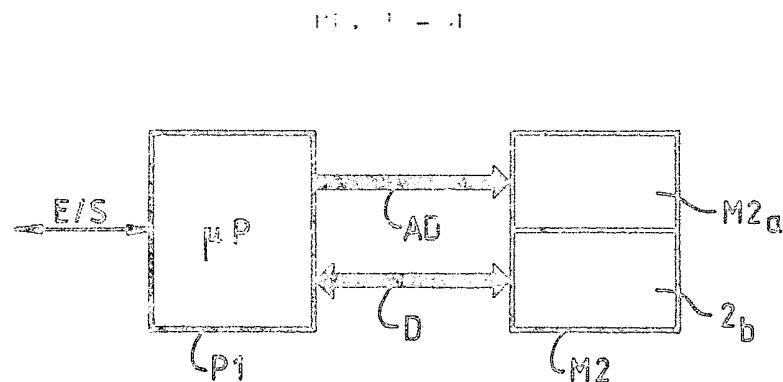

La figure 1 est une représentation simplifiée du dispositif incorporant l'invention.

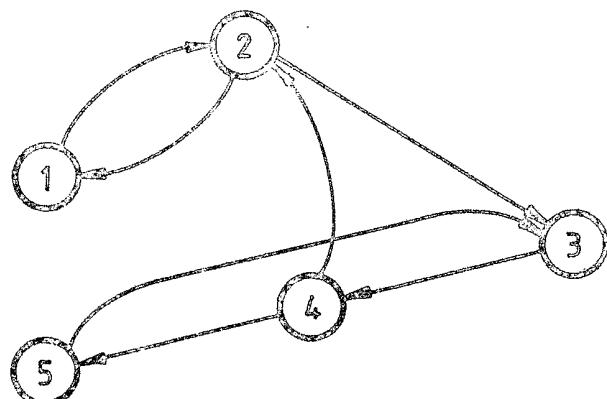

La figure 2 représente un diagramme d'états d'un processus.

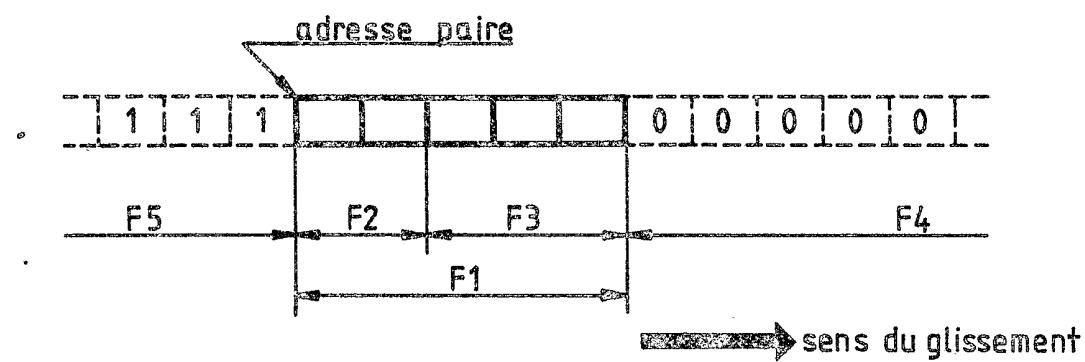

La figure 3 est une représentation de la fenêtre d'états.

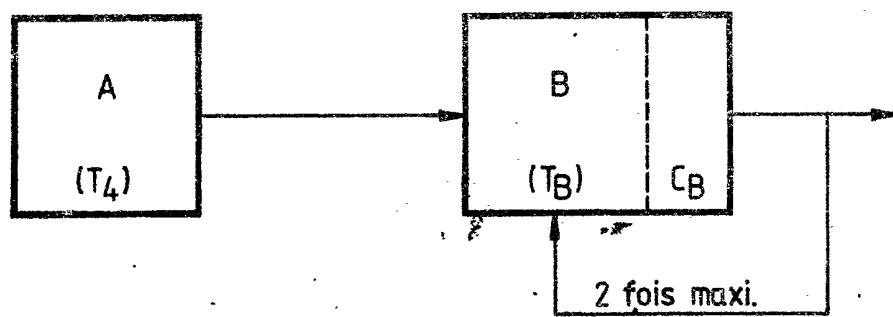

La figure 4 est un bloc diagramme illustrant le déroulement d'un processus industriel auquel peut s'appliquer l'invention.

- 4 -

La figure 5 représente un graphe des états du processus industriel illustré à la figure 4.

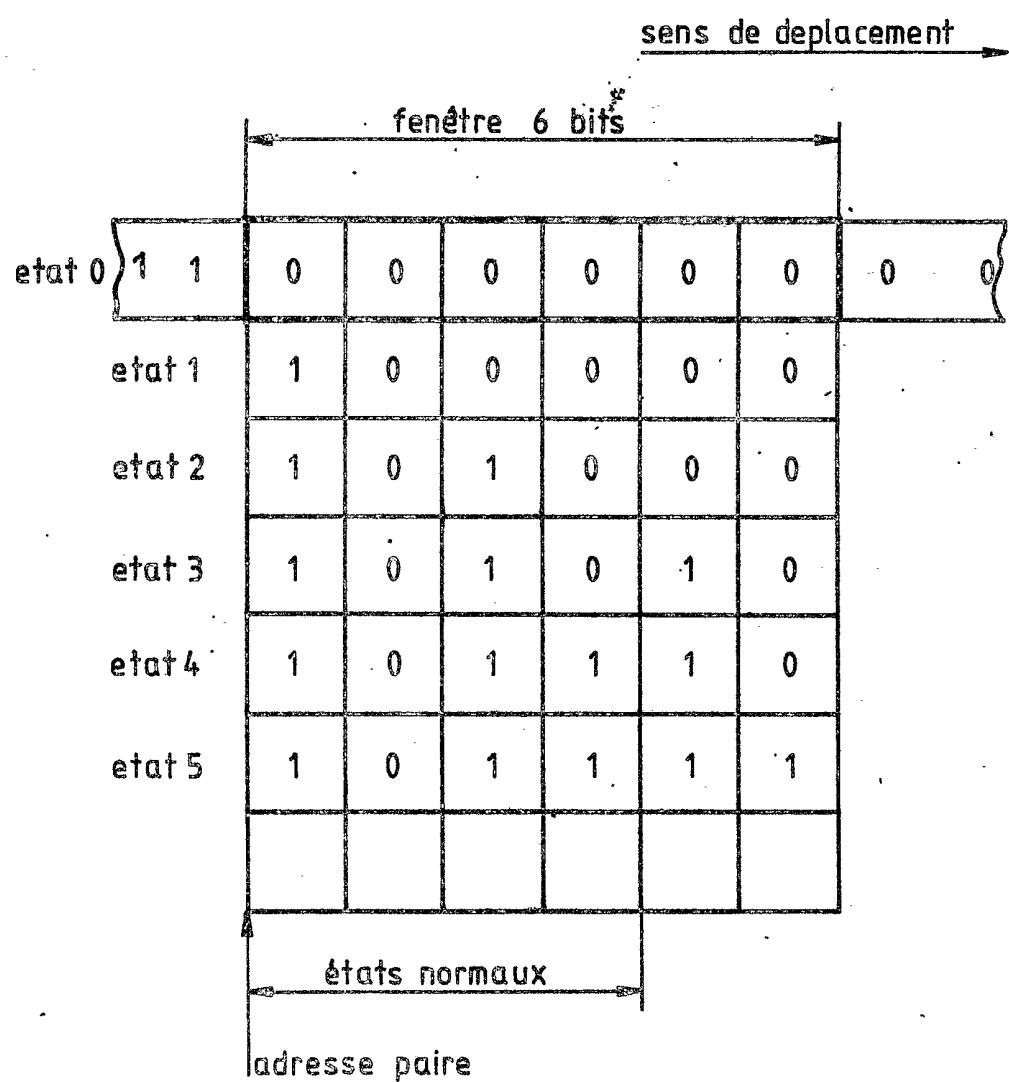

5 La figure 6 représente une table des configurations binaires utilisée pour le codage des états de la figure 5.

La figure 7 montre une réalisation du dispositif de mémorisation selon l'invention.

10 Le dispositif incorporant l'invention montré à la figure 1 se compose d'une logique de commande P<sub>1</sub> qui commande les accès à la mémoire M<sub>2</sub> en lecture comme en écriture par l'intermédiaire de ses bus d'adresse AD et 15 données D. Une réalisation possible de l'invention pourra s'effectuer à l'aide du microprocesseur décrit dans la demande de brevet n° 78.12.119 déposée au nom de la demanderesse.

20 L'accès du milieu extérieur à la mémoire s'effectue à l'aide de la porte spécialisée d'entrée-sortie E/S. La mémoire M<sub>2</sub> est partagée en deux zones, une zone de travail M<sub>2a</sub> et une zone réservée à la mémoire d'états M<sub>2b</sub>.

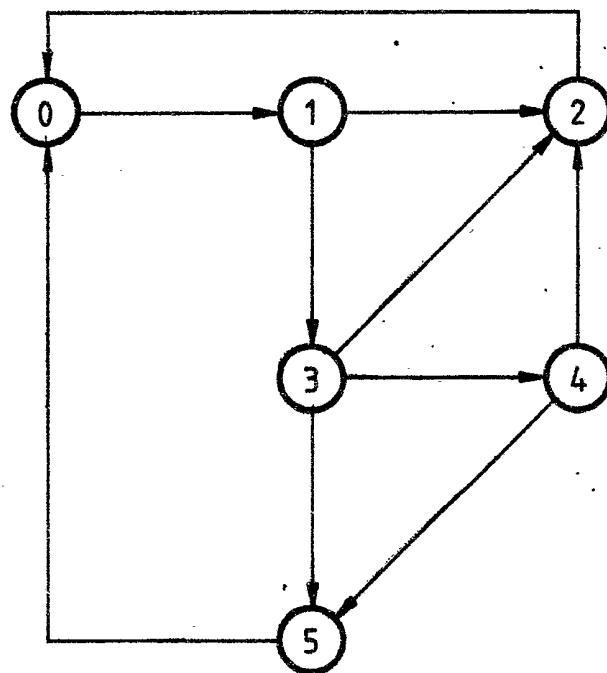

25 La figure 2 illustre le fonctionnement du dispositif de mémorisation d'état logique dans une application particulière où le processus contrôlé présente 5 états stables. Ce graphe fait apparaître les règles de 30 changement d'état du processus. Seules les transitions suivantes sont autorisées.

Estat 1 vers Etat 2

Estat 2 vers Etat 1

- 5 -

Estat 2 vers Etat 3

Estat 3 vers Etat 4

Estat 4 vers Etat 2

Estat 4 vers Etat 5

5                   Estat 5 vers Etat 3.

Parmi les 5 états possibles du processus représentés à la figure 2 un certain nombre peut être considéré comme obtenu séquentiellement au cours d'un fonctionnement normal (Etat 1 et 2 par exemple) alors que les états restants 3, 4 et 5 sont obtenus par exception, lorsqu'un évènement (externe) anormal se produit. Le principe de l'invention consiste à mémoriser l'état présent du processus dans la mémoire d'état M<sub>2b</sub> de la figure 1 à l'intérieur d'une zone F (ou fenêtre), de 5 bits consécutifs comme cela est représenté à la figure 3. On comprendra que l'exemple qui est décrit ici ne se limite pas à contrôler un processus limité à 5 états possibles, pour un processus à n états la zone de mémoire F devrait comporter au plus n bits consécutifs. La zone F, constitue une fenêtre de mémoire qui peut être lue et écrite à l'aide de la logique de commande P<sub>1</sub>. La fenêtre F<sub>1</sub> est précédée d'une zone totalement vierge F<sub>4</sub> et suivie d'une zone totalement écrite F<sub>(5)</sub>, comme cela sera expliqué plus loin, la fenêtre est déplaçable dans un seul sens dans la mémoire d'états. Dans l'exemple de la figure 3, la zone F<sub>4</sub> ne contient que des bits dans l'état 0 alors que ceux de la zone F<sub>5</sub> se trouvent tous à l'état 1.

30

La fenêtre F<sub>1</sub> se décompose en deux zones, une zone F<sub>2</sub> d'états normaux (2 bits) et une zone F<sub>3</sub> d'états anormaux (3 bits). Dans le cas présent, l'adresse de début de la fenêtre est toujours paire dans la mémoire

- 6 -

d'états comme cela sera expliqué plus loin. D'après ce qui précède, la convention suivante est adoptée pour coder les états normaux.

- |   |                                  |                                                                                    |

|---|----------------------------------|------------------------------------------------------------------------------------|

| 5 | Fenêtre matérialisant l'état 1   |  |

|   | Fenêtre matérialisant l'état 2   |  |

|   | Retour de l'état 2 dans l'état 1 |  |

De cette façon le retour à l'état 1 en partant de l'état 2 est possible par glissement de la fenêtre à l'adresse paire suivante et écriture d'un bit.

Dans le cas des états anormaux, les codes adoptés peuvent être les suivants :

- 20 Dans ces conditions le passage de l'état 4 à l'état 2 s'effectue en écrivant 2 bits et en décalant la fenêtre de 4 positions binaires.

De même le passage de l'état 5 à l'état 3 s'obtient en écrivant 2 bits et en décalant la fenêtre de 4 positions binaires.

Selon ce principe, la fenêtre  $F_1$  glisse d'une longueur de 2 bits dans le passage d'un état normal à un autre état normal et de 4 bits entre un état quelconque et un état anormal ou réciproquement.

L'adresse de la fenêtre est cadrée à gauche sur la première paire de configurations binaires rencontrée en

- 7 -

balayant la mémoire d'états de gauche à droite.

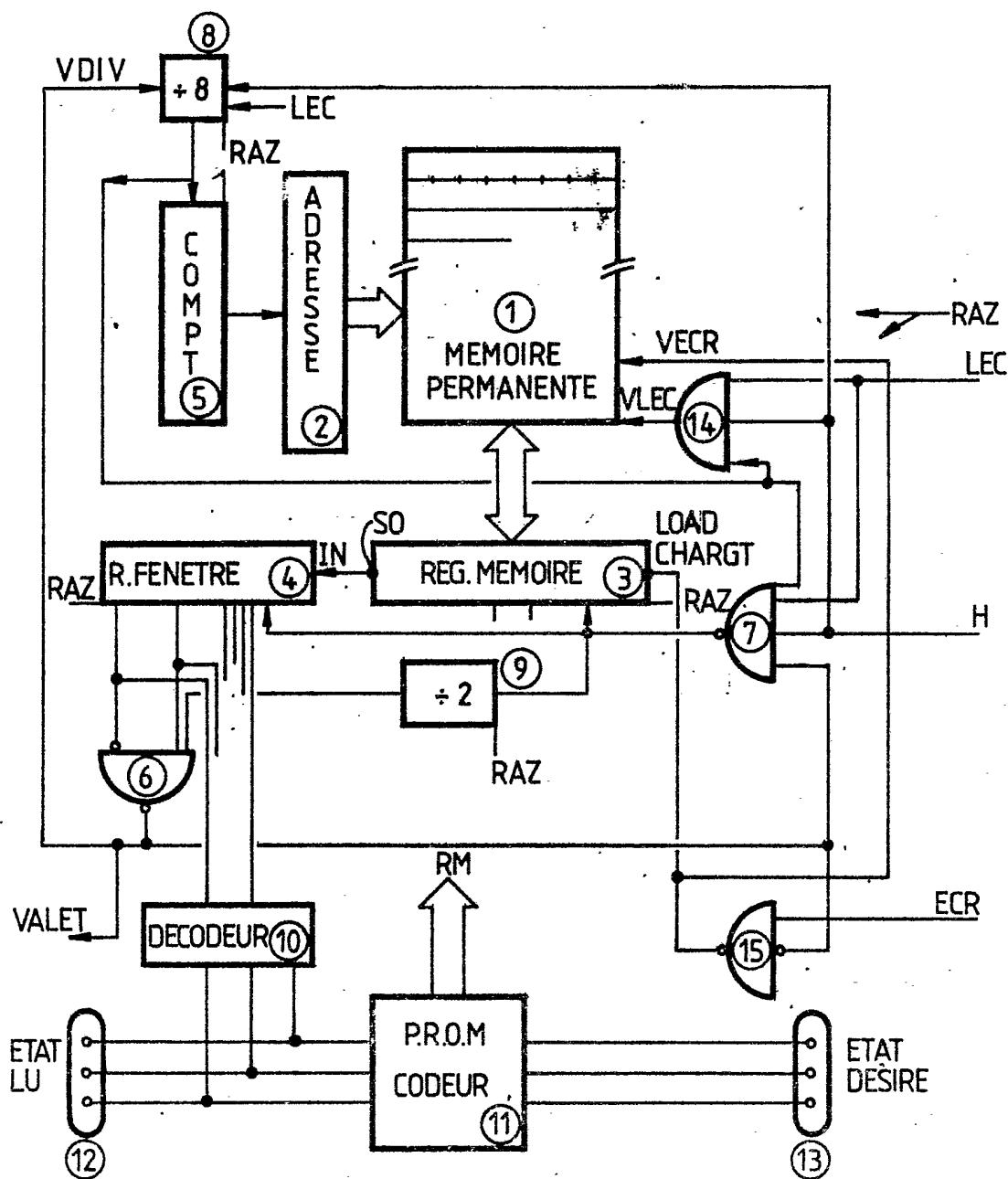

La réalisation du dispositif de mémorisation conformément au principe qui vient d'être décrit est montrée sur la figure 7. Ce dispositif comprend une mémoire permanente 1 effaçable ou non de types FAMOS, PROM, MNOS ou équivalents. Ces types de mémoire sont décrits dans le livre intitulé "les microprocesseurs, techniques et applications" par RODNAY ZAKS et PIERRE LE BEUX édité par SYBEX 313 rue Lecourbe 75015 PARIS. La mémoire 1 est adressée par le registre d'adresse 2. Les données à écrire ou à lire dans la mémoire 1 sont recueillies dans un registre de données bidirectionnel 3 monté en registre à décalage. La sortie S0 du registre 3 est reliée à l'entrée IN d'un autre registre à décalage 4 destiné à recevoir la fenêtre d'analyse des états de processus selon l'invention. Les sorties parallèles de ce registre d'état 4 sont appliquées à l'entrée d'un décodeur d'états 10 dont les sorties sont reliées à un codeur 11. Le codeur 11 peut être réalisé à l'aide de mémoires type PROM ou ROM, sa fonction est de déterminer le codage de la fenêtre d'état en fonction de l'état décodé par le décodeur 10 après l'opération de lecture de la mémoire 1 et de l'état désiré que l'on veut obtenir. L'état lu dans la mémoire 1 et traduit par le décodeur 10 apparaît sur les sorties 12 du dispositif. L'état désiré qui est transmis de l'extérieur du dispositif par les entrées 13. Les entrées du registre d'adresses 2 sont directement reliées aux sorties d'un compteur 5 dont la progression est assurée par les signaux délivrés par un diviseur d'impulsions 8 de rapport 8. Le diviseur 8 compte les impulsions d'horloge qui sont appliquées à son entrée lorsqu'elles sont validées par la sortie de

- 8 -

la porte 6 et le signal LEC (lecture) appliqué de l'extérieur du dispositif. Le diviseur par 8 permet l'adressage d'octets dans la mémoire 1. La porte 6 est connectée respectivement par deux de ses entrées, une 5 entrée normale et une entrée complémentée, aux deux sorties poids fort du registre fenêtre 4 et est connectée par une troisième entrée à un diviseur 9 de rapport 2, dont l'entrée reçoit les impulsions d'horloge 4 délivrées par la porte "non et" 7, qui les 10 retransmet également sur les entrées d'horloge des registres à décalage 3 et 4, pour assurer le décalage à gauche des informations contenues dans ces registres. La porte "non et" 7 est connectée, par une entrée à la 15 sortie du diviseur 8, par une entrée à la liaison de commande de lecture provenant de l'extérieur du dispositif, par une autre entrée à la liaison transmettant le signal d'horloge H et provenant de l'extérieur du dispositif et par une dernière entrée à la 20 sortie de la porte 6 générant le signal VALET. La mémoire 1 est commandée en lecture par le signal VLEC émis par la sortie de la porte "non et" 14 qui est connectée, par une première entrée à la sortie du diviseur 8, par une deuxième entrée à la liaison 25 d'horloge H qui reçoit sur une troisième entrée le signal de lecture LEC. La mémoire 1 est commandée en écriture par la sortie de la porte "non et" 15 qui reçoit sur une première entrée le signal ECR d'écriture transmis de l'extérieur du dispositif et sur une 30 deuxième entrée le signal VALET émis par la sortie de la porte 6. La sortie de la porte 15 commande également le chargement du registre de mémoire 3. Le signal RAZ est transmis de l'extérieur du dispositif et assure la remise à zéro de l'ensemble des registres diviseurs et compteurs du dispositif.

- 9 -

- Le fonctionnement du dispositif est le suivant : au départ une remise à zéro générale initialise les compteurs, diviseurs et registres du dispositif. Deux types de fonctionnement peuvent avoir lieu. Le premier peut consister à lire l'état d'un processus mémorisé dans le dispositif. Dans ce cas, le registre fenêtre 4 étant au départ à zéro, la sortie de la porte 6 délivre un signal à l'état 1 logique qui valide la porte 7. Dès que le signal de lecture LEC est appliqué le registre de mémoire 3 est chargé par le premier octet sortant de la mémoire pendant le premier pas d'horloge H grâce à la porte 14. Les sept impulsions d'horloge suivantes n'ont pas d'autres effets que de faire progresser le diviseur 8. Les huit impulsions suivantes décalent le registre 3 dans le registre 4, dont les deux positions de bits de poids forts sont testées en permanence par la porte 6 validée par le diviseur par deux 9. Deux cas peuvent alors se présenter.

- 20      1er cas : La porte 6 ne détecte aucune coïncidence et l'octet lu de la mémoire ne correspond pas à la fenêtre d'état recherchée, dans ce cas le deuxième mot (octet) est chargé dans le registre 3 et le processus se poursuit.

- 25      2ème cas : Une coïncidence est détectée par la porte 6, la porte 7 ainsi que le diviseur 8 sont alors bloqués et arrêtés par le signal VALET. En conséquence, le compteur 5 n'évolue plus, figeant l'adresse contenue dans le registre 2 ainsi que la valeur de la fenêtre contenue dans le registre fenêtre 4. Le décodeur 10 établit alors une correspondance numérique entre la configuration binaire dans le registre 4 et l'état lu

- 10 -

dans la mémoire. Bien entendu cet état ne pourra être pris en compte par le milieu extérieur au dispositif que sur validation du signal VALET.

5 Le deuxième type de fonctionnement est celui de l'écriture dans la mémoire 1 mais son existence est subordonnée à l'exécution au préalable de la séquence de lecture décrite précédemment. Il suffira alors d'appliquer l'indicatif de l'état désiré en 13. Cet

10 état constitue l'entrée d'une partie de l'adresse du codeur 11, réalisé par exemple avec une mémoire PROM, qui en fonction de l'état lu délivré par le décodeur 10 constituant la deuxième partie d'adresse, délivre la configuration binaire à écrire dans le registre de mémoire 3. Cette configuration binaire est envoyée en

15 parallèle dans le registre 3 sur l'ordre d'écriture ECR qui doit subsister le temps nécessaire lié à la technologie de la mémoire. La réalisation du dispositif qui vient d'être décrit pourra être exécutée en

20 utilisant les procédés de fabrication de composants électroniques à haute intégration type LSI de façon à rendre le dispositif aisément transportable. Une application du dispositif qui vient d'être décrit peut être la suivante.

25

Il existe de nombreux cas où il est nécessaire de contrôler qu'un certain nombre d'actions ont été effectuées dans un ordre déterminé avec possibilité de "retour en arrière", c'est-à-dire qu'il est possible de recommencer l'une des actions, si celle-ci n'a pas été exécutée correctement ou d'éliminer des cas marginaux.

30

Un exemple peut être donné par le suivi de pièces devant subir des traitements divers en des lieux

- 11 -

differents.

Considérons le cas de plusieurs usines spécialisées participant à la réalisation d'un produit P (voir 5 figure 4) réalisé suivant un processus de façon sûre, c'est-à-dire subir avec certitude un enchaînement donné d'opérations.

Dans l'exemple simple qui va suivre P doit subir dans 10 l'usine A une transformation  $T_A$ , par exemple un usinage sur une machine spéciale.

P doit ensuite être traité chimiquement dans l'usine B qui possède un centre d'analyse ( $C_B$ ). Si cette analyse 15 est négative la pièce doit subir à nouveau le traitement, et ceci, deux fois de suite au maximum, après quoi la pièce est définitivement rebutée.

Le contrôle physique d'un grand nombre de pièces 20 transitant entre les différents postes peut être avantageusement fait par un support électronique mémorisant les états de la pièce auquel il est associé.

On voit facilement sur cet exemple simple que le 25 cheminement de la pièce peut être caractérisé par 5 états (figure 5).

Le support enregistre à chaque stade, dans sa mémoire permanente l'avancement de la pièce. L'enregistrement 30 proprement dit étant fait par une machine d'écriture connectée au support.

Dans le cas qui nous occupe, les 5 états sont les suivants :

- 12 -

- |   |         |                                           |

|---|---------|-------------------------------------------|

|   | Estat 0 | Etat de départ - Pièce non traitée        |

|   | Estat 1 | Pièce traitée en A                        |

|   | Estat 2 | Pièce traitée en B acceptée               |

|   | Estat 3 | Pièce refusée une fois en C <sub>B</sub>  |

| 5 | Estat 4 | Pièce refusée deux fois en C <sub>B</sub> |

|   | Estat 5 | Pièce rebutée.                            |

Ces cinq états peuvent être enregistrés suivant la méthode décrite précédemment dans la mémoire permanente

10 par l'intermédiaire de la machine d'écriture.

Lorsque la pièce a atteint la fin du traitement, le support correspondant peut être affecté à une autre pièce (retour à l'état 0) et le cycle peut être exécuté

15 à nouveau.

Les configurations binaires utilisées sont représentées figure 6.

20 La fenêtre possède une largeur de 6 bits pour analyser la mémoire.

On voit donc sur cet exemple, et en reprenant le graphe des états de la figure 5 que le nombre de bits à écrire

25 pour passer d'un état dans un autre est donné par le tableau suivant

| <u>Sens</u> | 0 | 1 | 2 | 3 | 4 | 5 |

|-------------|---|---|---|---|---|---|

| <u>De</u>   | 0 | 1 | - | - | - | - |

| 1           | - | 0 | 1 | 2 | - | - |

| 2           | 2 | - | 0 | 1 | - | - |

| 3           | - | - | 1 | 0 | 1 | 2 |

| 4           | - | - | 2 | - | 0 | 1 |

| 5           | 1 | 1 | - | - | - | 0 |

- 13 -

Ceci montre :

- que le passage d'un état dans un autre est caractérisé par l'écriture de 2 bits au maximum

- 5 - que les états normaux 0, 1 et 2 n'utilisent que 4 bits de la mémoire

- que les états anormaux utilisent 6 bits

- les retours aux états antérieurs 0 et 2 s'effectuent par des décalages de la fenêtre de 2, 4 et 6 bits.

10

Il va de soi que le mode de réalisation qui vient d'être donné de l'invention n'est nullement limitatif, l'homme de l'art pourra concevoir d'autres dispositifs de structures différentes mais ayant des fonctions identiques à celles décrites dans la présente demande. En particulier, ces fonctions pourront être réalisées à l'aide de logique microprogrammable ou programmable sans que l'idée même de l'invention s'en trouve modifiée.

15

## REVENDICATIONS

1. Dispositif pour la mémorisation d'états logiques d'un processus comprenant une mémoire 1 associée à des moyens d'écriture et de lecture d'informations dans ladite mémoire, lesdites informations étant 5 représentatives de l'état du processus, ladite mémoire étant adressée à partir d'un registre d'adresse 2 et étant connectée au registre de mémoire 3 pour recevoir le contenu d'une information à écrire ou à lire en mémoire aux emplacements sélectionnés par les moyens 10 d'adressage 2 caractérisé en ce qu'il comprend des moyens de codage 11 des états possibles du processus, les états d'un processus codé par les moyens de codage étant représentés dans la forme d'une suite de configurations binaires de longueur variable en 15 fonction de chaque état, les longueurs desdites configurations étant d'autant plus courtes qu'elles correspondent à des états possibles du processus se produisant le plus fréquemment.

- 20 2. Dispositif selon la revendication 1 caractérisé en ce que les états successifs du processus sont écrits et analysés dans ladite mémoire 1 au moyen d'une fenêtre glissante d'écriture lecture ayant une longueur fixe et dont l'adresse de début est représentée par un nombre 25 entier de positions binaires prédéterminées, cette fenêtre étant située dans la mémoire de façon que tous les chiffres binaires la précédant soient dans le même état et que tous ceux qui la suivent soient dans l'état opposé; le contenu de la fenêtre pouvant avoir une 30 configuration binaire mixte c'est à dire différente des

- 15 -

deux précédentes.

3. Dispositif selon la revendication 2 caractérisé en ce que la fenêtre F d'écriture lecture est divisée elle même en différents champs, la position des champs étant d'autant plus proche du début de la fenêtre qu'ils correspondent à des états plus fréquents de façon à réduire la longueur des configurations binaires utiles.

5

- 10 4. Dispositif selon la revendication 3 caractérisé en ce que les champs de la fenêtre sont codés de façon que les positions binaires utilisées dans chacun des champs soient d'autant plus proches du début du champ qu'elles se rapportent à des états plus fréquents.

15

- 20 5. Dispositif selon la revendication 1 caractérisé en ce que les moyens de codage 11 des états possibles du processus ont leurs sorties directement reliées au registre mémoire 3 et sont commandés sur leurs entrées d'une part par les signaux représentatifs de l'état du processus lu dans ladite fenêtre et d'autre part, à partir des signaux représentatifs de l'état réel du processus qui est à mémoriser à l'intérieur de ladite fenêtre, de façon à mettre à jour l'état de la fenêtre située à l'intérieur de ladite mémoire (1).

25

- 30 6. Dispositif selon les revendications 1 et 5 caractérisé en ce que ledit registre mémoire 3 est relié à des moyens de détection 4 et 6 de la présence de ladite fenêtre dans le registre de mémoire 3 pour transmettre l'état du processus lu dans ladite fenêtre à l'entrée desdits moyens de codage 11.

7. Dispositif selon la revendication 6 caractérisé en

- 16 -

ce que lesdits moyens de détection sont constitués,

d'un registre fenêtre 4 recopiant l'état du registre de

mémoire 3, associé à des moyens de détection 6 des bits

d'information de poids forts situés à l'intérieur de

5 ladite fenêtre.

FIG.1

FIG.2

FIG.3

PL. IT - 0

FIG.4

FIG.5

PL. III - 4

FIG.6

PL. IV - 4

FIG.7