(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6664259号

(P6664259)

(45) 発行日 令和2年3月13日(2020.3.13)

(24) 登録日 令和2年2月20日(2020.2.20)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| HO4N 5/3745 (2011.01) | HO4N 5/3745 200 |

| HO4N 5/357 (2011.01)  | HO4N 5/357      |

| HO4N 5/225 (2006.01)  | HO4N 5/225 300  |

| GO3B 15/00 (2006.01)  | GO3B 15/00 V    |

請求項の数 14 (全 20 頁)

(21) 出願番号 特願2016-72990(P2016-72990)

(22) 出願日 平成28年3月31日(2016.3.31)

(65) 公開番号 特開2017-184185(P2017-184185A)

(43) 公開日 平成29年10月5日(2017.10.5)

審査請求日 平成31年3月23日(2019.3.23)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 落合 慧

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 小林 秀央

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

審査官 鈴木 明

最終頁に続く

(54) 【発明の名称】撮像装置、撮像システム、および、移動体

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換によって生じた電荷を受ける入力ノードを有し、前記入力ノードの電圧に基づく信号を出力する出力部と、

オンとオフとに制御され、前記オンのときに前記入力ノードの電圧をリセットするリセット部と、

制御信号を受けるゲート電極を有し、前記制御信号に応じて前記入力ノードの容量を第1の容量値と前記第1の容量値より大きい第2の容量値とに制御する制御部と、をそれぞれが含む複数の画素ユニットを備え、

前記入力ノードの容量が前記第1の容量値である状態で、前記出力部が前記信号を出力する第1のモードと、

前記入力ノードの容量が前記第2の容量値である状態で、前記出力部が前記信号を出力する第2のモードと、を有し、

前記第1のモードにおいて、

前記リセット部が前記オンである状態で、前記制御部が前記入力ノードの容量を前記第2の容量値から前記第1の容量値に切り替え、その後、前記入力ノードの容量が前記第1の容量値である状態で、前記リセット部が前記オンから前記オフに制御される動作と、

前記リセット部が前記オフである状態で、前記制御部が前記入力ノードの容量を前記第1の容量値から前記第2の容量値に切り替え、その後、前記入力ノードの容量が前記第2の容量値である状態で、前記リセット部が前記オフから前記オンに制御されるリセット動

10

20

作と、

前記リセット動作の後に、前記入力ノードの容量が前記第1の容量値である状態で前記出力部が前記信号を出力する出力動作と、を行う、

ことを特徴とする撮像装置。

【請求項2】

前記第2のモードにおいて、

前記入力ノードの容量が前記第2の容量値に制御された状態で前記リセット部が前記オフから前記オンに制御される第2のリセット動作と、

前記第2のリセット動作の後に、前記入力ノードの容量が前記第2の容量値である状態で前記出力部が前記信号を出力する第2の出力動作と、を行い、

前記第2のリセット動作から前記第2の出力動作までの間、前記入力ノードの容量が前記第2の容量値に維持される、

ことを特徴とする請求項1に記載の撮像装置。

【請求項3】

前記複数の画素ユニットのそれぞれが、前記電荷を前記入力ノードに転送する転送部を備え、

前記出力動作は、

前記電荷が転送される前に、前記出力部が第1の信号を出力する第1の出力動作と、

前記電荷が転送された後に、前記出力部が第2の信号を出力する第2の出力動作と、を含む、

ことを特徴とする請求項1または請求項2に記載の撮像装置。

【請求項4】

前記複数の画素ユニットのそれぞれが、複数の光電変換部を含み、

前記入力ノードが、前記複数の光電変換部のそれぞれで生じた電荷を受ける、

ことを特徴とする請求項1乃至請求項3のいずれか一項に記載の撮像装置。

【請求項5】

前記複数の光電変換部が、単一のマイクロレンズの下に配される、

ことを特徴とする請求項4に記載の撮像装置。

【請求項6】

前記複数の光電変換部それぞれで生じた電荷が、前記入力ノードにおいて加算される、

ことを特徴とする請求項5に記載の撮像装置。

【請求項7】

前記複数の光電変換部のそれぞれが、互いに異なるマイクロレンズの下に配される、

ことを特徴とする請求項4に記載の撮像装置。

【請求項8】

前記複数の画素ユニットは、前記複数の複数の列を構成するように配置され、

前記複数の列の1つに対応して、複数の出力線が配される、

ことを特徴とする請求項1乃至請求項7のいずれか一項に記載の撮像装置。

【請求項9】

前記複数の出力線は、少なくとも第1の出力線と、第2の出力線とを含み、

前記複数の画素ユニットのそれぞれは、前記出力部と前記第1の出力線とを接続する第1の選択トランジスタと、前記出力部と前記第2の出力線とを接続する第2の選択トランジスタと、を含む、

ことを特徴とする請求項8に記載の撮像装置。

【請求項10】

前記の出力線に対応した複数の列回路を含み、

前記複数の列回路の間に、前記複数の画素ユニットが配置される、

ことを特徴とする請求項8または請求項9に記載の撮像装置。

【請求項11】

前記入力ノードを構成する第1導電型のフローティングディフュージョン領域と、

10

20

30

40

50

前記フローティングディフュージョン領域の隣に配された第2導電型の半導体領域と、を備え、

前記ゲート電極は、前記半導体領域の上に絶縁膜を介して配置される、ことを特徴とする請求項1乃至請求項10のいずれか一項に記載の撮像装置。

**【請求項12】**

前記容量は、PN接合の容量成分を含むことを特徴とする請求項1乃至請求項11のいずれか一項に記載の撮像装置。

**【請求項13】**

請求項1乃至請求項12のいずれか一項に記載の撮像装置と、

前記撮像装置からの信号を処理する信号処理装置と、を備えた撮像システム。

10

**【請求項14】**

移動体であって、

請求項1乃至13のいずれか一項に記載の撮像装置と、

前記撮像装置からの信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と、を有することを特徴とする移動体。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

20

本発明は撮像装置、撮像システム、および、移動体に関する。

**【背景技術】**

**【0002】**

特許文献1に記載の撮像装置は複数の画素を備える。各画素は、光電変換により生じた電荷を保持するフローティングディフュージョン領域(以下、FD領域)と、当該FD領域で電荷電圧変換された電圧を增幅して出力する增幅部とを含む。

**【0003】**

特許文献1の撮像装置は、さらに、異なる画素に含まれる複数のFD領域の間の接続および非接続を制御するFD接続トランジスタを備える。個々のFD領域の容量値と比べて、互いに接続された複数のFD領域からなるノードの容量値は大きい。つまり、FD接続トランジスタが複数のFD領域を互いに接続することで、FD領域の容量値を変化させることができる。FD領域での電荷電圧変換係数は当該FD領域の容量値に基づいて決まる。そのため、特許文献1の撮像装置においては、FD接続トランジスタのオンおよびオフに応じて、撮像時のゲインを変えることができる。

30

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献1】特開2010-193437号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

40

**【0005】**

撮像装置の動作において、一般に、画素からの信号を出力する前にFD領域の電圧がリセットされる。FD領域の電圧をリセットするリセット動作は、リセットトランジスタがオンすることによって行われている。特許文献1の撮像装置は、特許文献1の図3に示されるように、FD接続トランジスタがオフの状態で信号を出力するモードを持つ。そのモードにおいてFD領域の電圧をリセットする際に、FD接続トランジスタをオンしている。

**【0006】**

しかしながら、特許文献1は、リセットトランジスタをオンするタイミングと、FD接続トランジスタをオンするタイミングとの関係について、明確に開示していない。本発明

50

者らは、リセットトランジスタをオンするタイミングと、F D接続トランジスタをオンするタイミングとの関係次第で、ノイズが生じる可能性があるという課題を見出した。

#### 【0007】

例えば、リセットトランジスタとF D接続トランジスタとが同時にオンすると、各トランジスタのゲートとF D容量とのカップリングのために、F D領域の電圧が大きく変動する。トランジスタの動作に伴ってF D領域の電圧が大きく変動すると、F D領域の電圧を正確にリセットすることができない可能性がある。結果として、正確な信号を出力することが困難となる。

#### 【0008】

あるいは、複数のF D領域を互いに接続した状態で信号を出力するモードと、複数のF D領域を接続しない状態で信号を用いる撮影モードとで、リセット動作が異なる場合がある。この場合に、リセット動作によるF D領域の電圧変動の大きさが異なりうる。結果としてシェーディングなどのノイズが生じる可能性がある。

#### 【0009】

なお、引用文献1ではF D接続トランジスタによって、F D領域の容量を変化させていく。しかし、上述のノイズの課題は、F D領域の容量を変えるための他の構成においても、同様に生じうる。

#### 【0010】

このような課題に鑑み、本発明はノイズを低減することを目的とする。

#### 【課題を解決するための手段】

#### 【0011】

本発明の1つの側面に係る実施例の撮像装置は、光電変換によって生じた電荷を受ける入力ノードを有し、前記入力ノードの電圧に基づく信号を出力する出力部と、オンとオフとに制御され、前記オンのときに前記入力ノードの電圧をリセットするリセット部と、制御信号を受けるゲート電極を有し、前記制御信号に応じて前記入力ノードの容量を第1の容量値と前記第1の容量値より大きい第2の容量値とに制御する制御部と、をそれぞれが含む複数の画素ユニットを備え、前記入力ノードの容量が前記第1の容量値である状態で、前記出力部が前記信号を出力する第1のモードと、前記入力ノードの容量が前記第2の容量値である状態で、前記出力部が前記信号を出力する第2のモードと、を有し、前記第1のモードにおいて、前記リセット部が前記オフである状態で、前記制御部が前記入力ノードの容量を前記第1の容量値から前記第2の容量値に切り替え、その後、前記入力ノードの容量が前記第2の容量値である状態で、前記リセット部が前記オフから前記オンに制御されるリセット動作と、前記リセット動作の後に、前記入力ノードの容量が前記第1の容量値である状態で前記出力部が前記信号を出力する出力動作と、を行う、ことを特徴とする。

#### 【発明の効果】

#### 【0012】

本発明によれば、ノイズを低減することができる。

#### 【図面の簡単な説明】

#### 【0013】

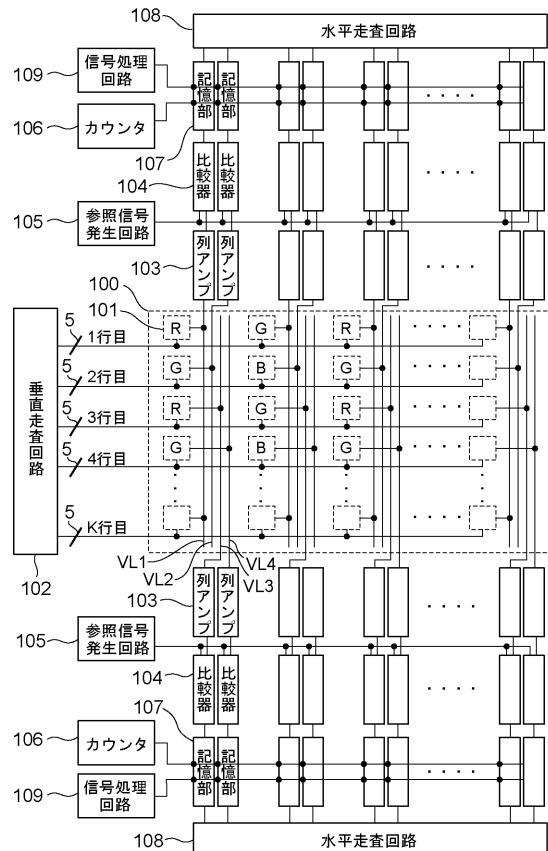

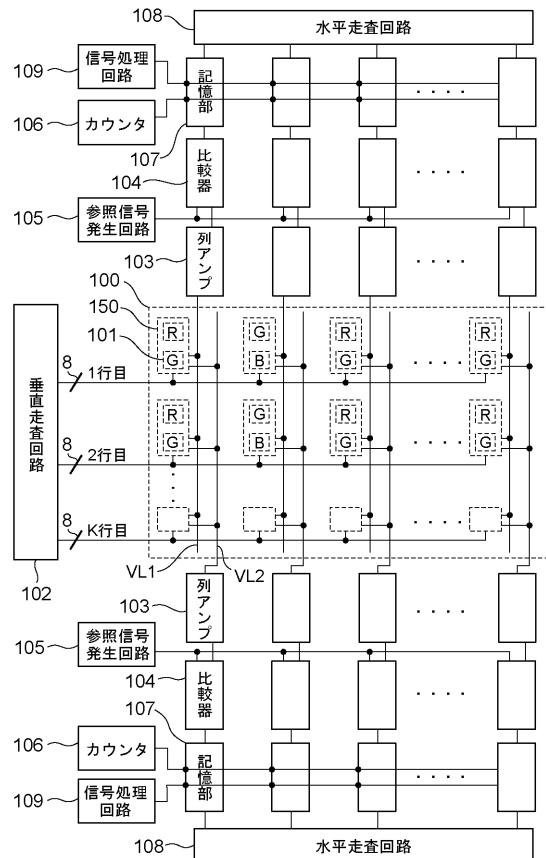

【図1】撮像装置の全体構成を模式的に示す図。

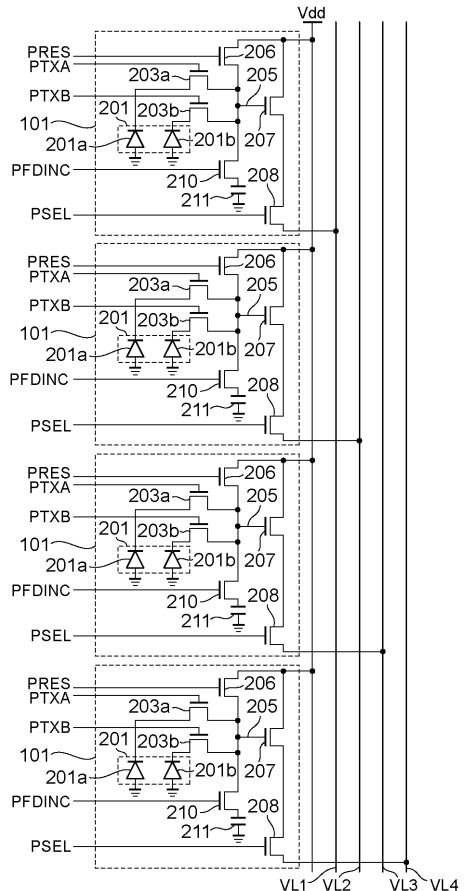

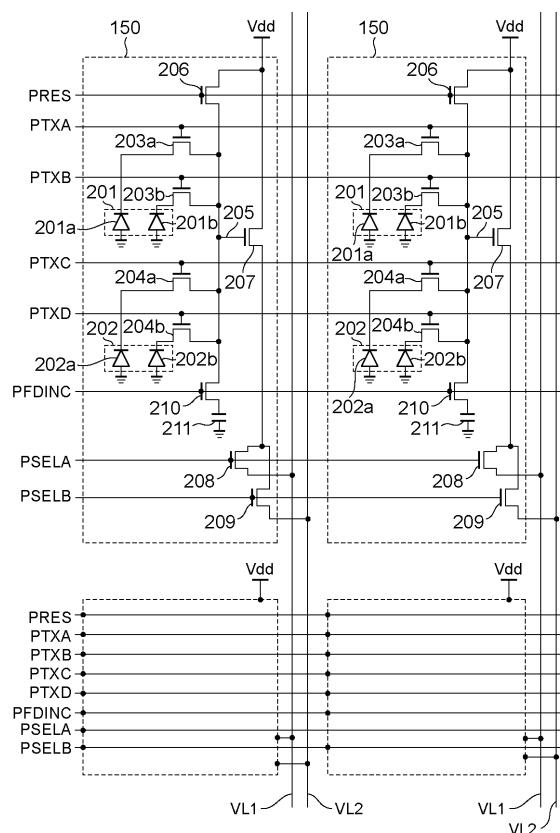

【図2】撮像装置の画素の等価回路を示す図。

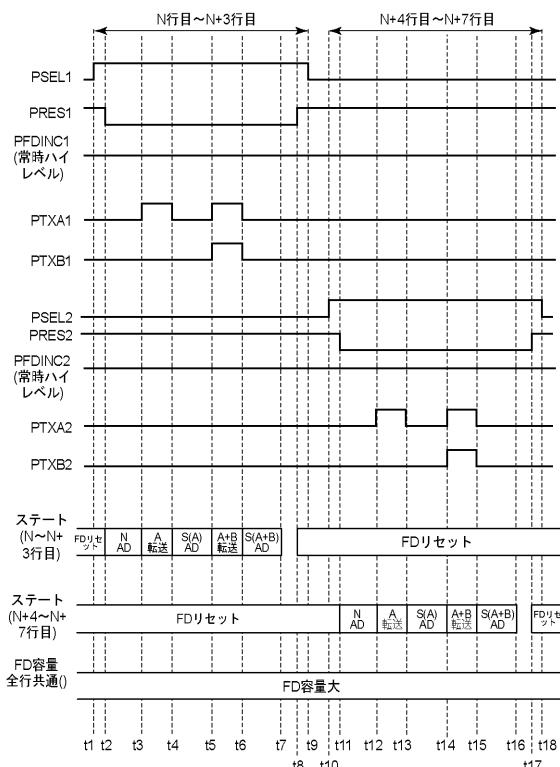

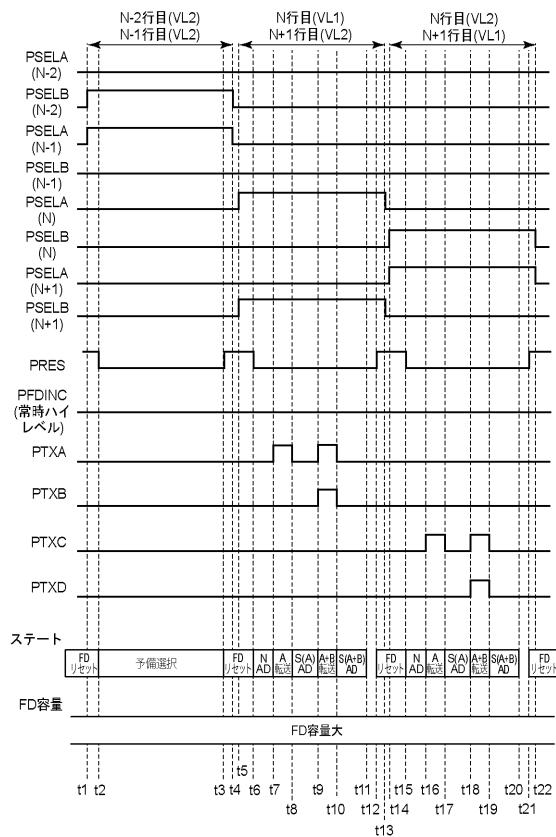

【図3】撮像装置の駆動に用いられる制御信号のタイミングチャート図。

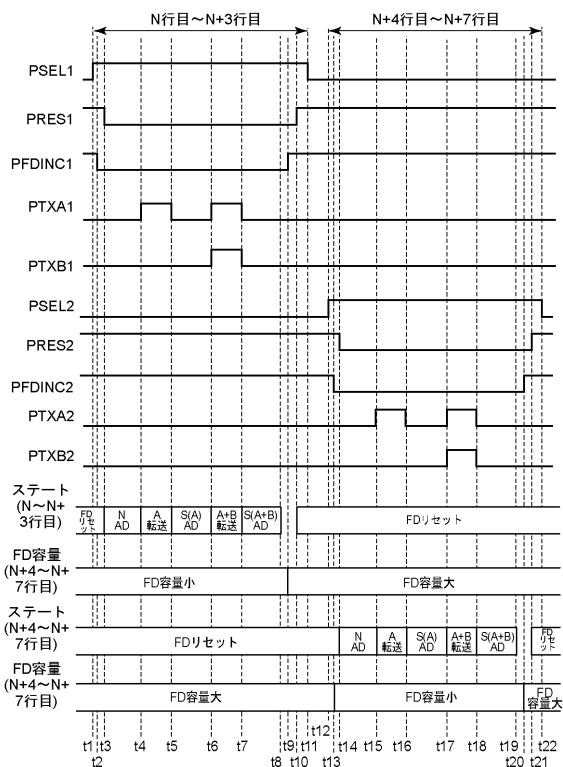

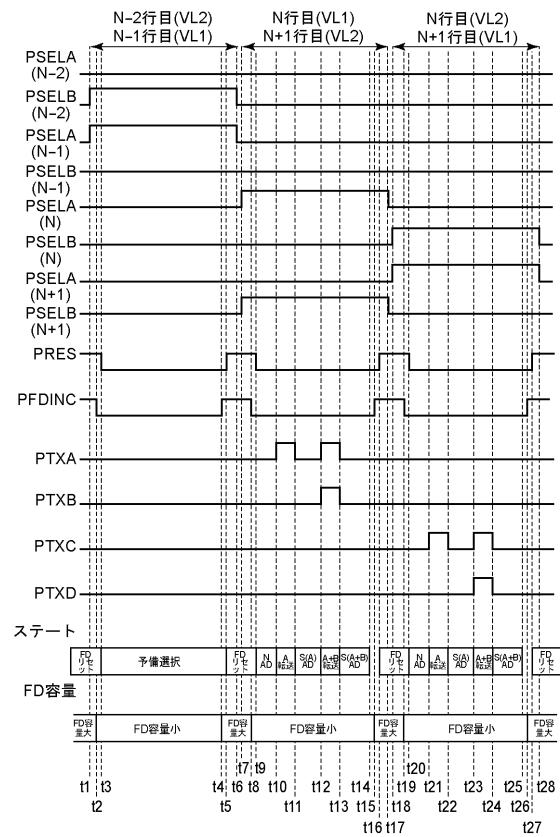

【図4】撮像装置の駆動に用いられる制御信号のタイミングチャート図。

【図5】撮像装置の全体構成を模式的に示す図。

【図6】撮像装置の画素の等価回路を示す図。

【図7】撮像装置の駆動に用いられる制御信号のタイミングチャート図。

【図8】撮像装置の駆動に用いられる制御信号のタイミングチャート図。

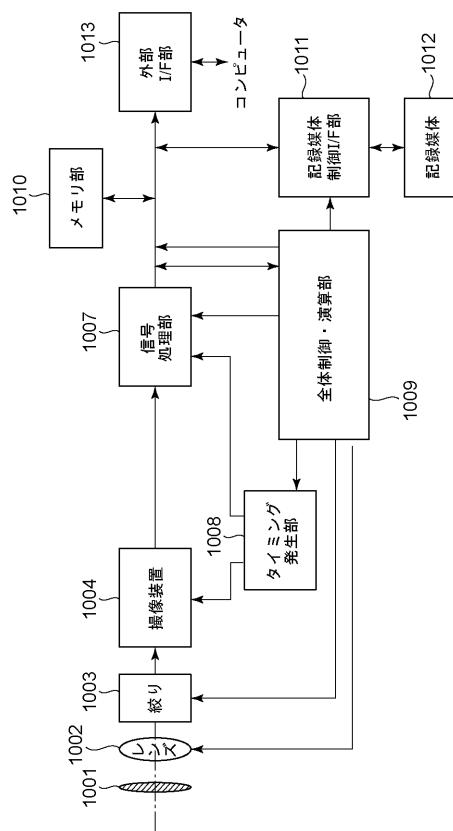

【図9】光電変換システムの実施例のブロック図。

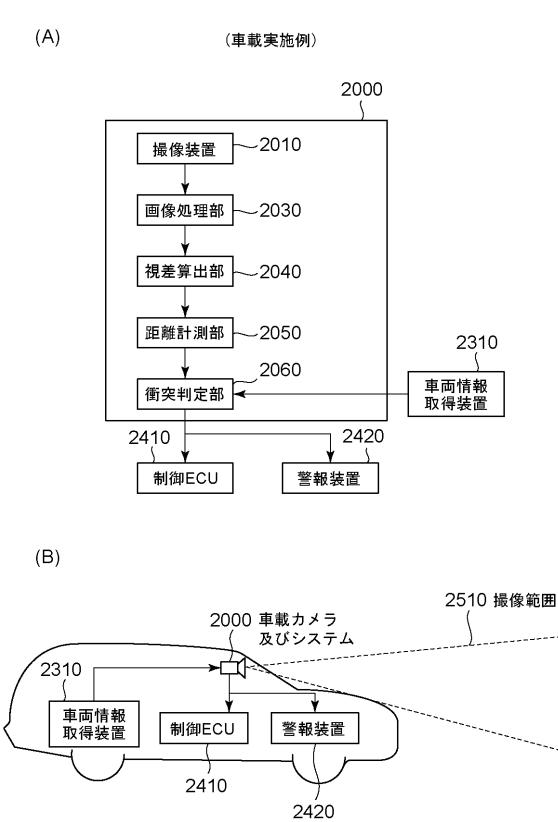

【図10】移動体の実施例のブロック図。

10

20

30

40

50

**【発明を実施するための形態】**

**【0014】**

**[実施例1]**

図1は、第1の実施例に係る撮像装置の全体構成を模式的に示したブロック図である。画素部100に、複数の画素101が配置される。本実施例では、1つの画素101が1つの画素ユニットを構成する。複数の画素101は複数の行、および、複数の列を含む行列状に配されている。画素101は、光電変換により生じた電荷に基づく画素信号を出力する。それぞれの画素101に対して、赤R、緑G、または、青Bのいずれかのカラーフィルタが割り当てられる。したがって、配置されたカラーフィルタを透過する色を持つ光が画素101に入射する。複数のカラーフィルタが、通常、ベイヤー状に配置されている。

10。

**【0015】**

本実施例では1行目からK行目に渡って画素101が配されている。また一列の画素101に対応して、複数の出力線VLが配される。具体的に、4本の出力線VL1、VL2、VL3、VL4が配される。N+1行目の画素101は出力線VL1に接続される。ここで、Nは0以上の整数である。同様に、N+2行目の画素101、N+3行目の画素101、および、N+4行目の画素101は、それぞれ、出力線VL2、出力線VL3、および、出力線VL4に接続される。このような構成により、複数の行に含まれる画素101の画素信号を並列して読み出すことができる。以降、本実施例の説明において、4つの出力線VLを互いに区別するときには、符号の末尾に数字を付す。4つの出力線VLを特に区別しないときは、単にVLとのみ標記する。

20

**【0016】**

垂直走査回路102は、画素101の駆動を制御する制御信号を、行ごとに、画素101に供給する。本実施例では、行ごとに、5種類の制御信号が供給される。したがって、垂直走査回路102は各行に配された5つの制御線に接続される。なお、図1では、各行の5つの制御線をまとめて1つの配線で示している。

**【0017】**

本実施例では、一列の画素101に対応して、4つの列アンプ103が配される。垂直走査回路102によって選択された4行の画素101の信号が、4つの出力線VLを介して並行に4つの列アンプ103に入力される。列アンプ103は画素101から読みだされる画素信号を増幅する。列アンプ103によって増幅された画素信号が、列アンプ103から出力される。

30

**【0018】**

各列アンプ103に対応して、比較器104が配される。また、参照信号発生回路105が、複数の比較器104に共通に接続される。比較器104には、列アンプ103により増幅された画素信号と、参照信号発生回路105で生成されるランプ波形の参照信号とが入力される。比較器104は、画素信号と参照信号と電圧の大きさを比較して、信号電圧の大小信号が反転する時にハイレベルからローレベル若しくはローレベルからハイレベルに出力を遷移させる。

**【0019】**

カウンタ106は、複数の記憶部5に共通に接続される。カウンタ106は、参照信号発生回路105からの参照信号の出力に合わせてカウント動作を行い、カウント値を出力する。記憶部107は、対応する比較器104の出力が遷移するタイミングで、カウンタ106から出力されているカウント値をデジタルデータとして記憶する。

40

**【0020】**

記憶部107に記憶されたデジタルデータは、水平走査回路108によって列毎に信号処理回路109に順次読み出される。信号処理回路109は、CDS(Correlate d Dual Sampling)処理や加算などの処理を行う。

**【0021】**

上述の画素101からの画素信号の読み出し動作は、垂直走査回路102で画素部10

50

0の画素行を選択しながら行われる。なお、列アンプ103、比較器104、記憶部107が、列回路を構成する。

#### 【0022】

図2は画素101の等価回路を示す。フォトダイオード（以下、PDと表記する）201は、光電変換により入射光を電荷に変換する。つまり、PD201は光電変換部の1つの例である。本実施例では、画素101が並列に接続された2つのPD201aとPD201bとを含む。換言すると、本実施例の画素101は、複数の光電変換部を含んでいる。

#### 【0023】

2つのPD201aとPD201bとは、それぞれ、電荷を蓄積する第1導電型（例えば、N型）の半導体領域を含む。第1導電型の半導体領域は、隣接する第2導電型（例えば、P型）の半導体領域とPN接合を構成する。PD201aの第1導電型の半導体領域と、PD201bの第1導電型の半導体領域とは、互いに電気的に分離されている。

#### 【0024】

PD201aとPD201bとは、単一のマイクロレンズの下に配される。PD201aで生じた電荷に基づく画素信号と、PD201bで生じた電荷に基づく画素信号とを、個別に読み出すことで、焦点検出を行うことができる。一方、PD201aで生じた電荷とPD201bで生じた電荷とを加算することができる。当該加算された電荷に基づく画素信号は、画像生成に利用されうる。

#### 【0025】

転送トランジスタ203a、および、転送トランジスタ203bは、それぞれ、PD201aで生じた電荷、PD201bで生じた電荷を、入力ノード205に転送する。転送トランジスタ203a、および、転送トランジスタ203bは、画素101の転送部を構成する。転送トランジスタ203aのゲートは、転送制御線PTXAに接続される。転送トランジスタ203bのゲートは、転送制御線PTXBに接続される。

#### 【0026】

入力ノード205は、転送トランジスタ203a、203bを介して転送された電荷を受ける。入力ノード205は電気的にフローティングになるように構成される。そのため、入力ノード205に、転送された電荷の量に応じた電圧が生じる。つまり、入力ノード205は電荷電圧変換の機能を持つ。撮像装置が半導体基板に形成される場合には、入力ノード205は例えば第1導電型のフローティングディフュージョン領域（以下、FD領域）によって構成される。

#### 【0027】

入力ノード205は、増幅トランジスタ207のゲートに接続される。増幅トランジスタ207は、不図示の増幅トランジスタ207は入力ノード205の電圧に基づく信号を出力線VLへ出力する。つまり、入力ノード205および増幅トランジスタ207が、画素101の出力部を構成する。例えば、増幅トランジスタ207のドレインには電源電圧Vddが供給される。そして、増幅トランジスタ207と、出力線VLに接続された電流源とが、ソースフォロア回路を構成する。このような構成により、増幅トランジスタ207は出力部を構成しうる。別の例として、増幅トランジスタ207が差動増幅回路を構成してもよい。なお、入力ノード205は、前述のFD領域、増幅トランジスタ207のゲート電極、および、両者を接続する導電部材によって構成されてもよい。

#### 【0028】

リセットトランジスタ206は、入力ノード205の電圧をリセットする。リセットトランジスタ206のドレインはリセット電圧、例えば、電源電圧Vddを供給するノードに接続される。したがって、リセットトランジスタ206がオンすると、入力ノード205の電圧がリセットされる。リセットトランジスタ206のゲートは、リセット制御線PREに電気的に接続されている。リセット制御線PREに供給される制御信号PREにより、リセットトランジスタ206はオンとオフとに制御される。本実施例では、リセットトランジスタ206は、入力ノード205をリセットするリセット部を構成する。

10

20

30

40

50

## 【0029】

増幅トランジスタ207と出力線VLとの間の電気経路に、選択トランジスタ208が配される。選択トランジスタ208のゲートは選択制御線PSELに電気的に接続されている。制御信号PSELに応じて、選択トランジスタ208はオンとオフとに制御される。選択トランジスタ208がオンのときに、対応する増幅トランジスタ207から出力線VLに画素信号が出力される。1つの出力線VLに接続された複数の画素101のうち、一部の画素101の選択トランジスタ208がオンし、他の画素101の選択トランジスタ208がオフすることにより、画素信号を出力する画素101が選択される。1つの出力線VLに接続された2つ以上の画素101が同時に選択されてもよい。

## 【0030】

入力ノード205には、容量制御部210が接続される。容量制御部210は、制御信号PFDINCを受けるゲート電極を少なくとも有する。容量制御部210のゲート電極は、前述のFD領域の隣に配された第2導電型の半導体領域の上に、絶縁膜を介して配される。容量制御部210は、制御信号PFDINCに応じて、入力ノード205の容量を、第1の容量値C1と、第1の容量値C1より大きい第2の容量値C2とに制御する。

10

## 【0031】

例えば、容量制御部210は、FD領域、ゲート電極、および、FD領域と同じ導電型を有する半導体領域とを含むトランジスタによって構成されうる。本実施例では、図2の等価回路における容量211が、FD領域と同じ導電型を有する半導体領域によって構成されている。容量211は、FD領域と同じ導電型を有する半導体領域のもつPN接合の容量成分を含む。

20

## 【0032】

制御信号PFDINCに応じて、容量制御部210を構成するトランジスタがオンおよびオフに制御される。これにより、入力ノード205と容量211との接続および非接続が切り替わる。容量211が接続されていないとき、入力ノード205の容量は、第1の容量値C1である。容量211が接続されたとき、入力ノード205の容量は、第2の容量値C2である。

## 【0033】

このように、容量制御部210および容量211は、入力ノード205の容量を可変とする容量可変手段として機能する。このような構成により、入力ノード205に転送された電荷の量に対する増幅トランジスタ207から出力される画素信号の変換比、すなわちゲインを切り替えることができる。一般に、入力ノード205の容量と、ゲインとは派比例の関係にある。容量211が入力ノード205に接続されたときのゲインは、容量211が入力ノード205に接続されていないときのゲインより小さくなる。このように、本実施例の撮像装置は、制御信号PFDINCに応じて画素101のゲインを切り替えることができる。

30

## 【0034】

なお、容量制御部210は、図2で示されたトランジスタおよび容量211の分離された2つの素子を含む構成には限定されない。容量制御部210は、制御信号PFDINCに応じて、入力ノード205の容量を、第1の容量値C1と、第1の容量値C1より大きい第2の容量値C2とに制御することが可能であればよい。他の例として、MOS型容量を用いることで、容量制御部210の機能を実現することができる。例えば、MOS型トランジスタのソース及びドレインを短絡した端子と、ゲート端子との間の容量を用いたMOS型容量である。このMOS型容量は、端子間の電圧により容量が変化する可変容量素子として機能し得る。そのため、入力ノード205の容量を可変とする容量可変手段として適用可能である。あるいは、別の例として、MOS型容量は、MOS型トランジスタのソース及びドレインの一方を省略した構成であってもよい。具体的には、上述のFD領域と同じ導電型の半導体領域を省略する構成が用いられる。

40

## 【0035】

容量制御部210により撮影条件に適した撮像を行うことができる。入力ノード205

50

の容量を大きくすると、ゲインは小さくなるが、蓄積可能な電荷量が多くなる。そのため、入射光量が多い撮影条件に好適な設定となる。逆に、入力ノード 205 の容量を小さくすると、蓄積可能な電荷量は少なくなるが、ゲインが大きくなる。そのため、入射光量が少ない撮影条件に好適な設定となる。

#### 【0036】

続いて、本実施例の撮像装置の動作について説明する。本実施例の撮像装置は、第1のモードと第2のモードとを持つ。第1のモードと第2のモードとは、例えば、被写体からの入射光量等の撮影条件に基づいて切り替えられる。第1のモードでは、入力ノード 205 の容量値が第1の容量値 C1 である状態で、画素 101 の出力部が画素信号を出力する。第2のモードでは、入力ノード 205 の容量値が第2の容量値 C2 である状態で、画素 101 の出力部が画素信号を出力する。10

#### 【0037】

図3のタイミングチャートを用いて、第2のモードの動作を説明する。図3は画素 101 に供給される制御信号のタイミングチャートを示す。上述の通り、本実施例では4行の画素 101 が並行して画素信号を出力する。図3において、N 行目から N + 3 行目の画素 101 に共通して与えられる制御信号（符号の末尾が 1）と、N + 4 行目から N + 7 行目の画素 101 に共通して与えられる制御信号（符号の末尾が 2）とが示されている。制御信号がハイレベルのときに、対応するトランジスタがオンする。制御信号がローレベルのときに、対応するトランジスタがオフする。

#### 【0038】

時刻 t1 から時刻 t9 において、N 行目～N + 3 行目の画素 101 から画素信号が読み出される。続いて、時刻 t10 から時刻 t18 において、N + 4 行目～N + 7 行目の画素 101 から画素信号が読み出される。読み出しを行う期間には、対応する制御信号 PSE\_L がハイレベルになっている。また、第2のモードでは、制御信号 PFDINC が常時ハイレベルである。そのため、入力ノード 205 の容量は、常に、第2の容量値 C2 に制御されている。20

#### 【0039】

まず、N 行～N + 3 行の画素 101 から画素信号が読み出し動作について説明する。時刻 t1 から時刻 t2 は、リセットトランジスタ 206 がオンしている。この期間に、入力ノード 205 の電圧をリセットするリセット動作が行われている。30

#### 【0040】

続いて、時刻 t2 から時刻 t3 の期間に、画素 101 の増幅トランジスタ 207 は、画素信号として、リセット時のノイズを含むノイズ信号を出力する。出力されたノイズ信号は列回路においてアナログデジタル変換（以下、AD 変換）される。

#### 【0041】

時刻 t3 から時刻 t4 の期間に、転送トランジスタ 203a が P D 201a の電荷を入力ノード 205 に転送する。その後、時刻 t4 から時刻 t5 の期間に、画素 101 の増幅トランジスタ 207 は、画素信号として、P D 201a で生じた電荷に基づく第1の光信号（以下、A 信号）を出力線 VL へ出力する。出力された A 信号は列回路において AD 変換される。40

#### 【0042】

時刻 t5 から時刻 t6 の期間に、転送トランジスタ 203a および転送トランジスタ 203b がオンする。これにより、P D 201a の電荷、および、P D 201b の電荷がそれぞれ入力ノード 205 に転送される。転送された P D 201a の電荷および P D 201b の電荷は、入力ノード 205 において加算される。したがって、時刻 t6 から時刻 t7 の期間に、P D 201a の電荷および P D 201b の電荷に基づく第2の光信号（以下、A + B 信号）が出力される。出力された A 信号は列回路において AD 変換される。

#### 【0043】

ここで、制御信号 PFDINC がハイレベルであるため、入力ノード 205 の容量が第2の容量値 C2 である状態で、画素 101 の増幅トランジスタ 207 は、上述のノイズ信

10

20

30

40

50

号、A信号、および、A+B信号を出力する出力動作を行う。

**【0044】**

デジタル信号に変換されたノイズ信号、A信号、および、A+B信号は、それぞれ、水平走査回路108によって信号処理回路109に転送される。信号処理回路109は、ノイズ信号、A信号、および、A+B信号を用いてCDS処理を行う。

**【0045】**

次に、時刻t8にて駆動信号PRESがハイレベルとなり、リセット動作が行われる。時刻t9にて制御信号PSELをローレベルとすることで、N行目からN+3行目の画素101の画素信号の読み出し動作が終了する。

**【0046】**

時刻t10から時刻t18では、上記の時刻t1から時刻t9の動作が、N+4行目からN+7行目の画素101に対して行われる。これらの動作は、N行目からN+3行目の画素101からの画素信号の読み出しと同じである。

**【0047】**

図4のタイミングチャートを用いて、第1のモードの動作を説明する。図4は画素101に供給される制御信号のタイミングチャートを示す。図4において、N行目からN+3行目の画素101に共通して与えられる制御信号（符号の末尾が1）と、N+4行目からN+7行目の画素101に共通して与えられる制御信号（符号の末尾が2）とが示されている。制御信号がハイレベルのときに、対応するトランジスタがオンする。制御信号がローレベルのときに、対応するトランジスタがオフする。

**【0048】**

時刻t1から時刻t11において、N行目～N+3行目の画素101から画素信号が読み出される。続いて、時刻t12から時刻t22において、N+4行目～N+7行目の画素101から画素信号が読み出される。読み出しを行う期間には、対応する制御信号PSELがハイレベルになっている。

**【0049】**

第2のモードと異なる点として、第1のモードでは、入力ノード205の容量が第1の容量値C1に制御された状態で、増幅トランジスタ207が画素信号を出力する。そのため、一部の期間で、制御信号PFDINCがローレベルである。具体的には、時刻t2から時刻t9までの期間、制御信号PFDINC1がローレベルである。また、時刻t13から時刻t21までの期間、制御信号PFDINC2がローレベルである。

**【0050】**

それ以外の動作は、第2のモードと同様である。図3および図4のステートの欄に、対応する動作を示してある。これらの動作について詳細な説明は省略する。

**【0051】**

第1のモードにおいては、入力ノード205の容量が第1の容量値C1に制御された状態で、増幅トランジスタ207が画素信号を出力する。言い換えると、入力ノード205に容量211が接続されていない状態で、増幅トランジスタ207が画素信号を出力する。しかし、入力ノード205のリセット動作は、入力ノード205に容量211が接続された状態で行われる。入力ノード205と容量211との間に電位差があると、入力ノード205へのリーク電流が発生する可能性がある。入力ノード205に容量211が接続された状態で入力ノード205の電圧をリセットすることにより、両者の電圧をほぼ等しくすることができる。結果として、このようなリーク電流によるノイズを低減できる。

**【0052】**

本実施例では、画素101からの画素信号の読み出しが終わった後に、入力ノード205のリセット動作を行う。N行目～N+3行目の画素101を例に、このリセット動作を説明する。まず、時刻t9において制御信号PFDINCがハイレベルになる。このとき、制御信号PRESはローレベルである。したがって、リセットトランジスタ206がオフである状態で、入力ノード205の容量が第1の容量値C1から、第2の容量値C2に切り替えられる。その後、時刻t9に制御信号PRESがハイレベルになる。このとき、

10

20

30

40

50

制御信号 P F D I N C はハイレベルである。したがって、入力ノード 205 の容量が第 2 の容量値 C2 である状態で、リセットトランジスタ 206 がオフからオンに制御される。以上により、入力ノード 205 のリセット動作が行われる。この状態が、次のフレームの画素信号を読み出す時まで維持される。次のフレームの画素信号を読み出す時に、再び、制御信号 P F D I N C がローレベルになる。つまり、入力ノード 205 の容量が第 1 の容量値 C1 に制御された状態で、画素信号が出力される。

#### 【0053】

このように、本実施例では、容量制御部 210 が入力ノード 205 の容量を第 1 の容量値 C1 からそれよりも大きい第 2 の容量値 C2 に切り替えた後に、リセットトランジスタ 206 がオンする。この制御により、リセット動作による入力ノード 205 の電圧の変動を低減することができる。これはリセットトランジスタ 206 が動作する時に、入力ノード 205 の容量が大きいため、カップリングによる電圧の変動を小さくできるからである。

10

#### 【0054】

上述のように、リセット動作の後に、次のフレームの画素信号を出力する出力動作を行う。もし、リセット動作において入力ノード 205 の電圧が大きく変動すると、出力動作までにその電圧の変動が静定しない可能性がある。結果として、ノイズが生じる可能性がある。リセット動作による入力ノード 205 の電圧の変動を低減することで、これらのノイズを低減することができる。

#### 【0055】

また、1つのリセット制御線 P R E S が 1000 列以上の画素 101 に接続される場合、画素 101 の位置に応じて制御信号 P R E S の波形が変化する可能性がある。複数の画素 101 において入力ノード 205 とリセットトランジスタ 206 のゲートとの寄生容量が同じであっても、リセットトランジスタ 206 のゲートに供給される制御信号 P R E S が異なると、入力ノード 205 の電位変動は異なる可能性がある。そうすると、列ごとに入力ノード 205 のリセット状態がばらつく可能性がある。このリセット状態のばらつきは、シェーディングなどによる画質の低下の原因となる可能性がある。リセット動作による入力ノード 205 の電圧の変動を低減することで、列ごとのリセット状態のばらつきを小さくできる。結果として、シェーディングを低減し、画質を向上させることができる。

20

#### 【0056】

以上に説明したとおり、本実施形態においては、容量制御部 210 が入力ノード 205 の容量を第 1 の容量値 C1 からそれよりも大きい第 2 の容量値 C2 に切り替えた後に、リセットトランジスタ 206 がオフからオンに制御される。このような構成によれば、ノイズを低減することができる。

30

#### 【0057】

##### [実施例 2]

別の実施例を説明する。本実施形態は、1つの画素ユニットが複数の画素を含む点で実施例 1 と異なる。また、1つの画素ユニットに含まれる複数の画素は、画素ユニットに含まれる回路の一部を共有している。そのため、画素から画素信号を読み出すための動作が、実施例 1 と異なる。以下では実施例 1 と異なる部分を主に説明する。実施例 1 と同じ部分については、説明を省略する。

40

#### 【0058】

図 5 は、第 2 の実施例に係る撮像装置の全体構成を模式的に示したブロック図である。画素部 100 に、複数の画素 101 が配置される。複数の画素 101 が行列状に配されていること、および、カラーフィルタが各画素 101 に割り当てられることは、実施例 1 と同様である。本実施例では、2つの画素 101 が1つの画素ユニット 150 を構成する。そこで本実施例では、画素ユニット 150 を単位として行を定義する。図 5 に示されるように、K 行の画素ユニット 150 が配される。この場合、画素 101 は  $2 \times K$  行に渡って配置されることになる。

#### 【0059】

10

20

30

40

50

本実施例では、一列の画素 101 に対応して、2 本の出力線 VL1、VL2 が配される。1 つの画素ユニット 150 は、出力線 VL1 および出力線 VL2 の両方に接続される。

#### 【0060】

垂直走査回路 102 は、画素 101 の駆動を制御する制御信号を、行ごとに、画素 101 に供給する。本実施例では、1 つの画素ユニット 150、すなわち、2 つの画素 101 に対して、8 種類の制御信号が供給される。したがって、垂直走査回路 102 は行ごとに配された 8 つの制御線に接続される。なお、図 5 では、8 つの制御線をまとめて 1 つの配線で示している。

#### 【0061】

列アンプ 103、比較器 104、参照信号発生回路 105、カウンタ 106、記憶部 107、水平走査回路 108、信号処理回路 109 の構成は、実施例 1 と同じである。ただし、本実施例では、1 つの列に対して、2 つの列回路が配される。

#### 【0062】

図 6 は画素 101 の等価回路を示す。1 つの画素ユニット 150 に含まれる 2 つの画素 101 を、便宜的に第 1 の画素 101 および第 2 の画素 101 と呼ぶ。第 1 の画素 101 は、光電変換部として、PD201a および PD201b を含む。PD201a および PD201b は、実施例 1 の PD201a および PD201b と同じである。第 2 の画素 101 は、光電変換部として、PD202a および PD202b を含む。便宜的に異なる符号が付されているが、PD202a および PD202b は、実施例 1 の PD201a および PD201b と同じである。PD201a および PD201b は単一のマイクロレンズの下に配される。PD202a および PD202b は別の単一のマイクロレンズの下に配される。光電変換部についての詳細な説明は省略する。

#### 【0063】

第 1 の画素 101 は、転送トランジスタ 203a、および、転送トランジスタ 203b を含む。転送トランジスタ 203a、および、転送トランジスタ 203b は、それぞれ、実施例 1 の転送トランジスタ 203a、および、転送トランジスタ 203b と同じである。ただし、転送トランジスタ 203a のゲートは転送制御線 PTXA に接続される。転送トランジスタ 203b のゲートは転送制御線 PTXB に接続される。また、第 2 の画素 101 は、転送トランジスタ 204a、および、転送トランジスタ 204b を含む。便宜的に異なる符号が付されているが、転送トランジスタ 204a、および、転送トランジスタ 204b は、それぞれ、実施例 1 の転送トランジスタ 203a、および、転送トランジスタ 203b と同じである。ただし、転送トランジスタ 204a のゲートは転送制御線 PTXC に接続される。転送トランジスタ 204b のゲートは転送制御線 PTXD に接続される。転送部についての詳細な説明は省略する。

#### 【0064】

1 つの画素ユニット 150 は、入力ノード 205、リセットトランジスタ 206、増幅トランジスタ 207、容量制御部 210、容量 211 を含む。これらは実施例 1 と同様であるため、個々の説明は省略する。このように、本実施例においては、1 つの画素ユニット 150 に含まれる 2 つの画素 101 が、例えば、増幅トランジスタ 207 を共有している。そのため、1 画素あたりに配されるトランジスタの数を低減することができる。

#### 【0065】

1 つの画素ユニット 150 は、選択トランジスタ 208 および選択トランジスタ 209 を含む。選択トランジスタ 208 および選択トランジスタ 209 は、それぞれ、実施例 1 の選択トランジスタ 208 と同じ機能をもつ。選択トランジスタ 208 は、増幅トランジスタ 207 と出力線 VL1 とを接続する。また、選択トランジスタ 208 は、増幅トランジスタ 207 と出力線 VL2 とを接続する。選択トランジスタ 208 のゲートは、制御線 PSEL A に接続される。選択トランジスタ 209 のゲートは制御線 PSEL B に接続される。このような構成により、画素ユニット 150 の画素信号を、複数の出力線 VL のうち任意の 1 つに出力することができる。

#### 【0066】

10

20

30

40

50

続いて、本実施例の撮像装置の動作について説明する。本実施例の撮像装置は、第1のモードと第2のモードとを持つ。第1のモードと第2のモードとは、例えば、被写体からの入射光量等の撮影条件に基づいて切り替えられる。第1のモードでは、入力ノード205の容量値が第1の容量値C1である状態で、画素ユニット150の出力部が画素信号を出力する。第2のモードでは、入力ノード205の容量値が第2の容量値C2である状態で、画素ユニット150の出力部が画素信号を出力する。

#### 【0067】

図7のタイミングチャートを用いて、第2のモードの動作を説明する。図7は画素101に供給される制御信号のタイミングチャートを示す。図7には、N-2行目～N+1行目までの画素ユニット150に供給される選択制御信号PSEL A(N-2)～PSEL A(N+1)、PSEL B(N-2)～(N+1)が示されている。複数の行に供給される複数の選択制御信号が示されるため、符号の末尾が対応する行を示している。また、図7には、N行目の画素ユニット150およびN+1行目の画素ユニット150に共通して与えられる制御信号PRESS、PFDINC、PTXA、PTXB、PTXC、PTXDが示されている。制御信号がハイレベルのときに、対応するトランジスタがオンする。制御信号がローレベルのときに、対応するトランジスタがオフする。

#### 【0068】

図7の時刻t1から時刻t4までの期間で、N-2行目の画素ユニット150およびN-1行目の画素ユニット150の画素信号が並行して読み出される。また、時刻t5から時刻t13までの期間で、N行目の画素ユニット150の画素信号と、N+1行目の画素ユニット150の画素信号とが、並行して読み出される。各画素ユニット150は2つの画素101を含むため、さらに、時刻t14から時刻t22までの期間で、N行目の画素ユニット150の画素信号と、N+1行目の画素ユニット150の画素信号とが、並行して読み出される。時刻t5から時刻t13までの期間に、各画素ユニット150に含まれる第1の画素101の画素信号が読み出される。また、時刻t14から時刻t22までの期間に、各画素ユニット150に含まれる第2の画素101の画素信号が読み出される。

#### 【0069】

各期間の動作は、実施例1と同様である。そのため、詳細な説明は省略する。図7のステートの欄に、対応する動作を示してある。これらの動作について詳細な説明は省略する。ただし、N行目の画素ユニット150の画素信号と、N+1行目の画素ユニット150の画素信号とが、互いに異なる出力線VLへ出力されるように、選択制御信号PSEL A、および、選択制御信号PSEL Bが構成される。例えば、N行目の画素ユニット150へ供給される制御信号PSEL A(N)がハイレベルの期間は、N+1行目の画素ユニット150へ供給される制御信号PSEL A(N+1)はローレベルであり、一方、選択制御信号PSEL B(N+1)がハイレベルである。また、1つの画素ユニット150に含まれる2つの画素101のどちらから画素信号が読み出されるかは、制御信号PTXA、制御信号PTXB、制御信号PTXC、および、制御信号PTXDによって制御される。

#### 【0070】

本実施例では、N-2行目およびN-1行目の画素ユニット150の画素信号を読み出す期間において、N行目およびN+1行目の画素ユニット150の入力ノード205のリセットが解除される。この動作を予備選択と呼ぶ。なお、リセットが解除された状態とは、リセットトランジスタ206がオフの状態のことである。

#### 【0071】

本実施例では、2つの画素101が1つの入力ノード205を共有する。この場合、第1の画素101の画素信号を読み出すためのリセット動作と、第2の画素101の画素信号を読み出すためのリセット動作との間で、リセット動作が開始されてからリセットが解除されるまでの時間が異なる可能性がある。結果として、行毎に筋状のノイズが生じる可能性がある。上述の予備選択を行うことで、リセットトランジスタのゲート絶縁膜中にトランプされた電荷の放出が促進され、リセットレベルの変動によるシェーディングやバターンノイズを低減することができる。

10

20

30

40

50

### 【0072】

具体的に、時刻  $t_1$  から時刻  $t_4$  までの期間では制御信号 PSELB (N - 2) および制御信号 SELA (N - 1) によって、N - 2 行目と N - 1 行目の画素ユニット 150 が選択されている。一方、N 行目と N + 1 行目の画素ユニット 150 は非選択の状態である。しかし、前述の予備選択を行うため、時刻  $t_2$  で N 行目および N + 1 行目の画素ユニット 150 へ供給される制御信号 PRES をローレベルする。これにより、N 行目および N + 1 行目の画素ユニット 150 の入力ノード 205 のリセットが解除された状態となる。その後、時刻  $t_3$  にて、制御信号 PRES がハイレベルになり、N 行目および N + 1 行目の画素ユニット 150 の入力ノード 205 に対してリセット動作が行われる。時刻  $t_4$  にて制御信号 PSELB (N - 2) と制御信号 SELA (N - 1) がローレベルとなることで、N - 2 行と N - 1 行目の画素ユニット 150 を選択している状態が終了する。その後、時刻  $t_5$  にて制御信号 SELA (N) と制御信号 PSELB (N + 1) がハイレベルになる。これにより、N 行目の画素ユニット 150 および N + 1 行目の画素ユニット 150 が選択される。以降の動作は、実施例 1 と同様である。10

### 【0073】

第 2 のモードでは、制御信号 PFDINC がハイレベルである。そのため、入力ノード 205 の容量が第 2 の容量値 C2 である状態で、各画素ユニット 150 の増幅トランジスタ 207 は、ノイズ信号、A 信号、および、A + B 信号を出力する出力動作を行う。20

### 【0074】

図 8 のタイミングチャートを用いて、第 1 のモードの動作を説明する。図 8 は画素 101 に供給される制御信号のタイミングチャートを示す。図 8 には、図 7 と同じ制御信号が示されている。20

### 【0075】

図 8 の時刻  $t_1$  から時刻  $t_6$  までの期間で、N - 2 行目の画素ユニット 150 および N - 1 行目の画素ユニット 150 の画素信号が並行して読み出される。また、時刻  $t_7$  から時刻  $t_{17}$  までの期間で、N 行目の画素ユニット 150 の画素信号と、N + 1 行目の画素ユニット 150 の画素信号とが、並行して読み出される。各画素ユニット 150 は 2 つの画素 101 を含むため、さらに、時刻  $t_{18}$  から時刻  $t_{28}$  までの期間で、N 行目の画素ユニット 150 の画素信号と、N + 1 行目の画素ユニット 150 の画素信号とが、並行して読み出される。時刻  $t_7$  から時刻  $t_{17}$  までの期間と、時刻  $t_{118}$  から時刻  $t_{28}$  までの期間とでは、各画素ユニット 150 に含まれる異なる画素 101 の画素信号が読み出される。30

### 【0076】

第 2 のモードと異なる点として、第 1 のモードでは、入力ノード 205 の容量が第 1 の容量値 C1 に制御された状態で、増幅トランジスタ 207 が画素信号を出力する。そのため、一部の期間で、制御信号 PFDINC がローレベルである。具体的には、時刻  $t_8$  から時刻  $t_{15}$  までの期間、および、時刻  $t_{19}$  から時刻  $t_{26}$  までの期間、制御信号 PFDINC1 がローレベルである。

### 【0077】

さらに、本実施例では、予備選択を行っている期間の一部でも、入力ノード 205 の容量が第 1 の容量値 C1 に制御される。具体的には、時刻  $t_2$  から時刻  $t_4$  までの期間、制御信号 PFDINC がローレベルである。予備選択の期間において、入力ノード 205 の容量を第 1 の容量値 C1 に制御することで、第 1 の画素 101 のリセット動作と、第 2 の画素 101 のリセット動作とで、入力ノード 205 のリセット後の電圧のばらつきを低減することができる。これにより、行ごとの筋状のノイズを低減することができる。40

### 【0078】

容量制御部 210 に関する動作を除いて、第 1 のモードの動作は、第 2 のモードの動作と同様である。図 7 および図 8 のステートの欄に、対応する動作を示してある。これらの動作について詳細な説明は省略する。

### 【0079】

10

20

30

40

50

実施例 1 と同様に、第 1 のモードにおいては、入力ノード 205 の容量が第 1 の容量値 C1 に制御された状態で、増幅トランジスタ 207 が画素信号を出力する。言い換えると、入力ノード 205 に容量 211 が接続されていない状態で、増幅トランジスタ 207 が画素信号を出力する。しかし、入力ノード 205 のリセット動作は、入力ノード 205 に容量 211 が接続された状態で行われる。入力ノード 205 と容量 211との間に電位差があると、入力ノード 205 へのリーク電流が発生する可能性がある。入力ノード 205 に容量 211 が接続された状態で入力ノード 205 の電圧をリセットすることにより、両者の電圧をほぼ等しくすることができる。結果として、このようなリーク電流によるノイズを低減できる。

#### 【0080】

本実施例では、画素 101 からの画素信号の読み出しの前に、入力ノード 205 のリセット動作を行う。N 行目および N + 1 行目の画素ユニット 150 の第 1 の画素 101 を例に、このリセット動作を説明する。まず、時刻 t4 において制御信号 PFDINC がハイレベルになる。このとき、制御信号 PRES はローレベルである。したがって、リセットトランジスタ 206 がオフである状態で、入力ノード 205 の容量が第 1 の容量値 C1 から、第 2 の容量値 C2 に切り替えられる。その後、時刻 t5 に制御信号 PRES がハイレベルになる。このとき、制御信号 PFDINC はハイレベルである。したがって、入力ノード 205 の容量が第 2 の容量値 C2 である状態で、リセットトランジスタ 206 がオフからオンに制御される。以上により、入力ノード 205 のリセット動作が行われる。その後、時刻 t8 に制御信号 PFDINC がローレベルになり、入力ノード 205 の容量が第 2 の容量値 C2 から、第 1 の容量値 C1 に切り替えられる。そして、時刻 t9 に制御信号 PRES がローレベルになり、リセットが解除される。以後、入力ノード 205 の容量が第 1 の容量値 C1 に制御された状態で、画素信号が出力される。

#### 【0081】

このように、本実施例では、容量制御部 210 が入力ノード 205 の容量を第 1 の容量値 C1 からそれよりも大きい第 2 の容量値 C2 に切り替えた後に、リセットトランジスタ 206 がオンする。この制御により、リセット動作による入力ノード 205 の電圧の変動を低減することができる。これはリセットトランジスタ 206 が動作する時に、入力ノード 205 の容量が大きいため、カップリングによる電圧の変動を小さくできるからである。

#### 【0082】

もし、リセット動作において入力ノード 205 の電圧が大きく変動すると、出力動作までにその電圧の変動が静定しない可能性がある。結果として、ノイズが生じる可能性がある。リセット動作による入力ノード 205 の電圧の変動を低減することで、これらのノイズを低減することができる。

#### 【0083】

図 7 および図 8 に示される動作では、先に、N 行目の画素ユニット 150 の第 1 の画素 101 (図 5 の R で示された画素) の画素信号と N + 1 行目の画素ユニット 150 の第 2 の画素 101 (図 5 の G で示された画素) の画素信号とが読み出される。次に、N 行目の画素ユニット 150 の第 2 の画素 101 (図 5 の G で示された画素) の画素信号と N + 1 行目の画素ユニット 150 の第 1 の画素 101 (図 5 の R で示された画素) の画素信号が読み出される。しかし、画素ユニット 150 の中の順番は、これらに限定されない。

#### 【0084】

変形例では、先に、N 行目の画素ユニット 150 の第 1 の画素 101 (図 5 の R で示された画素) の画素信号と N + 1 行目の画素ユニット 150 の第 1 の画素 101 (図 5 の R で示された画素) の画素信号とが並行して読み出される。その後、N 行目の画素ユニット 150 の第 2 の画素 101 (図 5 の G で示された画素) の画素信号と N + 1 行目の画素ユニット 150 の第 2 の画素 101 (図 5 の G で示された画素) の画素信号とが並行して読み出される。

#### 【0085】

10

20

30

40

50

また、さらに別の変形例では、N行目の画素ユニット150の第2の画素101の画素信号と、N+1行目の画素ユニット150の第1の画素ユニット101の画素信号とが並行に読み出される。次に、N+1行目の画素ユニット150の第2の画素101の画素信号と、N+2行目の画素ユニット150の第1の画素ユニット101の画素信号とが並行に読み出される。それから、N+2行目の画素ユニット150の第2の画素101の画素信号と、N+3行目の画素ユニット150の第1の画素ユニット101の画素信号とが並行に読み出される。このように、様々な読み出しの順序を用いることができる。

#### 【0086】

以上に説明したとおり、本実施例においては、容量制御部210が入力ノード205の容量を第1の容量値C1からそれよりも大きい第2の容量値C2に切り替えた後に、リセットトランジスタ206がオフからオンに制御される。このような構成によれば、ノイズを低減することができる。10

#### 【0087】

特に、本実施例は2つの画素101が1つの入力ノード205および1つの増幅トランジスタ207を共有している。そのため、1つの入力ノード205において、第1の画素101の画素信号を読み出した後に行われるリセット動作から、第2の画素101の画素信号の読み出しまでの期間が短い。また、予備選択を行う場合にも同様に、リセット動作から画素信号の読み出しまでの時間が短い。そのため、入力ノード205の電圧の変動を小さくすることによるノイズ低減の効果が実施例1に比較して顕著である。

#### 【0088】

##### 【実施例3】

本発明に係る撮像システムの実施例について説明する。撮像システムとして、デジタルスチルカメラ、デジタルカムコーダ、カメラヘッド、複写機、ファックス、携帯電話、車載カメラ、観測衛星などがあげられる。図9に、撮像システムの例としてデジタルスチルカメラのブロック図を示す。

#### 【0089】

図9において、1001はレンズの保護のためのバリア、1002は被写体の光学像を撮像装置1004に結像させるレンズ、1003はレンズ1002を通った光量を可変するための絞りである。1004は上述の各実施例で説明した撮像装置であって、レンズ1002により結像された光学像を画像データとして変換する。ここで、撮像装置1004の半導体基板にはA/D変換部が形成されているものとする。1007は撮像装置1004より出力された撮像データに各種の補正やデータを圧縮する信号処理部である。そして、図9において、1008は撮像装置1004および信号処理部1007に、各種タイミング信号を出力するタイミング発生部、1009はデジタルスチルカメラ全体を制御する全体制御部である。1010は画像データを一時的に記憶する為のフレームメモリ部、1011は記録媒体に記録または読み出しを行うためのインターフェース部、1012は撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体である。そして、1013は外部コンピュータ等と通信する為のインターフェース部である。ここでも、タイミング信号などは撮像システムの外部から入力されてもよく、撮像システムは少なくとも撮像装置1004と、撮像装置1004から出力された撮像信号を処理する信号処理部1007とを有すればよい。3040

#### 【0090】

本実施例では、撮像装置1004とA/D変換部とが別の半導体基板に設けられた構成を説明した。しかし、撮像装置1004とA/D変換部とが同一の半導体基板に形成されていてもよい。また、撮像装置1004と信号処理部1007とが同一の半導体基板に形成されていてもよい。

#### 【0091】

また、それぞれの画素101が第1の光電変換部101Aと、第2の光電変換部101Bを含むように構成されてもよい。信号処理部1007は、第1の光電変換部101Aで生じた電荷に基づく信号と、第2の光電変換部101Bで生じた電荷に基づく信号とを処50

理し、撮像装置 1004 から被写体までの距離情報を取得するように構成されてもよい。

#### 【0092】

撮像システムの実施例において、撮像装置 1004 には、実施例 1 乃至実施例 2 のいずれかの撮像装置が用いられる。このような構成によれば、ノイズの低減された画像を取得することができる。

#### 【0093】

##### [実施例 4]

図 10 は、車載カメラに関する撮像システムの一例を示したものである。撮像システム 2000 は、上述した実施例の撮像装置 2010 を有する。撮像システム 2000 は、撮像装置 2010 により取得された複数の画像データに対し、画像処理を行う画像処理部 2030 と、撮像システム 2000 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差算出部 2040 を有する。また、撮像システム 2000 は、算出された視差に基づいて対象物までの距離を算出する距離計測部 2050 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 2060 と、を有する。ここで、視差算出部 2040 や距離計測部 2050 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 2060 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array) や ASIC (Application Specific Integrated Circuit) などによって実現されてもよいし、これらの組合せによって実現されてもよい。

#### 【0094】

撮像システム 2000 は車両情報取得装置 2310 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 2000 は、衝突判定部 2060 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU 2410 が接続されている。また、撮像システム 2000 は、衝突判定部 2060 での判定結果に基づいて、ドライバーへ警報を発する警報装置 2420 とも接続されている。例えば、衝突判定部 2060 の判定結果として衝突可能性が高い場合、制御 ECU 2410 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 2420 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

#### 【0095】

本実施例では車両の周囲、例えば前方または後方を撮像システム 2000 で撮像する。図 10 (b) に、車両前方を撮像する場合の撮像システムを示した。また、上記では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。さらに、撮像システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム (ITS) 等、広く物体認識を利用する機器に適用することができる。

#### 【符号の説明】

#### 【0096】

101 画素

150 画素ユニット

205 入力ノード

206 リセットトランジスタ

207 増幅トランジスタ

210 容量制御部

10

20

30

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(56)参考文献 特開2010-193437(JP,A)

特開2013-051576(JP,A)

特開2015-012127(JP,A)

特開2009-017219(JP,A)

特開2016-025332(JP,A)

特開2008-079001(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30-5/378

H04N 5/222-5/257

G03B 15/00