(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4307230号

(P4307230)

(45) 発行日 平成21年8月5日(2009.8.5)

(24) 登録日 平成21年5月15日(2009.5.15)

|                       |              |

|-----------------------|--------------|

| (51) Int.Cl.          | F 1          |

| HO4N 5/32 (2006.01)   | HO4N 5/32    |

| GO1T 1/20 (2006.01)   | GO1T 1/20 E  |

| HO1L 27/146 (2006.01) | GO1T 1/20 F  |

| HO1L 27/14 (2006.01)  | GO1T 1/20 G  |

|                       | HO1L 27/14 C |

請求項の数 11 (全 27 頁) 最終頁に続く

(21) 出願番号 特願2003-408032 (P2003-408032)

(22) 出願日 平成15年12月5日 (2003.12.5)

(65) 公開番号 特開2005-175526 (P2005-175526A)

(43) 公開日 平成17年6月30日 (2005.6.30)

審査請求日 平成18年11月27日 (2006.11.27)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 遠藤 忠夫

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 吉川 潤

最終頁に続く

(54) 【発明の名称】放射線撮像装置及び放射線撮像方法

## (57) 【特許請求の範囲】

## 【請求項 1】

入射した放射線を検出する複数の画素が基板上に2次元状に配置された放射線検出回路部と、

前記放射線検出回路部を駆動させるための駆動用回路部と

を有する放射線撮像装置であって、

前記画素は、

入射した放射線を電気信号に変換するMIS型の変換素子と、

前記変換素子で変換された電気信号を読み出すソースフォロア型の第1の電界効果トランジスタと、

前記駆動用回路部により行単位で選択された前記変換素子の電気信号を前記第1の電界効果トランジスタから読み出すために設けられた第2の電界効果トランジスタと、

前記第1の電界効果トランジスタで電気信号が読み出された前記変換素子のリセットを行単位で行うために設けられた第3の電界効果トランジスタと

を含み、

前記変換素子の一方の電極は前記第3の電界効果トランジスタに接続され、前記変換素子の他方の電極は前記変換素子が変換動作を行うためのセンサバイアスを与える共通のバイアス配線に接続されており、

前記第3の電界効果トランジスタは前記リセットを行単位で行うためのリセットバイアスと前記変換素子のリフレッシュを行単位で行うためのリフレッシュバイアスとを切り替

えるスイッチに接続されており、

前記第3の電界効果トランジスタが前記駆動用回路部により行単位でオン状態とされている間に前記スイッチが前記リフレッシュバイアス側に接続されることにより前記リフレッシュが行単位で行われ、前記第3の電界効果トランジスタが前記駆動用回路部により行単位でオン状態とされている間に前記スイッチが前記リセットバイアス側に接続されることにより前記リセットが行単位で行われることを特徴とする放射線撮像装置。

【請求項2】

前記変換素子の他方の電極は、前記バイアス配線を介して前記センサバイアスと前記変換素子の電気信号をリフレッシュするための他のリフレッシュバイアスとを切り替える他のスイッチに接続されていることを特徴とする請求項1に記載の放射線撮像装置。 10

【請求項3】

前記変換素子におけるリフレッシュにおいて、前記リフレッシュバイアスは動画画像を取得するために用い、前記他のリフレッシュバイアスは静止画画像を取得するために用いることを特徴とする請求項2に記載の放射線撮像装置。

【請求項4】

前記第1の電界効果トランジスタにおけるゲート閾値電圧に応じて、前記リセットバイアス、前記リフレッシュバイアス、前記センサバイアス及び前記他のリフレッシュバイアスのうち、少なくとも1つのバイアス値を決定することを特徴とする請求項2又は3に記載の放射線撮像装置。 20

【請求項5】

前記放射線検出回路部からの出力信号を読み出す読み出し用回路部を更に有し、

前記読み出し用回路部は、前記放射線検出回路部からの出力信号を增幅する増幅手段と、増幅された出力信号を一時的に蓄積する蓄積手段と、蓄積された出力信号をシリアル変換するシリアル変換手段とを含むことを特徴する請求項1～4のいずれか1項に記載の放射線撮像装置。 30

【請求項6】

前記変換素子、前記第1の電界効果トランジスタ、前記第2の電界効果トランジスタ、及び前記第3の電界効果トランジスタがアモルファスシリコン半導体を主材料として形成されていることを特徴とする請求項1～5のいずれか1項に記載の放射線撮像装置。

【請求項7】

前記変換素子は、前記基板上に下部電極として形成された第1の金属薄膜層と、前記第1の金属薄膜層上に形成され、電子及び正孔の通過を阻止するアモルファス窒化シリコンからなる絶縁層と、当該絶縁層上に形成された水素化アモルファスシリコンからなる光電変換層と、当該光電変換層上に形成され、正孔の注入を阻止するN型の注入阻止層と、当該注入阻止層上に上部電極として形成された透明導電層又は当該注入阻止層上的一部分に形成された第2の金属薄膜層とを有して構成され、

リフレッシュモードでは、前記変換素子に対して、正孔を前記光電変換層から前記第2の金属薄膜層に導く方向に電界を与え、

光電変換モードでは、前記変換素子に対して、前記光電変換層に入射した放射線により発生した正孔を当該光電変換層に留まらせて電子を前記第2の金属薄膜層に導く方向に電界を与え、 40

前記光電変換モードにより前記光電変換層に蓄積される前記正孔もしくは前記第2の金属薄膜層に導かれた前記電子を光信号として検出することを特徴とする請求項1～6のいずれか1項に記載の放射線撮像装置。

【請求項8】

前記放射線の波長変換を行う波長変換体を更に有することを特徴とする請求項1～7のいずれか1項に記載の放射線撮像装置。

【請求項9】

前記波長変換体は、Gd<sub>2</sub>O<sub>2</sub>S、Gd<sub>2</sub>O<sub>3</sub>、CsIのいずれかを主成分とするものであることを特徴とする請求項8に記載の放射線撮像装置。 50

## 【請求項 10】

前記放射線検出回路部において、複数行の前記画素のうちの 1 行の画素における前記第 2 の電界効果トランジスタと、前記 1 行とは異なる行の画素における前記第 3 の電界効果トランジスタとが、前記 1 行のゲート配線に接続されていることを特徴とする請求項 1 ~ 9 のいずれか 1 項に記載の放射線撮像装置。

## 【請求項 11】

入射した放射線を電気信号に変換する M I S 型の変換素子と、当該電気信号を読み出すソースフォロア型の第 1 の電界効果トランジスタと、選択された前記変換素子の電気信号を前記第 1 の電界効果トランジスタから読み出すために設けられた第 2 の電界効果トランジスタと、前記変換素子のリセットを行単位で行うために設けられた第 3 の電界効果トランジスタとを備えた画素が基板上に 2 次元状に配置された放射線検出回路部と、前記放射線検出回路部を駆動させるための駆動用回路部とを有し、前記変換素子の一方の電極は前記第 3 の電界効果トランジスタに接続され、前記変換素子の他方の電極は前記変換素子が変換動作を行うためのセンサバイアスを与える共通のバイアス線に接続され、前記第 3 の電界効果トランジスタは前記リセットを行単位で行うためのリセットバイアスと前記変換素子のリフレッシュを行単位で行うためのリフレッシュバイアスとを切り替えるスイッチに接続されている放射線撮像装置における放射線撮像方法であって、

前記第 3 の電界効果トランジスタが前記駆動用回路部により行単位でオン状態とされている間に前記スイッチを前記リフレッシュバイアス側に接続することにより、前記変換素子の前記リセットを行単位で行い、

前記駆動用回路部により行単位で前記第 3 の電界効果トランジスタを駆動している間に前記スイッチを前記リセットバイアス側に接続することにより、前記変換素子の前記リセットを行単位で行うことを特徴とする放射線撮像方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、医療用の診断や工業用の非破壊検査等に用いて好適な放射線撮像装置及び放射線撮像方法に関する。なお、本明細書では、X 線、線などの電磁波や 線、線も放射線に含めるものとする。

## 【背景技術】

## 【0002】

従来、病院内などに設置されている X 線撮影システムには、患者に X 線を照射し、患者を透過した X 線をフィルムに露光するフィルム撮影方式と、患者を透過した X 線を電気信号に変換してデジタル画像処理を行う画像処理方式とがある。

## 【0003】

画像処理方式を実現するひとつの装置として、X 線を可視光に変換する蛍光体と可視光を電気信号に変換する光電変換装置とを備えた放射線撮像装置がある。患者を透過した X 線が蛍光体に照射され、蛍光体で可視光に変換された患者の体内情報を光電変換装置により電気信号として出力する。患者の体内情報が電気信号に変換されれば、その電気信号を A D コンバータでデジタル変換し、記録、表示、印刷、診断などを行うための X 線画像情報をデジタル値として扱うことができる。

## 【0004】

最近では、光電変換装置にアモルファスシリコン半導体薄膜を用いた放射線撮像装置が実用化されている。

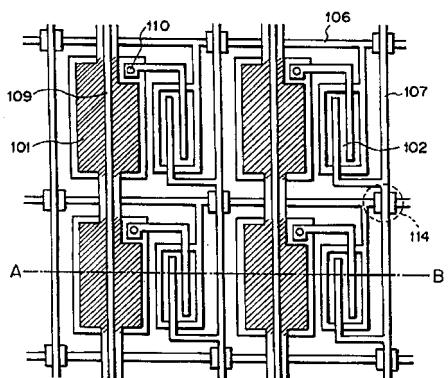

図 10 は、例えば特開平 8 - 116044 号公報（特許文献 1）に記載される、M I S 型光電変換素子とスイッチ素子の材料にアモルファスシリコン半導体薄膜を用いて構成した従来の光電変換基板の上面図であり、それらを結線する配線を含めて表している。

## 【0005】

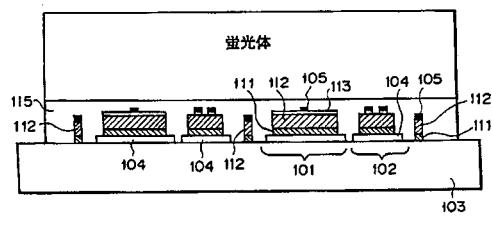

図 11 は、図 10 に示した A - B 間における断面図である。以後の説明では、簡単のために、M I S 型光電変換素子は、単に光電変換素子と呼ぶことにする。

10

20

30

40

50

図11に示すように、光電変換素子101及びスイッチ素子102（アモルファスシリコンTFT、以下単にTFTと記す）は同一基板103上に形成されており、光電変換素子101の下部電極は、TFT102の下部電極（ゲート電極）と同一の第1の金属薄膜層104で形成されており、また、光電変換素子102の上部電極は、TFT102の上部電極（ソース電極、ドレイン電極）と同一の第2の金属薄膜層105で形成されている。

#### 【0006】

また、第1及び第2の金属薄膜層104, 105は、図10に示した光電変換回路部（放射線検出回路部）内のゲート駆動用配線106及びマトリクス信号配線107にも共有して形成されている。図10においては、画素数として $2 \times 2$ の計4画素分を記載しており、図10のハッチング部は、光電変換素子101の受光面である。また、109は光電変換素子にバイアスを与える電源ラインであり、110は光電変換素子101とTFT102とを接続するためのコンタクトホールである。

#### 【0007】

アモルファスシリコン半導体を主たる材料にした図10で示されるような構成を用いれば、光電変換素子101、スイッチ素子102、ゲート駆動用配線106、マトリクス信号配線107を、同一基板上に同時に作製することができ、大面積の光電変換回路部（放射線検出回路部）が容易に、しかも安価に提供することができる。

#### 【0008】

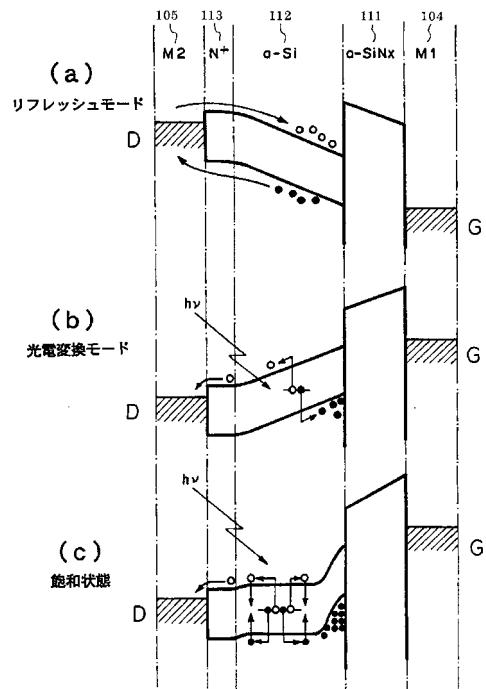

次に、光電変換素子101のデバイス動作について図12を用いて説明する。

図12(a)～(c)は、図10, 図11で示した光電変換素子101のデバイス動作を説明するためのエネルギー・バンド図である。

#### 【0009】

図12(a), (b)は、それぞれリフレッシュモード及び光電変換モードにおける動作を示しており、横軸は図11で示した各層の膜厚方向の状態を表している。ここで、M1は、例えばCrなどの第1の金属薄膜層104で形成された下部電極（G電極）である。また、アモルファス窒化シリコン(a-SiNx)絶縁薄膜層111は、電子とホールをともにその通過を阻止する絶縁層であり、トンネル効果をもたらさない程度の厚さが必要であり、通常は50nm以上で形成される。

#### 【0010】

水素化アモルファスシリコン(a-Si:H)薄膜層112は、意図的にドーパントをドープしていない真性半導体層(i層)で形成された光電変換半導体層である。また、N<sup>+</sup>層113は、水素化アモルファスシリコン薄膜層112へのホールの注入を阻止するために形成されたN型の水素化アモルファスシリコン薄膜層などの非単結晶半導体からなる単一導電型キャリアの注入阻止層である。また、M2は、例えばAlなどの第2金属薄膜層105で形成された上部電極（D電極）である。

#### 【0011】

図10では、上部電極であるD電極はN<sup>+</sup>層113を完全には覆っていないが、D電極とN<sup>+</sup>層113との間は電子の移動が自由に行われるためD電極とN<sup>+</sup>層113とは常に同電位であり、以下では、そのことを前提として説明を行う。

光電変換素子101のデバイス動作には、D電極やG電極への電圧の印可の仕方によりリフレッシュモードと光電変換モードという2種類の動作モードがある。

#### 【0012】

図12(a)に示すリフレッシュモードの場合には、D電極にはG電極に対して負の電位が与えられており、図中の黒丸で示したi層112中のホールは、電界によりD電極に導かれる。これと同時に、図中の白丸で示した電子は、i層112に注入される。この時、一部のホールと電子はN<sup>+</sup>層113、i層112において再結合して消滅する。この状態が十分に長い時間続ければ、ホールはi層112から掃き出される。

#### 【0013】

前述の状態から、図12(b)に示す光電変換モードにするためには、D電極にG電極

10

20

30

40

50

に対し正の電位を与える。これにより、i層112層中の電子は、瞬時にD電極に導かれる。しかし、ホールは、N<sup>+</sup>層113が注入阻止層として働くため、i層112に導かれないことはない。この状態でi層112に光が入射すると、光は吸収され電子ホール対が発生する。この電子は電界によりD電極に導かる。一方、ホールはi層112内を移動して、i層112とアモルファス窒化シリコン絶縁薄膜層111との界面に達するが、この絶縁層111内には移動できないため、i層112内に留まることになる。この時、電子はD電極に移動し、ホールはi層112内の絶縁層界面に移動するため、光電変換素子101内の電気的中性を保つためにG電極から電流が流れる。この電流は、光により発生した電子・ホール対に対応するため、入射した光に比例したものとなる。

## 【0014】

10

図12(b)に示した光電変換モードの状態をある期間保った後、再び、図12(a)のリフレッシュモードの状態になると、i層112に留まっていたホールは前述のようにD電極に導かれて、このホールに対応した電流が流れる。このホールの量は、光電変換モード期間に入射した光の総量に対応する。この時、i層112内に注入される電子の量に対応した電流も流れるが、この量はおよそ一定であるため、差し引いて検出すればよい。つまり、この光電変換素子101はリアルタイムに入射する光の量を出力すると同時に、ある期間に入射した光の総量も検出することができる。

## 【0015】

しかしながら、何らかの理由により光電変換モードの期間が長くなった場合や入射する光の照度が強い場合には、光の入射があるにもかかわらず電流が流れないことがある。これは、図12(c)に示すように、i層112内にホールが多数留まり、このホールによりi層112内の電界が小さくなり、発生した電子が導かれなくなつてi層112内でホールと再結合してしまうからである。この状態を光電変換素子101の飽和状態と称する。この状態で光の入射の状態が変化すると、電流が不安定に流れることもあるが、再びリフレッシュモードにすればi層112内のホールは掃き出されるため、次の光電変換モードでは再び光に比例した電流が流れる。

20

## 【0016】

また、前述の説明において、リフレッシュモードでi層112内のホールを掃き出す場合には、すべてのホールを掃き出すのが理想であるが、一部のホールを掃き出すだけでも効果があり、前述と等しい電流が得られて何ら問題はない。つまり、次の光電変換モードでの検出機会において、図12(c)の飽和状態になつていなければよく、リフレッシュモードでのD電極のG電極に対する電位、リフレッシュモードの期間及びN<sup>+</sup>層113の注入阻止層の特性を決めればよい。

30

## 【0017】

また、更にリフレッシュモードにおいて、i層112への電子の注入は必要条件でなく、D電極のG電極に対する電位は負に限定されるものでもない。ホールが多数i層112に留まっている場合には、たとえD電極のG電極に対する電位が正の電位であっても、i層112内の電界はホールをD電極に導く方向に加わるからである。また、注入阻止層であるN<sup>+</sup>層113の特性も同様に電子をi層112に注入できることが必要条件ではない。

40

## 【0018】

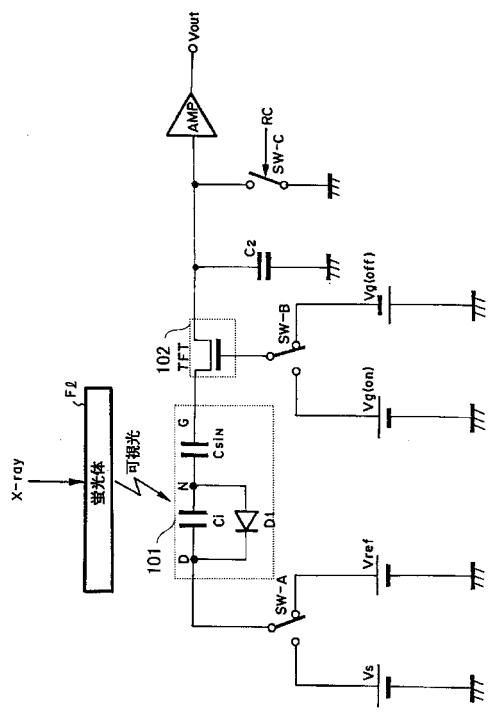

図13は、光電変換素子101とTFT102とを備えて構成される1画素分の従来における光電変換回路図である。

図13において光電変換素子101は、i層からなる容量成分のC<sub>i</sub>と注入阻止層からなる容量成分のC<sub>SiN</sub>とを含んでいる。また、i層と注入阻止層との接合点(図13中のノードN)は、光電変換素子101が飽和状態になった時、すなわちD電極とノードNの間(i層)に電界がない(小さい)状態になった時、光によって生成された電子とホールとが再結合するために、ホールキャリアをN部に蓄えることができなくなる。

## 【0019】

つまり、ノードNの電位は、D電極の電位より高くなることはない。この飽和状態にお

50

ける動作を具現化するために、図13ではダイオード(D1)を容量成分 $C_i$ に並列に接続している。すなわち、光電変換素子101は、容量成分 $C_i$ 、容量成分 $C_{SiN}$ 、ダイオードD1の3つの構成要素を有している。

#### 【0020】

図14は、図13に示した1画素分の光電変換回路における動作を示すタイムチャートである。以下に、図13、図14を用いて、光電変換素子101とTFT102で構成される画素の回路動作を説明する。

#### 【0021】

まず、リフレッシュ動作を説明する。

図13において、 $V_s$ を9V、 $V_{ref}$ を3Vに設定する。リフレッシュ動作は、スイッチSW-Aを $V_{ref}$ 、スイッチSW-Bを $V_g(on)$ 、スイッチSW-Cをオンにする。この状態にすることにより、D電極は $V_{ref}$ (6V)にバイアスされ、G電極はGND電位にバイアスされ、ノードNは最大 $V_{ref}$ (6V)にバイアスされる。ここで、最大というのは、今回のリフレッシュ動作以前の光電変換動作により、ノードNの電位が既に $V_{ref}$ 以上の電位まで蓄積されていた場合、ダイオードD1を介し $V_{ref}$ にバイアスされる。一方、以前の光電変換動作によりノードNの電位が $V_{ref}$ 以下であった場合、本リフレッシュ動作により $V_{ref}$ の電位にバイアスされることはない。実際の使用にあたっては、複数回の光電変換動作を過去に繰り返していれば、ノードNは、本リフレッシュ動作により事実上 $V_{ref}$ (6V)にバイアスされると言つてよい。

#### 【0022】

続いて、ノードNが $V_{ref}$ にバイアスされた後に、スイッチSW-Aを $V_s$ 側に切り替える。これにより、D電極は $V_s$ (9V)にバイアスされる。このリフレッシュ動作により、光電変換素子101のノードNに蓄えられていたホールキャリアがD電極側へ一掃されたことになる。

#### 【0023】

次にX-ray照射期間について説明する。

図14に示すように、X線をパルス状に照射する。検出体を透過したX線が蛍光体F1に照射され、可視光に変換される。蛍光体F1からの可視光は、半導体層(i層)に照射され光電変換される。光電変換により生成されたホールキャリアは、ノードNに蓄積され電位を上昇させる。TFT102はオフした状態なので、G電極側の電位も同じ分だけ上昇する。

#### 【0024】

wait期間は、リフレッシュ期間とX-ray照射期間との間に設けられている。特に何かを動作させているわけではなく、リフレッシュ動作直後の暗電流などで光電変換素子101の特性が不安定な状態にある場合、緩和するまでに何も動作させないために設けられた待機期間である。光電変換素子101がリフレッシュ動作直後に不安定な特性でない場合、特にwait期間を設ける必要はない。

#### 【0025】

次に、転送動作について説明する。

転送動作は、スイッチSW-Bを $V_g(on)$ 側にして、TFT102をオン状態にする。これによりX-ray照射により蓄えられたホールキャリアの量( $S_h$ )に対応する電子キャリア( $S_e$ )が、読み出し容量 $C_2$ 側からTFT102を介してG電極側に流れ、読み出し容量 $C_2$ の電位を上昇させる。この時、 $S_e$ と $S_h$ との関係は、 $S_e = S_h \times C_{SiN} / (C_{SiN} + C_i)$ である。読み出し容量 $C_2$ の電位は、同時にアンプを介し増幅して出力される。TFT102は、信号電荷を充分に転送するに足りる時間だけオンさせ、やがてオフさせる。

#### 【0026】

最後に、リセット動作について説明する。

リセット動作はスイッチSW-Cをオンさせ、読み出し容量 $C_2$ をGND電位にリセットして次回の転送動作に備える。

10

20

30

40

50

## 【0027】

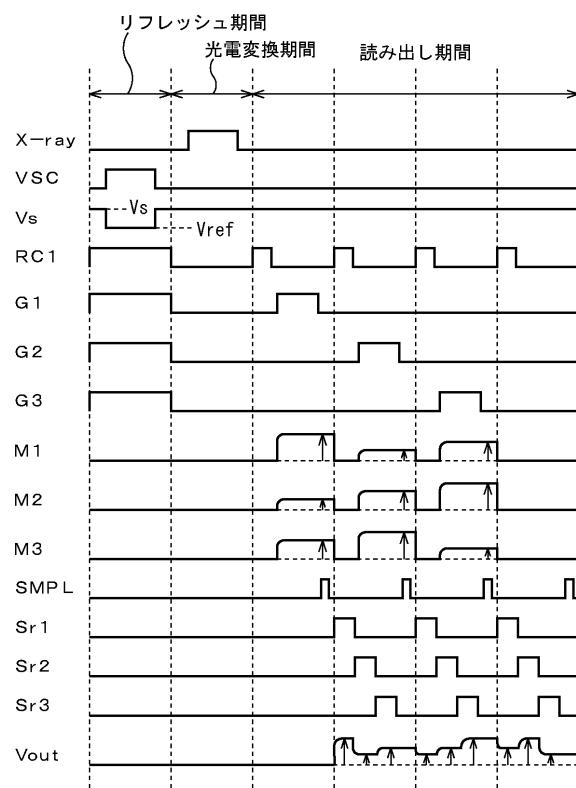

図15は、従来の光電変換装置の2次元的回路図である。

図15では説明を簡略化するために、 $3 \times 3 = 9$ 画素分のみを記載している。S1-1～S3-3は光電変換素子、T1-1～T3-3はスイッチ素子(TFT)、G1～G3はTFT(T1-1～T3-3)をオン/オフさせるためのゲート配線、M1～M3は信号配線、Vs線は光電変換素子(S1-1～S3-3)に蓄積バイアスを与えた後、リフレッシュバイアスを与えた後するための配線である。

## 【0028】

図15において、光電変換素子(S1-1～S3-3)の黒く塗りつぶされた側の電極はG電極であり、対向側はD電極である。また、D電極は、Vs線の一部と共有しているが、光を入射させる都合上、薄いN<sup>+</sup>層をD電極として利用している。光電変換素子(S1-1～S3-3)、TFT(T1-1～T3-3)、ゲート配線G1～G3、信号配線M1～M3、Vs線、これらを総じて光電変換回路部(放射線検出回路部)701と称する。

## 【0029】

Vs線は、電源Vsや電源Vrefによりバイアスされ、これらはVSCのコントロール信号により切り替えられる。SR1はゲート配線G1～G3に駆動用のパルス電圧を与えるシフトレジスタであり、TFT(T1-1～T3-3)をオンさせる電圧は外部から供給する。このとき供給される電圧は、電源Vg(on)により決定される。

## 【0030】

読み出し用回路部702は、光電変換回路部(放射線検出回路部)701内の信号配線M1～M3の並列信号出力を増幅し、直列変換して出力する。

RES1～RES3は信号配線M1～M3をリセットするスイッチ、A1～A3は信号配線M1～M3の信号を増幅するアンプ、CL1～CL3はアンプA1～A3で増幅された信号を一時的に蓄積するサンプルホールド容量、Sn1～Sn3はサンプルホールドを行うためのスイッチ、B1～B3はバッファアンプ、Sr1～Sr3は並列信号を直列変換するためのスイッチ、SR2はスイッチSr1～Sr3に直列変換するためのパルスを与えるシフトレジスタ、Abは直列変換された信号を出力するバッファアンプである。

## 【0031】

図16は、図15に示した光電変換装置の動作を示すタイムチャートである。以下、このタイムチャートを用いて図15の光電変換装置の動作について説明する。

## 【0032】

制御信号VSCは、Vs線、すなわち光電変換素子(S1-1～S3-3)のD電極に、2種類のバイアスを与えるためのものである。D電極は、制御信号VSCが“Hi”的時にVref(V)になり、制御信号VSCが“Lo”的時にVs(V)になる。読み取り用電源Vs(V)、リフレッシュ用電源Vref(V)は、それぞれ直流電源である。

## 【0033】

まず、リフレッシュ期間の動作について説明する。

シフトレジスタSR1の信号をすべて“Hi”で、かつ読み出し用回路部702のCRES信号を“Hi”的状態にする。このようにすると、スイッチング用の全TFT(T1-1～T3-3)が導通し、かつ読み出し用回路702内のスイッチ素子RES1～RES3も導通し、全光電変換素子(S1-1～S3-3)のG電極がGND電位になる。そして、制御信号VSCが“Hi”的になると、全光電変換素子(S1-1～S3-3)のD電極がリフレッシュ用電源Vref(V)にバイアスされた状態(負電位)になる。これにより、全光電変換素子(S1-1～S3-3)はリフレッシュモードとなり、リフレッシュが行われる。

## 【0034】

次に、光電変換期間について説明する。

制御信号VSCが“Lo”的状態に切り替わると、全光電変換素子(S1-1～S3-3)のD電極は読み取り用電源Vsにバイアスされた状態(正電位)になる。このように

10

20

30

40

50

すると光電変換素子 (S1-1～S3-3) は光電変換モードになる。この状態でシフトレジスタ S R 1 の信号をすべて “Lo” で、かつ読み出し用回路部 702 の C R E S 信号を “Lo” の状態にする。これにより、スイッチング用の全 T F T (T1-1～T3-3) がオフし、かつ読み出し用回路 702 内のスイッチ素子 R E S 1～R E S 3 もオフし、全光電変換素子 (S1-1～S3-3) の G 電極は、直列的にはオープン状態になるが、光電変換素子 (S1-1～S3-3) は容量成分も構成要素として有しているため電位は保持される。

#### 【0035】

ここまで時点では、光電変換素子 (S1-1～S3-3) に光が入射されていないために電荷は発生しない。すなわち電流は流れない。この状態で、光源がパルス状にオンすると、それぞれの光電変換素子 (S1-1～S3-3) の D 電極 (N<sup>+</sup>電極) に光が照射され、いわゆる光電流が流れる。光源については、図 15 中に特に記載はしていないが、例えば、複写機であれば蛍光灯、L E D、ハロゲン灯等である。X 線撮影装置であれば文字通り X 線源であり、この場合は X 線可視変換用のシンチレータを用いればよい。また、光によって流れた光電流は、電荷としてそれぞれの光電変換素子 (S1-1～S3-3) 内に蓄積され、光源がオフ後も保持される。

#### 【0036】

次に、読み出し期間について説明する。

読み出し動作は、1 行目の光電変換素子 (S1-1～S1-3)、続いて、2 行目の光電変換素子 (S2-1～S2-3)、続いて、3 行目の光電変換素子 (S3-1～S3-3) の順で行われる。

#### 【0037】

まず、1 行目の光電変換素子 (S1-1～S1-3) を読み出すためにスイッチ素子の T F T (T1-1～T1-3) のゲート配線 G 1 に S R 1 からゲートパルスを与える。この時、ゲートパルスのハイレベルは、外部から供給されている電圧 V (on) である。これにより、T F T (T1-1～T1-3) がオン状態になり、1 行目の光電変換素子 (S1-1～S1-3) に蓄積されていた信号電荷が、信号配線 M 1～M 3 に転送される。

#### 【0038】

信号配線 M 1～M 3 には、特に図 15 中には記載していないが読み出し容量が付加されており、信号電荷は T F T (T1-1～T1-3) を介し、読み出し容量に転送されることになる。例えば、信号配線 M 1 の付加されている読み出し容量は、信号配線 M 1 に接続されている各 T F T (T1-1～T3-1) のゲート / ソース間の電極間容量 (Cgs) の総和 (3 個分) であり、図 13 における容量成分 C<sub>2</sub> に相当する。また、信号配線 M 1～M 3 に転送された信号電荷は、アンプ A 1～A 3 で増幅される。そして C R E S 信号をオンさせることにより、サンプルホールド容量 C L 1～C L 3 に転送され、C R E S 信号をオフするとともにホールドされる。

#### 【0039】

続いて、シフトレジスタ S R 2 からスイッチ S r 1, S r 2, S r 3 の順番で、パルスを印加することにより、サンプルホールド容量 C L 1～C L 3 にホールドされていた信号が、サンプルホールド容量 C L 1, C L 2, C L 3 の順でアンプ A b から出力される。結果として、光電変換素子 (S1-1～S1-3) の 1 行分の光電変換信号が順次出力される。2 行目の光電変換素子 (S2-1～S2-3) の読み出し動作、3 行目の光電変換素子 (S3-1～S3-3) の読み出し動作も同様に行われる。

#### 【0040】

1 行目の S M P L 信号により信号配線 M 1～M 3 の信号をサンプルホールド容量 C L 1～C L 3 にサンプルホールドすれば、信号配線 M 1～M 3 を C R E S 信号により G N D 電位にリセットし、その後、ゲート配線 G 2 にゲートパルスを印加することができる。すなわち、1 行目の信号を、シフトレジスタ S R 2 にて直列変換動作をする間に、同時に 2 行目の光電変換素子 (S2-1～S2-3) の信号電荷をシフトレジスタ S R 1 にて転送することができる。

10

20

30

40

50

以上の動作により、第1行から第3行までの全ての光電変換素子（S1-1～S3-3）の信号電荷を出力することができる。

【0041】

前述したX線撮像装置の動作は、リフレッシュ動作を行い、X線を照射し、そして読み出し動作を行うことにより、いわば1枚の静止画像を取得するための動作である。また、連続した動画像を取得する場合には、図16で記載したタイムチャートを取得したい動画の枚数分だけ繰り返して動作させればよい。

【0042】

【特許文献1】特開平8-116044号公報

【特許文献2】特開平11-307756号公報

10

【発明の開示】

【発明が解決しようとする課題】

【0043】

しかしながら、特に画素数が多いX線撮像装置で動画像を得ようとした場合には、更なるフレーム周波数の改善が必要となってくる。光電変換素子のリフレッシュ動作が全光電変換素子に共通のV<sub>S</sub>線を介して行われる場合には、1フレームに1回のリフレッシュ期間を設けることが必須となる。このことは、特に、動画像を取得する際、フレーム周波数が小さくなる、すなわち動作スピードが遅くなるという問題を生じる。

【0044】

一般的に、胸部の単純撮影において必要とされるスペックとして、撮影領域が40cm角以上、画素ピッチが200μm以下と言われている。仮に、撮影領域を40cm角、画素ピッチを200μmとしてX線撮像装置を作製した場合には、光電変換素子の数が4百万個にも及ぶ。こういった大多数の画素を、一括でリフレッシュすることは、リフレッシュ時に流れる電流も大きくなるため、X線撮像装置のGNDや電源ラインの電圧変動を大きくすることになり、安定した撮像を行うことができない。

20

【0045】

要求される画像によっては、これらの変動分が緩和するまでX線照射の待ち時間を設ける必要もある。図16では記載していないが、図14におけるwait期間がそれに相当する。つまり、光電変換装置を一括でリフレッシュすることは、1フレームに1回のリフレッシュ期間を設けるだけでなく、1フレームに1回のwait期間をも必要となる。

30

【0046】

以上述べてきたように、1フレームの読み出し動作毎に、1回の全光電変換素子のリフレッシュ動作を行う従来技術においては、動画撮影を困難にしているといった問題を有している。

【0047】

また、撮影領域が40cm角もの大面積になると、信号配線M1～M3の容量は50pF～100pFにも及ぶ。そして、撮影画素が200μmピッチで配列されたとすると、その画素容量は1pF～3pF程度である。仮に、信号配線の容量が100pF、画素容量が2pFであるとして、TFTを介して転送動作を行うと、その前後で信号電圧が2pF/(2pF+100pF)=1/50に減少することになる。これと同様に雑音電圧も減少するが、後段の読み出し用回路部702における雑音成分、例えば抵抗の熱雑音やトランジスタのショット雑音などのいわゆる回路雑音が零ではないために、結果としてシステムのS/Nとしては低下するという問題もある。

40

【0048】

このシステムとしてのS/Nの低下を少しでも補うためには、読み出し用回路部702の初段部の回路ノイズを低下させなければならない。具体的には、初段部分をかなりの低ノイズ設計を施されたアンプで作りこまなければならない。これを実現しようとすると、アンプを構成するトランジスタの素子サイズが巨大化して、その結果、チップサイズが大きくなる。これにより、消費電流が増大し、発熱による冷却機構を搭載しなければならないといった2次的な問題をも誘発してしまう。

50

## 【0049】

このS/Nの低下を解決するための1つの方法として、光電変換素子からの信号電位をTFTのゲートに入力させ、このTFTをソースフォロアとして出力する方法が特開平11-307756号公報（特許文献2）に提案されている。この場合、光電変換素子の出力信号は低下することなく、読み出し用回路に入力されるため、S/Nが有利である。

## 【0050】

しかしながら、ソースフォロアのTFTのゲート端子には、光電変換素子の蓄積電荷による電圧が長時間印加されている。一般に、アモルファスシリコンを主たる材料にしたTFTは、ゲート端子への電界ストレスにより、TFTがオンするための指標となるゲート閾値電圧（ $V_{th}$ ）が変動してしまうといった問題がある。

10

## 【0051】

特許文献2に記載されているような回路構成においては、光電変換素子の蓄積電荷によるソースフォロアのゲート端子電圧 $V_g$ に対して、出力信号はそのTFTの閾値電圧 $V_{th}$ 分だけ低下してソース端子から出力される。すなわち、 $V_g - V_{th}$ の信号電圧が出力されることになる。この電圧は、読み出し回路部に入力されることになる。一般に、結晶シリコンで構成される読み出し回路（集積IC）の入力端子に印加できる絶対最大定格は、その光電源電圧に対し、0.5V程度である。ソースフォロアのTFTにおける閾値電圧 $V_{th}$ が変動した場合、読み出し回路の入力定格を超える危険性があり、しいては読み出し回路を破壊してしまうという問題が生じる。

## 【0052】

20

最近の半導体プロセスは微細化が進み、ニーズの面においても低電源電圧、低消費電流の方向に向かっており、読み出し回路の電源電圧も、5V単一電源が多くなってきている。すなわち、読み出し回路への入力電圧も0Vから5V内外の仕様が多く、ソースフォロア型TFTの閾値電圧 $V_{th}$ の変動は、極めて低く抑えなければならないといった制限がある。実際にTFTの閾値電圧 $V_{th}$ は、工場出荷時（TFT作製時）においてもばらつきがあり、また、動作させている過程において変化していくものである。特許文献2においては、このTFTの閾値電圧 $V_{th}$ における変動の問題に関する解決手段は何ら記載されてはいない。

## 【0053】

30

また、特許文献2における光電変換素子は、PIN型フォトダイオードで形成されている。このPIN型フォトダイオードは、MIS型光電変換素子において必要なリフレッシュ動作が必要ないため、リフレッシュ動作に付随した動画撮影に困難であるといった問題は少ないものと思われる。しかしながら、PI接合とIN接合といった2つの接合が必要となり、ダーク電流が増大してしまうという問題がある。特に、P層は光電変換素子に特有の層であり、同一基板上に作り込む他のTFTの作製プロセスとは全く別である。このことは、TFTと光電変換素子とを別々に作製しなければならないために積層構造となってしまい、歩留まりやコストの点で不利となる。

## 【0054】

40

本発明は上述の問題点を解決するためになされたものであり、GNDや電源ラインの電圧変動を抑え、かつフレーム毎の待機時間を無くして、安定かつ高速な動画撮影を行うことを可能とするとともに、低コストでダーク電流の少ない放射線撮像装置及び放射線撮方法を提供することを目的とする。

## 【課題を解決するための手段】

## 【0055】

本発明の放射線撮像装置は、入射した放射線を検出する複数の画素が基板上に2次元状に配置された放射線検出回路部と、前記放射線検出回路部を駆動させるための駆動用回路部とを有する放射線撮像装置であって、前記画素は、入射した放射線を電気信号に変換するMIS型の変換素子と、前記変換素子で変換された電気信号を読み出すソースフォロア型の第1の電界効果トランジスタと、前記駆動用回路部により行単位で選択された前記変換素子の電気信号を前記第1の電界効果トランジスタから読み出すために設けられた第2

50

の電界効果トランジスタと、前記第1の電界効果トランジスタで電気信号が読み出された前記変換素子のリセットを行単位で行うために設けられた第3の電界効果トランジスタとを含み、前記変換素子の一方の電極は前記第3の電界効果トランジスタに接続され、前記変換素子の他方の電極は前記変換素子が変換動作を行うためのセンサバイアスを与える共通のバイアス配線に接続されており、前記第3の電界効果トランジスタは前記リセットを行単位で行うためのリセットバイアスと前記変換素子のリフレッシュを行単位で行うためのリフレッシュバイアスとを切り替えるスイッチに接続されており、前記第3の電界効果トランジスタが前記駆動用回路部により行単位でオン状態とされている間に前記スイッチが前記リフレッシュバイアス側に接続されることにより前記リフレッシュが行単位で行われ、前記第3の電界効果トランジスタが前記駆動用回路部により行単位でオン状態とされている間に前記スイッチが前記リセットバイアス側に接続されることにより前記リセットが行単位で行われる。

## 【0056】

本発明の放射線撮像装置における他の態様は、前記放射線検出回路部において、複数行の前記画素のうちの1行の画素における前記第2の電界効果トランジスタと、前記1行とは異なる行の画素における前記第3の電界効果トランジスタとが、前記1行のゲート配線に接続されている。

## 【0057】

また、本発明の放射線撮像装置におけるその他の態様は、前記変換素子の他方の電極は、前記バイアス配線を介して前記センサバイアスと前記変換素子の電気信号をリフレッシュするための他のリフレッシュバイアスとを切り替える他のスイッチに接続されている。

また、本発明の放射線撮像装置におけるその他の態様は、前記変換素子におけるリフレッシュにおいて、前記リフレッシュバイアスは動画画像を取得するために用い、前記他のリフレッシュバイアスは静止画画像を取得するために用いる。

## 【0058】

また、本発明の放射線撮像装置におけるその他の態様は、記第1の電界効果トランジスタにおけるゲート閾値電圧(Vth)に応じて、前記リセットバイアス、前記リフレッシュバイアス、前記センサバイアス及び前記他のリフレッシュバイアスのうち、少なくとも1つのバイアス値を決定する。

## 【0059】

また、本発明の放射線撮像装置におけるその他の態様は、前記放射線検出回路部からの出力信号を読み出す読み出し用回路部を更に有し、前記読み出し用回路部は、前記放射線検出回路部からの出力信号を增幅する増幅手段と、増幅された出力信号を一時的に蓄積する蓄積手段と、蓄積された出力信号をシリアル変換するシリアル変換手段とを含む。

## 【0060】

また、本発明の放射線撮像装置におけるその他の態様は、前記変換素子、前記第1の電界効果トランジスタ、前記第2の電界効果トランジスタ、及び前記第3の電界効果トランジスタがアモルファスシリコン半導体を主材料として形成されている。

## 【0061】

また、本発明の放射線撮像装置におけるその他の態様は、前記変換素子は、前記基板上に下部電極として形成された第1の金属薄膜層と、前記第1の金属薄膜層上に形成され、電子及び正孔の通過を阻止するアモルファス窒化シリコンからなる絶縁層と、当該絶縁層上に形成された水素化アモルファスシリコンからなる光電変換層と、当該光電変換層上に形成され、正孔の注入を阻止するN型の注入阻止層と、当該注入阻止層上に上部電極として形成された透明導電層又は当該注入阻止層上的一部分に形成された第2の金属薄膜層とを有して構成され、リフレッシュモードでは、前記変換素子に対して、正孔を前記光電変換層から前記第2の金属薄膜層に導く方向に電界を与え、光電変換モードでは、前記変換素子に対して、前記光電変換層に入射した放射線により発生した正孔を当該光電変換層に留まらせて電子を前記第2の金属薄膜層に導く方向に電界を与え、前記光電変換モードにより前記光電変換層に蓄積される前記正孔もしくは前記第2の金属薄膜層に導かれた前記電

子を光信号として検出する。

【0062】

また、本発明の放射線撮像装置におけるその他の態様は、前記放射線の波長変換を行う波長変換体を更に有する。

【0063】

また、本発明の放射線撮像装置におけるその他の態様は、前記波長変換体は、 $Gd_2O_3$ 、 $Gd_2O_3$ 、 $CsI$ のいずれかを主成分とするものである。

【0064】

本発明の放射線撮像方法は、入射した放射線を電気信号に変換するMIS型の変換素子と、当該電気信号を読み出すソースフォロア型の第1の電界効果トランジスタと、選択された前記変換素子の電気信号を前記第1の電界効果トランジスタから読み出すために設けられた第2の電界効果トランジスタと、前記変換素子のリセットを行単位で行うために設けられた第3の電界効果トランジスタとを備えた画素が基板上に2次元状に配置された放射線検出回路部と、前記放射線検出回路部を駆動させるための駆動用回路部とを有し、前記変換素子の一方の電極は前記第3の電界効果トランジスタに接続され、前記変換素子の他方の電極は前記変換素子が変換動作を行うためのセンサバイアスを与える共通のバイアス線に接続され、前記第3の電界効果トランジスタは前記リセットを行単位で行うためのリセットバイアスと前記変換素子のリフレッシュを行単位で行うためのリフレッシュバイアスとを切り替えるスイッチに接続されている放射線撮像装置における放射線撮像方法であって、前記第3の電界効果トランジスタが前記駆動用回路部により行単位でオン状態とされている間に前記スイッチを前記リフレッシュバイアス側に接続することにより、前記変換素子の前記リフレッシュを行単位で行い、前記駆動用回路部により行単位で前記第3の電界効果トランジスタを駆動している間に前記スイッチを前記リセットバイアス側に接続することにより、前記変換素子の前記リセットを行単位で行う。

【発明の効果】

【0065】

本発明によれば、電気信号が読み出された変換素子を行単位でリフレッシュ（又はリセット）するようにしたので、GNDや電源ラインの電圧変動を抑え、かつフレーム毎の待機時間を無くして、安定かつ高速な動画撮影を行うことができる。また、変換素子をMIS型で構成しているため、PIN型で構成する場合と比較して、ダーク電流を抑えることができるとともに、当該放射線撮像装置の作製を低コストで行うことができる。本発明における放射線撮像装置の実現により、特に将来の高齢化社会において現在よりも更に質の高い医療環境を作ることができる。

【0066】

また、変換素子の電気信号をソースフォロア型の第1の電界効果トランジスタを介して読み出すようにしたので、変換素子の出力信号を減少させることなく読み出すことができ、従来の放射線撮像装置に比べてS/Nを高くすることができる。また、第1の電界効果トランジスタの閾値電圧（ $V_{th}$ ）に応じて、リセットバイアス、第1のリフレッシュバイアス、センサバイアス及び第2のリフレッシュバイアスのうち、少なくとも1つのバイアス値を決定するようにしたので、例えば放射線撮像装置の使用途中で第1の電界効果トランジスタの閾値電圧（ $V_{th}$ ）が変化した場合でも、それに合わせてリセットバイアス等を変化させてその変動分を補うことができるため、変換素子の電気信号を安定的に出力することができ、信頼性の高い放射線撮像装置とすることができます。

【0067】

また、画素を構成する変換素子、第1の電界効果トランジスタ、第2の電界効果トランジスタ及び第3の電界効果トランジスタをアモルファスシリコン半導体を主材料として形成するようにしたので、変換素子と各電界効果トランジスタとを同一基板上に作製することができ、製造における放射線撮像装置の歩留まりを向上させることができる。

【発明を実施するための最良の形態】

【0068】

10

20

30

40

50

次に、本発明の放射線撮像装置及び放射線撮像方法の実施形態について図面を参照しながら説明する。なお、本発明の実施形態においては、放射線撮像装置として、従来例と同様にMIS型光電変換素子と電界効果トランジスタの半導体材料としてアモルファスシリコン半導体薄膜を用いた光電変換アレイが形成された基板を有する装置を例に挙げて説明する。また、本発明の実施形態においては、放射線としてX線を適用した実施例の説明を行うが、本発明はこれに限定されるわけではなく、 $\gamma$ 線などの電磁波や $\alpha$ 線、 $\beta$ 線なども含まれる。

#### 【0069】

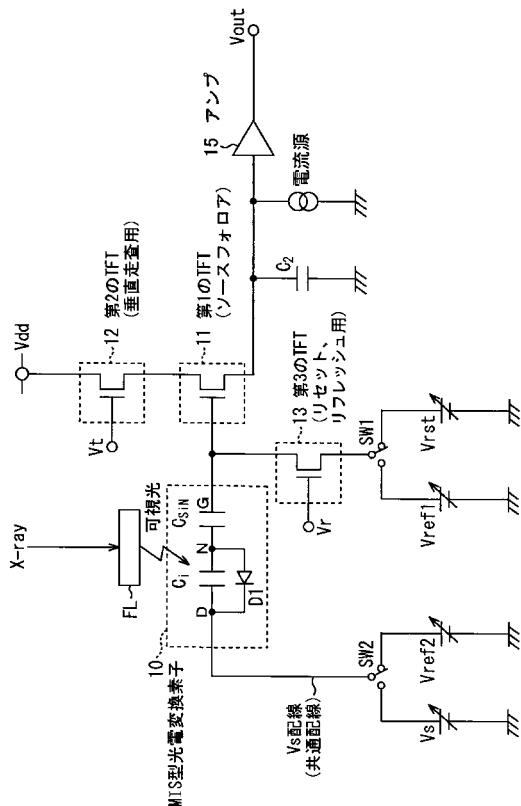

図1は、本発明の実施形態におけるX線撮像装置の1画素分の等価回路図である。

図1に示すように、MIS型の光電変換素子10は、半導体光電変換層としての水素化アモルファスシリコンなどのi層からなる容量成分 $C_i$ と、アモルファス窒化シリコンなどの絶縁層（両導電型のキャリアの注入阻止層）からなる容量成分 $C_{SiN}$ とを含んでいる。また、このi層と絶縁層との接合点（図1中のノードN）は、光電変換素子10が飽和状態になった時、すなわちD電極とノードNの間（i層）に電界がない（小さい）状態になった時、光によって生成された電子とホールとが再結合するために、ホールキャリアがN部に蓄えることができなくなる。

#### 【0070】

つまり、ノードNの電位は、D電極の電位より高くなることはない。この飽和状態における動作を具現化するために、図1ではダイオード（D1）を容量成分 $C_i$ に並列に接続している。すなわち、光電変換素子10は容量成分 $C_i$ 、容量成分 $C_{SiN}$ 、ダイオードD1の3つの構成要素を有している。

#### 【0071】

$V_{ref1}$ は光電変換素子10を第3のTFT（13）を介してリフレッシュするための第1のリフレッシュバイアス、 $V_{rst}$ は同様に第3のTFT（13）を介して光電変換素子10をリセットするためのリセットバイアスであり、これらのバイアスの切り替えは、第1のスイッチSW1を選択することにより行われる。第3のTFT（13）は、光電変換素子10をリセット又はリフレッシュするための電界効果トランジスタであり、スイッチ素子として機能する。また、 $V_s$ は光電変換素子10のD電極に各光電変換素子に共通の $V_s$ 配線を介して光電変換素子10の光電変換動作を行うための電圧を供給するセンサバイアス、 $V_{ref2}$ は光電変換素子10を各光電変換素子に共通の $V_s$ 配線を介してリフレッシュするための第2のリフレッシュバイアスであり、これらのバイアスの切り替えは、第2のスイッチSW2を選択することにより行われる。この第1のリフレッシュバイアス $V_{ref1}$ 、リセットバイアス $V_{rst}$ 、センサバイアス $V_s$ 、第2のリフレッシュバイアス $V_{ref2}$ は、すべて可変電源である。

#### 【0072】

第1のTFT（11）は、光電変換素子10に蓄積された信号電位を低減させることなく、アンプ15側へ出力するための電界効果トランジスタであり、光電変換素子10のG電極がゲート端子に接続されたソースフォロア型となっている。第2のTFT（12）は、第1のTFT（11）のドレイン端子に選択的にドレインバイアス $V_{dd}$ を与えるための電界効果トランジスタであり、スイッチ素子として機能する。容量成分 $C_2$ は、第1のTFT（11）のソース端子に寄生する読み出し容量である。FLは、X線を吸収して可視光に変換する蛍光体である。

#### 【0073】

蛍光体FLで変換された可視光は、MIS型の光電変換素子10に照射され、この光電変換素子で電子や正孔に光電変換される。蛍光体FLは、前述したように、X線波長を可視領域波長に変換するための波長変換用の蛍光体であり、直接又は間接的にTFTと密着した位置に配置されている。この蛍光体FLの母体材料には、 $Gd_2O_2S : Tb$ や $Gd_2O_3 : Tb$ 、 $CsI : Tl$ 、 $CsI : Na$ などが用いられる。また、光電変換素子10、第1のTFT（11）、第2のTFT（12）、第3のTFT（13）は、アモルファスシリコンを主たる材料として作製されている。

10

20

30

40

50

## 【0074】

本発明の実施形態では、光電変換素子10に蓄えられた信号電荷をソースフォロア接続された第1のTFT(11)を介してアンプ15側へ出力する際に、この第1のTFT(11)のゲート閾値電圧V<sub>th</sub>が例えば使用過程において変動し、当該閾値電圧における変動の出力への影響を、リセットバイアスV<sub>rst</sub>の変更することにより軽減もしくは無くすようとする。

## 【0075】

例えば、光電変換素子10のリセット電圧をV<sub>rst1</sub>とし、第1のTFT(11)の閾値電圧をV<sub>th1</sub>とすると、その出力電圧はダーク状態(信号電荷が零)の場合には、(V<sub>rst1</sub>) - (V<sub>th1</sub>)となる。また、信号電荷V<sub>sig</sub>が蓄積された場合には、出力電圧は(V<sub>rst1</sub>) + (V<sub>sig</sub>) - (V<sub>th1</sub>)となる。

10

## 【0076】

例えば、使用3年を過ぎた時に、その第1のTFT(11)の閾値電圧V<sub>th2</sub>が初期の閾値電圧V<sub>th1</sub>に対して+2V変化し、信号電荷V<sub>sig</sub>が蓄積された場合には、その出力電圧は(V<sub>rst1</sub>) + (V<sub>sig</sub>) - (V<sub>th2</sub>)、すなわち(V<sub>rst1</sub>) + (V<sub>sig</sub>) - (V<sub>th1</sub>) - 2となり、出力電圧が閾値電圧の変化量分の2Vだけ低く出力されることになる。これは、正しく信号検出がされないという問題を生じ、場合によつてはアンプ15(後述する信号読み出し用回路部)の入力定格をオーバーし、装置の故障を誘発する危険性もある。本発明の実施形態では、前述したように、リセットバイアスV<sub>rst</sub>を第1のTFT(11)の閾値電圧V<sub>th</sub>の変化分と等しいバイアス分だけ変化させることにより、この問題を解決している。

20

## 【0077】

第1のTFT(11)の閾値電圧V<sub>th</sub>の変化分は、予め光を照射しない暗状態で得た出力レベルと、既知のV<sub>rst</sub>レベルから算出してもよいし、実験的に得た「使用時間と閾値電圧V<sub>th</sub>との変化量」の関数から算出してもよい。第1のリフレッシュバイアスV<sub>ref1</sub>は、第3のTFT(13)を介して光電変換素子10をリフレッシュするための電源であるが、リセットバイアスV<sub>rst</sub>の変化分だけ同様に変化させることにより、第1のTFT(11)における閾値電圧V<sub>th</sub>の変化後においても同様のリフレッシュを行うことができる。

## 【0078】

30

光電変換素子10内に蓄積されたキャリアがホールキャリアである場合、リフレッシュするための条件は、(V<sub>ref1</sub>) > (V<sub>rst</sub>)の関係でなければならない。閾値電圧V<sub>th</sub>の変化分をV<sub>th</sub>とし、(V<sub>th</sub>) << (V<sub>ref1</sub>) - (V<sub>rst</sub>)であれば、第1のリフレッシュバイアスV<sub>ref1</sub>を変化させる必要性は少ない。

## 【0079】

V<sub>s</sub>はセンサバイアスであるが、第1のTFT(11)の閾値電圧V<sub>th</sub>が変化することにより第1のリフレッシュバイアスV<sub>ref1</sub>を変化させた場合に、光電変換素子10の半導体層(Ci)に加わる電位差が変化する。この電位差は飽和電荷量を決定する。この飽和電荷量は、常に一定に設定するほうが望ましい。すなわち、V<sub>th</sub>の分だけリセットバイアスV<sub>rst</sub>や第1のリフレッシュバイアスV<sub>ref1</sub>と同様、センサバイアスV<sub>s</sub>も変化させることが望ましい。

40

## 【0080】

V<sub>ref2</sub>は、光電変換素子10をリフレッシュするための第2のリフレッシュバイアスであり、第2のスイッチSW2を切り替えることにより、V<sub>s</sub>配線(共通配線)からリフレッシュを行うための電圧を供給する。このときの第3のTFT(13)はオンしており、かつ、第1のスイッチSW1は、リセットバイアスV<sub>rst</sub>側となっている。すなわち、リフレッシュ中のD電極はV<sub>ref2</sub>であり、G電極はV<sub>rst</sub>となっている。このリセットバイアスV<sub>rst</sub>を閾値電圧V<sub>th</sub>により変化させているため、第2のリフレッシュバイアスを用いる際には、この第2のリフレッシュバイアスV<sub>ref2</sub>をリセットバイアスV<sub>rst</sub>と同様に変化させることが望ましい。

50

## 【0081】

第2のリフレッシュバイアス  $V_{ref2}$  を用いる方式のリフレッシュでは、  $V_s$  配線が共通とされているために、1回のリフレッシュの操作によって莫大な電荷が移動し、系の  $GND$  電位や基準電位が変動し、その回復を待たなければ次の読み出し動作を行うことができない。この待ち時間は、40cm角の光電変換素子を構成した場合には、0.5秒程度から数秒にも及ぶ。したがって、第2のリフレッシュバイアス  $V_{ref2}$  を用いるリフレッシュは、動きがある動画撮影には不適である。本実施形態では、動画撮影には第1のリフレッシュバイアス  $V_{ref1}$  を用いたリフレッシュを行い、静止画撮影には第2のリフレッシュバイアス  $V_{ref2}$  を用いたリフレッシュを行う。

## 【0082】

10

以上説明したように、本実施形態では、第1のTFT(11)における閾値電圧  $V_{th}$  の変化に応じた分だけ、リセットバイアス  $V_{rst}$  を変化させる。また、これに応じて、第1のリフレッシュバイアス  $V_{ref1}$ 、センサバイアス  $V_s$ 、第2のリフレッシュバイアス  $V_{ref2}$  も変化させるようとする。

## 【0083】

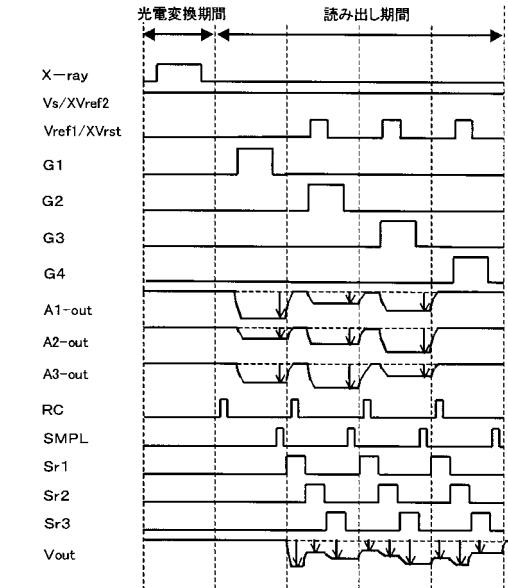

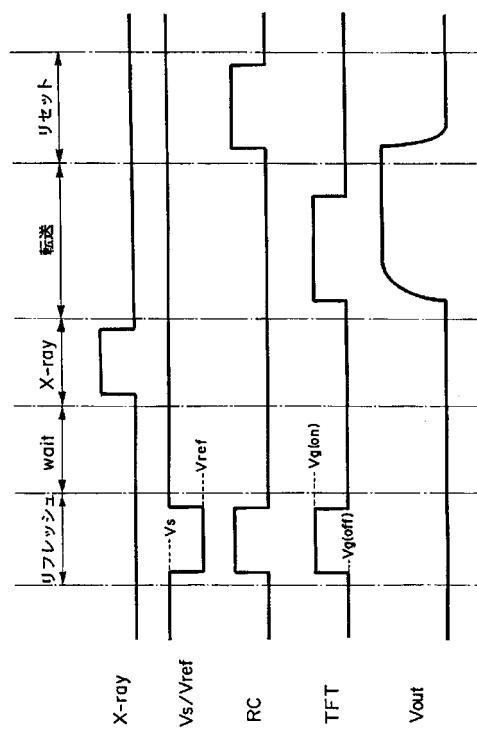

図2は、図1に示したX線撮像装置の動作を示すタイムチャートである。図2に示すように、動作期間は、X-ray照射期間、読み出し期間、リフレッシュ期間、リセット期間の4つの期間に分けられる。

## 【0084】

20

まず、X-ray照射期間について説明する。

図2に示すように、X線はパルス状に照射される。被検出体を透過したX線が蛍光体FLに照射され、この蛍光体FLで可視光に変換される。蛍光体で変換された可視光は、続いて、光電変換素子10の半導体層(i層)に照射されて、そこで光電変換される。光電変換により生成されたホールキャリアはi層と絶縁層(注入阻止層)界面に蓄えられ、ノードNの電位を上昇させる。また、G電極側の電位も同じ分だけ上昇する。なお、X-ray照射期間では、第1のスイッチSW1はリセットバイアス  $V_{rst}$  側に、第2のスイッチSW2はセンサバイアス  $V_s$  側になっている。

## 【0085】

次に、読み出し期間について説明する。

読み出し動作は、図1の第2のTFT(12)におけるゲート端子  $V_t$  に電圧を与え、スイッチ素子としてオン状態とすることにより行われる。X-ray照射により蓄えられたホールキャリアの量( $S_h$ )に対応する電位が第1のTFT(11)のゲートに印加されているため、第2のTFT(12)がオンすることにより、第1のTFT(11)のドレイン-ソース間に電流として流れることになる。これにより、アンプ15に出力信号が入力される。このとき、第3のTFT(13)のゲート閾値電圧  $V_{th}$  により、ゲートに印加されていた電位よりも  $V_{th}$  分だけシフトした出力信号が出力される。

30

## 【0086】

次に、リフレッシュ動作について説明する。

図2では、容量成分  $C_i$  と容量成分  $C_{SiN}$  とが等しい場合のD電極、G電極、ノードNの電位を表記している。リフレッシュ動作は、第3のTFT(13)のゲート端子  $V_r$  に信号を入力してスイッチ素子としてオン状態とし、また、第1のスイッチSW1を第1のリフレッシュバイアス  $V_{ref1}$  側に接続することにより行われる。このとき、ノードGの電位が高くなるが、同時にノードNの電位も  $C_i = C_{SiN}$  により半分の勾配で上昇する。ただし、ノードNの電位は、 $V_s = 9V$  を超えることはない。ノードNの電位を上昇させることにより、ノードNに蓄えられた信号電荷(ホールキャリア)の一部が、D電極側に吐き出される。すなわち、光電変換素子10のリフレッシュ動作が行われる。

40

## 【0087】

次に、リセット動作について説明する。

リセット動作は、第3のTFT(13)のゲート端子  $V_r$  に信号を入力してスイッチ素子としてオン状態とし、また、第1のスイッチSW1をリセットバイアス  $V_{rst}$  側にに

50

接続することにより行われる。この操作により、光電変換素子 10 の G 電極がリセットバイアス  $V_{rst}$  にリセットされる。このリセット動作において、ノード N の電位は、リフレッシュ動作時の電位（図 2 では  $V_s$ ）から減衰する。その減衰量  $V_N$  は、容量成分  $C_i$  と容量成分  $C_{SiN}$  とが等しい場合、第 1 のリフレッシュバイアス  $V_{ref1}$  とリセットバイアス  $V_{rst}$  の電位差の  $1/2$  になる。ノード N の減衰量  $V_N$  は、次回の光電変換動作で蓄えられるホールキャリア、すなわち飽和電荷量を決定する。

#### 【0088】

ここで、従来例を示した図 14 では wait 期間を設けているが、本実施形態の図 2 ではこの wait 期間を設けていない。その理由について図 3, 図 4 を用いて説明する。

#### 【0089】

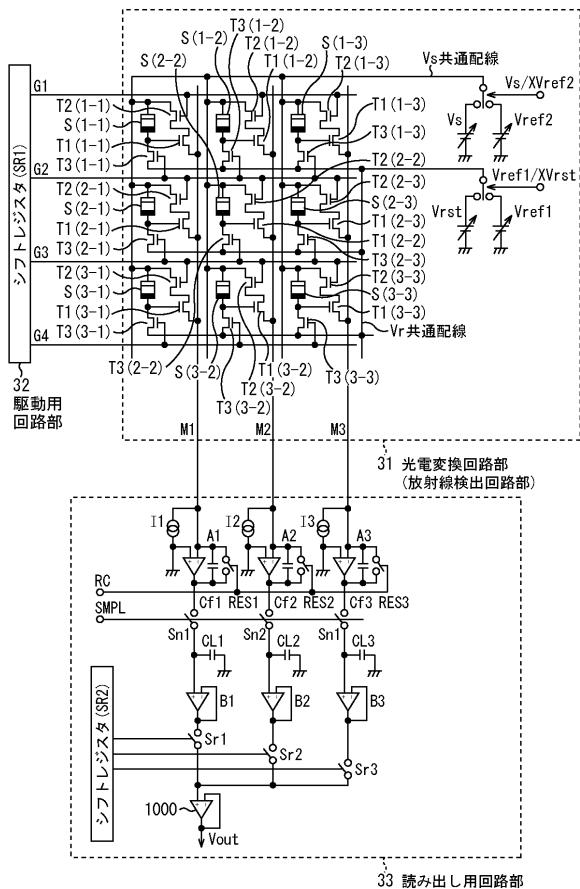

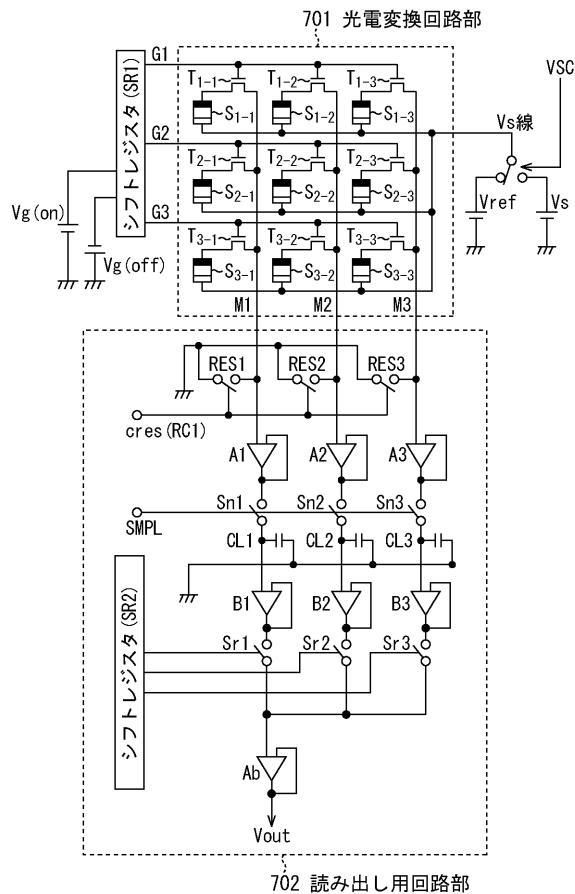

図 3 は、本発明の実施形態における X 線撮像装置の 2 次元的回路図である。

図 3 には、説明を簡単化するために  $3 \times 3 = 9$  画素分を記載している。S(1-1) ~ S(3-3) は光電変換素子である。T1(1-1) ~ T1(3-3) は光電変換素子 10 の G 電極がゲート端子に接続された第 1 の TFT、T2(1-1) ~ T2(3-3) は走査において光電変換素子の電気信号を行単位に選択的に読み出しするため設けられた第 2 の TFT、T3(1-1) ~ T3(3-3) は電気信号を読み出された光電変換素子をリフレッシュ又はリセットするために設けられた第 3 の TFT である。

#### 【0090】

G1 ~ G4 は、第 2 の TFT である T2(1-1) ~ T2(3-3) や、第 3 の TFT である T3(1-1) ~ T3(3-3) をオン / オフさせるためのゲート配線であり、M1 ~ M3 は信号配線である。Vs 共通配線は、光電変換素子 S(1-1) ~ S(3-3) の D 電極にセンサバイアス (Vs) 又は第 2 のリフレッシュバイアス (Vref2) を与えるための全画素に共通の配線である。また、Vr 共通配線は、光電変換素子 S(1-1) ~ S(3-3) の G 電極にリセットバイアス (Vrst) 又は第 1 のリフレッシュバイアス (Vref1) を与えるための全画素に共通の配線である。

#### 【0091】

光電変換素子 S(1-1) ~ S(3-3) の黒く塗りつぶされた側の電極は G 電極であり、対向側は D 電極である。D 電極は、Vs 共通配線の一部と共有しているが、光を入射させる都合上、薄い  $N^+$  層を D 電極として利用している。光電変換素子 S(1-1) ~ S(3-3)、第 1 の TFT (T1(1-1) ~ T1(3-3))、第 2 の TFT (T2(1-1) ~ T2(3-3))、第 3 の TFT (T3(1-1) ~ T3(3-3))、ゲート配線 G1 ~ G3、信号配線 M1 ~ M3、Vs 共通配線、Vr 共通配線、センサバイアス Vs、第 2 のリフレッシュバイアス Vref2、リセットバイアス Vrst、第 1 のリフレッシュバイアス Vref1、これらを総じて光電変換回路部（放射線検出回路部）31 と称する。

#### 【0092】

シフトレジスタ SR1 は、ゲート配線 G1 ~ G4 に駆動用のパルス電圧を与え、光電変換素子 S(1-1) ~ S(3-3) の電気信号を行単位で第 1 の TFT (T1(1-1) ~ T1(3-3)) から読み出すために、第 2 の TFT (T2(1-1) ~ T2(3-3)) や第 3 の TFT (T3(1-1) ~ T3(3-3)) をオン / オフさせる駆動用回路部 32 である。

#### 【0093】

読み出し用回路部 33 は、光電変換回路部 31 からの並列の出力信号を読み取り、直列変換して出力するものである。A1 ~ A3 は信号配線 M1 ~ M3 と反転端子 ( - ) をそれぞれ接続するオペアンプである。この反転端子 ( - ) と出力端子の間には、それぞれ容量素子 Cf1 ~ Cf3 が接続されている。また、信号配線 M1 ~ M3 には、それぞれ電流源 I1 ~ I3 が接続されている。容量素子 Cf1 ~ Cf3 は、第 2 の TFT (T2(1-1) ~ T2(3-3)) がオンしたときに、光電変換素子 S(1-1) ~ S(3-3) の電気信号を蓄積する。RES1 ~ RES3 は容量素子 Cf1 ~ Cf3 をリセットするスイッチであり、容量素子 Cf1 ~ Cf3 と並列に接続されている。図 3 では、リセットバイアスは、GND で表記している。CL1 ~ CL3 は、オペアンプ A1 ~ A3 や容量素子 Cf1 ~ Cf3

10

20

30

40

50

$f_3$  で蓄積された信号を一時的に記憶するサンプルホールド容量である。また、 $S_{n1} \sim S_{n3}$  はサンプルホールド容量  $CL_1 \sim CL_3$  でサンプルホールドを行うためのスイッチ、 $B_1 \sim B_3$  はバッファアンプ、 $S_{r1} \sim S_{r3}$  は並列信号を直列変換するためのスイッチ、 $SR_2$  は  $S_{r1} \sim S_{r3}$  に直列変換するためのパルスを与えるシフトレジスタ、 $1000$  は直列変換された信号を出力するアンプである。

#### 【0094】

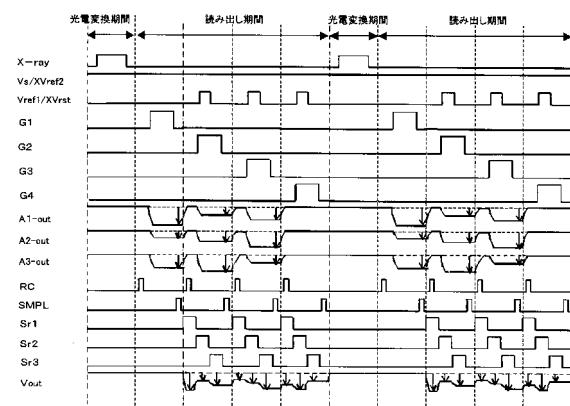

図4は、図3に示したX線撮像装置の動作を示すタイムチャートであり、2フレーム分の動作を表している。図4のタイムチャートには、光電変換期間と読み出し期間の2つの動作期間で示されている。

#### 【0095】

まず、光電変換期間について説明する。

全光電変換素子  $S(1-1) \sim S(3-3)$  のD電極は、読み取り用電源  $V_s$  (正電位)にバイアスされた状態にある。シフトレジスタ  $SR_1$  の信号はすべて“Lo”であり、第2のTFTである  $T_2(1-1) \sim T_2(3-3)$  及び第3のTFTである  $T_3(1-1) \sim T_3(3-3)$  はオフとなっている。この状態でX線がパルス的に入射すると、蛍光体を介して各光電変換素子のD電極 ( $N^+$ 電極) に可視光が照射され、各光電変換素子のi層内で電子とホールのキャリアが生成される。このとき、電子はセンサバイアス  $V_s$  によりD電極に移動するが、ホールは光電変換素子内のi層と絶縁層の界面に蓄えられ、X線の照射を停止した後においても保持される。

#### 【0096】

次に、読み出し期間について説明する。

読み出し動作は、1行目の光電変換素子 ( $S_{1-1} \sim S_{1-3}$ )、続いて、2行目の光電変換素子 ( $S_{2-1} \sim S_{2-3}$ )、続いて、3行目の光電変換素子 ( $S_{3-1} \sim S_{3-3}$ ) の順で行われる。

#### 【0097】

まず、1行目の光電変換素子 ( $S_{1-1} \sim S_{1-3}$ ) を読み出すために、シフトレジスタ  $SR_1$  からゲート配線  $G_1$  にゲートパルスを与え、1行目の第2のTFT ( $T_2(1-1) \sim T_2(1-3)$ ) をオンさせる。これにより、1行目の光電変換素子 ( $S_{1-1} \sim S_{1-3}$ ) の信号電荷に応じた電位がゲート端子に印加された1行目の第1のTFT ( $T_1(1-1) \sim T_1(1-3)$ ) にドレイン電流が流れ、読み出し用回路部33の初段部のオペアンプ  $A_1 \sim A_3$  に接続されている容量素子  $C_{f1} \sim C_{f3}$  に当該電流が流入して積分されることになる。

#### 【0098】

オペアンプ  $A_1 \sim A_3$  の出力端子は、光電変換素子の信号量に応じて図4に示されるように変化する。1行目の第2のTFT ( $T_2(1-1) \sim T_2(1-3)$ ) が同時にオンするため、オペアンプ  $A_1 \sim A_3$  の出力は同時に変化する。すなわち並列出力である。その状態で、「SMP L」信号をオンさせることにより、オペアンプ  $A_1 \sim A_3$  の出力信号はサンプルホールド容量  $CL_1 \sim CL_3$  に転送され、SMP L信号をオフするとともに一旦ホールドされる。続いて、シフトレジスタ  $SR_2$  からスイッチ  $S_{r1} \sim S_{r3}$  の順番でパルスを印加する、 $CL_2, CL_3$  の順でアンプ  $1000$  から出力される。この結果、1行目の光電変換素子 ( $S_{1-1} \sim S_{1-3}$ ) の光電変換信号が順次、直列変換されて出力される。2行目の光電変換素子 ( $S_{2-1} \sim S_{2-3}$ ) の読み出し動作、3行目の光電変換素子 ( $S_{3-1} \sim S_{3-3}$ ) の読み出し動作も同様に行われる。

#### 【0099】

1行目のSMP L信号によりオペアンプ  $A_1 \sim A_3$  の信号をサンプルホールド容量  $CL_1 \sim CL_3$  にサンプルホールドすれば、1行目の光電変換素子 ( $S_{1-1} \sim S_{1-3}$ ) の信号は光電変換回路部31から出力されることになる。したがって、読み出し用回路部33内でスイッチ  $S_{r1} \sim S_{r3}$  により直列変換されている出力される最中に、光電変換回路部31内の1行目の光電変換素子 ( $S_{1-1} \sim S_{1-3}$ ) のリフレッシュ動作やリセット動作、容量素子  $C_{f1} \sim C_{f3}$  のリセット動作を行うことができる。

10

20

30

40

50

## 【0100】

本実施形態では、1行目の光電変換素子(S1-1～S1-3)のリフレッシュ動作は2行目の光電変換素子(S2-1～S2-3)の読み出し動作と同時にを行う。これを実現するために、1行目の第3のTFT(T3(1-1)～T3(1-3))を制御するゲート配線と、2行目の第2のTFT(T2(2-1)～T2(2-3))を制御するゲート配線は同じゲート配線G2で共有としている。

## 【0101】

ゲート配線G2がオンしている間に、Vref1/XVrst信号が「Hi」になることにより、Vr共通配線がVref1にバイアスされ、1行目の光電変換素子(S1-1～S1-3)がリフレッシュされる。その後、同様に、ゲート配線G2がオンしている間に、Vref1/XVrst信号が「Lo」になることにより、Vr共通配線がリセットバイアスVrstにバイアスされ、1行目の光電変換素子(S1-1～S1-3)のG電極がリセットバイアスVrstによりリセットされる。このゲート配線G2がオンしている間は、同時に、2行目の第2のTFT(T2(2-1)～T2(2-3))がオン状態になっており、2行目の光電変換素子(S2-1～S2-3)の信号電荷に応じた電位が同様に読み出されることになる。このように、本実施形態では、n行目の光電変換素子の読みだし動作と、n-1行目の光電変換素子のリフレッシュ動作及びリセット動作を同時に行っている。

## 【0102】

以上の動作により、第1行から第3行のすべての光電変換素子S(1-1)～S(3-3)の信号電荷を出力することができる。

前述した動作を行って、光電変換期間と読み出し期間とを繰り返すことにより、連続した動画像を取得することができる。本実施形態で示したタイムチャートが従来例で示した図16のタイムチャートと異なるところは、リフレッシュ期間を設けていないところであり、その分だけ動画像を取得する際のフレーム周波数を大きくすることができる。また、従来例では、すべての光電変換素子を一括でリフレッシュしていたため、リフレッシュ時の暗電流成分による、GNDや電源などの変動を緩和させるためのwait期間を設ける必要があった。本実施形態では、各行単位でリフレッシュを行うために、一度にリフレッシュする光電変換素子の数がはるかに少ないため、別途にwait期間を設ける必要がなく、その分だけ動画のフレーム周波数を大きくすることができる。

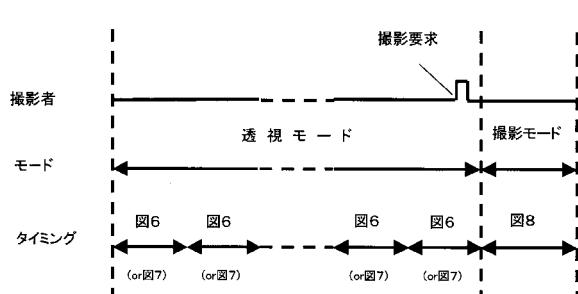

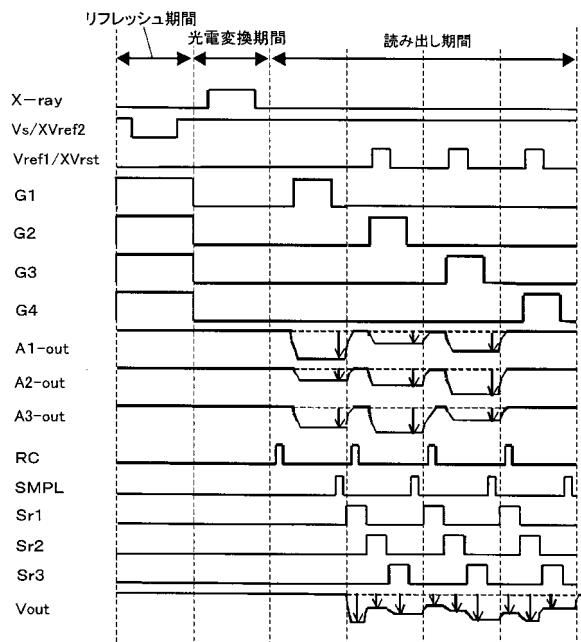

## 【0103】

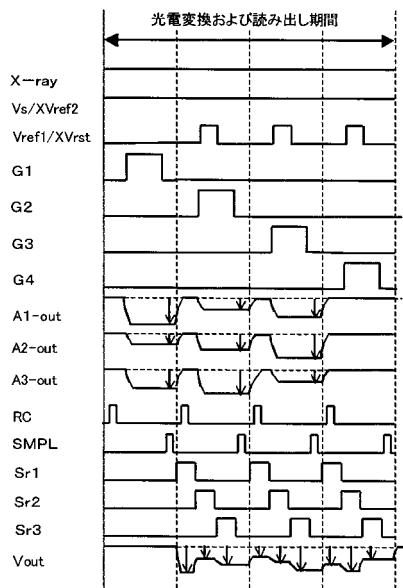

図5は、本発明の実施形態におけるX線撮像装置の撮影シーケンスを示した図である。図5では、透視モード(動画モード)で動作させている状態から、撮影者の静止画の撮影要求により、撮影モード(静止画モード)へ遷移して撮影を行うシーケンスを示している。

## 【0104】

また、図6は、図5に示したX線撮像装置の透視モード(動画モード)のタイムチャートである。つまり透視モードにおいては、図6のタイミング動作を繰り返している。この期間、撮影者は、静止画像を撮影のための被写体(患者)の位置や角度を決めるために、患者の透視画像をモニターしている。一般的に、この期間中のX線量は弱めに照射している。撮影者がX線撮像装置に曝射要求信号(静止画像を撮影する意思信号)を発令すると、透視モードから撮影モードに遷移する。撮影モードにおける動作タイミングを図8に示す。また、透視モードと撮影モードの流れは、図5に示すような撮影モードが1回だけとは限らず、撮影する被写体の撮影構図に応じ、透視モード 撮影モード 透視モード 撮影モード・・・と何回も繰り返してもよい。

## 【0105】

図7は、図5の透視モードにおけるタイムチャートが、図6とは異なる場合の例を示したタイムチャートである。図6との違いは、X線をパルス状に照射させないことである。これにより、読み出し期間と光電変換期間とを同時にを行うことができるため、透視モードにおける動作周波数を大きくできる利点がある。また、X線をパルス状に入射させないと

10

20

30

40

50

め、X線発生源に対する負荷を軽減できる利点もある。

【0106】

本発明のX線撮像装置を透視装置に応用した場合において、透視モードにおいては第3のTFT(T3(1-1)~T3(3-3))を介して第1のリフレッシュバイアスVref1を与える、透視撮影によって位置決めなどを決定し、静止画撮影モードに遷移した際には、Vs共通配線から第2のリフレッシュバイアスVref2を与える。Vs共通配線からのリフレッシュは、全画素一括で行うため、リフレッシュ動作後のGNDや系の基準電位の変動が大きくなり、その電位変動を待たなければ読み出し動作が行えないといった短所があるため、動画撮影(透視)には不適である。しかし、この反面、TFTを介在していないため、Vs共通配線と第2のリフレッシュバイアスVref2の電位差を大きくできるために、飽和電荷を大きく設定できる長所がある。つまり、診断画像を得るような静止画撮影には高いS/Nが求められ、第2のリフレッシュバイアスVref2で共通配線Vs側からリフレッシュした方が好適である。

【0107】

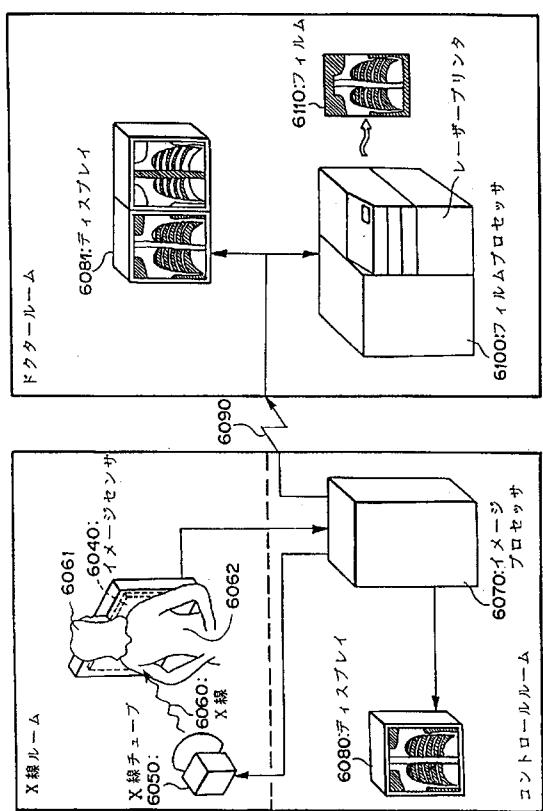

図9は、本発明の実施形態におけるX線撮像装置のX線診断システムへの適用例を示した概略図である。

X線チューブ6050で発生したX線6060は、患者あるいは被験者6061の胸部6062を透過し、放射線撮像装置(イメージセンサ)6040に入射する。この入射したX線には、被験者6061の体内部の情報が含まれている。X線の入射に対応して蛍光体で可視光に変換し、さらに、これを光電変換して電気信号を得る。この電気信号は、デジタル変換されてイメージプロセッサ6070により画像処理され、制御室のディスプレイ6080で観察される。

【0108】

また、この画像情報は、電話回線6090等の伝送手段により遠隔地へ転送することができ、ドクタールームなどの別の場所でディスプレイ6081に表示もしくは光ディスク等の保存手段に保存することができ、遠隔地の医師が診断することも可能である。また、この画像情報をフィルムプロセッサ6100によりフィルム6110に記録することもできる。

【0109】

以上の実施形態では、X線撮像装置、X線撮像システムを例にして説明を行ってきたが、 $\gamma$ 、 $\beta$ 、 $\alpha$ 線等の放射線を光に変換し、この光を光電変換する装置に適用することも可能である。また、本発明の光電変換素子アレイは、通常の可視光や赤外光を検出する撮像装置に用いることもできる。また、本発明に用いることができる電界効果トランジスタとしては、水素化アモルファスシリコンなどの非単結晶半導体を用いてチャネル領域を形成した薄膜トランジスタが好ましく用いられ、その形態は下ゲートスタガー型に限定されることなく、上ゲートスタガー型、上ゲートコプラナー型などであってもよい。

【0110】

また、本実施形態におけるMIS型光電変換素子10は、図11に示した光電変換素子101と同様な層構成で形成されている。すなわち、絶縁基板103上に下部電極として形成された第1の金属薄膜層104と、当該第1の金属薄膜層上に電子及び正孔の通過を阻止するアモルファス室化シリコンからなる絶縁層111と、当該絶縁層上に水素化アモルファスシリコンからなる光電変換層112と、当該光電変換層上に正孔の注入を阻止するN型の注入阻止層113と、当該注入阻止層上に上部電極として形成された透明導電層又は当該注入阻止層上的一部分に形成された第2の金属薄膜層105とを有して形成されている。また、MIS型光電変換素子10のデバイス動作としては、図12に示すように、リフレッシュモード(図12(a))では、正孔を光電変換層112から第2の金属薄膜層105に導く方向に電界を与える、光電変換モード(図12(b))では、光電変換層112に入射した放射線により発生した正孔を当該光電変換層に留ませて電子を第2の金属薄膜層105に導く方向に電界を与える。そして、光電変換モードにより光電変換層112に蓄積される正孔もしくは第2の金属薄膜層105に導かれた電子を光信号として検

出する。

【0111】

本発明の実施形態によれば、読み出されたMIS型光電変換素子10を行単位でリフレッシュ（又はリセット）するようにしたので、全画素を一括でリフレッシュする従来のX線撮像装置と比較して、リフレッシュされる光電変換素子10の数を少なくできるため、各リフレッシュ動作直後に流れる過渡電流を少なくすることができ、GNDや電源ラインの電圧変動を抑え、かつフレーム毎の待機時間を無くして、安定かつ高速な動画撮影を行うことができる。また、光電変換素子10をMIS型で構成しているため、PIN型で構成する場合と比較して、P層を形成する必要がなくダーク電流を抑えることができるとともに、当該放射線撮像装置の作製を低コストで行うことができる。

10

【0112】

また、変換素子の電気信号をソースフォロア型の第1の電界効果トランジスタを介して読み出すようにしたので、変換素子の出力信号を減少させることなく読み出すことができ、従来の放射線撮像装置に比べてS/Nを高くすることができる。これにより、従来例で示したような読み出し用回路部の初段部におけるアンプを低ノイズ設計が施されたものとする必要が無くなって素子サイズを大きくしなくてもよいため、消費電流が少なく、発熱量を抑えた読み出し用回路部を実現できる。これは、装置の複雑な放熱機構を簡素化でき、装置形状の設計自由度を増大させる。

【0113】

また、リセットバイアスVrstのバイアス値を可変できるようにしたので、第3のTFT(13)を介してMIS型光電変換素子10を任意の電圧でリセットできる。これにより、第1のTFT(11)のゲート端子に印加される蓄積開始電圧をVrstに決定することができるため、第1のTFT(11)の閾値電圧(Vth)がいかなる電圧であっても、読み出し用回路部33に出力される電圧レベルを蓄積開始時点では(Vrst)-(Vth)に調整することができる。これは、第1のTFT(11)の閾値電圧(Vth)が変化した場合でもその変化分を補うことができるため、MIS型光電変換素子10の電気信号を安定的に出力することができ、信頼性の高い放射線撮像装置とすることができます。

20

【0114】

また、本実施形態では、MIS型光電変換素子10を第3のTFT(13)を介して、第1のリフレッシュバイアスVref1でリフレッシュを行うが、MIS型光電変換素子10に蓄積されたホールキャリアをリフレッシュする場合、(Vrst) < (Vref1)の関係になければならない。したがって、本実施形態では、第1のTFT(11)の閾値電圧(Vth)に応じてリセットバイアスVrstを変更できるようしているが、第1のリフレッシュバイアスVref1も同様に変更することができる。

30

【0115】

また、画素を構成する光電変換素子10、第1のTFT(11)、第2のTFT(12)及び第3のTFT(13)をアモルファスシリコン半導体を主材料として形成するようにしたので、光電変換素子と各電界効果トランジスタとを同一基板上に作製することができ、製造における放射線撮像装置の歩留まりを向上させることができる。

40

【図面の簡単な説明】

【0116】

【図1】本発明の実施形態におけるX線撮像装置の1画素分の等価回路図である。

【図2】図1に示したX線撮像装置の動作を示すタイムチャートである。

【図3】本発明の実施形態におけるX線撮像装置の2次元的回路図である。

【図4】図3に示したX線撮像装置の動作を示すタイムチャートである。

【図5】本発明の実施形態におけるX線撮像装置の撮影シーケンスを示した図である。

【図6】図5に示したX線撮像装置の透視モード（動画モード）のタイムチャートである。

【図7】図5に示したX線撮像装置の透視モード（動画モード）の他のタイムチャートで

50

ある。

【図 8】図 5 に示した X 線撮像装置の撮影モード（静止画モード）のタイムチャートである。

【図 9】本発明の実施形態における X 撮像装置の X 線診断システムへの適用例を示した概略図である。

【図 10】光電変換素子とスイッチ素子の材料にアモルファスシリコン半導体薄膜を用いて構成した光電変換基板の上面図である。

【図 11】図 10 の A - B 間における断面図である。

【図 12】図 10 , 図 11 で示した光電変換素のデバイス動作を説明するためのエネルギー 10 バンド図である。

【図 13】光電変換素子と TFT を備えて構成される画素の 1 画素分の光電変換回路図である。

【図 14】図 13 に示した画素の 1 画素分の光電変換回路における動作を示すタイムチャートである。

【図 15】従来の X 線撮像装置の 2 次元的回路図である。

【図 16】従来の X 線撮像装置の動作を示すタイムチャートである。

【符号の説明】

【0117】

100、S(1 - 1) ~ S(3 - 3) 光電変換素子

111、T1(1 - 1) ~ T1(3 - 3) 第 1 の TFT (ソースフォロア接続)

20

122、T2(1 - 1) ~ T2(3 - 3) 第 2 の TFT (スイッチ機能)

133、T3(1 - 1) ~ T3(3 - 3) 第 3 の TFT (スイッチ機能)

15 アンプ

31 光電変換回路部 (放射線検出回路部)

32 駆動用回路部

33 読み出し用回路部

101 光電変換素子

102 スイッチ素子 (TFT)

103 絶縁基板

104 第 1 の金属薄膜層

30

105 第 2 の金属薄膜層

106 ゲート駆動用配線

107 マトリクス信号配線

110 コンタクトホール部

111 a - SiN 絶縁薄膜層

112 a - Si 半導体薄膜層

113 N<sup>+</sup>層

114 配線クロス部

115 保護膜

701 光電変換回路部 (放射線検出回路部)

40

702 読み出し用回路部

1000、A1 ~ A3、B1 ~ B3 オペアンプ

Cf1 ~ Cf3 積分容量

I1 ~ I3 電流源

FL X 線を可視光に変換する蛍光体

G1 ~ G3 ゲート駆動配線

M1 ~ M3 マトリクス信号配線

RES1 ~ RES3 Cf1 ~ Cf3 に形成される負荷容量をリセットするスイッチ

Sn1 ~ Sn3 読み出し容量に信号を転送するための転送スイッチ

Sr1 ~ Sr3 読み出し容量の信号を順次読み出すための読み出し用スイッチ

50

S R 1、S R 2 シフトレジスタ

V ref 1 第1のリフレッシュバイアス

V ref 2 第2のリフレッシュバイアス

V s 光電変換素子のセンサバイアス

V rst リセットバイアス

S W 1 第1のスイッチ

S W 2 第2のスイッチ

S 1 - 1 ~ S 3 - 3 光電変換素子

T 1 - 1 ~ T 3 - 3 スイッチ素子

V ref リフレッシュバイアス

V s 光電変換素子のセンサバイアス

V g (on) TFTをオンするための電源

V g (off) TFTをオフするための電源

S W - A 光電変換素子のVs配線に与えるバイアスを切り替えるスイッチ

S W - B TFTをオン/オフするためのスイッチ

S W - C 信号配線をリセットするためのスイッチ

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 8 】

【 図 9 】

【 図 1 0 】

- 101: 光電変換素子

- 102: スイッチング素子(TFT)

- 106: ゲート駆動用配線

- 107: マトリクス信号配線

- 110: コンタクトホール部

- 114: 配線クロス部

【図11】

- 101:光電変換素子

102:スイッチング素子(TFT)

103:絶縁基板

104:第1の金属薄膜層

105:第2の金属薄膜層

111:a-SiNx絶縁薄膜層

112:a-Si半導体薄膜層

113:N<sup>+</sup>層

115:保護膜

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(51)Int.Cl.

F I

H 01L 27/14

K

(56)参考文献 特開2003-324213 (JP, A)

特開平10-125891 (JP, A)

特開2003-078124 (JP, A)

特開平08-116044 (JP, A)

特開平09-064332 (JP, A)

特開平10-150182 (JP, A)

特開2000-004399 (JP, A)

特開2001-196572 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 04N 5/30 - 5/335

G 01T 1/20 - 1/24

H 01L 27/14 - 27/146

H 01L 31/09