(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 699 24 233 T2 2006.03.30

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 046 232 B1

(51) Int Cl.<sup>8</sup>: H03M 3/02 (2006.01)

(21) Deutsches Aktenzeichen: 699 24 233.9

(86) PCT-Aktenzeichen: PCT/US99/00580

(96) Europäisches Aktenzeichen: 99 903 040.6

(87) PCT-Veröffentlichungs-Nr.: WO 99/035746

(86) PCT-Anmeldetag: 11.01.1999

(87) Veröffentlichungstag

der PCT-Anmeldung: 15.07.1999

(97) Erstveröffentlichung durch das EPA: 25.10.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 16.03.2005

(47) Veröffentlichungstag im Patentblatt: 30.03.2006

(30) Unionspriorität:

5355 09.01.1998 US

(84) Benannte Vertragsstaaten:

CH, DE, ES, FI, FR, GB, IT, LI, SE

(73) Patentinhaber:

Qualcomm, Inc., San Diego, Calif., US

(72) Erfinder:

MATHE, Karl-Axel, Lennart, San Diego, US

(74) Vertreter:

WAGNER & GEYER Partnerschaft Patent- und

Rechtsanwälte, 80538 München

(54) Bezeichnung: RAUSCHUNTERDRÜCKUNGSSCHALTUNG UND QUADATUR- ABWÄRTSUMSETZER

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung**

Hintergrund der Erfindung

I. Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung betrifft die Kommunikationstechnik. Insbesondere betrifft die vorliegende Erfindung eine neue und verbesserte Rauschunterdrückungsschaltung und einen Quadraturabwärtsumsetzer.

II. Beschreibung des verwandten Standes der Technik

**[0002]** In vielen modernen Kommunikationssystemen wird eine digitale Übertragung aufgrund einer verbesserten Effizienz und der Fähigkeit verwendet, Übertragungsfehler zu erfassen und zu korrigieren. Beispielhafte digitale Übertragungsformate umfassen eine binäre Phasenlagenmodulation (BPSK – binary phase shift keying), eine Vierphasen-Umtastung (QPSK – quaternary phase shift keying), eine Offset-Vierphasen-Umtastung (OQPSK – offset quaternary phase shift keying), eine m-wertige Phasenumtastung (m-PSK – m-ary phase shift keying) und eine Quadratur-Amplitudenmodulation (QAM – quadrature amplitude modulation). Beispielhafte Kommunikationssysteme, die eine digitale Übertragung verwenden, umfassen Kommunikationssysteme mit CDMA-Verfahren (CDMA – code division multiple access bzw. Codemultiplex-Vielfachzugriff) und HDTV-Systeme (HDTV, high definition television bzw. hochauflösendes Fernsehen). Die Verwendung von CDMA-Techniken in einem Mehrfachzugriffs-Kommunikationssystem wird offenbart in dem U.S. Patent Nr. 4,901,307 mit dem Titel „Spread Spectrum Multiple Access Communication System Using Satellite or Terrestrial Repeaters“ und dem U.S. Patent Nr. 5,103,459 mit dem Titel „System and Method for Generating Waveforms in a CDMA Cellular Telephone System“, die beide dem Anmelder der vorliegenden Erfindung erteilt wurden und durch Bezugnahme hier enthalten sind. Ein Beispielhaftes HDTV-System ist in U.S. Patent Nr. 5,452,104, U.S. Patent Nr. 5,107,345 und U.S. Patent Nr. 5,021,891, alle drei mit dem Titel „Adaptive Block Size Image Compression Method and System“, und U.S. Patent Nr. 5,576,767 mit dem Titel „Interframe Video Encoding and Decoding System“ offenbart, wobei alle vier Patente dem Anmelder der vorliegenden Erfindung erteilt wurden und durch Bezugnahme hier enthalten sind.

**[0003]** In dem CDMA-System kommuniziert eine Basisstation mit einer oder mehreren entfernten Station(en). Die Basisstation befindet sich typischerweise an einem festen Ort. Somit ist der Stromverbrauch eine weniger wichtige Überlegung bei der Gestaltung der Basisstation. Die entfernten Stationen sind typischerweise Verbrauchereinheiten, die in einer gro-

ßen Anzahl hergestellt werden. Somit sind aufgrund der Anzahl der hergestellten Einheiten Kosten und Zuverlässigkeit wichtige Gestaltungsüberlegungen. Darüber hinaus ist in manchen Anwendungen, wie einem CDMA-Mobilkommunikationssystem, aufgrund der tragbaren Eigenschaft der entfernten Station der Stromverbrauch kritisch. Bei der Gestaltung der entfernten Stationen werden normalerweise Kompromisse zwischen Leistung, Kosten und Stromverbrauch eingegangen.

**[0004]** Bei der digitalen Übertragung werden die digitalisierten Daten verwendet, um eine Träger-Sinuskurve unter Verwendung eines der oben angeführten Formate zu modulieren. Die modulierte Wellenform wird weiter verarbeitet (z.B. gefiltert, verstärkt und aufwärtsgewandelt) und an die entfernte Station übertragen. An der entfernten Station wird das übertragene HF-Signal empfangen und von einem Empfänger demoduliert.

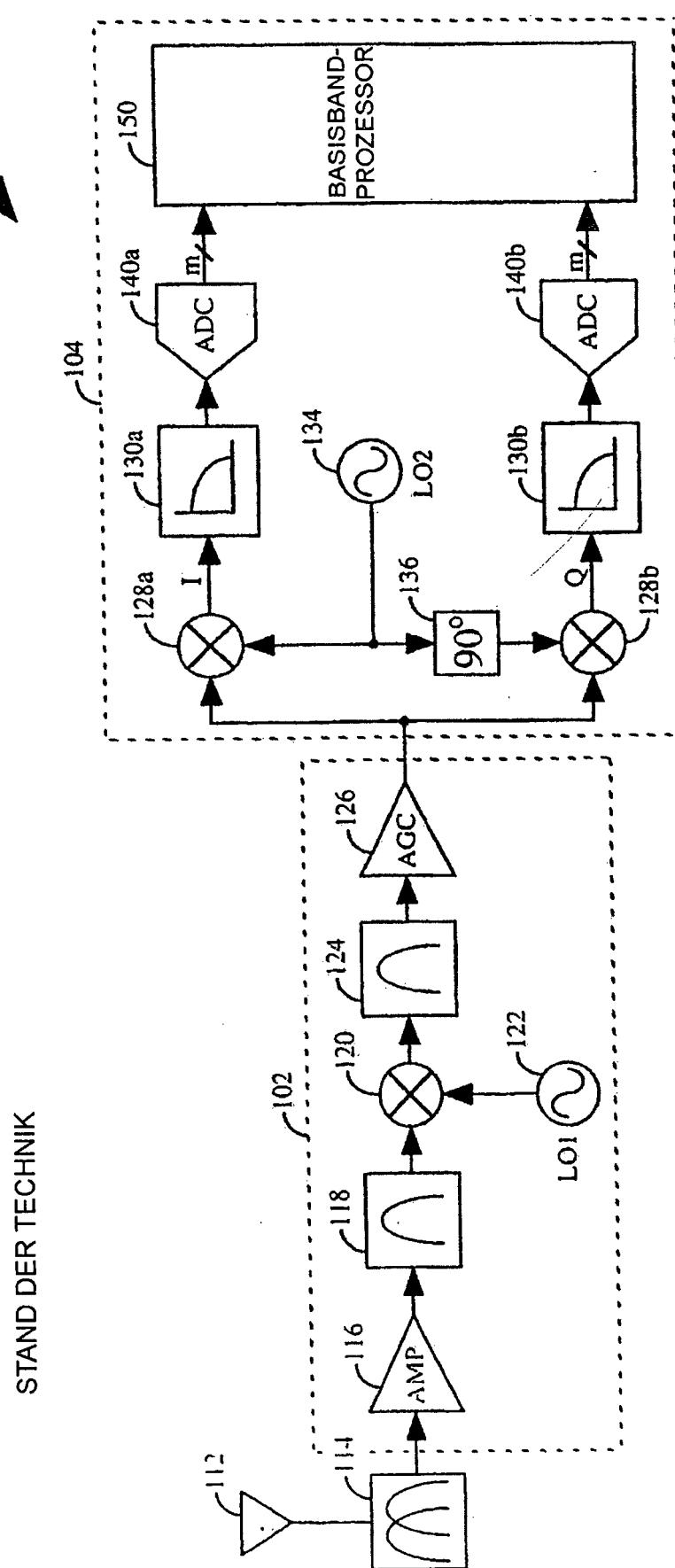

**[0005]** Ein Blockdiagramm eines beispielhaften Zwischenfrequenzempfängers (Superheterodynempfänger) gemäß dem Stand der Technik, der für eine Quadraturdemodulation von QSPK-, OQPSK- und QAM-Signalen verwendet wird, wird in [Fig. 1](#) dargestellt. Ein Empfänger **100** kann an der Basisstation oder an der entfernten Station verwendet werden. In dem Empfänger **100** wird das übertragene HF-Signal von einer Antenne **112** empfangen, durch einen Duplexer **114** geleitet und an ein Eingangsteil bzw. Frontend **102** geliefert. In dem Eingangsteil **102** verstärkt ein Verstärker (AMP) **116** das Signal und liefert das Signal an einen Bandpassfilter **118**, der das Signal filtert, um unerwünschte Spiegelsignale und Störsignale zu entfernen. Das gefilterte HF-Signal wird an einen Mischer **120** geliefert, der das Signal mit der Sinuskurve von einem Empfängeroszillator (LO1) **122** auf eine Zwischenfrequenz (ZF) abwärtswandelt. Das ZF-Signal von dem Mischer **120** wird von einem Bandpassfilter **124** gefiltert und von einem Verstärker mit automatischer Verstärkungsregelung (AGC – automatic gain control) **126** verstärkt, um die erforderliche Signalamplitude an dem Eingang von Analog-Digital-Wandlern (ADCs – analog to digital converter) **140** zu erzeugen. Das verstärkungsgeregelte Signal wird an einen Demodulator **104** geliefert. In dem Demodulator **104** wandeln zwei Mischer **128a** und **128b** das Signal in die Basisband-I- und -Q-Signale mit der Sinuskurve abwärts, die jeweils von einem Empfänger- bzw. Lokaloszillator (LO2) **134** und einem Phasenschieber **136** geliefert wird. Die Basisband-I- und -Q-Signale werden jeweils an die Tiefpassfilter **130a** und **130b** geliefert, die ein signalangepasstes (match) Filtern und/oder ein Anti-Alias-Filtern der Basisbandsignale vorsehen. Die gefilterten Signale werden an ADCs **140a** und **140b** geliefert, welche die Signale abtasten, um die digitalisierten Basisband-Abtastwerte zu erzeugen. Die Abtastwerte werden an einen Basisband-Prozessor **150** für eine weitere Ver-

arbeitung (z.B. Fehlererkennung, Fehlerkorrektur und Dekomprimierung) geliefert, um rekonstruierte Schätzungen der übertragenen Daten zu erzeugen.

**[0006]** Die erste Frequenz-Abwärtswandlung mit dem Mischer **120** ermöglicht dem Empfänger **100**, Signale mit verschiedenen HF-Frequenzen auf eine feste ZF-Frequenz abwärtszuwandeln, wo mehr Signalverarbeitung durchgeführt werden kann. Die feste ZF-Frequenz ermöglicht, dass der Bandpassfilter **124** als ein fester Bandpassfilter, wie ein Oberflächenwellenfilter (SAW – surface acoustic wave), implementiert wird, um unerwünschte Spiegelsignale und Störsignale aus dem ZF-Signal zu entfernen. Ein Entfernen von Spiegelsignalen und Störsignalen ist wichtig, da diese Signale bei der zweiten Frequenz-Abwärtswandlungsstufe in das Signalband (z.B. das Band, in dem das Eingangssignal vorhanden ist) gefaltet werden können. Ferner können die Spiegelsignale und Störsignale die Amplitude des Signals in verschiedene aktive Komponenten signifikant erhöhen, wie die Verstärker und Mischer, was einen höheren Grad an Intermodulationsprodukten als Ergebnis einer Nicht-Linearität in den aktiven Komponenten verursachen kann. Störsignale und Intermodulationsprodukte können eine Verschlechterung der Leistung des Kommunikationssystems verursachen.

**[0007]** Der Quadratur-Demodulator gemäß dem Stand der Technik hat mehrere größere Nachteile. Erstens kann das erforderliche Filtern durch den Bandpassfilter **124** und/oder die Tiefpassfilter **130** komplex sein. Diese Filter können einen flachen Durchlassbereich bzw. Passband, eine hohe Dämpfung in dem Sperrbereich und einen scharfen Übergang (roll-off) in dem Übergangsbereich erfordern. Diese Filter werden oft mit analogen Schaltungen implementiert. Eine Komponententoleranz von analogen Schaltungen ist schwierig beizubehalten und kann in dem Frequenzverhalten dieser Filter eine Verzerrung verursachen. Die Leistung des Empfängers **100** kann als Ergebnis der Verzerrung vermindert sein. Zweitens ist es schwierig, eine Quadratur-Balance über viele Produktionseinheiten aufgrund von Komponententoleranz in Phasenteilern **136**, Mischern **128**, Tiefpassfiltern **130** und ADCs **140** beizubehalten. Jegliche Nichtübereinstimmung der beiden Signalpfade führt zu einem Quadratur-Ungleichgewicht und einer Verschlechterung der Leistung des Empfängers **100**. Eine Pfad-Nichtübereinstimmung führt zu einem Nebensprechen (Kreuzkopplung) des I-Signals auf das Q-Signal und umgekehrt. Das Nebensprechsignal wirkt als additives Rauschen in dem gewünschten Signal und führt zu schlechter Demodulation des gewünschten Signals. Und drittens können ADCs **140** eine Verschlechterung der Leistung des Empfängers **100** aufgrund verschiedener, im Folgenden beschriebener Gründe verursachen.

**[0008]** In den meisten Demodulatoren sind ein oder mehrere ADC(s) erforderlich, um eine analoge Wellenform in kontinuierlicher Zeit in diskrete Abtastwerte zu gleichmäßig verteilten Zeitintervallen umzuwandeln. Einige wichtige Leistungsparameter eines ADCs umfassen Dynamikbereich, Linearität und DC-Offset. Jeder dieser Parameter kann die Leistung des Kommunikationssystems beeinflussen. Der Dynamikbereich kann die Bitfehlerrate (BER – bit error rate)-Leistung des Empfängers beeinflussen, da das Rauschen von dem ADC die Fähigkeit des ADCs herabsetzt, das Eingangssignal richtig zu erfassen. Die Linearität betrifft den Unterschied zwischen einer tatsächlichen Übertragungskurve (z.B. digitale Ausgabe gegenüber analoger Eingabe) und der idealen Übertragungskurve. Eine gute Linearität ist schwieriger zu erhalten, wenn die Anzahl von Bit in dem ADC zunimmt. Eine schlechte Linearität kann den Vorgang der Fehlererkennung/korrektur verschlechtern. Schließlich kann ein DC-Offset die Leistung des Phasenregelkreises (phase locked loop) in dem Empfänger und dem Fehlerkorrektur-Decodierer, wie dem Viterbi-Decodierer, herabsetzen.

**[0009]** In dem Stand der Technik werden Flash-ADCs oder ADCs mit sukzessiver Approximation verwendet, um die Basisbandsignale abzutasten. In dem Flash-ADC wird das Eingangssignal an L-1-Vergleicher geliefert, wobei  $L = 2^m$  und m die Anzahl der Bits in dem ADC ist. Jedem Vergleicher wird auch eine Vergleichsspannung geliefert. Die L-1-Vergleichsspannungen werden von einer Widerstands-Reihen- oder Serien-Schaltung von Zweitoren mit L-Widerständen erzeugt. Flash-ADCs sind sperrig und verbrauchen viel Energie, da L-1-Vergleicher und L-Widerstände erforderlich sind. Flash-ADCs können eine schlechte Linearität und schlechte DC-Offset-Charakteristiken aufweisen, wenn die Widerstände in der Widerstands-Reihen- oder Serien-Schaltung nicht angepasst sind. Flash-ADCs sind jedoch aufgrund ihrer hohen Betriebsgeschwindigkeit weit verbreitet.

**[0010]** ADCs mit sukzessiver Approximation sind für Kommunikationssysteme ebenfalls weit verbreitet. Diese ADCs minimieren die Komplexität, indem sie Approximationen des Eingangssignals über zwei oder mehrere Stufen durchführen. Jedoch können diese ADCs ebenso eine schlechte Linearität und schlechte DC-Offset-Charakteristiken aufweisen, ähnlich zu denen der Flash-ADCs. Somit sind Flash-ADCs und ADCs mit sukzessiver Approximation keine idealen Kandidaten zur Verwendung in vielen Kommunikationsanwendungen.

**[0011]** Sigma-Delta-Analog-zu-Digital-Wandler ( $\Sigma\Delta$ -ADCs) weisen aufgrund der inhärenten Architektur des  $\Sigma\Delta$ -ADCs eine bessere Leistung als Flash-ADCs und ADCs mit sukzessiver Approximation auf. Ein  $\Sigma\Delta$ -ADC führt eine Analog-Digital-Wand-

lung des Eingangssignals durch, indem er sukzessive ein-Bit-Approximationen der Veränderung in dem Eingangssignal durchführt, da der vorherige Abtastwert geschätzt wurde, mit einer Abtastfrequenz, die viele mal höher ist als die Bandbreite des Eingangssignals. Die ausgegebenen Abtastwerte weisen das Eingangssignal und das Quantisierungsrauschen auf. Jedoch kann der  $\Sigma\Delta$ -ADC derart gestaltet werden, dass das Quantisierungsrauschen in dem Signalband auf eine Außerband-Frequenz geschoben wird (oder das Rauschen geformt (shaped) wird), wo ein Filtern durchgeführt werden kann. US-A-5283578 offenbart eine Architektur für eine Oversampling- $\Sigma\Delta$ -A/D-Wandlung von Hochfrequenz-Schmalbandsignalen, einschließlich Mehrstufen- $\Sigma\Delta$ -Modulatoren, die eine Bandsperre-Rauschformung aufweisen.

**[0012]** Ein  $\Sigma\Delta$ -ADC kann einen hohen Dynamikbereich, eine gute Linearität und einen niedrigen DC-Offset aufgrund der inhärenten Struktur des  $\Sigma\Delta$ -ADCs liefern. Zum Beispiel kann ein hoher Dynamikbereich durch Auswahl eines ausreichenden Oversampling-Verhältnisses (OSR – oversampling ratio) und der geeigneten Rauschformungsfilter-Charakteristik erreicht werden. Das Oversampling-Verhältnis ist definiert als die Abtastfrequenz dividiert durch die zweiseitige Bandbreite des Eingangs. Zusätzlich können eine gute Linearität und ein geringer DC-Offset aufgrund des einfachen ein-Bit-Quantisierers in dem  $\Sigma\Delta$ -ADC erreicht werden.

**[0013]** Da für eine hohe Leistung ein hohes Oversampling-Verhältnis erforderlich ist, waren  $\Sigma\Delta$ -ADC herkömmlicherweise begrenzt auf Anwendungen, in denen das Eingangssignal ein Signal mit niedriger Bandbreite ist, wie in einer Audio-Anwendung. Mit dem Erscheinen von analogen Hochgeschwindigkeitsschaltungen können jedoch ADCs implementiert werden, um bei hoher Geschwindigkeit zu arbeiten. Entwicklungen und Implementierungen mit Hochgeschwindigkeits-Bandpass- und Basisband- $\Sigma\Delta$ -ADCs werden detailliert offenbart in der ebenfalls anhängigen U.S.-Patentanmeldung, Seriennummer 08/928,847 mit dem Titel „Sigma-Delta Analog-to-Digital Converter“, angemeldet am 12. September 1997, von dem Anmelder der vorliegenden Erfindung, die durch Bezugnahme hier enthalten ist.

**[0014]** Der Bandpass- $\Sigma\Delta$ -ADC liefert ZF-Abtastwerte, deren Rauschen geformt wird. Für einen Bandpass-Abtast- $\Sigma\Delta$ -ADC werden die ZF-Abtastwerte dann gefiltert und quadraturabwärtsumgewandelt, um I- und Q-Basisband-Ausgaben zu liefern.

#### Zusammenfassung der Erfindung

**[0015]** Die vorliegende Erfindung ist eine neue und verbesserte Rauschunterdrückungsschaltung und

ein Quadraturabwärtsumsetzer. Die Rauschunterdrückung weist zumindest einen Bandpassdezimator und einen Summierer auf. In dem beispielhaften Ausführungsbeispiel wird ein Bandpass-Mehrstufen-Rauschform-Sigma-Delta-Analog-zu-Digital-Wandler (MASH- $\Sigma\Delta$ -ADC – MultistAge noise Shaping sigma delta analog-to-digital converter) verwendet, um das analoge Eingangssignal abzutasten, und jede Schleife in dem MASH- $\Sigma\Delta$ -ADC liefert ein Ausgabesignal Y. Die Ausgabe jeder Schleife wird an einen entsprechenden Bandpassdezimator geliefert. In dem beispielhaften Ausführungsbeispiel weist jeder Bandpassdezimator einen FehlerunterdrückungsfILTER, einen Bandpassfilter und einen Dezimator auf. Der Bandpassfilter wird verwendet, um das Signal von dem FehlerunterdrückungsfILTER zu filtern. In dem beispielhaften Ausführungsbeispiel wird das gefilterte Signal dann von dem Dezimator um N dezimiert. Die Signale von allen Bandpassdezimatoren werden zusammen summiert und die resultierende Ausgabe weist die ZF-Abtastwerte auf.

**[0016]** Für eine Quadraturabwärtsumwandlung werden die ZF-Abtastwerte an zwei Multiplizierer geliefert, welche die ZF-Abtastwerte jeweils in I- und Q-Basisband-Abtastwerte mit einer phasengleichen und einer um  $90^\circ$  phasenverschobenen Sinuskurve abwärtswandeln. Die Basisband-Abtastwerte werden tiefpassgefiltert, um ein Quantisierungsrauschen und unerwünschte Signale weiter zu entfernen.

**[0017]** Es ist eine Aufgabe der vorliegenden Erfindung, eine Rauschunterdrückungsschaltung und einen Bandpassfilter vorzusehen, der eine Schaltungskomplexität minimiert und einen Energieverbrauch reduziert. In dem beispielhaften Ausführungsbeispiel ist die Übertragungsfunktion der Fehlerunterdrückungsschaltung in einen Satz von Übertragungsfunktionen zerlegt, eine Funktion für jedes Ausgabesignal Y von dem  $\Sigma\Delta$ -ADC. Jede Übertragungsfunktion entspricht einem FehlerunterdrückungsfILTER. Die Übertragungsfunktionen für jeden der FehlerunterdrückungsfILTER und den Bandpassfilter sind gefaltet (convolved), um die Übertragungsfunktion eines Bandpassdezimators vorzusehen. Die gefaltete Übertragungsfunktion für jeden Bandpassdezimator kann mit weniger Hardware implementiert werden als die direkte Implementierung des entsprechenden Fehlerunterdrückungsfilters und Bandpassfilters. Ferner arbeitet jeder Bandpassdezimator auf einem Ein-Bit-Signal Y von einer entsprechenden Schleife des MASH-ADCs. Eine direkte Implementierung der Fehlerunterdrückungsschaltung und des Bandpassfilters würde erfordern, dass der Bandpassfilter auf einer Mehr-Bit-Ausgabe von der Fehlerunterdrückungsschaltung arbeitet. Zusätzlich kann die Dezimierung um N in den Bandpassdezimator derart aufgenommen werden, dass die Bandpassdezimatoren nur bei  $1/N$  der Frequenz des ADC-Abtast-Takts arbeiten, wodurch der Energieverbrauch reduziert wird.

**[0018]** Es ist eine weitere Aufgabe der vorliegenden Erfindung, einen Quadraturabwärtsumsetzer mit reduzierter Schaltungskomplexität vorzusehen. In dem beispielhaften Ausführungsbeispiel wird die Mittelfrequenz des analogen Eingangssignals bei  $f_{IF} = 0.25 \cdot (2n + 1) \cdot f_{ADC}$  beibehalten, wobei  $n$  ein ganzzahliger Wert von Null oder größer ist und  $f_{ADC}$  die ADC-Abtastfrequenz ist. Diese Mittelfrequenz erzeugt nach der Analog-Digital-Wandlung ein Spiegelignal des Eingangssignals bei  $f_c = 0.25f_{ADC}$ . Ein Beibehalten der Mittelfrequenz des Spiegelsignals auf  $0.25f_{ADC}$  vereinfacht die Frequenz-Abwärtswandlung, da die Abwärtswandlungs-Sinuskurven  $\cos(w_c t)$  und  $\sin(w_c t)$  einfache Werte von 1, 0 und -1 annehmen. In dem beispielhaften Ausführungsbeispiel wird die Dezimierung um  $N$  derart gewählt, dass die Frequenz des Spiegelsignals bei  $0.25f_s$  beibehalten wird, wobei  $f_s$  die Abtastrate der dezimierten Abtastwerte ist (oder  $f_s = f_{ADC}/N$ ). Dies kann durch Auswahl eines ungeraden Wertes für  $N$  (z.B. 3, 5, 7, 9, usw.) erreicht werden.

#### Kurze Beschreibung der Zeichnungen

**[0019]** Die Merkmale, Aufgaben und Vorteile der vorliegenden Erfindung werden offensichtlicher aus der folgenden detaillierten Beschreibung unter Bezugnahme auf die Zeichnungen, in denen gleiche Bezugszeichen entsprechendes identifizieren und in denen:

**[0020]** [Fig. 1](#) ein Blockdiagramm eines beispielhaften Zwischenfrequenz bzw. Super-Heterodyneempfängers gemäß dem Stand der Technik ist;

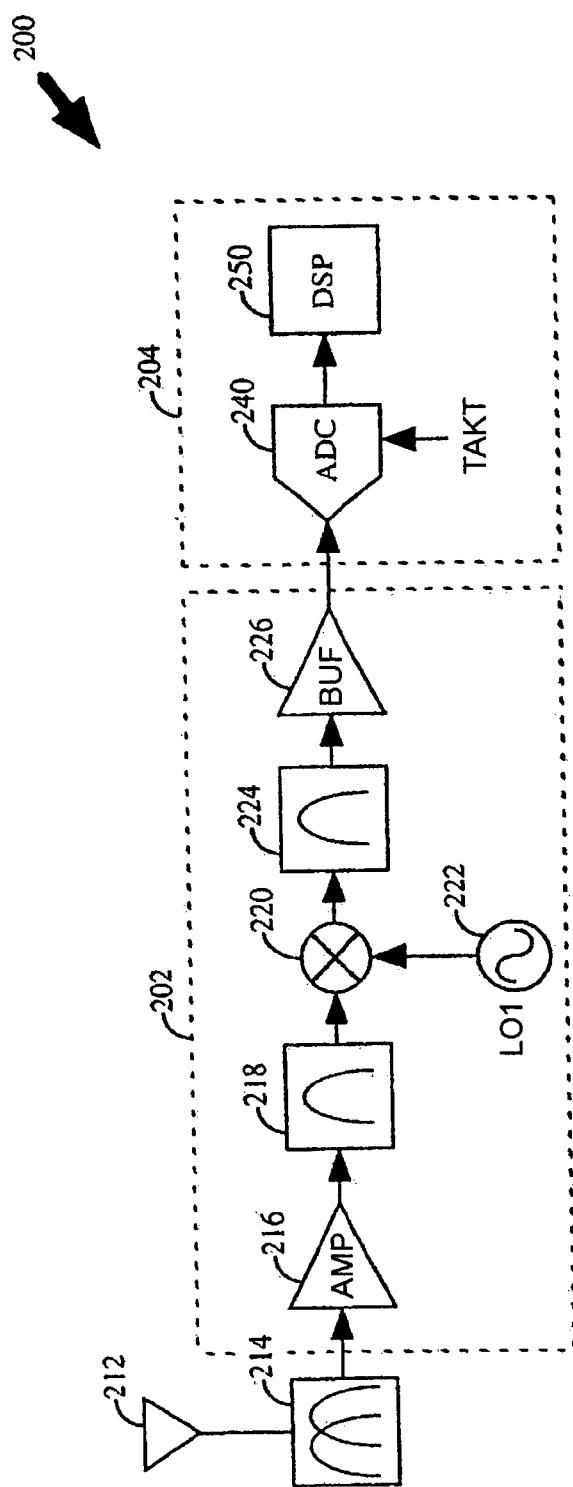

**[0021]** [Fig. 2](#) ein Blockdiagramm eines beispielhaften Bandpassabtastempfängers der vorliegenden Erfindung ist;

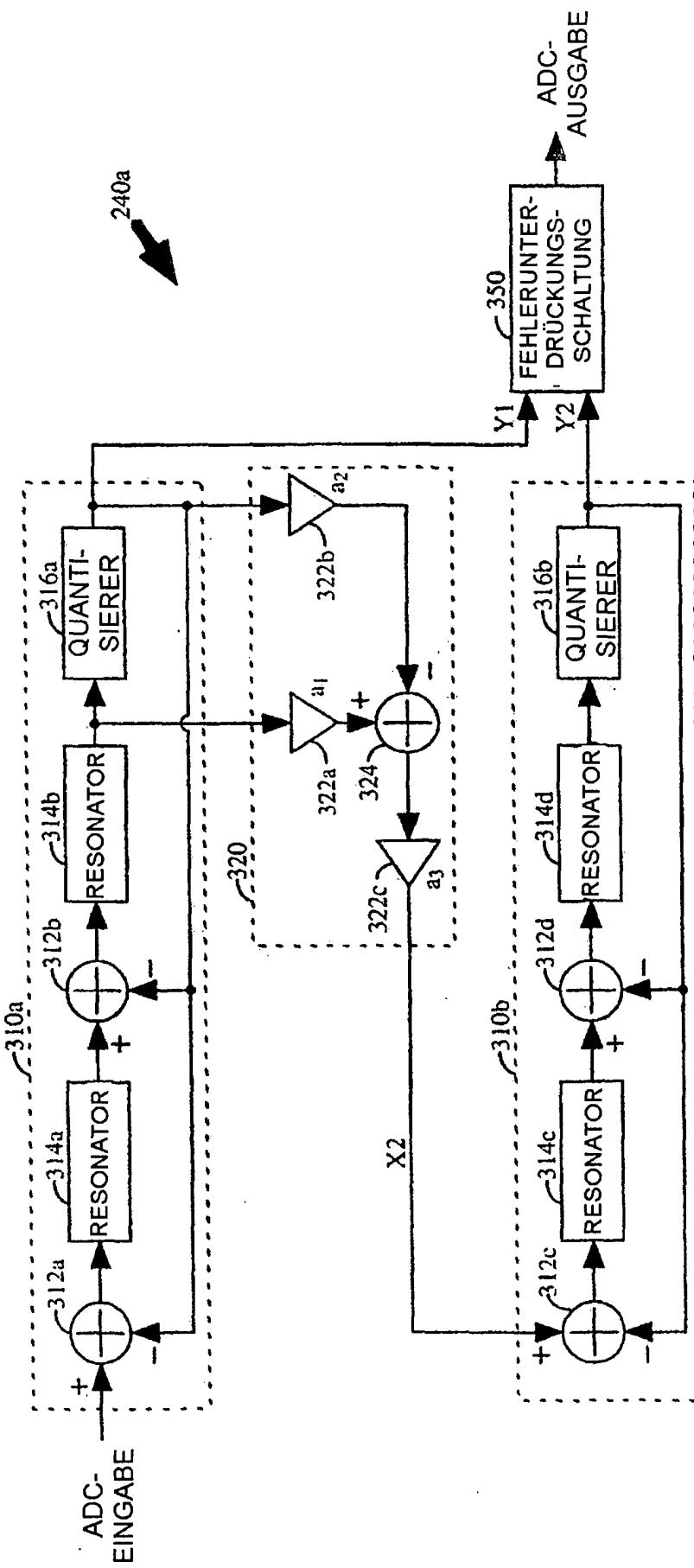

**[0022]** [Fig. 3](#) ein Blockdiagramm eines beispielhaften zwei-Schleifen-Bandpass-MASH- $\Sigma\Delta$ -ADCs ist;

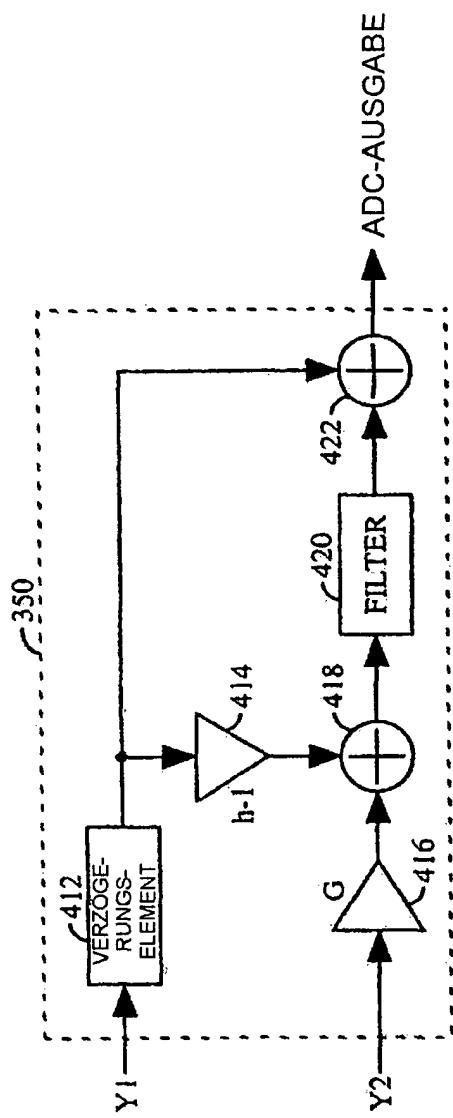

**[0023]** [Fig. 4](#) ein Blockdiagramm einer beispielhaften Fehlerunterdrückungsschaltung der vorliegenden Erfindung ist;

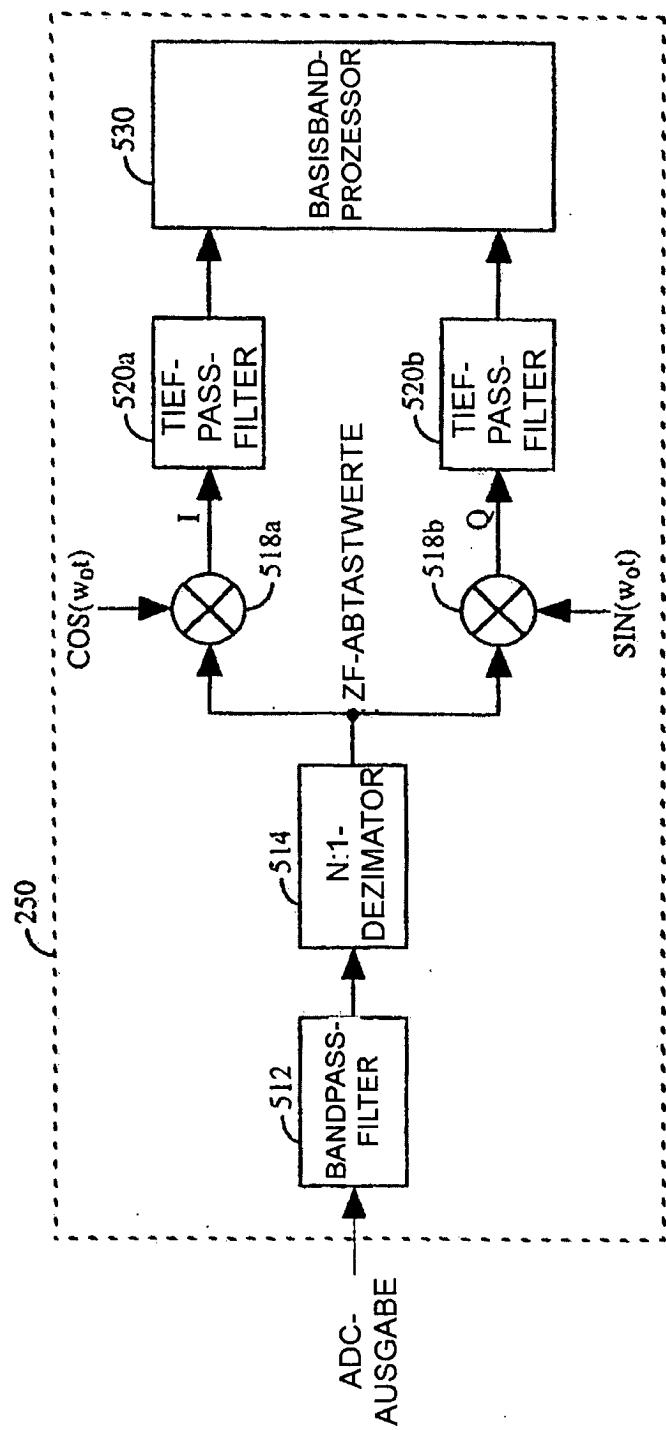

**[0024]** [Fig. 5](#) ein Blockdiagramm eines beispielhaften digitalen Signalprozessors ist, der für eine Quadraturdemodulation verwendet wird;

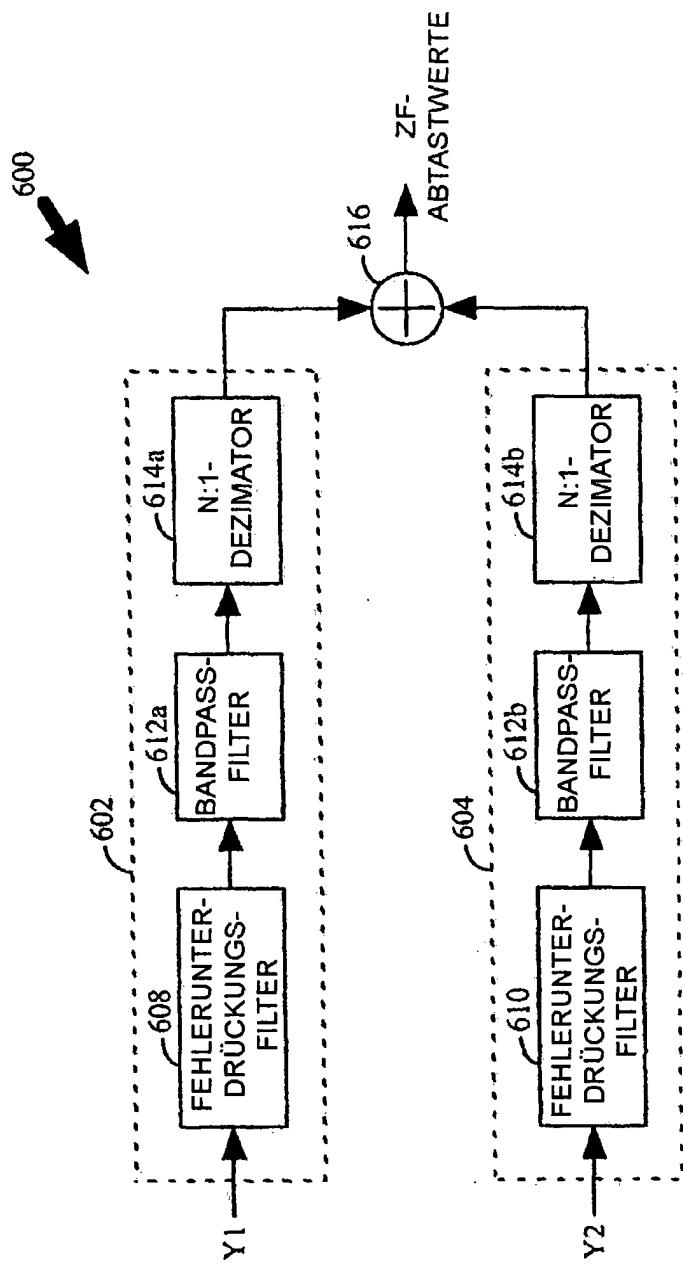

**[0025]** [Fig. 6](#) ein Blockdiagramm ist, das eine beispielhafte Rauschunterdrückungsschaltung zeigt;

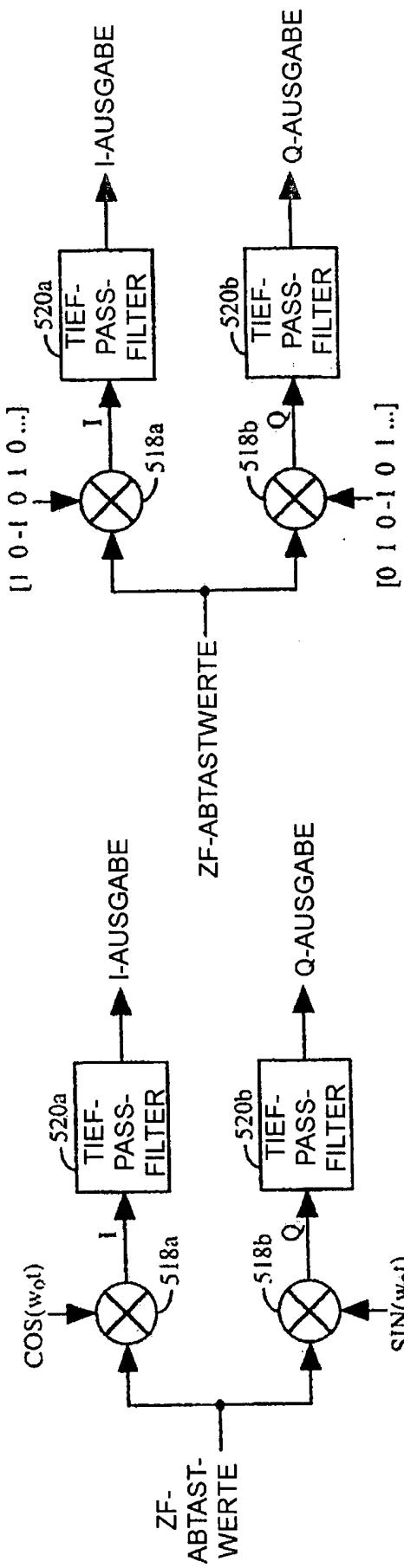

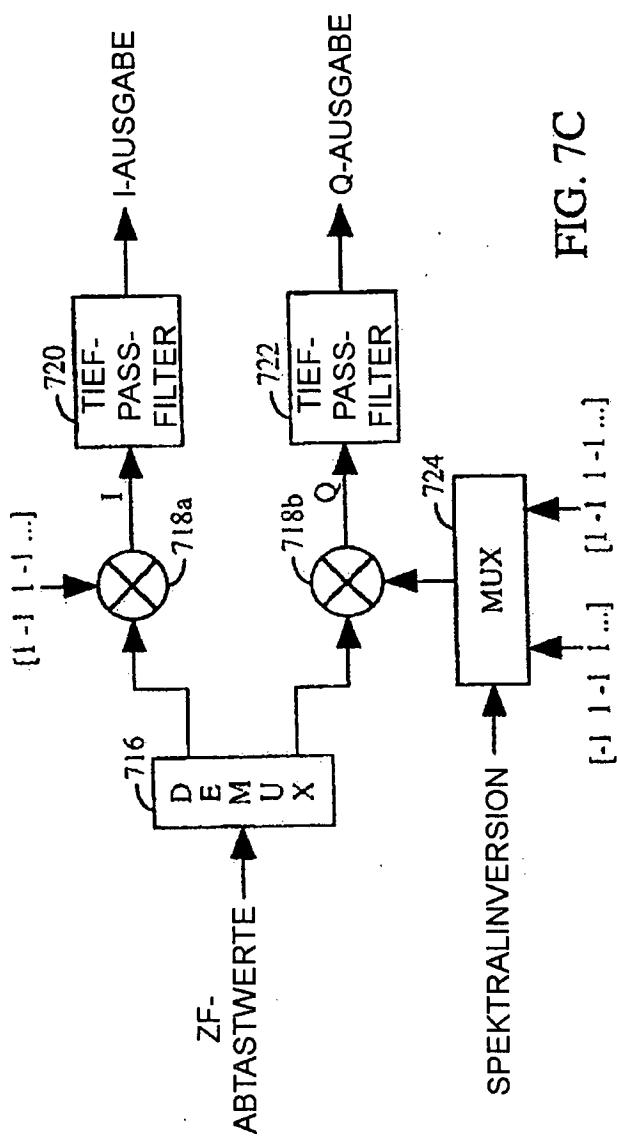

**[0026]** [Fig. 7A](#) und [Fig. 7B](#) Blockdiagramme eines beispielhaften Quadraturabwärtsumsetzers für ZF-Abtastwerte, die an einer Frequenz zentriert sind, und für ZF-Abtastwerte sind, die an  $0.25f_s$  zentriert sind;

**[0027]** [Fig. 7C](#) ein Blockdiagramm einer beispiel-

haften Implementierung eines Quadraturabwärtsumsetzers für ZF-Abtastwerte ist, die an  $0.25f_s$  zentriert sind;

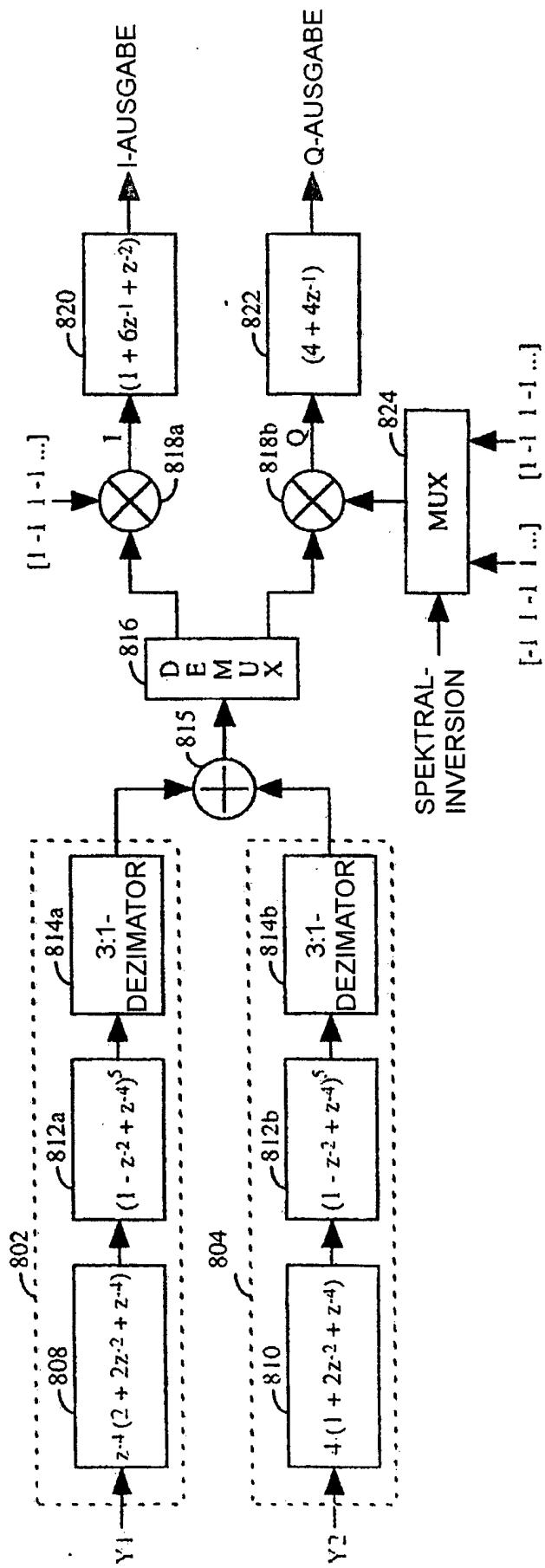

**[0028]** [Fig. 8](#) ein Blockdiagramm ist, das beispielhafte Rauschunterdrückungsschaltungen und Quadraturabwärtsumsetzer zeigt;

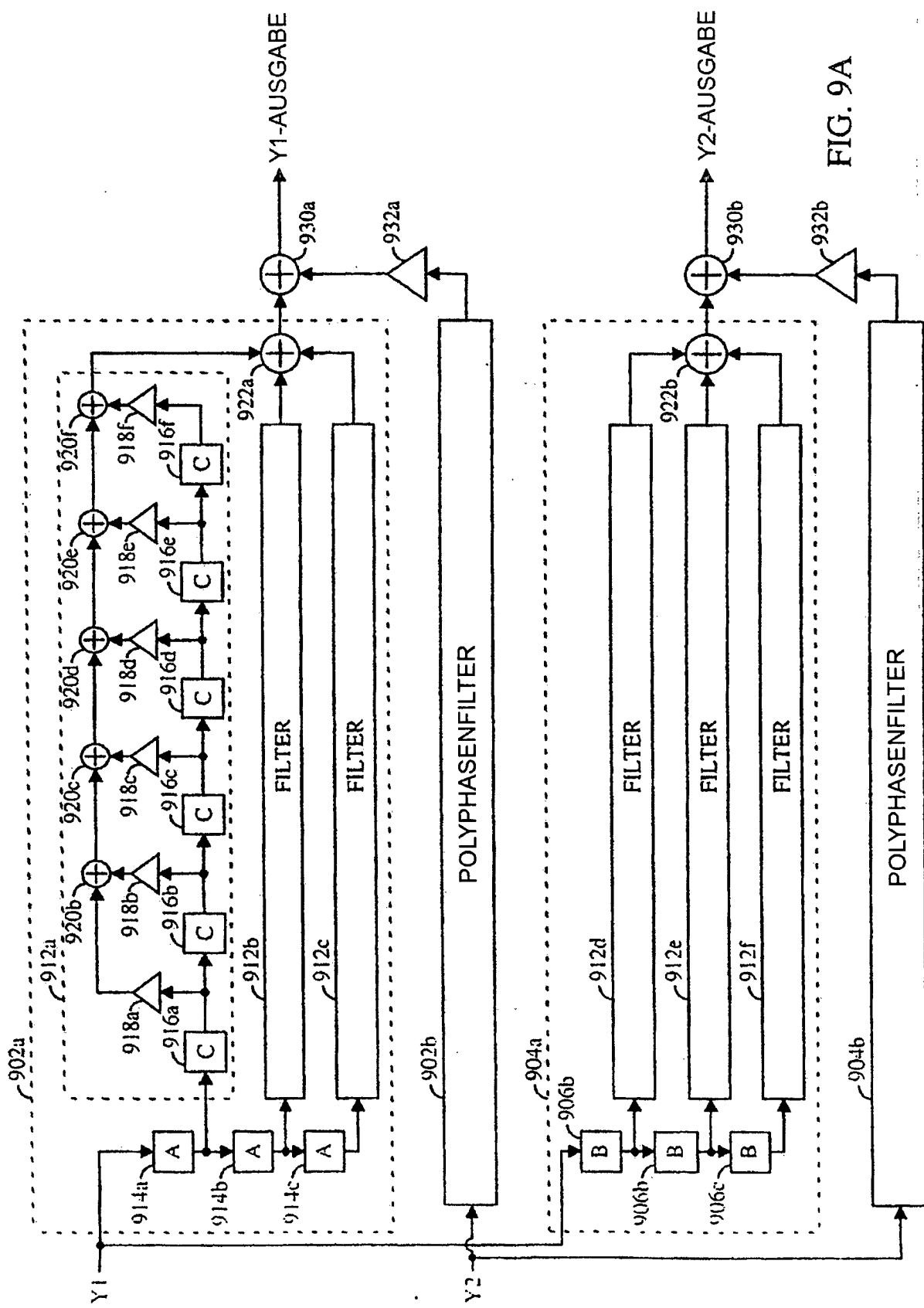

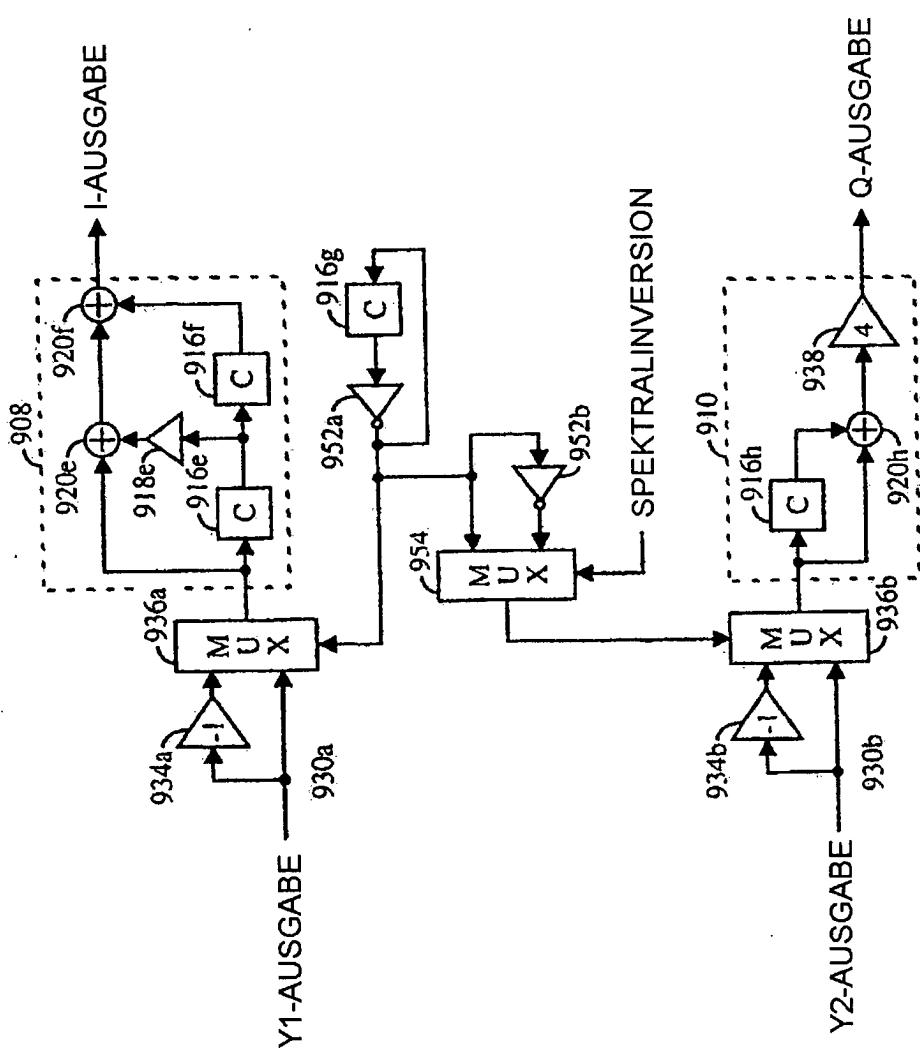

**[0029]** [Fig. 9A](#)–[Fig. 9B](#) jeweils Blockdiagramme einer beispielhaften Implementierung der Rauschunterdrückungsschaltungen und Quadraturabwärtsumsetzer von [Fig. 8](#) unter Verwendung einer polyphasigen Struktur sind; und

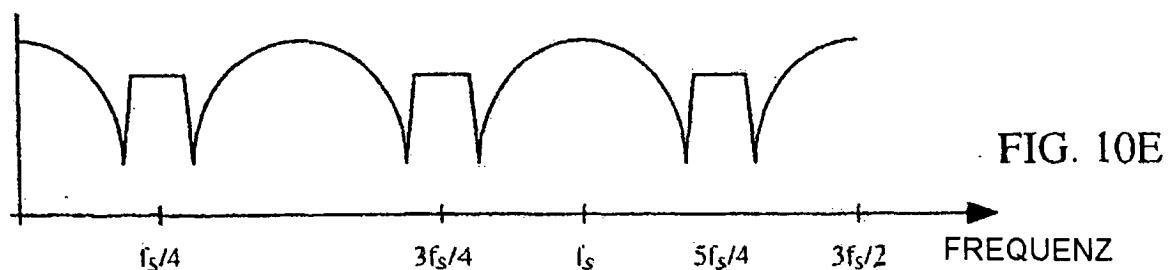

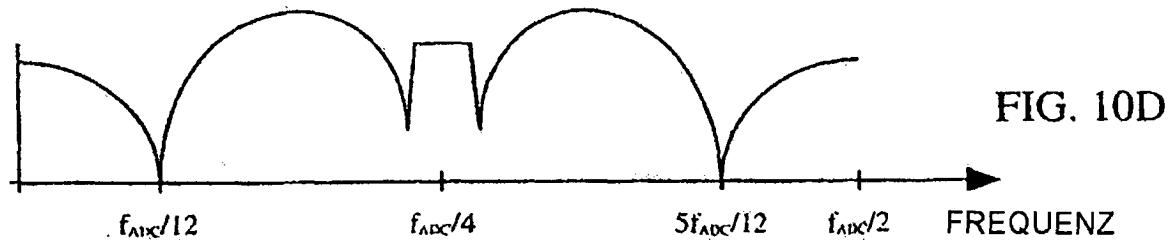

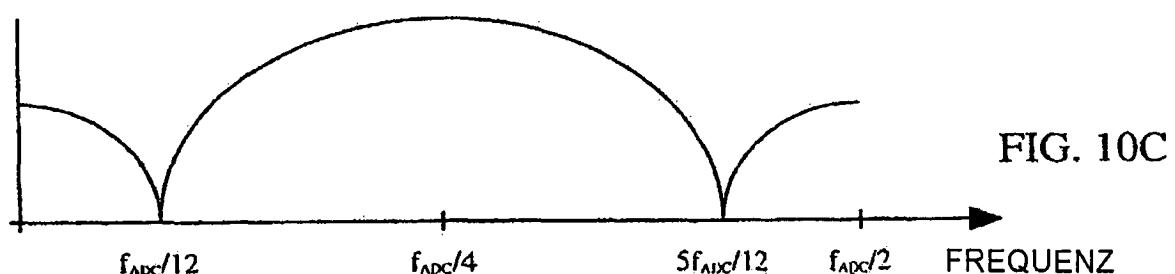

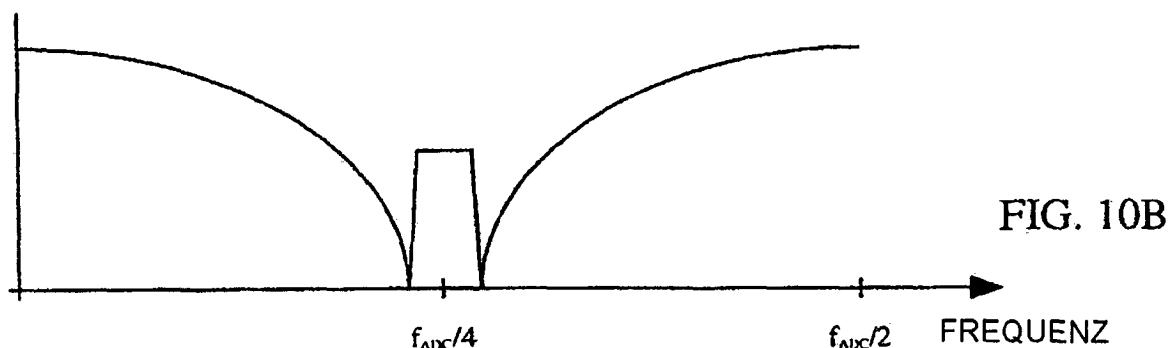

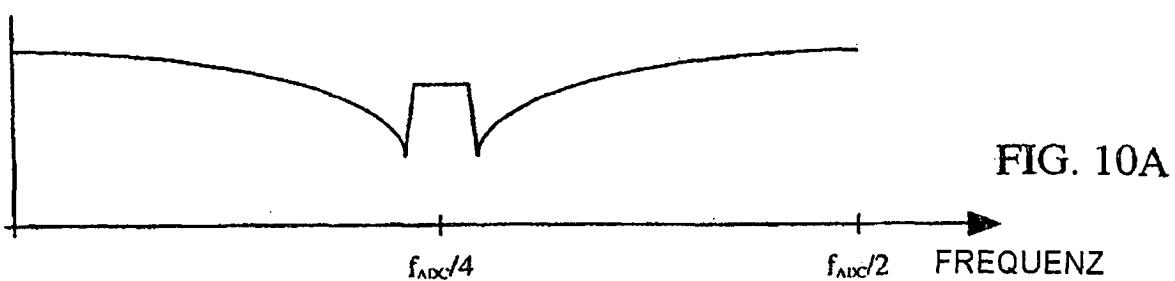

**[0030]** [Fig. 10A](#)–[Fig. 10E](#) jeweils ein beispielhaftes Spektrum des Y1-Signals von dem MASH- $\Sigma\Delta$ -ADC, das Spektrum des Y1-Signals nach dem Fehlerunterdrückungsfilter, das Frequenzverhalten des Bandpassfilters nach dem Fehlerunterdrückungsfilter, das Spektrum des Y1-Signals nach dem Bandpassfilter und das Spektrum des Y1-Signals nach der 3:1-Dezimierung sind.

#### Detaillierte Beschreibung der bevorzugten Ausführungsbeispiele

**[0031]** Die vorliegende Erfindung ist eine neue und verbesserte Rauschunterdrückungsschaltung und ein Quadraturabwärtsumsetzer, die in Zusammenhang mit einem Analog-Digital-Wandler (ADC) verwendet werden. Insbesondere ist die vorliegende Erfindung gut zur Verwendung in Kombination mit einem Sigma-Delta-Analog-Digital-Wandler ( $\Sigma\Delta$ -ADC) geeignet, der in der oben angeführten U.S. Patentanmeldung Nr. PA447 offenbart ist. Beispielhafte Anwendungen, welche die Rauschunterdrückungsschaltung und den Quadraturabwärtsumsetzer verwenden können, umfassen CDMA-Kommunikationssysteme und HDTV-Systeme.

**[0032]** In einem Bandpass-Abtast-ADC ist das Eingangssignal in den ADC an einer Zwischenfrequenz (ZF) zentriert anstatt einem Basisband. Ein Abtasten bei ZF ermöglicht ein Entfernen einer Frequenz-Abwärtswandlungsstufe in dem Empfänger, wodurch die Gestaltung der Hardware vereinfacht wird und eine Zuverlässigkeit erhöht wird. Die Verwendung von  $\Sigma\Delta$ -ADC liefert viele Vorteile gegenüber herkömmlichen ADCs (z.B. Flash-ADCs und ADCs mit sukzessiver Approximation), wie oben beschrieben. Der Rauschformer in dem  $\Sigma\Delta$ -ADC kann derart gestaltet werden, dass das Quantisierungsrauschen um das Signalband außerhalb geschoben wird (oder das Rauschen geformt wird), wo ein Filtern durchgeführt werden kann.

#### I. Bandpassabtastempfänger

**[0033]** Ein Blockdiagramm eines beispielhaften Bandpassabtastempfängers wird in [Fig. 2](#) gezeigt. Ein

Empfänger **200** kann verwendet werden, um BPSK, QPSK, OQPSK, QAM und andere digitale und analoge Modulationsformate zu demodulieren. In dem Empfänger **200** wird das übertragene HF-Signal von einer Antenne **212** empfangen, durch einen Duplexer **214** geleitet und an ein Eingangsteil **202** geliefert. In dem Eingangsteil **202** verstärkt ein Verstärker (AMP) **216** das Signal und liefert das verstärkte Signal an einen Bandpassfilter **218**, der das Signal filtert, um unerwünschte Spiegelsignale und Störsignale zu entfernen. Das gefilterte Signal wird an einen Mischer **220** geliefert, der das Signal mit der Sinuskurve von einem Empfängeroszillator (LO1) **222** auf eine Zwischenfrequenz abwärtswandelt. Das ZF-Signal von dem Mischer **220** wird an einen Bandpassfilter **224** geliefert, der das Signal weiter filtert. In dem beispielhaften Ausführungsbeispiel ist der Bandpassfilter **224** ein Oberflächenwellenfilter (SAW – surface acoustic wave), dessen Implementierung im Stand der Technik bekannt ist. Das gefilterte Signal wird an einen Puffer (BUF) **226** geliefert, der eine Verstärkung und/oder ein Puffern des Signals vorsieht. Das gepufferte Signal wird an einen Demodulator **204** geliefert. In dem Demodulator **204** tastet der ADC **240** das gepufferte Signal mit einer von dem CLK-Signal bestimmten hohen Abtastfrequenz ab und liefert die Abtastwerte bzw. Abtastungen an einen digitalen Signalprozessor (DSP) **250**. Der digitale Signalprozessor **250** wird im Folgenden detailliert beschrieben.

**[0034]** Für Applikationen, in denen eine Quadraturdemodulation erforderlich ist, wie QPSK, OQPSK und QAM, wird ein Bandpass-ADC verwendet. Der Bandpass-ADC kann als ein Bandpass- $\Sigma\Delta$ -ADC auf die in der ebenfalls anhängigen U.S. Patentanmeldung Nr. PA447 beschriebene Weise gestaltet und implementiert werden.

**[0035]** Ein Blockdiagramm eines beispielhaften zwei-Schleifen-Bandpass-MASH- $\Sigma\Delta$ -ADCs wird in [Fig. 3](#) dargestellt.  $\Sigma\Delta$ -ADCs mit einer Schleife oder mehr als zwei Schleifen können gestaltet und verwendet werden und befinden sich in dem Bereich der vorliegenden Erfindung. Der MASH-ADC **240a** weist zwei Schleifen **310a** und **310b**, ein Eingangs-Vorwärtselement **320** und eine Fehlerunterdrückungsschaltung **350** auf. In dem beispielhaften Ausführungsbeispiel empfängt der MASH-ADC **240a** eine analoge ADC-Eingabe und erzeugt eine digitale ADC-Ausgabe mit zumindest zwei Bit pro Abtastwert, zumindest einem Bit pro Abtastwert für jede Schleife **310**.

**[0036]** Die ADC-Eingabe wird an die Schleife **310a** geliefert, die als Antwort darauf ein 1-Bit-Y1-Signal erzeugt. Ein Anteil der ADC-Eingabe und des Quantisierungsrauschens ( $X_2$ ) von der Schleife **310a** wird an die Schleife **310b** geliefert, wo ein zusätzliches Rauschformen durchgeführt wird. Die Y1- und Y2-Signale von den Schleifen **310a** und **310b** werden je-

weils an die Fehlerunterdrückungsschaltung **350** geliefert. Die Fehlerunterdrückungsschaltung **350** verzögert, filtert und kombiniert die Y1- und Y2-Signale, um die ADC-Ausgabe zu erzeugen.

**[0037]** In der Schleife **310a** empfängt ein Summieren **312a** die ADC-Eingabe und das Y1-Signal von einem Quantisierer **316a**, subtrahiert Y1 von der ADC-Eingabe und liefert das Fehlersignal an einen Resonator **314a**. Der Resonator **314a** filtert das Fehlersignal und gibt das gefilterte Signal an einen Summierer **312b**. In dem beispielhaften Ausführungsbeispiel ist jeder Resonator **314** in dem MASH-ADC **240a** mit der Bandpassübertragungsfunktion

$$\frac{k_n * z^{-2}}{1 + z^{-2}}$$

implementiert, wobei  $k_n$  die Verstärkung des n-ten Resonators **314** in der Schleife **310** ist. Der Summierer **312b** empfängt ebenfalls Y1 von dem Quantisierer **316a**, subtrahiert Y1 von dem Fehlersignal von dem Resonator **314a** und liefert das Fehlersignal an den Resonator **314b**, der das Fehlersignal weiter filtert. Das gefilterte Signal von dem Resonator **314b** wird an den Quantisierer **316a** gegeben, der als Antwort darauf das 1-Bit-Y1-Signal erzeugt. Die Schleife **310b** ist auf ähnliche Weise wie die Schleife **310a** verbunden.

**[0038]** Die gefilterte Ausgabe von dem Resonator **314b** wird auch an ein Verstärkungselement **322a** geliefert, welches das Signal mit dem Skalierungsfaktor  $a_1$  skaliert. Das Y1-Signal von dem Quantisierer **316a** wird an ein Verstärkungselement **322b** geliefert, welches das Signal mit dem Skalierungsfaktor  $a_2$  skaliert. Die Ausgaben von den Verstärkungselementen **322a** und **322b** werden an einen Summierer **324** geliefert, der die Ausgabe von dem Verstärkungselement **322b** von der Ausgabe von dem Verstärkungselement **322a** subtrahiert. Das Fehlersignal von dem Summierer **324** wird an ein Verstärkungselement **322c** geliefert, welches das Fehlersignal mit dem Skalierungsfaktor  $a_3$  skaliert. Die Ausgabe von dem Verstärkungselement **322c** weist X2 auf, das an die Schleife **310b** geliefert wird.

**[0039]** Ein Blockdiagramm einer beispielhaften Fehlerunterdrückungsschaltung **350** wird in [Fig. 4](#) gezeigt. In der Fehlerunterdrückungsschaltung **350** wird das Y1-Signal von der Schleife **310a** an ein Verzögerungselement **412** geliefert, das Y1 um ein Zeitintervall verzögert, das gleich der Verarbeitungsverzögerung von Schleife **310b** ist. Das verzögerte Y1 von dem Verzögerungselement **412** wird Y2 zeitlich zugeordnet. Das Y2-Signal von der Schleife **310b** wird an ein Verstärkungselement **416** geliefert, das Y2 mit dem Skalierungsfaktor G skaliert. Das verzögerte Y1 wird an ein Verstärkungselement **414** geliefert, welches das verzögerte Y1 mit dem Skalierungsfaktor (h

– 1) skaliert. Die Skalierungsfaktoren G und ( $h - 1$ ) bestimmen teilweise die Rauschform-Charakteristiken von  $\Sigma\Delta$ -ADC **240a**. In dem beispielhaften Ausführungsbeispiel werden die Skalierungsfaktoren als  $G = 4$  und  $(h - 1) = 1$  gewählt. Die Ausgaben von den Verstärkungsselementen **414** und **416** werden an einen Summierer **418** geliefert, der die beiden skalierten Ausgaben summiert. Das kombinierte Signal von dem Summierer **418** wird an einen Filter **420** gegeben, der das kombinierte Signal mit der Übertragungsfunktion  $N(z)$  filtert. Die Übertragungsfunktion  $N(z)$  des Filters **420** und die Verzögerung des Verzögerungselements **412** werden basierend auf den Charakteristiken des  $\Sigma\Delta$ -ADCs gewählt. In dem beispielhaften Ausführungsbeispiel hat für einen MASH-4-4-Bandpass- $\Sigma\Delta$ -ADC **240a**, wie in [Fig. 3](#) gezeigt, der Filter **420** die Übertragungsfunktion  $N(z) = (1 + z^{-2})^2$  und das Verzögerungselement **412** die Übertragungsfunktion  $D(z) = z^{-4}$ . Andere Übertragungsfunktionen für den Filter **420** und das Verzögerungselement **412** können ebenfalls verwendet werden und befinden sich im Bereich der vorliegenden Erfindung. Für einen um  $f_{ADC}/4$  zentrierten Bandpass- $\Sigma\Delta$ -ADC ist jeder zweite Koeffizient von  $N(z)$  Null und diese Charakteristik wird verwendet, um die Gestaltung der Fehlerunterdrückungsschaltung und des Bandpassfilters der vorliegenden Erfindung zu vereinfachen. Die Ausgabe von dem Filter **420** und das verzögerte  $Y_1$  werden an den Summierer **422** geliefert, der die beiden Signale summiert, um die ADC-Ausgabe zu erzeugen.

**[0040]** Aus den obigen beispielhaften Übertragungsfunktionen für das Verzögerungselement **412**,  $D(z)$ , und den Filter **420**,  $N(z)$ , und den beispielhaften Skalierungsfaktoren  $G = 4$  und  $(h - 1) = 1$  kann die beispielhafte Übertragungsfunktion  $Y_{(z)}$  für die Fehlerunterdrückungsschaltung **350** ausgedrückt werden als:

$$\begin{aligned} Y(z) &= EC_{Y_1}(z) \cdot Y_1(z) + EC_{Y_2}(z) \cdot Y_2(z) \\ &= z^{-4}(2 + 2z^{-2} + z^{-4}) \cdot Y_1(z) + 4(1 + 2z^{-2} + z^{-4}) \cdot Y_2(z) \\ &= [z^{-4}Y_1(z)] + [(1 + 2z^{-2} + z^{-4})(z^{-4}Y_1(z) + 4Y_2(z))] \quad (1) \end{aligned}$$

**[0041]** In der Gleichung (1) weist der Ausdruck in der ersten Klammer die Signalkomponente auf und der Ausdruck in der zweiten Klammer weist das gesamte Quantisierungsrauschen nach der Fehlerunterdrückung auf. Es ist zu beachten, dass die Übertragungsfunktion  $Y(z)$  der Fehlerunterdrückungsschaltung **350** betrachtet werden kann als Durchlaufen lassen des  $Y_1$ -Signals durch einen ersten „endliche Impulsantwort“ (FIR – finite impulse response)-Filter mit den Koeffizienten  $EC_{Y_1}(z)$ , Durchlaufen lassen des  $Y_2$ -Signals durch einen zweiten FIR-Filter mit den Koeffizienten  $EC_{Y_2}(z)$  und Summieren der beiden Ausgaben der FIR-Filter. Die Koeffizienten für die FIR-Filter können ausgedrückt werden als:

$$\begin{aligned} EC_{Y_1}(z) &= [0 \ 0 \ 0 \ 0 \ 2 \ 0 \ 2 \ 0 \ 1] \\ EC_{Y_2}(z) &= [1 \ 0 \ 2 \ 0 \ 1] \cdot 4 \quad (2) \end{aligned}$$

**[0042]** Aus der Gleichung (2) ist zu sehen, dass, obwohl die Eingaben in die Fehlerunterdrückungsschaltung **350** zwei Signale,  $Y_1$  und  $Y_2$ , aufweisen, wobei jedes ein Bit an Auflösung aufweist, die Ausgabe von der Fehlerunterdrückungsschaltung **350** fünf Bit Auflösung aufweist und einen Bereich von 0 bis 21 umfasst. Aus der Gleichung (1) ist zu sehen, dass die Amplitude des Signals nicht verstärkt ist. Jedoch ist das Quantisierungsrauschen verarbeitet und geformt und ein zusätzlicher Bereich ist für das geformte Ausserband-Quantisierungsrauschen erforderlich.

**[0043]** Ein beispielhaftes Blockdiagramm eines digitalen Signalprozessors **250**, der für eine Quadraturdemodulation verwendet wird, wird in [Fig. 5](#) dargestellt. Die ADC-Ausgabe von dem ADC **240** wird an einen Bandpassfilter **512** geliefert, der das Signal filtert, um ein Quantisierungsrauschen und andere Störsignale zu entfernen. In dem beispielhaften Ausführungsbeispiel weist der Bandpassfilter **512** die folgende Übertragungsfunktion auf:

$$H_{BPF}(z) = (1 - z^{-2} + z^{-4})^p, \quad (3)$$

wobei  $p$  die Ordnung der Ordnung des Bandpassfilters **512** ist. Die Übertragungsfunktion in der Gleichung (3) liefert Nullstellen bei  $f_{ADC}/12$  und  $5f_{ADC}/12$  und hat eine maximale Verstärkung bei  $f_{ADC}/4$ . In dem beispielhaften Ausführungsbeispiel wird die Charakteristik des Bandpassfilters **512** in Verbindung mit einem Dezimator **514** gewählt, wie im Folgenden beschrieben wird. Andere Bandpassfilter-Übertragungsfunktionen können ebenfalls verwendet werden und befinden sich in dem Bereich der vorliegenden Erfindung.

**[0044]** Die Verwendung des Bandpassfilters **512** nach der Fehlerunterdrückungsschaltung **350** liefert viele Vorteile. In dem beispielhaften Ausführungsbeispiel wird das empfangene Signal nach einer Umwandlung durch den ADC **240a** bei  $f_{ADC}/4$  zentriert. Somit ist der Amplitudengang des Bandpassfilters **512** derart gestaltet, dass er einen Durchlassbereich um  $f_{ADC}/4$  herum bereitstellt, und die Übertragungsfunktion des Bandpassfilters **512** weist Null für jeden anderen Koeffizient auf. Diese Filter-Koeffizienten-Charakteristiken können mit einer ähnlichen Charakteristik der Fehlerunterdrückungsschaltung **350** kombiniert werden, wie in der Gleichung (2) gezeigt, um die gesamte Gestaltung der Fehlerunterdrückungsschaltung **350** und des Bandpassfilters **512** zu vereinfachen. Ferner kann, wie oben angeführt, die Ausgabe von der Fehlerunterdrückungsschaltung **350** fünf Bit Auflösung aufweisen. Eine Gestaltung des Bandpassfilters **512**, um die erforderliche 5-Bit-Präzisionsarithmetik zu berechnen, kann die Komplexität des Bandpassfilters **512** beträchtlich

erhöhen. In dem beispielhaften Ausführungsbeispiel sind die Fehlerunterdrückungsschaltung **350** und der Bandpassfilter **512** derart kombiniert, dass die entstehende Schaltung direkt auf den 1-Bit-Y1- und Y2-Signalen arbeitet. Schließlich entfernt der Bandpassfilter **512** einen großen Teil des Quantisierungsrauschens derart aus dem ADC **240a**, dass der erforderliche Dynamikbereich nach dem Bandpassfilter **512** demgemäß reduziert wird.

**[0045]** Das gefilterte Signal von dem Bandpassfilter **512** wird an den Dezimator **514** geliefert, der das Signal um einen Faktor von N bis 1 dezimiert, wobei N in dem beispielhaften Ausführungsbeispiel eine ungerade Zahl ist. Für alle N eingegebenen Abtastwerte behält der Dezimator **514** einen Abtastwert und verwirft die verbleibenden N – 1 Abtastwerte. Die Ausgabe von dem Dezimator **514** weist die ZF-Abtastwerte auf, die an Multiplizierer **518a** und **518b** gegeben werden. Die Multiplizierer **518a** und **518b** wandeln die ZF-Abtastwerte in I- und Q-Basisband-Abtastwerte herab, jeweils mit den phasengleichen  $\cos(w_c t)$ - und Quadratur- $\sin(w_c t)$ -Sinuskurven. Die I- und Q-Basisband-Abtastwerte werden jeweils an Tiefpassfilter **520a** und **520b** gegeben, welche die Abtastwerte filtern, um die I- und Q-Ausgaben zu liefern. Die I- und Q-Ausgaben werden an einen Basisband-Prozessor **530** gegeben, der eine zusätzliche Signalverarbeitung durchführt, wie Filtern, Dezimierung, Fehlererfassung/Fehlerkorrektur und Dekomprimierung. In dem beispielhaften Ausführungsbeispiel können der Bandpassfilter **512** und/oder die Tiefpassfilter **520** auch ein Skalieren des Signals vorsehen, um dem digitalen Signalprozessor **530** zu ermöglichen, Basisbanddaten verschiedener Amplituden zu liefern. Andere Implementierungen des digitalen Signalprozessors **250** können zur Durchführung einer Quadraturdemodulation gestaltet werden und befinden sich in dem Bereich der vorliegenden Erfindung.

**[0046]** Die Fehlerunterdrückungsschaltung **350** und der Bandpassfilter **512** können in direkter Implementierung implementiert werden, wie in den [Fig. 5](#) und [Fig. 6](#) gezeigt wird. Jedoch würde eine direkte Implementierung eine komplizierte Gestaltung hervorbringen, da zwei Schaltungen für die Fehlerunterdrückungsschaltung **350** und den Bandpassfilter **512** erforderlich sind, und der Bandpassfilter **512** wäre derart gestaltet, dass er auf einem Signal mit einer fünf-Bit-Auflösung arbeitet. In der vorliegenden Erfindung sind die Fehlerunterdrückungsschaltung **350** und der Bandpassfilter **512** kombiniert.

**[0047]** Ein beispielhaftes Blockdiagramm der digitalen Signalverarbeitung der Y1- und Y2-Signale unter Verwendung einer Rauschunterdrückungsschaltung **600** wird in [Fig. 6](#) dargestellt. Die Y1- und Y2-Signale werden jeweils an Bandpassdezimatoren **602** und **604** gegeben. In dem beispielhaften Ausführungsbei-

spiel ist ein Bandpassdezimator für jede Schleife des MASH-ADCs **240a** vorgesehen. In dem Bandpassdezimator **602** wird das Y1-Signal an einen FehlerunterdrückungsfILTER **608** gegeben, der Y1 mit der in der Gleichung (2) gezeigten Übertragungsfunktion  $EC_{Y_1}(z)$  filtert. Das gefilterte Y1 wird an einen Bandpassfilter **612a** geliefert. In dem beispielhaften Ausführungsbeispiel weisen die Bandpassfilter **612** jeweils dieselbe, wie in der Gleichung (3) gezeigte, Übertragungsfunktion wie der Bandpassfilter **512** auf. Das gefilterte Signal von dem Bandpassfilter **612a** wird an einen Dezimator **614** gegeben, der auf dieselbe Weise wie der Dezimator **514** arbeitet. Der Bandpassdezimator **604** ist identisch zu dem Bandpassdezimator **602**, außer dass ein FehlerunterdrückungsfILTER **610** die in der Gleichung (2) gezeigte Übertragungsfunktion  $EC_{Y_2}(z)$  implementiert.

**[0048]** In dem beispielhaften Ausführungsbeispiel sind die Übertragungsfunktionen des Fehlerunterdrückungsfilters **608** und des Bandpassfilters **612a** gefaltet, um die Übertragungsfunktion des Bandpassdezimators **602** zu erzeugen. Ähnlich sind die Übertragungsfunktionen des Fehlerunterdrückungsfilters **610** und des Bandpassfilters **612b** gefaltet, um die Übertragungsfunktion des Bandpassdezimators **604** zu erzeugen. Die Verbesserung, die durch eine Implementierung der Bandpassdezimatoren **602** und **604** mit den gefalteten Übertragungsfunktionen erreicht wird, kann für einen beispielhaften Bandpassfilter **612** der dritten Ordnung dargestellt werden. Die Übertragungsfunktion  $N_{BPF_3}(z)$  des Bandpassfilters **612** der dritten Ordnung kann aus der Gleichung (3) mit  $p = 3$  berechnet werden und als ein FIR-Filter mit den folgenden Koeffizienten dargestellt werden:

$$H_{BPF_3}(z) = [1 \ 0 \ -3 \ 0 \ 6 \ 0 \ -7 \ 0 \ 6 \ 0 \ -3 \ 0 \ 1]. \quad (4)$$

**[0049]** Für den Bandpassdezimator **602** erzeugt ein Falten der Koeffizienten des Fehlerunterdrückungsfilters **608** mit den Koeffizienten des Bandpassfilters **612a** die resultierende Übertragungsfunktion  $H_{Y_1}(z)$ , die in der Gleichung (5) gezeigt wird. Ähnlich erzeugt für den Bandpassdezimator **604** ein Falten der Koeffizienten des Fehlerunterdrückungsfilters **610** mit den Koeffizienten des Bandpassfilters **612b** die resultierende Übertragungsfunktion  $H_{Y_2}(z)$ .  $H_{Y_1}(z)$  und  $H_{Y_2}(z)$  können als FIR-Filter mit den in Gleichung (5) gezeigten Koeffizienten ausgedrückt werden.

$$\begin{aligned} H_{Y_1} &= [0 \ 0 \ 0 \ 2 \ 0 \ -4 \ 0 \ 7 \ 0 \ -5 \ 0 \ 4 \ 0 \ -1 \ 0 \ 2 \ 0 \ -1 \ 0 \ 1] \\ H_{Y_2} &= [1 \ 0 \ -1 \ 0 \ 1 \ 0 \ 2 \ 0 \ -2 \ 0 \ 2 \ 0 \ 1 \ 0 \ -1 \ 0 \ 1] \cdot 4 \end{aligned} \quad (5)$$

**[0050]** Die Faltung der Koeffizienten für die FehlerunterdrückungsfILTER **608** und **610** mit den Koeffizienten für den Bandpassfilter **612**, um jeweils die gefalteten Filter-Koeffizienten  $H_{Y_1}(z)$  und  $H_{Y_2}(z)$  zu bekommen, sieht viele Verbesserungen vor. Erstens wird die erforderliche Anzahl von Additionsschaltungen (adders) durch die Faltung der zwei Übertragungs-

funktionen reduziert. Aus der Gleichung (4) ist offensichtlich, dass die Implementierung der Bandpassfilter-Übertragungsfunktion  $H_{BPF3}(z)$  zwölf Addierer erfordert (z.B. einen Addierer für jeden Koeffizient von 1 und zwei Addierer für jeden Koeffizient von  $-3, 6$  oder  $7$ ). Im Gegensatz dazu ist aus der Gleichung (5) offensichtlich, dass die Implementierung des gefalteten Filters  $H_{Y1}(z)$  elf Addierer erfordert (z.B. einen Addierer für jeden Koeffizient von  $1, -1, 2, 4$  oder  $-4$  und zwei Addierer für jeden Koeffizient von  $-5$  oder  $7$ ). Ähnlich ist offensichtlich, dass die Implementierung des gefalteten Filters  $H_{Y2}(z)$  neun Addierer erfordert (z.B. einen Addierer für jeden Koeffizient von  $1, -1, 2$  oder  $-2$ ). Die Anzahl der für die gefalteten Filter (Fehlerunterdrückungsfilter und Bandpassfilter) erforderlichen Addierer ist geringer als die für den Bandpassfilter alleine. Zweitens arbeiten die gefalteten Filter  $H_{Y1}(z)$  und  $H_{Y2}(z)$  jeweils auf den Y1- und Y2-Signalen, wobei jedes nur ein Bit Auflösung hat. Im Gegensatz dazu würde eine direkte Implementierung (z.B. ohne eine Faltung) der Fehlerunterdrückungsfilter **608** und **610** und der Bandpassfilter **612** dazu führen, dass die Bandpassfilter **612** auf 5-Bit-Ausgaben von den Fehlerunterdrückungsfiltern **608** und **610** betrieben werden müssen. Drittens können die Dezimatoren **614** in die gefalteten Filter  $H_{Y1}(z)$  und  $H_{Y2}(z)$  derart integriert werden, dass ein Ausgabe-Abtastwert einmal alle N Eingabe-Abtastwerte berechnet wird. Ein Betreiben der gefalteten Filter bei  $1/N$  der Frequenz des ADC-Abtast-Takts minimiert den Energieverbrauch.

**[0051]** In dem beispielhaften Ausführungsbeispiel ist für einen Subsampling-Bandpassempfänger der ADC **240** ein Bandpass- $\Sigma\Delta$ -ADC **240a**, der das Quantisierungsrauschen auf die in der ebenfalls anstehenden U.S. Patentanmeldung Nr. PA447 offenbare Weise formt. Für einen Bandpass- $\Sigma\Delta$ -ADC wird das Quantisierungsrauschen um  $0.25 \cdot f_{ADC}$  herum nach DC (Gleichstrom) und  $0.50 \cdot f_{ADC}$  geschoben, wo ein Filtern des Quantisierungsrauschens durchgeführt werden kann. In dem beispielhaften Ausführungsbeispiel wird die Mittenfrequenz des ZF-Signals derart gewählt, dass ein Spiegelsignal nach der Analog-Digital-Wandlung bei  $f_c = 0.25 \cdot f_{ADC}$  erscheint, die Frequenz, bei der das Quantisierungsrauschen minimiert ist.

**[0052]** Der in [Fig. 5](#) gezeigte Quadraturabwärtsumsetzer wird in [Fig. 7A](#) erneut dargestellt. Die ZF-Abtastwerte von dem Dezimator **514** werden durch die Multiplizierer **518a** und **518b** jeweils mit den phasengleichen  $\cos(w_c t)$ - und Quadratur- $\sin(w_c t)$ -Sinuskurven auf Basisband-Abtastwerte abwärtsgewandelt. Durch eine geeignete Auswahl der ADC-Abtastfrequenz in Bezug zu der Mittenfrequenz des ZF-Signals kann die Stufe der Frequenz-Abwärtswandlung einfach gemacht werden. Insbesondere, wenn die ADC-Abtastfrequenz so gewählt wird, dass sie ungefähr viermal die Mittenfrequenz des abwärtsgewan-

delten Spiegelsignals ( $z.B. f_c = 0.25 \cdot f_{ADC}$ ) ist, kann die Quadraturabwärtsumwandlung durch die Multiplizierer **518a** und **518b** durch Multiplizieren der ZF-Abtastwerte jeweils mit der phasengleichen Sequenz  $[1, 0, -1, 0, 1, 0, \dots]$  und der Quadratur-Sequenz  $[0, 1, 0, -1, 0, 1, \dots]$  durchgeführt werden, wie in [Fig. 7B](#) gezeigt wird. Wenn  $f_c = 0.25 \cdot f_{ADC}$  ist, werden die Sinus- und Kosinusfunktionen bei  $(i\pi/2)$  berechnet und nehmen die Werte von  $1, 0$  oder  $-1$  für ganzzahlige Werte von  $i$  an. In dem beispielhaften Ausführungsbeispiel kann ein externer Frequenzregelkreis verwendet werden, um die Mittenfrequenz des Spiegelsignals bei ungefähr einem Viertel der ADC-Abtastfrequenz zu halten.

**[0053]** Unter Bezugnahme auf [Fig. 7B](#) ist zu sehen, dass jeder zweite Wert der phasengleichen Sequenz  $[1, 0, -1, 0, 1, 0, \dots]$  Null ist. Ähnlich ist auch zu sehen, dass jeder zweite Wert der Quadratur-Sequenz  $[0, 1, 0, -1, 0, 1, \dots]$  Null ist. Ferner sind die phasengleichen Sequenz und die Quadratur-Sequenz gültig (z.B. nicht Null) auf alternativen Werten. Diese Charakteristiken können verwendet werden, um die Gestaltung des Quadraturabwärtsumsetzers zu vereinfachen.

**[0054]** Ein Blockdiagramm eines beispielhaften Quadraturabwärtsumsetzers, der die obigen Charakteristiken ausnutzt, wird in [Fig. 7C](#) gezeigt. In dem beispielhaften Ausführungsbeispiel ist der Quadraturabwärtsumsetzer derart ausgebildet, dass jeder zweite ZF-Abtastwert von einem Demultiplexer (DEMUX) **716** an einen Multiplizierer **718a** geliefert wird und jeder zweite alternative ZF-Abtastwert an einen Multiplizierer **718b** geliefert wird. Unter Verwendung dieser Architektur können die Multiplizierer **718a** und **718b** mit der Hälfte der Geschwindigkeit der Multiplizierer **518a** und **518b** betrieben werden, wodurch der Energieverbrauch reduziert wird. Die Tiefpassfilter **720** und **722** sind jeweils äquivalent zu den Tiefpassfiltern **520a** und **520b**. Jedoch sind, aufgrund des Demultiplexverfahrens durch den DEMUX **716**, die an die Multiplizierer **718a** und **718b** gelieferten Abtastwerte in der Phase um  $90^\circ$  verschoben oder um einen Abtastwert zeitverschoben. In dem beispielhaften Ausführungsbeispiel ist, um die I-Ausgabe und die Q-Ausgabe von den Tiefpassfiltern **720** und **722** jeweils zeitlich zuzuordnen, der Tiefpassfilter **720** mit einer zusätzlichen Verzögerung von einem halben Abtastzyklus in Bezug zu der Verzögerung des Tiefpassfilters **722** ausgebildet. In dem beispielhaften Ausführungsbeispiel ist der Amplitudengang der Tiefpassfilter **720** und **722** annähernd gleich ausgebildet, um ein IQ-Ungleichgewicht und ein IQ-Nebensprechen zu minimieren. Die zusätzliche Verzögerung kann durch Verwendung unterschiedlicher Filterübertragungsfunktionen für die Filter **720** und **722** vorgenommen werden. Alternativ kann die zusätzliche Verzögerung durch Verwendung derselben Filterübertragungsfunktion für die Filter **720** und **722**, die mit zu-

mindest der doppelten Abtastrate getaktet sind, und Verzögern der Ausgabe des Filters **720** um einen halben Abtastwert vorgesehen werden. Verschiedene andere Verfahren, um einen im Wesentlichen gleichen Amplitudengang, aber unterschiedliche Verzögerungen für die Tiefpassfilter **720** und **722** vorzusehen, können in Betracht gezogen werden und befinden sich in dem Bereich der vorliegenden Erfindung.

**[0055]** Eine Spektralinversion des Spektrums des abgetasteten Signals kann auftreten, wenn das Signal unterabgetastet wird. Das Auftreten einer Spektralinversion ist abhängig von der Abtastfrequenz des ADCs in Bezug zu der Mittenfrequenz des abgetasteten Signals. In dem beispielhaften Ausführungsbeispiel ist das CDMA-Signal zentriert bei  $f_{ZF} = 0.25 \cdot (2n + 1) \cdot f_{ADC}$ , wobei  $n$  ein ganzzahliger Wert gleich oder größer als Null und  $f_{ADC}$  die ADC-Abtastfrequenz ist. Für ungerade  $n$  tritt eine Spektralinversion auf und für gerade  $n$  tritt keine Spektralinversion auf. Ebenso verursacht eine Dezimierung um 3 durch die Dezimatoren **614** eine Spektralinversion. Die Spektralinversion kann korrigiert werden durch Wahl einer Quadratur-Sinuskurve, die in der Phase um  $180^\circ$  verschoben ist, oder einer invertierten Quadratur-Sinuskurve. Die Quadratur-Sinuskurve oder die invertierte Quadratur-Sinuskurve kann durch einen Multiplexer (MUX) **724** von dem Spektralinversionssignal gewählt werden, wie in [Fig. 7C](#) gezeigt.

## II. Beispielhafte Gestaltung eines Bandpassemprängers

**[0056]** Eine beispielhafte Gestaltung für eine Rauschunterdrückungsschaltung und einen Quadraturabwärtsumsetzer für eine CDMA-Anwendung wird in [Fig. 8](#) gezeigt. Die in [Fig. 8](#) dargestellte Signalverarbeitung ist eine Kombination der in [Fig. 6](#) gezeigten Rauschunterdrückungsschaltungen und des in [Fig. 7C](#) gezeigten Quadraturabwärtsumsetzers. In dem beispielhaften Ausführungsbeispiel hat das CDMA-Signal eine Bandbreite von 1.228 MHz und ist bei  $f_{ZF} = 0.25 \cdot (2n + 1) \cdot f_{ADC}$  zentriert. Diese Beziehung zwischen der Mittenfrequenz und der ADC-Abtastfrequenz erzeugt ein Spiegelsignal des CDMA-Signals bei  $0.25 \cdot f_{ADC}$  nach der Umwandlung durch den ADC. In dem beispielhaften Ausführungsbeispiel ist der ADC als ein MASH-4-4- $\Sigma\Delta$ -ADC implementiert, wie in der oben angeführten U.S. Patentanmeldung Nr. PA447 beschrieben. In dem beispielhaften Ausführungsbeispiel kann der  $\Sigma\Delta$ -ADC in einem von mehreren Modi arbeiten. In dem Modus des hohen Dynamikbereichs liefert der  $\Sigma\Delta$ -ADC die Y1- und Y2-Signale, wie in [Fig. 3](#) gezeigt wird. In dem Modus des mittleren oder niedrigen Dynamikbereichs kann der  $\Sigma\Delta$ -ADC entweder das Y1-Signal oder das Y2-Signal liefern. Ein beispielhaftes Spektrum des Y1-Signals wird in [Fig. 10A](#) gezeigt.

**[0057]** In dem beispielhaften Ausführungsbeispiel

weist ein Bandpassdezimator **802** einen Fehlerunterdrückungsfilter **808**, einen Bandpassfilter **812a** und einen Dezimator **814a** auf, und ein Bandpassdezimator **804** weist einen Fehlerunterdrückungsfilter **810**, einen Bandpassfilter **812b** und einen Dezimator **814b** auf. In dem beispielhaften Ausführungsbeispiel sind die Fehlerunterdrückungsfilter **808** und **810** jeweils mit den Übertragungsfunktionen  $EC_{Y_1}(z)$  und  $EC_{Y_2}(z)$  ausgebildet, wie in der Gleichung (1) gezeigt wird. Ein beispielhaftes Spektrum des Y1-Signals nach dem Fehlerunterdrückungsfilter **808** wird in [Fig. 10B](#) gezeigt. In dem beispielhaften Ausführungsbeispiel sind die Bandpassfilter **812a** und **812b** jeweils mit den Fehlerunterdrückungsfiltern **808** und **810** verbunden und sind jeweils als ein Bandpassfilter der fünften Ordnung mit der in [Fig. 8](#) gezeigten Übertragungsfunktion ausgebildet. Die Bandpassfilter **812** der fünften Ordnung sind verschieden von dem beispielhaften Bandpassfilter der dritten Ordnung, der in den obigen Gleichungen (4) und (5) gezeigt wird. Die Filter der höheren Ordnung werden verwendet, um die Leistung des  $\Sigma\Delta$ -ADCs vollständiger zu erfassen. Die Fehlerunterdrückungsschaltung erzeugt eine tiefe Kerbe (notch) um das erwünschte Signalband herum (wodurch der Rauschgrundanteil des erwünschten Signalbands verringert wird) und verschiebt das Quantisierungsrauschen außerbands. Um den Dynamikbereich des  $\Sigma\Delta$ -ADCs vollständiger zu erfassen, wird der Bandpassfilter der fünften Ordnung dazu verwendet, das Ausserband-Quantisierungsrauschen derart zu filtern, dass das Rauschen, das von der nachfolgenden Dezimierungsstufe in das erwünschte Signalband gefaltet wird, in der Größe vergleichbar ist mit dem Rauschgrundanteil des  $\Sigma\Delta$ -ADCs. Ein beispielhaftes Frequenzverhalten des Bandpassfilters **812** wird in [Fig. 10C](#) gezeigt und ein beispielhaftes Spektrum des Y1-Signals nach dem Bandpassfilter **812a** wird in [Fig. 10D](#) gezeigt. Unterschiedliche Bandpassfilter-Übertragungsfunktionen und eine unterschiedliche Filterordnung können verwendet werden und befinden sich in dem Bereich der vorliegenden Erfindung.

**[0058]** In dem beispielhaften Ausführungsbeispiel sind die Dezimatoren **814** jeweils als ein 3:1-Dezimator implementiert. Eine Dezimierung um eine ungerade Ganzzahl (z. B. 3, 5, 7, 9, usw.) hält das CDMA-Signal derart auf einem Viertel der Abtastrate nach der Dezimierung, dass der nachfolgende Schritt der Quadraturabwärtsumwandlung einfach durchgeführt werden kann. Anfangs ist das CDMA-Signal nach der Wandlung durch den ADC um  $f_{ADC}/4$  zentriert, wie in den [Fig. 10A](#) und [Fig. 10B](#) gezeigt wird. Nach einer Dezimierung durch drei wird das CDMA-Signal derart gefaltet, dass das um  $f_{ADC}/4$  zentrierte Signal nach  $f_{ADC}/12$  oder  $f_s/4$  übertragen wird, wobei  $f_s$  die Abtastrate der dezimierten Abtastwerte ist. Für eine verbesserte Leistung wird das Rauschen bei  $f_{ADC}/12$  gefiltert durch Platzieren einer Kerbe (notch) an dieser Frequenzstelle in dem Bandpassfilter **812**, wie in der

**Fig. 10C** gezeigt. Ferner ist zu sehen, dass nach der Dezimierung um drei das Signal bei  $f_{ADC}/12$  ebenfalls auf  $f_{ADC}/12$  gefaltet wird. Somit ist der Bandpassfilter **812** mit einer zweiten Kerbe (notch) bei  $f_{ADC}/12$  ausgebildet, um unerwünschte Signale an dieser Frequenzstelle auszufiltern, die auf  $f_{ADC}/12$  gefaltet wird. Das beispielhafte Spektrum des Y1-Signals nach einer Dezimierung um drei wird in **Fig. 10E** gezeigt.

**[0059]** Wie oben angemerkt, wird die Übertragungsbzw. Transferfunktion der Bandpassfilter **812** basierend auf der Auswahl der Dezimatoren **814** gewählt. In dem beispielhaften Ausführungsbeispiel ist die Übertragungsfunktion des Bandpassfilters **812** mit einer Nullstelle bei  $f_s/4$  und bei jeder Frequenzstelle ausgebildet, die nach einer Dezimierung um N auf  $f_s/4$  gefaltet wird. Anders ausgedrückt, für eine Dezimierung um N ist der Bandpassfilter **812** derart ausgebildet, dass eine Nullstelle bei  $mf_{ADC}/4N$  platziert wird, wobei m eine positive ungerade Ganzzahl kleiner als 2N ist und  $m \neq N$  ist. Für die oben beschriebene Gestaltung der Dezimierung um drei werden Nullstellen bei  $f_{ADC}/12$  und  $5f_{ADC}/12$  platziert. Ähnlich werden für eine Gestaltung der Dezimierung um fünf Nullstellen bei  $f_{ADC}/20$ ,  $3f_{ADC}/20$ ,  $7f_{ADC}/20$  und  $9f_{ADC}/20$  platziert.

**[0060]** In dem beispielhaften Ausführungsbeispiel können die Koeffizienten für den Bandpassfilter, welche die Nullstellen an den erwünschten Frequenzstellen aufweisen, wie folgt synthetisiert werden. Beginne zuerst mit derselben Anzahl von Einsen wie die Dezimierung um N, z. B. [1 1 1] für eine Dezimierung um drei. Kehre zweitens jeden zweiten Filter-Koeffizienten um, z.B. [1 -1 1]. Und füge drittens eine Null zwischen jedes Paar von Koeffizienten ein, z.B. [1 0 -1 0 1]. Die Filter-Koeffizienten nach dem dritten Schritt weisen die Filterübertragungsfunktion auf, welche die Nullstellen an den erwünschten Frequenzstellen liefert. Für eine Dezimierung um fünf sind die Filter-Koeffizienten [1 0 -1 0 1 0 -1 0 1]. Ähnlich für eine Dezimierung um sieben sind die Filter-Koeffizienten [1 0 -1 0 1 0 -1 0 1 0 -1 0 1]. Es sei angemerkt, dass dieses Synthese-Verfahren nur für ungerade N anwendbar ist. Jedoch ist eine Dezimierung um ungerade N bevorzugt, da das Spiegelsignal des dezimierten Signals bei  $f_s/4$  behalten wird, um die Gestaltung des Quadraturabwärtsumsetzers zu vereinfachen.

**[0061]** Unter Bezugnahme auf **Fig. 8** werden die Ausgaben von den Dezimatoren **814a** und **814b** an einen Summierer **815** geliefert und kombiniert. Die ZF-Abtastwerte von dem Summierer **815** werden an einen Demultiplexer (DEMUX) **816** geliefert, der alternative Abtastwerte an Multiplizierer **816a** (**818a**) und **816b** (**818b**) leitet. Der DEMUX **816**, die Multiplizierer **818** und ein Multiplexer (MUX) **824** führen die Funktionen aus, die für den DEMUX **716**, die Multiplizierer **718** und den MUX **724**, in **Fig. 7C** gezeigt, be-

schrieben wurden. Die Ausgaben von den Multiplizierern **818a** und **818b** werden jeweils an Tiefpassfilter **820** und **822** gegeben. In dem beispielhaften Ausführungsbeispiel haben die Tiefpassfilter **820** und **822** die wie in **Fig. 8** gezeigten Übertragungsfunktionen. Die Übertragungsfunktion des Tiefpassfilters **820** hat einen im Wesentlichen gleichen Amplitudengang wie die Übertragungsfunktion des Tiefpassfilters **822**. Jedoch sieht die Übertragungsfunktion des Tiefpassfilters **820** eine zusätzliche Verzögerung um einen Abtastwert in Bezug zu der Verzögerung des Tiefpassfilters **822** derart vor, dass die I-Ausgabe der Q-Ausgabe zeitlich zugeordnet ist.

### III. Beispielhafte Polyphasenimplementierung

**[0062]** Die Rauschunterdrückungsschaltung und der Quadraturabwärtsumsetzer, die in **Fig. 8** gezeigt werden, können auf viele Arten implementiert werden. Eine beispielhafte Implementierung der Rauschunterdrückungsschaltung und des Quadraturabwärtsumsetzers unter Verwendung einer Polyphasenstruktur (polyphase structure) wird jeweils in den **Fig. 9A–B** gezeigt. Die Polyphasenstruktur ist ein funktionales und Bit-genaues Äquivalent zu der direkten Implementierung und zieht einen Vorteil aus der Eigenschaft, dass jeder zweite Koeffizient in den Übertragungsfunktionen der FehlerunterdrückungsfILTER **808** und **810** und des Filters **812** Null ist. Die Polyphasenstruktur führt eine einfache Signalverarbeitung auf mehreren Phasen des Eingangssignals durch und kombiniert die Zwischenausgaben, um die gewünschte Ausgabe hervorzu bringen. Der Dezimator **814** kann in die Polyphasenstruktur integriert werden unter Verwendung eines Taktschemas, in dem die Y1- und Y2-Signale um sechs dezimiert werden, bevor eine Verarbeitung durchgeführt wird. Die Vor-Dezimierung ermöglicht, dass die Register der Polyphasenstruktur bei einer geringeren Taktfrequenz betrieben werden, was den Energieverbrauch reduziert.

**[0063]** Wie in **Fig. 9A** gezeigt, wird das Y1-Signal an die Polyphasenfilter **902a** und **904a** geliefert und das Y2-Signal wird an die Polyphasenfilter **902b** und **904b** geliefert. In dem beispielhaften Ausführungsbeispiel sind alle in **Fig. 9A** mit „A“ bezeichneten Register mit der ansteigenden Flanke eines Takts ( $f_{ADC}/2$ ) getaktet, was die Hälfte der Frequenz des ADC-Abtast-Takts ist, alle mit „B“ bezeichneten Register sind mit der abfallenden Flanke des  $f_{ADC}/2$ -Takts getaktet und alle mit „C“ bezeichneten Register sind mit der ansteigenden Flanke eines Takts ( $f_{ADC}/6$ ) getaktet, was ein Sechstel der Frequenz des ADC-Abtast-Takts ist.

**[0064]** In dem Polyphasenfilter **902a** wird Y1 an ein Register **914a** gegeben. Die Ausgabe von dem Register **914a** wird an ein Register **914b** gegeben und die Ausgabe von dem Register **914b** wird an ein Re-

gister **914c** gegeben. Die Register **914** liefern drei Phasen des Y1-Signals. Die drei Phasen von Y1 von den Registern **914a**, **914b** und **914c** werden jeweils an Filter **912a**, **912b** und **912c** geliefert. In dem Filter **912a** wird die Ausgabe von dem Register **914a** an ein Register **916a** geliefert, die Ausgabe von dem Register **916a** wird an ein Register **916b** und an ein Verstärkungselement **918a** geliefert, die Ausgabe von dem Register **916b** wird an ein Register **916c** und an ein Verstärkungselement **918b** geliefert, die Ausgabe von dem Register **916c** wird an ein Register **916d** und an ein Verstärkungselement **918c** geliefert, die Ausgabe von dem Register **916d** wird an ein Register **916e** und an ein Verstärkungselement **918d** geliefert, die Ausgabe von dem Register **916e** wird an ein Register **916f** und an ein Verstärkungselement **918e** geliefert und die Ausgabe von dem Register **916f** wird an ein Verstärkungselement **918f** geliefert. In dem beispielhaften Ausführungsbeispiel sind die Verstärkungen der Verstärkungselemente **918a**, **918b**, **918c**, **918d**, **918e** und **918f** in dem Filter **912a**  $[0, -8, 45, -21, 7, 0]$ . Ähnlich sind in dem beispielhaften Ausführungsbeispiel die Verstärkungen des Filters **912b**  $[0, 21, -42, 15, -3, 0]$  und die Verstärkungen des Filters **912c** sind  $[2, -35, 33, -10, 1, 0]$ . In dem beispielhaften Ausführungsbeispiel sind die Verstärkungen der drei Filter in dem Polyphasenfilter **902b**  $[1, -5, -12, -5, 1, 0]$ ,  $[-3, 0, 9, 6, 0, 0]$  und  $[6, 9, 0, -3, 0, 0]$ . Die beispielhaften Verstärkungen des Filters **912d** betragen  $[0, 2, -35, 33, -10, 1]$ , die beispielhaften Verstärkungen des Filters **912e** betragen  $[0, -8, 45, -21, 7, 0]$  und die beispielhaften Verstärkungen des Filters **912f** betragen  $[0, 21, -42, 15, -3, 0]$ . Die beispielhaften Verstärkungen der drei Filter in dem Polyphasenfilter **904b** betragen  $[0, 6, 9, 0, -3, 0]$ ,  $[1, -5, -12, -5, 1, 0]$  und  $[-3, 0, 9, 6, 0, 0]$ . Die Polyphasenfilter können derart implementiert werden, dass die Koeffizienten neu angeordnet und/oder kombiniert werden können, um die Gestaltung der Hardware zu vereinfachen. Zum Beispiel können die Filterverstärkungen von  $[-3, 0, 9, 6, 0, 0]$  als  $3 \cdot [-1, 0, 3, 2, 0, 0]$  implementiert werden. In diesem Fall können die Datenabtastwerte, die den Koeffizienten  $-1$  und  $2$  entsprechen, skaliert und kombiniert werden, die resultierende Summe kann mit dem skalierten Datenabtastwert kombiniert werden, der dem Koeffizient  $3$  entspricht, und das gesamte Ergebnis kann um drei skaliert werden.

**[0065]** Ein Addierer **920b** empfängt die Ausgaben von den Verstärkungselementen **918a** und **918b**, summiert die beiden Signale und liefert die Ausgabe an einen Addierer **920c**. Der Addierer **920c** empfängt auch die Ausgabe von dem Verstärkungselement **918c**, summiert die beiden Signale und liefert die Ausgabe an einen Addierer **920d**. Der Addierer **920d** empfängt auch die Ausgabe von dem Verstärkungselement **918d**, summiert die beiden Signale und liefert die Ausgabe des Filters **912a**. Die Ausgaben der Filter **912a**, **912b** und **912c** werden an einen Addierer

**922a** geliefert, der die drei Signale summiert, um die Ausgabe des Polyphasenfilters **902a** zu liefern. Der Polyphasenfilter **902b** ist identisch zu dem Polyphasenfilter **902a**. Die Polyphasenfilter **904** sind identisch zu den Polyphasenfiltern **902** mit der Ausnahme, dass die „A“-Register **914** in dem Polyphasenfilter **902** von den „B“-Registern **906** in dem Polyphasenfilter **904** ersetzt werden.

**[0066]** Die Polyphasenfilter **902** und **904** führen jeweils die meisten Funktionen der Fehlerunterdrückungsfilter **808** und **810** und der Bandpassfilter **812** in [Fig. 8](#) durch. Die Ausgabe von den Polyphasenfiltern **902b** und **904b** werden jeweils an Verstärkungselemente **932a** und **932b** geliefert. Jedes Verstärkungselement **932** skaliert die jeweilige Ausgabe mit einer beispielhaften Verstärkung von vier, um die Verstärkung des Fehlerunterdrückungsfilters **810** zu berücksichtigen. Die Ausgabe von dem Polyphasenfilter **902a** und die Ausgabe von dem Verstärkungselement **932a** werden an einen Addierer **930a** geliefert, der die beiden Signale summiert. Ähnlich wird die Ausgabe von dem Polyphasenfilter **904a** und die Ausgabe von dem Verstärkungselement **932b** an einen Addierer **930b** geliefert, der die beiden Signale summieren. Die Ausgaben von den Addierern **930a** und **930b** weisen die beiden Ausgaben von der Rauschunterdrückungsschaltung auf und entsprechen den Ausgaben von dem DEMUX **816** in [Fig. 8](#).

**[0067]** Unter Bezugnahme auf [Fig. 9B](#) wird die Ausgabe von dem Addierer **930a** an einen Multiplexer (MUX) **936a** und ein Verstärkungselement **934a** geliefert, das das Signal mit einer Verstärkung von  $-1$  skaliert. Die Ausgabe von dem Verstärkungselement **934a** wird an den MUX **936a** geliefert. Der MUX **936a** wählt alternativ die Ausgabe von dem Verstärkungselement **934a** und die Ausgabe von dem Addierer **930a** und führt effektiv die Funktion des Multiplizierers **818a** in [Fig. 8](#) durch. Ein Register **916g** und ein Inverter **952a** liefern eine Sequenz von alternierenden Einsen und Nullen  $[1\ 0\ 1\ 0\ ...]$ , die zur Steuerung des MUX **936a** verwendet wird. Die Ausgabe von dem MUX **936a** wird an einen Tiefpassfilter **908** geliefert, der die Übertragungsfunktion des Tiefpassfilters **820** in [Fig. 8](#) implementiert. In dem Tiefpassfilter **908** wird die Ausgabe von dem MUX **936a** an ein Register **916e** und einen Addierer **920e** geliefert. Die Ausgabe von dem Register **916e** wird an ein Register **916f** und ein Verstärkungselement **918e** geliefert, das das Signal mit einer Verstärkung von sechs skaliert. Die Ausgabe von dem Verstärkungselement **918e** wird an den Addierer **920e** geliefert, der die beiden Eingaben summieren und die Ausgabe an einen Addierer **920f** liefert. Die Ausgabe von dem Register **916f** wird an den Addierer **920f** geliefert, der die beiden Eingaben summieren und die I-Ausgabe liefert.

**[0068]** Die Ausgabe von dem Addierer **930b** wird an einen Multiplexer (MUX) **936b** und ein Verstärkungs-

element **934b** geliefert, das das Signal mit einer Verstärkung von -1 skaliert. Die Ausgabe von dem Verstärkungselement **934b** wird an den MUX **936b** geliefert. Der MUX **936b** wählt alternativ die Ausgabe von dem Verstärkungselement **934b** und die Ausgabe von dem Addierer **930b** und führt effektiv die Funktion des Multiplizierers **818b** in [Fig. 8](#) durch. Die Sequenz von alternierenden Einsen und Nullen [1 0 1 0 ...] von dem Inverter **952a** wird an einen MUX **954** und einen Inverter **952b** geliefert. Die Ausgabe des Inverters **952b** wird an den MUX **954** geliefert. Der MUX **954** implementiert die Funktion des MUX **824** in [Fig. 8](#) und liefert eine der beiden Sequenzen zur Steuerung des MUX **936b**, abhängig von dem Spektralinversionssteuersignal. Die Ausgabe von dem MUX **936b** wird an einen Tiefpassfilter **910** geliefert, der die Übertragungsfunktion des Tiefpassfilters **822** in [Fig. 8](#) implementiert. In dem Tiefpassfilter **910** wird die Ausgabe von dem MUX **936b** an ein Register **916h** und einen Addierer **920h** geliefert. Die Ausgabe von dem Register **916h** wird ebenfalls an den Addierer **920h** geliefert, der die beiden Eingaben summiert und die Ausgabe an ein Verstärkungselement **938** liefert. Das Verstärkungselement **938** skaliert das Signal mit einer Verstärkung von vier und liefert die Q-Ausgabe.

**[0069]** Die vorliegende Erfindung wurde für einen Bandpassabtastempfänger beschrieben, der einen ΣΔ-ADC verwendet. Für einen Bandpassemmpfänger wird die Übertragungsfunktion des Fehlerunterdrückungsfilters entsprechend gewählt und ein Bandpassfilter wird verwendet, um das Quantisierungsrauschen vor der Quadraturabwärtsumwandlung zu filtern. Die vorliegende Erfindung ist auch anwendbar für einen Basisbandempfänger, der einen ΣΔ-ADC verwendet. Für einen Basisbandempfänger wird die Übertragungsfunktion des Fehlerunterdrückungsfilters für den Basisband-ΣΔ-ADC modifiziert und ein Tiefpassfilter wird verwendet, um das Quantisierungsrauschen zu filtern. Die Übertragungsfunktionen des Basisband-Fehlerunterdrückungsfilters und des Tiefpassfilters können gefaltet sein, um die Rauschunterdrückungsschaltung auf ähnliche Weise wie die oben für die Gestaltung des Bandpassemmpfängers beschriebene Weise zu erzeugen. Somit befindet sich die Adaptierung des oben beschriebenen erfinderischen Konzepts zur Verwendung in einem Basisbandempfänger in dem Bereich der vorliegenden Erfindung.

**[0070]** Die obige Beschreibung der bevorzugten Ausführungsbeispiele dient dazu, jedem Fachmann zu ermöglichen, die vorliegende Erfindung herzustellen oder zu verwenden. Die verschiedenen Modifikationen dieser Ausführungsbeispiele sind für Fachleute offensichtlich und die hier definierten generischen Prinzipien können auf andere Ausführungsbeispiele angewendet werden ohne die Anwendung einer erfinderischen Leistung.

## Patentansprüche

1. Eine Rauschunterdrückungsschaltung (**600**), die Folgendes aufweist:

zumindest einen Bandpassdezimator bzw. -dezimierer (**802**), wobei jeder Bandpassdezimator (**802**) einen Fehlerunterdrückungsfilter (**808**) aufweist, um ein Signal von einem Analog-zu-Digital-Wandler (analog-to-digital-converter = ADC) zu empfangen, und einen Filter (**812a**) aufweist, der verbunden ist mit dem Fehlerunterdrückungsfilter zum Filtern einer Ausgabe von dem Fehlerunterdrückungsfilter, **dadurch gekennzeichnet** dass Folgendes vorgesehen ist:

ein Summierer (**815**) verbunden mit jedem der mindestens einen Bandpassdezimatoren (**802**) zum Summieren der Ausgaben der Bandpassdezimatoren (**802**) und wobei eine Transferfunktion des Fehlerunterdrückungs- bzw. Löschungsfilters (**808**) mit einer Transferfunktion des Filters (**812a**) gefaltet (convolve) wird, um eine gefaltete Transferfunktion des jeweiligen Bandpassdezimators (**802**) zu generieren.

2. Rauschunterdrückungsschaltung (**600**) nach Anspruch 1, wobei der ADC ein Sigma-Delta-ADC ist.

3. Rauschunterdrückungsschaltung (**600**) nach Anspruch 2, wobei der ADC ein MASH-Sigma-Delta-ADC mit zwei Schleifen ist.

4. Rauschunterdrückungsschaltung (**600**) nach Anspruch 3, wobei der ADC ein MASH-4-4-Sigma-Delta-ADC ist.

5. Rauschunterdrückungsschaltung (**600**) nach einem der vorhergehenden Ansprüche, wobei der Filter entweder ein Bandpass- oder ein Tiefpassfilter ist.

6. Rauschunterdrückungsschaltung (**600**) nach einem der vorhergehenden Ansprüche, wobei jeder der zumindest einen Bandpassdezimatoren (**802**) weiterhin einen Dezimator (**814a**) aufweist, der verbunden ist mit dem Filter (**812a**) und zwar um eine Ausgabe des Filters (**812a**) zu empfangen und zu dezimieren.

7. Rauschunterdrückungsschaltung (**600**) nach Anspruch 6, wobei der Dezimator bzw. Dezimierer (**814a**) um N dezimiert, wobei N ein positiver, ungerader Integer- bzw. Ganzzahlwert ist.

8. Rauschunterdrückungsschaltung (**600**) nach Anspruch 6, wobei der Dezimierer (**814a**) um drei dezimiert.

9. Rauschunterdrückungsschaltung (**600**) nach Anspruch 6, wobei der Dezimierer (**814a**) um fünf dezimiert.

10. Rauschunterdrückungsschaltung (**600**) nach

Anspruch 6, wobei der Filter (812a) ein Bandpassfilter ist, der bei einem Viertel einer Abtastrate der dezimierten Abtastwerte bzw. Abtastungen von dem Dezimierer (814a) eine Null platziert hat.

11. Rauschunterdrückungsschaltung (600) nach Anspruch 10, wobei der Bandpassfilter mit zusätzlichen Nullen bzw. Nullstellen konstruiert ist, die bei  $mf_{ADC}/4N$  platziert sind, wobei N ein Dezimierungsfaktor des Dezmators, m ein positiver, ungerader Integer kleiner als 2N und nicht gleich N, und  $f_{ADC}$  eine Abtastfrequenz des ADC ist.

12. Rauschunterdrückungsschaltung (600) nach einem der vorhergehenden Ansprüche, der in einer Polyphasenstruktur implementiert ist.

13. Ein Quadraturabwärtsumsetzer, der Folgendes aufweist:

eine Rauschunterdrückungsschaltung nach einem der Ansprüche 1 bis 12, zum Empfangen zumindest einer Ausgabe von dem Analog-zu-Digital-Wandler (analog-to-digital-converter = ADC) und zum Vorsehen von ZF-Abtastwerten (IF samples);

zumindest einen Multiplizierer (818a), der mit der Rauschunterdrückungsschaltung (600) verbunden ist, zum Empfangen der ZF-Abtastwerte und zum Abwärtsumsetzen der ZF-Abtastwerte zu Basisbandabtastwerten.

14. Quadraturabwärtsumsetzer nach Anspruch 13, der Folgendes aufweist:

zumindest einen Bandpassdezimator (814a, 814b), einen Bandpassdezimator für jede Schleife eines MASH- $\Sigma$ - $\Delta$ -ADC, wobei jeder Bandpassdezimator eine Ausgabe von der entsprechenden Schleife empfängt;

der Summierer (815a) mit den Bandpassdezimatoren (814a, 814b) verbunden ist, wobei der Summierer (815) die Ausgaben der Bandpassdezimatoren summiert, um ZF-Abtastungen vorzusehen; und

zwei Multiplizierer (818a, 818b), die mit dem Summierer (815) verbunden sind, zum Empfangen der ZF-Abtastwerte und zum Abwärtsumsetzen der ZF-Abtastwerte zu Basisbandabtastwerten.

15. Quadraturabwärtsumsetzer nach Anspruch 14, der weiterhin Folgendes aufweist:

ein Tiefpassfilter (820, 822), der mit jedem der Multiplizierer (818a, 818b) verbunden ist, wobei die Tiefpassfilter (820, 822) die Basisbandabtastwerte filtern, um Basisbandausgaben vorzusehen.

16. Quadraturabwärtsumsetzer nach Anspruch 15, wobei die Amplitudenantworten der Tiefpassfilter (820, 822) im wesentlichen ähnlich sind.

17. Quadraturabwärtsumsetzer nach Anspruch 15, wobei eine Verzögerungsantwort eines Tiefpassfilters (820, 822) bezüglich Verzögerungen von den verbleibenden Filtern verzögert ist.

18. Quadraturabwärtsumsetzer nach einem der Ansprüche 14 bis 17, der in einer Polyphasenstruktur implementiert ist.

Es folgen 12 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7B

FIG. 7A

FIG. 7C

FIG. 8

FIG. 9B