(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6352552号

(P6352552)

(45) 発行日 平成30年7月4日(2018.7.4)

(24) 登録日 平成30年6月15日(2018.6.15)

(51) Int.Cl.

F 1

G 11 C 8/08 (2006.01)

G 11 C 8/10 (2006.01)G 11 C 8/08

G 11 C 8/10

請求項の数 19 (全 16 頁)

(21) 出願番号 特願2017-548466 (P2017-548466)

(86) (22) 出願日 平成28年3月16日 (2016.3.16)

(65) 公表番号 特表2018-513520 (P2018-513520A)

(43) 公表日 平成30年5月24日 (2018.5.24)

(86) 國際出願番号 PCT/US2016/022593

(87) 國際公開番号 WO2016/149333

(87) 國際公開日 平成28年9月22日 (2016.9.22)

審査請求日 平成30年4月24日 (2018.4.24)

(31) 優先権主張番号 62/133,840

(32) 優先日 平成27年3月16日 (2015.3.16)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 15/070,963

(32) 優先日 平成28年3月15日 (2016.3.15)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100112807

弁理士 岡田 貴志

最終頁に続く

(54) 【発明の名称】高速ワードラインデコードおよびレベルシフタ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の複数のデコードされた信号の第1のパワーサプライ電圧へのアサーションに応答してワードラインドライバノードをディスチャージするように構成された第1のロジックゲートと、

ワードラインと、

第2のパワーサプライ電圧により電力供給されるインバータと、ここにおいて、前記インバータは、前記ワードラインドライバノードの電圧を前記ワードラインに関するワードライン電圧に反転するように構成される、

前記第1のロジックゲートへのパワーサプライ入力ノードと前記第2のパワーサプライ電圧に関するパワーサプライノードとの間に結合されたスイッチと、

前記ワードラインドライバノードの前記ディスチャージと前記第1の複数のデコードされた信号内の前記デコードされた信号のうちの1つの補数のディスチャージとに応答して前記スイッチをスイッチオフするように構成された第2のロジックゲートと、ここにおいて、前記第2のパワーサプライ電圧は、前記第1のパワーサプライ電圧よりも大きい、を備えた回路。

## 【請求項 2】

前記第1のロジックゲートは、NANDゲートを備える、請求項1の回路。

## 【請求項 3】

前記NANDゲートは、前記第1の複数のデコードされた信号に対応する第1の複数の

10

20

PMOSトランジスタを備え、ここにおいて、前記第1の複数のPMOSトランジスタ内の各PMOSトランジスタは、前記パワーサプライ入力ノードに結合されたソースと、前記ワードラインドライバノードに結合されたドレインと、前記対応するデコードされた信号により駆動されるゲートとを含む、請求項2の回路。

【請求項4】

前記NANDゲートは、前記第1の複数のデコードされた信号に対応する第1の複数のNMOSトランジスタをさらに備え、前記第1の複数のNMOSトランジスタは、前記ワードラインドライバノードとグラウンドとの間に直列に配列され、前記第1の複数のNMOSトランジスタ内の各NMOSトランジスタは、前記対応するデコードされた信号により駆動されるゲートを有する、請求項3の回路。

10

【請求項5】

前記第2のロジックゲートは、前記第2のパワーサプライ電圧により電力供給されるNORゲートを備える、請求項1の回路。

【請求項6】

前記スイッチは、前記パワーサプライノードに結合されたソースと、前記パワーサプライ入力ノードに結合されたドレインとを有する第1のPMOSトランジスタを備え、前記NORゲートの出力は、前記第1のPMOSトランジスタのゲートに結合する、請求項5の回路。

【請求項7】

前記NORゲートは、第3のPMOSトランジスタに直列な第2のPMOSトランジスタを備え、前記第2のPMOSトランジスタは、前記パワーサプライノードに結合されたソースと、前記第3のPMOSトランジスタのソースに結合されたドレインと、前記デコードされた信号のうちの1つの前記補数により駆動されるように構成されるゲートとを有し、前記第3のPMOSトランジスタは、前記NORゲートの前記出力に結合されたドレインと、前記ワードラインドライバノードに結合されたゲートとを有する、請求項6の回路。

20

【請求項8】

前記NORゲートは、グラウンドに結合されたソースを有し、前記ワードラインドライバノードに結合されたゲートを有し、前記NORゲートの前記出力に結合されたドレインを有する第1のNMOSトランジスタをさらに備え、前記NORゲートは、グラウンドに結合されたソースを有し、前記NORゲートの前記出力に結合されたドレインを有し、前記デコードされた信号のうちの1つの前記補数により駆動されるように構成されたゲートを有する第2のNMOSトランジスタをさらに備える、請求項7の回路。

30

【請求項9】

前記第1の複数のデコードされた信号を提供するために複数のアドレス信号をデコードするように構成された行デコーダをさらに備えた、請求項1の回路。

【請求項10】

前記行デコーダは、前記複数のアドレス信号をデコードされた信号の複数のセットにデコードするようにさらに構成され、前記第1の複数のデコードされた信号は、デコードされた信号の前記複数のセット内のデコードされた信号の各セットから1つのデコードされた信号を備える、請求項9の回路。

40

【請求項11】

第1のパワーサプライ電圧により電力供給される第1のパワードメインにおいて、複数のデコードされた信号を前記第1のパワーサプライ電圧にアサートするためにアドレス信号をデコードすることと、

第2のパワーサプライ電圧により電力供給される第2のパワードメインにおいて、前記第2のパワーサプライ電圧を供給するパワーサプライノードからワードラインドライバノードを絶縁するためにスイッチを開放している間、前記複数のデコードされた信号の前記アサーションに応答して前記ワードラインドライバノードをディスチャージすることと、

前記ワードラインドライバノードの前記ディスチャージに応当して、前記第2のパワードライバノードをアサートすることと、

50

ドメイン内のワードラインに関する電圧を前記第2のパワーサプライ電圧にチャージすることと、

前記複数のデコードされた信号内の前記デコードされた信号の少なくとも1つのディスチャージに応当して、前記スイッチを閉成し、前記ワードラインドライバノードを前記第2のパワーサプライ電圧にチャージすることと、ここにおいて、前記第2のパワーサプライ電圧は、前記第1のパワーサプライ電圧よりも大きい、

を備えた方法。

【請求項12】

前記ワードラインドライバノードの前記第2のパワーサプライ電圧への前記チャージに応答して前記ワードラインをディスチャージすることをさらに備えた、請求項11の方法。

【請求項13】

NORゲート出力信号を生成するために前記第2のパワーサプライ電圧により電力供給されるNORゲートにおいて前記ワードラインドライバノードの電圧と前記デコードされた信号のうちの前記1つの補数をNORすることをさらに備え、前記スイッチを前記閉成することは、前記NORゲート出力信号のディスチャージに応当する、請求項11の方法。

【請求項14】

前記スイッチの前記開放は、前記第2のパワーサプライ電圧への前記NORゲート出力信号のチャージングに応答する、請求項13の方法。

【請求項15】

前記ワードラインドライバノードの電圧を制御するNANDゲート出力信号を生成するために前記スイッチを介して電力供給されるNANDゲート内の複数のデコードされた信号のNANDをとることをさらに備え、前記ワードラインドライバノードを前記第2のパワーサプライ電圧にチャージすることは、前記NANDゲート出力信号を前記第2のパワーサプライ電圧へ駆動することを備える、請求項11の方法。

【請求項16】

前記ワードラインドライバノードをディスチャージすることは、前記NANDゲート出力信号をディスチャージすることを備える、請求項15の方法。

【請求項17】

複数のデコードされた信号を生成するために複数のアドレス信号をデコードするように構成された行デコーダと、ここにおいて、前記行デコーダは、第1のパワーサプライ電圧により電力供給される第1のワードメイン内にある、

NANDゲート出力信号を生成するために前記複数のデコードされた信号のNANDをとるように構成されたNANDゲートと、ここにおいて、前記NANDゲートは、第2のパワーサプライ電圧により電力供給される第2のワードメイン内にあり、前記第2のパワーサプライ電圧は、前記第1のパワーサプライ電圧よりも大きい、

前記複数のデコードされた信号内の前記デコードされた信号のうちの1つのリセットに応答して前記第2のパワーサプライ電圧から前記NANDゲートを絶縁し、前記デコードされた信号のうちの前記1つのアサーションに応答して前記第2のパワーサプライ電圧に前記NANDゲートを結合する手段と、

ワードラインと、

前記NANDゲート出力信号のディスチャージに応当して前記第2のパワーサプライ電圧に前記ワードラインの電圧をアサートするように構成されたワードラインドライバと、を備えた、メモリ。

【請求項18】

前記ワードラインドライバは、前記第2のパワーサプライ電圧により電力供給されるインバータを備える、請求項17のメモリ。

【請求項19】

前記手段は、NORゲートとスイッチトランジスタとを備える、請求項17のメモリ。

10

20

30

40

50

## 【発明の詳細な説明】

## 【関連出願への相互参照】

## 【0001】

[0001]本願は2016年3月15日に出願された米国特許出願第15/070,963号および2015年3月16日に出願された米国仮出願第62/133,840号の優先権を主張し、それらの内容はすべての目的のためにそのすべてがここで参照することにより組み込まれる。

## 【技術分野】

## 【0002】

[0002]この出願はメモリに関し、特に、ワードラインを駆動するための高速レベルデコーダおよびレベルシフタに関する。 10

## 【背景技術】

## 【0003】

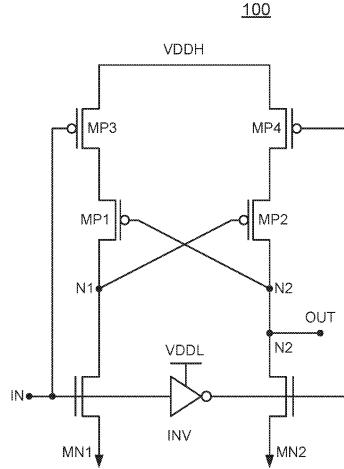

[0003]半導体技術がディープサブミクロンレジーム(deep submicron regime)に進化するにつれパワーサプライ電圧はトランジスタ寸法のスケーリングに呼応してスケールダウンされる。たとえば、マイクロプロセッサは現在1ボルト未満(a sub-one volt)のパワーサプライ電圧により電力供給されるトランジスタで製造される。しかし、これらのモダンシステムはより高い電圧ドメイン(domain)で動作する埋め込まれたメモリとインターフェースする必要があるかもしれない。電力を節約するために、メモリ内で駆動するワードラインに関するアドレスデコーディングは低電圧ドメインで生じる。従って、結果として生じるデコードされたワードライン信号は、選択されたワードラインを駆動するためにメモリの高電圧ドメインで使用される高パワーサプライ電圧にレベルシフトしなければならない。ワードライン駆動信号に関する入力信号(IN)と出力信号(OUT)との間の電圧レベルシフトを実行することができる典型的なレベルシフタ100が図1に示される。 20

## 【0004】

[0004]入力信号はN MOSトランジスタMN1のゲートを駆動する。入力信号がロウ(グラウンドまたはVSS)の場合、トランジスタMN1はスイッチオフしノードN1がグラウンドに対してフロート(float)することを可能にする。入力信号はまたN MOSトランジスタMN2のゲートを次に(in turn)駆動する反転入力信号を生成するインバータINVを駆動する。インバータINVは低電圧ドメイン(low-voltage power supply voltage)パワーサプライ電圧VDDLを供給するパワーサプライノードにより電力供給される。したがって、インバータINVは入力信号がロウのときトランジスタMN2のゲートをチャージし、それはノードN2をグラウンドにプルする(pull)ためにトランジスタMN2をスイッチオンする。 30

## 【0005】

[0005]ノードN2はそのドレインがノードN1に結合されたPMOSトランジスタMP1のゲートに結合する。トランジスタMP1はPMOSトランジスタMP2とクロス結合される。入力信号はまたトランジスタMP1と直列のPMOSトランジスタMP3のゲートを駆動する。入力信号がロウであるとき、トランジスタMP3とMP1は両方ともオンになり、それはノードN1を高電圧ドメインパワーサプライ電圧VDDHにチャージする。ノードN1はノードN2に結合されたトランジスタMP2のゲートを駆動する。したがって、入力信号がロウのときトランジスタMP2はオフになるであろう。反転入力信号によりそのゲートが駆動される別のPMOSトランジスタMP4はトランジスタMP3と直列である。 40

## 【0006】

[0006]ハイ(high)からVDDLに切り替わる入力信号に応答して、トランジスタMN1がスイッチオンしトランジスタMN2がスイッチオフするであろう。その結果入力信号がロウの間ディスチャージされた出力ノードN2はトランジスタMP2がスイッチオンすることができるまでフロートしなければならない。次に、トランジスタMP2はトランジスタMN1がノードN1をディスチャージできるまでスイッチオンすることができない。 50

しかしながら、トランジスタM P 1は依然として瞬間的にオンであり、ノードN 1をチャージし続けようと試み、その結果ノードN 1をディスチャージするトランジスタM N 1と競合する(fight with)。V D D Lは事実上(effectively)V D D Hに対して弱いゼロ(weak zero)なので、トランジスタM P 3はわずかにオンしているだけである。したがって、トランジスタM P 3はトランジスタM P 1への電荷の流れを制限することによりノードN 1をディスチャージする観点からトランジスタM N 1を支援する。ノードN 1がディスチャージされると、トランジスタM P 2はスイッチオンするであろう。反転入力信号がロウに駆動されることによりトランジスタM P 4はすでにオンであるので、トランジスタM P 2のスイッチオンは出力信号をV D D Hにチャージするであろう。入力信号がロウに遷移することに応答して反転信号がV D D Lに駆動されると、トランジスタM N 2とM P 2との間に類似の競合(analogous struggle)が生じる。

#### 【0007】

[0007] レベルシフタ100内のN M O SトランジスタとP M O Sトランジスタの間のこの競合はN M O S / P M O S競合の期間に被った遅延によりメモリタイミングに悪影響を及ぼす。より高い動作スピードでは、そのようなワードラインに関する一般的なレベルシフトは過度の遅延を招く。したがって、定電圧ドメインから高電圧ドメインへ遷移するときワードライン駆動信号に関する改良されたレベルシフトスピードを有する改良されたメモリ設計の必要性がある。

#### 【発明の概要】

#### 【0008】

[0008] 行デコーダによりデコードされるアドレスに従って選択された複数のワードラインを含むメモリが提供される。行デコーダはアドレスを複数のデコードされた信号にデコードする。各デコードされた信号はアドレス内の対応するビットのグループのデコードに対応する。各ワードラインにはデコードされた信号の固有の組み合わせまたはセットが割当られる。行デコーダによるアドレスのデコードはアドレスによりどのワードラインが選択されるかに応じてセットの1つのみがアサート(assert)される。したがって、デコードされた信号の1ワードラインのセットがアサートされると、デコードされた信号の残りのセットはいずれもアサートされないであろう。各ワードラインはデコードされた信号のそのセットがアサートされるかどうかを決定するように機能する対応するデコーダレベルシフタにより駆動される。セットがアサートされる場合、デコーダレベルシフタが対応するワードラインをメモリパワードメイン(power domain)に関するメモリパワーサプライ電圧に駆動する。対照的に、行デコーダは、ロジックパワーサプライ電圧により電力供給されるロジックパワードメイン内にある。したがって、デコードされた信号はメモリパワーサプライ電圧にアサートされるのとは対照的にロジックパワーサプライ電圧にアサートされる。

#### 【0009】

[0009] ワードラインの駆動に関する一般的なレベルシフトにおける遅延と電力損失を無くすために、各デコーダレベルシフタはすべてがロジックパワーサプライ電圧にアサートされるデコードされた信号のデコーダレベルシフタのセットに応答してワードラインドライバノードをディスチャージするN A N Dゲートのような第1のロジックゲートを含む。メモリパワードメインインバータ(a memory-power-domain inverter)はワードラインドライバノードのディスチャージに応答してメモリパワーサプライ電圧に対応するワードラインを駆動するようにワードラインドライバノードを反転する。第1のロジックゲートは、メモリパワーサプライ電圧を供給するメモリパワーサプライノードにスイッチを介して結合する。N O Rゲートのような第2のロジックゲートはスイッチを制御するためにリセット信号とワードラインドライバノード電圧を処理する。リセット信号はデコーダレベルシフタに関するセット内のデコードされた信号の1つの補数(complement)を備えることができる。したがって、セット内のすべてのデコードされた信号がアサートされたときリセット信号はディスチャージされる。ワードラインドライバノード電圧のディスチャージとリセット信号に応答して、第2のロジックゲートはスイッチを遮断する。反対に、第2の口

10

20

30

40

50

ジックゲートはリセット信号がアサートされデコードされた信号がグラウンドにデアサート(de-assert)されることに応答してスイッチをオンに駆動する。第1および第2のロジックゲートの組み合わせはかなりの改良されたメモリ動作スピードと低減された電力消費をもたらす。たとえば、デコーダレベルシフタがそのワードラインをアサートするとき P M O S / N M O S 競合はない。対照的にワードラインに関する一般的なレベルシフタはワードラインをアサートするような P M O S / N M O S 競合を被る。これらの有利な特徴は、以下の例となる実施形態に関連してより良く認識され得る。

【図面の簡単な説明】

【0010】

【図1】[0011]一般的なワードラインレベルシフタの回路図である。

10

【図2A】[0012]は本開示の態様に従うメモリのブロック図である。

【図2B】[0013]本開示の態様に従う図2Aのメモリ内のデコーダレベルシフタに関する回路図。

【図3】[0014]本開示の態様に従う図2Bのデコーダレベルシフタに関するより詳細な回路図。

【図4】[0015]本開示の態様に従うデコーダレベルシフタを含むメモリに関する動作方法に関するフローチャート。

【0011】

[0016]本開示の実施形態およびそれらの利点は以下の詳細な記述を参照することにより最もよく理解される。図の1つまたは複数において類似の素子を識別するために類似の参考符号が用いられることが理解されるべきである。

20

【発明の詳細な説明】

【0012】

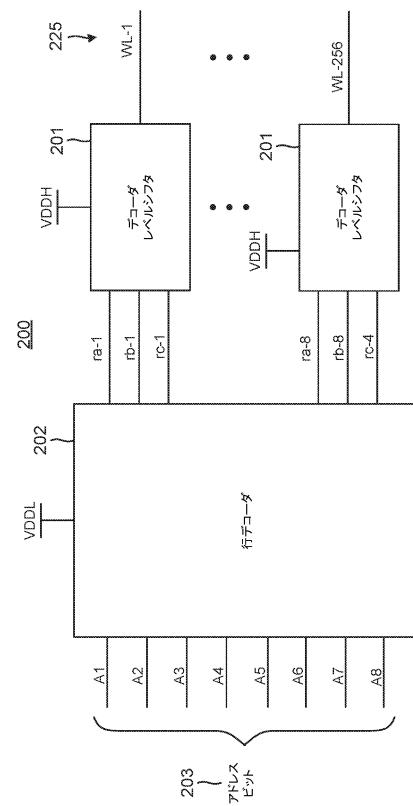

[0017]レベルシフタとしても機能するワードラインデコーダはメモリ動作スピードを増すために提供される。複数のワードライン(WL)を含む例示メモリ200が図2Aに示される。メモリ200において、第1のワードライン(WL-1)から最終ワードライン(WL-256)に及ぶ256ワードラインがある。しかしながら、代替態様では、ワードラインの数は256を超えるまたは未満であり得る。したがって、8ビットアドレス203は256ワードラインのいずれか1つを選択するのに十分である。アドレス203は第1のアドレスビットA1乃至最後のアドレスビットA8に及ぶ。ロジックパワードメイン(logic-power-domain)行デコーダ202はアドレス203をデコードする。ロジックパワードメインはロジックパワーサプライ電圧VDDLにより電力供給される。したがって、行デコーダ202はロジックパワーサプライ電圧VDDLを供給するロジックドメインパワーサプライノードに結合される。行デコーダ202と対照的に、複数のデコーダレベルシフタ201は、ロジックパワーサプライ電圧VDDLとは異なるメモリパワーサプライ電圧VDDHにより電力供給されるメモリパワードメイン内にある。一般に、ロジックパワーサプライ電圧VDDLとメモリパワーサプライ電圧VDDHに関する相対レベルはメモリ200を含む集積回路に関する動作モードに依存するであろう。

30

【0013】

[0018]ロジックパワードメインがハイパワー mode にあるのに対して、メモリパワードメインがロウパワー動作モードにある場合、ロジックパワーサプライ電圧VDDLはメモリパワーサプライ電圧より高いかもしれない。反対にロジックパワードメインがスタンバイまたはロウパワー動作モードにある場合、メモリパワーサプライ電圧VDDHはロジックパワーサプライ電圧VDDLよりも高いかもしれない。一般に、ロジックパワーサプライ電圧VDDLは典型的にメモリパワーサプライ電圧よりも低いので以下の説明はメモリパワーサプライ電圧VDDHは実際にはロジックパワーサプライ電圧VDDLよりも大きいと仮定する。しかしながら、ここに開示されたレベルシフトはまたワードラインを駆動することに関して振幅におけるレベルシフトダウンに適用可能であることが理解されよう。

40

【0014】

50

[0019]アドレス203のような相対的に広いアドレスをデコードする場合、全体のアドレスを各ワードラインに個別に対応する単一のデコードされた信号にデコードすることは極めて非効率である。言い換えれば、デコードされた信号が1対1でワードラインと対応するように行デコーダ202はアドレスビット203を256の異なるデコードされた信号にデコードすることは考えられ得る。しかし、そのような広範囲のデコーディングは遅くかつ非効率であろう。従って、行デコーダ202はアドレスビットのサブセットを複数の対応するデコードされた信号にデコードするよう構成される。メモリ200において、デコーダ202は3つのアドレスビット(例えば、アドレスビット(A1、A2、およびA3)をra-1乃至ra-8に及ぶraデコード信号にデコードするよう構成される。同様に、デコーダ202は別の3つのアドレスビット(例えば、アドレスビットA4、A5およびA6)をrb-1乃至rb-8(図示せず)に及ぶrbデコード信号にデコードするよう構成される。最後に、デコーダ202はアドレスビットA7およびA8のような残りの2つのアドレスビットをrc-1乃至rc-4に及ぶrcデコード信号にデコードするよう構成される。

#### 【0015】

[0020]したがって、デコーダ202は並列に動作している(running)3つの異なるデコーダを含むとみなすことができる。デコーダ202内の第1の3ビットデコーダ(図示せず)は対応するデコード信号ra-1乃至ra-8(ra信号)を生成する。デコーダ202内の第2の3ビットデコーダは対応するデコード信号rb-1乃至rb-8(rb信号)を生成する。最後に、デコーダ202内の2ビットデコーダは対応するデコード信号rc-1乃至rc-4(rc信号)を生成する。デコード信号に関して各ワードラインは独自の対応するデコーダレベルシフタ201を有する。したがって、256ワードラインに対応する256デコーダレベルシフタ201がある。ビットセルバンクに構成されるインプリメンテーションにおいて、1つのデコーダレベルシフタ201は右ワードラインおよび左ワードラインのような1対のワードラインに対応することができる。しかし、各バンク内では、デコーダレベルシフタに対するワードラインの対応はメモリ200に関して示されるように1対1である。

[0021]256のデコーダレベルシフタ201があるので、各デコードされたra信号に関して $256/8 = 32$ のデコーダレベルシフタがある。したがって、32のデコーダレベルシフタ201の1つのグループはデコードされたra-1信号を受信するであろう。32のデコーダレベルシフタ201の別のグループは32のデコーダレベルシフタ201の最終グループがデコードされたra-8信号を受信するようにデコードされたra-2信号を受信する、等々であろう。デコーダレベルシフタ201の類似のグループングはデコードされたrb信号に関してなされることができる。デコードされたrc信号に関して、rc信号は2つのアドレスビットをデコードすることから生じるという事実により、デコーダレベルシフタ201の4つのグループがあるのみであろう。この結果、各デコーダレベルシフタ201はデコードされた信号ra、rbおよびrcの固有の一意的な(its own unique)セットを受信する。

#### 【0016】

[0022]結果として生じるデコードされたra、rbおよびrcの分配において、デコーダレベルシフタ201とその対応するワードラインとの間の1対1の対応があるのと同じように、デコードされた信号とデコーダレベルシフタ201のいかなる所与のインスタンシエーション.instantiationの間にも1対1の対応がある。例えば、デコードされたra-1、rb-1およびrc-1のセットを受信する唯一つのデコーダレベルシフタ201がある。デコードされた信号の少なくとも1つは残りのデコーダレベルシフタ201のすべてに関して異なるであろう。例えば、他の(another)デコーダレベルシフタ(図示せず)はデコードされた信号ra-1およびrc-1を受信することができるがデコードされた信号rb-1は受信することができないであろう。そのかわり、この他の(this other)デコーダレベルシフタは残りのデコードされた信号rb-2乃至rb-8の1つを受信しなければならない。この態様において、各デコーダレベルシフタ201はアドレス信号

10

20

30

40

50

203が一意的に各ワードラインを識別することができるようにデコードされた信号の固有の組み合わせまたはセットを受信する。

【0017】

[0023]メモリ200と対照的に、一般的なメモリは各デコーダレベルシフタ201をANDゲートのようなロジックパワードメイン(logic-power-domain)デコーダで置き換えるであろう。その点に関して、行デコーダ202は選択されたワードラインに関して各デコードされた信号をアサートするように機能する。例えば、行デコーダ202は、ワードラインWL-1を選択するためにロジックパワーサプライ電圧VDDLにデコードされた信号ra-1、rb-1およびrc-1の各々をアサートするであろう。従って、一般的なVDDLパワーANDゲートはアサートされたデコード信号のセットを受信することに応答してその出力をハイにドライブするであろう。このANDゲート出力は次に図1に関して説明したレベルシフタ100によるようなメモリパワードメインに関するVDDHにレベルシフトされる必要があるであろう。しかし、この一般的なレベルシフトは上述したように低速でありかつ過度の電力を消費する。対照的に、デコーダレベルシフタ201は高速でありかつ電力消費が少ない。

【0018】

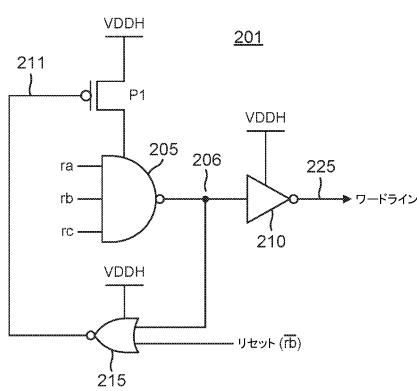

[0024]これらの利点のある特徴を提供するために、各デコーダレベルシフタ201は図2Bに示されるようにインプリメントされることができる。NANDゲート205のような第1のロジックゲートは特定のデコーダレベルシフタ201に割り当てられたra、rbおよびrc信号のデコードされたセットを処理する。デコードされた信号ra、rbおよびrcの集合はこれらのデコードされた信号の256の異なるインスタンシエーションの1つを表す。ra、rb、またはrcのような任意の個別のデコードされた信号に関して、デコーディングは終了される。たとえば、メモリ200(図2A)内の行デコーダ202はデコードされた信号ra-1乃至ra-8の1つをアサートするために3つのアドレスビットをデコードする。適切にデコードされた信号raのアサーションに関して為されるべきさらなるデコーディングはない。しかし、各デコーダレベルシフタ201はそのセット内の各デコードされた信号ra、rbおよびrcがアサートされるかどうかを決定するように機能する。したがって、この処理ステージはデコードされた信号ra、rbおよびrcのグループに関してである。行デコーダ202は従って個々のデコーディングを実行するのに対して各デコーダレベルシフタ201はグループデコーディングまたは処理を実行するように考慮されることができる。

【0019】

[0025]このグループデコーディングに関して、そのセット内の各デコードされた信号ra、rbおよびrcがアサートされる場合(行デコーダ202によってロジックパワーサプライ電圧VDDLにチャージされる)、NANDゲート205はNAND出力ノード206(ワードラインドライバノード)上を転送される(carried on)NAND出力信号をデイスチャージするであろう。メモリパワードメインインバータ210は、デコードされた信号ra、rbおよびrcのセットがすべてアサートされるとワードライン225をメモリパワーサプライ電圧VDDHに対してハイにチャージするためにNAND出力信号を反転する。NANDゲート205は、PMOSトランジスタP1のようなスイッチを介してメモリパワーサプライ電圧VDDHを供給するメモリドメインパワーサプライノードに結合する。トランジスタP1のソースはメモリドメインパワーサプライノードに結合し一方そのドレインはNANDゲート205のパワーサプライ入力ノードに結合する。NORゲート215のような第2のロジックゲートはNAND出力信号およびリセット信号を処理することに応答してトランジスタP1が導通か非導通かを制御する。rbの補数(complement)

【0020】

【数1】

( $\overline{rb}$ )

【0021】

10

20

30

40

50

のようなデコードされた信号の1つの補数としてリセット信号を形成することは便利である。その点に関して、行デコーダ202はワードラインアサーション期間の後でデコードされた信号をリセットすることに留意する必要がある。特に、行デコーダ202はアドレス203をデコードし、読み取りまたは書き込み期間の間にワードアサーション期間に適切なデコードされた信号をアサートする。ワードラインアサーション期間が終了された後、次に行デコーダ202はワードラインがデアサート(de-asserted)されるようすべてのデコードされた信号をデフォルトゼロ(ディスチャージされた値)にリセットする。したがって、ワードラインのセット内のすべてのデコードされた信号ra, rbおよびrcはワードラインアサーションの後ゼロにリセットされるのでどのデコードされた信号がリセット信号とし選択されるかは問題ではない。

10

## 【0022】

[0026] NORゲート215はトランジスタP1のゲートを駆動するNOR出力ノード211でフィードバック信号を生成するためにNAND出力信号とリセット信号を処理する。セット内のデコードされた信号ra、rb、rcの各々がアサートされると、リセット信号はNAND出力信号とともにロウになるであろう。NORゲート215はメモリパワードメイン内にあるので、NORゲート215は次にメモリパワーサプライ電圧VDDHへのフィードバック信号をアサートするであろう。メモリパワーサプライ電圧VDDHからNANDゲート205を絶縁するためにフィードバック信号のアサーションによってトランジスタP1は完全にオフになる。

20

## 【0023】

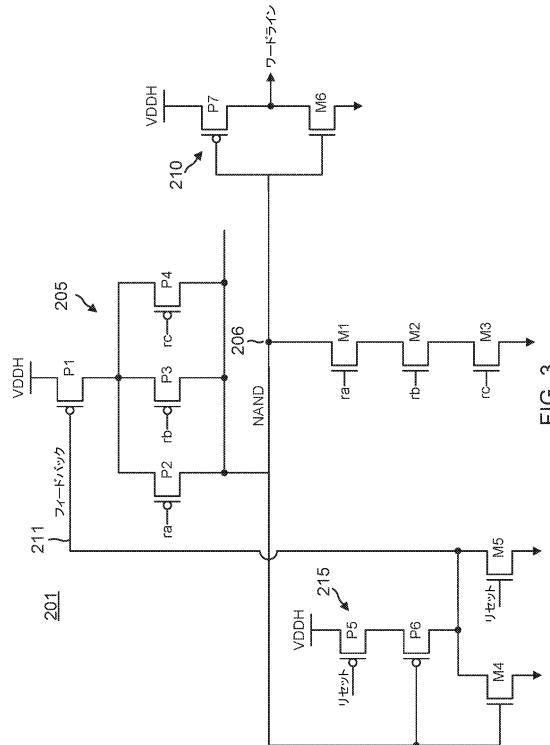

[0027] NANDゲート205は図3に示されるようにインプリメントされることができる。NAND出力ノード206はPMOSトランジスタP3とPMOSトランジスタP4に並列に配列されたPMOSトランジスタP2を介してトランジスタP1のドレインに結合する。トランジスタP2、P3、およびP4のソースはNANDゲート205に関するパワーサプライ入力ノードを形成する。デコードされた信号raはトランジスタP2のゲートを駆動する。同様に、デコードされた信号rbはトランジスタP3のゲートを駆動し、一方デコードされた信号rcはトランジスタP4のゲートを駆動する。NAND出力ノード206はNMOSトランジスタM1、NMOSトランジスタM2およびNMOSトランジスタM3の直列アレイを介してグラウンドに結合する。デコードされた信号raはトランジスタM1のゲートを駆動する。同様に、デコードされた信号rbはトランジスタM2のゲートを駆動し、一方デコードされた信号rcはトランジスタM3のゲートを駆動する。デコードされた信号ra、rb、rcはVDDLパワーサプライ電圧にのみアサートされるロジックドメイン信号である。それらのソースがパワーサプライノードに直接結合するなら、デコードされた信号ra、rb、rcがすべてそれらのロジックパワーサプライ電圧VDDLにアサートされるとメモリパワードメイントランジスタP1、P2、P3はすべて弱くオンになる(be weakly on)であろう。トランジスタP2、P3、P4は次にNAND出力ノード206のディスチャージの期間にトランジスタM1、M2およびM3と競合する(fight with)可能性があるであろう。したがって、トランジスタP1のスイッチングオフによってNAND出力ノード206のディスチャージの期間にメモリパワーサプライ電圧VDDHからトランジスタP2、P3、およびP4を絶縁することは電力を節約し、メモリ動作スピードを高める点で極めて有利である。

30

## 【0024】

[0028] 一般に、NANDゲート205内のP2、P3、およびP4のような並列に配列されたPMOSトランジスタの数はデコードされた信号の数に依存し、それは次にアドレス信号203に間接的に依存する(図1)。同様に、M1、M2およびM3のような直列に配列されたNMOSトランジスタの数もデコードされた信号の数、したがってアドレス信号203の幅に依存子し、それは次にメモリ200内のワードの数に依存する。Nのデコードされた信号(Nは複数の整数)を有する実施形態において、NANDゲート205は次にNAND出力ノード206とトランジスタP1のドレインとの間に並列に配列されたN個のPMOSトランジスタを含むことができる。N個のPMOSトランジスタはデコ

40

50

ーダレベルシフタ201に関するデコードされた信号のセット内のデコードされた信号に1対1で対応する。各デコードされた信号はその対応するPMOSトランジスタのゲートを駆動する。同様に、同じ実施形態はNAND出力ノード206とグラウンドとの間に並列に配列されたN個のNMOSトランジスタを含むであろう。N個のNMOSトランジスタはセット内の各デコードされた信号は対応するNMOSトランジスタのゲートを駆動するようにデコードされた信号に1対1で対応するであろう。

[0029]NANDゲート205がNAND出力ノード206に関してNANDゲート205がどのように配列されるかに比べて相補的な様でNOR出力ノード211に関してNORゲート215が配列される。特に、メモリパワーサプライ電圧VDDHを供給するメモリパワーサプライノードとNOR出力ノード211との間に直列に配列されたPMOSトランジスタP5とPMOSトランジスタP6が直接に配列される。反対に、NMOSトランジスタM4とNMOSトランジスタM5はグラウンドとNOR出力ノード211との間に並列に配列される。NAND出力信号はトランジスタP6とM4とを駆動する。同様に、リセット信号はトランジスタP5とM5のゲートを駆動する。デコードされた信号ra、rb、rcがアサートされると、リセット信号は、トランジスタM5を遮断し、トランジスタP5をスイッチオンするためにディスチャージされる。トランジスタM1、M2およびM3がすべて導通するので、NAND出力信号はディスチャージされ、それはトランジスタP6をスイッチオンし、トランジスタM4を遮断する。トランジスタP5とP6が導通するので、NOR出力ノード211上を転送されるフィードバック信号はメモリパワーサプライ電圧VDDHにチャージされる。ロジックパワーサプライ電圧VDDLがメモリパワーサプライ電圧VDDHよりも十分に低い場合、トランジスタP2、P3およびP4はデコードされた信号がすべてアサートされると弱くオンになるであろう(weakly on)。しかし、VDDHパワーサプライ電圧へのフィードバック信号のチャージは、トランジスタP2、P3およびP4がNAND出力信号のディスチャージに関してトランジスタM1、M2およびM3と競合(struggle with)できないようにトランジスタP1をスイッチオフする。PMOSトランジスタP1とNORゲート215の組み合わせは、デコードされた信号の1つのリセットに応答してメモリパワーサプライ電圧VDDHからNANDゲート205を絶縁し、デコードされた信号の1つのアサーションに応答してNANDゲートを第2のパワーサプライ電圧に結合する手段を備えるとみなすことができる。

### 【0025】

[0030]インバータ210はNMOSトランジスタM6と直列にPMOSトランジスタP7を備える。トランジスタP7とM6に関するドレインはワードラインに結合する。NAND出力信号はトランジスタP7とM6の両方のゲートを駆動する。トランジスタP7のソースはメモリドメインパワーサプライノードに結合されているので、NAND出力信号がディスチャージされると、トランジスタP7は次にワードラインをメモリパワーサプライ電圧VDDHにチャージする。読み取りまたは書き込み動作が終了すると、デコードされた信号は次にリセットされる(グラウンドにディスチャージされる)。リセット信号は次にトランジスタM5をスイッチオンするようにアサートされ、それはトランジスタP1をスイッチオンするためにフィードバック信号をディスチャージする。トランジスタP2、P3およびP4は次にNAND出力信号をメモリパワーサプライ電圧VDDHにチャージすることができる。したがって、ワードラインをディスチャージするようにNAND出力信号のアサーションに応答してトランジスタM6がスイッチオンされる。

### 【0026】

[0031]結果として生じるデコーダレベルシフタ201はレベルシフタ100のような一般的なレベルシフタが続く各ワードラインに関する一般的なグループデコーダの使用に比べて非常に有利である。特に、デコーダレベルシフタ201にNMOS/PMOS競合(struggle)が存在しないので、メモリ動作スピードは一般的なレベルシフタ100の使用に関して有利に増加される。さらに、NMOS/PMOS競合の消去はクローバ(crowbar)電流の関連づけられたディスチャージを消去するので、この増加された動作スピードはパワーセービングの増加を伴う(come with)。デコーダレベルシフタを含むメモリに関する

10

20

30

40

50

動作の方法が以下に説明される。

【0027】

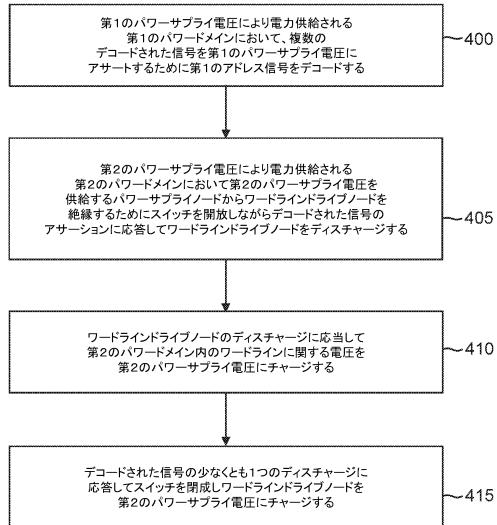

[0032]図4は本開示の観点に従うデコーダレベルシフタに関する動作の例示方法に関するフローチャートである。行為(act)400は第1のパワーサプライ電圧により電力供給される第1のパワードメインで実行され、複数のデコードされた信号を第1のパワーサプライ電圧にアサートするために第1のアドレス信号をデコードすることを備える。デコードされた信号r<sub>a</sub>、r<sub>b</sub>およびr<sub>c</sub>を生成するために行デコーダ202によるアドレス203のデコーディングは行為400の一例である。方法は、また第1のパワーサプライ電圧よりも大きい第2のパワーサプライ電圧により電力供給される第2のパワードメインにおいて実行される行為405を含み、第2のパワーサプライ電圧を供給するパワーサプライノードからワードラインドライバノードを絶縁するスイッチを動作させながらデコードされた信号のアサーションに応答してワードラインドライバノードをディスチャージすることを備える。トランジスタP1がスイッチオフされる間にNAND出力ノード206をディスチャージすることは行為405の一例である。方法はまたワードラインドライバノードのディスチャージに応当する行為410を含み第2のパワードメイン内のワードラインに関する電圧を第2のパワーサプライ電圧にチャージすることを備える。ワードライン225のアサーションは行為410の一例である。最後に、方法はデコードされた信号の少なくとも1つのディスチャージに応当して行為415を含みスイッチを閉じてワードラインドライバノードをパワーサプライノードにチャージすることを備える。トランジスタP1が導通している間にNAND出力ノード206をチャージすることは行為415の一例である。

【0028】

[0033]当業者が、近い将来に特定のアプリケーションを現時点で理解することとなり、依存していることとなる時、多くの修正、代替および変形は、その主旨および範囲から逸脱することなく、本開示のデバイスの使用の方法、構成、装置、およびマテリアルおよびそれらの中になれることができる。このことを踏まえて、本開示の範囲は、単にそれらのいくつかの例として、本明細書で例示され、説明された特定の実施形態のそれに、限定されるべきでなく、むしろ、以下に添付された特許請求の範囲のそれに十分に相応するべきである。

以下に本願の出願当初の特許請求の範囲に記載された発明を付記する。

30

[C1]

第1の複数のデコードされた信号を第1のパワーサプライ電圧にアサーションすることに応答してワードラインドライバノードをディスチャージするように構成された第1のロジックゲートと、

ワードラインと、

第2のパワーサプライ電圧により電力供給されるインバータと、ここにおいて前記インバータはワードラインドライバノードの電圧をワードラインに関するワードライン電圧に反転するように構成される、

第1のロジックゲートへのパワーサプライ入力ノードと前記第2のパワーサプライ電圧に関するパワーサプライノードとの間に結合されたスイッチと、

前記ワードラインドライバノードと前記第1の複数のデコードされた信号内の前記デコードされた信号の1つの補数に応答して前記スイッチをスイッチオフするように構成された第2のロジックゲートと、

を備えた回路。

40

[C2]

前記第1のロジックゲートはNANDゲートを備える、C1の回路。

[C3]

前記NANDゲートは前記第1の複数のデコードされた信号に対応する第1の複数のPMOSトランジスタを備え、ここにおいて、前記第1の複数のPMOSトランジスタ内の各PMOSトランジスタは前記パワーサプライ入力ノードに結合されたソースと、前記ワ

50

ードライアンドライバノードに結合されたドレインと、前記対応するデコードされた信号により駆動されるゲートを含む、C 1 の回路。

[ C 4 ]

前記 N A N D ゲートは、前記第 1 の複数のデコードされた信号に対応する第 1 の複数の N M O S トランジスタをさらに備え、前記第 1 の複数の N M O S トランジスタは前記ワードライアンドライバノードとグラウンドとの間に直列に配列され、前記第 1 の複数の N M O S トランジスタ内のある N M O S トランジスタは前記対応するデコードされた信号により駆動されるゲートを有する、C 3 の回路。

[ C 5 ]

前記第 2 のロジックゲートは前記第 2 のパワーサプライ電圧により電力供給される N O R ゲートを備える、C 1 の回路。

10

[ C 6 ]

前記スイッチは、ソースが前記パワーサプライノードに結合されドレインが前記パワーサプライ入力ノードに結合され第 1 の P M O S トランジスタを備え、前記 N O R ゲートの出力は前記第 1 の P M O S トランジスタのゲートに結合する、C 5 の回路。

[ C 7 ]

前記 N O R ゲートは第 3 の P M O S トランジスタに直列な第 2 の P M O S トランジスタを備え、

前記第 2 の P M O S トランジスタは前記パワーサプライノードに結合されたソースと、前記第 3 の P M O S トランジスタのソースに結合されたドレインと前記デコードされた信号の 1 つの補数 (complement) により駆動されるように構成されるゲートを有し、

20

前記第 3 の P M O S トランジスタは前記 N O R ゲートの前記出力に結合されたドレインと前記ワードライアンドライバノードに結合されたゲートを有する、C 6 の回路。

[ C 8 ]

前記 N O R ゲートは、グラウンドに結合されたソースと、前記ワードライアンドライバノードに結合されたゲートと、前記 N O R ゲートの前記出力に結合されたドレインを有する第 1 の N M O S トランジスタをさらに備え、

前記 N O R ゲートは、グラウンドに結合されたソースと、前記 N O R ゲートの前記出力に結合されたドレインと、前記デコードされた信号の 1 つの補数により駆動されるように構成されたゲートを有する第 2 の N M O S トランジスタをさらに備える、C 7 の回路。

30

[ C 9 ]

前記第 1 の複数のデコードされた信号を提供するために複数のアドレス信号をデコードするように構成された行デコーダをさらに備えた、C 1 の回路。

[ C 1 0 ]

前記行デコーダは前記複数のアドレス信号を複数のセットのデコードされた信号にデコードするようにさらに構成され、

前記第 1 の複数のデコードされた信号は前記デコードされた信号の複数のセット内のデコードされた信号の各セットから 1 つのデコードされた信号を備える、C 9 の回路。

[ C 1 1 ]

第 1 のパワーサプライ電圧により電力供給される第 1 のパワードメインにおいて、複数のデコードされた信号を前記第 1 のパワーサプライ電圧にアサートするためにアドレス信号をデコードすることと、

40

第 2 のパワーサプライ電圧により電力供給される第 2 のパワードメインにおいて、前記第 2 のパワーサプライ電圧を供給するパワーサプライノードから前記ワードライアンドライバノードを絶縁するためにスイッチを開放している間前記複数のデコードされた信号のアサーションに応答してワードライアンドライバノードをディスチャージすることと、

前記ワードライアンドライバノードの前記ディスチャージに応当して、前記第 2 のパワードメイン内のワードラインに関する電圧を前記第 2 のパワーサプライ電圧にチャージすることと、

前記複数のデコードされた信号内の前記デコードされた信号の少なくとも 1 つのディス

50

チャージに応当して、前記スイッチを閉成し、前記ワードラインドライバノードを前記第2のパワーサプライ電圧にチャージすることと、

を備えた方法。

[ C 1 2 ]

前記第2のパワーサプライ電圧は前記第1のパワーサプライ電圧よりも大きい、C 1 1の方法。

[ C 1 3 ]

ワードラインドライバノードを第2のパワーサプライ電圧にチャージすることに応答して前記ワードラインをディスチャージすることをさらに備えた、C 1 1の方法。

[ C 1 4 ]

N O Rゲート出力信号を生成するために前記第2のパワーサプライ電圧により電力供給されるN O Rゲートにおいて前記ワードラインドライバノードの電圧と前記デコードされた信号の前記1つの補数をN O Rすることをさらに備え、

前記スイッチを閉成することは前記N O Rゲート出力信号のディスチャージに応当する、C 1 1の方法。

[ C 1 5 ]

前記スイッチの開放は前記第2のパワーサプライ電圧への前記N O Rゲート出力のチャージングに応答する、C 1 4の方法。

[ C 1 6 ]

前記ワードラインドライバノードを制御するN A N Dゲート出力信号を生成するために前記スイッチを介して電力供給されるN A N Dゲート内の複数のデコードされた信号のN A N Dをとることをさらに備え、

前記ワードラインドライバノードを前記第2のパワーサプライ電圧にチャージすることは、前記N A N Dゲート出力信号を前記第2のパワーサプライ電圧へ駆動することを備える、C 1 4の方法。

[ C 1 7 ]

前記ワードラインドライバノードをディスチャージすることは前記N A N Dゲート出力信号をディスチャージすることを備える、C 1 6の方法。

[ C 1 8 ]

複数のデコードされた信号を生成するために複数のアドレス信号をデコードするように構成された行デコーダと、ここにおいて、前記行デコーダは、第1のパワーサプライ電圧により電力供給される第1のパワードメイン内にある、

N A N Dゲート出力信号を生成するために前記複数のデコードされた信号のN A N Dをとるように構成されたN A N Dゲートと、ここにおいて前記N A N Dゲートは第2のパワーサプライ電圧により電力供給される第2のパワードメイン内にある、

前記複数のデコードされた信号内の前記デコードされた信号の1つのリセットに応答して前記第2のパワーサプライ電圧から前記N A N Dゲートを絶縁し、前記デコードされた信号の1つのアサーションに応答して前記第2のパワーサプライ電圧に前記N A N Dゲートを結合する手段と、

ワードラインと、および

前記N A N Dゲート出力信号のディスチャージに応当して前記第2のパワーサプライ電圧に前記ワードラインの電圧をアサートするように構成されたワードラインドライバと、を備えた、メモリ。

[ C 1 9 ]

前記ワードラインドライバは、前記第2のパワーサプライ電圧により電力供給されるインバータを備える、C 1 8のメモリ。

[ C 2 0 ]

前記手段は、N O Rゲートとスイッチトランジスタを備える、C 1 8のメモリ。

10

20

30

40

【図1】

FIG. 1

- 従来技術 -

【図2A】

FIG. 2A

【図2B】

FIG. 2B

【図3】

FIG. 3

【図4】

FIG. 4

---

フロントページの続き

(72)発明者 ジュン、チョルミン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 チエン、ポ-フン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 リ、デイビッド

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 ユン、セイ・スン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 後藤 彰

(56)参考文献 特開2011-8902(JP, A)

特開2008-152845(JP, A)

特開2004-334982(JP, A)

米国特許出願公開第2006/0176081(US, A1)

特開2000-187977(JP, A)

米国特許出願公開第2014/0159773(US, A1)

(58)調査した分野(Int.Cl., DB名)

G11C 8/08

G11C 8/10