(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6773277号

(P6773277)

(45) 発行日 令和2年10月21日(2020.10.21)

(24) 登録日 令和2年10月5日(2020.10.5)

(51) Int.Cl.

G09F 9/30 (2006.01)

F 1

G09F 9/30 338

G09F 9/30 365

請求項の数 16 (全 23 頁)

(21) 出願番号 特願2016-155049 (P2016-155049)

(22) 出願日 平成28年8月5日 (2016.8.5)

(65) 公開番号 特開2018-22117 (P2018-22117A)

(43) 公開日 平成30年2月8日 (2018.2.8)

審査請求日 令和1年6月13日 (2019.6.13)

(73) 特許権者 519380923

天馬微電子有限公司

中華人民共和国廣東省深▲セン▼市竜華区

民治街道北駅社区留仙大道天馬大▲カ▼1

918

(74) 代理人 100114557

弁理士 河野 英仁

(72) 発明者 松枝 洋二郎

神奈川県川崎市中原区下沼部1753番地

NLTテクノロジー株式会社内

(72) 発明者 高取 肇一

神奈川県川崎市中原区下沼部1753番地

NLTテクノロジー株式会社内

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

非矩形状の表示領域内に、第1方向と第2方向とに沿って配列された複数の画素と、

前記第1方向に沿う第1画素群に、走査線を介して、走査信号を出力する走査回路を含む走査回路ブロックと、

前記第2方向に沿う第2画素群に、データ線を介して、前記走査信号が入力される画素の発光輝度に応じたデータ信号を出力するデータ信号回路を含むデータ信号回路ブロックと、

前記走査回路を制御する第1信号が供給される第1配線部と、

前記データ信号回路を制御する第2信号が供給される第2配線部と、

前記第1配線部と前記走査回路とを接続する第1補助配線部と、

前記第2配線部と前記データ信号回路とを接続する第2補助配線部とを備え、

前記走査回路ブロックは、前記第1配線部及び前記第1補助配線部並びに前記第2配線部を含み、

前記データ信号回路ブロックは、前記第2配線部及び前記第2補助配線部並びに前記第1配線部を含み、

前記走査回路と前記データ信号回路とは、前記表示領域の外周における第1領域に配置され、

前記第1配線部と前記第2配線部とは、前記第1領域の外周における第2領域に配置され、

10

20

前記第1補助配線部は、前記第1配線部の延伸方向と略直交する方向に沿って配置され、

前記第2補助配線部は、前記第2配線部の延伸方向と略直交する方向に沿って配置される表示装置。

**【請求項2】**

複数の走査回路と、

複数のデータ信号回路とを備え、

前記複数のデータ信号回路の各々は、複数のデータ線に時分割でデータ信号を順次出力するデマルチプレクサである請求項1に記載の表示装置。

**【請求項3】**

前記走査回路と前記データ信号回路とは、前記表示領域の外周に沿って配置され、更に、隣接する請求項1に記載の表示装置。

**【請求項4】**

前記複数の走査回路は、前記表示領域の外周の辺から略等距離に配置され、

前記データ信号回路は、前記表示領域の外周の辺から略等距離に配置される請求項1に記載の表示装置。

**【請求項5】**

前記複数の走査回路の各々は、前記第1信号がゲートに入力される薄膜トランジスタを備え、

前記薄膜トランジスタの半導体層のチャネル領域において電流が流れる方向と前記第1配線部の延伸方向とが略平行である請求項2に記載の表示装置。

**【請求項6】**

前記複数のデータ信号回路の各々は、前記第2信号がゲートに入力される薄膜トランジスタを備え、

前記薄膜トランジスタの半導体層のチャネル領域において電流が流れる方向と前記第2配線部の延伸方向とが略平行である請求項2に記載の表示装置。

**【請求項7】**

前記画素は、有機発光層を含む発光部と、容量と前記容量の電圧に応じた電流を前記発光部に流す駆動トランジスタとを含む画素回路とを備え、

前記画素回路は基板面に層状に形成され、前記発光部は、前記画素回路が形成された層の上側に形成され、

層状に形成された前記画素回路において、前記駆動トランジスタに含まれるソースとドレインの少なくとも1つに接続する配線が形成される配線層に前記第1配線部と前記第2配線部とが形成され、前記容量の金属電極が形成される層に前記第1補助配線部と前記第2補助配線部とが形成される請求項1に記載の表示装置。

**【請求項8】**

前記画素は、有機発光層を含む発光部と、容量と前記容量の電圧に応じた電流を前記発光部に流す駆動トランジスタとを含む画素回路とを備え、

前記画素回路は基板面に層状に形成され、前記発光部は、前記画素回路が形成された層の上側に形成され、

層状に形成された前記画素回路において、前記駆動トランジスタに含まれるソースとドレインの少なくとも1つに接続する配線が形成される配線層に前記第1配線部と前記第2配線部とが形成され、前記容量の第1金属電極が形成される層又は前記容量の第2金属電極が形成される層に前記第1補助配線部と前記第2補助配線部とが形成される請求項1に記載の表示装置。

**【請求項9】**

前記画素回路の駆動トランジスタは、前記電流を前記画素回路の直上に配置された前記発光部に流す請求項7又は8に記載の表示装置。

**【請求項10】**

前記データ線は、前記第2方向に沿って配置され、

10

20

30

40

50

さらに、前記データ線の一端側に配置された、前記走査回路とデータ信号回路とを制御する制御回路に接続する接続配線部を備え、

前記第1領域は、前記接続配線部側の第3領域と前記第3領域と異なる第4領域とを含み、

前記第3領域に配置された走査回路の幅は、前記第4領域に配置された走査回路の幅に比べて短い請求項7又は8に記載の表示装置。

【請求項11】

前記データ線は、前記第2方向に沿って配置され、

さらに、前記データ線の一端側に、前記走査回路とデータ信号回路とを制御する制御回路と接続する接続配線部を備え、

前記画素回路の駆動トランジスタは、前記電流を、前記画素回路の直上に配置された発光部を基準にして前記データ線の一端側に向けて1画素分ずれた位置に配置された発光部に流す請求項7又は8に記載の表示装置。

【請求項12】

前記表示領域において最も外側に配置されている画素の配置領域と、前記走査回路又は前記データ信号回路の配置領域との間の領域に、金属層が配置された請求項1に記載の表示装置。

【請求項13】

非矩形状の表示領域内に、第1方向と第2方向とに沿って配列された複数の画素と、

前記第1方向に沿う第1画素群に、走査線を介して、走査信号を出力する走査回路を含む走査回路ブロックと、

前記第2方向に沿う第2画素群に、データ線を介して、走査信号が入力される画素の発光輝度に応じたデータ信号を出力するデータ信号回路を含むデータ信号回路ブロックと、

前記走査回路を制御する第1信号が供給される第1配線部と、

前記データ信号回路を制御する第2信号が供給される第2配線部と、

前記第1配線部と前記走査回路とを接続する第1補助配線部と、

前記第2配線部と前記データ信号回路とを接続する第2補助配線部とを備え、

前記走査回路ブロックは、前記第1配線部及び前記第1補助配線部並びに前記第2配線部を含み、

前記データ信号回路ブロックは、前記第2配線部及び前記第2補助配線部並びに前記第1配線部を含み、

前記データ信号回路は、前記表示領域の外周における第1領域に円弧状に配置され、

前記第2配線部は、前記第1領域の外周における第2領域に円弧状に配置され、

前記第2補助配線部は、前記第2配線部の延伸方向と略直交する方向に沿って配置され、

円弧状に配置された複数の前記データ信号回路の各々の配置角度は、前記第1方向又は前記第2方向に対して異なる、表示装置。

【請求項14】

前記データ信号回路は、所定の本数のデータ線を介して、前記第2画素群に前記データ信号を出力し、

更に、前記所定の本数のデータ線と、前記所定の本数のデータ線に前記データ信号を出力する前記データ信号回路とを接続する所定の本数の出力配線を備え、

前記所定の本数の出力配線の各々は、前記所定の本数のデータ線の各々と一対一で接続する、請求項13に記載の表示装置。

【請求項15】

前記所定の本数の出力配線は、前記所定の本数のデータ線と前記データ信号回路とを最短距離で接続する、請求項14に記載の表示装置。

【請求項16】

第1の出力配線の前記第1方向に対する傾き角と、第2の出力配線の前記第1方向に対する傾き角とが異なる、請求項15に記載の表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示は、表示装置に関する。

**【背景技術】****【0002】**

近年、表示領域が円形といった非矩形の表示装置が製品化されている（特許文献1）。表示領域が非矩形の表示装置では、デマルチプレクサ（DEMUX）を使用した部分ドライバ内蔵型が主流となっている。部分ドライバ内蔵型では、DEMUX回路と走査ドライバ回路とを、表示装置を構成する表示パネルの外周部に配置する。

10

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】特開2008-292995号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

表示領域が非矩形の表示装置では、DEMUX回路と走査ドライバ回路とが外周部の一部領域に集中する場合がある。なお、この一部領域は、表示領域の外周部において、ドライバICが配置される側の領域である。その結果、かかる領域に対応する額縁が広くなる。一方、額縁を狭くして表示領域を相対的に広くすることが好ましい。

20

本開示の一側面は、表示領域が非矩形状の表示装置において、額縁を狭くすることを目的とする。

**【課題を解決するための手段】****【0005】**

本開示の一側面の表示装置は、非矩形状の表示領域内に、第1方向と第2方向とに沿って配列された複数の画素と、前記第1方向に沿う第1画素群に、走査線を介して、走査信号を出力する走査回路と、前記第2方向に沿う第2画素群に、データ線を介して、前記走査信号が入力される画素の発光輝度に応じたデータ信号を出力するデータ信号回路と、前記走査回路を制御する第1信号が供給される第1配線部と、前記データ信号回路を制御する第2信号が供給される第2配線部と、前記第1配線部と前記走査回路とを接続する第1補助配線部と、前記第2配線部と前記データ信号回路とを接続する第2補助配線部とを備え、前記走査回路と前記データ信号回路とは、前記表示領域の外周における第1領域に配置され、前記第1配線部と前記第2配線部とは、前記第1領域の外周における第2領域に配置され、前記第1補助配線部は、前記第1配線部の延伸方向と略直交する方向に沿って配置され、前記第2補助配線部は、前記第2配線部の延伸方向と略直交する方向に沿って配置される。

30

**【発明の効果】****【0006】**

本開示の一側面によれば、表示領域が非矩形の表示装置において、額縁を狭くすることが可能となる。

40

**【図面の簡単な説明】****【0007】**

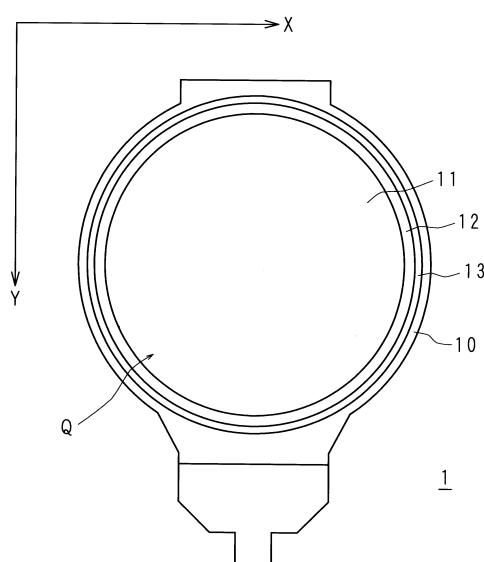

【図1】表示装置の外観を示す平面図である。

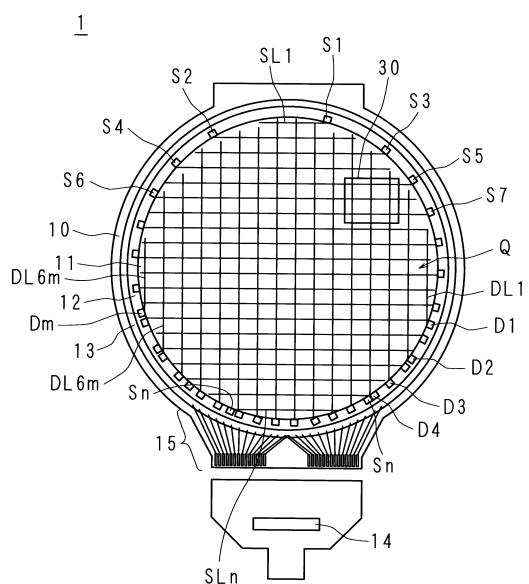

【図2】表示装置の構成を示す平面図である。

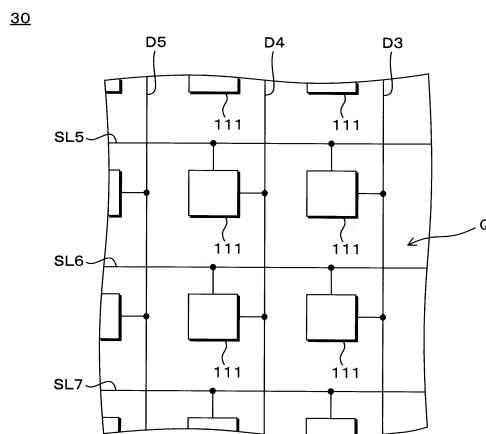

【図3】表示装置の構成を示す部分拡大図である。

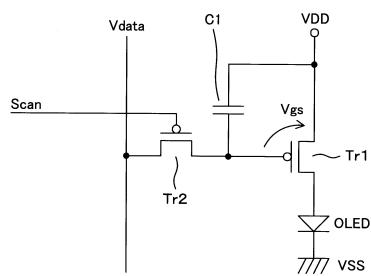

【図4】画素に含まれる画素回路の一例を示す回路図である。

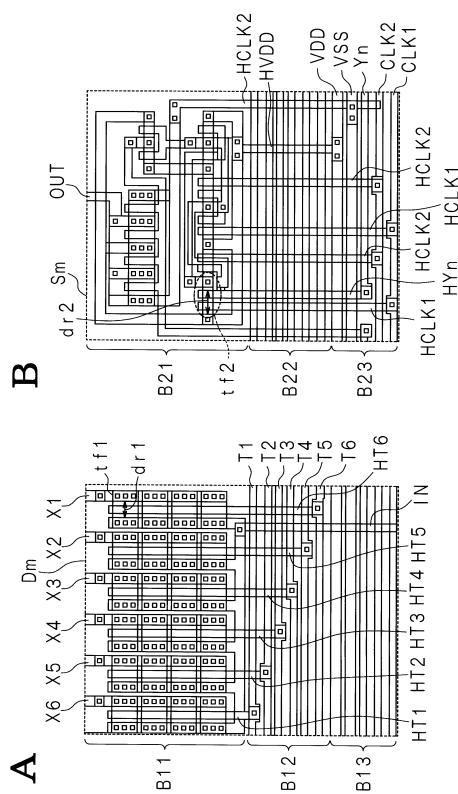

【図5】データドライバブロック、走査線ドライバブロックの構成例を示すブロック図である。

【図6】データドライバブロック、走査線ドライバブロックの構成例を示す平面図である

50

。

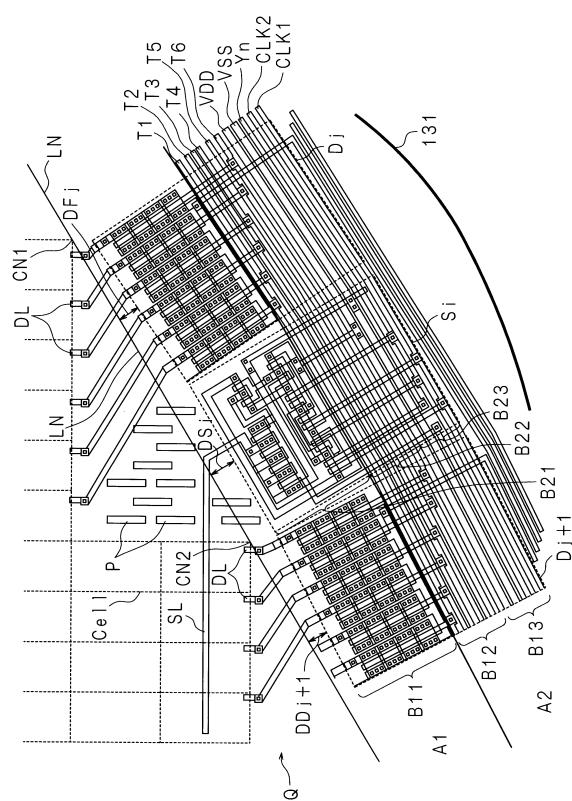

【図7】データドライバブロック、走査ドライバブロックの配置例を示す平面図である。

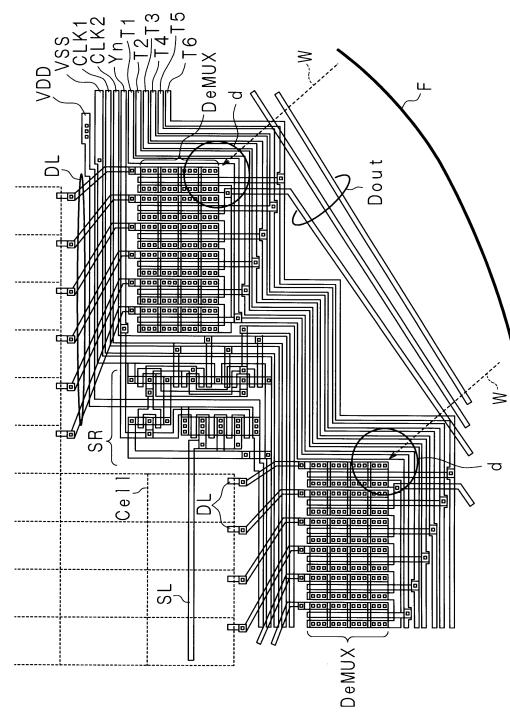

【図8】関連技術における走査ドライバブロック、データドライバブロックの配置例を示す平面図である。

【図9】表示部の断面図の一例である。

【図10】表示部の断面図の一例である。

【図11】データドライバブロックの構成例を示す平面図である。

【図12】データドライバブロック、走査線ドライバブロックの配置例を示す平面図である。

【図13】図12の部分拡大図である。

10

【図14】表示装置の構成を示す平面図である。

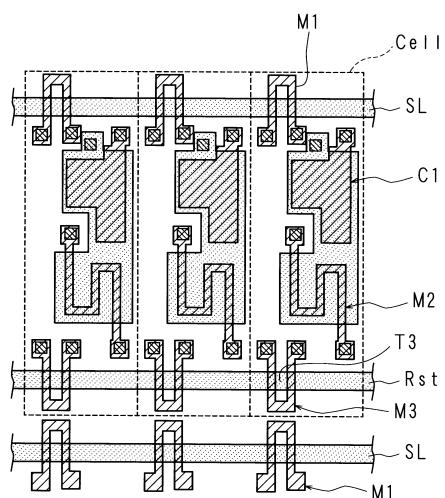

【図15】画素回路の構成例を示す平面図である。

【図16】レイヤのパターン例を示す平面図である。

【図17】レイヤのパターン例を示す平面図である。

【図18】レイヤのパターン例を示す平面図である。

【図19】レイヤのパターン例を示す平面図である。

【図20】画素に含まれる画素回路の他の例を示す回路図である。

【発明を実施するための形態】

【0008】

(実施の形態1)

20

以下、実施の形態について図面を参照して詳細に説明する。なお、明細書、特許請求の範囲における“第1”、“第2”等の序数は、要素間の関係を明確にするため、および要素間の混同を防ぐために付している。したがって、これらの序数は、要素を数的に限定しているものではない。

【0009】

また、非矩形は、矩形(四角形)以外の形状を示す。非矩形には、三角形、五角形以上の多角形を含む。非矩形には、円形、橢円形、星形、ハート形、くさび形を含む。

【0010】

さらにまた、以下の説明において、2つの方向が略直角とは、2つの方向を示す2つのベクトルのなす角が、例えば60度から120度となることを言う。2つの方向が略平行とは、2つの方向を示す2つのベクトルのなす角が、0度から30度となることを言う。

30

【0011】

以下の説明においては、表示領域が非矩形の一例として、表示領域が円形の表示装置について説明する。特に、発光素子として、OLED(Organic Light Emitter Diode、有機発光ダイオード)を用いるOLED表示装置について説明する。

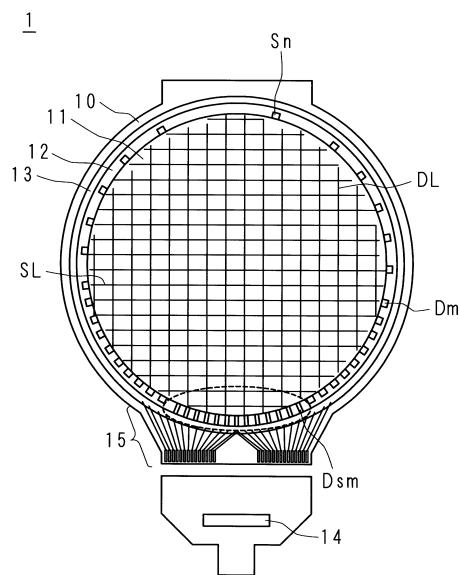

【0012】

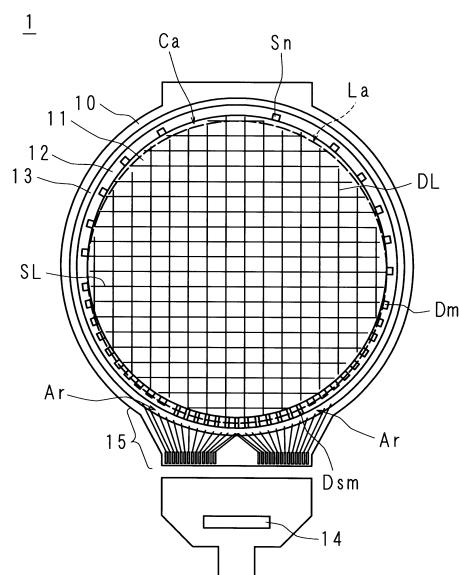

図1は表示装置1の外観を示す平面図である。表示装置1は基板10、表示部11、ドライバIC14を含む。基板10はガラス基板等の透光性基板である。表示部11は基板10上に形成してある。表示部11の外周縁部には、TFT(Thin Film Transistor)回路配置領域12が設けてある。TFT回路配置領域12の外周縁部には、ガラスフリットシール部13が設けてある。

40

【0013】

以下の説明においては、表示装置1における2つの方向を定義する。図1に示すように、表示部11の表示領域と平行な平面において、直行する2つの軸を定義する。2つの軸をx軸とy軸とする。x軸方向を第1方向とする。y軸方向を第2方向とする。

【0014】

図2は表示装置1の構成を示す平面図である。図3は表示装置1の構成を示す部分拡大図である。図3は図2の領域30を拡大したものである。表示装置1は第1方向に沿った走査線と第2方向に沿ったデータ線とを含む。走査線は、走査線SL1からSLnのn本

50

配置されている。データ線は、データ線 D L 1 からデータ線 D L 6 m の 6 m 本配置してある。

【 0 0 1 5 】

表示装置 1 は n 個の走査ドライバブロック S 1 から S n を含む。走査ドライバブロック S 1 から S n は、TFT 回路配置領域 1 2 に配置してある。走査ドライバブロック S 1 から S n それぞれは、走査線 S L 1 から S L n それぞれに走査信号を供給する。以下の説明において、走査ドライバブロック S 1 から S n の共通の機能、動作を説明する場合、走査ドライバブロック S n すべての走査ドライバブロック S 1 から S n を代表させる。

【 0 0 1 6 】

表示装置 1 は m 個のデータドライバブロック D 1 から D m を含む。データドライバブロック D 1 から D m は、TFT 回路配置領域 1 2 に配置してある。データドライバブロック D 1 から D m それぞれは、1 対 6 のデマルチプレクサを含む。データドライバブロック D 1 は、データ線 D L 1 から D L 6 にデータ信号を分配する。データドライバブロック D m は、データ線 D L m - 6 からデータ線 D L m にデータ信号を分配する。以下の説明において、データドライバブロック D 1 から D m の共通の機能、動作を説明する場合、データドライバブロック D m すべてのデータドライバブロック D 1 から D m を代表させる。

10

【 0 0 1 7 】

表示装置 1 は、走査ドライバブロック S 1 から S n 、データドライバブロック D 1 から D m を制御するドライバ I C 1 4 を含む。ドライバ I C 1 4 からの制御信号は、接続配線部 1 5 に含まれる配線により、走査ドライバブロック S 1 から S n 、データドライバブロック D 1 から D m へ伝達される。

20

【 0 0 1 8 】

図 3 に示すように、データ線 2 本と走査線 2 本に囲まれた領域には、画素 1 1 1 が形成してある。各画素 1 1 1 には、データ線、走査線がそれぞれ 1 本接続してある。複数の画素 1 1 1 は行列上に配置してある。画素 1 1 1 の行方向の配置数は、最大 6 m 個 ( m は 2 以上の整数 ) である。画素 1 1 1 の列方向の配置数は、最大 n 個 ( n は 2 以上の整数 ) である。上述の第 1 方向は行方向である。上述の第 2 方向は列方向である。表示装置 1 は、非矩形状の表示領域 Q 内に、第 1 方向と第 2 方向とに沿って配列された複数の画素を備える。

【 0 0 1 9 】

30

表示装置 1 は、第 1 方向に沿う第 1 画素群に、走査線を介して、走査信号を出力する走査回路を備える。第 1 画素群の例は、行方向に配置してある複数の画素 1 1 1 である。走査回路の一例は、走査ドライバブロック S 1 から S n である。表示装置 1 は、第 2 方向に沿う第 2 画素群に、データ線を介して、前記走査信号が入力される画素の発光輝度に応じたデータ信号を出力するデータ信号回路を備える。第 2 画素群の例は、列方向に配置してある複数の画素 1 1 1 である。データ信号回路の一例は、データドライバブロック D 1 から D m である。

【 0 0 2 0 】

図 4 は画素 1 1 1 に含まれる画素回路の一例を示す回路図である。画素回路は、O L E D 、駆動トランジスタ T r 1 、スイッチトランジスタ T r 2 、保持容量 C 1 を含む。画素回路には、正電源 V D D 、負電源 V S S 、映像信号 V d a t a および走査信号 S c a n が入力される。映像信号 V d a t a は、データドライバブロック D M 1 から D M m のそれから対応する画素回路に出力される。走査信号 S c a n は、走査ドライバブロック S 1 から S 2 n のそれから対応する画素回路へ出力される。映像信号 V d a t a は、スイッチトランジスタ T r 2 のソース電極に入力される。走査信号 S c a n は、スイッチトランジスタ T r 2 のゲート電極に入力される。正電源 V D D は保持容量 C 1 の第 1 の電極および駆動トランジスタ T r 1 のソース電極に接続されている。負電源 V S S は、O L E D のカソード電極に接続されている。スイッチトランジスタ T r 2 のドレイン電極は、保持容量 C 1 の第 2 の電極および駆動トランジスタ T r 1 のゲート電極に接続されている。駆動トランジスタ T r 1 のドレイン電極は、O L E D のアノード電極に接続されている

40

50

## 【0021】

各画素回路に対して、走査信号  $S_{can}$  および映像信号  $V_{data}$  の電圧が印加される。走査線が走査ドライバブロック  $S_1$  から  $S_2$  にのいずれかにより選択されている場合、すなわち走査信号  $S_{can}$  が ON である場合には、スイッチトランジスタ  $T_{r2}$  が ON になり、スイッチトランジスタ  $T_{r2}$  のドレイン電極から映像信号  $V_{data}$  に応じた電圧が出力される。

## 【0022】

スイッチトランジスタ  $T_{r2}$  のドレイン電極の出力電圧と正電源  $V_{DD}$  との間の電位差  $V_{gs}$  に応じた電流を、駆動トランジスタ  $T_{r1}$  は  $LED$  に供給する。その結果、 $LED$  は電流に比例した輝度で発光する。走査信号  $S_{can}$  が OFF になった後は、保持容量  $C$  に蓄積された電荷により駆動トランジスタ  $T_{r1}$  の電位差  $V_{gs}$  が維持され、 $LED$  は発光を継続する。10

## 【0023】

データドライバブロック  $D_m$  は、1対6のデマルチプレクサを含むから、データ線6本に対して、1つのデータドライバブロック  $D_m$  を配置する。そして、走査線1本に対して、1つの走査ドライバブロック  $S_n$  を配置する。以下、図5～図7を参照して、額縁を狭くする技術的手段について詳細に説明する。なお、額縁を狭くすることを狭額縁化と記す。10

## 【0024】

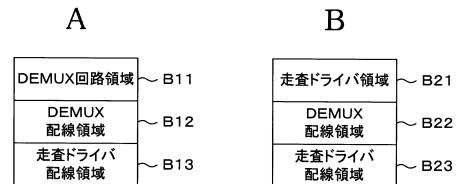

図5はデータドライバブロック  $D_m$ 、走査ドライバブロック  $S_n$  の構成例を示すブロック図である。図5Aはデータドライバブロック  $D_m$  の構成を示している。データドライバブロック  $D_m$  は、3つの領域を有する。3つの領域は、 $DEMUX$ 回路領域  $B_{11}$ 、 $DEMUX$ 配線領域  $B_{12}$ 、走査ドライバ配線領域  $B_{13}$  である。 $DEMUX$ 回路領域  $B_{11}$  にはデマルチプレクサの回路を構成する。 $DEMUX$ 配線領域  $B_{12}$  は、データドライバブロック  $D_m$  の制御信号の配線を配置する領域である。走査ドライバ配線領域  $B_{13}$  は、走査ドライバブロック  $S_n$  の制御信号の配線を配置する領域である。走査ドライバ配線領域  $B_{13}$  に配置する配線は、走査ドライバブロック  $S_n$  の制御信号、電源の配線である。これらの信号は、 $DEMUX$ の動作には影響しない。20

## 【0025】

図5Bは走査ドライバブロック  $S_n$  の構成を示している。走査ドライバブロック  $S_n$  は、3つの領域からなる。3つの領域は、走査ドライバ領域  $B_{21}$ 、 $DEMUX$ 配線領域  $B_{22}$ 、走査ドライバ配線領域  $B_{23}$  である。走査ドライバ領域  $B_{21}$  には走査ドライバの回路を構成する。 $DEMUX$ 配線領域  $B_{22}$  はデマルチプレクサの制御信号の配線を配置する領域である。この領域の配線は、データドライバブロック  $D_m$  の制御信号の配線である。走査ドライバ配線領域  $B_{23}$  は走査ドライバブロック  $S_n$  の制御信号の配線を配置する領域である。30

## 【0026】

走査ドライバブロック  $S_n$  に隣接して、データドライバブロック  $D_m$  を配置した場合であっても、走査ドライバブロック  $S_n$  を迂回して、データドライバブロック  $D_m$  への制御信号配線を配置する必要はない。走査ドライバブロック  $S_n$  の  $DEMUX$ 配線領域  $B_{22}$  を用いれば良いからである。同様に、データドライバブロック  $D_m$  に隣接して、走査ドライバブロック  $S_n$  を配置した場合であっても、データドライバブロック  $D_m$  を迂回して、走査ドライバブロック  $S_n$  への制御信号配線を配置する必要はない。データドライバブロック  $D_m$  の走査ドライバ配線領域  $B_{13}$  を用いれば良いからである。40

## 【0027】

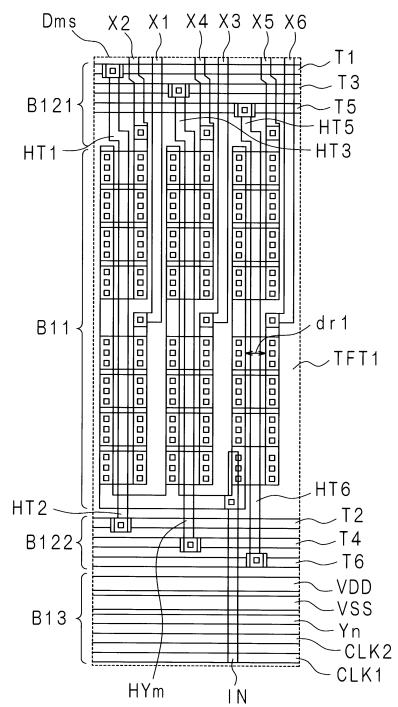

走査ドライバブロック  $S_n$ 、データドライバブロック  $D_m$  の構成例を説明する。図6はデータドライバブロック  $D_m$ 、走査ドライバブロック  $S_n$  の構成例を示す平面図である。図6Aはデータドライバブロック  $D_m$  の構成例を示す。データドライバブロック  $D_m$  は図5Aに示したような構成となっている。データドライバブロック  $D_m$  の  $DEMUX$ 回路領域  $B_{11}$  には、1対6のデマルチプレクサを構成してある。デマルチプレクサの出力配線50

は、X 1 から X 6 である。デマルチプレクサは複数の TFT を含むが、この複数の TFT の中の 1 つの TFT を例えば TFT\_tf1 として示している。入力配線 IN は、例えばドライバ I C 1 4 ( 図 2 参照 ) に接続し、ドライバ I C 1 4 が入力配線 IN にデータ信号を出力する。なお、データ信号は、走査信号が入力される画素の発光輝度に応じた信号である。入力配線 IN は、DEMUX 配線領域 B 1 2 、走査ドライバ配線領域 B 1 3 を縦断する。DEMUX 配線領域 B 1 2 には、デマルチプレクサの制御信号 ( 選択信号 ) の配線が配置してある。DEMUX 配線領域 B 1 2 には、出力配線 X 1 から X 6 に対応して、制御信号配線 T 1 から T 6 が配置されている。制御信号配線 T 1 から T 6 それぞれは、対応する TFT 1 それぞれのゲートに接続する。DEMUX 配線領域 B 1 2 は、制御信号配線 T 1 から T 6 と対応する TFT 1 のゲートへの補助配線 HT 1 から HT 6 を含む。補助配線 HT 1 から HT 6 は、制御信号配線 T 1 から T 6 の延伸方向と略直交する方向に沿って配されている。TFT 1 のチャネル層を流れる電流の向き dr1 は、制御信号配線 T 1 から T 6 の延伸方向と略平行である。走査ドライバ配線領域 B 1 3 には、後述する VDD 、 VSS 、 Yn 、 CLK1 、 CLK2 の配線が配置してある。走査ドライバ配線領域 B 1 3 は、デマルチプレクサと電気的に接続されている配線はない。

#### 【 0028 】

図 6 B は走査ドライバブロック Sn の構成例を示す。走査ドライバブロック Sn は、図 5 B に示したような構成となっている。走査ドライバ領域 B 2 1 には、走査ドライバに含まれるシフトレジスタ等が構成してある。走査ドライバはスイッチトランジスタ TFT2 を含む。走査ドライバ領域 B 2 1 には、走査線へ走査信号を出力する出力配線 OUT が設けてある。出力配線 OUT は走査線と接続されている。走査ドライバ配線領域 B 2 3 には、走査ドライバへの電源線、信号線等を含む制御信号配線が配置してある。VDD 、 VSS は電源である。Yn は入力信号である。CLK1 、 CLK2 はクロック信号である。走査ドライバ配線領域 B 2 3 には、制御信号配線と走査ドライバを結ぶ補助配線 HVDD 、 HVSS 、 HYn 、 HCLK1 、 HCLK2 が配置してある。これらの補助配線は、制御信号配線の延伸方向と略直交する方向に沿って配されている。走査ドライバブロック Sn は、複数の TFT を含むが、この複数の TFT の中の 1 つの TFT を例えば TFT\_tf2 として示している。TFT\_tf2 のチャネル層を流れる電流の向き dr2 は、制御信号配線 VDD 、 VSS 等の延伸方向と略平行である。DEMUX 配線領域 B 2 2 には、前述した制御信号配線 T 1 から T 6 が配置されている。DEMUX 配線領域 B 2 2 は、走査ドライバと電気的に接続されている配線はない。

#### 【 0029 】

データドライバブロック Dm において、DEMUX 配線領域 B 1 2 と走査ドライバ配線領域 B 1 3 との配置は逆でも良い。この場合、走査ドライバブロック Sn において、DEMUX 配線領域 B 2 2 と走査ドライバ配線領域 B 2 3 との配置も逆にする。

#### 【 0030 】

図 7 は、データドライバブロック、走査ドライバブロックの配置例を示す平面図である。図 7 には、2 つのデータドライバブロック Dj 、 Dj + 1 、1 つの走査ドライバブロック Si が示されている。データドライバブロック Dj 、 Dj + 1 、走査ドライバブロック Si は表示領域の外周に配置してある。データドライバブロック Dj 、 Dj + 1 、走査ドライバブロック Si のそれぞれと、表示領域 Q の外周線 LN との距離をそれぞれ DDj 、 DDj + 1 、 DSi とする。DDj 、 DDj + 1 、 DSi は、略同じ値である。すなわち、データドライバブロック Dj 、 Dj + 1 、走査ドライバブロック Si それぞれは、表示領域 Q から略等距離に配置してある。データドライバブロック Dj 、 Dj + 1 の DEMUX 回路領域 B 1 1 は、表示領域の外周における第 1 領域 A 1 に配置してある。データドライバブロック Dj 、 Dj + 1 の DEMUX 配線領域 B 1 2 、走査ドライバ配線領域 B 1 3 は、第 1 領域 A 1 の外周における第 2 領域 A 2 に配置してある。走査ドライバブロック Si の走査ドライバ領域 B 2 1 は、表示領域の外周における第 1 領域 A 1 に配置してある。走査ドライバブロック Si の DEMUX 配線領域 B 2 2 、走査ドライバ配線領域 B 2 3 は、第 1 領域 A 1 の外周における第 2 領域 A 2 に配置してある。

10

20

30

40

50

## 【0031】

以上の説明をまとまる以下とおりである。表示装置1は、走査回路を制御する第1信号が供給される第1配線部を備える。第1配線部の一例は、走査ドライバブロックS<sub>n</sub>のVDD、VSSなどの制御信号配線である。表示装置1は、データ信号回路を制御する第2信号が供給される第2配線部を備える。第2配線部の一例は、データドライバブロックD<sub>m</sub>の制御信号配線T<sub>1</sub>からT<sub>6</sub>である。表示装置1は、第1配線部と走査回路とを接続する第1補助配線部を備える。第1補助配線部の例は、補助配線H<sub>VDD</sub>、H<sub>VSS</sub>、H<sub>YN</sub>、H<sub>CLK1</sub>、H<sub>CLK2</sub>である。表示装置1は、第2配線部とデータ信号回路とを接続する第2補助配線部を備える。第2補助配線部の一例は、補助配線H<sub>T1</sub>からH<sub>T6</sub>である。

10

## 【0032】

第1配線部の一例である走査ドライバブロックS<sub>n</sub>のY<sub>n</sub>、CLK1、CLK2などの制御信号配線は、表示領域の外周に沿って配置してある。第2配線部の一例であるデータドライバブロックD<sub>m</sub>の制御信号配線T<sub>1</sub>からT<sub>6</sub>は、表示領域の外周に沿って配置してある。

## 【0033】

第1配線部の一例である走査ドライバブロックS<sub>n</sub>のY<sub>n</sub>、CLK1、CLK2などの制御信号配線は、表示領域に遠い領域に配置してある。それに対して、第2配線部の一例であるデータドライバブロックD<sub>m</sub>の制御信号配線T<sub>1</sub>からT<sub>6</sub>は、表示領域に近い領域に配置してある。第1配線部と第2配線部の配置は逆でも良い。第1配線部を表示領域に近い領域に配置し、第2配線部を表示領域に遠い領域に配置する。

20

## 【0034】

表示装置1の表示領域の外周近傍において、階段上に配置されている、外側の第1画素の角と、階段上に配置されている、外側の第2画素の角とを結ぶ線と、第1配線部の延伸方向と第2配線部の延伸方向とが略平行である。第1画素の角の一例は、図7に示す角CN1である。第2画素の角の一例は、図7に示す角CN2である。第1画素の角と第2画素の角とを結ぶ線の一例は、図7に示す表示領域の外周線LNである。

## 【0035】

図7に示すCell1は画素セルである。SLは走査線である。DLはデータ線である。PはESD対策ダミーパターンである。131はガラスフリットシールの印刷中心を示す。図7に示すように、1つの走査ドライバブロックSiに隣接して、データドライバブロックDj、Dj+1が配置してある。3つのドライバブロックが備える走査ドライバ配線領域B13(B23)、DEMUX配線領域B12(B22)により、隣接するドライバブロックへの配線が整然と配置可能となっている。

30

## 【0036】

図8は関連技術における走査ドライバブロック、データドライバブロックの配置例を示す平面図である。図8には、1つの走査ドライバブロックSRと、2つのデータドライバブロックDEMUX、DEMUXが示されている。なお、図8において、1つの走査ドライバブロックSR、2つのデータドライバブロックDEMUX、DEMUXを制御するドライバIC14については図示していないが、図2と同様に、ドライバICは図8の下側に配置されている。

40

データドライバブロックDEMUXが、ドライバICが配置される側(下側)に配置されている理由を説明する。データ線は、表示領域内において、一般的に縦方向(図8では図面上下方向)に延伸しており、縦方向に延伸するデータ線の一端側にデータドライバブロックDEMUXが配置される。また、配線が長くなることによる信号遅延を抑制するため、ドライバICとデータドライバブロックDEMUXとを接続する配線の距離をなるべく短くすることが好ましい。このような理由から、データドライバブロックDEMUXは、ドライバICが配置される側(下側)に配置される。

図8では、データドライバブロックDEMUX、走査ドライバブロックSRが、下側に配置されている一例を示している。

50

ドライバ I C が配置される側（下側）にデータドライバブロックを配置すると、データドライバブロック、走査ドライバブロックが集中配置され、さらに、配線も密集する。このように、ドライバの配置を工夫せずに単にドライバを集中配置すると、ドライバの専有面積が大きくなり額縁が広くなる。そこで、本実施の形態では、ドライバ配置を工夫して狭額縁化を実現する。

さらに、レーザー照射によりガラスフリットを溶解しその後冷却硬化して O L E D を封止する場合、レーザー照射領域とドライバの配置領域との距離（いわゆるマージン）を十分に確保する必要がある。図 8 の例では、データドライバブロック D E M u X において、符号 d で示す円で囲った部分は、ガラスフリットシール部の印刷中心 F との距離が最も小さい部分である。この部分と印刷中心 F とのマージン W を十分に取らないと、ガラスフリットレーザ照射時に、この部分がダメージを受ける可能性がある。また、ドライバ I C の出力信号をデータドライバブロック D E M u X に伝達する配線 D o u t も、印刷中心 F に近い。そのため、配線 D o u t と印刷中心 F とのマージンを確保する必要がある。このマージンを確保する必要性から、印刷中心 F と表示領域までの距離が長くなる。この距離が長くなると、額縁が広くなる。

関連技術に対して、本実施の形態では、回路配置、配線配置を工夫して、狭額縁化できるように走査ドライバブロック、データドライバブロックを最適配置（最密充填とも呼ぶ）する。最密充填するためには、例えば、走査ドライバブロック、データドライバブロックが配置されている領域を、T F T 配置領域と、配線領域とに分割する。この配線領域は、走査ドライバブロックの配線群の配置領域、データドライバブロックの配線群の配置領域とを共通して含む共通領域である。

さらに、表示領域の外周の接線方向と、ドライバブロックの横方向とが、略平行になるようにすることが好ましい。具体的には、表示領域の外周の接線方向と、配線領域に配置された配線の延伸方向とが、略平行になるようにすることが好ましい。さらに、表示領域の外周の接線方向と、T F T 配置領域に配置された半導体のチャネル領域において電流が流れる方向（図 6 の方向 d r 1、d r 2 参照）とが略平行になるようにすることが好ましい。なお、回路構成によっては、表示領域の外周の接線方向と、この電流が流れる方向と直角な方向とが略平行になるようにしてもよい。

または、ドライバブロックの横方向と表示領域の外周近傍において、階段上に配置されている、外側の第 1 画素の角と、階段上に配置されている、外側の第 2 画素の角とを結ぶ線（例えば、図 7 で示す L N ）とが、略平行になるようにすることが好ましい。具体的には、線 L N と、配線領域に配置された配線の延伸方向とが、略平行になるようにすることが好ましい。さらに、線 L N と、T F T 配置領域に配置された半導体のチャネル領域において電流が流れる方向（図 6 の方向 d r 1、d r 2 参照）とが略平行になるようにすることが好ましい。なお、回路構成によっては、線 L N と、この電流が流れる方向と直角な方向とが略平行になるようにしてもよい。

さらに、ガラスフリット部のシール印刷部に近い領域に、配線を配置する。このような配線の配置により、T F T 配置領域とレーザー照射領域との間の距離を十分に確保しつつ、ガラスフリットシールの印刷中心を表示領域側に近づけて額縁を狭くすることができる。配線の金属に高融点金属を使用すれば、レーザーが配線に照射されても配線が破壊される可能性が抑制できるので、より額縁を狭くすることができる。

### 【 0 0 3 7 】

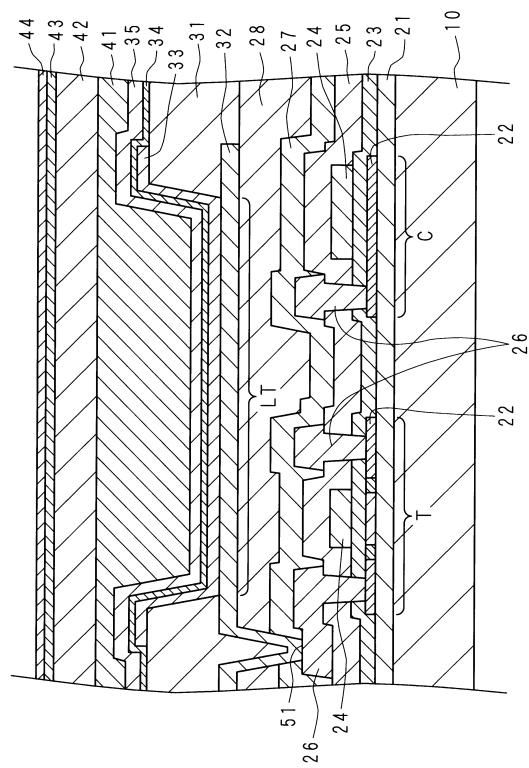

図 9 は表示部 1 1 の断面図の一例である。図 9 は、表示部 1 1 のうちの一個の O L E D 素子 L T を含む部分を、画像を表示する面に対して垂直な面で切断した断面図である。図 9 の左下部分には、トランジスタ T が形成されている。図 9 の右下部分には、保持容量 C が形成されている。トランジスタ T と保持容量 C の上には、O L E D 素子 L T が形成されている。ここで示す断面は、トランジスタ T 、保持容量 C 、O L E D 素子 L T が、どのような階層構造で形成されるかを、単に示しているものである。トランジスタ T は、例えば、O L E D 素子 L T を駆動する駆動トランジスタ T r 1 である。

### 【 0 0 3 8 】

10

20

30

40

50

基板 10 上には、下地絶縁膜 21 が積層されている。下地絶縁膜 21 上には、ポリシリコン層 22 が形成されている。ポリシリコン層 22 上には、ゲート絶縁膜 23 が形成されている。ゲート絶縁膜 23 上には、第 1 金属層 24 が積層されている。第 1 金属層 24 は、モリブデン (Mo) 等で形成する。第 1 金属層 24 上には、層間絶縁膜 25 が積層されている。層間絶縁膜 25 上には、第 2 金属層 26 が積層されている。第 2 金属層 26 は、モリブデン (Mo) 等の高融点金属で形成する。第 2 金属層 26 の一部はコンタクトホールを介して、ポリシリコン層 22 と物理的及び電気的に接続している。第 2 金属層 26 上には、パッシベーション膜 27 が形成されている。パッシベーション膜 27 は無機絶縁膜である。パッシベーション膜 27 上には、平坦化層 28 が積層されている。

【0039】

10

平坦化層 28 上には、アノード電極 32、OLED デバイス 33、カソード電極 34、キャップ層 35 が積層されている。アノード電極 32 は TFT 回路出力接続部 51 に接続されている。TFT 回路出力接続部 51 は、トランジスタ T のドレインと接続されている。平坦化層 28 及びアノード電極 32 それぞれの一部と、OLED デバイス 33 及びカソード電極 34 それぞれの一部との間には、素子分離膜 31 が形成されている。素子分離膜 31 は有機膜である。素子分離膜 31 は、矩形の孔を有する絶縁性の層である。素子分離膜 31 は、TFT 回路出力接続部 51 及びアノード電極 32 の縁を覆い、アノード電極 32 の中央部を覆わない。

【0040】

20

キャップ層 35 上には空隙 41 を間に挟んで、封止ガラス 42 が配置されている。封止ガラス 42 上には、1/4 波長位相差板 43 及び偏光板 44 が配置されている。

【0041】

OLED 素子 LT は、アノード電極 32 の素子分離膜 31 に覆われていない部分及びその上側に積層された部分の OLED デバイス 33、カソード電極 34、キャップ層 35 である。

【0042】

アノード電極 32 の中央部および素子分離膜 31 に設けられた孔の縁の上側は、OLED デバイス 33 で覆われている。OLED デバイス 33 は、電圧が印加されると第 1 色、第 2 色または第 3 色のいずれかの色で発光する有機化合物の層である。

【0043】

30

表示装置 1 は複数の画素を有する。画素は有機発光層を含む発光部と、輝度に応じた電流を発光部に流す駆動トランジスタを含む画素回路を有する。発光部の一例は、OLED 素子 LT である。駆動トランジスタの一例は、駆動トランジスタ Tr 1 である。

【0044】

OLED デバイス 33 の上側は、カソード電極 34 が設けられている。カソード電極 34 は表示部 11 に含まれる各 OLED 素子 LT を連続して覆う透明電極である。すなわち、カソード電極 34 は隣接する OLED 素子 LT の各々に共通して設けられた電極である。

【0045】

40

カソード電極 34 の上側に、キャップ層 35 が設けられている。キャップ層 35 は、カソード電極 34 と同様に各 OLED 素子 LT を連続して覆う層である。キャップ層 35 は、屈折率の高い透明な材料製の層である。

【0046】

空隙 41 には乾燥空気が封入してある。キャップ層 35、空隙 41 及び封止ガラス 42 は、OLED デバイス 33 のカソード電極 34 が湿気等により劣化する事および外力により破損する事を防ぐ保護層の役割を果たす。

【0047】

画素回路の駆動トランジスタ Tr 1 は、電流を画素回路の直上に配置された発光部に流す。

【0048】

50

図9に示す表示部11の構造は、金属層を2層含む2層メタル構造である。図9に示す2層メタル構造では、走査線SLは第1金属層24で形成する。データ線DLは、第2金属層26で形成する。

#### 【0049】

図9に示す2層メタル構造では、保持容量CはトランジスタTと同様な構造となっている。保持容量Cは所謂、MOS(Metal Oxide Semiconductor)容量である。保持容量Cの上電極とトランジスタTのゲート電極とは、同じ第1金属層24からなる。保持容量Cの下電極とトランジスタTのチャネル層とは、同じポリシリコン層22からなる。保持容量Cの下電極となるポリシリコン層22は、不純物が添加されたドープ層である。

10

#### 【0050】

図9に示す2層メタル構造では、ポリシリコン層22の形成後に、第1金属層24を形成する前に、ポリシリコン層22に不純物を添加する必要がある。第1金属層24を形成後に、不純物を添加する処理をした場合、第1金属層24が覆っているポリシリコン層22の一部には、不純物が添加されない。ポリシリコン層22において、不純物が添加できていない部分は、真性半導体となる。真性半導体は抵抗値が高い。そのため、保持容量Cは機能しない。

#### 【0051】

また、ゲート絶縁膜23は所定の厚さ以上とする。ゲート絶縁膜23を薄くすると、ゲート電極とチャネル層とが電気的に接続してしまい、トランジスタTが機能しなくなるからである。

20

#### 【0052】

本実施の形態は以下の効果を奏する。データドライバブロックDm、走査ドライバブロックSnそれぞれに、走査ドライバブロックSn用の配線領域、データドライバブロックDm用の配線領域を設けたので、TFT回路配置領域12に配線領域を確保しなくても、データドライバブロックDm、走査ドライバブロックSnを配置することができる。それにより、TFT回路配置領域12の幅を小さくすることができる。その結果、表示装置1の狭額縁が可能となる。配線領域が少なくて済むので、ESD対策用のダミーパターンを設けることが可能となる。データドライバブロックDm、走査ドライバブロックSnそれぞれを、TFT回路配置領域12に配置する際、デマルチプレクサやシフトレジスタを内側となるように配置する。それによって、ガラスフリット部のシール印刷部に近い領域には、配線が配置され、デマルチプレクサやシフトレジスタが配置されない。その結果、レーザー照射時に、デマルチプレクサやシフトレジスタが破壊されてしまうことを防ぐことが可能となる。さらにまた、配線を高融点金属で構成すれば、配線にレーザーが照射されたとしても、配線が破壊されてしまうことを防ぐことが可能となる。

30

#### 【0053】

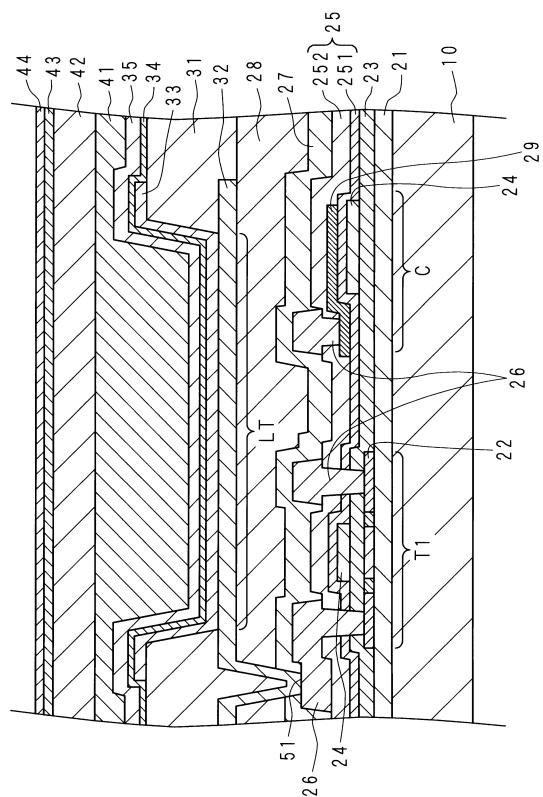

##### (実施の形態2)

実施の形態2は、表示部11を3層メタル構造で形成する形態に関する。3層メタル構造とは、金属層を3層含む構造である。図10は表示部11の断面図の一例である。実施の形態1と同様な構成については、同じ符号を付し、説明を省略する。

40

#### 【0054】

本実施の形態においては、第1金属層24上に形成される層間絶縁膜25が第1の層間絶縁膜251と第2の層間絶縁膜252との2つの層になっている。第1の層間絶縁膜251と第2の層間絶縁膜252との間には、第3金属層29が形成されている。第3金属層29は、モリブデン(Mo)等で形成する。第3金属層29の一部は、保持容量Cの下電極と対向する上電極となっている。

#### 【0055】

本実施の形態においては、走査線SL1は第1金属層24で形成する。データ線DL1からDL6mは、第2金属層26で形成する。

#### 【0056】

50

本実施の形態は、実施の形態1の奏する効果に加えて、以下の効果を奏する。保持容量Cは第1金属層24、第3金属層29、第1の層間絶縁膜251により構成される。駆動トランジスタTr1を正常の機能させるためには、層間絶縁膜25の厚さを所定以上としなくてはならない。本実施の形態では層間絶縁膜25は第1の層間絶縁膜251と第2の層間絶縁膜252とで構成している。そのため、第2の層間絶縁膜252を厚くすることで、第1の層間絶縁膜251を薄くすることが可能となる。保持容量Cはデータ信号として印加される電圧に耐えられれば良い。そのため、第1の層間絶縁膜251は必要最低限の厚さとすることが可能である。その結果、保持容量Cの単位面積あたりの容量を増やすことが可能である。その結果、保持容量Cに構成するのに必要な面積を小さくできる。よって、画素回路を構成するための必要面積が減少する。したがって、表示部11の高精細化が可能となる。

#### 【0057】

また、金属層が2層から3層に増えることにより、配線を配置する層が増える。よって、2層と同じ面積で、2層よりも複雑な回路を作成可能となる。

#### 【0058】

データ線DLは、第2金属層26で形成する。スイッチトランジスタTr2のソースドレインを第2金属層26で構成すれば、ソースドレインと接続するデータ線DLが同じ金属層となるからである。それより、配線が設計し易くなる。また、同じ層となることにより、スイッチトランジスタTr2への配線が短くなり、データの遅延時間を短くすることが可能となる。

#### 【0059】

##### (実施の形態3)

本実施の形態では、ドライバブロックの形状を縦長にして、ドライバブロックをより最密充填する表示装置について説明する。最密充填する場合、例えば、データドライバブロックや走査ドライバブロックの形状を縦長にする。換言すれば、データドライバブロックや走査ドライバブロックの形状を、周方向に対して短くし、この周方向と垂直の方向に対して長くする。このようにドライバブロックを縦長にして、周方向に沿ってより多くのドライバブロックを配置できるようにする。

図11は、実施の形態3におけるデータドライバブロックの構成例を示す平面図である。図11において、実施の形態1と同様な構成は同じ符号を付し、説明を省略する。図11に示すデータドライバブロックDsmは4つの領域からなる。4つの領域は、DEMUX回路領域B11、第1DEMUX配線領域B121、第2DEMUX配線領域B122、走査ドライバ配線領域B13である。データドライバブロックDsmでは、DEMUX回路領域B11に含まれるTFTの配置を変えている。それにより、DEMUX回路領域B11に含まれる出力配線X1からX6のピッチが小さくなっている。また、DEMUX配線領域は、第1DEMUX配線領域B121、第2DEMUX配線領域B122の2つに分割されている。本実施の形態のデータドライバブロックDsmは、実施の形態1のデータドライバブロックDmよりも縦長となっている。図示は省略するが、走査ドライバブロックについても、データドライバブロックDsmと同様に縦長構成とする。以下の説明では、縦長構成の走査ドライバブロックの符号をSSmとする。

#### 【0060】

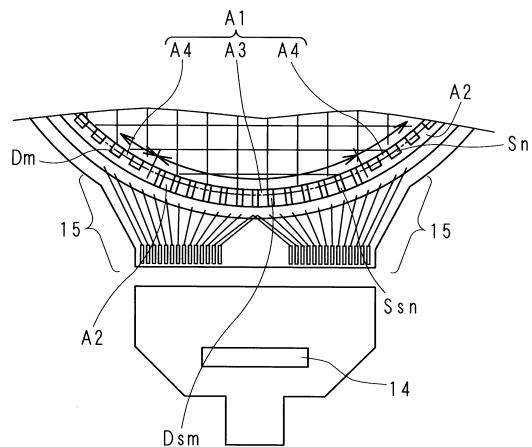

図12はデータドライバブロック、走査線ドライバブロックの配置例を示す平面図である。図13は図12の部分拡大図である。ドライバIC14に近い部分は配線領域に余裕があるが、データドライバブロックが集中する。そこで、駆動出力配線ピッチを小さくできる縦長のデータドライバブロックDsmを配置する。走査ドライバブロックについても、縦長の走査ドライバブロックSSmを配置する。それ以外の領域については、表示部11の外縁に沿うように斜め置きをする。

#### 【0061】

図13に示すように、第1領域A1を2つの領域に分ける。接続配線部15側の領域を第3領域A3とする。第3領域A3以外の領域を第4領域A4とする。この場合において

10

20

30

40

50

、第3領域には縦長のデータドライバブロック  $D_s m$  を配置する。第4領域  $A_4$  には実施の形態1と同じデータドライバブロック  $D_s$  を配置する。データドライバブロック  $D_s m$  は、データドライバブロック  $D_s$  より幅が狭い(短い)。同様に、第3領域  $A_3$  には縦長の走査ドライバブロック  $S_s n$  を配置する。第4領域  $A_4$  には実施の形態1と同じ走査ドライバブロック  $S_s n$  を配置する。走査ドライバブロック  $S_s n$  は、走査ドライバブロック  $S_n$  より幅が狭い(短い)。

#### 【0062】

データ線は、第2方向に沿って配置され、さらに、データ線の一端側に配置された、走査回路とデータ信号回路とを制御する制御回路に接続する接続配線部を備え、第1領域は、接続配線部側の第3領域と第3領域と異なる第4領域とを含み、第3領域に配置された走査回路の幅は、第4領域に配置された走査回路の幅に比べて短い。制御回路の一例はドライバIC14である。接続配線部の一例は、接続配線部15である。第1領域から第4領域の一例は、第1領域  $A_1$  から第4領域  $A_4$  である。10

#### 【0063】

以上の構成により、データドライバブロック  $D_m$  の配置ピッチに、比較的に余裕を持たせることが可能となる。すなわち、画素ピッチに対して使用できる回路ブロック出力数が増える。そのため、配線幅を減らす目的で、実施の形態1と同様なデータドライバブロック  $D_m$ 、走査ドライバブロック  $S_n$  を配置する。

#### 【0064】

本実施の形態においては、実施の形態1が奏する効果に加え、以下の効果を奏する。データドライバブロックが集中するドライバIC付近に、縦長のデータドライバブロック  $D_s m$  及び走査ドライバブロック  $S_s m$  を配置することにより、駆動出力配線ピッチを小さくできるので、配線設計が容易となる。20

#### 【0065】

##### (実施の形態4)

本実施の形態は、実施の形態3よりも更に狭額縁化を可能とする構成に関する。図14は表示装置1の構成を示す平面図である。表示部11の下側(ドライバIC接続側)には、ドライバICとドライバブロックとを接続する配線が密集している。しかし、例えば、この配線間の距離を短くして配線領域を小さくすることは最適ではない。なぜならば、配線間の距離を短くすると、配線間の寄生容量が増える可能性が高くなるからである。特に、左右の配線領域  $A_r$  が最も配線領域が大きい。左右の配線領域  $A_r$  がボトルネックとなり、狭額縁化を難しくしている。30

#### 【0066】

そこで、画素の発光エリア  $L_a$  を画素回路の配置エリア  $C_a$  より画面下方に移動する。それにより、実質的な額縁(モジュール外形部から表示領域までの距離)を減らすことが可能となる。なお、移動する距離は例えば約1画素分である。本実施の形態は、いわゆるトップエミッション構造のOLEDに適用することが好ましい。

#### 【0067】

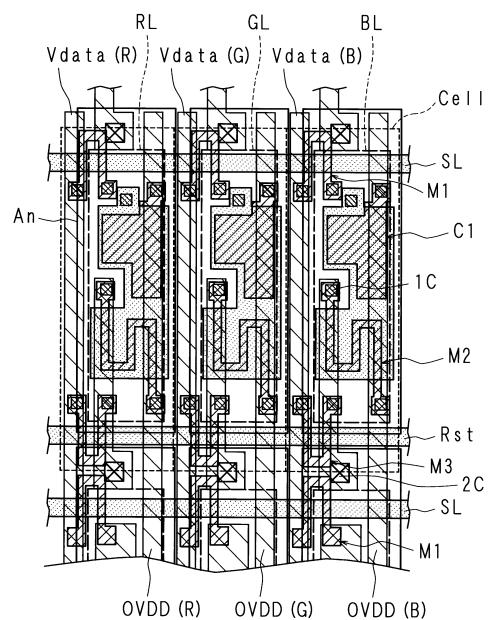

図15は画素回路の構成例を示す平面図である。図15に示す画素回路は、図9と同様に2層メタル構造としてある。細い点線が囲んだ領域  $C_{e11}$  が画素回路セル枠を表している。図15に示すのは、RGBストライプ配列の例である。一画素内に3つの画素回路が構成される。実線で囲んだ領域  $A_n$  はアノード電極の外縁を示す。アノード電極  $A_n$  内の点線  $R_L$  は、赤色の発光領域を示す。同じく点線  $G_L$  は緑色の発光領域を示す。点線  $B_L$  は青色の発光領域を示す。なお、図15に示す画素回路は、図20を用いて説明するリセットトランジスタを含む構成である。40

#### 【0068】

図15において、右側に示している青色のサブ画素を例に、画素回路についての構成を説明する。画素回路の構成要素は、紙面上方から順に以下のように配置してある。保持容量  $C_1$  が形成してある。保持容量  $C_1$  の第1電極は、右側の電源供給線  $OVDD(B)$  と接続している。なお、保持容量  $C_1$  の第2電極と、後記する駆動トランジスタ  $M_2$  のゲー50

トとは、同じ金属層を共有する。

保持容量C1の紙面下側には、駆動トランジスタM2が配置してある。保持容量C1と駆動トランジスタM2との間には、コンタクトホール1Cが配置してある。コンタクトホール1Cを介して、駆動トランジスタM2のドレインと、リセットトランジスタM3のソース又はドレインのいずれかとが電気的に接続する。

駆動トランジスタM2の紙面下側には負電圧印加用のリセットトランジスタM3が配置してある。リセットトランジスタM3は、リセット線Rstによりオンオフする。さらに保持容量C1の紙面上側にはスイッチトランジスタM1が配置してある。スイッチトランジスタM1は走査線SLにより、オンオフする。リセット線Rstと走査線SLとの間には、コンタクトホール2Cが設けてある。コンタクトホール2Cを介して、駆動トランジスタM2のドレインとOLEDのアノード電極(図15参照)とが電気的に接続する。このアノード電極は、領域Cell1内に配置されている画素回路の紙面下側に配置されているOLED素子のアノード電極である。

以上のように、図15の紙面上において、リセット線Rstの上側に配置されている画素回路(領域Cell1内に配置)が、リセット線Rstの下側に配置されているOLED素子の発光を制御する。すなわち、OLED素子の発光部は、画素回路セル枠に対して略一画素分、下側にずれて配置してある。

#### 【0069】

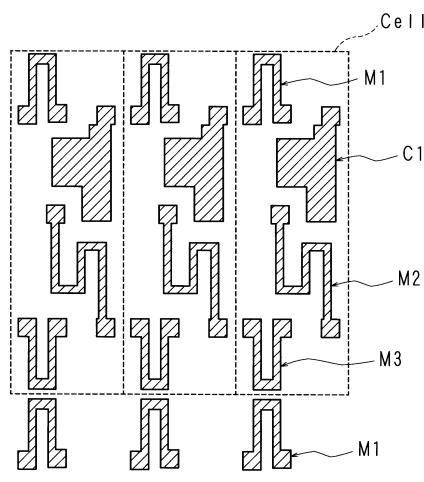

図16から図19は、レイヤのパターン例を示す平面図である。図16はポリシリコン層22のパターンを示している。また、ポリシリコン層22は、スイッチトランジスタM1、駆動トランジスタM2、リセットトランジスタM3のチャネルを含む。

#### 【0070】

図17はポリシリコン層22の上に、第1金属層24のパターンを積層した状態を示す。第1金属層24は、走査線SL、リセット線Rstを含む。第1金属層24は、保持容量C1の上側電極を含む。第1金属層24は、スイッチトランジスタM1、駆動トランジスタM2、リセットトランジスタM3のゲートを含む。第1金属層24は、保持容量C1の第2電極を含む

#### 【0071】

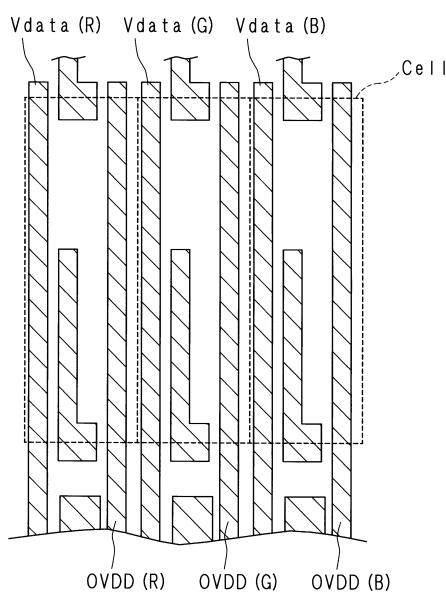

図18は第2金属層26のパターンを示している。第2金属層26は、データ線Vdata(R)、Vdata(G)、Vdata(B)を含む。第2金属層26は、電源供給線OVDD(R)、OVDD(G)、OVDD(B)を含む。第2金属層26は、スイッチトランジスタM1、駆動トランジスタM2、リセットトランジスタM3、のソースドレインを含む。

#### 【0072】

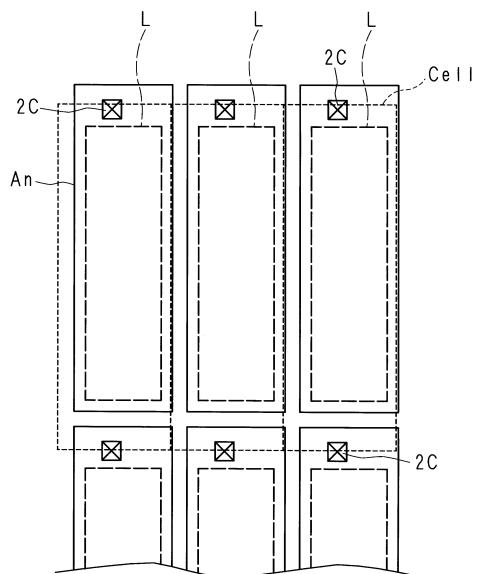

図19は発光領域と画素回路セル枠との位置関係を示す平面図である。図19において、発光領域Lと画素回路セル枠とは、重なっている。しかし、発光領域Lの直下の画素回路は、一つ下にずれた発光領域Lに対応したOLED素子を駆動する。

#### 【0073】

本実施の形態の表示装置1において、データ線は、第2方向に沿って配置され、さらに、データ線の一端側に、走査回路とデータ信号回路とを制御する制御回路と接続する接続配線部を備え、画素回路の駆動トランジスタは、電流を、画素回路の直上に配置された発光部を基準にしてデータ線の一端側に向けて1画素分ずれた位置に配置された発光部に流す。

#### 【0074】

本実施の形態においては、実施の形態1が奏する効果に加え、以下の効果を奏する。発光領域と画素回路との位置関係をずらしたことにより、表示装置のさらなる狭額縫化が可能となる。

#### 【0075】

画素回路は図4に示した回路に限らない。図20は画素Cell1に含まれる画素回路の他の例を示す回路図である。画素回路は、OLED、駆動トランジスタTr1、スイッチト

10

20

30

40

50

ランジスタTr2、リセットトランジスタTr3、保持容量Cを含む。画素回路には、正電源VDD、負電源VSS、映像信号Vdata、走査信号1であるScan(N)、走査信号2であるScan(N-1)およびリセット信号Vreが入力される。映像信号Vdataは、データドライバブロックDM1からDMmのそれぞれから対応する画素回路に出力される。走査信号1であるScan(N)は、N番目の走査ドライバブロックSNから出力される。走査信号2であるScan(N-1)は、N-1番目の走査ドライバSN-1から出力される。

【0076】

映像信号Vdataは、スイッチトランジスタTr2のソース電極に入力される。リセット信号Vreは、リセットトランジスタTr3のソース電極に入力される。

10

【0077】

走査信号1であるScan(N)は、スイッチトランジスタTr2のゲート電極に入力される。走査信号2であるScan(N-1)は、リセットトランジスタTr3のゲート電極に入力される。正電源VDDは保持容量Cの第1の電極および駆動トランジスタTr1のソース電極に接続されている。負電源VSSは、OLEDのカソード電極に接続されている。

【0078】

スイッチトランジスタTr2のドレイン電極は、保持容量Cの第2の電極および駆動トランジスタTr1のゲート電極に接続されている。駆動トランジスタTr1のドレイン電極は、リセットトランジスタTr3のドレイン電極と共に、OLEDのアノード電極に接続されている。

20

【0079】

映像信号Vdataは、それぞれのOLEDを発光させる明るさに対応した、黒電位から白電位までの間の電圧である。図4の画素回路と図20の画素回路とで異なる点は、リセットトランジスタTr3によりOLEDのアノード電極をリセットする機能の有無である。リセットトランジスタTr3は、OLEDにおけるアノード電極とカソード電極との間の電圧を順方向状態（アノード電極の電圧がカソード電極の電圧よりも高い）でなく、バイアス0の状態、または、逆方向状態（アノード電極の電圧がカソード電極の電圧よりも低い）とする事で、OLEDの発光を停止するために用いられる。

【0080】

30

具体的には、リセットトランジスタTr3は、走査信号1であるScan(N)がオンとなる直前に、走査信号2であるScan(N-1)により、オンとなる。リセットトランジスタTr3がオンになると、リセット信号VreがOLEDのカソード電極に印加される。リセット信号Vreは例えば負電源VSSと同じ電位または負電源VSSより低い電位とされる。その結果、OLEDはダイオードの逆方向領域となり、発光しなくなる。

【0081】

このように、リセットTFTを用いて、OLEDの発光を停止する事により、黒レベルを低くすることが出来る。また、しばしば見られるサブ画素間のクロストークを改善することが出来る。

【0082】

40

画素回路として、図4に示すものを採用するか、図20に示すものを採用するかにより、ドライバIC14、データドライバブロックDM1からDMm、走査ドライバブロックS1からSnの構成を変更することは、適宜可能である。なお、図20に示す画素回路では、同じ画素回路に2種類のScan信号が入力される構成（1つの画素回路に2本の走査信号線が配線される構成）となる。したがって、走査ドライバブロックS1からSnのそれぞれは、2本の走査信号線に接続し、2本の走査信号線に異なる信号を出力する。このような変更についても、適宜可能である。

【0083】

各実施の形態で記載されている技術的特徴（構成要件）はお互いに組み合わせ可能であり、組み合わせすることにより、新しい技術的特徴を形成することができる。

50

今回開示された実施の形態はすべての点で例示であって、制限的なものでは無いと考えられるべきである。本発明の範囲は、上記した意味では無く、特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0084】

|                  |             |    |

|------------------|-------------|----|

| 1                | 表示装置        |    |

| 1 1              | 表示部         |    |

| 1 1 1            | 画素          |    |

| 1 2              | TFT回路配置領域   | 10 |

| 1 3              | ガラスフリットシール部 |    |

| D 1 ~ D m, D s m | データドライバブロック |    |

| B 1 1            | DEMUX回路領域   |    |

| B 1 2            | DEMUX配線領域   |    |

| B 1 3            | 走査ドライバ配線領域  |    |

| S 1 ~ S n, S s n | 走査ドライバブロック  |    |

| B 2 1            | 走査ドライバ領域    |    |

| B 2 2            | DEMUX配線領域   |    |

| B 2 3            | 走査ドライバ配線領域  |    |

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(72)発明者 野中 義弘

神奈川県川崎市中原区下沼部1753番地 NLTテクノロジー株式会社内

審査官 村川 雄一

(56)参考文献 特開2009-122636 (JP, A)

国際公開第2011/104945 (WO, A1)

国際公開第2014/112459 (WO, A1)

特開2005-077635 (JP, A)

特開2008-292995 (JP, A)

特開2017-102457 (JP, A)

米国特許出願公開第2016/0225306 (US, A1)

特開2009-134246 (JP, A)

国際公開第11/104945 (WO, A1)

国際公開第14/112459 (WO, A1)

特開2008-051908 (JP, A)

国際公開第10/095306 (WO, A1)

特開2014-106297 (JP, A)

米国特許出願公開第2010/0134743 (US, A1)

韓国公開特許第10-2016-0082883 (KR, A)

(58)調査した分野(Int.Cl., DB名)

G09F9/00-9/46

H01L27/32; H05B33/00-33/28

G09G3/00-3/08; 3/12-3/16; 3/19-3/26;

3/30-3/34; 3/38

G02F1/133; 1/1333; 1/1334; 1/1337;

1/1343-1/1345; 1/1339-1/1341;

1/135; 1/1347