(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-103668

(P2008-103668A)

(43) 公開日 平成20年5月1日(2008.5.1)

(51) Int.Cl.

H01L 27/148 (2006.01)

H04N 5/335 (2006.01)

F 1

H01L 27/14

H04N 5/335

テーマコード(参考)

4M118

5C024

審査請求 未請求 請求項の数 14 O L (全 21 頁)

(21) 出願番号 特願2007-123376 (P2007-123376)

(22) 出願日 平成19年5月8日 (2007.5.8)

(31) 優先権主張番号 特願2006-254041 (P2006-254041)

(32) 優先日 平成18年9月20日 (2006.9.20)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 306037311

富士フィルム株式会社

東京都港区西麻布2丁目26番30号

(74) 代理人 100115107

弁理士 高松 猛

(74) 代理人 100132986

弁理士 矢澤 清純

(72) 発明者 宇家 真司

宮城県黒川郡大和町松坂平1丁目6番地

富士フィルムフォトニックス株式会社内

F ターム(参考) 4M118 AA01 AB01 BA13 CA03 CA04

CA18 CA32 FA17 FA19 FA35

GA02 GB04 GB07 GB11 GB13

GC07 GD04 GD07

5C024 CX04 CX41 CX54 GX07 GX24

GY04 GZ02 GZ27 HX40

(54) 【発明の名称】裏面照射型撮像素子及びこれを備えた撮像装置

## (57) 【要約】

【課題】微細化に有利で且つ青感度の低下を防ぐことができ且つ不要電荷を確実に排出すること可能なオーバーフロードレイン機構を有する裏面照射型撮像素子を提供する。

【解決手段】p 基板 30 の裏面側から光を照射し、前記光に応じて p 基板 30 内で発生した電荷を p 基板 30 の表面側から読み出して撮像を行う裏面照射型撮像素子 100 であって、p 基板 30 内の p 基板 30 表面近傍の同一面上に形成された前記電荷を蓄積するための複数の n 層 4 と、複数の n 層 4 の各々と p 基板 30 の表面との間に形成され、複数の n 層 4 の各々に蓄積される不要な電荷を排出するためのオーバーフロードレインとして機能する複数の n + 層 6 と、複数の n + 层 6 の各々と複数の n 層 4 の各々との間に形成され、オーバーフロードレインのオーバーフローバリアとして機能する複数の p + 層 5 とを備え、n + 層 6 が、平面視において n 層 4 の最大電位点(中心)と重なる位置に形成されている。

【選択図】図 1

## 【特許請求の範囲】

## 【請求項 1】

半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子であって、

前記半導体基板内の前記半導体基板表面近傍の同一面上に形成された前記電荷を蓄積するための第一導電型の複数の第一の不純物拡散層と、

前記複数の第一の不純物拡散層の各々と前記半導体基板の表面との間に形成された前記第一導電型の第二の不純物拡散層であって、前記複数の第一の不純物拡散層の各々に蓄積される不要な電荷を排出するためのオーバーフロードレインとして機能する複数の第二の不純物拡散層と、

前記複数の第二の不純物拡散層の各々と前記複数の第一の不純物拡散層の各々との間に形成され、前記オーバーフロードレインのオーバーフローバリアとして機能する前記第一導電型の反対の第二導電型の複数の第三の不純物拡散層とを備え、

前記第二の不純物拡散層が、平面視において前記第一の不純物拡散層の最大電位点と重なる位置に形成されている裏面照射型撮像素子。

## 【請求項 2】

請求項 1 記載の裏面照射型撮像素子であって、

前記第一の不純物拡散層の最大電位点が、平面視において前記第一の不純物拡散層の中心にある裏面照射型撮像素子。

## 【請求項 3】

請求項 1 又は 2 記載の裏面照射型撮像素子であって、

前記第一の不純物拡散層の最大電位点が、前記第一の不純物拡散層と前記第三の不純物拡散層との境界面から  $0.3 \mu m$  以内の深さにある裏面照射型撮像素子。

## 【請求項 4】

請求項 1 ~ 3 のいずれか 1 項記載の裏面照射型撮像素子であって、

前記複数の第二の不純物拡散層の各々に近接して形成された前記第二の不純物拡散層よりも低濃度の第一導電型の不純物拡散層であって、前記第二の不純物拡散層によって形成される空乏層を前記表面に平行な方向に拡大するための空乏層拡大層を備える裏面照射型撮像素子。

## 【請求項 5】

請求項 1 ~ 4 のいずれか 1 項記載の裏面照射型撮像素子であって、

前記第二の不純物拡散層によって形成される空乏層が、平面視において前記第一の不純物拡散層の  $2/3$  以上を覆っている裏面照射型撮像素子。

## 【請求項 6】

請求項 1 ~ 5 のいずれか 1 項記載の裏面照射型撮像素子であって、

前記複数の第二の不純物拡散層の各々が前記表面に露出する露出面を有し、

前記露出面に接続された電極を備える裏面照射型撮像素子。

## 【請求項 7】

請求項 6 記載の裏面照射型撮像素子と、

前記第一の不純物拡散層の飽和電荷量を決定する第一の電圧を前記電極に印加する第一の電圧印加手段と、

前記第一の電圧印加時に前記第三の不純物拡散層によって形成されるオーバーフローバリアを消失させるために必要な前記第一の電圧よりも高い第二の電圧を前記電極に印加する第二の電圧印加手段とを備える撮像装置。

## 【請求項 8】

請求項 7 記載の撮像装置であって、

前記第二の電圧印加手段が、前記第二の電圧の印加タイミングを可変制御することで、前記裏面照射型撮像素子の露光時間を調整する撮像装置。

## 【請求項 9】

請求項 7 又は 8 記載の撮像装置であって、

10

20

30

40

50

前記第一の電圧印加手段が、前記第一の電圧を可変制御することで前記第一の不純物拡散層の飽和電荷量を調整する撮像装置。

【請求項 1 0】

請求項 7 ~ 9 のいずれか 1 項記載の撮像装置であって、

前記第二の電圧が、前記第一の電圧を基準とした値で決められている撮像装置。

【請求項 1 1】

請求項 7 ~ 1 0 のいずれか 1 項記載の撮像装置であって、

前記裏面照射型撮像素子が、前記複数の第一の不純物拡散層の各々に蓄積された電荷を垂直方向に転送する垂直電荷転送装置と、前記垂直電荷転送装置を転送された電荷を前記垂直方向に直交する水平方向に転送する水平電荷転送装置とを備え、

10

前記第一の電圧が、前記水平電荷転送装置の駆動電圧以下であり、

前記第二の電圧が、前記電荷を前記垂直電荷転送装置に読み出すための読み出し電圧以下である撮像装置。

【請求項 1 2】

請求項 1 1 記載の撮像装置であって、

前記複数の第一の不純物拡散層を  $n$  ( $n$  は 2 以上の自然数) 個のグループに分けて、各グループに蓄積された電荷同士を前記垂直電荷転送装置で加算して転送する加算転送モードと、各グループに蓄積された電荷同士を前記垂直電荷転送装置で非加算で転送する非加算転送モードとが設定可能であり、

20

前記加算転送モード設定時、前記第一の電圧印加手段は、前記第一の不純物拡散層の飽和電荷量が前記非加算転送モード設定時に前記電極に印加すべき前記第一の電圧によって決まる前記第一の不純物拡散層の飽和電荷量の  $1/n$  となるように、前記第一の電圧を可変制御する撮像装置。

【請求項 1 3】

請求項 1 1 又は 1 2 記載の撮像装置であって、

前記裏面照射型撮像素子が、前記水平電荷転送装置を転送された電荷を電圧信号に変換して出力するソースフォロワ回路を備え、

前記垂直電荷転送装置が、最も大きな電圧である  $V_H$  と、最も小さな電圧である  $V_L$  と、前記  $V_H$  と前記  $V_L$  の間の電圧である  $V_M$  との 3 つの電圧で駆動されるものであり、

30

前記第二の電圧が、前記ソースフォロア回路の最終段のトランジスタのドレイン印加電圧、前記  $V_L$  と前記  $V_M$  の差分、及び前記  $V_H$  と前記  $V_M$  の差分のいずれかと前記第一の電圧とを加算した値である撮像装置。

【請求項 1 4】

請求項 1 ~ 1 0 のいずれか 1 項記載の撮像装置であって、

前記裏面照射型撮像素子が、前記複数の第一の不純物拡散層の各々に蓄積された電荷を読み出して蓄積しておくための電荷蓄積層と、前記電荷蓄積層に蓄積された電荷に応じた信号を出力する CMOS 回路とを備える撮像装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

40

本発明は、半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子に関する。

【背景技術】

【0 0 0 2】

半導体基板の裏面側から光を照射し、この光に応じて半導体基板内で発生した電荷を、半導体基板の表面側に形成された電荷蓄積領域に蓄積し、ここに蓄積された電荷に応じた信号を、CCD や CMOS 回路等によって外部に出力して撮像を行う裏面照射型撮像素子が提案されている。以下では、この裏面照射型撮像素子に対し、現在普及している一般的な撮像素子のことを表面照射型撮像素子という。

50

## 【0003】

この裏面照射型撮像素子においても、表面照射型撮像素子と同様に、光電変換素子に蓄積された撮像に不要な過剰電荷を排出するためのオーバーフロードレイン機構を設ける必要がある。表面照射型撮像素子に適用されているオーバーフロードレイン機構には、縦型オーバーフロードレイン機構と横型オーバーフロードレイン機構がある。横型オーバーフロードレイン機構は、各光電変換素子に隣接して各光電変換素子に並行にドレイン領域が設けられるため、この機構では、微細化が進んだ場合に、各構成素子の大きさを十分に大きくすることができず、飽和信号量を維持させることが難しい。一方、縦型オーバーフロードレイン機構は、各光電変換素子の下方に、ドレイン領域を設ける構成であるため、微細化が進んだ場合でも、各構成素子の大きさを確保することができ、飽和信号量を維持することが可能となる。

10

## 【0004】

特許文献1には、裏面照射型撮像素子において縦型オーバーフロードレイン機構を採用した構成が開示されている。

## 【0005】

特許文献2には、裏面照射型撮像素子において表面側にオーバーフロードレイン機構を設けた構成が開示されている。

20

## 【0006】

【特許文献1】特開2001-257337号公報

【特許文献2】特開2006-49338号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0007】

特許文献1に開示された構成は、裏面照射型撮像素子の裏面から照射された光が、まず、縦型オーバーフロードレイン領域に入射し、ここを通過した光が光電変換素子に入射する構成であるため、縦型オーバーフロードレイン領域とその空乏層で発生した電荷が、このドレイン領域から排出されてしまう。このドレイン領域は、光入射側から見て半導体基板内の浅い位置に存在する。ここでは青色の波長域の光が多く吸収され、この結果、著しく青感度の低い撮像素子となってしまう。

30

## 【0008】

これに対し、特許文献2に開示された構成によれば、青感度の低下を防ぐことはできるが、フォトダイオードの最大電位点から離れた位置の上方にドレイン領域が設けられているため、過剰電荷の排出を十分に行うことができない。特に、フォトダイオードに蓄積された電荷を全て掃き出して電子シャッタ機能を実現する際には、電子シャッタON時にフォトダイオードに電荷が残ってしまい、固定パターンノイズなどが発生してしまう。

40

## 【0009】

本発明は、上記事情に鑑みてなされたものであり、微細化に有利で且つ青感度の低下を防ぐことができ且つ不要電荷を完全に掃き出すことが可能な、つまり、固定パターンノイズの少ない電子シャッタ機能を実現可能なオーバーフロードレイン機構を有する裏面照射型撮像素子を提供することを目的とする。

## 【課題を解決するための手段】

## 【0010】

本発明の裏面照射型撮像素子は、半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子であって、前記半導体基板内の前記半導体基板表面近傍の同一面上に形成された前記電荷を蓄積するための第一導電型の複数の第一の不純物拡散層と、前記複数の第一の不純物拡散層の各々と前記半導体基板の表面との間に形成された前記第一導電型の第二の不純物拡散層であって、前記複数の第一の不純物拡散層の各々に蓄積される不要な電荷を排出するためのオーバーフロードレインとして機能する複数の第二の不純物拡散層と、前記複数の第二の不純物拡散層の各々と前記複数の第一の不純物拡散層の各々と

50

の間に形成され、前記オーバーフロードレインのオーバーフローバリアとして機能する前記第一導電型の反対の第二導電型の複数の第三の不純物拡散層とを備え、前記第二の不純物拡散層が、平面視において前記第一の不純物拡散層の最大電位点と重なる位置に形成されている。

## 【0011】

本発明の裏面照射型撮像素子は、前記第一の不純物拡散層の最大電位点が、平面視において前記第一の不純物拡散層の中心にある。

## 【0012】

本発明の裏面照射型撮像素子は、前記第一の不純物拡散層の最大電位点が、前記第一の不純物拡散層と前記第三の不純物拡散層との境界面から $0.3\mu\text{m}$ 以内の深さにある。

10

## 【0013】

本発明の裏面照射型撮像素子は、前記複数の第二の不純物拡散層の各々に近接して形成された前記第二の不純物拡散層よりも低濃度の第一導電型の不純物拡散層であって、前記第二の不純物拡散層によって形成される空乏層を前記表面に平行な方向に拡大するための空乏層拡大層を備える。

## 【0014】

本発明の裏面照射型撮像素子は、前記第二の不純物拡散層によって形成される空乏層が、平面視において前記第一の不純物拡散層の $2/3$ 以上を覆っている。

## 【0015】

本発明の裏面照射型撮像素子は、前記複数の第二の不純物拡散層の各々が前記表面に露出する露出面を有し、前記露出面に接続された電極を備える。

20

## 【0016】

本発明の撮像装置は、前記裏面照射型撮像素子と、前記第一の不純物拡散層の飽和電荷量を決定する第一の電圧を前記電極に印加する第一の電圧印加手段と、前記第一の電圧印加時に前記第三の不純物拡散層によって形成されるオーバーフローバリアを消失させるために必要な前記第一の電圧よりも高い第二の電圧を前記電極に印加する第二の電圧印加手段とを備える。

## 【0017】

本発明の撮像装置は、前記第二の電圧印加手段が、前記第二の電圧の印加タイミングを可変制御することで、前記裏面照射型撮像素子の露光時間を調整する。

30

## 【0018】

本発明の撮像装置は、前記第一の電圧印加手段が、前記第一の電圧を可変制御することで前記第一の不純物拡散層の飽和電荷量を調整する。

## 【0019】

本発明の撮像装置は、前記第二の電圧が、前記第一の電圧を基準とした値で決められている。

## 【0020】

本発明の撮像装置は、前記裏面照射型撮像素子が、前記複数の第一の不純物拡散層の各々に蓄積された電荷を垂直方向に転送する垂直電荷転送装置と、前記垂直電荷転送装置を転送された電荷を前記垂直方向に直交する水平方向に転送する水平電荷転送装置とを備え、前記第一の電圧が、前記水平電荷転送装置の駆動電圧以下であり、前記第二の電圧が、前記電荷を前記垂直電荷転送装置に読み出すための読み出し電圧以下である。

40

## 【0021】

本発明の撮像装置は、前記複数の第一の不純物拡散層を $n$  ( $n$  は $2$ 以上の自然数) 個のグループに分けて、各グループに蓄積された電荷同士を前記垂直電荷転送装置で加算して転送する加算転送モードと、各グループに蓄積された電荷同士を前記垂直電荷転送装置で非加算で転送する非加算転送モードとが設定可能であり、前記加算転送モード設定時、前記第一の電圧印加手段は、前記第一の不純物拡散層の飽和電荷量が前記非加算転送モード設定時に前記電極に印加すべき前記第一の電圧によって決まる前記第一の不純物拡散層の飽和電荷量の $1/n$ となるように、前記第一の電圧を可変制御する。

50

## 【0022】

本発明の撮像装置は、前記裏面照射型撮像素子が、前記水平電荷転送装置を転送された電荷を電圧信号に変換して出力するソースフォロワ回路を備え、前記垂直電荷転送装置が、最も大きな電圧であるVHと、最も小さな電圧であるVLと、前記VHと前記VLの間の電圧であるVMとの3つの電圧で駆動されるものであり、前記第二の電圧が、前記ソースフォロア回路の最終段のトランジスタのドレイン印加電圧、前記VLと前記VMの差分、及び前記VHと前記VMの差分のいずれかと前記第一の電圧とを加算した値である。

## 【0023】

本発明の撮像装置は、前記裏面照射型撮像素子が、前記複数の第一の不純物拡散層の各々に蓄積された電荷を読み出して蓄積しておいたための電荷蓄積層と、前記電荷蓄積層に蓄積された電荷に応じた信号を出力するCMOS回路とを備える。

10

## 【発明の効果】

## 【0024】

本発明によれば、微細化に有利で且つ青感度の低下を防ぐことができ且つ不要電荷を完全に掃き出すことが可能な、つまり、固定パターンノイズの少ない電子シャッタ機能を実現可能なオーバーフロードレイン機構を有する裏面照射型撮像素子を提供することができる。

## 【発明を実施するための最良の形態】

## 【0025】

以下、本発明の実施形態について図面を参照して説明する。

20

## 【0026】

## (第一実施形態)

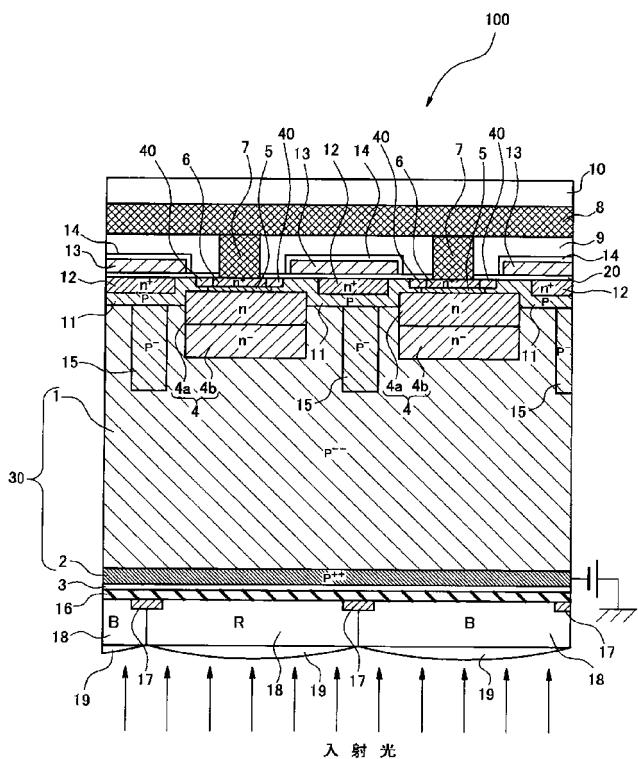

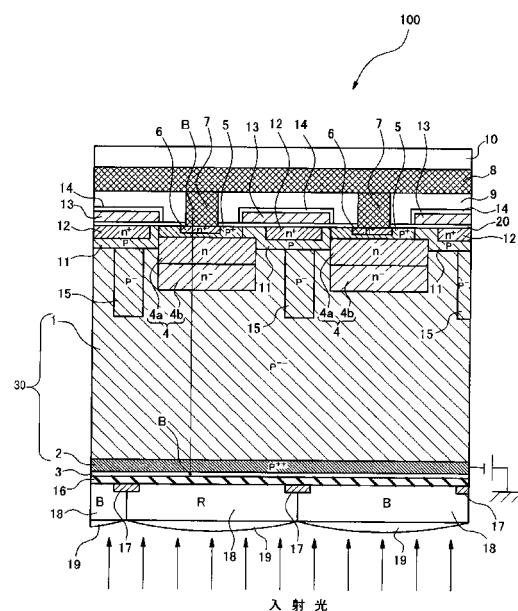

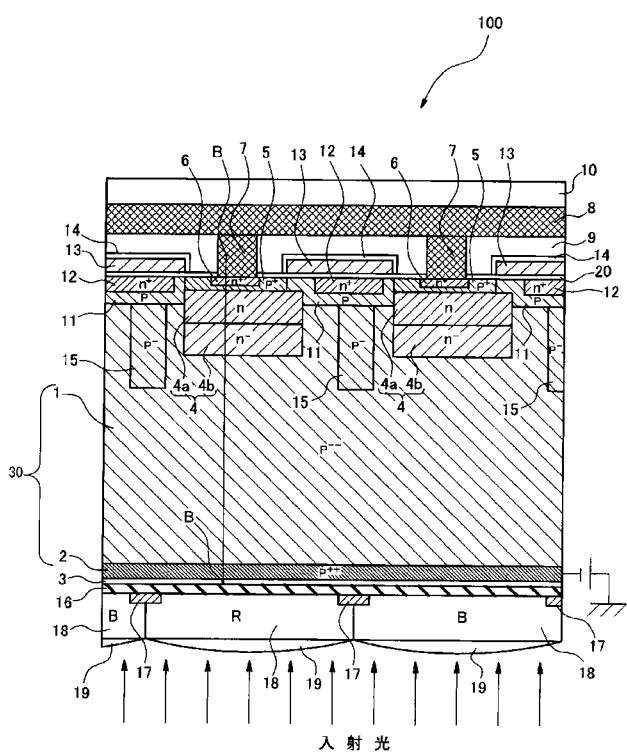

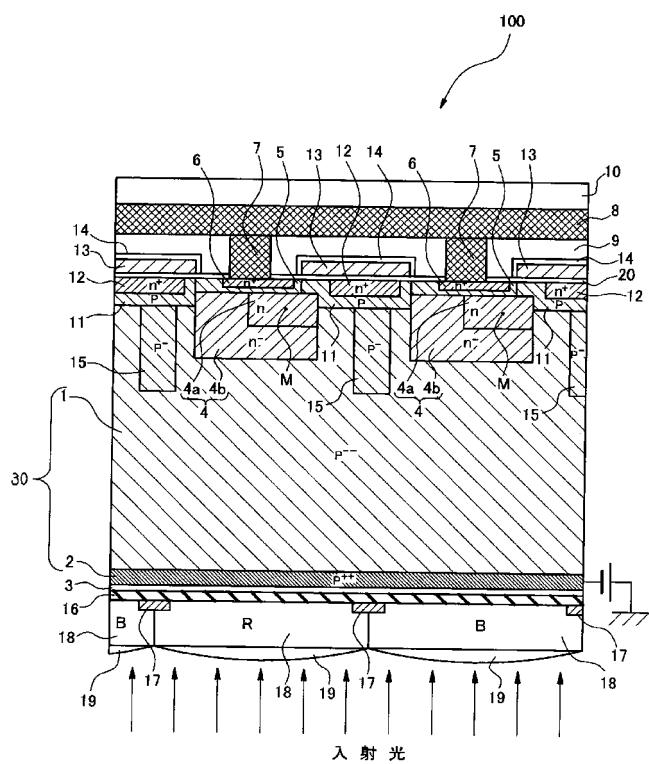

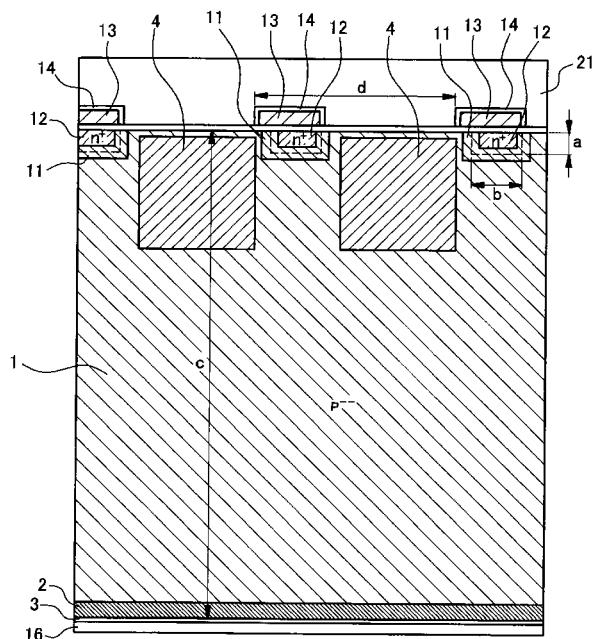

図1は、本発明の第一実施形態を説明するためのインターライン型の裏面照射型撮像素子の部分断面模式図である。

図1に示す裏面照射型撮像素子100は、p型のシリコン層（以下、p層という）1とp層1よりも不純物濃度の高いp++型のシリコン層（以下、p++層という）2とからなるp型の半導体基板（以下、p基板という）30を備える。裏面照射型撮像素子100は、図中下方から上方に向かって光を入射させて撮像を行うものである。本明細書では、p基板30の光入射方向に対して垂直な2つの面のうち、光入射側の面を裏面といい、その反対面を表面という。又、裏面照射型撮像素子100を構成する各構成要素を基準にしたときに、入射光が進む方向を、その構成要素の上方と定義し、入射光が進む方向の反対方向を、その構成要素の下方と定義する。又、p基板30の裏面及び表面に直交する方向を垂直方向、p基板30の裏面及び表面に平行な方向を水平方向と定義する。

30

## 【0027】

p層1内のp基板30表面近傍の水平方向に延びる同一面上には、入射光に応じてp基板30内で発生した電荷を蓄積するためのn型の不純物拡散層（以下、n層という）4が複数配列されている。n層4は、p基板30の表面側に形成されたn層4aと、n層4aの下に形成されたn層4bよりも不純物濃度の低いn-層4bとの2層構造となっているが、これに限らない。n層4で発生した電荷と、このn層4に入射する光の経路上でp基板30内に発生した電荷とが、n層4に蓄積される。

40

## 【0028】

各n層4上にはp基板30表面に発生する暗電荷が各n層4に蓄積されるのを防ぐための高濃度のp型の不純物拡散層（以下、p+層という）5が形成されている。各p+層5内部には、p基板30の表面からその内側に向かってn層4よりも高濃度のn型の不純物拡散層（以下、n+層という）6が形成されている。n+層6は、n層4に蓄積される不要な電荷を排出するためのオーバーフロードレインとして機能し、p+層5が、このオーバーフロードレインのオーバーフローバリアとしても機能する。図示したように、n+層6は、p基板30の表面に露出する露出面を有している。

## 【0029】

p+層5及びn層4の右隣には、少し離間してn層4よりも高濃度のn型不純物拡散層

50

からなる電荷転送チャネル 12 が形成され、電荷転送チャネル 12 の周囲には p+層 5 よりも濃度の低い p 層 11 が形成されている。電荷転送チャネル 12 は、n 層 4 から読み出された電荷を紙面に対して垂直な方向に転送する。

【0030】

p+層 5 及び n 層 4 と電荷転送チャネル 12 との間の p 層 11 及び p 層 1 には、n 層 4 に蓄積された電荷を電荷転送チャネル 12 に読み出すための電荷読み出し領域（図示せず）が形成されている。電荷転送チャネル 12 と電荷読み出し領域の上方には、シリコン酸化膜や ONO 膜等からなるゲート絶縁膜 20 を介して、電荷転送チャネル 12 に電圧を供給して電荷転送動作を制御するための電荷転送電極と、電荷読み出し領域に読み出し電圧を供給して電荷読み出し動作を制御するための電荷読み出し電極とを兼ねたポリシリコン等からなる電極 13 が形成されている。電極 13 の周囲には酸化シリコン等の絶縁膜 14 が形成されている。電荷転送チャネル 12 とその上方の電極 13 とにより、垂直電荷転送装置（VCCD）が構成される。

10

【0031】

尚、図 1 には図示していないが、p 層 1 表面には、電荷転送チャネル 12 を転送された電荷を受け取り、これを電荷転送チャネル 12 の電荷転送方向と直交する方向に転送する電荷転送チャネルが形成され、その上方には電荷転送チャネルの電荷転送動作を制御するための電荷転送電極が形成され、これら電荷転送チャネルと電荷転送電極とにより、水平電荷転送装置（HCCD）が構成される。そして、HCCD の終端には、HCCD を転送されてきた電荷を蓄積するフローティングディフュージョン（FD）領域が設けられ、この FD 領域に、FD 領域に蓄積された電荷に応じた信号を出力するソースフォロア回路からなる信号出力アンプが接続されている。

20

【0032】

隣接する n 層 4 同士の間には、p 層 11 の下に p 型不純物拡散層からなる素子分離層 15 が形成されている。素子分離層 15 は、n 層 4 に蓄積されるべき電荷が、その隣の n 層 4 に漏れてしまうのを防ぐためのものである。

20

【0033】

p 基板 30 の表面上にはゲート絶縁層 20 が形成されており、ゲート絶縁層 20 上には酸化シリコン等の絶縁層 9 が形成されており、この絶縁層 9 内に電極 13 及び絶縁膜 14 が埋設されている。又、ゲート絶縁層 20 と絶縁層 9 内には、n+層 6 の露出面上に、平面視において、その露出面と同じかそれよりも小さい面積のコンタクトホールが形成され、このコンタクトホール内に電極 7 が形成されている。

30

【0034】

電極 7 は、導電性材料であればよく、特に、W（タンクステン）、Ti（チタン）、又は Mo（モリブデン）等の金属材料、或いは、これらとのシリサイド等で構成されることが好ましい。電極 7 と n+層 6 との間には、電極 7 を構成する導電性材料の拡散を防止するための拡散防止層を設けることが好ましい。拡散防止層の構成材料としては、例えば TiN（窒化チタン）を用いる。拡散防止層を設けることにより、n+層 6 と p+層 5 の PN 接合が均一になり、画素間の飽和バラつきを低減することができる。

40

【0035】

絶縁層 9 上には電極 8 が形成され、電極 8 は電極 7 と接続される。電極 8 上には保護層 10 が形成されている。電極 8 は、導電性材料であれば良い。電極 8 には端子が接続され、この端子に、所定の電圧を印加できるようになっている。

【0036】

n+層 6 に移動した電荷は、n+層 6 の露出面に接続された電極 7 とこれに接続された電極 8 に移動するため、これにより、n+層 6 をオーバーフロードレインとして機能させることができる。

【0037】

p 基板 30 の裏面から内側には、p 基板 30 の裏面で発生する暗電荷が n 層 4 に移動するのを防ぐために、p++層 2 が形成されている。p++層 2 には端子が接続され、この

50

端子に所定の電圧（電圧が接地電圧である場合も含む）が印加できるようになっている。

$p^{++}$ 層2の濃度は、例えば $1 \times 10^{17} / \text{cm}^3$ ～ $1 \times 10^{20} / \text{cm}^3$ である。

【0038】

$p^{++}$ 層2の下には、酸化シリコンや窒化シリコン等の入射光に対して透明な絶縁層3が形成されている。絶縁層3の下には、絶縁層3と $p$ 基板30との屈折率差に起因する $p$ 基板30の裏面での光の反射を防止するために、窒化シリコンやダイヤモンド構造炭素膜等の入射光に対して透明な高屈折率透明層16が形成されている。高屈折率透明層16としては、プラズマCVDや光CVD等の400以下の低温形成が可能なアモルファス窒化シリコン等の $n = 1.46$ を超える例えば $n = 1.8 \sim 2.2$ の屈折率の層とすることが好みしい。

10

【0039】

高屈折率透明層16の下には、複数のカラーフィルタ18を水平方向に配列してなるカラーフィルタ層が形成されている。複数のカラーフィルタ18は、それぞれ異なる波長域の光を透過する複数種類のカラーフィルタに分類される。例えば、カラーフィルタ層は、赤色の波長域の光を透過するRカラーフィルタと、緑色の波長域の光を透過するGカラーフィルタと、青色の波長域の光を透過するBカラーフィルタとを配列した構成となっている。カラーフィルタ18は、複数の $n$ 層4の各々の下方に形成されており、各 $n$ 層4に1つのカラーフィルタ18が対応して設けられている。又、各 $n$ 層4には、1つの $n^+$ 層6が対応するため、カラーフィルタ18は、複数の $n^+$ 層6のいずれかに対応していると言うことができる。

20

【0040】

隣接するカラーフィルタ18同士の間には、混色を防止するための遮光部材17が形成されている。この遮光部材17は、光を透過させない機能を持つものであれば良く、W、Mo、及びAl（アルミニウム）等の可視光透過率の低い金属やブラックフィルタを用いることができる。

【0041】

遮光部材17は、その断面形状が、 $p$ 基板30の裏面に向かって広がるテーパー状（頂点が光入射側に向いた三角形や、上底が下底よりも長くなった台形）となっていることが好みしい。このようにすることで、遮光部材17に垂直入射した光を、テーパー面で反射させて $p$ 基板30内に導くことができ、光利用効率を上げることができる。

30

【0042】

各カラーフィルタ18の下には、マイクロレンズ19が形成されている。マイクロレンズ19は、屈折した光が、その上方のカラーフィルタ18とそのカラーフィルタ18に隣接するカラーフィルタ18との間にある遮光部材17を避ける光路となるように、その形状が決定されている。又、マイクロレンズ19の焦点は、 $n$ 層4の中心に来るよう設計されている。

【0043】

$n$ 層4上面から $p$ 基板30の裏面までの領域のうち、平面視において素子分離層15で区画された領域が、撮像に寄与する光電変換を行う領域のため、以下では光電変換領域という。1つの光電変換領域で発生する電荷に応じた信号が、画像データの1画素データのもととなることから、本明細書では、この光電変換領域のことを画素ともいう。つまり、裏面照射型撮像素子100は、複数の画素と、複数の画素の各々で発生した電荷に応じた信号を読み出すCCD型又はCMOS型の信号読出し部とを備える構成となる。

40

【0044】

シリコン基板では、波長毎の光吸収係数の違いにより、可視域の光をもれなく吸収するためには、実験上、その厚みが $9 \mu\text{m}$ 以上必要であることが分かっている。このため、裏面照射型撮像素子100においても、 $p$ 基板30の垂直方向の長さを $9 \mu\text{m}$ 以上としておくことが好みしい。このようにすることで、可視光をもれなく吸収することができ、感度を向上させることができる。

【0045】

50

p 基板 3 0 の垂直方向の長さを  $9 \mu m$  以上にした場合には、次のような利点がある。

・電荷転送チャネル 1 2 には光がほとんど到達しなくなるため、p 基板 3 0 内に、電荷転送チャネル 1 2 を遮光するための遮光層を設けることなく、又、裏面照射型撮像素子をフレームインターライン型にすることなく、インターライン型でも十分スミアの低い撮像素子を実現することができる。

- ・量子効率が高まり、感度が向上する。

- ・長波長の感度が高くなる。

- ・近赤外の感度が飛躍的に高くなる。

#### 【0046】

ただし、p 基板 3 0 の垂直方向の長さを  $9 \mu m$  以上とすると、電荷分離層 1 5 等の影響により、低い n 層 4 の空乏化電圧（現状の撮像素子で用いられる 3 V 程度）では、各光電変換領域に空乏層を形成することが難しくなる。そこで、各光電変換領域に空乏層を形成でき、且つ、この空乏層で発生した電荷を n 層 4 に移動させることのできるような電位勾配を持たせるように、p 基板 3 0 の濃度を最適に設計しておく必要がある。

10

#### 【0047】

本出願人は、シミュレーションの結果、p 基板 3 0 を次の（1）～（3）の構成としていることで、上記条件を満たせることを見出した。

（1）n 層 4 と p + + 層 2 との間の中間層に、 $1 \times 10^{-4} / cm^3$  以下の n 層又は p 層、或いは i 層を少なくとも含む構成

（2）上記中間層に、 $2 \times 10^{-4} / cm^3$  以下の n 層と、 $2 \times 10^{-4} / cm^3$  以下の p 層とを含む構成

（3）（2）の n 層と p 層の間に、 $1 \times 10^{-4} / cm^3$  以下の n 層、 $1 \times 10^{-4} / cm^3$  以下の p 層、及び i 層のうちの少なくとも 1 つを含む構成

20

#### 【0048】

このように構成された裏面照射型撮像素子 1 0 0 では、1 つのマイクロレンズ 1 9 に入射した光が、そのマイクロレンズ 1 9 上方のカラーフィルタ 1 8 に入射し、ここを透過した光が、このカラーフィルタ 1 8 に対応する n 層 4 へと入射される。このとき、p 基板 3 0 のうち入射光の経路となる部分でも電荷が発生するが、この電荷は、光電変換領域に形成されたポテンシャルスロープを介して n 層 4 へと移動し、ここで蓄積される。n 層 4 に入射してここで発生した電荷も、ここに蓄積される。n 層 4 に蓄積された電荷は、電荷転送チャネル 1 2 に読み出されて転送され、出力アンプによって信号に変換されて外部に出力される。

30

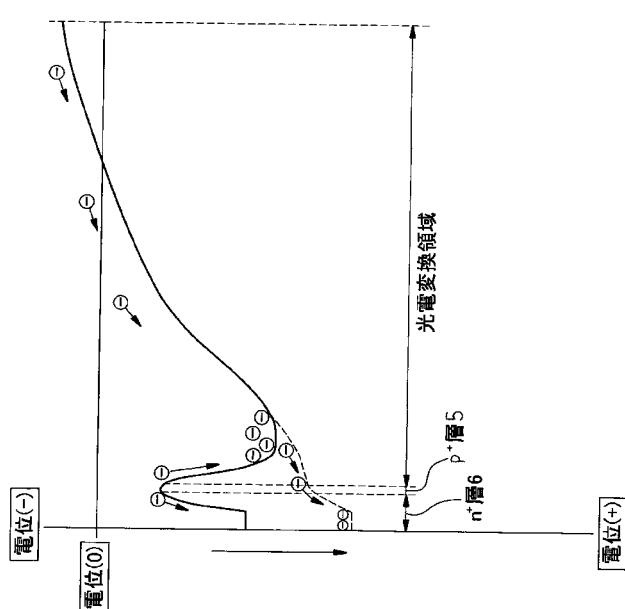

#### 【0049】

図 2 は、図 1 に示す B - B 線の電位プロファイルを示す図である。

図 2 に示すように、n + 層 6 と光電変換領域においてそれぞれ電位井戸が形成され、p + 層 5 がこれらの電位井戸同士の間のバリアとして機能していることが分かる。光電変換領域に形成される電位井戸の飽和容量を超えた電荷は、n + 層 6 に形成される電位井戸に流れ込み、流れ込んだ電荷は電極 7 に移動することで、外部に排出される。このため、n + 層 6 に接続される電極 7 に印加する電圧を変化させて p + 層 5 のバリアの高さを調整することで、n 層 4 の飽和容量の制御が可能となる。例えば、信号を加算して読み出す動画撮影モード時においては、n 層 4 の飽和容量を減少させる制御を行うことで、電荷転送チャネル 1 2 でのオーバーフローを防ぐことができる。

40

#### 【0050】

又、図 2 の破線で示すように、p + 層 5 に形成されるバリアを消失させられる程度のレベルの電圧を n + 層 6 に接続される電極 7 に印加することで、光電変換領域に形成された電位井戸内の電荷をリセットすることができたため、このことを利用して電子シャッタを実現することができる。

#### 【0051】

光電変換領域に形成された電位井戸内の電荷を完全にリセットするためには、n + 層 6 の形成位置が重要となる。n 層 4 の最大電位点（光電変換領域の最大電位点と同義）は、

50

電位井戸の最も深い場所となるため、ここに溜まった電荷を  $n +$  層 6 に移動させることができれば、光電変換領域に形成された電位井戸内の電荷を完全にリセットすることができる。裏面照射型撮像素子 100 は、 $n$  層 4 の最大電位点と平面視上重なる位置に、 $n +$  層 6 が形成されており、この位置関係によって、光電変換領域に形成された電位井戸内の電荷を完全にリセットすることを可能にしている。特許文献 2 にあるように、 $n$  層 4 の最大電位点と重ならない位置に  $n +$  層 6 を設けた場合には、光電変換領域に形成された電位井戸の最も深い場所に溜まった電荷が  $n +$  層 6 に移動できない恐れがあり、電子シャッタ機能の実現には適当ではないが、裏面照射型撮像素子 100 の構成によれば、電子シャッタ機能を十分に実現することができる。

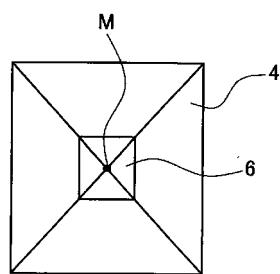

## 【0052】

10

図 3 は  $n$  層 4 の平面図である。図 3 に示すように、 $n$  層 4 は水平方向にはその濃度が一定であるため、 $n$  層 4 の中心に最大電位点 M が存在することになる。このため、裏面照射型撮像素子 100 においては、 $n$  層 4 の中心と重なる位置に  $n +$  層 6 を設けることで、電子シャッタ機能を実現可能としている。

## 【0053】

尚、 $n$  層 4 の最大電位点は、 $n$  層 4 の中心にあるとは限らない。例えば、 $n$  層 4 の構成を図 4 に示すようにした場合、 $n$  層 4 の最大電位点は、図示したように、その中心からずれた位置に存在する。この場合には、図 4 に示した最大電位点 M と重なる位置に  $n +$  層 6 を設けた構成とすれば良い。

## 【0054】

20

又、 $n$  層 4 の最大電位点の  $p +$  層 5 と  $n$  層 4 との境界面からの距離（深さ）は、光電変換領域に形成された電位井戸内からの電荷の掃き出しをより完全なものとし、且つ、電荷掃き出し時に電極 7, 8 に印加する電圧をより低く抑えるために、0.3 μm 以内とすることが好ましい。

## 【0055】

30

尚、 $n +$  層 6 に接続する電極 7 を、その  $n +$  層 6 に対応するカラーフィルタ 18 の種類毎に共通に接続し、カラーフィルタ 18 の種類毎に共通化された電極 7 のそれぞれに独立に電圧を印加できるようにしておく構成も考えられる。このようにした場合、各種類のカラーフィルタに対応する光電変換領域毎に、独立に電子シャッタをかけられるようにすることが可能である。つまり、各光電変換領域における電荷蓄積時間を、そこに入射する光の色毎に変えることができ、電荷蓄積時間の制御でカラーバランスを揃えた出力を得ることが可能となる。

## 【0056】

40

又、複数の  $n +$  層 6 を、動画撮影モード等の間引き読み出しを行う撮影モードにおいて電荷を読み出す  $n$  層 4 に対応する  $n +$  層 6 からなる第一のグループと、該撮影モードにおいて電荷を読み出さない  $n$  層 4 に対応する  $n +$  層 6 からなる第二のグループとに分類しておき、同一グループに属する  $n +$  層 6 每に、電極 7 を共通に接続しておき、共通化された電極 7 のそれぞれに独立に電圧を印加できるようにしておく構成も考えられる。このようにした場合、グループ毎に印加電圧を変えることで、ハイライト光に対する画素間ブルーミング抑制効果を高めることが可能となる。

## 【0057】

尚、これらの電極 7 及び電極 8 への電圧印加は、裏面照射型撮像素子 100 を備えるデジタルカメラ等の撮像装置において、裏面照射型撮像素子 100 を駆動するドライバが行えれば良い。以下、裏面照射型撮像素子 100 を備えた撮像装置の構成例について説明する。

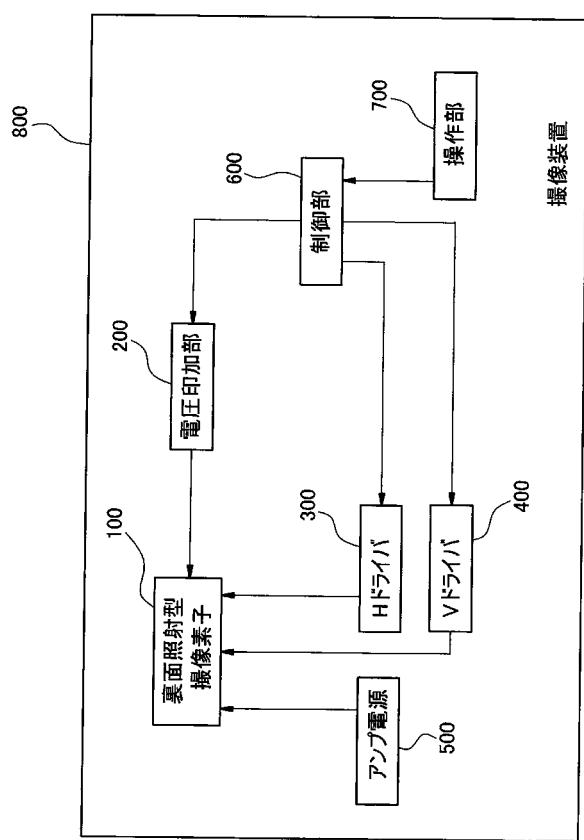

## 【0058】

図 5 は、裏面照射型撮像素子 100 を備えた撮像装置の構成例を示すブロック図である。

図 5 に示す撮像装置 800 は、裏面照射型撮像素子 100 と、裏面照射型撮像素子 100 の電極 8 に電圧を印加する電圧印加部 200 と、裏面照射型撮像素子 100 の HCCD

50

を駆動するHドライバ300と、裏面照射型撮像素子100のVCCDを駆動するVドライバ400と、裏面照射型撮像素子100の信号出力アンプの電源であるアンプ電源500と、撮像装置全体を統括制御する制御部600と、操作部700とを備える。

#### 【0059】

Vドライバ400は、n層4からVCCDに電荷を読み出すための読み出し電圧VHと、電荷転送するために必要な電圧VM, VLとを裏面照射型撮像素子100に供給してVCCDを駆動する。尚、VH > VM > VLとなっており、VHは例えば15V程度である。

#### 【0060】

Hドライバ300は、電荷転送するために必要な電圧vHとvLとを裏面照射型撮像素子100に供給してHCCDを駆動する。尚、vH > vLとなっており、vHは例えば3.3V程度である。

10

#### 【0061】

アンプ電源500は、信号出力アンプのソースフォロア回路の各段のトランジスタのドレイン電圧を供給する電源である。

#### 【0062】

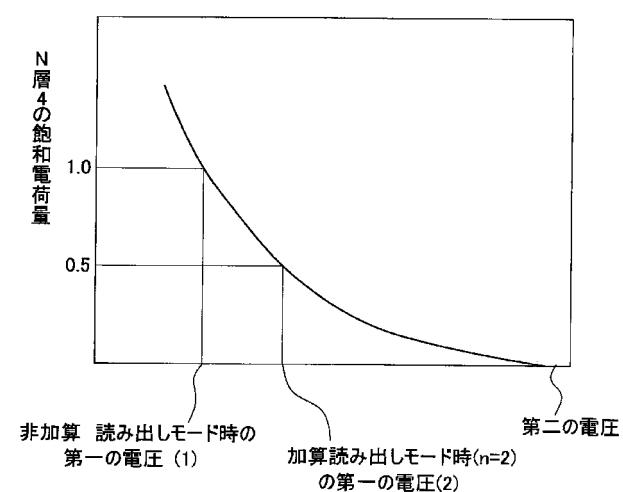

電圧印加部200は、n層4の飽和電荷量（光電変換領域の飽和電荷量と同義）を決定する第一の電圧を電極8に印加する第一の機能と、第一の電圧を印加した状態でp+層5によって形成されているオーバーフローバリアを消失させるために必要な第一の電圧よりも高い第二の電圧を電極8に印加する第二の機能とを有する。第一の電圧はHCCDの駆動電圧（振幅3.3V）以下とし、第二の電圧は読み出し電圧VH（振幅15V）以下とすることが好ましい。このようにすることで、既存の電源から第一の電圧及び第二の電圧を生成することができ、新たな電源が不要となるからである。

20

#### 【0063】

又、第二の電圧は第一の電圧を基準とした値に設定することが好ましい。例えば、第二の電圧を、ソースフォロア回路の最終段のトランジスタのドレイン印加電圧、VLとVMの差分、及びVHとVMの差分のいずれかを第一の電圧に加算した値とする。このようにすることで、既存の電源から第二の電圧を生成することができ、新たな電源を不要にすることができる。

30

#### 【0064】

電圧印加部200は、第一の電圧を可変制御することでn層4の飽和電荷量を調整したり、第二の電圧の印加タイミングを可変制御することで裏面照射型撮像素子100の露光時間を調整したりする。例えば、撮像装置800が、複数のn層4をn（nは2以上の自然数）個のグループに分けて、各グループに蓄積された電荷同士をVCCDで加算して転送する加算転送モードと、該各グループに蓄積された電荷同士をVCCDで加算しないで転送する非加算転送モードとが設定可能であるものとする。非加算転送モードは、例えば高画質が求められる静止画撮影モード時に実行され、加算転送モードは、例えば高速動作が求められる動画撮影モード時に実行される。

電圧印加部200は、加算転送モード設定時、n層4の飽和電荷量が非加算転送モード設定時に電極8に印加すべき第一の電圧によって決まるn層4の飽和電荷量の1/nとなるように、第一の電圧を可変制御する（図6参照）。このようにすることで、VCCDやHCCDで電荷がオーバーフローしてしまうのを防ぐことができる。

40

#### 【0065】

以上のような構成の撮像装置800の動作を説明する。

ユーザによって操作部700を介して静止画撮影モードが設定され、制御部600により露光時間が決定されると、電圧印加部200は、制御部600によって決定された露光時間の開始直前まで、電極8に図6に示したような第二の電圧の印加を繰り返し行う。そして、露光開始と同時に、電極8に印加する電圧を図6に示したような第一の電圧（1）に切り替える。露光期間終了後は、Hドライバ300及びVドライバ400によってn層4に蓄積された電荷が信号出力アンプまで転送され、ここで信号に変換されて出力される

50

。

## 【0066】

一方、ユーザによって操作部700を介して動画撮影モードが設定され、制御部600により露光時間が決定されると、電圧印加部200は、制御部600によって決定された露光時間の開始直前まで、電極8に図6に示したような第二の電圧の印加を繰り返し行う。そして、露光開始と同時に、電極8に印加する電圧を図6に示したような第一の電圧(2)に切り替える。露光期間終了後は、Hドライバ300及びVドライバ400によってn層4に蓄積された電荷が信号出力アンプまで転送され、ここで信号に変換されて出力される。

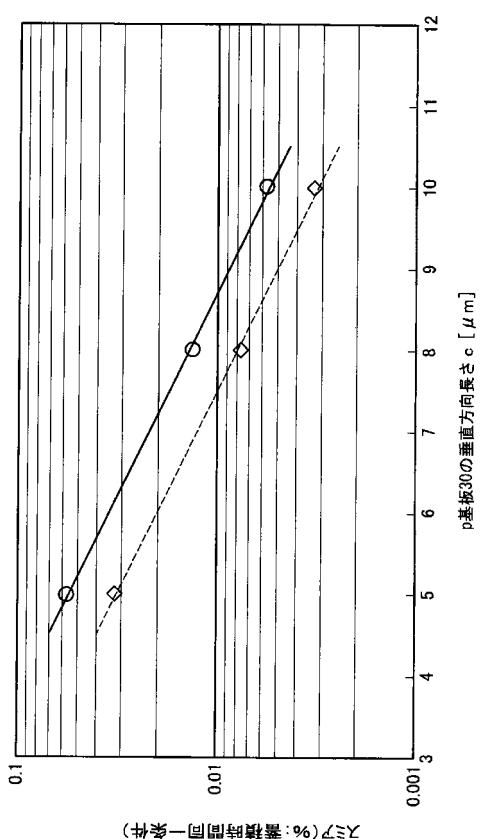

## 【0067】

裏面照射型撮像素子100はインターライン型であるため、露光期間中に、電荷転送チャネル12にも光が入射する可能性があり、これがスミアの原因となる。以下では、上述したように、p基板30の垂直方向の長さを9μm以上とすれば、スミアを低く抑えられることを、シミュレーション結果に基づいて証明する。

## 【0068】

図7は、図1に示す裏面照射型撮像素子100を一部簡略化した図であり、図1と同一要素には同一符号を付してある。

図7において、符号aは電荷転送チャネル12の空乏層の垂直方向の長さを示し、符号bは、電荷転送チャネル12の空乏層の水平方向の長さを示し、符号cは、p基板30の垂直方向の長さを示し、符号dは、n層4の配列ピッチを示している。図7に示すモデルでは、絶縁層9の変わりに、光を吸収する光吸収層21を設けたものとしている。

## 【0069】

ここで、 $a = 0.00004\text{ cm}$ 、 $b = 0.00005\text{ cm}$ 、 $c = 0.0005\text{ cm}$ 、 $d = 0.0002\text{ cm}$ とし、電荷転送チャネル12のうち、そこに形成される空乏層以外で発生した電子は、全てその電荷転送チャネル12に対応するn層4に流れ込んで信号になるとし、電荷転送チャネル12の空乏層で発生した電子は、全てスミア信号になると仮定した。n層4の配列は正方配列とし、信号読み出し方式はインターライン方式とした。又、p基板30を通過した光は全て光吸収層21に吸収されるものとした。

## 【0070】

厚さ $x$ (cm)のシリコンの光吸収率Yは、 $Y = \{1 - E \times p(-\times x)\}$ (ここで、 $E$ はシリコンの光吸収係数)であるので、図7に示す裏面照射型撮像素子のp基板30の裏面側下方にIRカットフィルタを配置し、IRカットフィルタに3300K光源から光を照射した場合の各画素の透過分光から、各波長毎(400~700nm、10nm間隔)に信号とスミア信号を計算して平均値を計算し、p基板30の垂直方向の1/10の領域で注入が起こる条件で信号に対するスミア信号の比を求めるとき、0.032%(n層4をハニカム配列とした場合は0.056%)となった(図8参照)。

## 【0071】

又、 $c = 8\text{ μm} = 0.0008\text{ cm}$ とすると、スミア信号の比は、0.0075%(n層4をハニカム配列とした場合は0.013%)となり、 $c = 10\text{ μm} = 0.001\text{ cm}$ とすると、スミア信号の比は、0.0032%(n層4をハニカム配列とした場合は0.0056%)となった(図8参照)。

## 【0072】

ここで、ハニカム配列とは、行方向に配列された多数のn層4からなる行を、行方向に直交する列方向に多数並べた配列であって、偶数行と奇数行とを、行方向に1/2ピッチずらした配列であり、正方配列と比較した場合、電荷転送チャネルの面積は1.75倍に増えるので、正方配列の結果を1.75倍したものと、ハニカム配列の見積もり値とした。

## 【0073】

図8に示すシミュレーション結果から、インターライン型の裏面照射型撮像素子100は、p基板30の垂直方向の長さを5μm以上とすれば、同一感度を得るためのインター

10

20

30

40

50

ライン型の表面照射型撮像素子よりもスミアを抑制できることが分かった。又、p 基板 30 の垂直方向の長さを 8  $\mu\text{m}$  以上とすれば、よりスミアを抑制でき、10  $\mu\text{m}$  以上とすれば更にスミアを抑制できることが分かった。

【0074】

以上のように、裏面照射型撮像素子 100 によれば、入射光がほぼ到達しない p 基板 30 の表面側にオーバーフロードレインを設けているため、p 基板 30 の裏面側にオーバーフロードレインを設ける従来構造に比べて、青感度を向上させることができる。

【0075】

又、このオーバーフロードレインに印加する電圧を制御することで、各光電変換領域の飽和容量や電荷蓄積時間を一律に又は独立に制御することができ、様々なパターンの駆動を容易に実現することができる。

10

【0076】

又、裏面照射型撮像素子 100 によれば、電子シャッタを実現する際に n+ 層 6 に印加する電圧振幅を、p 基板 30 の裏面側にオーバーフロードレインを設ける従来構造に比べて大幅に下げるができる (23V 15V 以下)。逆に、電圧振幅が従来と同じであれば、各光電変換領域の飽和容量を大幅に増やすことが可能となる。

20

【0077】

尚、図 1 において、p++ 層 2 を省略し、その代わりに、絶縁層 3 の下に入射光に対して透明な ITO 等の透明電極を設け、この透明電極に電圧が印加できるように構成し、この透明電極に負電圧を印加しておけば、p 基板 30 の裏面で発生する暗電流を抑制することができる。

20

【0078】

又、以上の説明では、上述したように、p 基板 30 の垂直方向の長さが 8  $\mu\text{m}$  以上であれば、スミアは十分に抑制されるため、裏面照射型撮像素子 100 をインターライン型としたが、光電変換領域の深さが 8  $\mu\text{m}$  以上であっても、スミアは多少なりとも発生してしまう。このため、裏面照射型撮像素子 100 をフレームインターライン型とすれば、更なるスミア低減が可能となる。

20

【0079】

又、以上の説明では、裏面照射型撮像素子 100 が CCD 型のものとしたが、これはもちろん MOS 型であっても良い。つまり、n 層 4 に蓄積された電荷に応じた信号を、CMOS 回路や NMOS 回路等の MOS 回路で読み出す構成としても良い。

30

【0080】

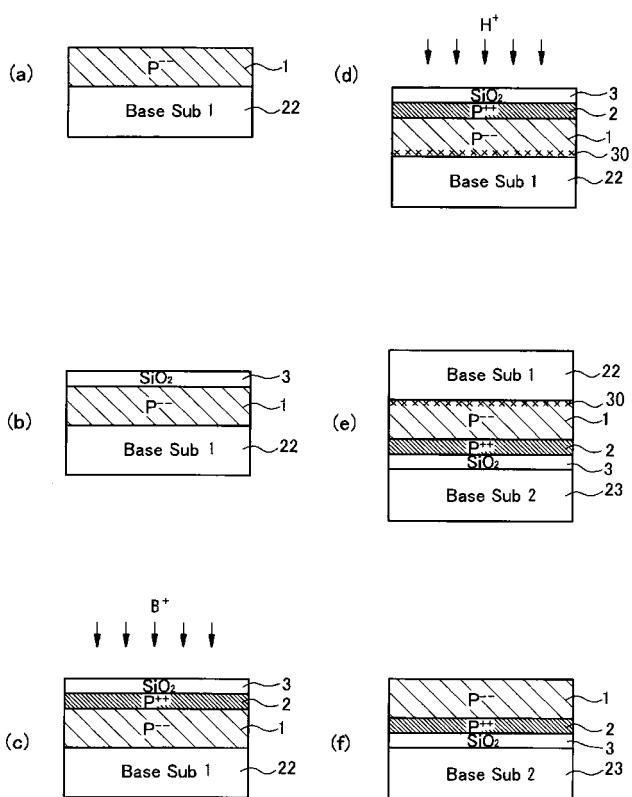

次に、図 1 に示した裏面照射型撮像素子 100 の p 基板 30 及び絶縁層 3 からなる SOI 基板の製造方法の一例を説明する。

図 9 は、裏面照射型撮像素子 100 に用いる SOI 基板の製造工程を説明するための図である。図 9 において、図 1 と同様の構成には同一符号を付してある。

まず、シリコン等のベース基板 22 上に、エピタキシャル成長等によって p 層 1 を形成する (図 9 (a))。図 9 (a) において p 層 1 の露出している面が、p 基板 30 の裏面となる。次に、p 層 1 の露出している面上に、CVD や熱酸化等によって酸化シリコンからなる絶縁層 3 を形成する (図 9 (b))。

40

【0081】

次に、絶縁層 3 上方からボロン等のイオン注入を行って、p 層 1 の絶縁層 3 との界面内側に p++ 層 2 を形成する (図 9 (c))。次に、ベース基板 22 と p 層 1 との界面付近に水素イオンを注入する (図 9 (d))。このイオン注入によりベース基板 22 と p 層 1 とが分離されるための境界層 30 が形成される。

【0082】

次に、絶縁層 3 上に、シリコン等のベース基板 23 を結合した後、ベース基板 23 が下側に、ベース基板 22 が上側となるように回転させる (図 9 (e))。次に、ベース基板 22 を境界層 30 と共に p 層 1 から剥離する (図 9 (f))。

【0083】

50

そして、図9(f)の状態から、p基板30の表面近傍にある要素を形成し、形成後、ベース基板23を、絶縁層3をストップとしてエッチングして除去した後、カラーフィルタ18やマイクロレンズ19等を形成して、裏面照射型撮像素子100の製造を完了する。

#### 【0084】

図9(f)でベース基板23を除去する方法としては、KOHをエッチャントとしたエッチングを行う方法が考えられる。又、光励起法を使ったエッチングも考えられる。絶縁層3としては酸化シリコンの他に、窒化シリコンも用いることができるため、この場合には、窒化シリコンがストップとなるようなエッチャントを使用すれば良い。

#### 【0085】

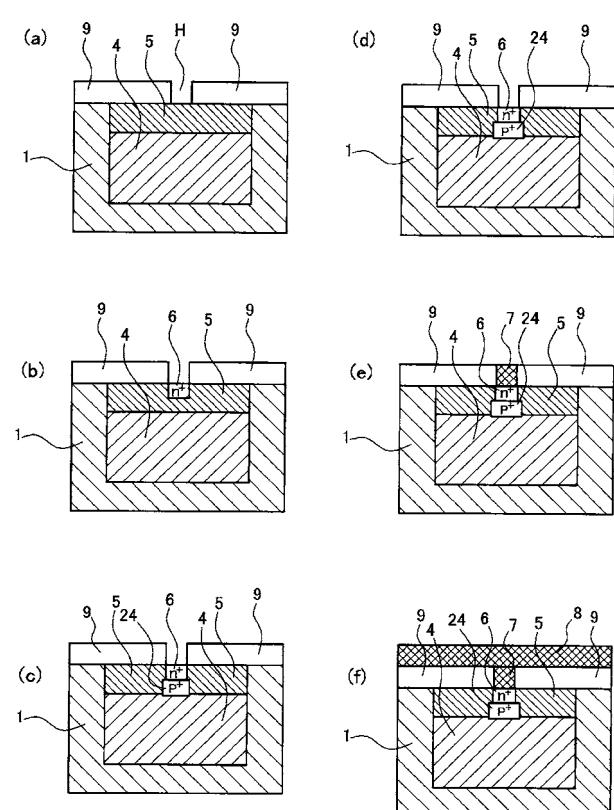

次に、裏面照射型撮像素子100のn+層6と電極7の形成方法を説明する。

裏面照射型撮像素子100のオーバーフロードレインの特性を不安定にする要因として、p+層5とn+層6との合わせずれ、n+層6と電極7との合わせずれ、絶縁層9内に形成されたコンタクトホールへの電極7の被覆不良等が考えられる。このような合わせずれや被覆性の改善のためには、平面視において、p+層5とn+層6の面積を大きくし、電極7の面積を大きくすることが最も簡単な策であるが、このような策は、画素の微細化を進める上で大きな障害となってしまう。そこで、本実施形態では、合わせずれや被覆性の改善と、画素の微細化とを同時に実現可能な方法を提案する。

#### 【0086】

図10は、裏面照射型撮像素子100のn+層6と電極7と電極8の形成方法を説明するための図である。図10において、図1と同様の構成には同一符号を付してある。

まず、図9(f)の状態から、p基板30の表面上方からライオン注入等によってn層4とその上のp+層5を形成した後、p基板30表面上にゲート絶縁層20を形成し(図示省略)、その上に絶縁層9を形成し、平面視において、p+層5と重なるゲート絶縁層20及び絶縁層9の領域の一部に、フォトリソフライ法とエッチングによってコンタクトホールHを形成する(図10(a))。

#### 【0087】

次に、ゲート絶縁層20及び絶縁層9をマスクとして例えばAs(ヒ素)をイオン注入し、セルフアラインでp+層5内にn+層6を形成する(図10(b))。この状態から、電極7を構成する金属材料として例えばタンクスチンをCVD法等によって成膜し、絶縁層9をストップとしたエッチングやCMP等によって平坦化して、コンタクトホールH内に金属材料膜を埋め込み、電極7を形成する。そして、絶縁層9及び電極7上に電極8を構成する導電性材料を成膜することで、n+層6、電極7、及び電極8の形成を完了する。

#### 【0088】

尚、n+層6の下面とn層4とが接触してしまうと、オーバーフローバリアがなくなってしまい、n+層6をオーバーフロードレインとして機能させることができない。このような事態を確実に防ぐための方法を、図10(b)~(f)に示してある。

#### 【0089】

n+層6をセルフアラインで形成した後、ゲート絶縁層20及び絶縁層9をマスクとして、n+層6の不純物よりも拡散係数が大きい不純物、例えばB(ボロン)をイオン注入し、セルフアラインでn+層6の下にp+層24を形成する(図10(c))。次に、活性化のためのアニール処理を実施すると、AsよりBの方が拡散係数が大きいため、n+層6の端部をカバーするように、p+層24が広がる(図10(d))。次に、電極7を構成する金属材料として例えばタンクスチンをCVD法等によって成膜し、絶縁層9をストップとしたエッチングやCMP等によって平坦化して、コンタクトホールH内に金属材料膜を埋め込み、電極7を形成する(図10(e))。そして、絶縁層9及び電極7上に電極8を構成する導電性材料を成膜することで、n+層6、電極7、及び電極8の形成を完了する(図10(f))。

#### 【0090】

10

20

30

40

50

尚、ここでは、ゲート絶縁層20及び絶縁層9をマスクとしているが、ゲート絶縁層20及び絶縁層9に開口を形成するために用いたレジスト材料層を残しておき、このレジスト材料層を併せてマスクにしても良い。又、ゲート絶縁層20及び絶縁層9を形成する前に、p基板30表面上にレジスト材料層を形成し、このレジスト材料層に開口を形成した後、このレジスト材料層をマスクとしてn+層6とp+層24を形成しても良い。この場合は、n+層6、p+層24を形成して電極7を形成後に、レジスト材料層を除去してゲート絶縁層20及び絶縁層9を形成すれば良い。

#### 【0091】

図10(c)～(f)で示した方法によれば、図10(b)の状態で、n+層6の下面がn層4に接触していた場合でも、n+層6とn層4の間にp+層24を形成することができるため、このp+層24がオーバーフローバリアとして機能し、n+層6をオーバーフロードレインとして機能させることができる。

10

#### 【0092】

以上の方法によれば、n+層6を、ゲート絶縁層20及び絶縁層9をマスクとしたセルファーラインによって形成するため、n+層6と電極7との合わせずれが発生する事がない。このため、コンタクトホールHの水平方向の幅を極力小さくすることが可能であり、画素を微細化する場合の障害とならなくなる。

#### 【0093】

又、コンタクトホールHのアスペクト比が厳しくなっても、電極7の材料としてタンゲステンを用いれば、電極7の埋め込みは可能であり、絶縁層9を厚くすることが可能である。

20

#### 【0094】

又、裏面照射型撮像素子100の場合、n層4上方に開口を設ける必要がないため、電極13の電荷転送チャネル12と重なる部分からn層4側にはみ出した部分の水平方向の長さを、水平方向に延ばすことが可能である。この部分を長くできれば、n層4から電荷転送チャネル12に電荷を読み出す際の読み出し電圧を低くすることができ、逆に、読み出し電圧を変えないのであれば、n層4の濃度を濃くして、飽和容量を大きくすることができるため好ましい。したがって、裏面照射型撮像素子100では、電極13の電荷転送チャネル12と重なる部分からn層4側にはみ出した部分の水平方向の長さを、水平方向に延ばすことが有効である。

30

#### 【0095】

このように考えた場合、図10に示した方法によれば、電極7の水平方向の幅を極力薄くできるため、電極13を延ばせる量を増やすことができ、読み出し電圧の低下、飽和容量の増加に非常に有効となる。

#### 【0096】

尚、n+層6は、イオン注入時に絶縁層9の影が発生しないように、コンタクトホールHから露出するp+層5の表面に対して垂直にイオン注入を行って形成するか、又は、コンタクトホールHから露出するp+層5の表面に対して少なくとも4方向から斜めにイオン注入を行って形成することが好ましい。

40

#### 【0097】

コンタクトホールHから露出するp+層5の表面に対して1方向のみから斜め（水平及び垂直以外）にイオン注入を行った場合、絶縁層9の影によって、n+層6とコンタクトホールHの位置がずれてしまうため、電極7とp+層5が接触し、ショートしてしまう危険がある。これに対し、垂直にイオン注入を行った場合や、少なくとも4方向から斜めにイオン注入を行った場合には、絶縁層9の影ができなくなるため、電極7とp+層5が接触してしまうのを防止することができる。少なくとも4方向から斜めにイオン注入を行った場合は、n+層6の大きさをコンタクトホールHよりも確実に大きくするため、より好ましい。

#### 【0098】

尚、垂直にイオン注入を行う場合は、イオン注入を低加速で行うことが好ましい。低加

50

速で行うことで、チャネリングの問題をほぼ無視することが可能となる。

【0099】

同様に、p+層24は、イオン注入時に絶縁層9の影が発生しないように、コンタクトホールHから露出するp+層5の表面に対して垂直にイオン注入を行って形成するか、又は、コンタクトホールHから露出するp+層5の表面に対して少なくとも4方向から斜めにイオン注入を行って形成することが好ましい。

【0100】

コンタクトホールHから露出するp+層5の表面に対して1方向のみから斜め（水平及び垂直以外）にイオン注入を行った場合、絶縁層9の影によって、p+層24の位置がずれてしまうため、p+層24をオーバーフローバリアとして機能させることができなくなってしまう。これに対し、垂直にイオン注入を行った場合や、少なくとも4方向から斜めにイオン注入を行った場合は、絶縁層9の影ができなくなるため、n+層6の下面を覆うようにp+層24を形成することができ、p+層24をオーバーフローバリアとして確実に機能させることができる。少なくとも4方向から斜めにイオン注入を行った場合は、p+層24の大きさをn+層6よりも確実に大きくすることができるため、より好ましい。

10

【0101】

次に、SOI基板のp基板30の汚染をゲッタリングする方法の一例を以下に列挙する。

- ・p基板30と絶縁層3との界面にゲッタリングサイトを形成し、絶縁層3側から酸素イオンのイオン打ち込みを行って絶縁層3内に汚染不純物を固着する。

20

- ・p基板30と絶縁層3との界面にゲッタリングサイトを形成する方法としては、この界面に絶縁層3側からフッ素や炭素を注入する方法がある。

- ・p基板30と絶縁層3との界面にゲッタリングサイトを形成し、その後、エッチング等で絶縁層3、ゲッタリングサイトまでを除去した後、低温酸化（ラジカル酸化等）を行って絶縁層3の代わりとなる絶縁層を形成する。

【0102】

次に、裏面照射型撮像素子100の構成や製造方法の変形例を以下に列挙する。

- ・遮光部材17を、特定のカラーフィルタ18については、そのカラーフィルタ18と高屈折率層16との間の全面に設けておく。このような構成により、特定のカラーフィルタ18を透過した光を検出する光電変換領域を、光学的黒レベルを検出するための光電変換領域とすることができる。特定のカラーフィルタ18の位置を、裏面照射型撮像素子100の周辺とすれば、通常の撮像素子と同様に、スマア補正や黒レベル補正が可能となる。又、この場合、カラーフィルタ層と絶縁層3との間に遮光部材17を設ける構成であるため、この製造が容易である。

30

- ・遮光部材17を、裏面照射型撮像素子100の周辺回路の下方にも設けておく。

- ・p++層2をp型のアモルファスSiCからなる層に変更し、絶縁層3をITO等の入射光に対して透明な透明電極とし、この透明電極に電圧を印加できる構成としておく。

- ・p基板1を複数の不純物拡散層で構成する場合には、各不純物拡散層を、プロセスを分けて形成する。

- ・p基板1を複数の不純物拡散層で構成する場合には、各不純物拡散層を、プロセスを分けて形成し、その後、アニール処理してポテンシャル段差を丸める。

40

- ・p基板1を複数の不純物拡散層で構成する場合には、各不純物拡散層を同一プロセスでガス雰囲気濃度をアナログ的に変化させながら形成する。

【0103】

（第二実施形態）

図1に示した裏面照射型撮像素子100では、n+層6の周りを取り囲むようにp+層5が形成されているが、p+層5は、少なくともオーバーフローバリアとして機能する層であれば良いため、n+層6とn層4との間にだけp+層5を形成した図11に示したような構成であっても良い。但し、この場合は、p層1表面とn層4との間にp+層6ではなくp層11が存在することになってしまい、この部分から暗電荷がn層4に移動してし

50

まうおそれがある。

【0104】

$n+$ 層6を水平方向に可能な限り大きくすれば、 $p$ 層11を経由した暗電荷の移動を抑制することは可能であるが、 $n+$ 層6をあまり大きくすると、素子分離が阻害されるため好ましくない。そこで本実施形態では、 $n+$ 層6は必要最小限の大きさ（電極7の底面積と同程度の大きさ）とし、 $n+$ 層6の周囲に、 $n+$ 層6によって形成される空乏層を水平方向に拡大するための $n+$ 層6よりも低濃度の $n$ 型不純物拡散層（ $n$ 層）40を設けた構成としている。このようにすることで、 $n$ 層40に移動した暗電荷を $n+$ 層6側へ移動させることができ、素子分離を阻害することなく、 $n$ 層4に移動する暗電荷量を減らすことができる。

10

【0105】

尚、 $n$ 層4に移動する暗電荷を効果的に減らすためには、 $n+$ 層6によって形成される空乏層が平面視において $n$ 層4の2/3以上を覆っていることが好ましい。

【0106】

第一実施形態及び第二実施形態では、裏面照射型撮像素子100がCCD型である場合を説明したが、裏面照射型撮像素子100はCMOS型であっても良い。即ち、 $p$ 層1表面に、 $n$ 層4に蓄積された電荷を信号に変換するCMOSトランジスタからなるCMOS回路を設けた構成であっても良い。CMOS型にする場合、 $n$ 層4から読み出した電荷を一時的に蓄積する電荷蓄積層を $n$ 層4の近傍に形成しておき、この電荷蓄積層に蓄積した電荷に応じた信号をCMOS回路によって出力させる構成にすることが好ましい。このようにすることで、グローバルな露光時間制御が可能となり、動作中の被写体が歪んだ像になるCMOS型イメージセンサ特有の欠点を無くすことができる。

20

【図面の簡単な説明】

【0107】

【図1】本発明の第一実施形態を説明するためのインターライン型の裏面照射型撮像素子の部分断面模式図

【図2】図1に示すB-B線の電位プロファイルを示す図

【図3】図1に示した $n$ 層4の平面図

【図4】図1に示した裏面照射型撮像素子の変形例を示す図

【図5】図1に示した裏面照射型撮像素子を備えた撮像装置の構成例を示すブロック図

30

【図6】図1に示した裏面照射型撮像素子のドレインに印加する電圧と $n$ 層4の飽和電荷量との関係を示した図

【図7】シミュレーションに用いた裏面照射型撮像素子の構成を示す図

【図8】 $p$ 基板の厚さとスミアとの関係を求めたシミュレーション結果を示す図

【図9】裏面照射型撮像素子に用いるSOI基板の製造工程を説明するための図

【図10】裏面照射型撮像素子の $n+$ 層6と電極7と電極8の形成方法を説明するための図

40

【図11】本発明の第二実施形態を説明するためのインターライン型の裏面照射型撮像素子の部分断面模式図

【符号の説明】

【0108】

1  $p$ 層

2  $p++$ 層

3, 9, 14 絶縁層

4  $n$ 層

5  $p+$ 層（オーバーフローバリア）

6  $n+$ 層（オーバーフロードレイン）

7, 8 電極

10 保護層

11  $p$ 層

50

- |     |                 |

|-----|-----------------|

| 1 2 | 電荷転送チャネル        |

| 1 3 | 電荷転送電極兼電荷読み出し電極 |

| 1 5 | 素子分離層           |

| 1 6 | 高屈折率透明層         |

| 1 7 | 遮光部材            |

| 1 8 | カラーフィルタ         |

| 1 9 | マイクロレンズ         |

| 2 0 | ゲート絶縁層          |

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 8 】

【 9 】

【 図 1 0 】

【 図 1 1 】