**(12) NACH DEM VERTRAG ÜBER DIE INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES PATENTWESENS (PCT) VERÖFFENTLICHTE INTERNATIONALE ANMELDUNG**

**(19) Weltorganisation für geistiges Eigentum**

Internationales Büro

**(43) Internationales Veröffentlichungsdatum**

**3. September 2009 (03.09.2009)**

**(10) Internationale Veröffentlichungsnummer**

**WO 2009/106038 A1**

**(51) Internationale Patentklassifikation:**

**H01L 33/00 (2006.01)**

[DE/DE]; Am Protzenweiher 21 b, 93059 Regensburg (DE). **HAHN, Berthold** [DE/DE]; Am Pfannenstiel 2, 93155 Hemau (DE).

**(21) Internationales Aktenzeichen:** PCT/DE2009/000192

**(74) Anwalt:** EPPING HERMANN FISCHER PATENT-ANWALTSGESELLSCHAFT MBH; Ridlerstrasse 55, 80339 München (DE).

**(22) Internationales Anmeldedatum:**

11. Februar 2009 (11.02.2009)

**(81) Bestimmungsstaaten** (soweit nicht anders angegeben, für jede verfügbare nationale Schutzrechtsart): AE, AG, AL,

**(25) Einreichungssprache:**

Deutsch

AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY,

**(26) Veröffentlichungssprache:**

Deutsch

BZ, CA, CH, CN, CO, CR, CU, CZ, DK, DM, DO, DZ,

**(30) Angaben zur Priorität:**

10 2008 011 847.8

EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN,

29. Februar 2008 (29.02.2008)

HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR,

10 2008 027 045.8 6. Juni 2008 (06.06.2008)

DE

DE

KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME,

**(71) Anmelder** (für alle Bestimmungsstaaten mit Ausnahme von US): OSRAM OPTO SEMICONDUCTORS

MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO,

GMBH [DE/DE]; Leibnizstrasse 4, 93055 Regensburg (DE).

NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG,

STRASSBURG, Martin [DE/DE]; Lutherstrasse 1,

SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA,

93105 Tegernheim (DE). SABATHIL, Matthias

UG, US, UZ, VC, VN, ZA, ZM, ZW.

**(72) Erfinder; und**

**(84) Bestimmungsstaaten** (soweit nicht anders angegeben, für jede verfügbare regionale Schutzrechtsart): ARIPO (BW,

**(75) Erfinder/Anmelder (nur für US): AHLSTEDT, Magnus**

GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG,

[SE/DE]; Theodor-Koerner-Strasse 12, 93049 Regensburg (DE). BAUR, Johannes [DE/DE]; Burgfriedenweg

ZM, ZW), eurasisches (AM, AZ, BY, KG, KZ, MD, RU,

32, 93051 Regensburg (DE). ZEHNDER, Ulrich

TJ, TM), europäisches (AT, BE, BG, CH, CY, CZ, DE,

[DE/DE]; Aumbach 311, 93191 Rettenbach (DE).

DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT,

STRASSBURG, Martin [DE/DE]; Lutherstrasse 1,

LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI,

93105 Tegernheim (DE). SABATHIL, Matthias

UG, US, UZ, VC, VN, ZA, ZM, ZW.

*[Fortsetzung auf der nächsten Seite]*

**(54) Title:** SEMICONDUCTOR LIGHT-EMITTING DIODE AND METHOD FOR PRODUCING A SEMICONDUCTOR LIGHT-EMITTING DIODE

**(54) Bezeichnung:** HALBLEITERLEUCHTDIODE UND VERFAHREN ZUR HERSTELLUNG EINER HALBLEITERLEUCHTDIODE

**FIG 2**

**(57) Abstract:** A semiconductor light-emitting diode (10) is proposed, comprising at least one p-doped light-emitting diode layer (4), an n-doped light-emitting diode layer (2), and an optically active zone (3) between the p-doped light-emitting diode layer (4) and the n-doped light-emitting diode layer (2), comprising an oxide layer (8) made of transparent conductive oxide, and at least one mirror layer (9), wherein the oxide layer (8) is disposed between the light-emitting diode layers (2, 4) and the at least one mirror layer (9) and has a first interface (8a), which faces the light-emitting diode layers (2, 4), and a second interface (8b), which faces the at least one mirror layer (9), and wherein the second interface (8b) of the oxide layer (8) has lower roughness (R2) than the first interface (8a) of the oxide layer (8).

**(57) Zusammenfassung:** Es wird eine Halbleiterleuchtdiode (10) vorgeschlagen

*[Fortsetzung auf der nächsten Seite]*

SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ,

GW, ML, MR, NE, SN, TD, TG).

**Veröffentlicht:**

— *mit internationalem Recherchenbericht (Artikel 21 Absatz

3)*

---

mit zumindest einer p-dotierten Leuchtdiodenschicht (4), einer n-dotierten Leuchtdiodenschicht (2) sowie einer optisch aktiven Zone (3) zwischen der p-dotierten Leuchtdiodenschicht (4) und der n-dotierten Leuchtdiodenschicht (2), mit einer Oxidschicht (8) aus einem transparenten leitfähigen Oxid und mit mindestens einer Spiegelschicht (9), wobei die Oxidschicht (8) zwischen den Leuchtdiodenschichten (2, 4) und der mindestens einen Spiegelschicht (9) angeordnet ist und eine erste Grenzfläche (8a), die den Leuchtdiodenschichten (2, 4) zugewandt ist, sowie eine zweite Grenzfläche (8b), die der mindestens einen Spiegelschicht (9) zugewandt ist, aufweist und wobei die zweite Grenzfläche (8b) der Oxidschicht (8) eine geringere Rauhigkeit (R2) besitzt als die erste Grenzfläche (8a) der Oxidschicht (8).

## Beschreibung

Halbleiterleuchtdiode und Verfahren zur Herstellung einer Halbleiterleuchtdiode

5

Die Erfinung betrifft eine Halbleiterleuchtdiode und ein Verfahren zum Herstellen einer Halbleiterleuchtdiode.

Diese Patentanmeldung beansprucht die Prioritäten der deutschen Patentanmeldung 10 2008 011 847.8 und der deutschen Patentanmeldung 10 2008 027 045.8, deren Offenbarungsgehalte hiermit durch Rückbezug aufgenommen werden.

Halbleiterleuchtdioden besitzen einen Schichtenstapel aus Halbleiterschichten, deren Materialien (hinsichtlich Grundmaterial und Dotierstoff) gezielt ausgewählt und aufeinander abgestimmt sind, um die optoelektronischen Eigenschaften und die elektronische Bandstruktur innerhalb der einzelnen Schichten und an den Schichtgrenzen in vorbestimmtem Ausmaß einzustellen. Am Übergang zwischen zwei benachbarten, zueinander komplementär dotierten Leuchtdiodenschichten (p- und n-dotiert) entsteht eine optisch aktive Zone, die beim Stromfluss durch den Halbleiterschichtenstapel elektromagnetische Strahlung emittiert. Die erzeugte Strahlung wird zunächst in alle Richtungen, d.h. nur teilweise in Abstrahlungsrichtung der Halbleiterleuchtdiode emittiert. Um denjenigen Anteil der Strahlung, der zur entgegengesetzten Seite des Halbleiterschichtenstapels emittiert wird, wieder zurück in Abstrahlungsrichtung zu reflektieren, sind hinter dem Halbleiterschichtenstapel eine Oxidschicht aus einem transparenten leitfähigen Oxid und eine oder mehrere Spiegelschichten vorgesehen. Die auf die Spiegelschichten auftreffende elektromagnetische Strahlung wird zu einem Anteil reflektiert, der

- von der Differenz der optischen Brechungsindizes der Schichten, von der Leitfähigkeit der Spiegelschicht, von der Transparenz der Oxidschicht sowie von der Dicke der Oxidschicht und der ihr vorgelagerten Schichten zur optisch aktischen Zone hin abhängt. Zur Steigerung des reflektierten Anteils werden herkömmlich neben den Schichtdicken vor allem die Materialeigenschaften und Materialzusammensetzungen der jeweiligen Schichten verändert und optimiert.

- Wenn sich der Anteil der auf die Spiegelschicht auftreffenden elektromagnetischen Strahlung, der durch die Spiegelschicht wieder zurück reflektiert wird, vergrößern ließe, könnte die Lichtausbeute von Halbleiterleuchtdioden erhöht werden.

- Dies wird durch eine Halbleiterleuchtdiode gemäß einem der Ansprüche 1 und 2 sowie durch ein Verfahren gemäß Anspruch 14 ermöglicht.

Es wird eine Halbleiterleuchtdiode mit zumindest einer p-dotierten Leuchtdiodenschicht, einer n-dotierten Leuchtdiodenschicht und einer optisch aktiven Zone zwischen der p-dotierten Leuchtdiodenschicht und der n-dotierten Leuchtdiodenschicht, mit einer Oxidschicht aus einem transparenten leitfähigen Oxid und mit mindestens einer Spiegelschicht bereitgestellt, wobei die Oxidschicht zwischen den Leuchtdiodenschichten und der mindestens einen Spiegelschicht angeordnet ist und eine erste Grenzfläche, die den Leuchtdiodenschichten zugewandt ist, und eine zweite Grenzfläche, die der mindestens einen Spiegelschicht zugewandt ist, aufweist und wobei die zweite Grenzfläche der Oxidschicht eine geringere Rauhigkeit besitzt als die erste Grenzfläche der Oxidschicht.

Ferner wird eine Halbleiterleuchtdiode bereitgestellt, bei der die zweite Grenzfläche der Oxidschicht eine Rauigkeit besitzt, die kleiner ist als 1,0 nm.

- 5 Durch das Ausbilden der Spiegelschicht auf der zweiten Grenzfläche verringter Rauigkeit erhöht sich der Reflexionsgrad an der Grenzfläche zwischen Oxidschicht und Spiegelschicht, wobei vor allem die unter großen Einfallswinkeln auftreffenden Strahlungsanteile in einem größeren Ausmaß reflektiert

10 werden.

Wird die Oxidschicht mit einer Schichtdicke von mehr als 5 nm vorgesehen, so ist gewährleistet, dass Unebenheiten der ersten Grenzfläche der Oxidschicht, die durch die Rauigkeit der 15 darunterliegenden obersten Halbleiterschicht bedingt sind, nivelliert werden und daher die Rauigkeit der zweiten Grenzfläche der Oxidschicht nicht nachteilig beeinflussen.

Ist die p-dotierte Leuchtdiodenschicht näher an der Oxidschicht angeordnet als die n-dotierte Leuchtdiodenschicht, so befinden sich die Oxidschicht und die Spiegelschicht auf der p-Seite der Halbleiterleuchtdiode. Dort bringt das Anschließen der Oxidschicht zwar zunächst eine Erhöhung der Betriebsspannung der Halbleiterleuchtdiode mit sich, die sich jedoch 25 wie noch nachstehend beschrieben kompensieren lässt.

Gemäß einer Weiterbildung ist zwischen der p-dotierten Leuchtdiodenschicht und der Oxidschicht eine p-dotierte Halbleiterschicht angeordnet, die eine Dotierstoffkonzentration 30 besitzt, die mindestens so groß ist wie die Dotierstoffkonzentration der p-dotierten Leuchtdiodenschicht. Die p-dotierte Halbleiterschicht schützt die p-dotierte Leuchtdio-

denschicht vor Kristallgitterschäden beim Abscheiden der O-

xidschicht.

Gemäß einer ersten Ausführungsform grenzt die erste Grenzflä-

5 che der Oxidschicht an die p-dotierte Halbleiterschicht an.

Gemäß einer alternativen zweiten Ausführungsform ist vorgese-

hen sein, dass zwischen der p-dotierten Halbleiterschicht und

der Oxidschicht eine n-dotierte Halbleiterschicht angeordnet

10 ist und dass die Oxidschicht an die n-dotierte Halbleiter-

schicht angrenzt. Dadurch wird ein niederohmiger Anschluss

der Oxidschicht an den Halbleiterschichtenstapel erreicht.

Gemäß einer Weiterbildung ist zwischen der p-dotierten Halb-

15 leiterschicht und der n-dotierten Halbleiterschicht eine un-

dotierte Halbleiterschicht vorgesehen. Diese bildet gemeinsam

mit den beiden dotierten Halbleiterschichten einen Tunnelkon-

takt, wobei der Kontaktwiderstand des Tunnelkontakte durch

das niederohmige Anschließen der Oxidschicht über die n-

20 dotierte Halbleiterschicht mehr als kompensiert wird und die

erforderliche Betriebsspannung daher insgesamt verringert

wird.

Vorzugsweise ist die Oxidschicht elektrisch leitfähig.

25 Geeignete Materialien für die Oxidschicht sind beispielsweise Zinkoxid, Indiumzinnoxid oder Indiumzinkoxid.

Sofern die Spiegelschicht unmittelbar an die zweite Grenzflä-

30 che der Oxidschicht angrenzt, bildet die zweite Grenzfläche

der Oxidschicht zugleich eine Spiegelfläche besonders gerin-

ger Rauhigkeit.

Die Spiegelschicht umfasst gemäß einer Ausführungsform mindestens eine metallische Spiegelschicht.

Geeignete Materialien für die metallische Spiegelschicht sind

5 insbesondere Gold, Silber oder Aluminium, wobei sich Gold zur Reflexion im Infrarotbereich, Silber zur Reflexion im sichtbaren Wellenlängenbereich und Aluminium zur Reflexion im UV-Bereich eignet.

10 Gemäß einer weiteren Ausführungsform ist - alternativ oder zusätzlich zur metallischen Spiegelschicht – mindestens eine dielektrische Spiegelschicht vorgesehen. Insbesondere in Kombination mit der metallischen Spiegelschicht erhöht die dielektrische Spiegelschicht den Reflexionsgrad des Spiegels

15 auf der Rückseite der Halbleiterleuchtdiode.

Geeignete Materialien für die dielektrische Spiegelschicht sind beispielsweise Glas, Siliziumoxid, Siliziumnitrid oder Siliziumoxinitrid.

20 Gemäß einer Weiterbildung ist vorgesehen, dass die dielektrische Spiegelschicht zwischen der Oxidschicht und der metallischen Spiegelschicht angeordnet ist und lokale Ausnehmungen aufweist, in denen die metallische Spiegelschicht bis an die

25 zweite Grenzfläche der Oxidschicht heranreicht. Dadurch bildet die metallische Spiegelschicht Kontakte zur transparenten leitfähigen Oxidschicht, von denen ausgehend in der Oxidschicht eine laterale Stromaufweitung über die gesamte Grundfläche des Halbleiterschichtenstapels erfolgt.

30 Als Grundmaterial für die Leuchtdiodenschichten eignen sich etwa binäre, ternäre oder quaternäre III-V-Halbleitermaterialien, insbesondere solche, die zumindest eines der Elemente

Aluminium, Gallium und Indium und zumindest eines der Elemente Stickstoff, Phosphor und Arsen enthalten. Beispiele hierfür sind Aluminiumnitrid, Aluminiumindiumnitrid, Galliumnitrid, Aluminiumgalliumnitrid, Indiumgalliumnitrid sowie Indiumgalliumarsenidphosphid.

Das Verfahren zum Herstellen der Halbleiterleuchtdiode umfasst

- das Ausbilden zumindest einer p-dotierten Leuchtdiodenschicht und einer n-dotierten Leuchtdiodenschicht,

- das Abscheiden eines transparenten leitfähigen Oxsids, wodurch eine Oxidschicht gebildet wird, die eine erste Grenzfläche aufweist, die den Leuchtdiodenschichten zugewandt ist, wobei die Oxidschicht durch HF-unterstütztes DC-Sputtern abgeschieden wird und dabei eine zur ersten Grenzfläche entgegengesetzte zweite Grenzfläche der Oxidschicht erzeugt wird, die eine geringere Rauhigkeit besitzt als die erste Grenzfläche der Oxidschicht, und

- das Ausbilden mindestens einer Spiegelschicht oberhalb der zweiten Grenzfläche der Oxidschicht.

Dadurch, dass die Oxidschicht aus dem transparenten leitfähigen Oxd durch HF-unterstütztes DC-Sputtern abgeschieden wird, besitzt ihre zweite Grenzfläche eine Rauhigkeit, die kleiner ist als die Rauhigkeit ihrer ersten Grenzfläche und insbesondere kleiner ist als 1,0 nm. Dies führt bei der fertigen Halbleiterleuchtdiode zu einer stärkeren Reflexion bzw. Spiegelwirkung an der Grenzfläche zwischen der Oxidschicht und der Spiegelschicht.

Wird die Oxidschicht mit einer Schichtdicke von mindestens 5 nm abgeschieden, so werden dadurch Unebenheiten der ersten Grenzfläche der Oxidschicht, die durch die Rauhigkeit der da-

runterliegenden obersten Halbleiterschicht bedingt sind, ni-

velliert und können die Rauigkeit der zweiten Grenzfläche

der Oxidschicht nicht nachteilig beeinflussen.

- 5 Gemäß einer Weiterbildung wird auf die p-dotierte Leuchtdio-

denschicht eine p-dotierte Halbleiterschicht abgeschieden,

deren Dotierstoffkonzentration mindestens so groß ist wie die

Dotierstoffkonzentration der p-dotierten Leuchtdiodenschicht.

Die p-dotierte Halbleiterschicht schützt die p-dotierte

10 Leuchtdiodenschicht vor Kristallgitterschäden beim Aufsput-

tern der Oxidschicht.

Werden ferner über der p-dotierten Halbleiterschicht eine un-

dotierte Halbleiterschicht sowie eine n-dotierte Halbleiter-

15 schicht abgeschieden und wird die Oxidschicht auf die n-

dotierte Halbleiterschicht aufgesputtert, so entsteht ein

niederohmiger Anschluss der Oxidschicht über die n-dotierte

Halbleiterschicht; die p-dotierte, die undotierte und die n-

dotierte Halbleiterschicht bilden dabei einen Tunnelkontakt,

20 dessen Kontaktwiderstand durch den niederohmigen Anschluss

der Oxidschicht an die n-dotierte Halbleiterschicht mehr als

kompensiert wird.

Gemäß einer Weiterbildung umfasst das Ausbilden der Spiegel-

25 schicht das Abscheiden mindestens einer dielektrischen Spie-

gelschicht, das Ätzen von Ausnehmungen in die dielektrische

Spiegelschicht und das Abscheiden mindestens einer metalli-

schen Spiegelschicht auf die dielektrische Spiegelschicht;

dadurch bildet die metallische Spiegelschicht in den Ausneh-

30 mungen der dielektrischen Spiegelschicht Kontakte zur Oxid-

schicht, von denen ausgehend in der Oxidschicht die laterale

Stromaufweitung über die gesamte Grundfläche des Halbleiter-

schichtenstapels erfolgt.

Nachstehend werden einige Ausführungsbeispiele der Erfindung mit Bezug auf die Figuren beschrieben. Es zeigen:

5 Figur 1 ein erstes Ausführungsbeispiel einer Halbleiterleuchtdiode,

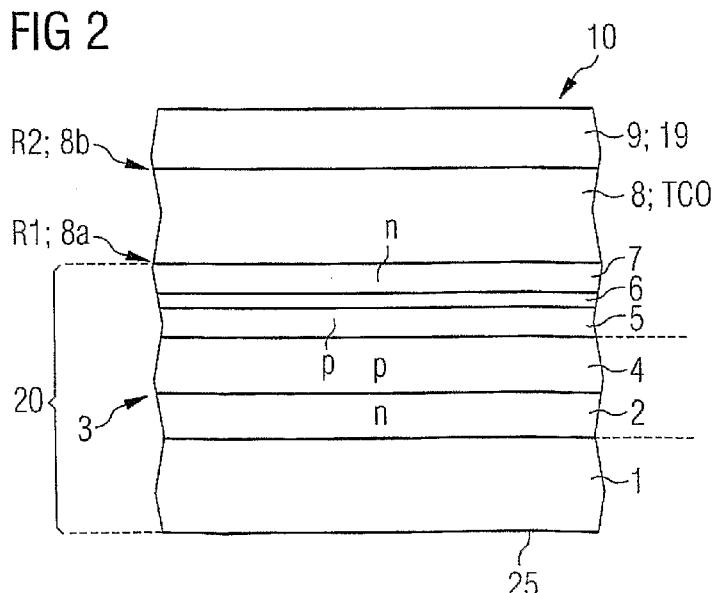

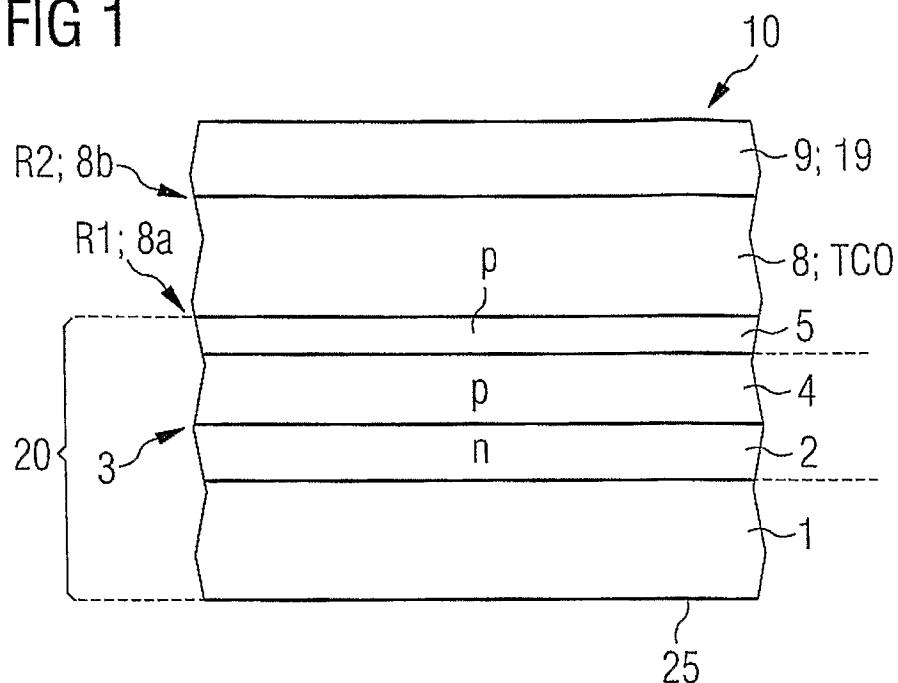

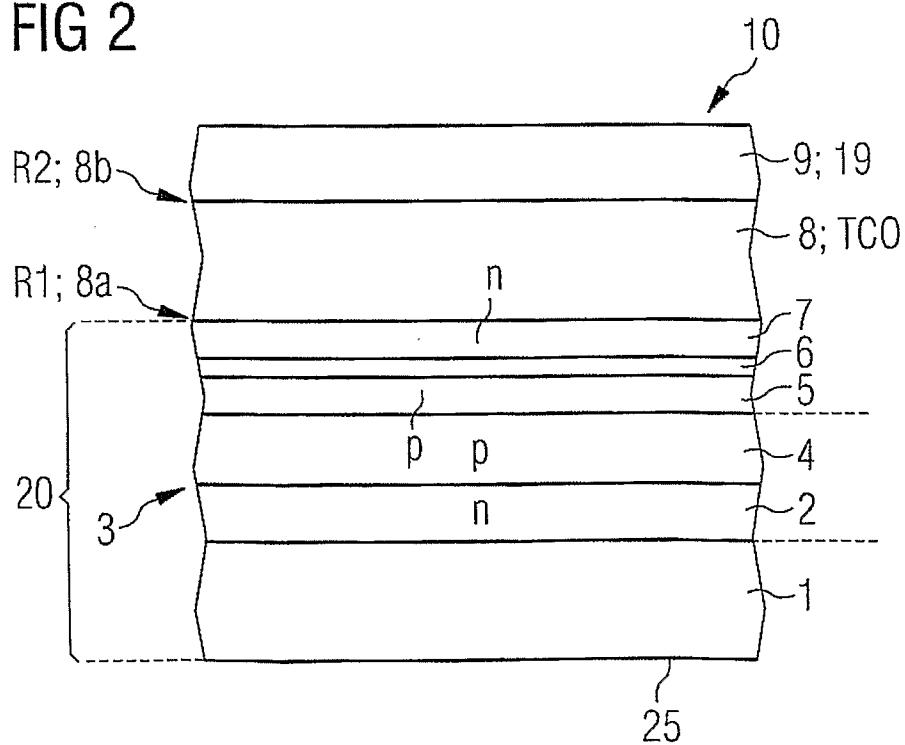

Figur 2 ein zweites Ausführungsbeispiel einer Halbleiterleuchtdiode,

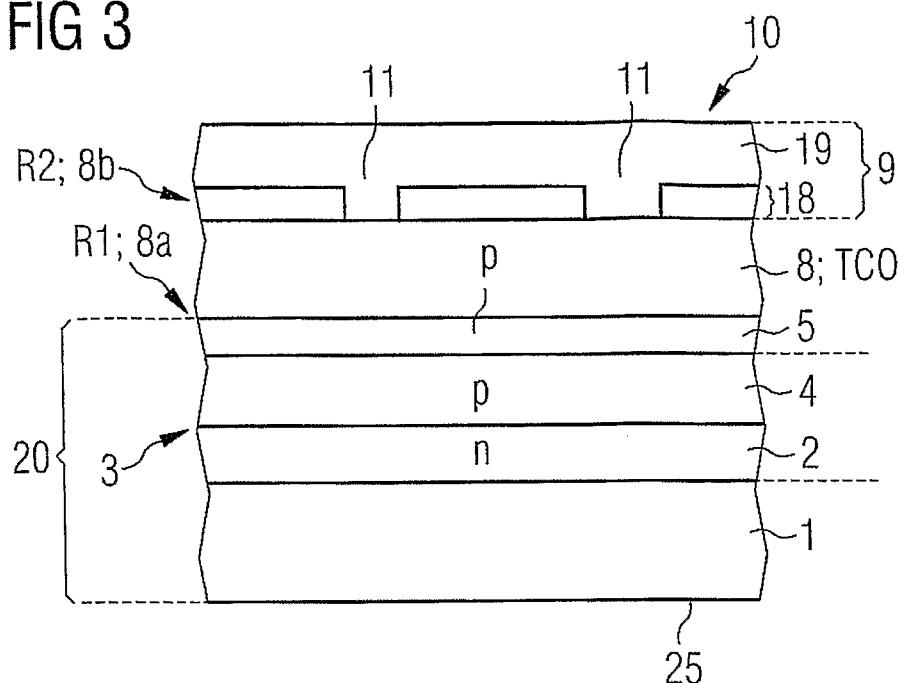

10 Figur 3 ein drittes Ausführungsbeispiel einer Halbleiterleuchtdiode mit mehreren Spiegelschichten,

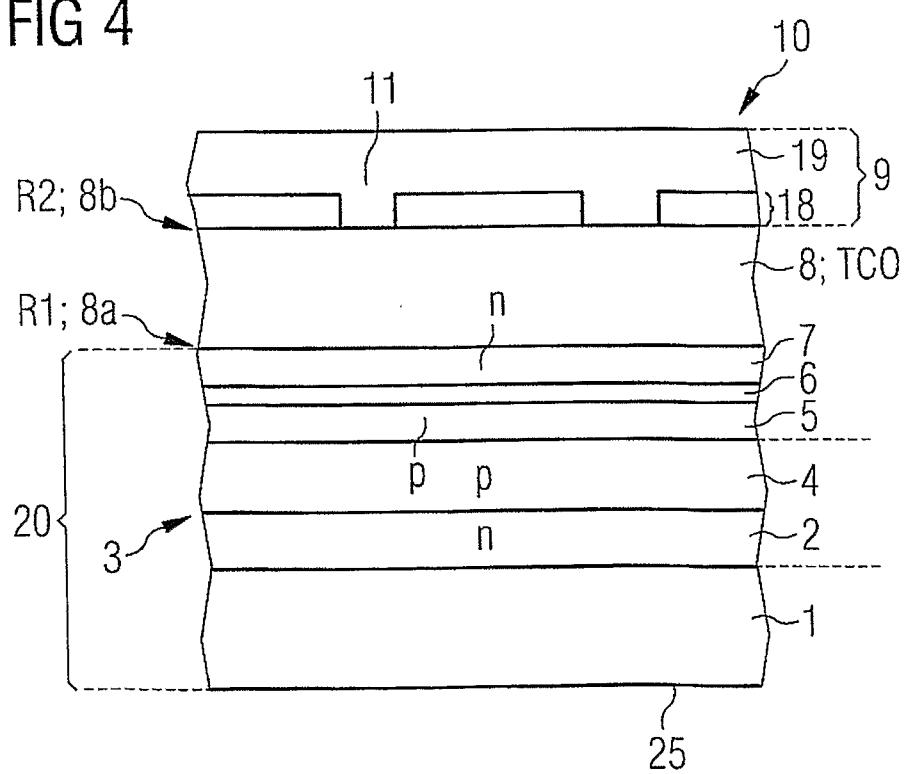

Figur 4 ein vierter Ausführungsbeispiel einer Halbleiterleuchtdiode mit mehreren Spiegelschichten und

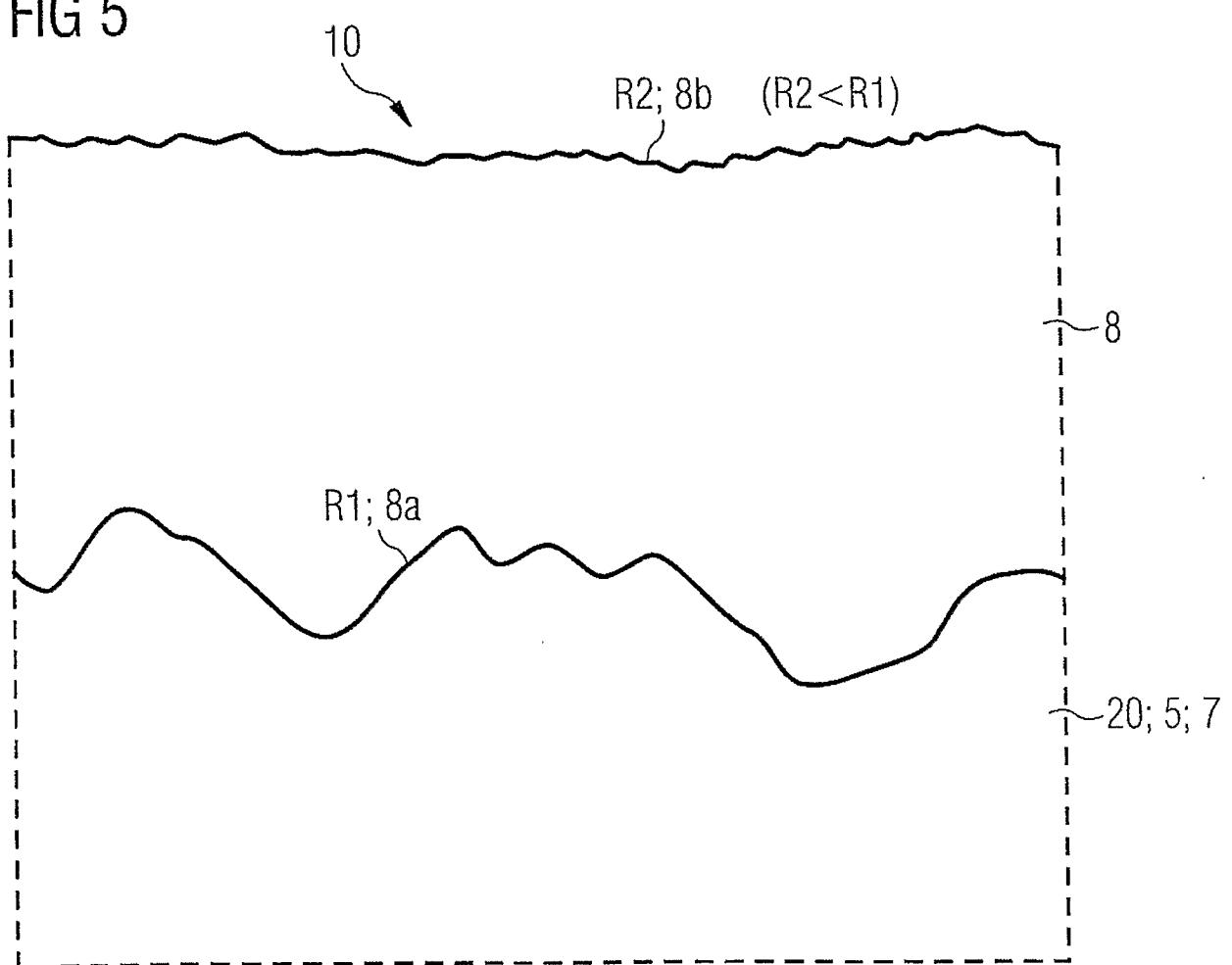

15 Figur 5 eine vergrößerte schematische Detailansicht eines vorläufigen Halbleiterprodukts während der Herstellung einer Halbleiterleuchtdiode gemäß einer der Figuren 1 bis 4.

20 Figur 1 zeigt in Querschnittsansicht ein erstes Ausführungsbeispiel einer Halbleiterleuchtdiode 10, die einen Halbleiterschichtenstapel 20 aufweist. Die erzeugte elektromagnetische Strahlung, die im sichtbaren Bereich, im Infrarot-Bereich oder im UV-Bereich liegt, wird zwar zunächst in alle Richtungen emittiert, soll jedoch möglichst vollständig durch eine Strahlungsaustrittsfläche 25 einer Strahlungsaustrittsschicht 1 (unten in Figur 1) abgestrahlt werden, die auf derjenigen Seite des Halbleiterschichtenstapels angeordnet ist, 25 die von der Oxidschicht und der Spiegelschicht abgewandt ist. Die Strahlungsaustrittsschicht 1 ist entweder eine Substratschicht, die zurückbleibt, nachdem sämtliche Schichten auf das Substrat aufgewachsen wurden und das Substrat nahezu

vollständig rückgeätzt wurde (Dünnfilm-LED), oder eine Halbleiterschicht, die vor den eigentlichen Leuchtdiodenschichten auf das Substrat aufgewachsen wurde, wobei das Substrat später vollständig entfernt wurde.

5

Auf die Strahlungsaustrittsschicht 1 werden die weiteren Schichten wie folgt aufgewachsen: Zunächst werden eine n-dotierte Leuchtdiodenschicht 2 und eine p-dotierte Leuchtdiodenschicht 4 abgeschieden. Die entgegengesetzt zueinander dotierten Leuchtdiodenschichten 2, 4 bilden eine Leuchtdiodenschichtenfolge, wie in Figur 1 durch gestrichelte Linien hervorgehoben. An der Grenzfläche zwischen beiden Halbleiterschichten 2, 4 entsteht eine optisch aktive Zone 3, die bei ausreichender Vorspannung geeigneter Polung an den Leuchtdiodenschichten 2, 4 eine Emission elektromagnetischer Strahlung bewirkt. Die n-dotierte Leuchtdiodenschicht 2 ist hier mit Silizium und die p-dotierte Leuchtdiodenschicht 4 mit Magnesium dotiert, wobei das Grundmaterial der Leuchtdiodenschichten 2, 4 jeweils ein III-V-Halbleitermaterial ist. Die Strahlungsaustrittsschicht 1 dient zum Schutz und zur elektrischen Isolierung der unteren, n-dotierten Leuchtdiodenschicht 2.

Auf derjenigen Seite der Leuchtdiodenschichtenfolge, auf der die p-dotierte Leuchtdiodenschicht 4 angeordnet ist (d. h. in Figur 1 oben), wird eine Oxidschicht 8 aus einem transparenten leitfähigen Oxid abgeschieden. Insbesondere enthält die Oxidschicht 8 ein transparentes elektrisch leitfähiges Oxid.

Die Oxidschicht dient zur Stromaufweitung in lateraler Richtung parallel zu den Schichtgrenzen sowie zur Vermeidung unerwünschter Migration zwischen der Spiegelschicht und dem Halbleiterschichtenstapel. Figur 1 zeigt ein Ausführungsbeispiel, bei dem die Oxidschicht 8 nicht unmittelbar auf die p-

dotierte Leuchtdiodenschicht 4 abgeschieden wird, sondern (zum Schutz der p-dotierten Leuchtdiodenschicht 4) zuerst eine p-dotierte Halbleiterschicht 5 abgeschieden wird, deren Dotierstoffkonzentration mindestens so groß ist wie diejenige 5 der p-dotierten Leuchtdiodenschicht 4.

Auf die p-dotierte Halbleiterschicht 5 wird dann die Oxidschicht 8 aus einem transparenten leitfähigen Oxid (TCO; transparent conductive oxide) abgeschieden. Dabei gibt die 10 Rauhigkeit der Oberseite der p-dotierte Halbleiterschicht 5 die Rauhigkeit R1 der ersten Grenzfläche 8a der Oxidschicht 8 vor. Als erste Grenzfläche der Oxidschicht wird hier diejenige Grenzfläche bezeichnet, die dem Halbleiterschichtenstapel zugewandt ist (und insbesondere an die oberste, zuletzt abgeschiedene Halbleiterschicht des Schichtenstapels unmittelbar 15 angrenzt).

Als transparentes leitfähiges Oxid eignet sich etwa Indiumzinnoxid, Indiumzinkoxid oder Zinkoxid. Im Falle von Zinkoxid 20 kann die Leitfähigkeit durch eine Dotierung mit Aluminium oder Gallium erhöht werden. Ferner kann anstelle einer einzigen Oxidschicht auch eine Schichtenfolge mehrerer Oxidschichten vorgesehen sein.

25 Die Abscheidung der Oxidschicht erfolgt durch HF-unterstütztes DC-Sputtern; dadurch erhält sie eine obere, zweite Grenzfläche 8b, die eine besonders geringe Rauhigkeit R2 besitzt. Nach dem Aufsputtern der Oxidschicht 8 liegt ihre zweite 30 Grenzfläche 8b zunächst frei; auf ihr wird gemäß Figur 1 schließlich die Spiegelschicht 9 (insbesondere eine metallische Spiegelschicht 19) abgeschieden.

Die Grenzflächen zwischen den jeweiligen Schichten des Halbleiterschichtenstapels sowie zwischen dem Halbleiterschichtenstapel, der Oxidschicht und der Spiegelschicht besitzen stets eine gewisse Rauigkeit. Die Rauigkeit wird meist als 5 numerische Angabe (etwa in nm) mit dem Zusatz 'Rms' angegeben ('root means squared'; Wurzel aus der mittleren quadratischen Abweichung von der idealisierten Grenzflächenebene, d.h. Standardabweichung der Höhenschwankung der Grenzfläche oder Oberfläche). Die Mittelung erfolgt dabei über einen Flächen-10 bereich der jeweiligen Oberfläche bzw. Grenzfläche. Die Rauigkeit von Grenzflächen innerhalb der Schichtenfolge für die Halbleiterleuchtdiode 10 liegt herkömmlich günstigstenfalls zwischen 1,5 und 5 nm, kann jedoch auch wesentlich größer sein und mehr als 20 nm betragen. Zur Rauigkeit tragen insbesondere Abweichungen vom idealen Kristallgitter bei, beispielsweise lokal variierende Wachstumsbedingungen oder Gitterverzerrungen, auch als Folge von Dotierstoffen.

Bei der Herstellung einer Halbleiterleuchtdiode werden herkömmlich die Materialien und Materialkombinationen der jeweiligen Schichten (samt Dotierstoffen) optimiert und aufeinander abgestimmt. Ferner werden Schichtdicken und Brechungsindizes der Schichten optimiert, um eine konstruktive Interferenz der an den Grenzflächen reflektierten elektromagnetischen Strahlung und damit eine große Helligkeit der Leuchtdiode zu erzielen. Der Einfluss rauigkeitsbedingter Höhenschwankungen der Schichtgrenzen, die um zwei bis drei Größenordnungen (entsprechend einem Faktor von 100 bis 1000) kleiner sind als die Wellenlänge der zu reflektierenden Strahlung, wird hingegen meist vernachlässigt.

Herkömmlich besitzt die zweite Grenzfläche der Oxidschicht, welche dem Halbleiterschichtenstapel abgewandt, d.h. der

Spiegelschicht zugewandt ist, eine noch größere Rauigkeit als die erste Grenzfläche der Oxidschicht, da das transparente leitfähige Oxid in der Regel nicht einkristallin, sondern polykristallin oder amorph aufwächst.

5

Das Abscheiden der Oxidschicht 8 durch einen HF-unterstützten DC-Sputterprozess wie hier vorgeschlagen bewirkt hingegen eine besonders geringe Rauigkeit R<sub>2</sub> der zweiten Grenzfläche 8b der Oxidschicht und erhöht so das Reflexionsvermögen der dar-

10 auf abzuscheidenden Spiegelschicht. Auf den HF-unterstützten DC-Sputterprozess wird noch mit Bezug auf Figur 5 eingegan-

gen.

Die Spiegelschicht 9 wird auf die (nach Durchführung des

15 Sputterprozesses freiliegende) zweite Grenzfläche 8b der O-

xidschicht 8 abgeschieden. Die Abscheidung der Spiegelschicht 9 erfolgt durch ein PVD- (physical vapour deposition) oder

ein CVD-Verfahren (chemical vapour deposition), insbesondere

ein PECVD-Verfahren (plasma enhanced chemical vapour deposi-

20 tion), durch ein MBE-Verfahren (molecular beam epitaxy), ein

IBE-Verfahren (ion beam etching) oder durch thermisches Ver-

dampfen. Die Spiegelschicht 9 ist bei diesem Ausführungsbei-

spiel eine metallische Spiegelschicht 19, die aus Gold, Sil-

ber oder Aluminium oder einer Legierung, die mindestens eines

25 dieser Metalle enthält, besteht. Die metallische Spiegel-

schicht 19 kann auch mehrere Schichten aus jeweils einem Me-

tall oder einer Metalllegierung umfassen.

Die Materialien und Schichtdicken der Oxidschicht 8 und der

30 Spiegelschicht 9 sind so aufeinander abgestimmt, dass derje-

nige Anteil der von der optisch aktiven Zone 3 emittierten

elektromagnetischen Strahlung, der in Richtung der Oxid-

schicht und der Spiegelschicht emittiert wird, an der zweiten

Grenzfläche 8b der Oxidschicht 8 möglichst vollständig reflektiert wird. Der Einfallswinkel der zu reflektierenden Strahlung unterliegt einer statistischen Verteilung und kann grundsätzlich jeden Wert zwischen 0 Grad und 90 Grad relativ 5 zur Flächennormalen der reflektierenden Grenzfläche der Spiegelschicht annehmen. Die geringe Rauigkeit der zweiten Grenzfläche 8b der Oxidschicht 8 hat zur Folge, dass auch bei großen Einfallwinkeln relativ zur Flächennormalen der zweiten Grenzfläche 8b insgesamt ein größerer Anteil der auftreffenden elektromagnetischen Strahlung reflektiert wird. Durch 10 wird die Intensität der durch die Halbleiterleuchtdiode abgestrahlten elektromagnetischen Strahlung erhöht.

Figur 2 zeigt ein zweites Ausführungsbeispiel einer Halbleiterleuchtdiode, bei dem zusätzlich zu den in Figur 1 dargestellten Schichten noch eine undotierte Halbleiterschicht 6 sowie eine n-dotierte Halbleiterschicht 7 vorgesehen sind, die zwischen der p-dotierten Halbleiterschicht 5 und der Oxidschicht 8 angeordnet sind. Die n-dotierte Halbleiterschicht 7 erleichtert das Anschließen der Oxidschicht 8 aus dem transparenten leitfähigen Oxid an den Halbleiterschichtstapel 20. Die undotierte Halbleiterschicht 6 ist zwischen der p-dotierten Halbleiterschicht 5 und der n-dotierten Halbleiterschicht 7 angeordnet. Die Folge der Halbleiterschichten 20 5, 6 und 7 bildet einen Tunnelkontakt zur eigentlichen Leuchtdiodenschichtenfolge aus den Leuchtdiodenschichten 4 und 2. Eine geringfügige Erhöhung der Betriebsspannung durch den Tunnelkontakt wird durch den niederohmigen Anschluss der Oxidschicht 8 über die n-dotierte Halbleiterschicht 7 mehr 25 als kompensiert.

Für die Schichten 5, 6 und 7 eignen sich dieselben Grundmaterialien wie für die Leuchtdiodenschichten 2, 4. Die Schicht-

dicke der dotierten Halbleiterschichten 5, 7 ist bei diesem Ausführungsbeispiel kleiner als 30 nm; sie liegt beispielsweise zwischen 3 und 20 nm. Ferner ist die Schichtdicke der undotierten Halbleiterschicht 6 bei diesem Ausführungsbeispiel kleiner als 20 nm; sie liegt beispielsweise zwischen 1 und 10 nm. Im übrigen gelten für Figur 2 dieselben Ausführungen wie für Figur 1.

Die in den Figuren 1 und 2 dargestellten Schichten des Halbleiterschichtenstapels 20 werden beispielsweise durch ein chemisches Gasphasenabscheidungsverfahren (CVD; chemical vapour deposition) abgeschieden, bevor auf den Halbleiterschichtenstapel 20 die Oxidschicht 8 und darauf die Spiegelschicht 9 abgeschieden wird. Auf der Unterseite des Halbleiterschichtenstapels 20 wird das Substrat nachträglich gedünnt oder vollständig entfernt, sodass die Strahlungsaustrittsschicht 1 freiliegt.

Während die Figuren 1 und 2 Ausführungsbeispiele zeigen, bei denen die Oxidschicht 8 unmittelbar an die Unterseite einer metallischen Spiegelschicht 19 angrenzt, zeigen die Figuren 3 und 4 Ausführungsbeispiele mit einer zusätzlichen dielektrischen Spiegelschicht 18 zwischen der Oxidschicht 8 und der metallischen Spiegelschicht 19. In Figur 3 besitzt der Halbleiterschichtenstapel 20 denselben Aufbau wie in Figur 1; in Figur 4 besitzt er denselben Aufbau wie in Figur 2. Die Erklärungen zu Figur 1 bzw. 2 gelten daher ebenso für Figur 3 bzw. 4.

Gemäß Figur 3 bzw. 4 wird auf die jeweils oberste Halbleiterschicht 5 bzw. 7 die Oxidschicht 8 durch HF-unterstütztes DC-Sputtern abgeschieden. Auf deren zweite Grenzfläche 8b wird dann zunächst eine dielektrische Spiegelschicht 18 (bei-

spielsweise aus Siliziumoxid) abgeschieden. In die dielektrische Spiegelschicht 18 werden dann Ausnehmungen 11 geätzt und es wird eine metallische Spiegelschicht 19 auf die dielektrische Spiegelschicht 18 abgeschieden. In den Ausnehmungen der 5 dielektrischen Spiegelschicht 18 reicht das Material der metallischen Spiegelschicht 19 bis an die zweite Grenzfläche 8b der Oxidschicht 8 heran und bildet dort somit Knüpfelkontakte zur Oxidschicht 8. Von den Knüpfelkontakten ausgehend erfolgt dann in der transparenten leitfähigen Oxidschicht 8 die laterale Stromaufweitung über die gesamte Grundfläche des Halbleiterschichtenstapels 20.

Die Spiegelschicht 9 umfasst bei diesem Ausführungsbeispiel sowohl eine dielektrische Spiegelschicht 18 als auch eine metallische Spiegelschicht 19. Da die Spiegelschichten 9; 18, 15 19 nach der Oxidschicht 8 abgeschieden werden, verringert sich durch die geringe Rauigkeit R2 der zweiten Grenzfläche 8b der Oxidschicht 8 auch die Rauigkeit der Grenzfläche zwischen den Spiegelschichten 18 und 19. Dadurch wird der Reflektionsgrad des Spiegelschichtenstapels weiter erhöht, denn 20 durch die geringe Rauigkeit der zweiten Grenzfläche der Oxidschicht verringert sich in gewissem Ausmaß auch die Rauigkeit der Grenzflächen nachfolgender Spiegelschichten. Im Übrigen gelten für Figur 3 und 4 dieselben Ausführungen wie 25 für Figur 1 und 2.

Bei den oben genannten Ausführungsbeispielen sind die folgenden Dotierstoffkonzentrationen vorgesehen: Die n-dotierte Leuchtdiodenschicht 2 besitzt eine Dotierstoffkonzentration 30 kleiner als  $1 \times 10^{20}/\text{cm}^3$ , insbesondere unterhalb von  $1 \times 10^{19}/\text{cm}^3$ . Die p-dotierte Leuchtdiodenschicht 4 besitzt eine Dotierstoffkonzentration kleiner als  $2 \times 10^{20}/\text{cm}^3$ . Die Dotierstoffkonzentration der p-dotierten Halbleiterschicht 5 ist

mindestens so groß wie diejenige der p-dotierten Leuchtdiodenschicht 4 und liegt oberhalb von  $2 \times 10^{20}/\text{cm}^3$ . Die Dotierstoffkonzentration der n-dotierten Halbleiterschicht 7 ist größer als diejenige der n-dotierten Leuchtdiodenschicht 2

5 und liegt oberhalb von  $2 \times 10^{20}/\text{cm}^3$ . Somit ist jede der beiden Halbleiterschichten 5, 7 stärker dotiert als die jeweilige Leuchtdiodenschicht 4, 2 desselben Dotierstofftyps. Die p-dotierten Schichten sind mit Magnesium und die n-dotierten Schichten mit Silizium dotiert.

10

Alternativ kann die Dotierstoffkonzentration der n-dotierten Halbleiterschicht 7 auch kleiner sein als die Dotierstoffkonzentration der n-dotierten Leuchtdiodenschicht 2.

15 Figur 5 zeigt eine vergrößerte schematische Detailansicht eines vorläufigen Halbleiterprodukts zur Herstellung der Halbleiterleuchtdiode gemäß einer der Figuren 1 bis 4, und zwar nach dem Aufsputtern der Oxidschicht 8. Dargestellt ist ein oberer Teilbereich der obersten Schicht des Halbleiterschichtenstapels 20 sowie der darauf aufgesputterten Oxidschicht aus dem transparenten leitfähigen Oxid. Die oberste Halbleiterschicht ist entweder die p-dotierte Halbleiterschicht 5 aus Figur 1 bzw. 3 oder die n-dotierte Halbleiterschicht 7 aus Figur 2 bzw. 4.

20

25

Wenn auf die Oberseite der obersten Halbleiterschicht 5 bzw. 7 die Oxidschicht 8 abgeschieden wird, gibt die Rauigkeit der obersten Halbleiterschicht die Rauigkeit R1 der unteren, ersten Grenzfläche 8a der Oxidschicht 8 vor; sie liegt typischerweise oberhalb von 1,5 nm Rms, kann jedoch auch wesentlich größere Werte annehmen - je nach Abscheidungsverfahren für die oberste Halbleiterschicht, deren Grundmaterial und deren Dotierstoffkonzentration. Im Falle einer p-dotierten

Halbleiterschicht 5 (Figur 1 bzw. 3) aus Galliumnitrid beträgt die Rauigkeit ihrer Oberseite zwischen 1,2 bis 1,8 nm.

Durch das HF-unterstützte DC-Sputter-Verfahren zum Abscheiden

5 der Oxidschicht 8 aus dem transparenten leitfähigen Oxid wird erreicht, dass die Rauigkeit R<sub>2</sub> ihrer zweiten Grenzfläche 8b wie in Figur 5 dargestellt kleiner ist als die Rauigkeit R<sub>1</sub> der ersten Grenzfläche 8a, insbesondere kleiner als 1,0 nm oder gar 0,5 nm.

10

Die Oxidschicht 8 wird bei den hier beschriebenen Ausführungsbeispielen mit einer Schichtdicke von zwischen 1 und 50 nm aufgesputtert, wobei die Schichtdicke auch größer gewählt werden kann. Wird die Oxidschicht mit einer Mindestschichtdicke von beispielsweise 5 nm abgeschieden, so werden Unebenheiten, die von der darunterliegenden Halbleiterschicht 5 bzw. 7 herrühren, während des Aufsputterns der Oxidschicht nivelliert. Dadurch ist gewährleistet, dass die Rauigkeit R<sub>2</sub> der zweiten Grenzfläche 8b der Oxidschicht 8 nur noch durch

15 das HF-unterstützte DC-Sputter-Verfahren, jedoch nicht durch Höhenschwankungen tieferliegender Halbleiterschichten beeinflusst wird.

20 Die Spiegelschichten, die auf der (durch das HF-unterstützte DC-Sputtern abgeschiedenen) Oxidschicht angeordnet sind, weisen äußerst glatte Reflexionsflächen auf. Zudem wird die vor dem Aufsputtern der Oxidschicht 8 freiliegende oberste Halbleiterschicht des Halbleiterschichtenstapels durch das HF-unterstützte DC-Sputter-Verfahren kaum geschädigt.

30

Das HF-unterstützte DC-Sputter-Verfahren, das als solches bekannt ist, wird hier zum Abscheiden der Oxidschicht 8 aus dem transparenten leitfähigen Oxid auf die oberste Schicht des

Halbleiterschichtenstapels 20 für die Leuchtdiode eingesetzt. Bei dem HF-unterstützten DC-Sputter-Verfahren wird einer elektrischen Gleichspannung eine hochfrequente Wechselspannung überlagert. Die zum Sputtern zugeführte elektrische Leistung umfasst somit einen DC-Anteil (direct current) sowie einen Hochfrequenz-Anteil (HF; high frequency). Die Frequenz des hochfrequenten Leistungsanteils beträgt beispielsweise 13,56 MHz. Beim Sputtern wird die kombinierte DC/HF-Leistung beispielsweise einer in einer Sputterkammer angeordneten Elektrode zugeführt.

Die zweite Grenzfläche 8b der durch das HF-unterstützte DC-Sputter-Verfahren abgeschiedenen Oxidschicht 8 und die Grenzflächen der weiteren, auf die zweite Grenzfläche 8b abgeschiedenen Spiegelschichten 18, 19 reflektieren aufgrund der verringerten Rauhigkeit einen höheren Anteil der auf sie auftreffenden elektromagnetischen Strahlung. Dies gilt insbesondere für diejenigen Strahlungsanteile, die unter größeren Einfallswinkeln relativ zur Flächennormalen auf diese Grenzflächen auftreffen.

Durch den erhöhten Reflexionsgrad strahlt die Halbleiterleuchtdiode 10 an ihrer Strahlungsaustrittsfläche 25 insgesamt eine größere Intensität elektromagnetischer Strahlung ab.

Die Erfindung ist nicht durch die Beschreibung anhand der Ausführungsbeispiele beschränkt. Vielmehr umfasst die Erfindung jedes neuen Merkmal sowie jede Kombination von Merkmalen, was insbesondere jede Kombination von Merkmalen in den Patentansprüchen beinhaltet, auch wenn dieses Merkmal oder diese Kombination selbst nicht explizit in den Patentansprüchen oder Ausführungsbeispielen angegeben ist.

## Patentansprüche

1. Halbleiterleuchtdiode (10) mit:

- zumindest einer p-dotierten Leuchtdiodenschicht (4), einer n-dotierten Leuchtdiodenschicht (2) sowie einer optisch aktiven Zone (3) zwischen der p-dotierten Leuchtdiodenschicht (4) und der n-dotierten Leuchtdiodenschicht (2),

- einer Oxidschicht (8) aus einem transparenten leitfähigen Oxid und

10 - mindestens einer Spiegelschicht (9),

wobei die Oxidschicht (8) zwischen den Leuchtdiodenschichten (2, 4) und der mindestens einen Spiegelschicht (9) angeordnet ist und eine erste Grenzfläche (8a), die den Leuchtdiodenschichten (2, 4) zugewandt ist, und eine zweite Grenzfläche (8b), die der mindestens einen Spiegelschicht (9) zugewandt ist, aufweist und

wobei die zweite Grenzfläche (8b) der Oxidschicht (8) eine geringere Rauhigkeit (R2) besitzt als die erste Grenzfläche (8a) der Oxidschicht (8).

20

2. Halbleiterleuchtdiode (10) mit:

- zumindest einer p-dotierten Leuchtdiodenschicht (4), einer n-dotierten Leuchtdiodenschicht (2) sowie einer optisch aktiven Zone (3) zwischen der p-dotierten Leuchtdiodenschicht (4) und der n-dotierten Leuchtdiodenschicht (2),

- einer Oxidschicht (8) aus einem transparenten leitfähigen Oxid und

- mindestens einer Spiegelschicht (9),

wobei die Oxidschicht (8) zwischen den Leuchtdiodenschichten (2, 4) und der mindestens einen Spiegelschicht (9) angeordnet ist und eine erste Grenzfläche (8a), die den Leuchtdiodenschichten (2, 4) zugewandt ist, und eine zweite Grenzfläche

(8b), die der mindestens einen Spiegelschicht (9) zugewandt ist, aufweist und

wobei die zweite Grenzfläche (8b) der Oxidschicht (8) eine Rauigkeit (R2) besitzt, die kleiner ist als 1,0 nm.

5

3. Halbleiterleuchtdiode nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass die Oxidschicht (8) eine Schichtdicke größer als 5 nm besitzt.

10

4. Halbleiterleuchtdiode nach einem der Ansprüche 1 bis 3, dadurch gekennzeichnet, dass die p-dotierte Leuchtdiodenschicht (4) näher an der Oxidschicht (8) angeordnet ist als die n-dotierte Leuchtdiodenschicht (2).

5. Halbleiterleuchtdiode nach einem der Ansprüche 1 bis 4, dadurch gekennzeichnet, dass zwischen der p-dotierten Leuchtdiodenschicht (4) und der Oxidschicht (8) eine p-dotierte Halbleiterschicht (5) angeordnet ist, die eine Dotierstoffkonzentration besitzt, die mindestens so groß ist wie die Dotierstoffkonzentration der p-dotierten Leuchtdiodenschicht (4).

25 6. Halbleiterleuchtdiode nach Anspruch 5, dadurch gekennzeichnet, dass die Oxidschicht (8) mit ihrer ersten Grenzfläche (8a) an die p-dotierte Halbleiterschicht (5) angrenzt.

30 7. Halbleiterleuchtdiode nach Anspruch 5, dadurch gekennzeichnet, dass zwischen der p-dotierten Halbleiterschicht (5) und der Oxidschicht (8) eine n-dotierte Halbleiterschicht (7) angeordnet

ist und dass die erste Grenzfläche (8a) der Oxidschicht (8) an die n-dotierte Halbleiterschicht (7) angrenzt.

8. Halbleiterleuchtdiode nach Anspruch 7,

5 dadurch gekennzeichnet, dass zwischen der p-dotierten Halbleiterschicht (5) und der n-dotierten Halbleiterschicht (7) eine undotierte Halbleiterschicht (6) angeordnet ist.

10 9. Halbleiterleuchtdiode nach einem der Ansprüche 1 bis 8,

dadurch gekennzeichnet, dass das transparente leitfähige Oxid der Oxidschicht (8) zumindest eines der Materialien Zinkoxid, Indiumzinnoxid und Indiumzinkoxid enthält.

15

10. Halbleiterleuchtdiode nach einem der Ansprüche 1 bis 9,

dadurch gekennzeichnet, dass die Spiegelschicht (9) an die zweite Grenzfläche (8b) der Oxidschicht (8) angrenzt.

20

11. Halbleiterleuchtdiode nach einem der Ansprüche 1 bis 10,

dadurch gekennzeichnet, dass die Spiegelschicht (9) mindestens eine metallische Spiegelschicht (19) umfasst.

25

12. Halbleiterleuchtdiode nach einem der Ansprüche 1 bis 11,

dadurch gekennzeichnet, dass die Spiegelschicht (9) mindestens eine dielektrische Spiegelschicht (18) umfasst.

30

13. Halbleiterleuchtdiode nach Anspruch 12,

dadurch gekennzeichnet, dass

die dielektrische Spiegelschicht (18) zwischen der Oxidschicht (8) und der metallischen Spiegelschicht (19) angeordnet ist und lokale Ausnehmungen (11) aufweist, in denen die metallische Spiegelschicht (19) bis an die zweite Grenzfläche 5 (8b) der Oxidschicht (8) heranreicht.

14. Verfahren zum Herstellen einer Halbleiterleuchtdiode (10), wobei das Verfahren folgendes umfasst:

- Ausbilden zumindest einer p-dotierten Leuchtdiodenschicht 10 (4) und einer n-dotierten Leuchtdiodenschicht (2),

- Abscheiden eines transparenten leitfähigen Oxihs, wodurch eine Oxidschicht (8) gebildet wird, die eine erste Grenzfläche (8a) aufweist, die den Leuchtdiodenschichten (2, 4) zugewandt ist, wobei die Oxidschicht (8) durch HF-unterstütztes 15 DC-Sputtern abgeschieden wird und dabei eine zur ersten Grenzfläche (8a) entgegengesetzte zweite Grenzfläche (8b) der Oxidschicht (8) erzeugt wird, die eine geringere Rauigkeit besitzt als die erste Grenzfläche (8a) der Oxidschicht (8), und

- Ausbilden mindestens einer Spiegelschicht (9) oberhalb der zweiten Grenzfläche (8b) der Oxidschicht (8).

15. Verfahren nach Anspruch 14,

dadurch gekennzeichnet, dass

- 25 das Ausbilden der mindestens einen Spiegelschicht (9) das Abscheiden mindestens einer dielektrischen Spiegelschicht (18), das Ätzen von Ausnehmungen in die dielektrische Spiegelschicht (18) und das Abscheiden mindestens einer metallischen Spiegelschicht (19) auf die dielektrische Spiegelschicht (18)

- 30 umfasst.

FIG 1

FIG 2

FIG 3

FIG 4

FIG 5

# INTERNATIONAL SEARCH REPORT

International application No

PCT/DE2009/000192

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H01L33/00

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, INSPEC, COMPENDEX, IBM-TDB

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                      | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | DE 10 2006 023685 A1 (OSRAM OPTO SEMICONDUCTORS GMBH [DE])<br>5 April 2007 (2007-04-05)                                                 | 1-6,9-11              |

| Y         | page 2, paragraph 6 – page 5, paragraph 38<br>page 6, paragraph 49 – page 8, paragraph 62<br>figure 2                                   | 7,8,14                |

| Y         | US 2006/249736 A1 (LEE JAE H [KR] ET AL)<br>9 November 2006 (2006-11-09)<br>figures 3-5f<br>page 3, paragraph 48 – page 5, paragraph 86 | 7,8                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

Date of the actual completion of the international search

29 Mai 2009

Date of mailing of the international search report

12/06/2009

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Sauerer, Christof

## INTERNATIONAL SEARCH REPORT

International application No

PCT/DE2009/000192

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                           | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y         | WO 01/86731 A (UNAXIS DEUTSCHLAND GMBH [DE]; KLOEPPEL ANDREAS [DE]; TRUBE JUTTA [DE]) 15 November 2001 (2001-11-15)<br>page 1, paragraph 4 – page 4, paragraph 2<br>page 4, paragraph 5 – page 5, last<br>paragraph<br>figure 1<br>-----                                                                     | 14, 15                |

| X         | WO 2007/105626 A (MATSUSHITA ELECTRIC WORKS LTD [JP]; FUKUSHIMA HIROSHI [JP]; YASUDA MAS) 20 September 2007 (2007-09-20)                                                                                                                                                                                     | 1, 3-6,<br>9-13       |

| Y         | figure 19<br>-& EP 1 995 794 A (MATSUSHITA ELECTRIC WORKS LTD [JP])<br>26 November 2008 (2008-11-26)<br>page 10, line 28 – page 11, line 35<br>figure 19<br>-----                                                                                                                                            | 7, 8, 14,<br>15       |

| X         | US 2005/121685 A1 (SEONG TAE-YEON [KR] ET AL) 9 June 2005 (2005-06-09)                                                                                                                                                                                                                                       | 1, 3-6,<br>9-11       |

| Y         | figures 8A-10<br>page 4, paragraph 83 – page 5, paragraph 103<br>-----                                                                                                                                                                                                                                       | 14                    |

| X         | DE 10 2005 013894 A1 (OSRAM OPTO SEMICONDUCTORS GMBH [DE])<br>26 January 2006 (2006-01-26)<br>page 5, paragraph 44<br>figure 3<br>-----                                                                                                                                                                      | 1, 3-6,<br>9-11       |

| X         | DE 10 2004 050891 A1 (LUMILEDS LIGHTING U S [US]) 20 April 2006 (2006-04-20)<br>page 3, paragraph 23 – page 7, paragraph 38<br>figure 7A<br>-----                                                                                                                                                            | 1, 3-5, 7,<br>9-11    |

| P, A      | WO 2009/015645 A (OSRAM OPTO SEMICONDUCTORS GMBH [DE]; AHLSTEDT MAGNUS [DE]; BADER STEFA)<br>5 February 2009 (2009-02-05)<br>the whole document<br>-----                                                                                                                                                     | 1-15                  |

| A         | BETZ ET AL: "On the synthesis of ultra smooth ITO thin films by conventional direct current magnetron sputtering". THIN SOLID FILMS, ELSEVIER-SEQUOIA S.A. LAUSANNE, CH,<br>vol. 516, no. 7,<br>29 January 2008 (2008-01-29), pages 1334-1340, XP022436931<br>ISSN: 0040-6090<br>the whole document<br>----- | 1-15                  |

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/DE2009/000192

| Patent document cited in search report | Publication date |                            | Patent family member(s)                                                  | Publication date                                                   |

|----------------------------------------|------------------|----------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------|

| DE 102006023685 A1                     | 05-04-2007       |                            | WO 2007036198 A2<br>EP 1929551 A2<br>JP 2009510737 T<br>KR 20080068831 A | 05-04-2007<br>11-06-2008<br>12-03-2009<br>24-07-2008               |

| US 2006249736 A1                       | 09-11-2006       | JP                         | 2006313888 A                                                             | 16-11-2006                                                         |

| WO 0186731 A                           | 15-11-2001       | DE<br>EP<br>JP<br>TW<br>US | 10023459 A1<br>1282919 A1<br>2003532997 T<br>253477 B<br>2003170449 A1   | 15-11-2001<br>12-02-2003<br>05-11-2003<br>21-04-2006<br>11-09-2003 |

| WO 2007105626 A                        | 20-09-2007       | CN<br>EP<br>KR             | 101395728 A<br>1995794 A1<br>20080099868 A                               | 25-03-2009<br>26-11-2008<br>13-11-2008                             |

| EP 1995794 A                           | 26-11-2008       | CN<br>WO<br>KR             | 101395728 A<br>2007105626 A1<br>20080099868 A                            | 25-03-2009<br>20-09-2007<br>13-11-2008                             |

| US 2005121685 A1                       | 09-06-2005       | CN<br>JP<br>KR             | 1622349 A<br>2005167237 A<br>20050051920 A                               | 01-06-2005<br>23-06-2005<br>02-06-2005                             |

| DE 102005013894 A1                     | 26-01-2006       | US                         | 2006011923 A1                                                            | 19-01-2006                                                         |

| DE 102004050891 A1                     | 20-04-2006       |                            | NONE                                                                     |                                                                    |

| WO 2009015645 A                        | 05-02-2009       | DE                         | 102007035687 A1                                                          | 05-02-2009                                                         |

# INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/DE2009/000192

## A. KLASIFIZIERUNG DES ANMELDUNGSGEGENSTANDES

INV. H01L33/00

Nach der Internationalen Patentklassifikation (IPC) oder nach der nationalen Klassifikation und der IPC

## B. RECHERCHIERTE GEBIETE

Recherchierter Mindestprüfstoff (Klassifikationssystem und Klassifikationssymbole )

H01L

Recherchierte, aber nicht zum Mindestprüfstoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen

Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe)

EPO-Internal, WPI Data, INSPEC, COMPENDEX, IBM-TDB

## C. ALS WESENTLICH ANGESEHENE UNTERLAGEN

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                                       | Betr. Anspruch Nr. |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| X          | DE 10 2006 023685 A1 (OSRAM OPTO SEMICONDUCTORS GMBH [DE])<br>5. April 2007 (2007-04-05)                                                 | 1-6,9-11           |

| Y          | Seite 2, Absatz 6 – Seite 5, Absatz 38<br>Seite 6, Absatz 49 – Seite 8, Absatz 62<br>Abbildung 2                                         | 7,8,14             |

| Y          | US 2006/249736 A1 (LEE JAE H [KR] ET AL)<br>9. November 2006 (2006-11-09)<br>Abbildungen 3-5f<br>Seite 3, Absatz 48 – Seite 5, Absatz 86 | 7,8                |

|            |                                                                                                                                          | -/-                |

Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu entnehmen  Siehe Anhang Patentfamilie

\* Besondere Kategorien von angegebenen Veröffentlichungen :

"A" Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonders bedeutsam anzusehen ist

"E" älteres Dokument, das jedoch erst am oder nach dem internationalen Anmeldedatum veröffentlicht worden ist

"L" Veröffentlichung, die geeignet ist, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belegt werden soll oder die aus einem anderen besonderen Grund angegeben ist (wie ausgeführt)

"O" Veröffentlichung, die sich auf eine mündliche Offenbarung, eine Benutzung, eine Ausstellung oder andere Maßnahmen bezieht

"P" Veröffentlichung, die vor dem internationalen Anmeldedatum, aber nach dem beanspruchten Prioritätsdatum veröffentlicht worden ist

"T" Spätere Veröffentlichung, die nach dem internationalen Anmeldedatum oder dem Prioritätsdatum veröffentlicht worden ist und mit der Anmeldung nicht kollidiert, sondern nur zum Verständnis des der Erfindung zugrundeliegenden Prinzips oder der ihr zugrundeliegenden Theorie angegeben ist

"X" Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann allein aufgrund dieser Veröffentlichung nicht als neu oder auf erforderlicher Tätigkeit beruhend betrachtet werden

"Y" Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann nicht als auf erforderlicher Tätigkeit beruhend betrachtet werden, wenn die Veröffentlichung mit einer oder mehreren anderen Veröffentlichungen dieser Kategorie in Verbindung gebracht wird und diese Verbindung für einen Fachmann naheliegend ist

"&" Veröffentlichung, die Mitglied derselben Patentfamilie ist

Datum des Abschlusses der internationalen Recherche

Absendedatum des internationalen Recherchenberichts

29. Mai 2009

12/06/2009

Name und Postanschrift der Internationalen Recherchenbehörde

Europäisches Patentamt, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Bevollmächtigter Bediensteter

Sauerer, Christof

## INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/DE2009/000192

| C. (Fortsetzung) ALS WESENTLICH ANGESEHENE UNTERLAGEN |                                                                                                                                                                                                                                                                                                                      |                    |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Kategorie*                                            | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                                                                                                                                                                                                                   | Betr. Anspruch Nr. |

| Y                                                     | WO 01/86731 A (UNAXIS DEUTSCHLAND GMBH [DE]; KLOEPPEL ANDREAS [DE]; TRUBE JUTTA [DE]) 15. November 2001 (2001-11-15)<br>Seite 1, Absatz 4 – Seite 4, Absatz 2<br>Seite 4, Absatz 5 – Seite 5, letzter<br>Absatz<br>Abbildung 1<br>-----                                                                              | 14, 15             |

| X                                                     | WO 2007/105626 A (MATSUSHITA ELECTRIC WORKS LTD [JP]; FUKUSHIMA HIROSHI [JP]; YASUDA MAS)<br>20. September 2007 (2007-09-20)                                                                                                                                                                                         | 1, 3-6,<br>9-13    |

| Y                                                     | Abbildung 19<br>-& EP 1 995 794 A (MATSUSHITA ELECTRIC WORKS LTD [JP])<br>26. November 2008 (2008-11-26)<br>Seite 10, Zeile 28 – Seite 11, Zeile 35<br>Abbildung 19<br>-----                                                                                                                                         | 7, 8, 14,<br>15    |

| X                                                     | US 2005/121685 A1 (SEONG TAE-YEON [KR] ET AL) 9. Juni 2005 (2005-06-09)                                                                                                                                                                                                                                              | 1, 3-6,<br>9-11    |

| Y                                                     | Abbildungen 8A-10<br>Seite 4, Absatz 83 – Seite 5, Absatz 103<br>-----                                                                                                                                                                                                                                               | 14                 |

| X                                                     | DE 10 2005 013894 A1 (OSRAM OPTO SEMICONDUCTORS GMBH [DE])<br>26. Januar 2006 (2006-01-26)<br>Seite 5, Absatz 44<br>Abbildung 3<br>-----                                                                                                                                                                             | 1, 3-6,<br>9-11    |

| X                                                     | DE 10 2004 050891 A1 (LUMILEDS LIGHTING U S [US]) 20. April 2006 (2006-04-20)<br>Seite 3, Absatz 23 – Seite 7, Absatz 38<br>Abbildung 7A<br>-----                                                                                                                                                                    | 1, 3-5, 7,<br>9-11 |

| P, A                                                  | WO 2009/015645 A (OSRAM OPTO SEMICONDUCTORS GMBH [DE]; AHLSTEDT MAGNUS [DE]; BADER STEFA)<br>5. Februar 2009 (2009-02-05)<br>das ganze Dokument<br>-----                                                                                                                                                             | 1-15               |

| A                                                     | BETZ ET AL: "On the synthesis of ultra smooth ITO thin films by conventional direct current magnetron sputtering"<br>THIN SOLID FILMS, ELSEVIER-SEQUOIA S.A.<br>LAUSANNE, CH,<br>Bd. 516, Nr. 7,<br>29. Januar 2008 (2008-01-29), Seiten<br>1334-1340, XP022436931<br>ISSN: 0040-6090<br>das ganze Dokument<br>----- | 1-15               |

**INTERNATIONALER RECHERCHENBERICHT**

Angaben zu Veröffentlichungen, die zur selben Patentfamilie gehören

Internationales Aktenzeichen

PCT/DE2009/000192

| Im Recherchenbericht<br>angeführtes Patentdokument | Datum der<br>Veröffentlichung |                            | Mitglied(er) der<br>Patentfamilie                                      | Datum der<br>Veröffentlichung                                      |

|----------------------------------------------------|-------------------------------|----------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------|

| DE 102006023685 A1                                 | 05-04-2007                    | WO<br>EP<br>JP<br>KR       | 2007036198 A2<br>1929551 A2<br>2009510737 T<br>20080068831 A           | 05-04-2007<br>11-06-2008<br>12-03-2009<br>24-07-2008               |

| US 2006249736 A1                                   | 09-11-2006                    | JP                         | 2006313888 A                                                           | 16-11-2006                                                         |

| WO 0186731 A                                       | 15-11-2001                    | DE<br>EP<br>JP<br>TW<br>US | 10023459 A1<br>1282919 A1<br>2003532997 T<br>253477 B<br>2003170449 A1 | 15-11-2001<br>12-02-2003<br>05-11-2003<br>21-04-2006<br>11-09-2003 |

| WO 2007105626 A                                    | 20-09-2007                    | CN<br>EP<br>KR             | 101395728 A<br>1995794 A1<br>20080099868 A                             | 25-03-2009<br>26-11-2008<br>13-11-2008                             |

| EP 1995794 A                                       | 26-11-2008                    | CN<br>WO<br>KR             | 101395728 A<br>2007105626 A1<br>20080099868 A                          | 25-03-2009<br>20-09-2007<br>13-11-2008                             |

| US 2005121685 A1                                   | 09-06-2005                    | CN<br>JP<br>KR             | 1622349 A<br>2005167237 A<br>20050051920 A                             | 01-06-2005<br>23-06-2005<br>02-06-2005                             |

| DE 102005013894 A1                                 | 26-01-2006                    | US                         | 2006011923 A1                                                          | 19-01-2006                                                         |

| DE 102004050891 A1                                 | 20-04-2006                    | KEINE                      |                                                                        |                                                                    |

| WO 2009015645 A                                    | 05-02-2009                    | DE                         | 102007035687 A1                                                        | 05-02-2009                                                         |