(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4914558号

(P4914558)

(45) 発行日 平成24年4月11日(2012.4.11)

(24) 登録日 平成24年1月27日(2012.1.27)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| G09G 3/36 (2006.01)   | G09G 3/36      |

| G02F 1/133 (2006.01)  | G02F 1/133 550 |

| G02F 1/1368 (2006.01) | G02F 1/1368    |

| G09G 3/20 (2006.01)   | G09G 3/20 611A |

| G09G 3/30 (2006.01)   | G09G 3/20 624B |

請求項の数 7 (全 15 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2003-514534 (P2003-514534)  |

| (86) (22) 出願日 | 平成14年7月12日 (2002.7.12)        |

| (65) 公表番号     | 特表2004-536347 (P2004-536347A) |

| (43) 公表日      | 平成16年12月2日 (2004.12.2)        |

| (86) 國際出願番号   | PCT/IB2002/002993             |

| (87) 國際公開番号   | W02003/009268                 |

| (87) 國際公開日    | 平成15年1月30日 (2003.1.30)        |

| 審査請求日         | 平成17年7月11日 (2005.7.11)        |

| 審判番号          | 不服2009-4532 (P2009-4532/J1)   |

| 審判請求日         | 平成21年3月2日 (2009.3.2)          |

| (31) 優先権主張番号  | 0117226.1                     |

| (32) 優先日      | 平成13年7月14日 (2001.7.14)        |

| (33) 優先権主張国   | 英國 (GB)                       |

| (31) 優先権主張番号  | 0125969.6                     |

| (32) 優先日      | 平成13年10月30日 (2001.10.30)      |

| (33) 優先権主張国   | 英國 (GB)                       |

|           |                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 307003227<br>ティーピーオー ホンコン ホールディング<br>リミテッド<br>香港、シャティン、サイエンス パーク<br>イースト アベニュー、フィリップス エ<br>レクトロニクス ビルディング 5, フロ<br>ア 2 |

| (74) 代理人  | 100147485<br>弁理士 杉村 憲司                                                                                                 |

| (74) 代理人  | 100143568<br>弁理士 英 貢                                                                                                   |

| (74) 代理人  | 100147692<br>弁理士 下地 健一                                                                                                 |

最終頁に続く

(54) 【発明の名称】アクティブマトリックスディスプレイ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

行列配置した複数の画素と、対応する画素の列に沿って延在する列電極とを具え、前記複数の画素の各々が、画像データ記憶キャパシタンスと、前記列電極と前記画像データ記憶キャパシタンスとの間に接続され、前記画像データ記憶キャパシタンスの電圧を一旦取り込み、前記取り込んだ画像データ記憶キャパシタンスの状態に基づいて前記列電極を荷電するバッファとして機能する読み出し回路と、有することを特徴とするアクティブマトリックス表示装置。

## 【請求項 2】

行電極と、前記対応する画素の行に沿って延在する読み出しラインとを有する請求項1記載のアクティブマトリックス表示装置であって、前記複数の画素の各々が、対応する行電極によって選択されたときに対応する列電極を前記データ記憶キャパシタンスに接続するスイッチを有し、前記読み出し回路が、前記画像データ記憶キャパシタンスの電圧を前記対応する列電極に読み出すために対応する読み出しラインによって制御されることを特徴とするアクティブマトリックス表示装置。

## 【請求項 3】

前記複数の画素の各々が、画素表示素子を駆動する駆動回路を有し、前記駆動回路が、前記画像データ記憶キャパシタンスに接続された入力部を有することを特徴とする請求項2記載のアクティブマトリックス表示装置。

10

20

**【請求項 4】**

前記複数の画素の各々が、複数の画像データ記憶キャパシタンスを有することを特徴とする請求項 1～3 のいずれか 1 項に記載のアクティブマトリックス表示装置。

**【請求項 5】**

前記複数の画像データ記憶キャパシタンスの各々に接続された専用の読み出し回路を有することを特徴とする請求項 4 記載のアクティブマトリックス表示装置。

**【請求項 6】**

行列配置した複数の画素と、行電極と、対応する画素の列に沿って延在する列電極と、対応する画素の行に沿って延在する読み出しラインとを具え、

前記複数の画素の各々が、画像データ記憶キャパシタンスと、

10

対応する行電極によって選択されたときに対応する列電極を前記データ記憶キャパシタンスに接続する第 1 スイッチと、

前記画像データ記憶キャパシタンスに接続された入力部を有し、画素表示素子を駆動する駆動回路と、

前記列電極と前記駆動回路の出力部との間に配置され、前記画像データ記憶キャパシタンスの電圧に基づいて前記列電極を荷電するために対応する読み出しラインによって制御され、前記対応する読み出しラインの制御の下で前記駆動回路の出力部を前記対応する列電極に接続する第 2 スイッチとを有することを特徴とするアクティブマトリックス表示装置。

**【請求項 7】**

行列配置した複数の画素と、対応する画素の列に沿って延在する列電極と、対応する画素の行に沿って延在する読み出しライン、選択ラインおよび複数の行電極とを具え、

20

前記複数の画素の各々が、複数の画像データ記憶キャパシタンスと、

データラインと、

対応する行電極によって選択されたときに対応する画像データ記憶キャパシタンスを前記データラインに接続する複数の第 3 スイッチと、

前記列電極と前記データラインとの間に接続され、前記複数の行電極の 1 つによって選択された前記画像データ記憶キャパシタンスの電圧を一旦取り込み、前記取り込んだ画像データ記憶キャパシタンスの電圧に基づいて前記列電極を荷電するバッファとして機能する読み出し回路と、

前記列電極上の電圧を前記複数の行電極の 1 つによって選択された前記画像データ記憶キャパシタンスに書き込むように、前記選択ラインの制御の下で前記列電極を前記データラインを介して前記第 3 スイッチに接続する第 4 スイッチと、

を有し、

30

前記読み出し回路が、前記読み出しラインの制御の下で前記データライン上にある前記複数の行電極の 1 つによって選択された前記画像データキャパシタンスの電圧を前記対応する列電極に読み出すことを特徴とするアクティブマトリックス表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示画素のアレイを具えるアクティブマトリックス表示装置に関し、特に、アクティブマトリックス液晶表示装置及びアクティブマトリックスエレクトロルミネッセント表示装置に関するが、それに限定されるものではない。

40

**【背景技術】****【0002】**

アクティブマトリックス表示装置、特にアクティブマトリックス液晶表示装置（AMLD）は、複数の製品分野において使用されており、その中では、ラップトップコンピュータスクリーン、ノートブックコンピュータスクリーン、デスクトップコンピュータモニタ、PDA、電子オルガン及び移動電話が最も一般的であると考えられる。

**【0003】**

典型的なアクティブマトリックス表示装置、この場合には AMLCD の構造及び一般的

50

な動作は、例えば米国特許第4130829号に記載されており、参照によりその全体の内容をここに組み込む。簡潔には、その表示装置は、行列配置された画素のアレイを具え、その各々は、電子光学表示素子と、通常は薄膜トランジスタ(TFT)の形態の関連の切替装置とを具える。画素は、行アドレス電極及び列アドレス電極のセットに接続され、各画素は、各セットの各電極間の交差部に隣接して配置され、それを通じて、画素は、行電極の各々に順次供給される選択(走査)信号によってアドレス指定されてその行を選択し、データ(ビデオ情報)信号が、行選択に同期を取りながら、列アドレス電極を通じて選択された行の画素に供給され、接続された行の個々の画素の表示出力を決定する。データ信号は、列アドレス電極に結合された列アドレス回路の入力ビデオ信号を適切にサンプリングすることによって取得される。画素の各行は、1フィールド(フレーム)周期の全アレイから表示を構成するために順にアドレス指定され、このようにして、画素のアレイは、連続するフィールドで繰返しアドレス指定される。画素に生じる損失のために、ビデオ情報を用いて画素を規則的にリフレッシュする必要がある。AMLCDの場合、LCD材料の劣化を防止するために、表示素子に供給されるデータ信号電圧の極性を周期的に反転する必要がある。これを、例えば各フィールド後に行い(いわゆるフィールド反転)、又は各行を同様にアドレス指定した後に行う(いわゆるライン又は行反転)を行う必要がある。

#### 【0004】

アクティブマトリックス表示装置の電力消費の大部分は、ビデオ情報のビデオ信号源から表示装置の画素への転送に関連する。表示装置の画素が不定期間にビデオ情報を格納できる場合、電力のこの成分を減少することができる。この場合、画素の表示出力(明るさ)状態の変化が要求されないときに、フレッシュビデオ情報を有するがそのアドレス指定を中止することができる。

#### 【0005】

したがって、アクティブマトリックス表示装置の画素をメモリと組み合わせることによって、静止画像が許容される際に電力を減少することができる。その理由は、画像が変化する際にのみデータを画素に送信するだけでよいからであり、したがって、外部回路における電力消費が減少するとともに、画素に対する接続部に関連したキャパシタンスを駆動する際の電力消費が減少する。

#### 【0006】

一つのアプローチは、画素にスタティクメモリセルを組み込むとともに、画素電極を適切な駆動源に接続するのを制御するためにメモリの状態を使用することである。しかしながら、スタティクメモリの主な不都合は、電力及び制御信号に要求されるトランジスタ及びバスラインの数に関連する複雑さである。

#### 【0007】

AMLCDに対する他の既知のアプローチは、動的な1ビット/画素メモリとして(1TFT/画素を有する)画素を用いることである。画素を列電極に接続する際に少ない電圧変化を検出することができるセンサアンプを列電極に追加することによって、画素の状態を検知することができる。この際、メモリの動的な性質によって要求されるように画素をリフレッシュすることができる。このアプローチに対する問題は、列電極で検知すべき信号の大きさは、列キャパシタンスに対する画素の比により決定されることであり、それは、予め決定された画素ピッチ及び解像度を有するAMLCDにおいては非常に小さくなうことである。他の問題は、AMLCDで用いられるLCD材料を駆動する際に材料の劣化を抑制するために極性が交互に切り換わる電圧を用いるのが一般的であるので、列を駆動するための精巧な外部検知及びリフレッシュ回路が必要とされることである。

#### 【0008】

この種のAMLCDの一例は、米国特許第4430648号に記載されており、その全内容は、参照によりここに組み込まれる。この場合、ディスプレイの画像を維持するために画素の電圧の周期的なリフレッシュが、ディスプレイの列アドレス指定回路内に検知及びリフレッシュ回路を組み込むことによって行われる。リフレッシュ動作中、電荷が、表

10

20

30

40

50

示装置の1行の画素から対応する関連の列電極に転送される。この電荷を検出するとともに画素の状態を決定するためにセンス回路が用いられる。この情報は、リフレッシュ回路によって同一画素に書き戻される。列キャパシタンスの値が画素キャパシタンスに比べて大きいので、センス回路によって検出される必要がある信号は比較的小さく、これによつて、センス回路の設計が困難になり、そのパフォーマンスが表示装置の動作に対して重大になる。特に、表示装置は、電気的な雑音源の影響を受けやすくなるおそれがある。さらに、表示装置内の画素がリフレッシュされると、表示装置の列は、リフレッシュ回路により蓄積ビデオ情報に従つて駆動される。列キャパシタンスの充放電は、表示装置の電力消費に寄与する。

## 【0009】

10

参照によつて全内容がここに組み込まれる米国特許第6169532号は、同様に列電極に結合したセンスアンプに関連したダイナミックメモリ画素を用いたAMLCDとアクティブマトリックエレクトロルミネッセント表示装置の両方の例を記載している。

## 【0010】

画素回路に何かのメモリを有する表示装置を画素機能のメモリを用いることなく通常モードで作動させることができることも知られている。この場合、(レイアウトの制約に起因する1ビット/カラーに制限することができる)統合されたメモリが、静止画像を表示する際に低電力モードで使用される。

## 【0011】

20

参照によつて全内容がここに組み込まれる欧州特許公開番号0797182号は、AMLCDで用いられる画素内低インピーダンス駆動回路を有するダイナミックメモリ回路の種々の例を記載している。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0012】

しかしながら、画素へのダイナミックメモリの組込みに伴う問題が存在する。不都合な複雑さ又はトランジスタのような素子の個数を制限することによる画素アーチャへの悪影響を回避するためにアクティブマトリックス表示装置の画素に信頼性のあるダイナミックメモリの統合は、重要な問題として考慮される。さらに、画素のダイナミック記憶素子のリフレッシュを、特定のタイプの表示装置に要求される適切な駆動電圧(又は場合によつては画素内駆動回路)とともに考慮する必要もある。

30

## 【0013】

本発明は、既知の装置より優れたアクティブマトリックス表示装置を提供することである。種々の新規の概念、発明の概念及び特定の実施の形態を、添付図面を参照してここで開示するが、それに限定されるものではない。

## 【課題を解決するための手段】

## 【0014】

本発明の第1の態様によるアクティブマトリックス表示装置は、行列配置した複数の画素と、対応する画素の列に沿つて延在する列電極とを具え、前記画素が、画像データ記憶キャパシタンスと、その画像データ記憶キャパシタンスの状態を読み出すとともに画像データ記憶キャパシタンスの状態に対応して列電極を荷電する読出し回路とを有することを特徴とする。

40

## 【発明の効果】

## 【0015】

したがつて、読み出し回路はバッファとして機能し、その結果、画素内のダイナミック記憶素子として用いられるキャパシタンスを、列電極を介してリフレッシュすることができる。それに対して、画素内に組み込まれた読み出し回路を有さず、各列ラインの端部でのセンス回路を有する従来の構成においては、各画素内の小さな組み込みキャパシタンスは、列ラインのキャパシタンスにより埋没され非常に小さいものとなりうるキャパシタンスの変化の影響を、センス回路において検出することを非常に困難としうる。さらに、列

50

ラインを読み出し回路とともに駆動することにより、電気的な雑音に対するアクティブマトリックスディスプレイの感度は、このような読み出し回路を有しない従来の構成に対して低減することができる。

#### 【0016】

実際には、本例では、読み出し回路を設けることによって、画像データ記憶キャパシタンスのサイズを減少することができ、又は、液晶画素電極のキャパシタンスのような他の理由による画素内に存在するキャパシタンスによって個別のキャパシタと置換することができる。

#### 【0017】

好適には、読み出し回路は高い入力インピーダンスを有し、その結果、キャパシタンスは 10 、読み出し中に少量しか放電されず、例えば、蓄積された電荷の 10 % 未満、好適には 2 % 未満しか放出されない。

#### 【0018】

本発明の例は、行電極と、画素の対応する行に沿って延在する読み出しラインとを有する請求項 1 又は 2 記載のアクティブマトリックス表示装置であって、前記画素が、対応する行電極によって選択されたときに対応する列電極を前記データ記憶キャパシタンスに接続するスイッチを有し、前記読み出し回路が、前記対応する列電極のキャパシタンスを読み出すために対応する読み出しラインによって制御される。

#### 【0019】

前記画素が、画素表示素子を駆動する駆動回路を有し、その駆動回路が、前記画像データ記憶キャパシタンスに接続された入力部を有してもよい。駆動回路は、LED、液晶表示電極又は他の画素表示素子を駆動することができる。この場合、読み出し回路は、読み出しラインの制御の下で駆動回路の出力部に列電極を接続するスイッチを構成する。 20

#### 【0020】

各画素が、複数の画像データ記憶キャパシタンスを有してもよい。

例示として、各行に沿った複数の行電極を有し、各行電極が、各画像データ記憶キャパシタをデータラインに接続するようスイッチを切り替え、選択ラインが、前記データラインが対応する列電極を接続するようスイッチを制御し、前記読み出し回路が、読み出しラインの制御の下でデータライン上のデータを列電極に読み出してもよい。

#### 【0021】

専用の読み出し回路を各画像データ記憶キャパシタンスに接続してもよい。 30

#### 【0022】

本発明は、記憶ノードを持つ画素を有するアクティブマトリックス表示装置を操作する方法であって、前記記憶ノードに画像データを記憶し、前記アクティブマトリックス装置を静止モードで操作し、記憶された画像データを表示し、前記画素内の読み出し回路に読み出し信号を周期的に供給して、記憶された画像データを列電極に対して読み出し、前記記憶ノードに記憶された画像データをリフレッシュすることを特徴とする方法にも関する。

#### 【0023】

この方法は、フレッシュビデオ情報を用いた画素の規則的なアドレス指定及びビデオ情報の表示を含む通常モードでの前記アクティブマトリックス表示装置の操作を行ってもよい。 40

#### 【発明を実施するための最良の形態】

#### 【0024】

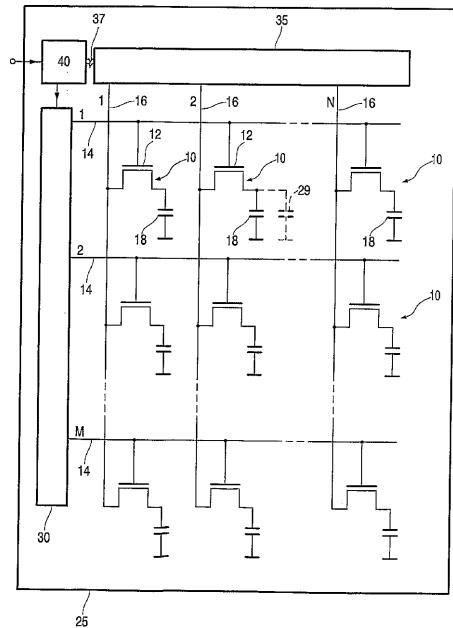

図 1において、表示画素 10 の行列マトリックスアレイ (N × M) を具える一般的に通常の形態の AMLCD の簡単化された回路図を示す。表示素子はそれぞれ、液晶表示素子 18 と、スイッチとして機能する関連の TFT12 とを有し、(M) 行及び (N) 列のアドレス電極 14, 16 のセットを通じてアドレス指定される。ここでは、簡単のために数個の表示画素のみを示し、実際には、数百行及び数百列の画素とすることができます。各 TFT12 のドレインは、行アドレス電極と列アドレス電極の交差部の各々に隣接して配置した表示素子電極にそれぞれ接続され、同時に、表示画素 10 の各行に関連した全ての T 50

F Tのゲートを、同一行のアドレス電極 1 4 に接続し、表示画素の各列に関連した全ての T F T のソースを、同一列のアドレス電極 1 6 に接続する。電極 1 4 , 1 6 、 T F T 1 2 及び表示素子電極は全て、同一の絶縁基板例えばガラス上に載せ置かれ、種々の導電層、絶縁層及び半導体層の堆積及びホトリソグラフィックパターンニングを含む既知の薄膜技術を用いて製造される。アレイの全ての表示素子に共通の連続的な透明電極を支持する第 2 のガラス基板(図示せず)が、基板 2 5 から離間して配置され、二つの基板は、液晶材料が含まれる包囲されたスペースを規定するために画素アレイの周辺で互いにシールされる。各表示素子電極は、共通電極の重複部及びその間の液晶材料とともに光変調 L C 表示素子を規定する。

## 【 0 0 2 5 】

10

作動中、選択(ゲーティング)信号が、例えばデジタルシフトレジスタを備える行駆動回路 3 0 によって行 1 から行 M の順に各行アドレス電極 1 4 に供給され、データ信号が、選択信号と同期を取りながら、列駆動回路 3 5 によって列電極に供給される。各行電極 1 4 が選択信号によってアドレス指定されると、その列に接続した画素 T F T 1 2 がターンオンされて、各表示素子は、この際に関連の列電極に存在するデータ信号のレベルに応じて荷電される。画素の行が、例えば、供給されたビデオ信号のライン周期に相当する各行アドレス周期( T L )でアドレス指定された後、関連の T F T は、表示素子を電気的に切り離すためにフィールド(フレーム)周期の残りに対する選択信号の終了に応じてターンオフされ、これによって、表示素子が次のフィールド周期で再びアドレス指定されるまでその表示出力を維持するために、供給された電荷が格納される。このように、行 1 から行 M までのアレイの画素の行の各々は、連続的な行アドレス周期 T L の各々に応答してアドレス指定されて、1 フィールド周期 T F でアレイから表示画像を構成し、この場合、 T F は、 M × T L に等しい又は僅かに大きく、その後、連続的なフィールドに対して動作が繰り返される。

## 【 0 0 2 6 】

20

行駆動回路 3 0 及び列駆動回路 3 5 の動作のタイミングは、例えばコンピュータ又は他の源から取得される入力ビデオ信号から取得したタイミング信号によりタイミング及び制御ユニット 4 0 によって制御される。この入力信号中のビデオ入力信号は、ユニット 4 0 のビデオ信号処理回路によって、バス 3 7 を通じて連続的に列駆動回路 3 5 に供給される。この回路は、一つ以上のシフトレジスタ / サンプル - ホールド回路を具え、それは、行走査と同期を取ってビデオ情報信号をサンプリングして、画素アレイの時間アドレス指定で行に適切な直列 - 並列変換を行う。入力ビデオ信号の連続的なフィールドに従うビデオ信号の連続的なフィールドは、連続的なフィールド周期におけるアレイの画素行を繰返し指定することによってアレイに書き込まれる。

## 【 0 0 2 7 】

30

動作の透過モードに対して、表示素子電極は、 I T O のような光透過性導電材料によって構成され、個別の表示素子は、例えばバックライトから一方の側に指導される光を変調するように作動し、その結果、アレイ中の全ての画素行をアドレス指定することによって構成された表示画像を、他方の側から見ることができる。動作の反射モードにおいて、表示素子電極は、光反射導電材料から構成され、共通電極を支持する基板を通じて装置の前方から入射する光は、その表示状態に応じて、各表示素子の L C 材料によって変調されるとともに、その基板から反射されて、前方から見える表示画像を発生する。

## 【 0 0 2 8 】

40

既知の実務に従って、表示素子に供給される駆動電圧は、例えば各フィールド後に周期的に反転されて、 L C 材料の劣化を回避する。極性反転を、フリッカの影響を減少するために各行の後に実行することもできる(行反転)。

## 【 0 0 2 9 】

この装置において、ビデオ信号源から表示画素へのビデオ信号の転送の際に著しい量の電力が消費される。移動式電話のノートブックコンピュータのような携帯式の電池給電装置に用いられる表示装置において、動作中に表示装置によって消費される電力を最小にす

50

るのが当然望ましい。画素が単に同一情報の表示を繰り返す場合にはフレッシュビデオ情報を有する画素のアドレス指定を中止できるので、不定期間中に画素がビデオ情報を記憶できる場合には消費電力を減少することができ、その表示出力に対する変更を必要としない。

#### 【0030】

本発明によるアクティブマトリックス表示装置の実施の形態、特に、AMLCD及びアクティブマトリックスLEDを説明する。これら実施の形態はそれぞれ、画素内のノードの一つのキャパシタンスに蓄積された電荷を用いる画素に統合されたダイナミックメモリを用いる。これら実施の形態の特徴は、読み出し回路が画素に統合され、これによって、画素の状態を列電極に読み出すことができる。画素内でダイナミック記憶素子として用いられるキャパシタンスを、列電極を通じてリフレッシュすることができる。好適には、画素に統合された読み出し回路は、高出力インピーダンスを有し、その結果、読み出し回路は、読み出し動作中さえも、記憶の際に用いられるキャパシタンスを放電しない。10

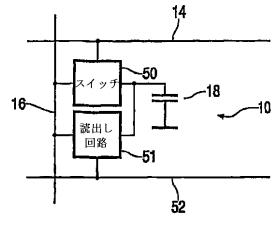

#### 【0031】

3例の画素形態を、図2, 3, 4に線図的に示す。これらの図に示したスイッチ50は、図1の配置のスイッチング装置12に相当し、同様にTFTを具える。画素10に含まれる読み出し回路に51を付す。各ケースにおいて、行電極14に平行に延在するとともに各行の全ての画素10によって共有される補助的な行電極52を設ける。図2において、表示素子18は、本来容量性（例えば、AMLCDのLC）であり、それ自体ダイナミックメモリの記憶ノードとして用いられる。（典型的には、AMLCDにおいて、他の記憶キャパシタンスは、通常LCに並列に追加され、これを図示しない。）行電極14によって制御されるスイッチ50が低インピーダンスを有するとき、電圧が列電極16から表示素子18に転送され、この電圧は、スイッチが高インピーダンス状態である間、表示素子のキャパシタンスに格納される。読み出し回路51は、表示素子18と行電極14との間に接続され、補助的な列電極52によって制御される。読み出し動作中、列電極16は、表示素子の状態によって決定された電圧まで荷電される。読み出し動作が行われると、列電極16を通じて表示素子18をリフレッシュすることができる。リフレッシュ動作は、読み出し動作中に発生した信号を処理する、列駆動回路35中の他の回路を伴うことができる。20

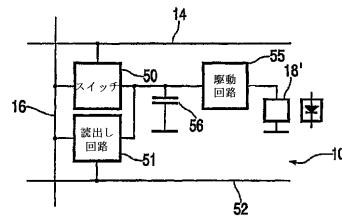

#### 【0032】

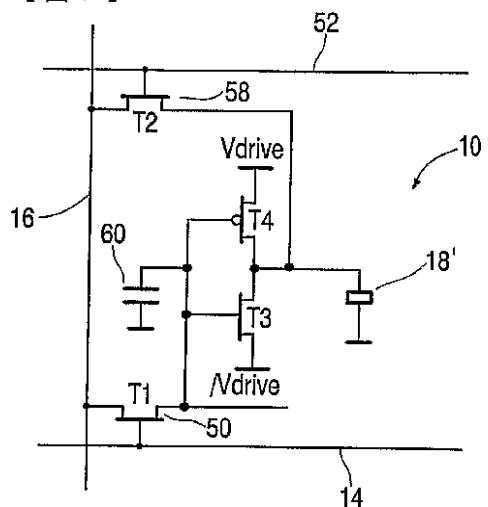

一部のアクティブマトリックス表示アプリケーションにおいて、18'を付した表示素子を有する図3の実施の形態に示すような表示素子を駆動する他の回路を有するのが望ましい。この一例は、例えばポリマーLED(PLED)又は有機LED(OLED)の図示したようなLEDを表示素子が具える表示装置であり、それは、電流を発生する55で示す駆動回路を必要とする。スイッチ50を通じて供給されるデータ（ビデオ情報）信号は、記憶ノードキャパシタンスを設けるよう機能するためにスイッチ50及び読み出し回路51と駆動回路55との間に接続されたメモリキャパシタ56の電圧として格納され、駆動回路は、表示素子18'に対する駆動電流を発生するよう動作可能であり、そのレベルは、格納された信号のレベルに対応し又はそれによって決定される。表示素子に対する駆動回路55の追加は別にして、基本的な読み出し及びリフレッシュ動作は、本実施の形態においては図2の実施の形態と同一である。図3の配置において、表示駆動回路55及び読み出し回路51の両方を、画素内で統合して示す。30

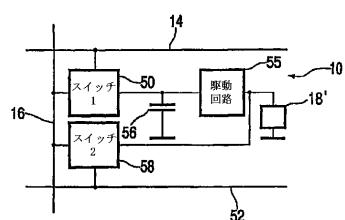

#### 【0033】

一部のケースにおいて、これを、表示駆動回路55の機能を読み出し回路5と組み合わせることによって簡単にすることができる。この一例を図4の実施の形態に示す。この場合、個別の読み出し回路が必要とされないが、その代わりに、第2スイッチ58が、表示素子駆動回路55の出力部と列電極16との間に挿入され、この第2スイッチ58の動作が、補助的な行電極52を通じて制御される。第2スイッチ58が低インピーダンス状態に切り替えられたときに読み出し動作が開始され、そのとき、表示素子18'を駆動する回路55が、画素の状態に依存する電圧まで列電極16を充電する。40

#### 【0034】

50

一般に、静止画像を表示する際、読み出し及びリフレッシュ動作を1行で一度に実行する必要がある。しかしながら、表示アレイの領域（すなわち、複数行）が平坦な背景を有する場合、単一の読み出し及びリフレッシュ動作でこの領域をリフレッシュすることができる。これによって、列電極16に必要な複数の電圧遷移を減少することにより消費される電力を減少する。行反転中に駆動されるAMLCDの場合において、平坦なフィールドを表示する領域に対する読み出し及びリフレッシュ動作を、各極性に対して1回ずつの2回の読み出し及びリフレッシュ動作によって行う。

#### 【0035】

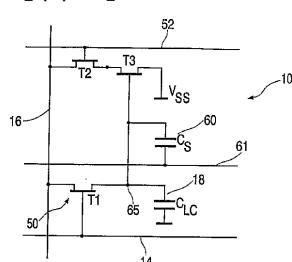

図5は、図2に示したような種類の形態を用いるAMLCD画素回路の一例を更に詳細に示す。本例でnチャネルTFTを示すが、駆動電圧の極性について適切な調整を行った場合には、pチャネルTFT（又はn及びpチャネルの組合せ）を用いることもできる。TFT T2, T3は読み回路51を形成する。本例において、画素は、表示素子18と記憶キャパシタ駆動ライン61との間に接続された記憶キャパシタ60を有し、それは、同一行で他の補助的な行電極の形態の他の画素によって共有される。低電力モードで静止画像を表示する場合、TFT T2, T3は、列電極16の二つの電圧のうちの一方として画素の状態を検知するのに用いられる。画素は、列電極16を通じてリフレッシュされ、LCは、画素がリフレッシュされる度に交互の極性で駆動される。ここで説明するように、回路は、1ビットのデータを画素に格納することができる。AMLCDを通常モードで作動することができ、この場合、表示アレイは、既知の行列駆動アーキテクチャを用いて外部源から連続的に表示装置に送信されるとともに画素10にサンプルされる。このモードにおいて、T3は使用されず、T2は、適切な電圧を補助的な行電極52に供給することによってオフ状態に保持される。

#### 【0036】

低電力モードで静止画像を表示する場合、好適には、共通電極を通じて又は表示素子電極と記憶キャパシタ駆動ライン61との間に接続した記憶キャパシタ60を通じてLC間に電圧の一部が印加される駆動形態が用いられる。これら特定の駆動形態は、読み出し及びリフレッシュ動作を容易にする。

#### 【0037】

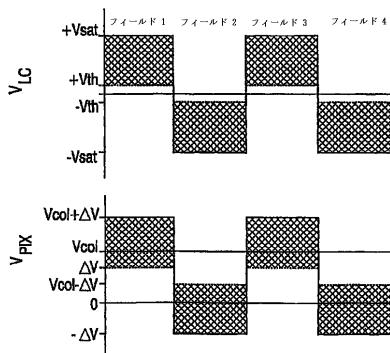

LC間の他の電圧を記憶キャパシタ駆動ライン61を通じて結合する場合を更に詳細に考察する。図6a, 6bは、装置の動作中に出現する典型的な電圧レベルをそれぞれ示す。Vsat, Vthは、LC表示素子飽和電圧レベル及びLC表示素子しきい値電圧レベルをそれぞれ示す。Vco1は、供給されたデータ信号に対応する列電極16の電圧である。図6aは、特定の行の所定の画素に対して四つの連続的なフィールド1~4で画像素子18のLCの両端間の電圧の変化の仕方を示す。LC間の電圧の大きさがVthであるとき、画素は、最大の明るさの状態であり、それがVsatであるとき、画素は黒である。陰影領域は、通常モードの動作で互いに相違するグレースケールを表示する際にLC材料の両端間の電圧の範囲を表す。LC間の電圧の極性は、フィールドごとに反転されてLCの寿命を延ばす。図6bは、列電極の電圧に関連する表示素子電極の対応する電圧を示し、この場合、列電極電圧範囲は、0の最小とVco1の最大との間にある。記憶キャパシタ駆動ライン61を通じて表示素子電極に結合された他の電極は、±Vとなり、この場合、

$$V = V_{cap} \cdot C_s / (C_s + CLC)$$

となり、Vcapは、記憶キャパシタ駆動ライン61で揺れ動く電圧であり、それは、（特定の行に対する）奇数フィールドで+Vcapとなり、（特定の行に対する）偶数フィールドで-Vcapとなり、Cs及びCLCはそれぞれ、記憶キャパシタ60のキャパシタンス及びLC表示素子16のキャパシタンスである。

#### 【0038】

低電力モードで静止画像を表示する際、LCが±Vth（「明」画素）又は±Vsat（「暗」画素）で駆動される。図6bからわかるように、表示素子電極の対応する電圧は、（i）明画素に対して、奇数フィールドで+Vとなるとともに偶数フィールドでVc

10

20

30

40

50

o 1 - V となり、暗画素に対して、奇数フィールドで V c o 1 + V となるとともに偶数フィールドで - V となる。

#### 【 0 0 3 9 】

画素の状態の検知は、記憶キャパシタ駆動ライン 6 1 から  $\pm V$  を結合する前に、表示素子電極の電圧を列電極から画素にサンプルした初期値に戻すことによって行われる。これは、容量ラインの電圧を切り替えることによって行われ、それは、表示素子電極の電圧が 0 又は V c o 1 に戻ることを意味する。明画素に対して、表示素子電極の電圧は、奇数フィールドで 0 に戻り、偶数フィールドで V c o 1 に戻る。暗画素に対して、表示素子電極の電圧は、奇数フィールドで V c o 1 に戻り、偶数フィールドで 0 に戻る。

#### 【 0 0 4 0 】

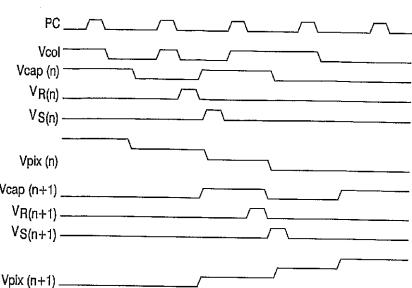

図 5 に示すような画素の検知及びリフレッシュ動作を図 7 に示し、それは、あり得る駆動波形と、同一列電極 1 6 に接続された連続する行  $n$  及び  $n + 1$  の互いに隣接する二つの暗画素に対する関連のタイミングを示す。本例において、LC 駆動電圧の極性が行ごとに反転されている（行反転）のを示すが、これは必要な形態ではない。図 7 において、V cap (n) 及び V cap (n + 1) は、画素行  $n$  及び  $n + 1$  に対して 記憶キャパシタ駆動ライン 6 1 に供給される波形をそれぞれ示し、V s (n) 及び V s (n + 1) は、画素行  $n$  及び  $n + 1$  に関連した行電極 1 4 に供給される選択信号波形をそれぞれ示し、VR (n) 及び VR (n + 1) はそれぞれ、画素行  $n$  及び  $n + 1$  に関連した補助的な行電極 5 2 に供給される波形であり、Vpix (n) 及び Vpix (n + 1) はそれぞれ、画素行  $n$  及び  $n + 1$  の画素（図 5）のノード 6 5 に出現する電圧波形である。検知及びリフレッシュ動作は、以下のステップを伴う。

1 ) 画素電圧を 0 又は V c o 1 に回復するよう 記憶キャパシタ駆動ライン 6 1 をスイッチ。

2 ) 列電極 1 6 を V c o 1 にプレチャージ（図 7 において、プレチャージ制御信号 P C がハイになると、プレチャージが生じる。）。

3 ) 列電極の画素の状態を検知するために T 2 をターンオン。Vpix = V c o 1 の場合、T 3 がターンオンされるとともに、列電極が VSS (0V) まで放電され、Vpix = 0 の場合、T 3 がターンオフされ、列電極電圧が V c o 1 に保持される。これは、列電極電圧が Vpix に対する反転されていることを意味する。

4 ) 記憶キャパシタ駆動ライン 6 1 を以前のレベルに戻す。

5 ) T 1 をターンオンすることによって、反転されたデータを画素に書き戻す。

6 ) LC を駆動するのに適切な他の画素電圧に結合するよう 記憶キャパシタ駆動ライン 6 1 をスイッチする。

所望の場合、Vss は、0V 以外の他の値をとることができる。

#### 【 0 0 4 1 】

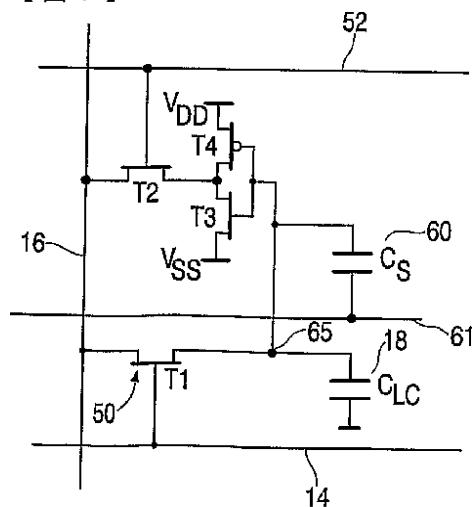

図 2 と同一形態を有するとともに A M L C D に適用される画素回路の第 2 の例を、図 8 に示す。この場合、TFT (p 型及び n 型の) T 4 及び T 3 によって構成されたインバータを用いて、読み出し動作中に画素の状態を検知して列電極 1 6 に読み出し、これによって、読み出し動作以前の列電極のプリチャージの要求を回避する。これは、画像に応じて及びフィールド反転とライン反転のうちのいずれが用いられるかに応じて列電極上の遷移の回数を減少できるという利点を有する。

#### 【 0 0 4 2 】

図 5 及び 8 を参照して既に説明した二つの例において、低電力モードで格納された静止画像はグレースケールを有しない（すなわち、格納された画像は 1 ビット / 画素である）。複数レベルを検出する同一の読み出し回路を用いることによってグレースケールを導入することができる。これを、読み出し時間を複数段階に分割するとともに 記憶キャパシタ駆動ライン 6 1 の電圧をステッピングすることによって行うことができる。これらステップの一つの間、画素の表示素子 1 8 の電圧はしきい値電圧を超え、しきい値電圧より上になると、読み出し回路が列電極の電圧を反転することができる。反転が生じるポイントは、表示素子の初期電圧に依存し、その結果、これは読み出し動作を引き起こす。この場合、画

素をリフレッシュするのに適切な電圧を発生するために他の回路が列駆動回路 35 に要求される。グレースケールを達成する他の方法は、各画素を複数の（エリア分けされた）副画素に細分し、この場合、副画素の各々は、暗又は最大の明るさで駆動されたままである。

#### 【0043】

既に説明した例が、キャパシタライン駆動形態が用いられる状況に対して適用可能であるとしても、同一原理が共通電極駆動形態に適用される。

#### 【0044】

図4と同一形態を有する画素回路の第3の例を、図9に示す。この回路において、TFT T2 は、第2スイッチ58を構成し、TFT T3, T4 は駆動回路55を構成する。表示素子を、LC表示素子又は電流駆動表示素子例えはLEDとすることができます。

10

#### 【0045】

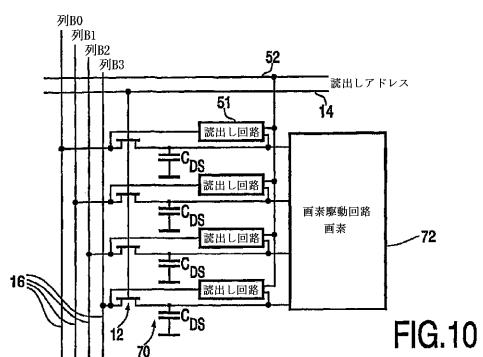

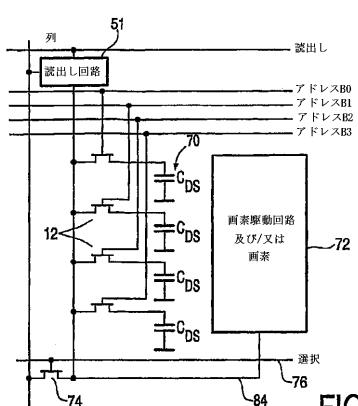

図10は、各々が1ビットデータを格納する複数のキャパシタを有するとともに複数ビットがグレースケールレベルを指定する回路を示す。

#### 【0046】

複数のデータ記憶キャパシタ70は、共通行アドレスライン14に接続したTFT12を通じて対応する複数の列16に接続される。補助的な行電極52は、データ記憶キャパシタ70の各々に対して読み出し回路51を制御する。画素駆動回路72は、データ記憶キャパシタ70の各々からの入力部を有するボックス72によって線形的に表される。

20

#### 【0047】

使用の際には、列16と並列にデータ記憶キャパシタ70にデータを供給することができる。補助的な行電極52に信号を供給することによって、列16からデータを呼び戻すことができ、その結果、データを順次再書き込みしてデータをリフレッシュすることができる。

#### 【0048】

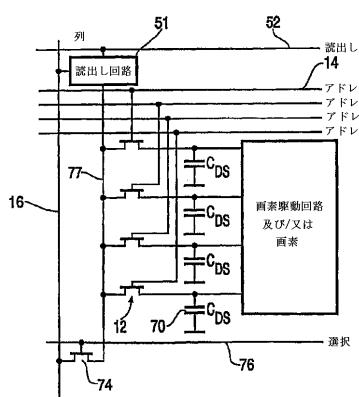

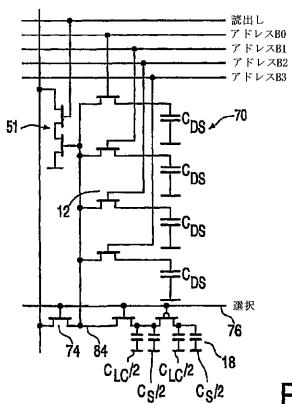

他のマルチビット配置を図11に示し、それは、各行に対する複数のアドレスライン14及び各列に対する単一列ライン16を有する。選択ライン76を各行に設けて、列ライン16をデータライン77を通じてTFT12に接続する選択トランジスタ74を制御する。

30

#### 【0049】

使用の際には、複数のアドレスライン14のうちの一つがイネーブルされて、対応するデータ記憶キャパシタ70が選択される。読み出しライン52をイネーブルして、列ライン16上の選択されたデータ記憶キャパシタ70のデータを読み出せるようにもよい。選択ライン76が選択TFT74をイネーブルして、選択されたデータ記憶キャパシタ70に列ライン16のデータを書き込むこともできる。

#### 【0050】

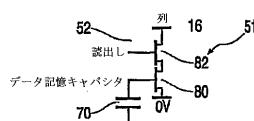

データ記憶キャパシタ70に接続した読み出し回路51の一例を、図12に示す。データ記憶キャパシタ70は、読み出しTFT82を通じて列16に直列接続した第1TFT80を制御する。読み出しTFT82は読み出しライン52によって制御される。リードライン52が読み出しTFT82をスイッチオンすると、データ記憶キャパシタ70に記憶されたデータが列16で読み出される。

40

#### 【0051】

既に説明したように回路72を駆動するためにデータ記憶キャパシタ70の並列接続とともに、複数のデータ記憶キャパシタ70のデータを、図13に図示したような單一データライン84によって駆動回路72に接続することができる。この回路において、個別のTFT12を次々とアドレス指定して対応するデータ記憶キャパシタ70を駆動回路72に接続することによって、データを駆動回路72に転送する。

#### 【0052】

他の実施の形態を図14に示し、それは、画素キャパシタンス18それ自体を用いて順次電荷再分布デジタル・アナログ変換を行う。この回路の特徴は、米国特許第54482

50

58号及び米国特許第5923311号に詳細に記載されており、参照することによってここに組み込まれる。現在の目的のために、図13に示すように、キャパシタ70を、各スイッチ12を通じてデータライン84に接続し、データライン84は画素キャパシタンス18を駆動する。

【0053】

静止モードにおいて画素内に格納されたデータを用いるとともにそれ以外において外部信号源から供給されたデータを用いて、アレイ中の一部の画素を同時に操作することができる。これを、適切な信号を用いてディスプレイを分割するだけで画素回路を変形することなく行うことができる。このアプローチは、電力消費を最小にすることができる。

【0054】

例えば、表示の一部が動画を示し、表示の残りが静止背景を示す。外部ビデオ源は、動画を示す画像の領域のデータをディスプレイに供給するだけでよく、これによって電力をセーブする。

【0055】

本発明は、種々のアクティブマトリックス表示装置に適用可能であり、既に説明したのと同様な画素回路を、AMLCD及びAMLED以外の表示装置に用いることができ、この場合、例えばエレクトロクロミック(electrochromic)タイプ、エレクトロホレティック(electrophoretic)タイプ及びエレクトロルミネセンス(electroluminescent)タイプの表示装置において静止画像を記憶するのが望ましい。アクティブマトリックスLEDの一例は、欧州特許公開番号第115205号に記載されており、その内容を、バックグラウンド材料としてここに組み込む。

【0056】

本発明は、上記実施の形態に限定されるものではなく、幾多の変更及び変形が可能である。

【図面の簡単な説明】

【0057】

【図1】典型的な既知のAMLCDの簡略化した線形図である。

【図2】本発明によるアクティブマトリックス表示装置の各実施の形態における互いに相違する画素回路形態を示す。

【図3】本発明によるアクティブマトリックス表示装置の各実施の形態における互いに相違する画素回路形態を示す。

【図4】本発明によるアクティブマトリックス表示装置の各実施の形態における互いに相違する画素回路形態を示す。

【図5】一実施の形態における典型的な画素回路の一例を更に詳細に示す。

【図6】特定の駆動形態を用いたAMLCDの一例に出現する種々のあり得る電圧レベルを示す。

【図7】AMLCDの一例における動作中の駆動波形の例示を示す。

【図8】本発明によるAMLCDの実施の形態における典型的な画素回路の他の例を詳細に示す。

【図9】本発明によるAMLCDの他の実施の形態における典型的な画素回路の他の例を詳細に示す。

【図10】複数のデータ記憶キャパシタを有する画素回路の他の例を示す。

【図11】複数のデータ記憶キャパシタを有する画素回路の他の例を示す。

【図12】読み出し回路を示す。

【図13】複数のデータ記憶キャパシタを有する画素回路の他の例を示す。

【図14】複数のデータ記憶キャパシタを有する画素回路の他の例を示す。

10

20

30

40

【図1】

FIG.1

【図2】

FIG.2

【図3】

FIG.3

【図4】

FIG.4

【図6】

FIG.6a

FIG.6b

【図5】

FIG.5

【図7】

FIG.7

【図8】

**FIG.8**

【図9】

FIG.9

【図10】

FIG.10

【 図 1 2 】

FIG.12

【図 1 1】

FIG. 11

〔図13〕

**FIG. 13**

【図 1 4】

FIG.14

---

フロントページの続き

|                         |                    |

|-------------------------|--------------------|

| (51)Int.Cl.             | F I                |

| H 01 L 29/786 (2006.01) | G 09 G 3/30 H      |

| H 01 L 51/50 (2006.01)  | H 01 L 29/78 6 1 4 |

|                         | H 05 B 33/14 A     |

(72)発明者 ジョン アール エイ アイレス

オランダ国 5 6 5 6 アーアー アンドーフェン プロフ ホルストラーン 6

(72)発明者 マーティン ジェイ エドワーズ

オランダ国 5 6 5 6 アーアー アンドーフェン プロフ ホルストラーン 6

## 合議体

審判長 小松 徹三

審判官 後藤 亮治

審判官 森 雅之

(56)参考文献 特開昭5 9 - 2 0 8 5 9 0 (JP, A)

特開平1 1 - 2 9 5 7 0 0 (JP, A)

特開平6 - 2 1 4 2 1 4 (JP, A)

特表平1 1 - 5 0 1 4 1 3 (JP, A)

特開平9 - 2 5 8 1 6 8 (JP, A)

特開平1 0 - 2 2 2 1 3 6 (JP, A)

特開昭5 6 - 1 0 4 3 8 7 (JP, A)

特開平1 0 - 6 9 2 4 9 (JP, A)

特開平7 - 7 2 5 1 1 (JP, A)

特開平9 - 2 7 4 2 0 0 (JP, A)

米国特許第5 1 3 0 8 2 9 (US, A)

## (58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/38