(19) 日本国特許庁(JP)

(12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-518523

(P2006-518523A)

(43) 公表日 平成18年8月10日(2006.8.10)

|                                |              |             |

|--------------------------------|--------------|-------------|

| (51) Int.Cl.                   | F I          | テーマコード (参考) |

| <b>G 11 C 29/04 (2006.01)</b>  | G 11 C 29/00 | 603N        |

| <b>G 11 C 11/409 (2006.01)</b> | G 11 C 11/34 | 353F        |

| <b>G 11 C 11/401 (2006.01)</b> | G 11 C 11/34 | 371D        |

審查請求 有 予備審查請求 有 (全 14 頁)

|               |                              |          |                                                                                                                     |

|---------------|------------------------------|----------|---------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2004-557464 (P2004-557464) | (71) 出願人 | 596079127<br>マイクロ・テクノロジー・インコーポレーテッド<br>MICRON TECHNOLOGY, INC.<br>アメリカ合衆国 アイダホ州 83707-0006 ボイシ エス フェデラル<br>ウェイ 8000 |

| (86) (22) 出願日 | 平成15年12月1日 (2003. 12. 1)     |          |                                                                                                                     |

| (85) 翻訳文提出日   | 平成17年7月27日 (2005. 7. 27)     |          |                                                                                                                     |

| (86) 國際出願番号   | PCT/US2003/038226            |          |                                                                                                                     |

| (87) 國際公開番号   | W02004/051662                |          |                                                                                                                     |

| (87) 國際公開日    | 平成16年6月17日 (2004. 6. 17)     |          |                                                                                                                     |

| (31) 優先権主張番号  | 10/309, 572                  | (74) 代理人 | 100078282<br>弁理士 山本 秀策                                                                                              |

| (32) 優先日      | 平成14年12月3日 (2002. 12. 3)     | (74) 代理人 | 100062409<br>弁理士 安村 高明                                                                                              |

| (33) 優先権主張国   | 米国 (US)                      | (74) 代理人 | 100113413<br>弁理士 森下 夏樹                                                                                              |

最終頁に続く

(54) 【発明の名称】異なるメモリ・アレイのカラムにより共有される電流制限ブリーダ・デバイスのための装置および方法

(57)【要約】

異なるメモリ・アレイのカラムの間で共用され、電源にかかる電流負荷を制限し、修復可能なメモリ・デバイスの故障を防止する電流制限ブリーダ・デバイスのための装置及び方法。メモリ・デバイスは、ローとカラムとに配列されたメモリセルを有する第一及び第二メモリ・アレイを含み、第一及び第二メモリ・アレイのカラムの各々は、それぞれのカラムを予備充電するための平衡回路を有する。ブリーダ・デバイスは、予備充電電圧源に結合され、第一メモリ・アレイ中のカラムの少なくとも一つの平衡回路及び第二メモリ・アレイ中のカラムの少なくとも一つの平衡回路にさらに結合され、予備充電電圧源から平衡回路へ流れる電流を制限する。

**【特許請求の範囲】****【請求項 1】**

メモリ・デバイスであって、

ローとカラムとに配列されたメモリセルを有し、カラムの各々は個別のカラムを予備充電するための平衡回路を有する、第一メモリ・アレイ、

ローとカラムとに配列されたメモリセルを有し、カラムの各々は個別のカラムを予備充電するための平衡回路を有する、第二メモリ・アレイ、及び

予備充電電圧源に結合され、前記第一メモリ・アレイ中のカラムの少なくとも一つの平衡回路及び前記第二メモリ・アレイ中のカラムの少なくとも一つの平衡回路にさらに結合され、予備充電電圧源から平衡回路へ流れる電流を制限するブリーダ・デバイス

10 を含むメモリ・デバイス。

**【請求項 2】**

請求項 1 に記載のメモリ・デバイスであって、前記第一メモリ・アレイのカラムに結合された前記少なくとも一つの平衡回路は、前記第一メモリ・アレイの第一及び第二カラムにそれぞれ結合された第一及び第二平衡回路を含み、前記第二メモリ・アレイのカラムに結合された前記少なくとも一つの平衡回路は、前記第二メモリ・アレイの第一及び第二カラムにそれぞれ結合された第一及び第二平衡回路を含む、メモリ・デバイス。

**【請求項 3】**

請求項 1 に記載のメモリ・デバイスであって、前記ブリーダ・デバイスは p チャネル MOS トランジスタを含む、メモリ・デバイス。

20

**【請求項 4】**

請求項 1 に記載のメモリ・デバイスであって、前記ブリーダ・デバイスは前記トランジスタにかかる電圧が増加するにつれて飽和する電流特性を示す、メモリ・デバイス。

**【請求項 5】**

請求項 1 に記載のメモリ・デバイスであって、前記予備充電電圧源は、電源電圧の半分に等しい電圧を持つ電圧源を含む、メモリ・デバイス。

**【請求項 6】**

請求項 1 に記載のメモリ・デバイスであって、前記第一及び第二メモリ・アレイの間に配置されるセンス增幅器領域をさらに含み、前記領域中にセンス增幅器が形成され、またブリーダ・デバイスも形成されるメモリ・デバイス。

30

**【請求項 7】**

メモリ・デバイスであって、

ローとカラムとに配列されたメモリセルを有し、前記カラムの各々は平衡回路を持つ、第一メモリ・アレイ、

ローとカラムとに配列されたメモリセルを有し、前記カラムの各々は平衡回路を持つ、第二メモリ・アレイ、

センス增幅器領域であって、前記領域中に形成された複数のセンス增幅器を有し、各センス增幅器は前記第一メモリ・アレイのそれぞれのカラムに結合され、前記第二メモリ・アレイのそれぞれのカラムにさらに結合されている、センス增幅器領域、及び

前記センス增幅器領域中に形成され、予備充電電圧源、ならびに前記第一メモリ・アレイのカラム及び前記第二メモリ・アレイのカラムの前記平衡回路に結合されているブリーダ・デバイスであって、前記第一及び第二メモリ・アレイの前記カラムは同一のセンス增幅器に結合されている、ブリーダ・デバイス

40 を含むメモリ・デバイス。

**【請求項 8】**

請求項 7 に記載のメモリ・デバイスであって、前記第一及び第二メモリ・アレイの前記カラムは、第一カラムを含み、前記ブリーダ・デバイスは、前記第一メモリ・アレイの第二カラム及び前記第二メモリ・アレイの第二カラムの平衡回路にさらに結合されており、前記第一及び第二メモリ・アレイの前記第二カラムは同一のセンス增幅器に結合されている、メモリ・デバイス。

50

**【請求項 9】**

請求項 7 に記載のメモリ・デバイスであって、前記ブリーダ・デバイスは p チャネル MOS トランジスタを含む、メモリ・デバイス。

**【請求項 10】**

請求項 7 に記載のメモリ・デバイスであって、前記ブリーダ・デバイスはトランジスタにかかる電圧が上昇するのに従って飽和する電流特性を示すトランジスタを含む、メモリ・デバイス。

**【請求項 11】**

請求項 7 に記載のメモリ・デバイスであって、前記予備充電電圧源は電源電圧の半分に等しい電圧を持つ電圧源を含む、メモリ・デバイス。

10

**【請求項 12】**

メモリセルのローとカラムとに配列されたメモリセル有し、各カラムはそれぞれのカラムを予備充電するための平衡回路を持つメモリ・デバイスであって、前記メモリ・デバイスは、複数のセンス増幅器を有するセンス増幅器領域を含み、各センス増幅器は、それぞれの第一アイソレーションスイッチを通してメモリセルの複数の第一カラムのそれぞれ一つに結合され、さらに、それぞれの第二アイソレーションスイッチを通してメモリセルの複数の第二カラムのそれぞれ一つに結合され、前記センス増幅器領域は複数のブリーダ・デバイスをさらに有し、前記ブリーダ・デバイスの各々は、予備充電電圧源、及び前記複数の第一カラムのカラムに連結された少なくとも一つの平衡回路、及び前記複数の第二カラムのカラムに連結された少なくとも一つの平衡回路に結合され、それぞれの平衡回路へ流れる電流を制限する、メモリ・デバイス。

20

**【請求項 13】**

請求項 12 に記載のメモリ・デバイスであって、前記複数のブリーダ・デバイスは複数の p チャネル MOS トランジスタを含む、メモリ・デバイス。

**【請求項 14】**

請求項 12 に記載のメモリ・デバイスであって、前記予備充電電圧源は電源電圧の半分に等しい電圧を持つ電圧源を含む、メモリ・デバイス。

30

**【請求項 15】**

請求項 12 に記載のメモリ・デバイスであって、前記複数のブリーダ・デバイスは、複数のトランジスタを含み、各トランジスタは、トランジスタにかかる電圧が増大するに従って飽和する電流特性を示す、メモリ・デバイス。

**【請求項 16】**

請求項 12 に記載のメモリ・デバイスであって、前記複数の第一カラムのカラムに結合された前記少なくとも一つの平衡回路は、前記複数の第一カラムの第一及び第二カラムにそれぞれ結合された第一及び第二平衡回路を含み、前記複数の第二カラムのカラムに結合された前記少なくとも一つの平衡回路は、前記複数の第二カラムの第一及び第二カラムにそれぞれ結合された第一及び第二平衡回路を含む、メモリ・デバイス。

**【請求項 17】**

メモリ・デバイスであって、

領域中にローとカラムとに配列されたメモリセルが形成されている第一メモリ・アレイ領域であって、前記カラムの各々は、それぞれの平衡回路に結合し、これもまた前記領域中に形成されている第一メモリ・アレイ領域、

40

領域中にローとカラムとに配列されたメモリセルが形成されている第二メモリ・アレイ領域であって、前記カラムの各々は、それぞれの平衡回路に結合し、これもまた前記領域中に形成されている第二メモリ・アレイ領域、

領域中にセンス増幅器及び複数のブリーダ・デバイスを形成しており、各ブリーダ・デバイスは、予備充電電圧源に結合され、前記第一メモリ・アレイ領域中に形成された少なくとも一つの平衡回路、及び前記第二メモリ・アレイ領域中に形成された少なくとも一つの平衡回路にさらに結合されている、センス増幅器領域、及び

前記センス増幅器領域に形成されたセンス増幅器の各々を、前記第一メモリ・アレイの

50

メモリセルのそれぞれのカラム、及び前記第二メモリ・アレイのメモリセルのそれぞれのカラムに結合する複数の第一及び第二アイソレーション・スイッチを含むメモリ・デバイス。

**【請求項 18】**

請求項17に記載のに記載のメモリ・デバイスであって、前記第一メモリ・アレイ領域中に形成された前記少なくとも一つの平衡回路は、前記第一メモリ・アレイ領域中に形成された第一及び第二平衡回路を含み、前記第二メモリ・アレイ領域中に形成された前記少なくとも一つの平衡回路は、前記第二メモリ・アレイ領域中に形成された第一及び第二平衡回路を含む、メモリ・デバイス。

**【請求項 19】**

請求項17に記載のメモリ・デバイスであって、前記複数のブリーダ・デバイスは、複数のpチャネルMOSトランジスタを含む、メモリ・デバイス。

**【請求項 20】**

請求項17に記載のメモリ・デバイスであって、前記複数のブリーダ・デバイスは、複数のトランジスタを含み、各トランジスタは、トランジスタにかかる電圧が増大するに従って飽和する電流特性を示す、メモリ・デバイス。

**【請求項 21】**

請求項17に記載のメモリ・デバイスであって、前記予備充電電圧源は、電源電圧の半分に等しい電圧を持つ電圧源を含む、メモリ・デバイス。

**【請求項 22】**

プロセッサ・バスを有するプロセッサ、

前記プロセッサ・バスを通して前記プロセッサに結合され、前記コンピュータシステムにデータを入力できるようになっている入力装置、

前記プロセッサ・バスを通して前記プロセッサに結合され、前記コンピュータシステムからデータを出力できるようになっている出力装置、及び

前記プロセッサ・バスを通して前記プロセッサに結合されたメモリ・デバイスを含むコンピュータシステムであって、

前記メモリ・デバイスは、メモリセルのローとカラムとに配列されたメモリセルを有し、各カラムはそれぞれのカラムを予備充電するための平衡回路を持ち、前記メモリ・デバイスは、複数のセンス增幅器を有するセンス增幅器領域を含み、各センス增幅器は、それぞれの第一アイソレーションスイッチを通してメモリセルの複数の第一カラムのそれぞれ一つに結合され、さらに、それぞれの第二アイソレーションスイッチを通してメモリセルの複数の第二カラムのそれぞれ一つに結合され、前記センス增幅器領域は複数のブリーダ・デバイスをさらに有し、前記ブリーダ・デバイスの各々は、予備充電電圧源、及び前記複数の第一カラムのカラムに連結された少なくとも一つの平衡回路、及び前記複数の第二カラムのカラムに連結されたされた少なくとも一つの平衡回路に結合され、それぞれの平衡回路へ流れる電流を制限する、コンピュータシステム。

**【請求項 23】**

請求項22に記載のコンピュータシステムであって、前記メモリ・デバイスの前記複数のブリーダ・デバイスは、複数のpチャネルMOSトランジスタを含む、コンピュータシステム。

**【請求項 24】**

請求項22に記載のコンピュータシステムであって、前記メモリ・デバイスの前記予備充電電圧源は、電源電圧の半分に等しい電圧を持つ電圧源を含む、コンピュータシステム。

**【請求項 25】**

請求項22に記載のコンピュータシステムであって、前記メモリ・デバイスの前記複数のブリーダ・デバイスは、複数のトランジスタを含み、各トランジスタは、トランジスタにかかる電圧が増大するに従って飽和する電流特性を示す、コンピュータシステム。

**【請求項 26】**

請求項22に記載のコンピュータシステムであって、前記複数の第一カラムのカラムに結

10

20

30

40

50

合された前記少なくとも一つの平衡回路は、前記複数の第一カラムの第一及び第二カラムにそれぞれ結合された第一及び第二平衡回路を含み、前記複数の第二カラムのカラムに結合された前記少なくとも一つの平衡回路は、前記複数の第二カラムの第一及び第二カラムにそれぞれ結合された第一及び第二平衡回路を含む、コンピュータシステム。

**【請求項 27】**

プロセッサ・バスを有するプロセッサ、

前記プロセッサ・バスを通して前記プロセッサに結合され、前記コンピュータシステムにデータを入力できるようになっている入力装置、

前記プロセッサ・バスを通して前記プロセッサに結合され、前記コンピュータシステムからデータを出力できるようになっている出力装置、及び

前記プロセッサ・バスを通して前記プロセッサに結合されたメモリ・デバイスを含むコンピュータシステムであって、前記メモリ・デバイスは、

ローとカラムとに配列されたメモリセルを有し、カラムの各々はそれぞれのカラムを予備充電するための平衡回路を有する、第一メモリ・アレイ、

ローとカラムとに配列されたメモリセルを有し、カラムの各々はそれぞれのカラムを予備充電するための平衡回路を有する、第二メモリ・アレイ、及び

予備充電電圧源に結合され、前記第一メモリ・アレイ中のカラムの少なくとも一つの平衡回路及び前記第二メモリ・アレイ中のカラムの少なくとも一つの平衡回路にさらに結合され、予備充電電圧源から平衡回路へ流れる電流を制限するブリーダ・デバイスを含む、

コンピュータシステム。

**【請求項 28】**

請求項 27 に記載のコンピュータシステムであって、前記第一メモリ・アレイのカラムに結合された前記少なくとも一つの平衡回路は、前記第一メモリ・アレイの第一及び第二カラムにそれぞれ結合された第一及び第二平衡回路を含み、前記第二メモリ・アレイのカラムに結合された前記少なくとも一つの平衡回路は、前記第二メモリ・アレイの第一及び第二カラムにそれぞれ結合された第一及び第二平衡回路を含む、コンピュータシステム。

**【請求項 29】**

請求項 27 に記載のコンピュータシステムであって、前記メモリ・デバイスの前記ブリーダ・デバイスは、p チャネルMOSトランジスタを含む、コンピュータシステム。

**【請求項 30】**

請求項 27 に記載のコンピュータシステムであって、前記メモリ・デバイスの前記ブリーダ・デバイスは、トランジスタにかかる電圧が増大するに従って飽和する電流特性を示すトランジスタを含む、コンピュータシステム。

**【請求項 31】**

請求項 27 に記載のコンピュータシステムであって、前記メモリ・デバイスの前記予備充電電圧源は、電源電圧の半分に等しい電圧を持つ電圧源を含む、コンピュータシステム。

**【請求項 32】**

メモリセルがメモリセルのローとカラムとに配列されている複数のメモリ・アレイを有し、各カラムはそれぞれの平衡回路に結合されているメモリ・デバイスにおいて、前記平衡回路への電流を制限する方法であって、

第一の複数メモリ・アレイ及び第二の複数メモリ・アレイの間に配置されたセンス增幅器領域を形成し、その中に、前記第一及び第二メモリ・アレイのメモリセルに保存されたデータ状態を増幅するためのセンス増幅器を形成すること、及び

前記センス増幅器領域中に、予備充電電圧源に結合された複数のブリーダ・デバイスを形成し、前記ブリーダ・デバイスの各々は、前記第一メモリ・アレイ中のメモリセルのカラムに連結された少なくとも一つの平衡回路及び前記第二メモリ・アレイ中のメモリセルのカラムに連結された少なくとも一つの平衡回路にさらに結合されることを含む方法。

**【請求項 33】**

10

20

30

40

50

請求項 3 2 に記載の方法であって、複数のブリーダ・デバイスを形成することは、複数の p チャネルMOSトランジスタを形成することを含む、方法。

【請求項 3 4】

請求項 3 2 に記載の方法であって、複数のブリーダ・デバイスを形成することは、複数のトランジスタを形成することを含み、各トランジスタは、トランジスタにかかる電圧が増大するに従って飽和する電流特性を示す、方法。

【請求項 3 5】

メモリセルがメモリセルのローとカラムとに配列されている複数のメモリ・アレイを有し、各カラムはそれぞれの平衡回路に結合されているメモリ・デバイスにおいて、前記平衡回路への電流を制限する方法であって、

第一の複数メモリ・アレイ及び第二の複数メモリ・アレイの間に配置されたセンス增幅器領域を形成し、その中に、前記第一及び第二メモリ・アレイのメモリセルに保存されたデータ状態を増幅するためのセンス増幅器を形成すること、及び

前記第一メモリ・アレイ中のメモリセルのカラムに連結された少なくとも一つの平衡回路と、前記第二メモリ・アレイ中のメモリセルのカラムに連結された少なくとも一つの平衡回路との間で、予備充電電圧源に結合された電流制限ブリーダ・デバイスを共用すること

を含む方法。

【請求項 3 6】

請求項 3 5 に記載の方法であって、前記電流制限ブリーダ・デバイスを共用することは、 p チャネルMOSトランジスタを共用することを含む、方法。 20

【請求項 3 7】

請求項 3 5 に記載の方法であって、前記電流制限ブリーダ・デバイスを共用することは、トランジスタにかかる電圧が増大するに従って飽和する電流特性を示すトランジスタを共用することを含む、方法。

【請求項 3 8】

メモリセルがメモリセルのローとカラムとに配列されている複数のメモリ・アレイを有し、各カラムはそれぞれの平衡回路に結合されているメモリ・デバイスにおいて、前記平衡回路への電流を制限する方法であって、

第一の複数メモリ・アレイ及び第二の複数メモリ・アレイの間に配置されたセンス增幅器領域を形成し、その中に、前記第一及び第二メモリ・アレイのメモリセルに保存されたデータ状態を増幅するためのセンス増幅器を形成すること、及び

前記センス増幅器領域中に形成され、予備充電電圧源に結合された電流制限ブリーダ・デバイスを通して前記第一及び第二メモリ・アレイの前記平衡回路へ流れる電流を制限すること

を含む方法。

【請求項 3 9】

メモリ・デバイスを形成する方法であって、

ローとカラムとに配列されているメモリセルを有し、前記カラムの各々は平衡回路を持つ、第一メモリ・アレイを形成すること、

ローとカラムとに配列されているメモリセルを有し、前記カラムの各々は平衡回路を持つ、第二メモリ・アレイを形成すること、

領域中に複数のセンス増幅器が形成されているセンス増幅器領域を形成し、各センス増幅器を前記第一メモリ・アレイのそれぞれのカラムに結合させ、さらに前記第二メモリ・アレイのそれぞれのカラムに結合させ、及び

ブリーダ・デバイスを前記センス増幅器領域中に形成し、前記ブリーダ・デバイスを予備充電電圧源に結合し、前記第一メモリ・アレイの各カラム及び前記第二メモリ・アレイの各カラムの前記平衡回路へ結合し、前記第一及び第二メモリ・アレイの前記カラムを同一のセンス増幅器に結合すること

を含む方法。

10

20

30

40

50

**【請求項 4 0】**

請求項 3 9 に記載の方法であって、前記センス増幅器領域中にブリーダ・デバイスを形成することは、前記センス増幅器領域中に p チャネル M O S トランジスタを形成することを含む、方法。

**【請求項 4 1】**

請求項 3 9 に記載の方法であって、前記センス増幅器領域中にブリーダ・デバイスを形成することは、トランジスタにかかる電圧が増大するに従って飽和する電流特性を示すトランジスタを前記センス増幅器領域中に形成することを含む、方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】****(技術分野)**

本発明は、全体として、コンピュータ・メモリ分野に、さらに具体的には、異なるメモリアレイのカラムの間で電流制限デバイスを共用することによって、高密度 D R A M アーキテクチャのためのフレキシブルなレイアウト選択を提供する装置及び方法に関する。

**【背景技術】****【0 0 0 2】****(発明の背景)**

一般に知られているように、従来型のダイナミック・ランダム・アクセス・メモリ (D R A M ) デバイスは、ローとカラムとに配列されたメモリセルを有するメモリ・アレイを含む。メモリセルの各々は、一般的に、記憶ノードとして作用するコンデンサと、コンデンサをセンス・ノードに結合するアクセス・デバイスとで形成されており、センス増幅器は、センス・ノードを通してコンデンサの充電状態を感知し、増幅する。センス・ノードは、典型的にはディジット線で表される。ディジット線は、相補的な対にグループ化されており、各対はそれぞれのセンス増幅器に結合されている。一対のディジット線はメモリセルの一カラムに相当する。メモリセルのローへのアクセス・デバイスは、ワード線に結合され、活性化されるとメモリセルをそれぞれのディジット線に結合する。

**【0 0 0 3】**

メモリセルにアクセスするプロセスの一部として、ディジット線の対は、メモリセルへのアクセス動作に備えて、予備充電回路によって「予備充電」される。予備充電によってディジット線対の電圧を平衡させ、予備充電電圧レベルに設定するが、この電圧レベルは、一般にメモリ・デバイスの電源電圧の半分である。この予備充電の間、全てのワード線は、接地され、メモリセルのコンデンサに保持された充電状態が変化しないことを確実にする。メモリセルへのアクセスが行われると、ワード線が活性化し、ロー中のメモリセルを、それぞれのディジット線に結合する。一回にメモリセル・アレイの一ローだけが活性化し、他のメモリセルのワード線は接地され、それらのアクセス・デバイスが不活性状態に確実に留まるようになる。それぞれ対応するディジット線に結合されると、活性化されたローのメモリセルのコンデンサは、ディジット線の電圧を予備充電電圧レベルから変化させる。この電圧変化を、各々のディジット線につながれたセンス増幅器が検知し、これを増幅する。

**【0 0 0 4】**

また、これも周知のことであるが、D R A M のようなメモリ・デバイスは、欠陥のあるロー及びカラムを代替するために、余分のロー及びカラムを含む。すなわち、欠陥メモリがある場所のメモアドレスは、余分のメモリに再マップされる。このようにして、メモリ・デバイスがいくつかの欠陥メモリを含んでいるとしても、冗長メモリを使用することによって正常に動作することができる。例えば、ディジット線がワード線に短絡している場合、よく知られた故障モードが発生する。前で論じたように、メモリへのアクセス動作中は、アクセスされているメモリのあるローを除き、全てのワード線は接地結合されている。ディジット線とワード線とが短絡すると、ディジット線は接地電位状態になる。その結果、そのカラムのいっさいのメモリセルの電圧如何にかかわらず、センス増幅器は、低

い電圧を感知し、増幅することになる。ディジット線と短絡したワード線へのさらなる負担として、短絡した区域において、ワード線が、メモリセルをそれぞれのディジット線に結合させるために十分な電圧を実現できないということがある。その結果、ショートしたローの短絡箇所近辺のメモリセルも不具合となる。欠陥のあるカラム及びローにより、「十字形」の欠陥メモリセルを発生させる故障パターンが生じる。多くの場合において、十字形欠陥の数が利用可能な冗長メモリのロー及びカラムの数を超えるければ、これら欠陥メモリセルのメモリアドレスを再マップすることによって、メモリ・デバイスは、これら冗長メモリを使って正常に動作できる。

#### 【0005】

但し、十分な量の冗長メモリを持っているからといって、十字形欠陥を有するメモリ・デバイスの正常な動作が確実なわけではない。欠陥のあるカラム及びローを、冗長メモリロー及びカラムで代替することはできるが、短絡は存在したままである。前に論じたように、待機状態の間、ワード線は接地され、ディジット線は平衡化され予備充電レベルに予備充電されている。このため、ディジット線とワード線との間の短絡により、予備充電電圧源からアースへの直通路が生じ、これにより、予備充電電圧源に異常に高い電流負荷がかかる。この余分な電流負荷が、予備充電電圧源の駆動能力を超える場合、予備充電電圧源の電圧レベルが低下し、予備充電電圧の許容レベルを下回ることがある。その結果、短絡したディジット線に加え、複数のディジット線が十分に予備充電されず、他の有効なディジット線のメモリセルの不具合を招くことがある。他の有効なディジット線が不具合となるほど極端でなく、故障したメモリセルを、冗長列のメモリで代替できる場合であっても、ディジット線のワード線への短絡に起因する余分な電流負荷によって電力消費が大きくなる。

#### 【0006】

十字形故障が発生した場合に、予備充電電圧源への電流負荷を制限するため取られる従来の取組みの一つは、予備充電電圧源とメモリ・カラムの予備充電回路との間に、ダイオード結合空乏型nチャネルMOS(NMOS)トランジスタを結合することである。空乏型NMOSトランジスタは、予備充電電圧源に負荷される最大電流を、ディジット線に十分な予備充電が可能な許容レベルに制限するよう設計された電流制限デバイスとして機能する。この従来型の取組みの詳細内容については、キリハタ他、「256Mb DRAMのための耐故障設計(Fault-Tolerant Designs for 256Mb DRAM)」、IEEE J.ソリッド・ステート回路、558-66頁、1996年4月、を参照されたい。前記の取組みは効果があるが、空乏型NMOSの形成には、ファブリケーション工程の一部として、追加の空乏注入ステップが必要である。一般に、工程ステップの追加は必然的にウェーハの処理歩留まりを低下させてるので、望ましくないと考えられている。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

したがって、修復可能な欠陥に起因する異常な高電流負荷の発生の場合に、電源に負荷される電流を制限するための別の取組みが必要である。

#### 【課題を解決するための手段】

#### 【0008】

##### (本発明の概要)

本発明は、異なるメモリ・アレイのカラムの間で共用され、電源への負荷電流を制限して修復可能なデバイス故障を防止するための電流制限ブリーダ・デバイスを有するメモリ・デバイスを対象とする。本メモリ・デバイスは、ロー及びカラムに配置されたメモリセルを有する第一及び第二メモリ・アレイを含む。第一及び第二メモリ・アレイのカラムの各々は、それらカラムを予備充電する平衡回路に結合されている。メモリ・デバイスには、さらに、予備充電電圧源に結合され、第一メモリ・アレイの少なくとも一つの平衡回路と第二メモリ・アレイの少なくとも一つの平衡回路とにさらに結合されたブリーダ・デバ

10

20

30

40

50

イスが含まれる。ブリーダ・デバイスは、予備充電電圧源から平衡回路へ流れる電流を制限する。本発明の一つの様態において、センス増幅器の領域は、第一メモリ・アレイと第二メモリ・アレイとの間に配置される。センス増幅器は、前記センス増幅器領域中に形成され、ブリーダ・デバイスもこの領域中に形成される。センス増幅器の各々は、第一メモリ・アレイの各カラム及び第二メモリ・アレイのカラムに結合される。

#### 【発明を実施するための最良の形態】

##### 【0009】

###### (発明の詳細な説明)

本発明の実施形態は、修復可能な欠陥に起因して異常な高電流が発生した場合に、電源にかかる電流負荷を制限するための、異なったメモリ・アレイのカラムの間で共有される電流制限ブリーダ・デバイスを有するメモリ・デバイスを対象とする。以下の本発明の典型的な実施形態の詳細説明において、添付図面を参照するが、これら図面は本明細書の一部であり、これらには、本発明を実施することができる具体的な代表例が図によって示されている。これらの実施形態を、当業者が本発明を実施することができるように、十分詳細に説明する。しかしながら、これらの特定な内容によらなくても、本発明が実施できることは、当業者には自明であろう。他の事項として、本発明を必要に分かり難くすることを避けるために、よく知られている回路、制御信号、タイミングプロトコル、ソフトウェア・オペレーションの詳細は示していない。本発明の精神と範囲から逸脱することなく、他の実施形態を用い、変更を加えることができよう。したがって、以下の詳細説明を内容を限定的な意味で理解すべきでなく、本発明の範囲は添付の請求事項だけによって規定される。

##### 【0010】

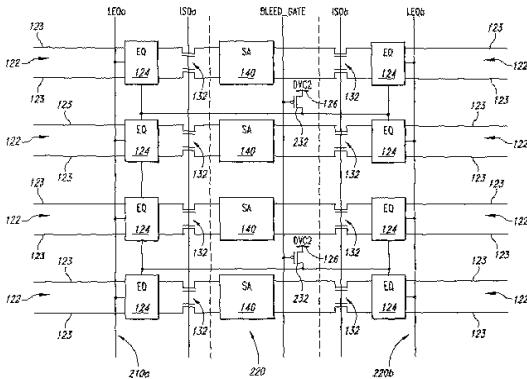

図1は、メモリ・アレイ領域110a、110bの間に設置されたセンス増幅器領域120の図である。図1は簡略化されたブロック図であって、本発明を分かり難くすることを避けるために、細部が省略されていることを理解いただけるであろう。但し、省略された細部は、それなくとも、本明細書で提示する内容に基づいて当業者が本発明を実施できるようなものである。

##### 【0011】

一般に、各メモリ・アレイ領域110a、110bの中のメモリセル(図示せず)は、ワード線のロー(図示せず)及びディジット線123のカラム122に配列されている。図1に示すように、メモリセルのカラム122の各々は、相補ディジット線123の対で形成される。平衡回路124は、相補ディジット線の各対に結合されており、この技術で周知されているように、アクセス動作の準備のため、それぞれのディジット線123を「予備充電」する。一般的には、平衡回路124は、活性化信号L E Q a、L E Q bによって活性化され、その時、メモリセルのカラム122のディジット線123は共に結合されてディジット線123の対の電圧を平衡させ、同時にDVC2電圧源126に結合されて、カラム122のディジット線123を予備充電圧レベルに充電する。DVC2電圧源126の電圧レベルは、一般にメモリ・デバイスの電源電圧の半分であり、既存技術でよく知られた従来型の電圧発生回路で発生させることができる。DVC2電圧源126は、それぞれのメモリ・アレイ領域110a、110b中に形成された比較的長いnチャネルMOS(NMOS)ブリーダ・デバイス130を通して各平衡回路124に供給される。NMOSブリーダ・デバイス130のドレインはDVC2電圧源126に結合されており、ソースは少なくとも一つの平衡回路124に結合されている。メモリ・アレイ領域110a、110bに対するNMOSブリーダ・デバイス130のゲートは、L E Q a、L E Q b信号と調整された活性化信号B L E E D a、B L E E D bを供給するそれぞれの制御ラインに結合され、ディジット線123をDVC2電圧源126の電圧レベルに予備充電する。後記でさらに詳細を説明するように、NMOSブリーダ・デバイス130は、ディジット線123がワード線と短絡した場合に、DVC2電圧源126にかかる電流負荷を制限するためにも使われる。

##### 【0012】

10

20

30

40

50

カラム 122 のディジット線 123 は、平衡回路 124 に加えて、それぞれのアイソレーション・トランジスタ 132 の対に結合されている。アイソレーション・トランジスタ 132 は、活性化信号 ISOa、ISOb によって活性化されると、カラム 122 をそれぞれのセンス増幅器 140 に選択的に結合する。

#### 【0013】

図 1 に示すように、センス増幅器 140 は、一般的に、2つのメモリ・アレイ領域 110a、110b の間に配置されたセンス増幅器領域 120 中に形成される。アイソレーション・トランジスタ 132 は、2つの異なるメモリ・アレイ領域 110a、110b のカラム 122 が一つのセンス増幅器 140 を共用できるようにする。すなわち、メモリ・アレイ領域 110a 又は 110b のいずれかにアクセスする際には、そのメモリ・アレイ領域のアイソレーション・トランジスタ 132 が活性化され、カラム 122 をセンス増幅器 140 に結合させる。他方のメモリ・アレイ領域のアイソレーション・トランジスタ 132 は不活性のままで、対応センス増幅器 140 からカラム 122 を隔離する。

#### 【0014】

前記のように、NMOS ブリーダ・デバイス 130 は、ディジット線がワード線と短絡した場合に、DVC2 電圧源 126 から流れる電流を制限する比較的長チャネルのトランジスタである。前に説明したように、待機状態の間、メモリ・アレイのワード線は接地され、ディジット線 123 は、DVC2 電圧発生器 126 の電圧レベルに予備充電される。このため、平衡回路 124 が活性化されている間は、ワード線と短絡したディジット線 123 を通して DVC2 電源 126 は接地電位に短絡される。NMOS ブリーダ・デバイス 132 も、待機状態の間、BLEEDa 及び BLEEDb 信号によって活性化されているが、これは、ディジット線 123 がワード線と短絡した場合に、アースに落ちる電流を制限する負荷デバイスとして機能する。NMOS ブリーダ・デバイス 132 は、ある程度電流を制限する働きをするが、ディジット線 123 の電圧は、ワード線との短絡により接地電位に引き下げられ（すなわち接地結合）、ゲート - ソース間電圧（すなわち、BLEED 信号とディジット線 123 の低下した電圧との電位差）及びドレイン - ソース間電圧（すなわち、DVC2 電圧源 126 の電圧とディジット線 123 の低下した電圧との電位差）の双方が増加するので、NMOS ブリーダ・デバイス 132 を通る電流は電圧の平方で増加する。上記のように、NMOS ブリーダ・デバイス 132 は、ディジット線 123 とワード線が短絡した場合にある程度の電流制限効果を備えているものの、DVC2 電源 126 から流れる電流を制限するための別の取組み方がさらに必要となる。

#### 【0015】

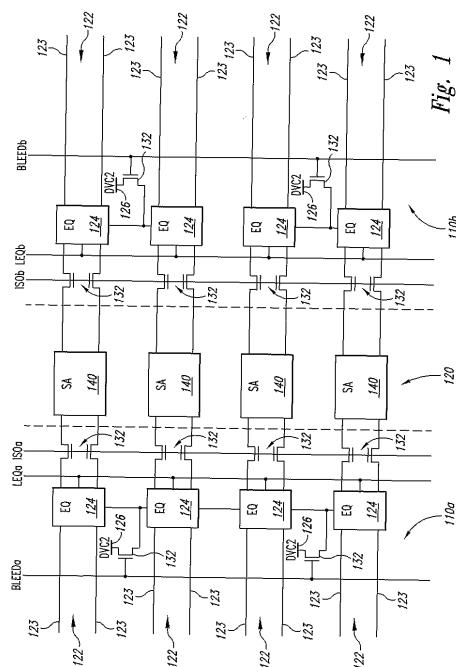

図 2 は、本発明の一つの実施形態に従ったセンス増幅器領域 220 及びメモリ・アレイ領域 210a、210b の一部の図である。図 2 において、類似の数字は、前の図 1 に記載されたのと実質的に同様な構成要素を表す。センス増幅器領域 220 は、メモリ・アレイ領域 210a、210b の間に配置されている。図 1 のように、図 2 中に図示されているメモリ・アレイ領域 210a、210b の一部には、カラム 122 の相補ディジット線 123 の各対に結合された平衡回路 124 が含まれている。平衡回路 124 は、前に説明したように、LEQa 及び LEQb 信号活性に応じて、それぞれのディジット線 123 を予備充電する。ディジット線 123 の相補対の各々には、アイソレーション・トランジスタ 132 の対がさらに結合され、これはメモリ・アレイ領域 210a、210b のディジット線 123 を、センス増幅器領域 220 に形成されたセンス増幅器 140 へ選択的に結合し、また分離させる。

#### 【0016】

図 1 と対照的に、図 2 に示す実施形態は、ディジット線 123 がワード線と短絡した場合に DVC2 電圧源 126 から流れ出す電量を制限するために、センス増幅器領域 220 に形成された p チャネル MOS (PMOS) ブリーダ・デバイス 232 を使っている。ブリーダ・デバイス 232 は、共通制御信号 BLEED\_GATE によって制御され、平衡回路 124 の活性化と連動して活性化され、ディジット線 123 を DCV2 電源 126 の電圧レベルに予備充電する。

10

20

30

40

50

## 【0017】

前に図1に関連して論じたように、N M O S ブリーダ・デバイス132を通る電流は、待機状態時にディジット線123とワード線とが接地短絡した場合に、電圧の平方で増加する傾向がある。しかしながら、図2に示す実施形態中のP M O S ブリーダ・デバイス232は、同一状態の下で飽和する電流特性を示す。すなわち、N M O S ブリーダ・デバイス132においては、ディジット線が接地電位に低下すると、ゲート-ソース及びドレイン-ソース双方の電圧が増大し、これにより、電流が幾何級数的に増加するのに対し、P M O S ブリーダ・デバイス232においては、ゲート-ソース電圧は一定である（すなわち、ゲートはLOW B L E E D \_ G A T E信号に結合され、ソースはD V C 2電圧源126に結合されている）。その結果、ディジット線123の接地電位への低下によりドレイン-ソース電圧が増加するにつれ、P M O S ブリーダ・デバイス232のドレイン-ソース電流は飽和し、これによって、D V C 2電圧源126への電流負荷が制限される。

## 【0018】

さらに、図2に示す本発明の実施形態において、ブリーダ・デバイス232は、2つのメモリ・アレイ領域210a、210bのカラム122の間で共用されている。これにより、図3に示した配列に比較して、メモリ・デバイス上のブリーダ・デバイス232の数を削減することができる。加えて、複数のメモリ・アレイ領域210a、210bの間でブリーダ・デバイス232を共用することによって、ブリーダ・デバイス232を作動するために必要な制御線の数が減少する。図示していないが、ブリーダ・デバイス232及びブリーダ制御線の低減によって、センス增幅器領域220及びメモリ・アレイ領域210a、210bのレイアウトが簡素化されることは、当業者には自明であろう。結果として、本発明の実施形態から、多くの利点を得ることができる。例えば、ブリーダ・デバイス232及びB L E E D \_ G A T E線のような、前記の回路構成のため形成される金属配線を、いくつものメモリ・アレイ領域210a、210b及びセンス增幅器領域220に広げるのでなく、特定の領域に限定することができる。さらに、一部の金属配線レイアウトを再配列することによって、他の信号線の経路変更も可能となる。例えば、ブリーダ制御線を特定領域に限定配置することによって、より低位の金属配線レベルからこれらの線を形成することができ、これにより、他の信号線を、センス增幅器領域を通して別の金属配線レベル上の経路設定の際、より柔軟に対処することができ、誘電体中間層に形成されたビアスを通して別の金属配線層へ接続する必要を回避できる。当業者には自明であろうが、金属配線を一つの金属配線層から別の層へジャンプさせるとその信号線のインピーダンスが増加し、その結果、メモリ・デバイスの全体的性能に影響する信号のタイミング及び速度問題が発生する。

## 【0019】

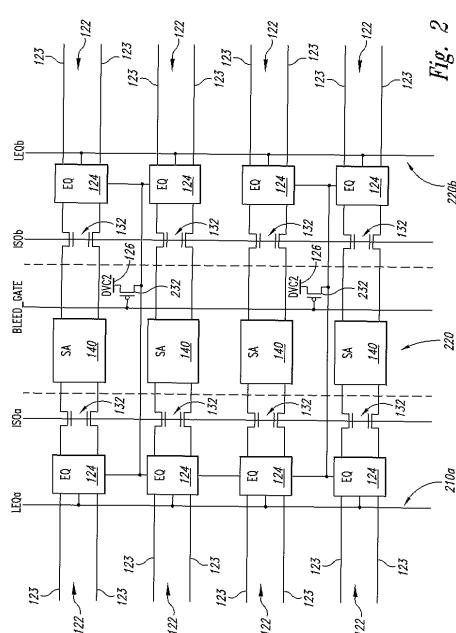

図3は、本発明の実施形態に従ってたメモリ・デバイス310を組み込んだコンピュータシステムのような電子システム312のブロック図である。システム312は、所望の計算及びタスクを遂行するためのソフトウェアを実行するといったコンピュータ機能を実施するためのコンピュータ回路314をも含む。回路314は、一般的に、プロセッサ316と、プロセッサ316に結合されたメモリ回路310とを含む。コンピュータ回路314にはキーボードやマウスのような一つ以上の入力装置318が結合され、操作者（図示せず）がデータを手動入力できるようにしている。コンピュータ回路314が生成したデータを操作者に提供するため、一つ以上の出力装置320がコンピュータ回路314に結合されている。このような出力装置320の例には、プリンター及び映像ディスプレ装置が含まれる。外部記憶媒体（図示せず）へのデータ格納又はこれからデータ読み取りをするための、一つ以上のデータ記憶装置322がコンピュータ回路314に結合されている。記憶装置322及び対応する記憶媒体の例には、ハード及びフロッピー（登録商標）・ディスク、テープカセット、及びコンパクトディスク読み取り専用メモリ（C D - R O M）に対応するドライブが含まれる。通常、コンピュータ回路314は、それぞれ、メモリ・デバイス310のA D R E S S、D A T A、及びC O M M A N Dバス、ならびに、C L K線に結合された、アドレス、データ及びコマンドバス、ならびに、クロック線を含む

10

20

30

40

50

。

## 【0020】

例証目的のため、本発明の特定の実施形態を本明細書で説明したが、本発明の精神及び範囲から逸脱することなく様々な修正案が作成できることは、前記から自明であろう。例えば、本発明の前記の実施形態は、センス増幅器領域220に形成されたブリーダ・デバイス232を含む。しかしながら、本発明の精神から逸脱することなく、異なったメモリ・アレイ領域210a、210bのカラム122の間で共用されるブリーダ・デバイス232をセンス増幅器領域220以外の領域に形成できることは自明であろう。さらに、特定の実施形態においてブリーダ・デバイス232を、PMOSトランジスタとして説明した。本発明の範囲を逸脱することなく、他の電流制限デバイスも同様に使用できることは当業者には自明であろう。したがって、本発明は、添付の請求範囲による以外には限定されない。

## 【図面の簡単な説明】

## 【0021】

【図1】図1は、メモリ・デバイスのセンス増幅器領域及びメモリ・アレイ領域の一部を示す簡単なブロック図である。

【図2】図2は、本発明の実施形態に従ったメモリ・デバイスのセンス増幅器領域及びメモリ・アレイ領域の一部を示す簡単なブロック図である。

【図3】図3は、本発明の実施形態に従ったメモリ・デバイスを含むコンピュータシステムの機能ブロック図である。

10

20

【図1】

【図2】

【図3】

Fig. 3

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 トムソン , ジェイ . ウエイン

アメリカ合衆国 アイダホ 83712 , ボイジ , ノース モーニングサイド ウェイ 52

5

(72)発明者 ラード , ジョージ ピー .

アメリカ合衆国 アイダホ 83706 , ボイジ , スピンネイカー コート 1735

(72)発明者 キルシュ , ハワード シー .

アメリカ合衆国 アイダホ 83616 , イーグル , ウエスト ボーガス ビュー ドライブ

479

F ターム(参考) 5L106 AA01 EE02 GG05

5M024 AA06 BB15 BB37 CC63 GG20 LL01 PP01 PP03