(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4340296号

(P4340296)

(45) 発行日 平成21年10月7日(2009.10.7)

(24) 登録日 平成21年7月10日(2009.7.10)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| HO3M 1/18 (2006.01)  | HO3M 1/18  |

| HO3M 1/56 (2006.01)  | HO3M 1/56  |

| HO3M 1/08 (2006.01)  | HO3M 1/08  |

| HO4N 5/335 (2006.01) | HO4N 5/335 |

|                      | A          |

|                      | HO4N 5/335 |

|                      | E          |

|                      | HO4N 5/335 |

|                      | Z          |

請求項の数 10 (全 28 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2007-18771 (P2007-18771)    |

| (22) 出願日  | 平成19年1月30日 (2007.1.30)        |

| (65) 公開番号 | 特開2008-187420 (P2008-187420A) |

| (43) 公開日  | 平成20年8月14日 (2008.8.14)        |

| 審査請求日     | 平成20年1月18日 (2008.1.18)        |

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 000005049<br>シャープ株式会社<br>大阪府大阪市阿倍野区長池町22番22号 |

| (74) 代理人  | 100114476<br>弁理士 政木 良文                       |

| (72) 発明者  | 丸山 正彦<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内    |

審査官 栗栖 正和

最終頁に続く

(54) 【発明の名称】 A／D変換器

## (57) 【特許請求の範囲】

## 【請求項1】

電圧値が一定期間単調変化するランプ電圧を発生するランプ電圧発生回路と、

被変換アナログ電圧をサンプリングホールドし、サンプリングホールドされた前記被変換アナログ電圧と、前記ランプ電圧発生回路から発生されるランプ電圧の電圧変化値または前記電圧変化値に比例する電圧値で与えられる参照電圧とを比較する演算器を備え、前記参照電圧が前記被変換アナログ電圧に等しくなった時点での出力変化する電圧比較回路と、

前記参照電圧に応じたディジタル値を計数して出力するカウンタと、

前記カウンタから出力される前記ディジタル値を前記電圧比較回路の出力変化時にラッチして出力するラッチ回路と、を備えたA／D変換器であって、

前記被変換アナログ電圧に含まれるノイズ成分を平均化して平均ノイズ電圧を求める平均化処理回路と、

前記平均ノイズ電圧の目標値としての目標ノイズ電圧を設定する目標ノイズ電圧設定回路と、

前記平均ノイズ電圧と前記目標ノイズ電圧の差に基づいて、前記ランプ電圧発生回路によって前記参照電圧が基準電圧レベルから変化を開始する前記制御基準タイミングに対する前記カウンタの計数開始タイミングの調整、及び、前記カウンタの計数開始タイミングにおける前記参照電圧の前記基準電圧レベルの調整の内、少なくとも前記カウンタの前記計数開始タイミングの調整を行う制御回路を備えることを特徴とするA／D変換器。

**【請求項 2】**

前記制御回路は、前記平均ノイズ電圧と前記目標ノイズ電圧の差を示す指標値を算出し、前記指標値に応じて前記カウンタの前記計数開始タイミングを調整するカウンタ待機時間を算出し、前記カウンタの前記計数開始タイミングを前記カウンタ待機時間に応じて調整することを特徴とする請求項1に記載のA/D変換器。

**【請求項 3】**

前記制御回路は、

前記平均ノイズ電圧と前記目標ノイズ電圧の差を示す指標値を算出し、前記指標値に応じて前記カウンタの前記計数開始タイミングを調整するカウンタ待機時間を算出し、

10

前記平均ノイズ電圧が前記目標ノイズ電圧を上回る場合に、前記制御基準タイミングに対する前記計数開始タイミングを前記カウンタ待機時間に応じて遅らせ、

前記平均ノイズ電圧が前記目標ノイズ電圧を下回る場合に、前記制御基準タイミングに対する前記計数開始タイミングを前記カウンタ待機時間に応じて早め、更に、前記制御基準タイミングにおける前記参照電圧の前記基準電圧レベルの調整量を前記指標値に基づいて算出し、前記制御基準タイミング前に、前記ランプ電圧の電圧変化方向とは反対の方向に、前記参照電圧の前記基準電圧レベルを前記調整量だけ変化させることを特徴とする請求項1に記載のA/D変換器。

**【請求項 4】**

前記制御回路は、

20

前記平均ノイズ電圧と前記目標ノイズ電圧の差を示す指標値を算出し、

前記指標値に基づいて、前記計数開始タイミングにおける前記参照電圧の前記基準電圧レベルの調整量を算出し、

前記計数開始タイミング前に、前記ランプ電圧の電圧変化方向に、前記参照電圧の前記基準電圧レベルを前記調整量に基づいて変化させることを特徴とする請求項1に記載のA/D変換器。

**【請求項 5】**

前記制御回路は、

前記平均ノイズ電圧が前記目標ノイズ電圧を下回る場合に、前記指標値に基づいて、前記計数開始タイミングにおける前記参照電圧の前記基準電圧レベルの調整量を算出し、

30

前記計数開始タイミング前に、前記ランプ電圧の電圧変化方向とは反対の方向に、前記参照電圧の前記基準電圧レベルを前記調整量に基づいて変化させることを特徴とする請求項4に記載のA/D変換器。

**【請求項 6】**

前記ランプ電圧発生回路は、

定電流源からの電流値を複製する第1カレントミラー回路及び第2カレントミラー回路と、

前記第1カレントミラー回路で複製した電流により放電し、前記第2カレントミラー回路で複製した電流により充電する積分容量と、

前記積分容量に対する前記第1カレントミラー回路による放電及び前記第2カレントミラー回路による充電を逐一的に切り替えるスイッチ回路と、を備えて構成されることを特徴とする請求項1～5の何れか1項に記載のA/D変換器。

40

**【請求項 7】**

前記演算器が、インバータ回路を用いて構成され、

前記インバータ回路の入力判定電圧に前記被変換アナログ電圧と前記参照電圧の差電圧を加えた合成電圧を前記インバータ回路の入力電圧として発生させる電圧合成回路を備えていることを特徴とする請求項1～6の何れか1項に記載のA/D変換器。

**【請求項 8】**

前記演算器が、前記被変換アナログ電圧と前記ランプ電圧を夫々入力電圧とする差動入力型の演算增幅器で構成されていることを特徴とする請求項1～6の何れか1項に記載の

50

A / D 変換器。

【請求項 9】

前記制御回路は、前記参照電圧の前記基準電圧レベルを、前記ランプ電圧の電圧変化方向とは反対の方向に変化させる場合に、前記ランプ電圧発生回路を反転動作させることを特徴とする請求項 1 ~ 8 の何れか 1 項に記載の A / D 変換器。

【請求項 10】

光電変換素子の複数がマトリクス状に配列してなるセンサ部と、

前記センサ部の各列に夫々対応して設けられた、請求項 1 ~ 9 の何れか 1 項に記載の A / D 変換器の前記電圧比較回路及び前記ラッチ回路からなる A / D 変換ユニットの複数と、

10

前記 A / D 変換器の前記ランプ電圧発生回路と、前記カウンタと、前記平均化処理回路と、前記目標ノイズ電圧設定回路と、前記制御回路と、を備え、

前記センサ部の周囲の一部に、遮光した光学的黒画素部が設けられ、

前記平均化処理回路は、前記光学的黒画素部の出力信号に対する前記 A / D 変換ユニットの A / D 変換値を平均化して前記平均ノイズ電圧を求める特徴とするセンサシステム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、A / D 変換器、特に、電圧値が一定期間単調変化するランプ電圧を発生するランプ電圧発生回路と、被変換アナログ電圧をサンプリングホールドし、サンプリングホールドされた前記被変換アナログ電圧と、前記ランプ電圧発生回路から発生されるランプ電圧の電圧変化値または前記電圧変化値に比例する電圧値で与えられる参照電圧とを比較する演算器を備え、前記参照電圧が前記被変換アナログ電圧に等しくなった時点で出力変化する電圧比較回路と、前記参照電圧に応じたディジタル値を計数して出力するカウンタと、前記カウンタから出力される前記ディジタル値を前記電圧比較回路の出力変化時にラッチして出力するラッチ回路と、を備えた A / D 変換器に関する。

20

【背景技術】

【0002】

近年、固体撮像素子に用いられる A / D 変換器には、高速、低消費電力であることが益々要求されている。当該要求を満たすためにコラム型 A / D 変換器（例えば、下記特許文献 1 参照）が用いられることが多い。

30

【0003】

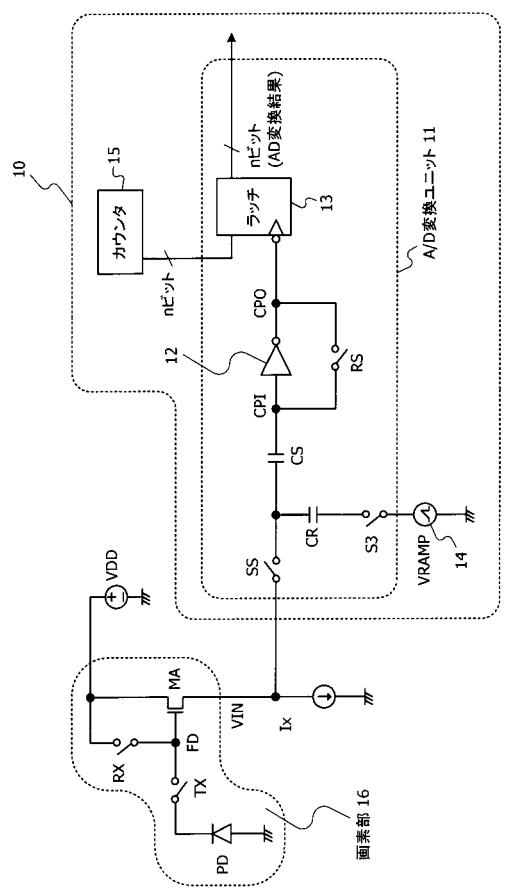

図 1 に、従来のコラム型 A / D 変換器のブロック図を示す。コラム型 A / D 変換器 10 は、A / D 変換ユニット 11、ランプ電圧  $V_{RAMP}$  を発生するランプ電圧源 14（ランプ電圧発生回路）、ランプ電圧の電圧変化値に応じたディジタル値（n ビットの 2 値信号）を計数して出力するカウンタ 15 を備えて構成されている。A / D 変換ユニット 11 は、回路要素として、インバータ回路 12 と、インバータ回路 12 の入力ノード C P I 及び出力ノード C P O を短絡するスイッチ R S、被変換アナログ電圧をサンプリングするためのキャパシタ C S、電圧値が一定期間単調変化するランプ電圧  $V_{RAMP}$  を入力ノード C P I に伝送するためのキャパシタ C R とスイッチ S 3、被変換アナログ電圧をサンプリングするためのスイッチ S S、被変換アナログ電圧に応じたカウンタ出力をラッチするためのラッチ回路 13 を備える。更に、図 1 では、コラム型 A / D 変換器 10 に対し、固体撮像素子の画素部 16 及びノード V I N に接続された定電流源 I X が合わせて図示されている。

40

【0004】

コラム型 A / D 変換器 10 の A / D 変換動作について、図 2 の動作タイミング図を参照して説明する。

【0005】

タイミング t 1 で、画素部 16 のスイッチ R X をオンにすることで、ノード F D が電圧

50

$V_{DD}$  にリセットされ、ノード V<sub>IN</sub> が MOS トランジスタ M<sub>A</sub> を介して高電位に充電される。また、同時にスイッチ R<sub>S</sub> がオンして、インバータ回路 12 の入力ノード C<sub>PI</sub> と出力ノード C<sub>PO</sub> が短絡して、入力ノード C<sub>PI</sub> がインバータ回路 12 の入力判定電圧（オートゼロレベル）に自動的にリセットされる。同時にスイッチ S<sub>3</sub> がオンするが、他のスイッチ S<sub>3</sub>、T<sub>X</sub> はオフ状態である。

## 【0006】

タイミング t<sub>2</sub> で、スイッチ R<sub>X</sub> をオフにすることで、ノード V<sub>IN</sub> には、リセット電圧が現れる。タイミング t<sub>3</sub> で、スイッチ R<sub>S</sub> をオフにすることで、キャパシタ C<sub>S</sub> には、リセット電圧がサンプリングされる。

## 【0007】

引き続き、タイミング t<sub>4</sub> で、スイッチ T<sub>X</sub> をオンにすると、画素部 16 の光電変換素子（フォトダイオード）P<sub>D</sub> で光電変換された蓄積された電荷がノード F<sub>D</sub> に転送され、ノード V<sub>IN</sub> には、光電変換された電荷量に応じた電圧レベル（光電変換レベル）に遷移する。ノード V<sub>IN</sub> の電圧レベルが安定するタイミング t<sub>5</sub> で、スイッチ T<sub>X</sub> をオフにし、スイッチ S<sub>3</sub> をオンにすると、キャパシタ C<sub>R</sub> には、その時点でのノード V<sub>IN</sub> の電圧レベル（光電変換レベル）とランプ電圧 V<sub>RAMP</sub> の初期電圧との差電圧が保持される。

## 【0008】

引き続き、タイミング t<sub>6</sub> で、スイッチ S<sub>S</sub> をオフにすることで、入力ノード C<sub>PI</sub> には、ノード V<sub>IN</sub> のリセット電圧（タイミング t<sub>3</sub>）と光電変換レベル（タイミング t<sub>6</sub>）の差分値 V<sub>SIG</sub> が、被変換アナログ電圧として保持される。

## 【0009】

タイミング t<sub>7</sub> で、ランプ電圧 V<sub>RAMP</sub> の電圧値を徐々に増加し始めると、入力ノード C<sub>PI</sub> の電圧も、ランプ電圧 V<sub>RAMP</sub> の電圧増加分に比例して増加する。また、タイミング t<sub>7</sub> で、カウンタ 15 のカウントアップも同時に開始させる。

## 【0010】

タイミング t<sub>8</sub> で、入力ノード C<sub>PI</sub> の電圧レベルが、インバータ回路 12 の入力判定電圧を超えると、インバータ回路 12 は出力ノード C<sub>PO</sub> の出力レベルを反転させる。ラッチ回路 13 は、出力ノード C<sub>PO</sub> の出力変化に応答してカウンタ出力の値を保持する。

## 【0011】

ここで、差分値 V<sub>SIG</sub> は、光電変換素子 P<sub>D</sub> への入射光量に応じた電圧であり、ラッチされたカウンタ出力の値は、差分値 V<sub>SIG</sub> の A/D 変換値（デジタル値）である。以上の要領で、ラッチ回路 13 で保持された A/D 変換値を出力することで、コラム型 A/D 変換器 10 は、被変換アナログ電圧 V<sub>SIG</sub> の A/D 変換動作を完了する。

## 【0012】

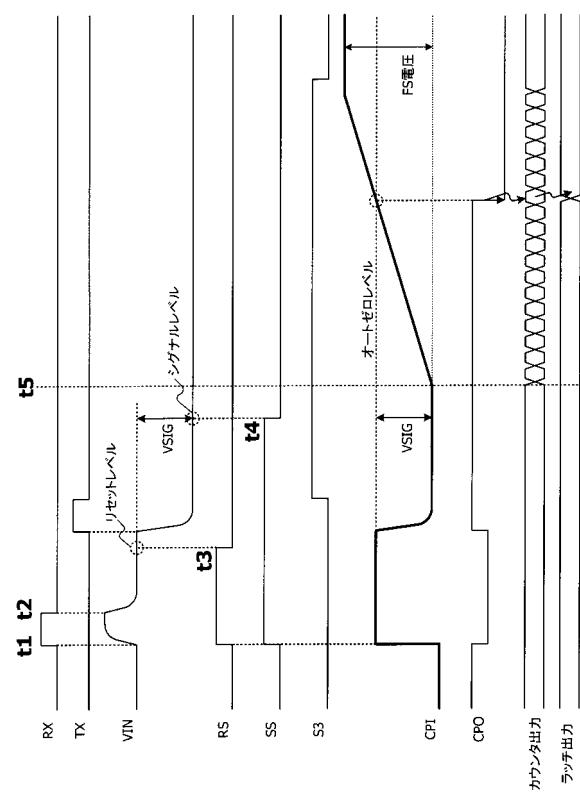

図 3 に、コラム型 A/D 変換器 10 において、被変換アナログ電圧 V<sub>SIG</sub> とランプ電圧 V<sub>RAMP</sub> の電圧増加値との間の電圧比較を行なうインバータ回路 12 の入出力特性を示す。インバータ回路 12 では、上記電圧比較は、被変換アナログ電圧 V<sub>SIG</sub> とランプ電圧 V<sub>RAMP</sub> の電圧増加値の差電圧を入力電圧として、入力判定電圧のオートゼロレベルと比較することで実行される。

## 【0013】

オートゼロレベルは、インバータ回路 12 の入出力間を短絡した状態で得られる電圧レベルであり、インバータの入出力特性曲線 A と、入力電圧 V<sub>in</sub> と出力電圧 V<sub>out</sub> が同電圧（V<sub>in</sub> = V<sub>out</sub>）となる直線 B の交差する点における電圧となる。

## 【0014】

インバータ回路 12 を構成する P チャンネル型 MOSFET と N チャンネル型 MOSFET の各閾値電圧を V<sub>thp</sub>、V<sub>thn</sub>、導電計数（数 5 参照）を p、n とすると、インバータ回路 12 の両 MOSFET を貫通して流れる電流量が等しいことから、以下の数 1 が成り立つ。尚、数 1 中、V<sub>DD</sub> は P チャンネル型 MOSFET のソース端子に供給される電源電圧で、V<sub>x</sub> はオートゼロレベルであり、数 2 の関係が成り立つ。

## 【0015】

10

20

30

40

50

[ 数 1 ]

$$n / 2 \times (V_x - V_{thn})^2 = p / 2 \times (V_{DD} - V_x - V_{thp})^2$$

【 0 0 1 6 】

[ 数 2 ]

$$V_x = V_{in} = V_{out}$$

【 0 0 1 7 】

数 1 の方程式を  $V_x$  について解くと、オートゼロレベル  $V_x$  が、以下の数 3 に示すよう

に得られる。

【 0 0 1 8 】

[ 数 3 ]

$$V_x = \{ (n / p)^{1/2} \times V_{thn} + V_{DD} - V_{thp} \} / (1 + (n / p)^{1/2})$$

【 0 0 1 9 】

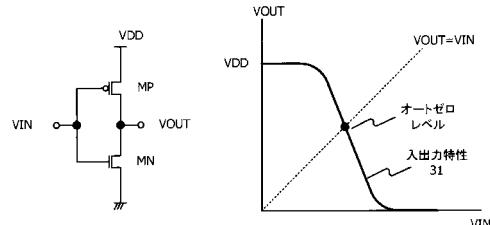

図 4 に、上述した従来のコラム型 A / D 変換器を用いたセンサシステム 100 の概略ブロッケ図を示す。センサシステム 100 は、光電変換素子の複数がマトリクス状に配列してなる個体撮像素子の画素部（センサ部）16 と、画素部 16 の各列に夫々対応して設けられた電圧比較回路 17 及びラッチ回路 13 からなる A / D 変換ユニット 11 の複数と、ランプ波発生回路 14 と、カウンタ 15 と、制御回路 18 と、を備えて構成されている。また、画素部 16 は、有効画素部 16 a と、画素部 16 の周囲の一部に設けられ遮光した光学的黒画素部 16 b から構成されている。より具体的には、画素部 16 は、光学的黒画素部 16 b が、有効画素部 16 a を囲むように画素部 16 の上下左右に配置されている。

【 0 0 2 0 】

図 4 に示すセンサシステム 100 において、CMOS イメージセンサ等の固体撮像素子は、被写体から受け取った光（入射光）を図 1 に示すフォトダイオード PD によって光電変換し、光の強度（入射光量）に応じた電流を有する被変換アナログ信号を出力する。ここで、フォトダイオード PD から出力される被変換アナログ信号には、入射光の強度に応じた電流の他に、熱によって電子 / 正孔対が発生することに起因する暗電流と呼ばれるノイズ成分が重畠している。暗電流による信号成分はノイズ成分（雑音成分）であるため、除去しなければ、センサシステム 100 から得られた画像の画質が低下する。このため、図 4 に示すセンサシステム 100 では、暗電流による信号成分を検出するために、画素部 16 の周囲の一部に、アルミ等で遮光され暗電流による信号成分のみを出力するように構成された光学的黒画素部 16 b が形成されている。尚、アルミ等によって遮光した画素は、一般的に、光学的黒画素、或いは、オブティカル・ブラック画素（以下、適宜 OB 画素と略称する）と呼ばれている。

【 0 0 2 1 】

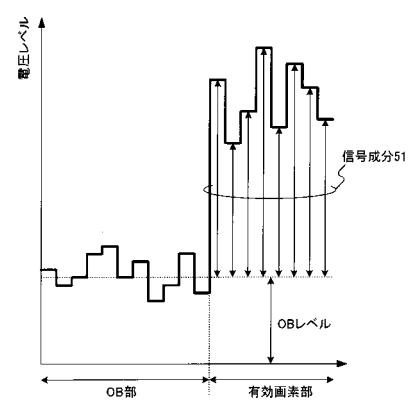

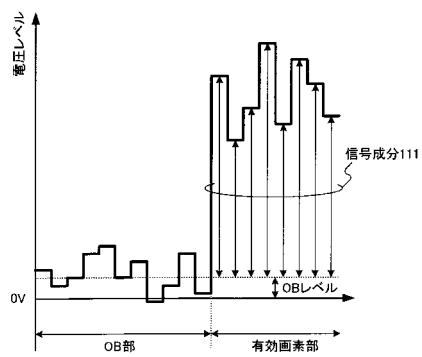

図 5 に、光学的黒画素部（以下、適宜 OB 部と略称する）16 b の各 OB 画素夫々から得られる OB 画素信号夫々と、有効画素部 16 a の各有効画素夫々から得られる有効画素信号夫々の模式図を示す。

【 0 0 2 2 】

図 5 に示すように、OB 部から出力される OB 画素信号夫々の電圧値は、全ての OB 画素で一様ではなく、各 OB 画素からの OB 画素信号の電圧値はランダムな値を示す。以下、OB 画素夫々から得られる OB 画素信号の電圧レベルの平均値を OB レベル（平均ノイズ電圧）と称することとする。また、有効画素部 16 b の各有効画素夫々から得られる有効画素信号夫々は、図 5 に示すように、暗電流による信号成分（OB レベル）と光電変換による信号成分が足し合わされた信号となっている。センサシステム 100 から取得したいデータは、光電変換による信号成分である。即ち、有効画素部 16 a から得られた有効画素信号の電圧レベルから OB レベルを減算した電圧レベル（信号成分 51）である。

【 0 0 2 3 】

ところで、例えば、センサシステム 100 による夜景の撮影時等、被写体から受け取る光の入射光量が少ない場合には、信号成分 51 の電圧レベルの値が非常に小さな値になる

10

20

30

40

50

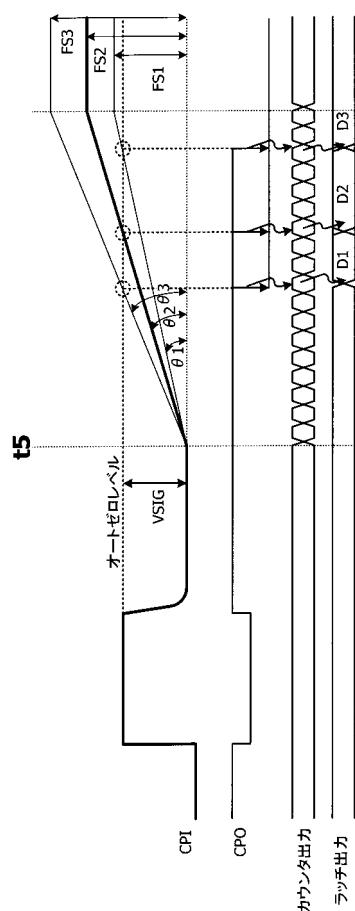

。このため、CMOSイメージセンサ等では、コントラストの高い画像を得るために、信号成分51にゲイン(利得)を掛けて、A/D変換結果を大きくする。図4に示すセンサシステム100のコラム型A/D変換器(図1)では、入力信号(被変換アナログ電圧)に対するゲインは、ランプ電圧 $V_{RAMP}$ の電圧変化の傾きを変えることで変更することができる。ここで、図6は、ランプ電圧 $V_{RAMP}$ の電圧変化の傾きを、傾斜角1~3(各傾斜角1~3は幾何学的角度ではなく、単位時間当たりの電圧変化量として定義)に設定したときのノードCPIの電圧波形と、ラッチ回路13の動作タイミング及び出力値(A/D変換結果)の関係を示している。図6に示すように、ランプ電圧 $V_{RAMP}$ の電圧変化の傾きを傾斜角1~3に変動させると、ノードCPIの電圧レベルがオートゼロレベル(インバータ12の閾値電圧)を超えるタイミングが変化する。ラッチ回路13は、インバータ12の出力変化時にカウンタ15から出力されるディジタル値をラッチする。このため、ノードCPIの電圧レベルがオートゼロレベルを超えるタイミングが変化すると、ラッチ回路13がラッチするカウンタ15のディジタル値が変化する。具体的には、ランプ電圧 $V_{RAMP}$ の電圧変化の傾きが傾斜角1に設定されているときはA/D変換結果としてデータD3が、傾斜角2のときはデータD2が、傾斜角3のときはデータD1が出力されることとなる。このように、ランプ電圧 $V_{RAMP}$ の電圧変化に応じて、A/D変換結果(ラッチ回路13の出力値)は変化する。即ち、図1に示すコラム型A/D変換器10に入力される被変換アナログ電圧に対するゲイン(利得)の設定は、ランプ電圧 $V_{RAMP}$ の電圧変化の傾きを変えることで実現できる。

## 【0024】

10

ここで、FS電圧(フルスケール電圧)とは、A/D変換器において、ディジタル値に変換可能な入力電圧(被変換アナログ電圧)の範囲を規定する電圧のことであり、FS電圧の値が小さい程、測定可能な入力電圧の範囲(即ち、ダイナミックレンジ)も小さくなる。CMOSイメージセンサ等で用いられるA/D変換器10では、画質向上等のため、光電変換による信号成分51のダイナミックレンジを大きく取ることが望ましい。

## 【0025】

【特許文献1】特開特開2000-286706号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0026】

30

ところで、図1に示す従来技術に係るA/D変換器10では、フルスケール電圧は、光電変換による信号成分と暗電流によるノイズ成分の両方に割り当てられる。ここで、図6において、FS3~FS1は、図5に示す光電変換による信号成分51と暗電流によるノイズ成分に割り当てられるフルスケール電圧を示している。更に、図1に示すA/D変換器10では、ノイズ成分が重畠した被変換アナログ電圧に対してゲインが掛かる。つまり、ノイズ成分に対してもゲインが掛かり、結果的に、OBレベルが増大するのと同じになる。このため、図1に示すA/D変換器10において、ゲインを増大させるためにランプ電圧 $V_{RAMP}$ の電圧変化の傾きを小さくするように制御すると、ノイズ成分に割り当られるフルスケール電圧の割合が高くなる。従って、図6に示すように、A/D変換器の入力信号に対するゲイン(利得)を増加させるために、ランプ電圧 $V_{RAMP}$ の電圧変化の傾きを傾斜角3~1に減少させると、光電変換による信号成分51に割り当て可能なFS電圧も、傾きの減少に応じて、FS3~FS1の減少に比例して減少してしまう。つまり、A/D変換器で測定可能な入力電圧の範囲(ダイナミックレンジ)は、ゲインの増大に応じて小さくなるという問題があった。

## 【0027】

40

尚、光電変換による信号成分51に対してのみゲインを掛けることができれば、光電変換による信号成分のフルスケール電圧を大きく取ることができ、信号成分51のダイナミックレンジを増大させることができる。しかし、図1に示す従来のA/D変換器では、光電変換による信号成分51のみにゲインを掛けることはできず、図5に示すOBレベルに対してもゲインが掛かる。このため、入力信号(被変換アナログ電圧)にゲインを掛ける

50

と、光電変換による信号成分 51 に対するフルスケール電圧の割り当てが少なくなり、光電変換による信号成分 51 のダイナミックレンジが小さくなるという問題があった。

【0028】

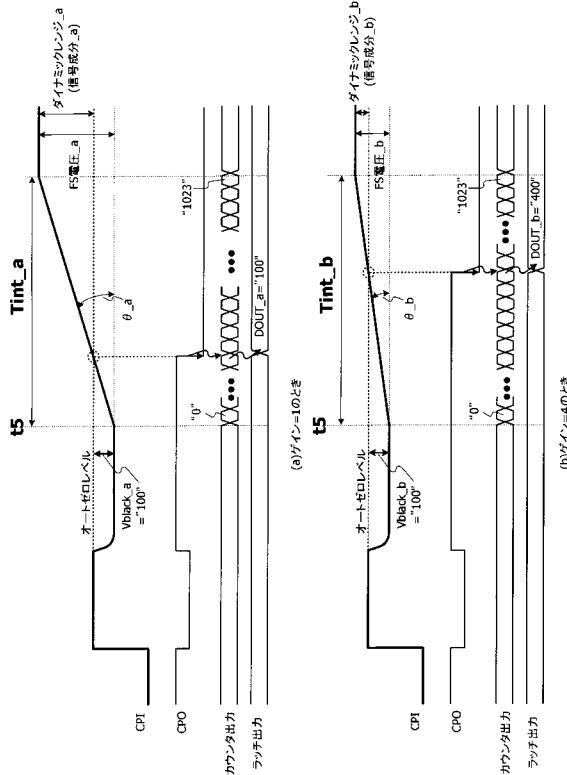

この問題を図解するために、図7に、10bit 精度のコラム型A/D変換器のタイミングチャートを示す。図7(a)は、ゲインが1の場合におけるノードCPIの電圧波形と、ラッチ回路13の動作タイミング及び出力値(A/D変換結果)の関係を、図7(b)は、ゲインが4の場合におけるノードCPIの電圧波形と、ラッチ回路13の動作タイミング及び出力値(A/D変換結果)の関係を示している。図7に示すコラム型A/D変換器では、10bitカウンタを用いた場合を想定しており、被変換アナログ電圧を“0(=2<sup>0</sup>)”～“1023(=2<sup>10</sup>-1)”のデジタル値に変換する。図7に示すコラム型A/D変換器のダイナミックレンジは、1024レベルとなる。

【0029】

図7(a)におけるOB部16bからのOB画素信号の電圧レベル $V_{b1ack\_a}$ と、図7(b)におけるOB部16bからのOB画素信号の電圧レベル $V_{b1ack\_b}$ は等しく、以下の数4で与えられる。

【0030】

[数4]

$$V_{b1ack\_a} = V_{b1ack\_b} = "100" \text{ (dec)}$$

【0031】

ここで、図7(a)ではゲインが1に設定されており、図7(b)ではゲインが4に設定されていることから、図7(a)の場合におけるランプ電圧 $V_{RAMP}$ の電圧変化の傾き $_a$ と、図7(b)の場合におけるランプ電圧 $V_{RAMP}$ の電圧変化の傾き $_b$ の間には、各傾きを幾何学的角度ではなく、単位時間当たりの電圧変化量として定義すると、以下の数5の関係が成り立つ。

【0032】

[数5]

$$_b = _a / 4$$

【0033】

従って、ゲインが1に設定されている場合におけるOB画素信号の電圧レベル $V_{b1ack\_a}$ に対するA/D変換結果 $DOUT\_a$ として、図7(a)より、 $DOUT\_a = 100$ (10進数)が得られる。同様に、ゲインが4に設定されている場合におけるOB画素信号の電圧レベル $V_{b1ack\_b}$ に対するA/D変換結果 $DOUT\_b$ として、図7(b)より、 $DOUT\_b = 400$ (10進数)が得られる。

【0034】

従って、ゲインが1に設定されている場合のダイナミックレンジは、図7(a)より、100レベルがノイズ成分に割り当てられ、残りの923(=1023-100)レベルが光電変換による信号成分に割り当てられる。同様に、ゲインが4に設定されている場合のダイナミックレンジは、図7(b)より、400レベルがノイズ成分に割り当てられ、残りの623(=1023-400)レベルが光電変換による信号成分に割り当てられる。即ち、ゲインを4に設定することで、光電変換による信号成分として表現可能なダイナミックレンジは、ゲインを1に設定した場合の923段階の階調から、ゲインを4に設定した場合の623段階の階調に減少することとなる。

【0035】

このため、例えば、CMOSイメージセンサ等に用いられるシングルスロープ型A/D変換器において、ランプ電圧の電圧波形の傾きを可変にして、入力される被変換アナログ電圧のゲインを変化させる場合に、被変換アナログ電圧に含まれるOBレベル(オプティカル・ブラック・レベル、或いは、光学的黒レベル)にゲインが掛かることに起因して、光電変換による信号成分に割り当てられる階調(ダイナミックレンジ)が減少するのをおさえることができるA/D変換器が望まれている。

【0036】

10

20

30

40

50

本発明は上記の問題に鑑みてなされたものであり、その目的は、画質の向上等を図るために入力される被変換アナログ電圧のゲインを増加させる場合に、光電変換による信号成分のダイナミックレンジの低下をおさえることができるA/D変換器を提供する点にある。また、該A/D変換器を用い、画質の向上等を図るために入力される被変換アナログ電圧のゲインを増加させる場合に、光電変換による信号成分のダイナミックレンジの低下をおさえることができるセンサシステムを提供する。

【課題を解決するための手段】

【0037】

上記目的を達成するための本発明に係るA/D変換器は、電圧値が一定期間単調変化するランプ電圧を発生するランプ電圧発生回路と、被変換アナログ電圧をサンプリングホールドし、サンプリングホールドされた前記被変換アナログ電圧と、前記ランプ電圧発生回路から発生されるランプ電圧の電圧変化値または前記電圧変化値に比例する電圧値で与えられる参照電圧とを比較する演算器を備え、前記参照電圧が前記被変換アナログ電圧に等しくなった時点で出力変化する電圧比較回路と、前記参照電圧に応じたディジタル値を計数して出力するカウンタと、前記カウンタから出力される前記ディジタル値を前記電圧比較回路の出力変化時にラッチして出力するラッチ回路と、を備えたA/D変換器であって、前記被変換アナログ電圧に含まれるノイズ成分を平均化して平均ノイズ電圧を求める平均化処理回路と、前記平均ノイズ電圧の目標値としての目標ノイズ電圧を設定する目標ノイズ電圧設定回路と、前記平均ノイズ電圧と前記目標ノイズ電圧の差に基づいて、前記ランプ電圧発生回路によって前記参照電圧が基準電圧レベルから変化を開始する前記制御基準タイミングに対する前記カウンタの計数開始タイミングの調整、及び、前記カウンタの計数開始タイミングにおける前記参照電圧の前記基準電圧レベルの調整の内、少なくとも前記カウンタの前記計数開始タイミングの調整を行う制御回路を備えることを第1の特徴とする。

10

【0038】

上記特徴の本発明に係るA/D変換器は、前記制御回路が、前記平均ノイズ電圧と前記目標ノイズ電圧の差を示す指標値を算出し、前記指標値に応じて前記カウンタの前記計数開始タイミングを調整するカウンタ待機時間を算出し、前記カウンタの前記計数開始タイミングを前記カウンタ待機時間に応じて調整することを第2の特徴とする。

20

【0039】

30

上記第1の特徴の本発明に係るA/D変換器は、前記制御回路が、前記平均ノイズ電圧と前記目標ノイズ電圧の差を示す指標値を算出し、前記指標値に応じて前記カウンタの前記計数開始タイミングを調整するカウンタ待機時間を算出し、前記平均ノイズ電圧が前記目標ノイズ電圧を上回る場合に、前記制御基準タイミングに対する前記計数開始タイミングを前記カウンタ待機時間に応じて遅らせ、前記平均ノイズ電圧が前記目標ノイズ電圧を下回る場合に、前記制御基準タイミングに対する前記計数開始タイミングを前記カウンタ待機時間に応じて早め、更に、前記制御基準タイミングにおける前記参照電圧の前記基準電圧レベルの調整量を前記指標値に基づいて算出し、前記制御基準タイミング前に、前記ランプ電圧の電圧変化方向とは反対の方向に、前記参照電圧の前記基準電圧レベルを前記調整量だけ変化させることを第3の特徴とする。

40

【0040】

上記第1の特徴の本発明に係るA/D変換器は、前記制御回路が、前記平均ノイズ電圧と前記目標ノイズ電圧の差を示す指標値を算出し、前記指標値に基づいて、前記計数開始タイミングにおける前記参照電圧の前記基準電圧レベルの調整量を算出し、前記計数開始タイミング前に、前記ランプ電圧の電圧変化方向に、前記参照電圧の前記基準電圧レベルを前記調整量に基づいて変化させることを第4の特徴とする。

【0041】

上記特徴の本発明に係るA/D変換器は、前記制御回路が、前記平均ノイズ電圧が前記目標ノイズ電圧を下回る場合に、前記指標値に基づいて、前記計数開始タイミングにおける前記参照電圧の前記基準電圧レベルの調整量を算出し、前記計数開始タイミング前に、

50

前記ランプ電圧の電圧変化方向とは反対の方向に、前記参照電圧の前記基準電圧レベルを前記調整量に基づいて変化させることを第5の特徴とする。

【0042】

上記何れかの特徴の本発明に係るA/D変換器は、前記ランプ電圧発生回路が、定電流源からの電流値を複製する第1カレントミラー回路及び第2カレントミラー回路と、前記第1カレントミラー回路で複製した電流により放電し、前記第2カレントミラー回路で複製した電流により充電する積分容量と、前記積分容量に対する前記第1カレントミラー回路による放電及び前記第2カレントミラー回路による充電を逐一的に切り替えるスイッチ回路と、を備えて構成されることを第6の特徴とする。

【0043】

上記何れかの特徴の本発明に係るA/D変換器は、前記演算器が、インバータ回路を用いて構成され、前記インバータ回路の入力判定電圧に前記被変換アナログ電圧と前記参照電圧の差電圧を加えた合成電圧を前記インバータ回路の入力電圧として発生させる電圧合成回路を備えていることを第7の特徴とする。

【0044】

上記第1～第6の特徴の本発明に係るA/D変換器は、前記演算器が、前記被変換アナログ電圧と前記ランプ電圧を夫々入力電圧とする差動入力型の演算増幅器で構成されていることを第8の特徴とする。

【0045】

上記何れかの特徴の本発明に係るA/D変換器は、前記制御回路が、前記参照電圧の前記基準電圧レベルを、前記ランプ電圧の電圧変化方向とは反対の方向に変化させる場合に、前記ランプ電圧発生回路を反転動作させることを第9の特徴とする。

【0046】

上記目的を達成するための本発明に係るセンサシステムは、光電変換素子の複数がマトリクス状に配列してなるセンサ部と、前記センサ部の各列に夫々対応して設けられた、請求項1～10の何れか1項に記載のA/D変換器の前記電圧比較回路及び前記ラッチ回路からなるA/D変換ユニットの複数と、前記A/D変換器の前記ランプ電圧発生回路と、前記カウンタと、前記平均化処理回路と、前記目標ノイズ電圧設定回路と、前記制御回路と、を備え、前記センサ部の周囲の一部に、遮光した光学的黒画素部が設けられ、前記平均化処理回路は、前記光学的黒画素部の出力信号に対する前記A/D変換ユニットのA/D変換値を平均化して前記平均ノイズ電圧を求めることが第1の特徴とする。

【0047】

尚、上記特徴のA/D変換器において、ランプ電圧発生回路におけるランプ電圧の単調変化は、ランプ電圧発生回路によって参照電圧が基準電圧レベルから変化を開始する制御基準タイミング以降において、ランプ電圧の電圧波形が、増加波形及び無変化波形の組み合わせからなる場合、または、減少波形及び無変化波形の組み合わせからなる場合を想定している。

【発明の効果】

【0048】

上記特徴のA/D変換器によれば、平均ノイズ電圧と目標ノイズ電圧の差に基づいて、制御基準タイミングに対するカウンタの計数開始タイミングの調整、及び、カウンタの計数開始タイミングにおける参照電圧の基準電圧レベルの調整の内、少なくとも前記カウンタの前記計数開始タイミングの調整を行うように構成したので、平均ノイズ電圧のA/D変換結果を、目標ノイズ電圧に対応するデジタル値に追従させることができるので、ゲインの設定値に依存することなく、ダイナミックレンジを広く確保することができる。

【0049】

より具体的には、上記特徴のA/D変換器によれば、OB部に含まれる全てのOB画素からの被変換アナログ信号（ノイズ成分）に対するA/D変換結果を平均化した平均ノイズ電圧が、該平均ノイズ電圧（OBレベル）の目標値としての目標ノイズ電圧の電圧レベル

10

20

30

40

50

に従うように、負帰還が掛かることになる。つまり、A / D 変換器の限られたフルスケール電圧 (FS 電圧) に対して、ノイズ成分である OB レベルを目標ノイズ電圧の電圧レベルに追従させてるので、特に、目標ノイズ電圧を小さな値に設定することで、光電変換による信号成分に対して、より多くのフルスケール電圧を割り当てることが可能となる。従って、上記特徴の A / D 変換器は、夜景等の暗い被写体を撮像する場合等、入射光量が少なく光電変換信号に対してゲインを掛ける必要がある場合に、特に有効である。この場合、上記特徴の A / D 変換器によれば、ゲインの設定値の増大に伴い、ゲインを掛けた後の平均ノイズ電圧が増大しても、光電変換による信号成分に対するフルスケール電圧の割り当てはあまり減少しないため、良好な画像を得ることが維持可能となる。

【0050】

10

また、本発明を適用したセンサシステムは、上記特徴の A / D 変換器を用いているため、上記特徴の A / D 変換器の作用効果を全て奏することが可能であり、光電変換による信号成分に対するダイナミックレンジの減少を防止することができ、画質の低下を防止することが可能になる。

【発明を実施するための最良の形態】

【0051】

以下、本発明に係る A / D 変換器及びセンサシステムの実施形態を図面に基づいて説明する。

【0052】

20

第 1 実施形態

本発明に係る A / D 変換器、及び、該 A / D 変換器を備えたセンサシステムの第 1 実施形態について、図 8 及び図 9 を基に説明する。

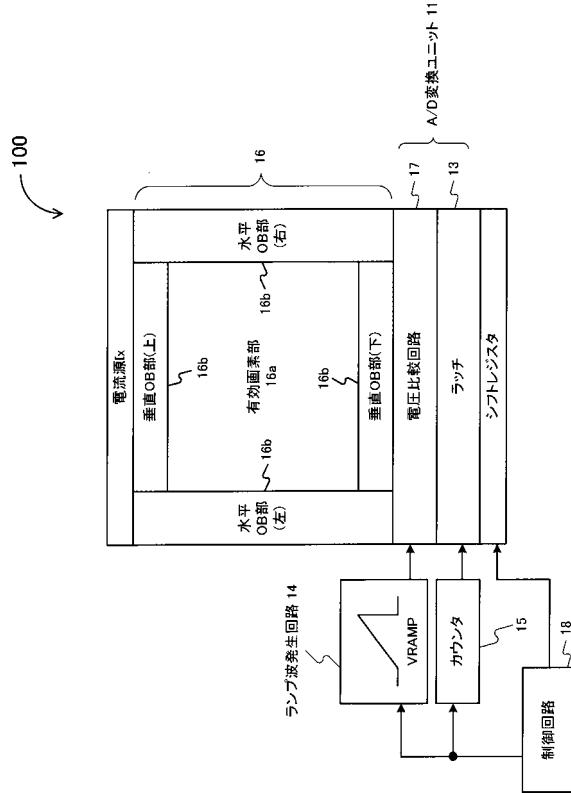

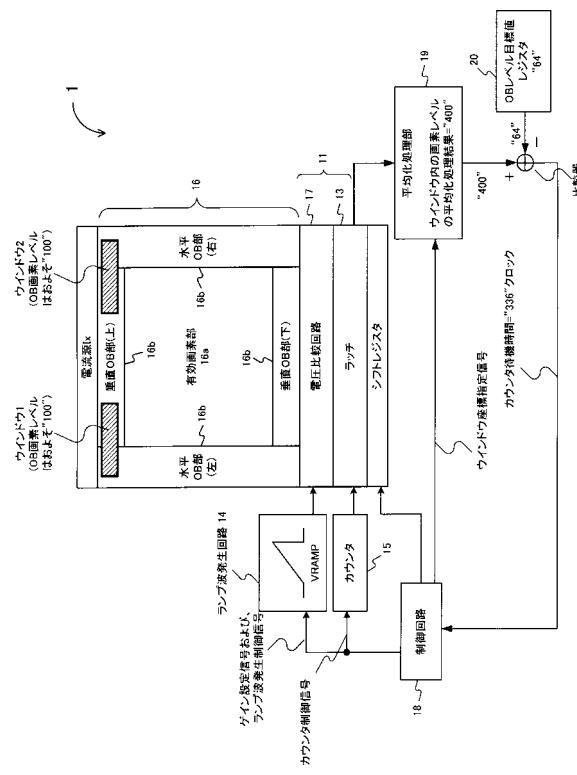

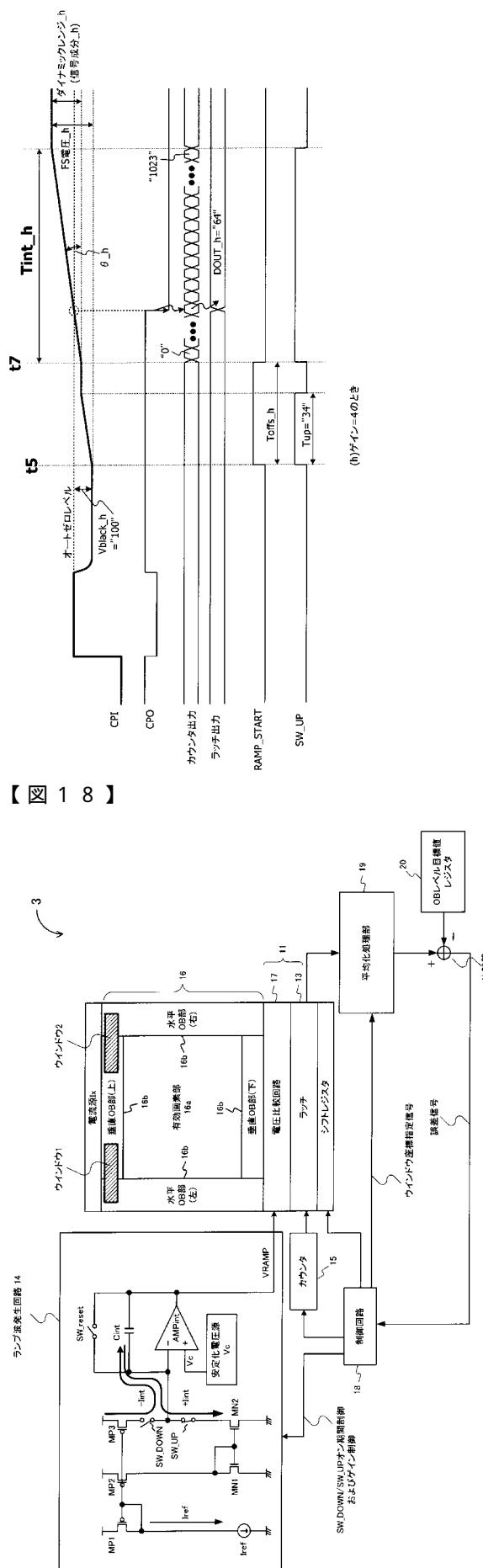

【0053】

先ず、本実施形態のセンサシステムの基本構成について図 8 を基に説明する。

【0054】

センサシステム 1 は、図 8 に示すように、光電変換素子の複数がマトリクス状に配列してなる画素部 (センサ部) 16 と、本発明に係る A / D 変換器の各構成を備えて構成されている。画素部 16 は、有効画素部 16a と、画素部 16 の周囲の一部に設けられた光学的黒画素部 (OB 部) 16b から構成されている。OB 部 16b は遮光されており、暗電流による被変換アナログ電圧、つまり、ノイズ成分に係る被変換アナログ電圧のみを出力する。

30

【0055】

A / D 変換器は、基本構成として、電圧値が一定期間単調変化するランプ電圧を発生するランプ波発生回路 (ランプ電圧発生回路) 14 と、被変換アナログ電圧をサンプリングホールドし、サンプリングホールドされた被変換アナログ電圧と、ランプ波発生回路 14 から発生されるランプ電圧の電圧変化値または電圧変化値に比例する電圧値で与えられる参照電圧とを比較する演算器を備え、参照電圧が被変換アナログ電圧に等しくなった時点での出力変化する電圧比較回路 17 と、参照電圧に応じたデジタル値を計数して出力するカウンタ 15 と、カウンタ 15 から出力されるデジタル値を電圧比較回路 17 の出力変化時にラッチして出力するラッチ回路 13 と、を備えている。尚、ランプ波発生回路 14 、電圧比較回路 17 及びラッチ回路 13 からなる A / D 変換ユニット 11 、及び、カウンタ 15 の構成は、図 1 に示す従来技術に係る A / D 変換器の構成と同じである。本実施形態のカウンタ 15 は、10bit カウンタであり、“0 (= 2<sup>0</sup>)” ~ “1023 (= 2<sup>10</sup> - 1)” のデジタル値を出力するように構成されている。

40

【0056】

更に、本実施形態の A / D 変換器は、被変換アナログ電圧に含まれるノイズ成分を平均化して平均ノイズ電圧を求める平均化処理部 (平均化処理回路) 19 と、平均ノイズ電圧の目標値としての目標ノイズ電圧を設定する目標ノイズ電圧設定回路 20 と、平均ノイズ電圧と目標ノイズ電圧の差に基づいて、ランプ波発生回路 14 によって参照電圧が基準電圧レベルから変化を開始する制御基準タイミングに対するカウンタ 15 の計数開始タイミ

50

ングの調整、及び、カウンタ15の計数開始タイミングにおける参照電圧の基準電圧レベルの調整の内、少なくともカウンタの計数開始タイミングの調整を行う制御回路18を備えている。

【0057】

平均化処理部19は、OB部16b（垂直OB部、水平OB部の何れでもよい）から出力された被変換アナログ電圧をA/D変換ユニット11によってA/D変換したA/D変換結果（デジタル値）を取り込み、平均化処理して、平均ノイズ電圧（デジタル値）の電圧レベル（OBレベル）を求める。平均化処理部19は、OB部16bを構成するOB画素夫々から出力される被変換アナログ電圧の電圧レベルはランダムな値を取るため、平均化処理して、OBレベルを検出する。

10

【0058】

目標ノイズ電圧設定回路20は、目標ノイズ電圧の電圧レベルの値を記憶するレジスター構成されており、本実施形態では、“64”に設定されている。

【0059】

次に、本実施形態のセンサシステム1の動作について、図8及び図9を基に説明する。ここでは、A/D変換器の入力信号に対するゲインが4に設定されている場合を想定して説明する。

【0060】

図8に示す制御回路18は、平均化処理部19にOBレベルの算出を指示するために、OB部16bの内、OBレベルの算出に用いるOB画素の領域（以下、適宜ウインドウと称する）を特定するウインドウ指定座標信号を平均化処理部19に出力する。ここでは、制御回路18は、図8に示すウインドウ1とウインドウ2を特定するためのウインドウ指定座標信号を平均化処理部19に対して出力する。また、制御回路18は、ランプ波発生回路14に対し、ゲインの値を4に設定するためのゲイン設定信号を出力する。

20

【0061】

続いて、平均化処理部19は、A/D変換ユニット11から、ウインドウ1及びウインドウ2に含まれるOB画素夫々の電圧レベルをA/D変換したA/D変換データを取り込む。尚、ここでは、ウインドウ1及びウインドウ2に含まれる各OB画素の電圧レベルをA/D変換したA/D変換データは、約“100”（dec）である場合を想定して説明する。平均化処理部19は、取り込んだOB画素夫々についてのA/D変換データの値（

30

“100”）を全てのOB画素について加算して、A/D変換データの加算値を求める。平均化処理部19は、A/D変換データの加算値を、ウインドウ1及びウインドウ2に含まれるOB画素の全画素数で除算することで、平均値（OBレベル）を算出する。ここでは、ゲインの値が4に設定されており、ウインドウ1及びウインドウ2に含まれるOB画素夫々についてのA/D変換データの値が約“100”なので、平均化処理部19に取り込まれるA/D変換データの値は、約“400”になる。従って、この場合は、OBレベルは“400”となる。

【0062】

制御回路18は、平均化処理部19から出力されるOBレベルの値“400”から目標ノイズ電圧設定回路20から出力される目標ノイズ電圧の値“64”を比較器によって減算した値“336”（＝“400” - “64”）を取り込む。続いて、制御回路18は、比較器からの出力値（ここでは“336”（dec）、平均ノイズ電圧と目標ノイズ電圧の差を示す指標値）に応じて、カウンタ15の計数開始タイミングを調整するカウンタ待機時間を算出する。本実施形態では、カウンタ15は、センサシステム1のクロックに同期して出力値を1ずつ加算するように構成されていることから、カウンタ待機時間T<sub>cw</sub> - c（クロック数）は、OBレベル（平均ノイズ電圧）V<sub>b1ack</sub>と目標ノイズ電圧N<sub>sp</sub>を用いて、以下の式で求められる。

40

【0063】

[数6]

T<sub>cw</sub> - c = V<sub>b1ack</sub> - N<sub>sp</sub>

50

## 【0064】

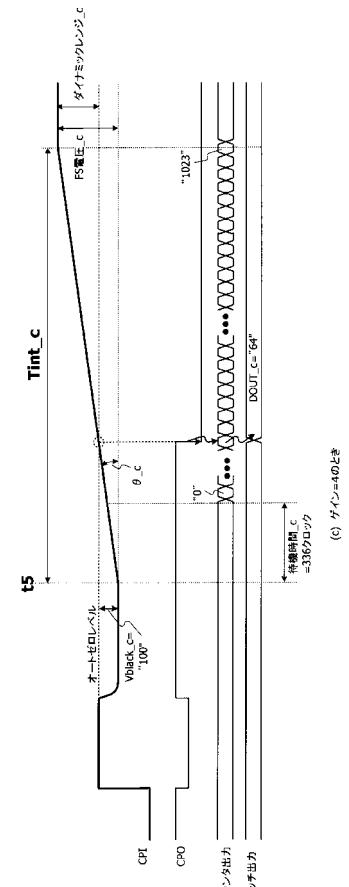

制御回路18は、数6で求めたカウンタ待機時間 $T_{c w\_c}$ 、ここでは、“336”を保存する。更に、制御回路18は、被変換アナログ電圧をA/D変換処理する際に、保存しておいたカウンタ待機時間 $T_{c w\_c}$ に基づいて、カウンタ15の計数開始時間を遅延させる。

## 【0065】

図9に、電圧比較回路17の入力ノード(ノードCPI)、カウンタ15の出力及びラッチ回路13の出力(A/D変換結果)夫々の電圧波形を示す。具体的には、制御回路18は、図9に示すように、OBレベル $V_{b1ack}$ が目標ノイズ電圧 $Nsp$ と等しい場合のカウンタ15の計数開始時間である時間 $t_5$ を起点として、カウンタ15の計数開始時間を、前処理で求めたカウンタ待機時間 $T_{c w\_c}$ (=“336”クロック)遅延させる。

10

## 【0066】

尚、図9において、ランプ波発生回路14から出力されるランプ電圧 $V_{RAMP}$ の電圧変化の傾き $_c$ は、各傾きを幾何学的角度ではなく、単位時間当たりの電圧変化量として定義すると、図7に示す傾き $_a$ 及び傾き $_b$ との間で以下の数7の関係が成り立つ。

## 【0067】

## [数7]

$$_c = _b = _a / 4$$

## 【0068】

従って、図9に示すように、OB画素夫々についてのA/D変換データの値 $V_{b1ack\_c}$ が“100”とすると、ラッチ回路13の出力値であるA/D変換結果 $DOUT_c$ は、“64”となる。これは、目標ノイズ電圧の設定値と同じである。従って、本発明によれば、ゲインの設定値如何に拘わらず、カウンタ待機時間を設定し、ランプ波発生回路14によって参照電圧が基準電圧レベルから変化を開始する制御基準タイミング $t_5$ に対するカウンタ15の計数開始タイミングを調整することで、仮想的に、OBレベルを目標ノイズ電圧に設定することが可能となる。この場合、光電変換による信号成分のダイナミックレンジは、“1023”-“64”=“959”階調となる。つまり、ゲインを4に設定した場合、図7(b)に示す従来技術に係るA/D変換器では、光電変換による信号成分のダイナミックレンジは“632”階調であったのに対し、本発明に係るA/D変換器では“959”階調となり、十分に大きなダイナミックレンジを確保できることが分かる。

30

## 【0069】

尚、図8に示すランプ波発生回路14の運転時間 $T_{int\_c}$ は、カウンタ待機時間 $T_{c w\_c}$ と、カウンタ15が初期値(ここでは“0”)から最大値(ここでは“1023”)まで計数する時間、即ち、カウンタクロック数 $Int_c$ を用いて、以下の数8で求められる。

## 【0070】

## [数8]

$$T_{int\_c} = T_{c w\_c} + Int_c$$

## 【0071】

本実施形態では、カウンタ待機時間 $T_{c w\_c}$ は“336”クロック、カウンタクロック数 $Int_c$ は $2^N$ (Nはカウンタ15のビット数、ここでは10)であるので、ランプ波発生回路14の運転時間 $T_{int\_c}$ は、 $336 + 1024 = 1316$ (クロック)となる。尚、ランプ波発生回路14の運転時間 $T_{int\_c}$ は、制御回路18によって設定される。

## 【0072】

## 第2実施形態

本発明に係るA/D変換器、及び、該A/D変換器を備えたセンサシステムの第2実施形態について、図10～図15を基に説明する。本実施形態では、OBレベル(平均ノイ

10

20

30

40

50

ズ電圧)が目標ノイズ電圧を上回る場合と、下回る場合とで異なる制御を行う場合について説明する。

【0073】

先ず、本実施形態のA/D変換器及びセンサシステムの構成について説明する。図14に、本実施形態におけるセンサシステム2の概略構成を示す。尚、本実施形態のA/D変換器及びセンサシステム2の基本構成は、上記第1実施形態におけるA/D変換器及びセンサシステムの構成と同じである。

【0074】

本実施形態の制御回路18は、OBレベル(平均ノイズ電圧)と目標ノイズ電圧の差を示す指標値を算出し、指標値に応じてカウンタ15の計数開始タイミングを調整するカウンタ待機時間を算出し、OBレベルが目標ノイズ電圧を上回る場合に、制御基準タイミングに対する計数開始タイミングをカウンタ待機時間に応じて遅らせるように制御する。また、制御回路18は、OBレベルが目標ノイズ電圧を下回る場合に、制御基準タイミングに対する前記計数開始タイミングをカウンタ待機時間に応じて早め、更に、制御基準タイミングにおける参照電圧の基準電圧レベルの調整量を指標値に基づいて算出し、制御基準タイミング前に、ランプ電圧の電圧変化方向とは反対の方向に、参照電圧の基準電圧レベルを調整量だけ変化させる。

【0075】

本実施形態のセンサシステム1の動作について、図8～図14を基に説明する。ここでは、上記第1実施形態と同様に、A/D変換器の入力信号に対するゲインが4に設定されている場合を想定して説明する。

【0076】

尚、OBレベル(平均ノイズ電圧)が目標ノイズ電圧を上回る場合は、上記第1実施形態における制御、即ち、制御回路18が、OBレベル(平均ノイズ電圧)と目標ノイズ電圧の差を示す指標値に基づいてカウンタ待機時間 $T_{c w\_c}$ を算出し、制御基準タイミング $t_5$ に対する計数開始タイミングをカウンタ待機時間 $T_{c w\_c}$ に応じて遅らせる制御を行う。

【0077】

以下、OBレベル(平均ノイズ電圧)が目標ノイズ電圧を下回る場合の制御について、図10～図15を基に説明する。

【0078】

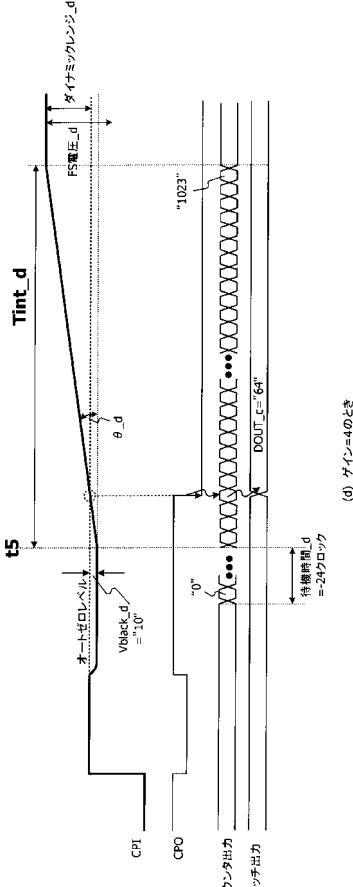

図10に、OBレベル(平均ノイズ電圧)が目標ノイズ電圧を下回る場合、即ち、カウンタ待機時間 $T_{c w\_d}$ が負の値になる場合において、カウンタの計数開始タイミングのみを調整した場合のタイミングチャートを示す。本実施形態では、OB部16bのウィンドウ1及びウィンドウ2に含まれるOB画素夫々についてのA/D変換データは、約“10”(dec)である場合を想定して説明する。図8に示す平均化処理部19の出力値は、OB画素夫々についてのA/D変換データが約“10”(dec)であり、ゲインが4に設定されていることから、約“40”となる。従って、比較器の出力値は、平均化処理部19から出力されるOBレベルの値“40”から、目標ノイズ電圧設定回路20から出力される目標ノイズ電圧の値“64”を減算した“-24”(=“40”-“64”)クロックとなる。制御回路18は、比較器の出力値“-24”クロックを取り込み、この値をカウンタ待機時間 $T_{c w\_d}$ として保存する。

【0079】

図11に、図10に示すOBレベル(平均ノイズ電圧)が目標ノイズ電圧を下回る場合における、有効画素部16a及びOB部16b夫々から出力される被変換アナログ電圧をデジタル変換したA/D変換データを示す。図11に示すように、OBレベルが目標ノイズ電圧より小さい場合、OB画素から電圧比較回路17に入力される被変換アナログ電圧の電圧レベルが、ほぼゼロになるか、負の値になるOB画素が存在する場合がある。

【0080】

ここで、図12は、電圧レベルが負の値になるOB画素からの被変換アナログ電圧をA

10

20

30

40

50

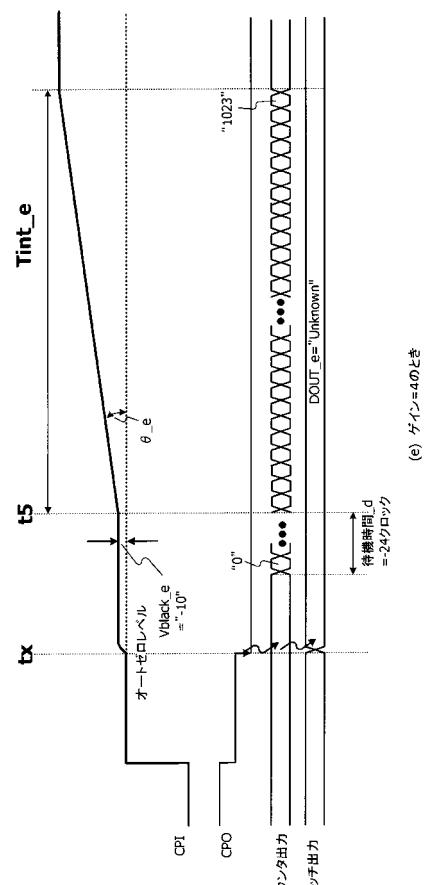

D変換する場合のタイミングチャートを示している。図12に示すように、この場合、被変換アナログ電圧( $V_{b1ack\_e}$  = “-10”)の極性は、電圧レベルが正の値になる画素からの被変換アナログ電圧の極性とは反対であるため、被変換アナログ電圧のサンプリングを開始した時間 $t_x$ において、ノードCPIの電圧レベルは、オートゼロレベル(インバータ回路12の入力判定電圧)を超える。このため、時間 $t_x$ でラッチ回路13がカウンタ15の出力値をラッチすることになるが、カウンタ15は計数開始前であるため、AD変換動作が正常に行われないこととなる。従って、OBレベル(平均ノイズ電圧)が目標ノイズ電圧を下回る場合は、カウンタ15の計数開始タイミングの調整と共に、被変換アナログ電圧のサンプリング開始時間 $t_x$ より前に、予め、ノードCPIの電圧レベルを、オートゼロレベルよりも下げておく(ランプ電圧の電圧変化方向とは反対の方向に変化させる)必要がある。

#### 【0081】

以下、制御基準タイミングに対するカウンタ15の計数開始タイミングの調整に加え、制御基準タイミングにおける参照電圧の基準電圧レベルの調整を行う場合の制御について、図13～図15を基に説明する。

#### 【0082】

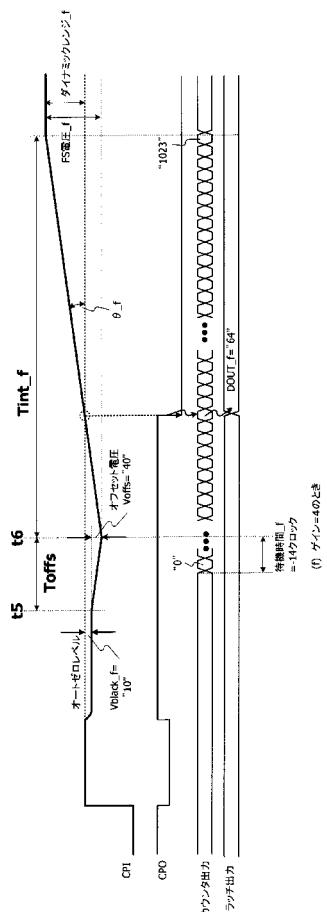

図13に、電圧レベルが負の値になるOB画素からの被変換アナログ電圧をAD変換する場合において、ランプ波発生回路14を反転動作させてランプ電圧にオフセット電圧を発生させた場合のタイミングチャートを示す。

#### 【0083】

制御回路18は、図13及び図14に示すように、制御基準タイミング $t_6$ の前に、ノードCPIの電圧レベルの調整を行うオフセット時間 $T_{off\_f\_s}$ 及び電圧レベルの調整量であるオフセット電圧 $V_{off\_f\_s}$ を設定する。ここで、本実施形態では、図13及び図14に示すように、OB部16のウィンドウ1及びウィンドウ2に含まれるOB画素夫々についての被変換アナログ電圧の電圧レベル $V_{b1ack\_f}$  = 約“10”、ゲイン = 4である。従って、制御回路18は、ノードCPIの電圧レベルを“40”( = “10” × 4)低下させるように、オフセット電圧 $V_{off\_f\_s}$  = “40”に設定する。この場合のオフセット時間 $T_{off\_f\_s}$ は、電圧レベルは1クロックにつき“1”(dec)低下するので、40クロックとなる。

#### 【0084】

ランプ波発生回路14は、制御回路18によって設定されたオフセット時間 $T_{off\_f\_s}$ の開始時間 $t_5$ から、反転動作して、出力するランプ電圧の電圧レベルを下げていき、ノードCPIの電圧レベルを下げていく。従って、制御基準タイミング $t_6$ におけるノードCPIの電圧レベル(参照電圧の基準電圧レベル)は、擬似的に、オートゼロレベルから、(“10” + “40”) = “50”下がったレベルとなる。また、このときの平均化処理部19の出力値(OBレベル)は、OB画素夫々についての被変換アナログ電圧の電圧レベル $V_{b1ack\_f}$ (約“10”) + オフセット電圧 $V_{off\_f\_s}$ (“40”) = “50”となる。

#### 【0085】

引き続き、制御回路18は、OBレベルと目標ノイズ電圧の差を示す指標値に基づいてカウンタ待機時間を算出する。制御回路18は、比較器から出力される平均化処理部19からのOBレベル( $T_{off\_f\_s} + V_{b1ack\_f}$ )と目標ノイズ電圧設定回路20からの目標ノイズ電圧( $N_{sp}$ )の差を受け付け、カウンタ待機時間 $T_{cw\_f}$ として保存する。カウンタ待機時間 $T_{cw\_f}$ は、ランプ電圧の電圧レベルを変化させるオフセット時間 $T_{off\_f\_s}$ 、OB画素からの被変換アナログ電圧 $V_{b1ack\_f}$ 、目標ノイズ電圧 $N_{sp}$ を用いて、以下の数9で求められる。

#### 【0086】

##### [数9]

$$T_{cw\_f} = T_{off\_f\_s} + V_{b1ack\_f} - N_{sp}$$

#### 【0087】

10

20

30

40

50

本実施形態では、数9より、カウンタ待機時間  $T_{c w\_f}$  は、“40”+“10”-“64”=“-14”となる。従って、制御回路18は、図13に示すように、カウンタ15の計数開始タイミングを、制御基準タイミング  $t_6$  を起点として、カウンタ待機時間  $T_{c w\_f}$  = “-14”クロック分調整する(14クロック分早める)。以上の動作により、OB部16のOBレベルの値が、擬似的に、目標ノイズ電圧の値とほぼ等しくなり、AD変換が良好に行われる。

#### 【0088】

また、制御回路18内に保存されたカウンタ待機時間  $T_{c w\_f}$  は、有効画素部16aからの被変換アナログ電圧をAD変換処理する際に利用する。これによって、OBレベルの値が、擬似的に目標ノイズ電圧の値とほぼ等しくなるので、図11に示す有効画素部16aからの被変換アナログ電圧に含まれる光電変換による信号成分111のダイナミックレンジを十分に大きくできる。

#### 【0089】

図15に、電圧レベルが負の値になるOB画素からの被変換アナログ電圧をAD変換する場合のタイミングチャートの一例を示す。図15に示すように、OB画素からの被変換アナログ電圧の電圧レベルは、 $V_{b1ack\_g}$  = “-10”相当であり、この場合の待機時間  $T_{c w\_f}$  は、上述したように、“-14”となる。このとき、ラッチ回路13から出力されるAD変換結果  $D_{out\_g}$  は、以下の数10で求められる。

#### 【0090】

##### 【数10】

$$D_{out\_g} = V_{b1ack\_g} + V_{off\_s} - T_{c w\_f}$$

#### 【0091】

従って、図15に示す場合には、AD変換結果  $D_{out\_g}$  = “-10”+“40”-“-14”=“44”となる。

#### 【0092】

従って、OBレベル(平均ノイズ電圧)が目標ノイズ電圧を下回る場合に、制御基準タイミングに対するカウンタ15の計数開始タイミングの調整に加え、制御基準タイミングにおける参照電圧の基準電圧レベルの調整を行うことで、OBレベル(平均ノイズ電圧)と目標ノイズ電圧の差が正負の何れになるかに拘わらず、AD変換を良好に行うことが可能になる。

#### 【0093】

##### 第3実施形態

本発明に係るA/D変換器、及び、該A/D変換器を備えたセンサシステムの第3実施形態について、図16及び図18を基に説明する。上記第1及び第2実施形態では、制御基準タイミングに対するカウンタの計数開始タイミングの調整を行う場合について説明したが、本実施形態では、計数開始タイミングにおける参照電圧の基準電圧レベルの調整を行う場合について説明する。

#### 【0094】

先ず、本実施形態のA/D変換器及びセンサシステムの構成について図18を基に説明する。本実施形態のA/D変換器及びセンサシステムの基本構成は、上記第1及び第2実施形態におけるA/D変換器及びセンサシステムの基本構成と同じである。

#### 【0095】

本実施形態の制御回路18は、OBレベル(平均ノイズ電圧)と目標ノイズ電圧の差を示す指標値を算出し、指標値に基づいて、計数開始タイミングにおける参照電圧の基準電圧レベルの調整量を算出し、計数開始タイミング前に、ランプ電圧の電圧変化方向に、参照電圧の基準電圧レベルを調整量に基づいて変化させる。

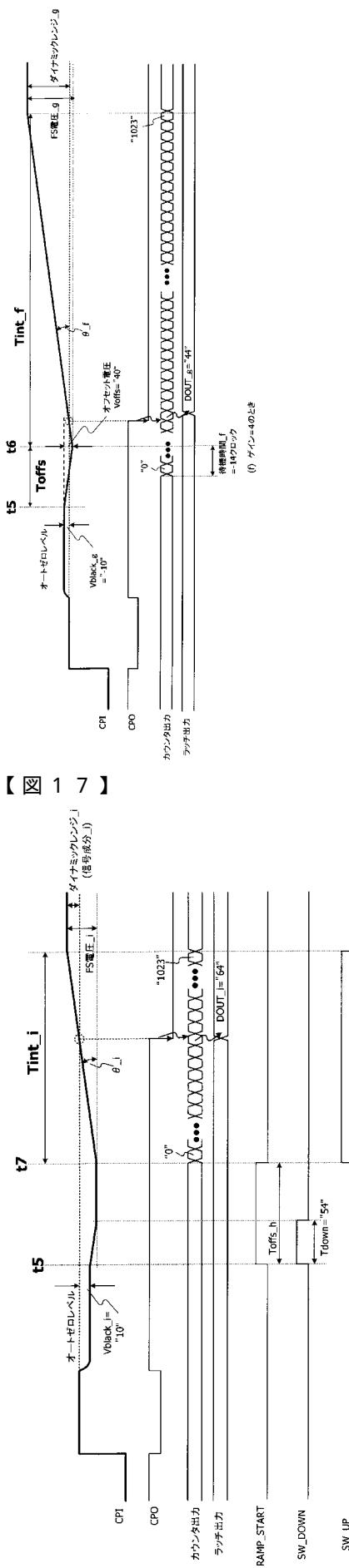

#### 【0096】

本実施形態のセンサシステムの動作について、図16を基に説明する。ここで、図16は、本実施形態において、計数開始タイミングにおける参照電圧の基準電圧レベルの調整を説明するタイミングチャートである。また、ここでは、上記第1及び第2実施形態と同

10

20

30

40

50

様に、A / D 変換器の入力信号に対するゲインが4に設定されている場合を想定して説明する。

【0097】

本実施形態の制御回路18は、ランプ波発生回路14を制御基準タイミングt7より前に一定期間動作させて、ランプ電圧の電圧変化方向（ここでは、増加方向）に、参照電圧の基準電圧レベルを変化させる。ランプ電圧 $V_{RAMP}$ の増加量は、ランプ波発生回路14の動作時間 $T_{up}$ によって規定される。ランプ波発生回路14の動作時間 $T_{up}$ は、OBレベル（平均ノイズ電圧） $V_{back}$ と目標ノイズ電圧 $N_{sp}$ を用いて、以下の数11で求められる。

【0098】

10

【数11】

$$T_{up} = V_{back} - N_{sp}$$

【0099】

ここで、本実施形態では、図16に示すように、OB画素からの被変換アナログ電圧をA / D 変換したA / D 変換データの値 $V_{back\_h} = "100"$ 、目標ノイズ電圧 $N_{sp} = "64"$ である。従って、ランプ波発生回路14の動作時間 $T_{up}$ は、"100" - "64" = "36"クロックとなる。

【0100】

制御回路18は、図16に示すように、時間t5から動作時間 $T_{up}$ の間、ランプ波発生回路14を動作させてランプ電圧を増加する方向に変化させる。結果として、ノードCPIの電圧レベルは、被変換アナログ電圧のサンプリング時の電圧レベルから"36"レベル分増加する。尚、時間t5は、制御基準タイミングt7の直前に設定された基準電圧レベルの調整のために割り当てられた時間 $T_{off\_start\_h}$ の開始時間である。時間 $T_{off\_start\_h}$ は、センサシステム3の回路特性等を考慮して予め設定されている。

20

【0101】

引き続き、制御回路18は、図16に示すように、積分時間 $T_{int\_h}$ の間、即ち、信号 $RAMP\_START$ の立ち下がり（制御基準タイミングt7）から、信号 $SW\_UP$ の立ち下がり（ランプ波発生回路14の運転時間 $T_{int\_h}$ の終了時間）までの時間、ランプ波発生回路14のランプ電圧の出力を行う。ここで、積分時間 $T_{int\_h}$ は、A / D 変換器の分解能と同じ数のクロック数で規定される固定時間である。本実施形態では、A / D 変換器の分解能（カウンタのビット数）が10bitなので、積分時間 $T_{int\_h}$ は、"1024 (= 2<sup>10</sup>)"クロック分となる。

30

【0102】

本実施形態では、図16に示すように、参照電圧の基準電圧レベル、即ち、ノードCPIの電圧レベルを被変換アナログ電圧のサンプリング時の電圧レベル $V_{back\_h} = "100"$ から"36"レベル分上昇させる。この場合、参照電圧を"64 (= 100 - 36)"レベル上昇させると、ノードCPIの電圧レベルがインバータ12の出力切り替えレベルであるオートゼロレベルを超える。このときのカウンタ15の出力値は"64"であり、A / D 変換結果 $DOUT\_h = "64"$ となる。従って、計数開始タイミングにおける参照電圧の基準電圧レベルを変化させることにより、OBレベルを擬似的に目標ノイズ電圧の値に設定することが可能になる。

40

【0103】

第4実施形態

本発明に係るA / D 変換器、及び、該A / D 変換器を備えたセンサシステムの第4実施形態について、図17及び図18を基に説明する。本実施形態では、上記第3実施形態において、OBレベル（平均ノイズ電圧）が目標ノイズ電圧を上回る場合と下回る場合で、制御回路18が異なる設定を行う場合について説明する。

【0104】

先ず、本実施形態のA / D 変換器及びセンサシステムの構成について図18を基に説明する。本実施形態のA / D 変換器及びセンサシステムの基本構成は、上記第3実施形態に

50

おける A / D 変換器及びセンサシステムの基本構成と同じである。

【 0 1 0 5 】

本実施形態の制御回路 18 は、O B レベル（平均ノイズ電圧）と目標ノイズ電圧の差を示す指標値に基づいて、計数開始タイミングにおける参照電圧の基準電圧レベルの調整量を算出する。そして、O B レベル（平均ノイズ電圧）が目標ノイズ電圧を上回る場合に、計数開始タイミング前に、ランプ電圧の電圧変化方向に、参照電圧の基準電圧レベルを調整量に基づいて変化させる。また、O B レベル（平均ノイズ電圧）が目標ノイズ電圧を下回る場合に、ランプ電圧の電圧変化方向とは反対の方向に、参照電圧の基準電圧レベルを調整量に基づいて変化させる。

【 0 1 0 6 】

10

本実施形態のセンサシステムの動作について、図 17 を基に説明する。ここで、図 17 は、本実施形態において、計数開始タイミングにおける参照電圧の基準電圧レベルの調整を説明するタイミングチャートである。また、ここでは、上記第 1 ~ 第 3 実施形態と同様に、A / D 変換器の入力信号に対するゲインが 4 に設定されている場合を想定して説明する。

【 0 1 0 7 】

尚、本実施形態の制御回路 18 は、O B レベル（平均ノイズ電圧）が目標ノイズ電圧を上回る場合は、上記第 3 実施形態と同じ処理を行う。

【 0 1 0 8 】

20

本実施形態の制御回路 18 は、O B レベル（平均ノイズ電圧）が目標ノイズ電圧を下回る場合、ランプ波発生回路 14 を制御基準タイミング  $t_7$  より前に、一定期間反転動作させて、ランプ電圧の電圧変化方向とは反対の方向（ここでは、減少方向）に、参照電圧の基準電圧レベルを変化させる。ランプ電圧  $V_{RAMP}$  の減少量は、ランプ波発生回路 14 の反転動作時間  $T_{down}$  によって規定される。ランプ波発生回路 14 の反転動作時間  $T_{down}$  は、O B レベル（平均ノイズ電圧）  $V_{black}$  と目標ノイズ電圧  $N_{sp}$  を用いて、以下の数 12 で求められる。

【 0 1 0 9 】

[ 数 1 2 ]

$$T_{down} = V_{black} - N_{sp}$$

【 0 1 1 0 】

30

ここで、本実施形態では、図 17 に示すように、O B 画素からの被変換アナログ電圧を A / D 変換した A / D 変換データの値  $V_{black\_h} = "10"$  、目標ノイズ電圧  $N_{sp} = "64"$  である。従って、ランプ波発生回路 14 の反転動作時間  $T_{down}$  は、"10" - "64" = "54" クロックとなる。

【 0 1 1 1 】

制御回路 18 は、図 17 に示すように、時間  $t_5$  から反転動作時間  $T_{down}$  の間、ランプ波発生回路 14 を反転動作させてランプ電圧を減少する方向に変化させる。結果として、ノード C P I の電圧レベルは、被変換アナログ電圧のサンプリング時の電圧レベルから "54" レベル分減少する。尚、時間  $t_5$  は、上記第 3 実施形態と同様に、制御基準タイミング  $t_7$  の直前に設定された基準電圧レベルの調整のために割り当てられた時間  $T_{off\_fs\_h}$  の開始時間である。時間  $T_{off\_fs\_h}$  は、センサシステム 3 の回路特性等を考慮して予め設定されている。

40

【 0 1 1 2 】

引き続き、制御回路 18 は、図 17 に示すように、積分時間  $T_{int\_i}$  の間、即ち、信号  $RAMP\_START$  の立ち下がり（制御基準タイミング  $t_7$  ）から、信号  $SW\_DOWN$  の立ち下がり（積分時間  $T_{int\_i}$  の終了時間）までの時間、ランプ波発生回路 14 のランプ電圧の出力を行う。尚、積分時間  $T_{int\_i}$  は、上記第 3 実施形態と同様に、A / D 変換器の分解能と同じ数のクロック数で規定される固定時間であり、"1024 (= 2^10)" クロック分となる。

【 0 1 1 3 】

50

本実施形態では、図17に示すように、ノードCPIの電圧レベル(参照電圧の基準電圧レベル)を被変換アナログ電圧のサンプリング時の電圧レベルV<sub>b1ack\_i</sub> = “10”から“54”レベル分減少させる。この場合、参照電圧を“64(=10+54)”レベル上昇させると、ノードCPIの電圧レベルがオートゼロレベルを超える。このときのカウンタ15の出力値は“64”であり、AD変換結果D<sub>OUT\_i</sub> = “64”となる。従って、計数開始タイミングにおける参照電圧の基準電圧レベルを変化させることにより、OBレベルを擬似的に目標ノイズ電圧の値に設定することが可能になる。

#### 【0114】

##### 第5実施形態

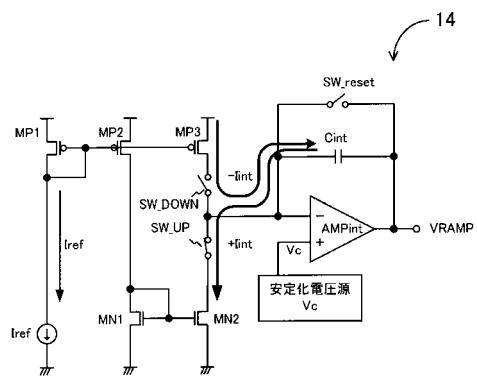

本発明に係るA/D変換器、及び、該A/D変換器を備えたセンサシステムで用いるランプ発生回路14について、図19及び図20を基に説明する。 10

#### 【0115】

図19に、本実施形態のランプ波発生回路14の概略構成例を示す回路図を、図20に、図19に示すランプ波発生回路14の動作を説明するタイミングチャートを示す。 11

#### 【0116】

ランプ波発生回路14は、図19に示すように、定電流源I<sub>ref</sub>からの電流値を複製する第1カレントミラー回路及び第2カレントミラー回路と、第1カレントミラー回路で複製した電流により放電し、第2カレントミラー回路で複製した電流により充電する積分容量C<sub>int</sub>と、積分容量C<sub>int</sub>に対する第1カレントミラー回路による放電及び第2カレントミラー回路による充電を逐一的に切り替えるスイッチ回路SW\_DOWN、SW\_UPと、を備えて構成される。本実施形態のランプ波発生回路14は、更に、安定化電圧源V<sub>c</sub>、差動アンプAMP<sub>int</sub>、リセットスイッチSW\_RESETを備えており、 20 安定化電圧源V<sub>c</sub>、差動アンプAMP<sub>int</sub>、積分容量C<sub>int</sub>、リセットスイッチSW\_RESETによって定積分器が構成される。 21

#### 【0117】

第1カレントミラー回路は、PMOSトランジスタMP1～MP3から構成される。第1カレントミラー回路では、定電流源I<sub>ref</sub>によって供給される定電流I<sub>ref</sub>が、PMOSトランジスタMP3を介して-I<sub>int</sub>として複製される。第2カレントミラー回路は、PMOSトランジスタMP1、MP2、NMOSトランジスタMN1、MN2から構成される。第2カレントミラー回路では、定電流源I<sub>ref</sub>によって供給される定電流I<sub>ref</sub>が、NMOSトランジスタMN2を介して電流+I<sub>int</sub>として複製される。 30

#### 【0118】

ランプ波発生回路14は、スイッチ回路SW\_UPをオン状態に、スイッチ回路SW\_DOWNをオフ状態にすることで、ランプ電圧を増加方向に変化させ、スイッチ回路SW\_UPをオフ状態に、スイッチ回路SW\_DOWNをオン状態にすることで、ランプ電圧を減少方向に変化させる。 31

#### 【0119】

次に、ランプ波発生回路14の動作原理について説明する。

#### 【0120】

第1カレントミラー回路により積分容量C<sub>int</sub>が充電される場合(-I<sub>int</sub>によって電流を注入する場合)、ランプ波発生回路14の出力電圧であるランプ電圧V<sub>RAMP</sub>は、減少する方向に電圧変化する。このときのランプ電圧V<sub>RAMP</sub>は、積分時間をT<sub>off</sub>fsとすると、以下の数13で求められる。 40

#### 【0121】

##### [数13]

$$V_{RAMP} = - (I_{int} / C_{int}) \times T_{off}fs + V_c$$

#### 【0122】

第2カレントミラー回路により積分容量C<sub>int</sub>が放電される場合(+I<sub>int</sub>によって電流を引き抜く場合)、ランプ電圧V<sub>RAMP</sub>は、増加する方向に電圧変化する。このときのランプ電圧V<sub>RAMP</sub>は、積分時間をT<sub>int</sub>とすると、以下の数14で求められ 50

る。

【0123】

[数14]

$$V_{RAMP} = + (I_{int} / C_{int}) \times T_{int} + V_c$$

【0124】

また、定電流源  $I_{ref}$  の  $\pm I_{int}$  に対するカレントミラー比を  $M$  とおくと、数13は以下の数15のよう に表すことができ、数14は以下の数16のよう に表せる。

【0125】

[数15]

$$V_{RAMP} = - M \times (I_{ref} / C_{int}) \times T_{off} + V_c \quad 10$$

【0126】

[数16]

$$V_{RAMP} = + M \times (I_{ref} / C_{int}) \times T_{int} + V_c$$

【0127】

従って、数15及び数16より、傾き（単位時間当たりの電圧変化量）は以下の数17及び数18で表される。

【0128】

[数17]

$$= - M \times (I_{ref} / C_{int})$$

【0129】

[数18]

$$= + M \times (I_{ref} / C_{int})$$

【0130】

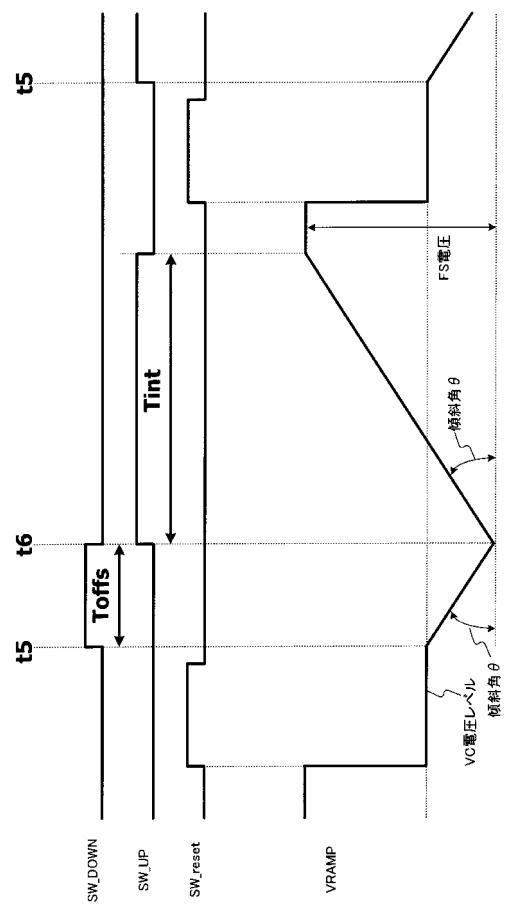

以下、ランプ波発生回路14の動作タイミングについて図20を基に説明する。

【0131】

ランプ波発生回路14は、画素部16からの被変換アナログ電圧のサンプリングを開始する前毎に、図19に示す積分容量  $C_{int}$  をリセット（放電）するために、リセットスイッチ  $SW_{reset}$  をHレベルにする。

【0132】

ランプ波発生回路14は、制御回路18によってオフセット時間  $T_{off}$  が設定されている場合には、ランプ電圧  $V_{RAMP}$  を減少する方向に電圧変化させるために、オフセット時間  $T_{off}$  の開始時間  $t_5$  のタイミングで、スイッチ回路  $SW_{DOWN}$  をHレベル（オン状態）に、スイッチ回路  $SW_{UP}$  をLレベル（オフ状態）にする。ランプ波発生回路14は、オフセット時間  $T_{off}$  の経過後、時間  $t_6$  でスイッチ回路  $SW_{DOWN}$  をLレベル（オフ状態）にする。このときのランプ電圧  $V_{RAMP}$  は数15で、傾き は数17で表される。数13及び数15に示すように、ランプ電圧  $V_{RAMP}$  の減少量は、積分時間  $T_{off}$  で制御できる。 30

【0133】

ランプ波発生回路14は、制御基準タイミング  $t_6$  から運転時間  $T_{int}$  の間、ランプ電圧  $V_{RAMP}$  を増加する方向に電圧変化させるために、スイッチ回路  $SW_{DOWN}$  をLレベル（オフ状態）に、スイッチ回路  $SW_{UP}$  をHレベル（オン状態）にする。ランプ波発生回路14は、運転時間  $T_{int}$  の経過後、スイッチ回路  $SW_{UP}$  をLレベル（オフ状態）にする。このときのランプ電圧  $V_{RAMP}$  は数16で、傾き は数18で表される。数14及び数16に示すように、ランプ電圧  $V_{RAMP}$  の増加量は、積分時間  $T_{int}$  で制御できる。 40

【0134】

上述したように、ランプ電圧  $V_{RAMP}$  の傾き を調整することで、A/D変換器のゲイン（利得）を設定することが可能である。数17及び数18より、傾き は、カレントミラー比  $M$ 、定電流源  $I_{ref}$ 、積分容量  $C_{int}$  をパラメータとする関数で定義されるので、カレントミラー比  $M$ 、定電流源  $I_{ref}$ 、積分容量  $C_{int}$  の何れか、或いは複数

を調整可能に構成することで傾きを調整することが可能になる。

【0135】

別実施形態

1 上記第5実施形態において、図19に示すランプ波発生回路14の定電流源Ir<sub>ef</sub>は、定電圧源と、定電圧源から発生される電圧を容量性負荷の充放電に寄与する定電流に変換する抵抗負荷と、を備えるように構成し、抵抗負荷をスイッチトキャパシタで構成しても良い。

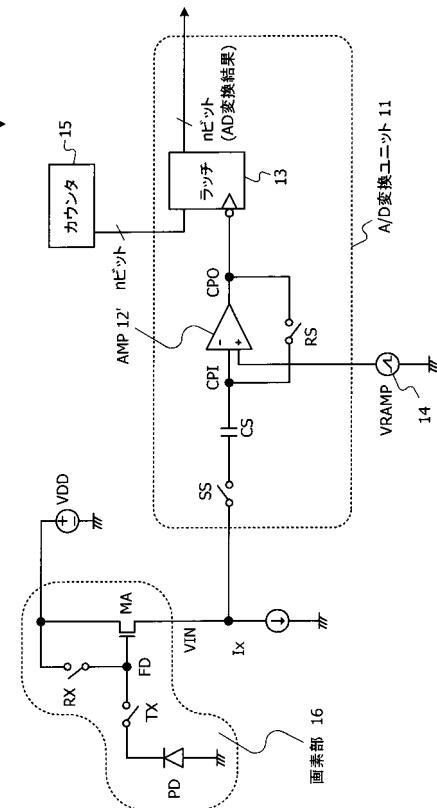

【0136】

2 上記第1～第5実施形態では、演算器がインバータ回路12を用いて構成されている場合について説明したが、演算器の構成は、これに限るものではない。演算器は、図22に示すように、被変換アナログ電圧とランプ電圧を夫々入力電圧とする差動入力型の演算増幅器で構成されていても良い。

【0137】

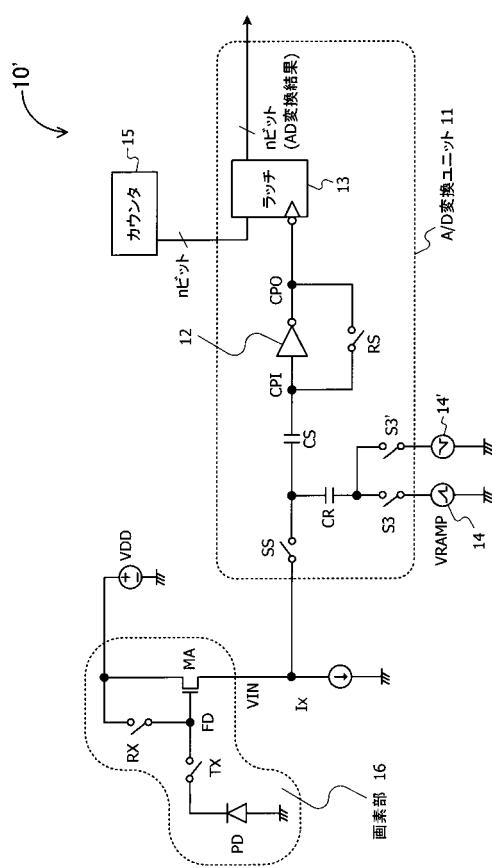

3 上記第1～第5実施形態では、制御回路18は、参照電圧の基準電圧レベルを、ランプ電圧の電圧変化方向とは反対の方向に変化させる場合に、ランプ波発生回路14を反転動作させる場合について説明したが、これに限るものではない。図21に示すように、A/D変換ユニット11に、ランプ波発生回路14とは極性が反対のランプ波発生回路14'、と、演算器に接続するランプ波発生回路14とランプ波発生回路14'を切り替えるためのスイッチS3'を設け、スイッチS3とスイッチS3'の切り替え動作によって、参照電圧の基準電圧レベルを変化させるように構成しても良い。

【図面の簡単な説明】

【0138】

【図1】従来技術に係るコラム型A/D変換器及び個体撮像素子の概略構成を示す概略ブロック図

【図2】図1に示すコラム型A/D変換器及び個体撮像素子の各ノードにおける概略信号波形を示す波形図

【図3】図1に示すコラム型A/D変換器のインバータ回路の構成と入出力特性を示す説明図

【図4】従来技術に係るコラム型A/D変換器を備えたセンサシステムの概略構成を示す概略ブロック図

【図5】従来技術に係るA/D変換器において、センサ部の有効画素部及び光学的黒画素部夫々から出力される被変換アナログ電圧をディジタル変換したディジタル変換信号を示す波形図

【図6】従来技術に係るA/D変換器において、ランプ電圧の電圧変化の傾きを変化させた場合におけるA/D変換結果の出力タイミングと出力値を示すタイミングチャート

【図7】従来技術に係るA/D変換器において、ゲインの設定値を変更した場合のダイナミックレンジを示すタイミングチャート

【図8】本発明に係るA/D変換器を備えたセンサシステムの第1実施形態における概略構成を示す概略ブロック図

【図9】本発明に係るA/D変換器を備えたセンサシステムの第1実施形態における演算器の入力ノード(ノードCPI)、カウンタ出力及びA/D変換結果夫々の電圧波形を示すタイミングチャート

【図10】本発明に係るA/D変換器を備えたセンサシステムの第2実施形態において、カウンタの計数開始タイミングを説明するタイミングチャート

【図11】本発明に係るA/D変換器の第2実施形態において、センサ部の有効画素部及び光学的黒画素部夫々から出力される被変換アナログ電圧をディジタル変換したディジタル変換信号を示す波形図

【図12】本発明に係るA/D変換器を備えたセンサシステムの第2実施形態において、カウンタの計数開始タイミングを説明するタイミングチャート

【図13】本発明に係るA/D変換器を備えたセンサシステムの第2実施形態において、

10

20

30

40

50

カウンタの計数開始タイミング及びオフセット電圧の調整方法を説明するタイミングチャート

【図14】本発明に係るA/D変換器を備えたセンサシステムの第2実施形態における概略構成を示す概略ブロック図

【図15】本発明に係るA/D変換器を備えたセンサシステムの第2実施形態において、カウンタの計数開始タイミング及びオフセット電圧の調整方法を説明するタイミングチャート

【図16】本発明に係るA/D変換器を備えたセンサシステムの第4実施形態において、参照電圧の基準電圧レベルの調整を説明するタイミングチャート

【図17】本発明に係るA/D変換器を備えたセンサシステムの第5実施形態において、参照電圧の基準電圧レベルの調整を説明するタイミングチャート

【図18】本発明に係るA/D変換器を備えたセンサシステムの第4実施形態における概略構成を示す概略ブロック図

【図19】本発明に係るA/D変換器を備えたセンサシステムで用いるランプ電圧発生回路の概略構成例を示す回路図

【図20】本発明に係るA/D変換器を備えたセンサシステムで用いるランプ電圧発生回路の動作を説明するタイミングチャート

【図21】本発明に係るA/D変換器を備えたセンサシステムで用いるA/D変換ユニットの別実施形態における概略構成例を示す概略回路図

【図22】本発明に係るA/D変換器を備えたセンサシステムで用いるA/D変換ユニットの別実施形態における概略構成例を示す概略回路図

【符号の説明】

【0139】

|            |                      |    |

|------------|----------------------|----|

| 1 ~ 3 :    | 本発明に係るセンサシステム        |    |

| 1 0 :      | 従来のコラム型A/D変換器        |    |

| 1 1 :      | A/D変換ユニット            |    |

| 1 2 :      | インバータ回路              |    |

| 1 3 :      | ラッチ回路                |    |

| 1 4 :      | ランプ波発生回路(ランプ電圧発生回路)  |    |

| 1 5 :      | カウンタ                 | 30 |

| 1 6 :      | 固体撮像素子の画素部           |    |

| 1 7 :      | 電圧比較回路               |    |

| 1 8 :      | 制御回路                 |    |

| 1 9 :      | 平均化処理部               |    |

| 2 0 :      | 目標ノイズ電圧設定回路          |    |

| 1 0 0 :    | 従来技術に係るセンサシステム       |    |

| C P I :    | インバータ回路の入力ノード        |    |

| C P O :    | インバータ回路の出力ノード        |    |

| C S、C R :  | キャパシタ                |    |

| I x :      | 電流源                  | 40 |

| M N 1 :    | Nチャンネル型MOSFET        |    |

| M N 2 :    | Nチャンネル型MOSFET        |    |

| M P 1 :    | Pチャンネル型MOSFET        |    |

| M P 2 :    | Pチャンネル型MOSFET        |    |

| M P 3 :    | Pチャンネル型MOSFET        |    |

| P D :      | フォトダイオード             |    |

| R S :      | リセットレベルのサンプリングスイッチ   |    |

| R X :      | リセットスイッチ             |    |

| S 3、S 3' : | ランプ電圧転送用スイッチ         |    |

| S S :      | 被変換アナログ電圧のサンプリングスイッチ | 50 |

T X : スイッチ

V D D : システム電源供給線（第2電源供給線）

V I N : 被変換アナログ電圧の入力ノード

V R A M P : ランプ電圧

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 8 】

〔 図 9 〕

【 図 10 】

【図 1 1】

【図 1 2】

(e) ゲイン=4のとき

【図 1 3】

【図 1 4】

【図15】

【図16】

【 図 1 7 】

【 囮 1 8 】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(56)参考文献 特開昭57-160221(JP,A)

特開2003-198371(JP,A)

特開2000-286706(JP,A)

特開2007-019682(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00-1/88

H04N 5/335