(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3967800号

(P3967800)

(45) 発行日 平成19年8月29日(2007.8.29)

(24) 登録日 平成19年6月8日(2007.6.8)

(51) Int.C1.

F 1

|                |              |                  |                |              |                |

|----------------|--------------|------------------|----------------|--------------|----------------|

| <b>G 1 1 B</b> | <b>20/14</b> | <b>(2006.01)</b> | <b>G 1 1 B</b> | <b>20/14</b> | <b>3 5 1 A</b> |

| <b>H 0 3 L</b> | <b>7/06</b>  | <b>(2006.01)</b> | <b>H 0 3 L</b> | <b>7/06</b>  | <b>A</b>       |

| <b>H 0 4 L</b> | <b>7/033</b> | <b>(2006.01)</b> | <b>H 0 4 L</b> | <b>7/02</b>  | <b>B</b>       |

請求項の数 9 (全 16 頁)

(21) 出願番号

特願平9-256401

(22) 出願日

平成9年9月22日(1997.9.22)

(65) 公開番号

特開平10-134523

(43) 公開日

平成10年5月22日(1998.5.22)

審査請求日

平成16年8月10日(2004.8.10)

(31) 優先権主張番号

96306940.6

(32) 優先日

平成8年9月24日(1996.9.24)

(33) 優先権主張国

英国(GB)

(73) 特許権者 398038580

ヒューレット・パッカード・カンパニー

HEWLETT-PACKARD COMPANY

アメリカ合衆国カリフォルニア州パロアルト ハノーバー・ストリート 3000

(74) 代理人 100081721

弁理士 岡田 次生

(72) 発明者 クリストファー・ヒュー・ウィリアムズ

イギリス、ウェールズ、エヌ・ピー6、6

エヌ・エックス、グウェント、ウェブストウ、デバウデン、ウェル・レーン、セン・

コッド(番地なし)

審査官 小林 大介

最終頁に続く

(54) 【発明の名称】信号処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

可変ビットレートを有する信号を処理する装置であって、

ゲイン制御信号を導出し、該ゲイン制御信号にしたがって前記可変ビットレートを有する信号のゲインを制御するゲイン制御手段と、

一組の係数にしたがって、ゲイン制御された可変ビットレートを有する信号を等化する適応等化手段であって、フィルタリングされた適応等化手段の出力にしたがって前記一組の係数を適応化する手段を含む適応等化手段と、

前記ゲイン制御された可変ビットレートを有する信号に応答して、システム読み取りクロック信号として動作するように出力周波数を出力する位相ロックループ手段と、

を備え、少なくとも、

(a) 前記一組の係数が予め設定されたしきい値を超えたとき、

(b) 前記ゲイン制御信号が予め設定されたしきい値を超えたとき、

のいずれか1つに応答して前記位相ロックループ手段の周波数をプリセット値にリセットするリセット手段をさらに備える、前記装置。

## 【請求項 2】

前記信号は、一連のトラックまたはデータのストリームであって、前記リセット手段は、前記位相ロックループ手段の周波数を、現時点におけるストリームまたはトラックの開始時の出力周波数にリセットする、請求項1記載の装置。

## 【請求項 3】

10

20

前記位相ロックループ手段は、

前記信号と前記位相ロックループ手段の前記出力周波数との間の位相のエラー信号を導出する位相検知器と、

前記エラー信号をフィルタリングするループフィルタと、

前記フィルタリングしたエラー信号を累算し、前記位相ロックループ手段の出力周波数を調整するためにアキュムレータ出力信号を提供する位相アキュムレータと、

を備える請求項 1 または 2 のいずれかに記載の装置。

#### 【請求項 4】

前記ループフィルタは、前記位相のエラー信号を積分するためのアキュムレータを含み

、前記リセット手段は、前記アキュムレータの中身をデフォルト値に置き換えるようにし

、これにより前記位相ロックループ手段の周波数をリセットする、請求項 3 に記載の装置

。

10

#### 【請求項 5】

前記位相ロックループ手段は、システムクロックを受け取るため、および連続するバージョンのシステムクロックを導出するためのタップ付き遅延線手段を含み、前記アキュムレータの出力は前記バージョンのうちの一つを選択するために使用される、請求項 3 または 4 のいずれかに記載の装置。

#### 【請求項 6】

位相オフセット信号を前記出力周波数に適用する手段をさらに含む請求項 5 記載の装置

。

20

#### 【請求項 7】

前記位相検知器は、前記入力信号の 2 つの予め設定されたしきい値と交差するタイミングを監視する手段と、前記交差するタイミングとシステム読み取りクロックとを比較して、これらの間の位相エラーを求める手段とを含む、請求項 3 乃至 6 のいずれかに記載の装置

。

#### 【請求項 8】

前記ループフィルタは、比例期間および積分期間を有するフィルタ関数を適用し、前記ループフィルタはそれぞれの倍数値を含み、レジスタ手段は 2 つの倍数値を記憶し、一つは速い時定数をループに提供するためのものであり、一つは遅い時定数をループに提供するためのものである、請求項 3 乃至 7 のいずれかに記載の装置。

30

#### 【請求項 9】

可変ビットレートを有する信号を処理する方法であって、

ゲイン制御信号を導出し、該ゲイン制御信号にしたがって前記可変ビットレートを有する信号のゲインを制御するステップと、

一組の係数にしたがって、ゲイン制御された可変ビットレートを有する信号を等化するステップと、

等化した出力にしたがって前記一組の係数を適応化するステップと、

前記ゲイン制御された可変ビットレートを有する信号を位相ロックループ手段に提供してシステム読み取りクロック信号として動作するように出力周波数を出力するステップと、

を含み、少なくとも、

40

( a ) 前記一組の係数が予め設定されたしきい値を超えたとき、

( b ) 前記ゲイン制御信号が予め設定されたしきい値を超えたとき、

のいずれか 1 つに応答して前記位相ロックループの周波数をプリセット値へとリセットするステップをさらに含む、前記方法。

#### 【発明の詳細な説明】

#### 【0001】

#### 【発明の属する技術分野】

本発明は、データ処理装置および方法、並びに、接続に使用される電子回路に関し、特に、これに限定されるわけではないが、DDS データ記憶システムを使用して、記憶されたデータを検索する装置および方法に関連する。また、本発明は、一般に、1 又は複数の通

50

信チャネルにおけるデータ処理の装置および方法に関する。

【0002】

【従来の技術】

特に、ISO11EC標準12247で定義されたDDS（デジタル・データ記憶）手段によって、コンピュータ・データのような、大容量のデジタル・データを確実に記憶し検索する装置を提供することが、既に知られている。

【0003】

上記のフォーマットを使用するDDS読出し／書き込み装置において、データは、1又は複数の電気磁気ヘッドを備える回転ドラムによって、磁気媒体でコーティングされたテープから成る細長い記録媒体上に記録される。テープは、2つのスプールまたはリール間に渡るパスに沿って、モータ駆動キャブスタンによって動かされ、部分的にドラムのまわりを巻く。ドラムのヘッドの回転面は、テープの移動面に対してある角度をなして配置されているので、各ヘッドは、中心線に対してある角度でテープの幅を横切って延びる連続したトラックに沿ってテープを横切る。この装置は、テープ上へ記録するに適した誤り検出訂正コードを含む信号にデータをエンコードする回路を含み、記録媒体の特性に最も適した形にそれらの信号を調整する回路を含む。データ検索のために、テープ上に記憶された境界変化を検出し、次の処理にふさわしい形式にそれらの信号を調整して対応する信号を誘導し、エンコードされたデータをデコードして、エラーを検出し訂正するために付加的な回路が備えられる。

【0004】

現在のフォーマット(DDS-2)において、データは、1インチにつきおよそ61キロビット(kbp*i*) (1センチメートルにつきおよそ24キロビット)のビット密度で記録される。このビット密度で、典型的なDDSテープ・カートリッジは、最も長く使用可能なテープと、テープが収容することができるデータ量を最大にするデータ圧縮のような技術を使用して、およそ8ギガバイト以上のデータを、現在記憶することができる。コンピュータ装置の使用が絶え間なく増加し、そのような装置によって処理され記憶されるデータ容量が増加するに従って、さらに、DDSテープ・カートリッジの容量を増やすことが望まれるようになった。

【0005】

我々は、線形記憶密度を2倍にし、ユーザ・データのために使用できる記録トラックの割合を増やすことによって、さらに記憶容量を増やす新しいフォーマット(DDS-3)を開発するプロセスにある。これとともに、これらの改良は、与えられたテープ長さのカートリッジに対して、DDS-2のデータ容量の約3倍の容量を提供すると予測されている。DDS-3フォーマットは、最も長く実行可能なテープ上に記録するとき、12ギガバイトの圧縮されていないユーザ・データか、または一般的に24ギガバイトの圧縮されたユーザ・データの記憶容量を提供するように設計される。

【0006】

この方式の詳細は我々の以前に発表された国際特許出願W095/15551によって示され、その特許出願の内容は、ここで参照されて取り入れられている。

【0007】

DDS-3の線形ビット密度がDDS-2の2倍であるため、テープの上のビット間隔は、好みの読み取りヘッドのギャップのおよそ半分である。このことは、読み取りヘッドからの出力信号が、2つの離れたレベル(+1、-1)の間で変化する代わりに、3つのレベル(+2、0、-2)の間で変化し、即ち、DDS-3は、3レベル・システムであることを意味する。

【0008】

部分応答最大確度(PRML: Partial Response Maximum-Likelihood)データ回復チャネルの使用によって、記録されたデータを回復することが提案されている。

【0009】

「部分応答」とは、検出回路入力で決定性符号間干渉を強制することによって、データ転

10

20

30

40

50

送のためにナイキスト周波数バンド幅までを必要とするだけの、実行可能な部分応答信号方式を示す。その一例は、離散的時間伝達関数  $F(D) = D + 1$  によって示される、PR - 1（または対2進（duobinary））部分応答システム（記録チャネル伝達関数）である。他の例として、クラスIVやPR - 4のようなものが存在し、これらの可能性を除くものではない。

#### 【0010】

「最大確度」とは、1度にちょうど1つの受取られたサンプルの代わりに、受取られたサンプルのシーケンスを使用する出力データの最も適当なシーケンスを選択するヴィテルビ・アルゴリズムを実行する、最大確度検出デコーディング方式を示す。

#### 【0011】

DDS - 3 の一般に提唱される方式の読み取りモードにおいて、ほぼ等化された信号が受取られて自動利得制御（AGC）にかけられ、信号振幅が確立され安定させられ、次いで完全な適応性等化（Adaptive Equalisation）にかけられ組み合わされた PR - 1 ターゲットになる。適応性等化ステップにおいて、適応性のサンプルされた有限インパルス応答フィルタが、3 レベル PR - 1 ターゲット伝達関数を提供するために使用される。一実施例において、適応性等化の後、信号は、アナログからデジタルへ変換され、3 レベル・ヴィテルビ（Viterbi）（すなわち最大確度）検出が続く。これを実行するために、クロック情報は、入力信号から抽出されて、適応性イコライザ、アナログ / デジタル変換器、およびヴィテルビ・デコーダを同期させるために使用される。他の実施例において、アナログ / デジタル変換の後で、適応性等化が代わりに実行される場合がある。

#### 【0012】

以前の DDS フォーマットにおける同様に、提案された DDS - 3 フォーマットにおいても、データは、交互のアジマス（azimuth）の一連のトラック（それぞれ A トラックおよび B トラックと呼ばれる）として記憶される。各トラックのそれぞれの端は、消耗してもよいマージン領域で占められ、フロント・マージンの後にしばしばそのマージンから区別がつかないプリアンブル領域が続く。プリアンブル領域は、通常単純な正弦波のトーンであり、データを全く運ばないが、AGC ループとクロック回復ループが速いロック・オンを達成するのを可能にし、さらに、メイン・データ領域の始まりを識別するために存在する。プリアンブル検出回路は、適応性イコライザを制御してチャネルがプリアンブルやマージン領域を適応化しないようにする。こうしないと、チャネルがデータ部分について最適化されないからである。

#### 【0013】

この明細書において、通信チャネルの用語は、記録媒体から読み取られるデータのチャネルを含む広い意味で使用される。

#### 【0014】

##### 【発明が解決しようとする課題】

DDS データ読み取りシステムは、いろいろな異なる条件下で、読み取り波形からビット・クロックを回復させることを位相同期ループ（PLL）に要求する。例えば、フィードフォーワード・イコライザ（FFE : Feed Forward Equalizer）、アナログ / デジタル変換器、およびヴィテルビ・デコーダのような他の構成装置を駆動するために使用されるので、回復された読み取りクロックは、強力でなければならない。本質的に、PLL は周波数と位相同期をトラックのはじめて獲得しなければならず、許容できる位相エラーでヘッド・テープ速度ジッタによって生じるビット周波数変動がこれに続く。

#### 【0015】

DDS - 2 フォーマットにおいて、テープの読み取りは、ビット・サンプリング時間がアイ・センタ（eye centre）にある 2 レベルの信号になる。従って、この方法が振幅変動に比較的無感応なので、PLL の位相検出器は、典型的にはゼロ交差をテストすることができます。

#### 【0016】

我々の提案する DDS - 3 フォーマットにおいて、テープの読み取りは、3 レベルの PR -

10

20

30

40

50

1信号になる。この場合、位相検出器は、入力信号の大きな部分を不適合にすることなく、単純なゼロ交差のテストをすることができない。従って、我々は、公称信号レベルの約半分、即ち、公称+2、0、-2のレベル信号について+1、-1で、閾値を有する閾値交差方式を使用する。

#### 【0017】

我々は、テープ・ドロップアウトのような一定の状況で、PLLがロックを失うことがあるを見いだした。

#### 【0018】

##### 【課題を解決するための手段】

従って、我々は、この条件またはこの条件になる状況をモニタし、条件が検出された場合、周波数をデフォルト値にリセットするシステムを設計した。また、この状況は、記録された媒体から導かれるもの以外の通信チャネルのタイプに広く適用できる。10

#### 【0019】

この発明の一面において、ビット・レートに変動を有する信号を処理する装置が提供され、この装置は、前記信号からビット・クロックを回復させる位相同期ループ手段と、前記位相同期ループ手段がそのロックを失うか、悪い条件が検出されるとき、前記位相同期ループの出力周波数を予め設定した値にリセットする手段と、を含む。

#### 【0020】

いろいろな条件が周波数の再設定をトリガするために使用されうる。例えば、周波数が、予め設定された許容バンドの外側に変化した場合、それはリセットされる。または、信号がFIRフィルタか同様のものによって適応的にフィルタされる場合、デジタル・フィルタの係数がモニタされ、これらの係数があらかじめ設定した値にリセットされる。20

#### 【0021】

ここで参照するように、FFEシステムは、キック・スタート・ルーチンを含み、フィルタ係数の反対のセットの始まりは、FFEのフィルタ係数のリセットと、PLLのデフォルト周波数のセットの両方のトリガに使用される。

#### 【0022】

さらに、信号に自動利得制御がかけられる場合、利得制御信号の大きさがモニタされ、これが、予め設定された範囲から離れるか、異常に低いSNRを示す傾向がある閾値を渡すならば、この条件は、PLL周波数をリセットするために使用される。30

#### 【0023】

##### 【発明の実施の形態】

ここに記載されているデータ記憶装置は、DATC協会規格(1987年6月、日本電子機械工業会(東京(日本)))に従うPCM音声データの記憶装置に使用されるフォーマットと同様のフォーマットで、記録テープ上の斜めのトラックにデータを記憶するらせん走査技術を利用する。しかしながら、本発明の装置は、デジタル化された音声情報よりもむしろコンピュータのデータを記憶するのに適用される。従来同様に、この装置は、ヘッド・ドラムが回転しているとき、磁気テープが所定の角度で回転ヘッド・ドラムを横切るらせん走査テープ・デッキを含む。ヘッド・ドラムは、直径に関して向かい合った一対の読み取りヘッドと、読み取りヘッドと90度の位置に、直径に関して向かい合った一対の書き込みヘッドを収納する。従来同様に、これらのヘッドは、テープを横切って斜めの重なるトラックに書き込む。1つのヘッドで書き込まれるトラックは、正のアジマスを有し、もう一つのヘッドで書き込まれるトラックは、負のアジマスを有する。40

#### 【0024】

トラックは、装置に提供されるデータ(メイン・データ)およびサブ・コードとして知られている補助情報の項目を記憶するために使用され、このサブ・コードは、例えば、メイン・データの論理的な構成、テープ上の配置、一定の記録パラメータ(フォーマット識別子やテープ・パラメータなど)、およびテープ使用ヒストリに関する。また、トラックは、データ・バイト境界を識別することを可能にする同期バイト(sync bytes)を含み、50

この同期バイトは、テープ移動などを制御するタイミング信号を生成するために使用される。各々のトラックの始めと終わりにはマージン領域があり、始めのマージンとメイン・データ領域の間にプリアンブル・ロックがある。

#### 【0025】

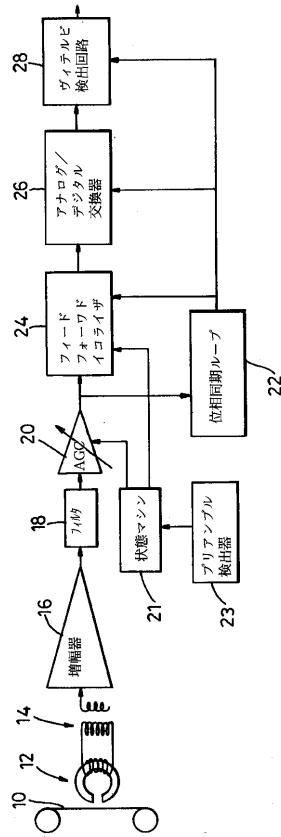

図1において、テープ10上に記憶されたデータは、メイン・ドラム上の読み取りヘッド12によって読み取られ、信号は回転変圧器14を通して増幅器16に渡され、そこからフィルタ18に渡され、組み合わされたPR-1ターゲットに初期近似等化される。実際上、一端をアースするのではなくむしろ読み取りヘッドから差動信号が受け取られる。しかし、図1は、1つの信号ラインのみを表示している。それから、信号は、自動利得制御(AGC)回路20に供給され、フィルタおよび積分回路18から受取った3レベル信号の+2と-2の振幅を確立して安定させる。AGC回路20からの信号は、クロック信号を回復する位相同期ループ(PLL)22に供給され、更に、結合されたPR-1ターゲットへの適応性等化を提供するフィードフォーワード・イコライザ(FFE)24として記載される適応フィルタに渡されるので、全チャネル周波数応答が、理想的なPR-1の部分応答チャネルの特性と一致する。フィルタされた信号は、アナログ/デジタル変換器(ADC)26に供給され、フィルタされた信号のデジタル化されたバージョンとなり、ヴィテルビ検出回路28へ供給される。ヴィテルビ検出回路28の出力は、NRZI-エンコードされたデータ・ストリームである。他の実施例において、フィードフォーワード・イコライザ24は、アナログ/デジタル変換器の前でなくて後に設置される。

#### 【0026】

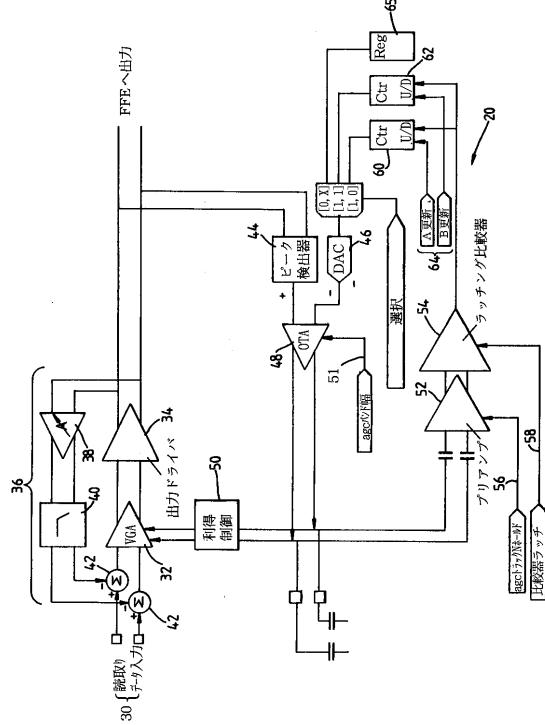

図2において、自動利得制御システムは、より詳細に示され、2つの差動信号ラインが明白になる。

#### 【0027】

動作時、自動利得制御システムは、指定された公称振幅の範囲内で、FFE24に一定の信号振幅を与えるのに役立つ。理想的な動作のために、この振幅は、1つのトラックの長さに沿って、または、同じアジャスのトラック間で変化してはならない。指定された絶対利得エラーの境界内では、信号振幅は、それが実質的に一定である限り、大きさは重要なことではない。AGC制御ループのどのような一時的な動作の間でも、VGA32の振幅の変動は、絶対利得エラーより非常に小さい予めセットされた相対利得エラーの範囲内に制御されなければならない。記録されたトラックは、異なるスペクトル特性の帯域を含む。これらの帯域の最も重要なものは、プリアンブル領域とランダム・データ領域である。AGCブロック20の理想的なオペレーションの流れのために、AGCシステムは、全体としては、周波数スペクトルの変化に対して免疫がなければならない。プリアンブル領域とランダム・データ領域の間の境界のいずれの側でも、相対振幅許容範囲を越えてはならない。

#### 【0028】

信号が、ライン30上で電圧利得増幅器(VGA)32に入力され、出力は、出力ドライバ34を通過して、前方のADC26またはFFE28(図2で示さず)に渡される。増幅器38、ローパスフィルタ40、およびサマー(合算器、summer)42を有するフィードバック・ループ36が、DCオフセット制御のために用意されている。また、出力ドライバ34からの出力は、出力信号のピークを検出する共通の簡単なピーク検出器44に渡される。ピーク検出器44の出力は、デジタル/アナログ変換器(DAC)46からのターゲット値と共に、比較回路として働く演算相互コンダクタンス増幅器(OTA: operational trans-conductance amplifier)48(VGA制御電圧)に供給される。

#### 【0029】

増幅器48の出力(VGA制御電圧)は、VGA32に利得制御信号を供給する利得制御回路50に供給される。ピーク検出回路44、増幅器48、および利得制御回路50によって定義される利得制御ループは、比較的速い応答時間を持つ。

#### 【0030】

また、増幅器48の出力は、プリアンプ52とラッチング比較器54に供給され、ラッチング比較器54は、プリアンブル領域とメイン・データ領域の間のインターフェースでまたはその直

10

20

30

40

50

前で、VGA制御電圧のメジャーVGA<sub>1</sub>を追跡し、それを保持する。VGA制御電圧の第2のメジャーVGA<sub>2</sub>は、いくつかのチャネル・ビットの後に（すなわち、メイン・データ領域の初めて）取られる。VGA1とVGA2の直接の比較によって、電圧利得アンプ32の利得は、プリアンブル領域とランダム・データ領域の間で転移する際に、増加したのか減少したのかを示す。この情報に基づいて、該当するAまたはBトラックのピーク検出器のプリアンブル・ターゲットを保持している該当するカウンタ60または62は、増やされるか減らされる。プリアンブル・ターゲットの調整は、ライン64を通して可能にされ、また不可能にされる。レジスタ65は、全ての条件下でのピーク検出器44についてのランダム・データ・ターゲットに対する定数値を保持する。ターゲット制御ループの応答は、利得制御ループより遅い。

10

#### 【0031】

初期トレーニング期間後、プリアンブル・ターゲットは、プリアンブル領域とメイン・データ領域の間のインターフェースの直前とその後で、VGA制御電圧を等化するよう適応している。これは、次のトラックのために用意されてカウンタ60と62に保持されるそれぞれのターゲット値を持つAおよびBトラックについて別々になされる。

#### 【0032】

したがって、この回路において、プリアンブルとランダム・データに対する単純なピーク検出器44の異なる応答は、適応的に調整される。プリアンブル・ターゲット・カウンタ60と62は、オーバーフロー・アンダーフローをしない飽和カウンタである。したがって、1つが、現在その最大カウントを保持し、更に増加することを要求されるならば、それはその最大カウントを維持する。同様に、それがその最小のカウントを保持しているとき、更に減らすように要求されるならば、それは最小のカウントを維持する。

20

#### 【0033】

ターゲット制御ループのバンド幅や応答時間は、ライン51でOTA增幅器48のバンド幅モードを調節することによって、予め設定した値の間で調節される。AおよびBのトラックのプリアンブル領域は、クロック回復ループとAGCループが、既知の特性のデータ上で速いロックアップを達成するのを可能にするために存在し、したがってそのような領域は短い。

#### 【0034】

AGCシステムのバンド幅は、この速いロックアップを容易にするために、プリアンブル領域の開始で高いように選択される。大まかな振幅調整が達成されたならば、正確な利得振幅調整が達成されるまで、媒体バンド幅モードをライン51で選択することができる。それから、VGA制御電圧による過度の信号の変調を避けるために、ランダム・データの到着に先立ち低帯域幅モードが選択される。

30

#### 【0035】

この配列によって、利得は、下流を処理するに十分正確に制御することができる。

#### 【0036】

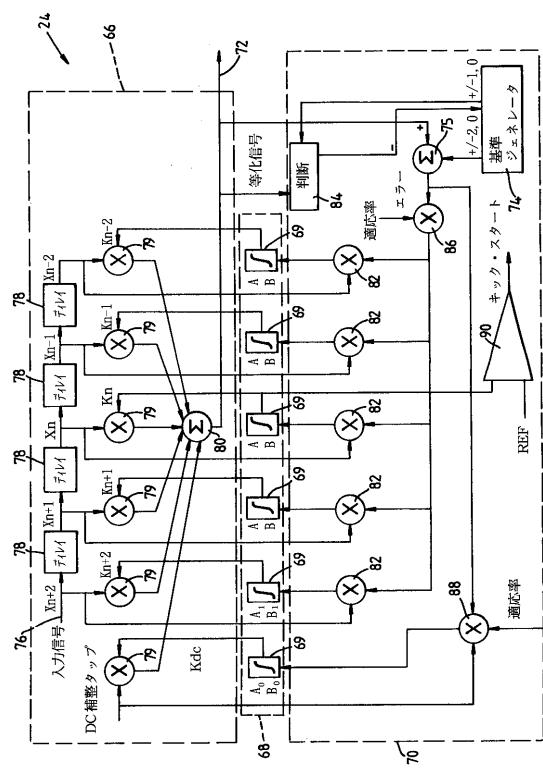

図3を参照すると、AGCブロック20を通過した後、信号は、FFE24に加えられる。FFE24は、有限インパルス応答(FIR)フィルタ66と、係数コンデンサ69のバンク68と、回路70を有する。回路70は、ライン72上の出力と基準ジェネレータ74によって生成された基準値との間のエラーを減らすために係数を適応させる。

40

#### 【0037】

AGCブロック20からの信号は、入力の連続的に遅らされたバージョンを同時に生成する遅延78をもつタップ付き遅延線76上のFIRフィルタ66へ入力される。FFE24内の回路構成の大多数は、スイッチ・コンデンサ技術で実行される。FIRフィルタ66の76での入力は、位相ロックループ(PLL)22によって決定されるクロック・タイムでコンデンサを充電することによって、サンプルされる。それから、この電荷は、遅延線を形成するビット時間に1つのコンデンサから他のコンデンサに渡される。

#### 【0038】

遅延線に沿った各段の出力は、乗算器79で、関連する係数コンデンサ69からのそれぞれの

50

加重係数で乗算され、全ての加重出力は、サマー80によって合計され、ライン72上にフィルタ・デジタル出力を提供する。

#### 【0039】

レジスタ68の係数は、位相ロックループ22によって定義されるようなビット・サンプリング時間で、ライン72上の等化されたアナログ信号のS/N比(S/NR)を最大にするよう繰り返して適応される。一方、ヘッドとテープの周波数応答またはヘッドとテープの接触条件は変化する(製造中のまたは動作中のどちらでも)。DDS-3モードにおいて、PR-1入力信号は、フィルタ18によって、通常、スペクトルで形成され、3つのレベル(+2、0、-2)から成る。この場合、適応ブロック70において、係数は、平均最小二乗(LMS)アルゴリズムで適応させられる。その場合、基準ジェネレータ74によって提供される最も近い3レベル公称信号レベルとFIRフィルタ出力との差であるエラー信号を使用する。エラー信号は、分岐され遅延された入力信号と共に、それぞれの乗算器82に並列に供給され、これは、係数コンデンサ69に各係数を適応させるために使用される。10

#### 【0040】

DDS-3モードにおいて、等化された信号は、それが基準ジェネレータ74からの基準値を使用する+2、0、または-2の信号であると考えられるかどうかを判断するために決定ブロック84でモニタされる。基準ジェネレータ74は、信号が+2、0、または-2のいずれかであるかを決定するために決定ブロック84が使用するプラスマイナス1のスライス・レベル信号を供給する。次いで決定ブロックは、基準ジェネレータ74に、適当な+2、0、-2の公称レベルをエラー・サマー75に供給させる。エラー・サマー75は、フィルタ出力信号をも受取り乗算器82に供給されるエラー信号を得る。適応のレートは、乗算器86、88で、信号( $\mu$ sig)とDC係数( $\mu$ dc)についての予め設定した値(一般的に6)の間で変化する。20

#### 【0041】

FFE24は、ランダムなデータ領域に対して最適の係数セットからすぐにはずれて適応するので、AおよびBデータ・トラックのブリアンブルまたはマージン領域に適応することを許されてはならない。メイン・データ領域の開始と終了は、テープ上のデータの構造と読み込まれるフォーマットの知識に基づき、とりわけブレアンブル検出器23(図1)に依存して、タイミングとインテリジェントな決定の組合せを使用するデータ回復状態マシーンによって、通常予測される。ブリアンブル検出回路23は、従来のタイプのものでよく、典型的にはブリアンブル領域の純粋な正弦波のトーンにマッチした整合フィルタの形であつてよい。それは、信号が特徴のある正弦波のトーンを含む時、高い出力を供給する。ブリアンブル検出回路23の出力は、状態マシーン21に供給され、状態マシーンは、AおよびBブリアンブルとAGC20におけるメイン・データ・ターゲットについてターゲット切り替えを制御し、フィードフォワード・イコライザ24におけるAおよびBトラック係数の選択をも制御する。30

#### 【0042】

AおよびBトラックのスペクトル特性は相違し、コンデンサ69は、AおよびBトラックに対する別々の係数を記憶し、適当なセットの係数が各トラックの始めてFFEコンデンサ69に書き込まれる。40

#### 【0043】

この装置は、係数コンデンサ69に対応する一組の係数レジスタ(図示せず)を含む。コンデンサ69で保持された値は、A/Dコンバータによって処理され、係数レジスタに記憶される。各トラックの始めて係数を回復するために、それらは、デジタル時間ログ・コンバータによって処理され、コンデンサに供給される。したがって、典型的な順序は、次のようになる。

1. A係数レジスタの内容がFFE係数コンデンサ69に書き込まれる。

2. FFEは、ブロック70によって実行される適応処理に従って、Aトラック上にこれらの係数を適応させる。

3. 適応されたFFE係数コンデンサ69の値がデジタル化され、A係数レジスタに記憶

され、B係数レジスタの内容がFFE係数コンデンサ69に書き込まれる。

4. FFEは、ブロック70によって実行された適応処理に従って、Bトラック上にこれらの係数を適応する。

5. Bトラックの適応されたFFE係数コンデンサ69の値がデジタル化されて、B係数レジスタに記憶される。

#### 【0044】

しかしながら、いろいろな他のルーチンが続いてもよい。例えば、そのアジマスの前のトラックの終わりで適応された係数値にかかわりなく、各トラックが、トラックの始めて係数コンデンサへロードされる係数のそれ自身の標準セットを有することが可能である。または、係数コンデンサは、そのアジマスの前のトラックを介する途中の一部で受け取られ適応された値をロードされてもよい。係数がとられる位置は、最高の適応を提供するための機械条件に従って最適化される。例えば、トラックが曲っている場合、トラックに沿っておよそ途中の半分から係数をとることがベストとなる。あらゆる機械の設計で、最適な位置は経験的に決定され、そして、製品化される機械は、この地点で係数をとるようにプログラムされる。AおよびB係数を異なるポイントでとることができること。

10

#### 【0045】

したがって、前のAトラックについての読み取り動作の最小のエラー部分からの適応されたフィルタ係数は、次のAトラックの係数の初期セットとして使用することができ、そして、同様の処理がBトラック係数に適用される。トラック終わりの非線形に迷い込むのを避けるために、読み取り動作の最小エラー部分の開始の後、あらかじめ決められた時間に係数値をとるために「スナップショット・タイマ」方式を使用することができます。

20

#### 【0046】

一実施例において、所与のAまたはBトラックの係数の連続したセットを多くのトラックにわたって平均して、次のAまたはBトラックのための係数の初期セットとして、使用することができる。これは、1トラックでは素早く適応させることができ、多重トラックでは遅いという利点がある。これは、デジタル方式で最も容易に実施することができる。

#### 【0047】

特別な例として、AおよびBトラック係数セットのそれぞれにおいて、13の信号の係数と1つのDC係数がある。

#### 【0048】

30

もし、FFE24が、読み取り信号でドロップ・アウトに対抗する間、適応しているならば、FFE係数は、回復することができない状態に誤って適応することがある。これに対抗するために、自動再始動装置が組み込まれる。中心係数がプログラム可能な閾値（例えば50%）の下に落ちると、その係数は全て、デフォルト・セットの値に強制される。例えば、中心信号係数に1単位の値がロードされるときの単位ステップのインパルス応答および残りの信号係数は、ゼロに強制される。この開始位置から、FFE24は適応し続けることを許される。それは、再び誤って適応するならば処理が自動的に繰り返されるか、または、ドロップ・アウトが回復可能な信号を含むならば、互いに正しい目標値に近づく。

#### 【0049】

したがって、図に示した実施例において、中心係数は、それを基準ジェネレータ91からのプリセット基準値と比較する比較回路90に供給され、そして、もし、実際問題として、中心係数が、不正確な状態で安定した係数になるような値以下に落ちた場合、係数のデフォルト・セットを強制する「キック・スタート」ルーチンを実行する。

40

#### 【0050】

トラック交差モードにおいて、テープの上のトラックが読み取りヘッドの走査パスと整合しないとき、ヘッド出力信号は、1走査につき何回も良／不良のSNRの間を循環し、この状況において、図3の方式は、回復されるデータ量を増やすことができる。

#### 【0051】

FFE係数の多数の安定した、適応された状態が可能であるが、これらうちの小さなセットだけがこの方式に有用である点に留意する必要がある。上述された技術は、中心係数だ

50

けをテストしており、全ての可能な望ましくない状態を検出することができるというわけではない。しかしながら、この技術は、この中心係数に加えて、またはこれに代えて他の係数をモニタするように拡張することができ、また、係数の異なるデフォルト・セットを強制することができる。また、それを一つの限度でなく範囲として、モニタすることができる。

#### 【0052】

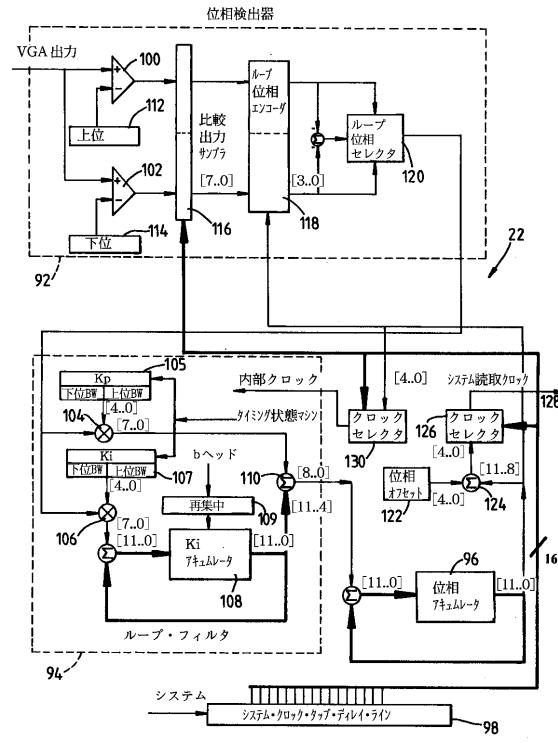

ここで図4を参照すると、位相同期ループ22は、いろいろな異なる条件で、読み取り波形からビット・クロックを回復させることを要求される。本質的に、位相ロックループ22は、周波数と位相同期をトラックの最初で獲得しなければならず、許容できる位相エラーで、ヘッド・テープ速度ジッタに起因するビット周波数変動に追従しなければならない。

10

#### 【0053】

幅広いアウトラインにおいて、位相同期ループ22は、位相検出器92、ループ・フィルタ94、および位相アキュムレータ96を有する。位相アキュムレータ96の出力は、システム・クロック・タップ付き遅延線98から得られる一連のクロック信号から適当なクロック信号を選択するために使用される。

#### 【0054】

入力信号が、AGC20で自動利得制御にかけられるので、公称レベルが、2、0、-2の単位となる。2つの入力比較回路100、102は、入力信号が+/-1単位(近似)閾値を横切る時間を捜す。そして、これらの閾値交差の時間は、位相エラーを決定するために現在のクロック・タイム(システム読み取りクロック)と比較される。位相エラーは、デジタル(すなわち、位相エラーの符号と大きさに従い、-4、-3、-2、-1、1、2、3、4)でエンコードされて、ループ・フィルタ94に渡される。

20

#### 【0055】

ループ・フィルタ94で、(デジタルの)位相エラーは、2つの乗算器104、106とアキュムレータを使用してフィルタされる。上位フィルタリング・パスで、位相エラーは、定数( $K_p$ )を掛けられる。下位フィルタリング・パスで、位相エラーは、定数 $K_i$ を掛けられ、その結果は、 $K_i$ アキュムレータ108によって累算される。累算された( $K_i$ )結果と直接の( $K_p$ )結果は、一緒にサマー110で加えられて、位相アキュムレータ96に渡される。

#### 【0056】

30

位相アキュムレータ96は、ループ・フィルタ94の出力を積分する。位相アキュムレータ出力の上位4ビットが、「ポインタ」の働きをする。このポインタは、遅延線98で得られる外部のシステム・クロックの16の遅延バージョンのうちのどれが、システム読み取りクロック(すなわち、入力信号に同期されたクロック)として使用されるかを示す。

#### 【0057】

したがって、入力信号がシステム読み取りクロックと位相外れになるにつれて、位相エラーがループ・フィルタ94の出力で大きな値になり、それによって、位相アキュムレータ96がインクリメントし、結局その出力の上位4ビットを変更する。これによって、入力信号の位相により近いシステム・クロックの遅延バージョンが選択される。

#### 【0058】

40

本方式のより細部を参照すると、最終製品における誤り率を最適化するためにループ・フィルタ・パラメータは、プログラム可能であり、第2順位のループが仮定される。更に、ループのバンド幅は、2つの前もってプログラムされた値の間で、リアルタイムでスイッチ可能である。これは、ブリアンブル・ゾーンを最も効率的に利用するためであり、データ領域で低い位相ジッタを維持する。位相同期ループ22は、トラックの通常のリプレイの間に発生する信号ドロップ・アウトの後、位相同期を回復させることができなければならない。

#### 【0059】

回復させられた読み取りクロックは、FFE24、ADC26およびヴィテルビ・デコーダ28を駆動するので、強力でなければならない。位相同期ループ22は、DDS-1/2またはD

50

D-3 のフォーマットで稼働ができることが好ましい。DDS-1 または 2 のフォーマットは、ビット・サンプリング時間がアイ・センタにあるとき 2 レベルの信号になる。ここで、この方法は単純で振幅変動に比較的無感応であるので、位相検出器 92 は、典型的にゼロ交差のテストをする。

( 0 0 6 0 )

DDS-3 フォーマットで、フォーマットの読み取りは、3 レベルの PR-1 信号になる。この場合、位相検出器 92 は、入力信号の大きな部分を不合格とすることなく、単純なゼロ交差のテストをすることができない。閾値交差方式が必要とされる（およそ +1, -1）。

〔 0 0 6 1 〕

したがって、PLL22は閾値交差時間位相検出器92を含み、その出力は、離散的なステップに量子化される。DDS-1または2のモードで、位相検出器は、ゼロ交差に応答するが、DDS-3モードでは、2分の1公称信号レベル交差に応答する。

【 0 0 6 2 】

図4は、位相検出器92を介す2つの（概念上の）パスを示す。ここで、入力信号（AGC20から）は、100、102で、半分の公称信号レベル閾値レベル（正および負）のそれぞれと比較される。入力信号の中の閾値交差のタイミングは、比較回路出力サンプラ116で、（16のタップ付き遅延線98から誘導された）出力クロックの（1/8の期間でシフトされた）8つの均一に区切られた位相と比較される。そして、ループ位相エンコーダ118で、現在の出力位相選択と比較される。量子化された位相は、入力交差が落す8つの出力クロック位相の間から、ループ位相セレクタ120によって直接判断される。

( 0 0 6 3 )

D D S - 1 または 2 のモードで、入力信号は、单一の公称ゼロ・レベル基準値と比較され、図 4 の上位（概念上の）信号バスのみが使用される。D D S - 3 モードで、半分の公称信号閾値は、位相検出器閾値基準レジスタ 112、114 から誘導される。これらのレジスタは、D A C 基準値を A G C ランダム・データ・ターゲット D A C 基準値にプログラムする。この方式は、A G C ターゲットおよび P L L 位相検出器が独立して最適化されることを可能にする。

[ 0 0 6 4 ]

ループ位相セレクタ120からの量子化された位相出力は、K<sub>p</sub>（比例項）とK<sub>i</sub>（積分項）項を有するデジタル・ループ・フィルタ94に供給される。図において、位相検出器92の出力は、（状態（-4、-3、-2、-1、0、1、2、3、4）をエンコードする）4ビット・バスとして、また、乗算器104、106の出力は、8ビット・バスとして表示される。

[ 0 0 6 5 ]

$K_p$  と  $K_i$  乗数は、一般的に以下の範囲を有することができる。

[ 0 0 6 6 ]

【数1】

K<sub>p</sub>の範囲 = 0 ~ 31

Ki の範囲 = 0 31

垂管器出力 = - 124 124

【0067】

Ki乗算器106は、この例では以下の範囲を有するKiキュムレータ108に、データを渡す。

[ 0 0 6 8 ]

【数2】

Ki アキコハレタ：ビット = 12

Ki アキュムレータ範囲 = - 2048 2047

【00691】

Ki アキコトヒニタ108は、入力Ki乗算器出力を積分するが、アキコトヒニタからの量

上位 8 ビットが、 $K_p$  乗算器 104 からの 8 ビットに加えられ、位相アキュムレータ 96 の（最下位）エンドに供給される。

#### 【0070】

したがって、ループ・フィルタ 94 は、ビット周期毎に、位相アキュムレータ 96 へ、 -252 . . . . . 252 を供給することができる。 $K_p$  および  $K_i$  値の 2 つのプログラム可能な対がレジスタ 105、107 で得られ、ループに速いまたは遅い時間定数を与える。この定数は、システム要求に従って状態マシンによって選択される。

#### 【0071】

$K_i$  アキュムレータ 108 は、位相同期を失うかまたはその危険にあることが示されるとき再プログラム可能なように構成される。例えば、プリアンブル領域において PLL 周波数 10 が初期化される場合がある。いわゆる「スタント・モード (stunt modes)」の間、速い前進テープ運動のために、A トランクの中心周波数が低くされ、B トランクの中心周波数が高くされる（逆テープ運動ではその逆になる）とき、周波数オフセットが発生する。更に、 $K_i$  アキュムレータ 108 が正または負にオーバーフローし、中心周波数が許容範囲外にあることを示すことがある。さらにまた、上述の FFE 系数「キック・スタート」ルーチンがトリガーされるならば、 $K_i$  アキュムレータ 108 は再び中心付けされてもよい。この状態は、テープ・ドロップ・アウトまたは信号に対してその他の障害が存在し、PLL がその位相同期を失いそうであることを示唆することを示す。

#### 【0072】

これらの状態で、 $K_i$  アキュムレータ 108 の最上位ビットは、可変位相発振器周波数オフセット・レジスタ 109 の内容をロードされ、これにより周波数がデフォルト値に中心づけられる。例えば、周波数は、PLL 22 が現在のトランクを読み始めた周波数に再び中心づけられてもよい。

#### 【0073】

デジタル位相アキュムレータ 96 は、ループ・フィルタ 94 の出力を合計し、4 つの最上位ビットを使用して 16 のタップ付き遅延線 98 から出力クロック位相を選択する。この遅延線 98 は、それ自身、システム・ビット周波数クロックに位相ロックされている。また、この遅延線 98 からの 16 のシステム・クロック位相は、位相検出器 92 の比較回路出力サンプラー 116 によって、閾値交差のタイミングを実行するために使用される。ループ・フィルタ・アキュムレータ 108 から位相アキュムレータ 96 まで渡されたビットの数は、支援できる最大の周波数エラーを決定する。位相アキュムレータ 96 は、ループ・フィルタ 94 の出力 ( $K_p$  と  $K_i$  項の合計) を積分する。最上位の 4 ビットは、現在のクロック位相として使用されたタップ付き遅延線からシステム・クロックの位相を選択するために使用される。

#### 【0074】

位相アキュムレータ出力 96 は、この例では 12 ビットの数で表示され、単純な符号なしアップ・ダウン・カウンタとみなされる。したがって、正のループ・フィルタ出力が加えられると、アキュムレータは、それが 4095 に達するまでカウントアップし次いでゼロにラップアラウンド（折り返す）する。同様に、負のループ・フィルタ出力が加えられると、ゼロに達するまでカウントダウンし、4095 にラップアラウンドする。これらの条件の下で、4 つの最上位ビットは、単純に 0 から 15 までインクリメントし、再び 0 にラップアラウンドする。こうしてシステム・クロックの次第に遅れる位相が出力クロックとして選択される。

#### 【0075】

タップ付き遅延線 98 は、16 の均一に区切られたタップを有し、システム・クロックを供給される。概念的には、（システム・クロック周波数がチャネルのいろいろなオペレーティング・モードについて異なるとき）16 番目のタップの出力が次のシステム・クロック期間と一致するように、遅延が調節される。

#### 【0076】

レジスタ 122 からの静的位相オフセット値がサマー 124 で組み込まれ、このサマー 124 は、クロック・セレクタ 126 に出力を提供し、このクロック・セレクタ 126 は、タップ付き遅延

10

20

30

40

50

線98から適当なクロック信号を選ぶ。ループがロックする位相と、F F E 24およびA D C 26によって使用される出力128に加えられるクロック位相との間の静的位相オフセットについての必要性に対して2つの要因がある。第一に、P L L 22が遷移が存在するビット端にロックするのに対して、F F E 24は、ビットの中心でサンプルをとる。第2に、位相測定ループと、クロックがF F Eで使用されるポイントとの間に未知の回路パス遅延がある。従って、位相オフセット・レジスタは、4ビットの（符号なし）数でプログラムされ、この数は、位相アキュムレータの4つの最上位ビットに加えられてF F E 24、A D C 26およびシステムの残りの部分に渡されるクロック位相を選択するが、P L L 内部クロックのクロック位相を選択するためには使われない。P L L 内部クロックのクロック位相は、クロック・セレクタ130によって選択される。

10

#### 【0077】

以上、図1乃至4において、サンプル・アナログ方式に関して記述したが、本発明は、デジタル形式で実施することもできる。

#### 【0078】

また、本発明は、同日に出願され、現在出願中の、出願番号96306941.4、96306938.0、および96306939.8の記載内容が本明細書中に参照され含まれる。

#### 【0079】

本発明は、例として以下の実施態様を含む。

(1) ビット・レートに変動を有する信号からビット・クロックを回復させる位相同期ループ手段を有する、信号を処理する装置であって、前記位相同期ループの周波数をモニタする手段と、前記周波数が予めセットされた範囲外にある場合、前記周波数を予めセットされた値にリセットする手段と、を備える前記装置。

20

(2) 前記装置は、前記信号を処理し、係数の適応セットを供給するサンプルされた時間フィルタと、少なくとも1つの前記係数をモニタリングする手段と、を有し、前記リセット手段は、少なくとも1つの前記係数が予め設定した閾値を越えた場合、前記位相同期ループ装置の周波数をリセットすることを特徴とする(1)記載の装置。

(3) 前記装置に直接または間接に供給される信号の利得を制御および／または獲得する自動利得制御手段を有し、前記リセット手段は、前記利得制御信号が予め設定した閾値を越えた場合、前記位相同期ループの周波数をリセットすることを特徴とする(1)または(2)記載の装置。

30

(4) データの複数のストリーム又はトラックを有する信号からビット・クロックを回復し、前記リセット手段は、現在のストリーム又はトラックの開始時に、前記位相同期ループ手段の周波数をリセットすることを特徴とする(1)ないし(3)記載の装置。

#### 【0080】

(5) 位相エラー信号を蓄積するアキュムレート手段を有するループ・フィルタ手段を有し、前記リセット手段は、前記位相同期ループがその同期を失い、または悪い条件が検出されたならば、前記アキュムレート手段の内容を予め設定した値に置き換えることを特徴とする(1)ないし(4)記載の装置。

(6) ビット・クロックを回復するために、ビット・レートに変動を有する信号を処理する方法であって、ビット・クロックを得るために位相同期ループ回路に前記信号を供給し、前記位相同期ループの周波数をモニタリングし、それが予め設定した範囲を超えるか、悪い条件が検出された場合、前記位相同期ループの周波数を予め設定した値にリセットする、前記方法。

40

#### 【0081】

#### 【発明の効果】

以上述べた通り、本発明の信号処理装置によれば、テープ・ドロップアウトのような一定の状況で、P L L がその同期を失うことがありえる条件、またはこの条件になる適当な状況をモニタし、条件が検出された場合、周波数をデフォルト値にリセットする。また、この状況は、記録された媒体から導かれるもの以外の通信チャネルのタイプに広く適用できる。

50

## 【図面の簡単な説明】

【図1】 本発明の装置を含むデータ読み取り装置のメイン構成要素の概要ブロック図。

【図2】 図1で示した装置の一部分を形成する自動利得制御システムのブロック図。

【図3】 図1の装置で使用されるフィードフォーワード・イコライザ(FFE)のブロック図。

【図4】 クロック信号を入力データから抜き出す位相同期ループのブロック図。

## 【符号の説明】

|              |                 |    |

|--------------|-----------------|----|

| 10 テープ       | 12 読取りヘッド       |    |

| 14 回転変圧器     | 16 増幅器          |    |

| 20 AGC回路     | 21 状態マシン        | 10 |

| 22 位相同期ループ   | 23 プリアンプル検出器    |    |

| 24 FFE       | 26 アナログ・デジタル交換器 |    |

| 28 ヴィテルビ検出回路 | 27 アナログ・デジタル変換器 |    |

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(56)参考文献 特開平04-013280(JP,A)

実開平02-008234(JP,U)

(58)調査した分野(Int.Cl., DB名)

G11B 20/14

H03L 7/06

H04L 7/033