(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년02월16일

(11) 등록번호 10-1707785

(24) 등록일자 2017년02월10일

(51) 국제특허분류(Int. Cl.)

*H01L 29/78* (2006.01) *H01L 21/8238* (2006.01)*H01L 27/088* (2006.01) *H01L 27/092* (2006.01)*H01L 29/06* (2006.01) *H01L 29/66* (2006.01)

(52) CPC특허분류

*H01L 29/7809* (2013.01)*H01L 21/823814* (2013.01)

(21) 출원번호 10-2016-7008058(분할)

(22) 출원일자(국제) 2011년12월19일

심사청구일자 2016년04월25일

(85) 번역문제출일자 2016년03월25일

(65) 공개번호 10-2016-0040727

(43) 공개일자 2016년04월14일

(62) 원출원 특허 10-2014-7017386

원출원일자(국제) 2011년12월19일

심사청구일자 2014년06월24일

(86) 국제출원번호 PCT/US2011/065931

(87) 국제공개번호 WO 2013/095349

국제공개일자 2013년06월27일

(56) 선행기술조사문헌

KR1020100079765 A\*

US07943469 B2\*

US20070057347 A1\*

US20090283824 A1

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

인텔 코포레이션

미합중국 캘리포니아 95054 산타클라라 미션 칼리지 블러바드 2200

(72) 발명자

자일스, 마틴, 디.

미국 97229 오리건주 포틀랜드 노스웨스트 다이아몬드 드라이브 12749

카펠라니, 안날리사

미국 97229 오리건주 포틀랜드 노스웨스트 레이크 뷰 드라이브 13668

(뒷면에 계속)

(74) 대리인

양영준, 백만기

전체 청구항 수 : 총 19 항

심사관 : 최정민

(54) 발명의 명칭 금속성 소스 및 드레인 영역들을 갖는 반도체 장치 및 구조

**(57) 요약**

금속성 소스 및 드레인 영역들을 갖는 반도체 장치가 기술된다. 예를 들어, 반도체 장치는 기판의 반전도 채널 영역 위에 배치된 게이트 전극 스택을 포함한다. 금속성 소스 및 드레인 영역들은 반전도 채널 영역의 양측에, 기판 위에 배치된다. 금속성 소스 및 드레인 영역들 각각은 프로필을 갖는다. 제1 반전도 외부 확산 영역은 반

(뒷면에 계속)

**대 표 도** - 도1b

전도 채널 영역과 금속성 소스 영역 사이에 그리고 금속성 소스 영역의 프로필에 등각을 이루도록, 기판 내에 배치된다. 제2 반전도 외부 확산 영역은 반전도 채널 영역과 금속성 드레인 영역 사이에 그리고 금속성 드레인 영역의 프로필에 등각을 이루도록, 기판 내에 배치된다.

(52) CPC특허분류

*H01L 27/088* (2013.01)

*H01L 27/092* (2013.01)

*H01L 29/0673* (2013.01)

*H01L 29/66636* (2013.01)

*H01L 29/66795* (2013.01)

*H01L 29/7839* (2013.01)

*H01L 29/7845* (2013.01)

*H01L 29/785* (2013.01)

(72) 발명자

**카베히에, 사나즈**

미국 97229 오리건주 포틀랜드 에이피티 308 노스

웨스트 갤리스 레인 21167

**리오스, 라파엘**

미국 97229 오리건주 포틀랜드 노스웨스트 브론슨

크레스트 루프 3688

**웨버, 코리, 이.**

미국 97124 오리건주 힐스버러 노스이스트 61번 플

레이스 524

**버드레비치, 아론 에이.**

미국 97229 오리건주 포틀랜드 노스웨스트 메릴허

스트 드라이브 17804

## 명세서

### 청구범위

#### 청구항 1

반도체 장치로서,

기판의 반전도 채널 영역(semiconducting channel region) 위에 배치된 게이트 전극 스택;

상기 게이트 전극 스택에 인접한 한 쌍의 절연 측벽 스페이서들;

상기 반전도 채널 영역의 양측에, 상기 기판 위에 배치된 금속성 소스 및 드레인 영역들 - 상기 금속성 소스 및 드레인 영역들 각각은 프로필(profile)을 가지고, 상기 금속성 소스 및 드레인 영역들은 상기 한 쌍의 절연 측벽 스페이서들 중 대응하는 절연 측벽 스페이서의 수직 아래(vertically beneath)에 배치되지만 상기 게이트 전극 스택 수직 아래에는 배치되지 않음 - ;

상기 반전도 채널 영역과 상기 금속성 소스 영역 사이에, 그리고 상기 금속성 소스 영역의 프로필에 등각을 이루도록(conformal with the profile), 상기 기판 내에 배치된 제1 반전도 외부 확산 영역(semiconducting out-diffusion region) - 상기 제1 반전도 외부 확산 영역의 일부는 상기 한 쌍의 절연 측벽 스페이서들 중 하나의 수직 아래에 배치되고 상기 게이트 전극 스택 수직 아래에 배치됨 -; 및

상기 반전도 채널 영역과 상기 금속성 드레인 영역 사이에, 그리고 상기 금속성 드레인 영역의 프로필에 등각을 이루도록, 상기 기판 내에 배치된 제2 반전도 외부 확산 영역 - 상기 제2 반전도 외부 확산 영역의 일부는 상기 한 쌍의 절연 측벽 스페이서들 중 다른 하나의 수직 아래에 배치되고 상기 게이트 전극 스택 수직 아래에 배치됨 -

을 포함하고,

상기 금속성 소스 및 드레인 영역들은 작은 면이 있는 프로필들(faceted profiles)을 갖고, 상기 제1 및 제2 반전도 외부 확산 영역들은 상기 작은 면이 있는 프로필들에 등각을 이루는, 반도체 장치.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

제1항에 있어서, 상기 금속성 소스 및 드레인 영역들은 각각 상기 기판 위에 배치된 유전체 층 안에 배치된 대응하는 연속 접촉 구조(corresponding continuous contact structure) 안에 포함되는, 반도체 장치.

#### 청구항 5

제1항에 있어서, 상기 금속성 소스 및 드레인 영역들은 금속 질화물, 금속 카바이드, 금속 실리사이드, 금속 알루미나이드, 하프늄, 지르코늄, 티타늄, 탄탈륨, 알루미늄, 루테늄, 팔라듐, 플래티넘, 코발트, 니켈 또는 전도 금속 산화물을 포함하는 그룹에서 선택된 전도 재료를 포함하는, 반도체 장치.

#### 청구항 6

제1항에 있어서, 상기 금속성 소스 및 드레인 영역들은 상기 반전도 채널 영역에 단축으로 응력을 주는(uniaxially stress), 반도체 장치.

#### 청구항 7

제1항에 있어서, 상기 반도체 장치는 N-형 장치이고, 상기 반전도 채널 영역은 실리콘을 포함하고, 상기 제1 및

제2 반전도 외부 확산 영역들은 인 및 비소를 포함하는 그룹에서 선택된 도편트 불순물 원자를 포함하는, 반도체 장치.

#### 청구항 8

제7항에 있어서, 상기 금속성 소스 및 드레인 영역들은 금속 카바이드 또는 금속 알루미나이드를 포함하는 그룹에서 선택된 재료를 포함하는, 반도체 장치.

#### 청구항 9

제1항에 있어서, 상기 반도체 장치는 P-형 장치이고, 상기 반전도 채널 영역은 실리콘을 포함하고, 상기 제1 및 제2 반전도 외부 확산 영역들은 붕소 도편트 불순물 원자를 포함하는, 반도체 장치.

#### 청구항 10

제9항에 있어서, 상기 금속성 소스 및 드레인 영역들은 금속 질화물, 금속 카바이드, 또는 금속 실리사이드를 포함하는 그룹에서 선택된 재료를 포함하는, 반도체 장치.

#### 청구항 11

제1항에 있어서, 상기 기판은 벌크 기판이며, 상기 반전도 채널 영역은 상기 벌크 기판과 연속인, 반도체 장치.

#### 청구항 12

제1항에 있어서, 상기 기판은 절연 층을 포함하고, 상기 반전도 채널 영역은 분리된 채널 영역인, 반도체 장치.

#### 청구항 13

제1항에 있어서, 상기 반전도 채널 영역은 3차원 바디(body)를 포함하고, 상기 게이트 전극 스택은 상기 3차원 바디의 적어도 상부 표면과 한 쌍의 측벽을 에워싸는, 반도체 장치.

#### 청구항 14

반도체 구조로서,

N-형 반도체 장치; 및

P-형 반도체 장치

를 포함하고,

상기 N-형 반도체 장치는,

기판의 제1 반전도 채널 영역 위에 배치된 N-형 게이트 전극 스택;

상기 N-형 게이트 전극 스택에 인접한 제1 쌍의 절연 측벽 스페이서들;

상기 제1 반전도 채널 영역의 양측에, 상기 기판 위에 배치된 제1 금속성 소스 및 드레인 영역들 - 상기 제1 금속성 소스 및 드레인 영역들 각각은 제1 프로필을 가지고, 상기 제1 금속성 소스 및 드레인 영역들은 상기 제1 쌍의 절연 측벽 스페이서들 중 대응하는 절연 측벽 스페이서의 수직 아래에 배치되지만 상기 N-형 게이트 전극 스택 수직 아래에는 배치되지 않음 - ; 및

상기 제1 반전도 채널 영역과 상기 제1 금속성 소스 및 드레인 영역들 중 대응하는 것 사이에, 그리고 대응하는 제1 프로필에 등각을 이루도록, 상기 기판 내에 배치된 제1 쌍의 반전도 외부 확산 영역들 - 상기 제1 쌍의 반전도 외부 확산 영역들의 일부는 상기 제1 쌍의 절연 측벽 스페이서들 수직 아래에 배치되고 상기 N-형 게이트 전극 스택 수직 아래에 배치됨 -;

을 포함하고,

상기 P-형 반도체 장치는,

기판의 제2 반전도 채널 영역 위에 배치된 P-형 게이트 전극 스택;

상기 P-형 게이트 전극 스택에 인접한 제2 쌍의 절연 측벽 스페이서들;

상기 제2 반전도 채널 영역의 양측에, 상기 기판 위에 배치된 제2 금속성 소스 및 드레인 영역들 - 상기 제2 금속성 소스 및 드레인 영역들 각각은 제2 프로필을 가지고, 상기 제2 금속성 소스 및 드레인 영역들은 상기 제2 쌍의 절연 측벽 스페이서들 중 대응하는 절연 측벽 스페이서의 수직 아래에 배치되지만 상기 P-형 게이트 전극 스택 수직 아래에는 배치되지 않음 - ; 및

상기 제2 반전도 채널 영역과 상기 제2 금속성 소스 및 드레인 영역들 중 대응하는 것 사이에, 그리고 대응하는 제2 프로필에 등각을 이루도록, 상기 기판 내에 배치된 제2 쌍의 반전도 외부 확산 영역들 - 상기 제2 쌍의 반전도 외부 확산 영역들의 일부는 상기 제2 쌍의 절연 측벽 스페이서들 수직 아래에 배치되고 상기 P-형 게이트 전극 스택 수직 아래에 배치됨 -;

을 포함하고,

상기 제1 또는 제2 금속성 소스 및 드레인 영역의 쌍들 중 하나는 작은 면이 있는 프로필들을 갖고, 대응하는 제1 쌍 또는 제2 쌍의 반전도 외부 확산 영역들은 상기 작은 면이 있는 프로필들에 등각을 이루는, 반도체 구조.

#### **청구항 15**

삭제

#### **청구항 16**

삭제

#### **청구항 17**

제14항에 있어서, 상기 제1 또는 제2 금속성 소스 및 드레인 영역의 쌍들은 상기 기판 위에 배치된 유전체 층 안에 배치된 연속 접촉 구조들의 쌍 안에 포함되는, 반도체 구조.

#### **청구항 18**

제14항에 있어서, 상기 제1 금속성 소스 및 드레인 영역들은 상기 제1 반전도 채널 영역에 단축으로 응력을 주고, 상기 제2 금속성 소스 및 드레인 영역들은 상기 제2 반전도 채널 영역에 단축으로 응력을 주는, 반도체 구조.

#### **청구항 19**

제14항에 있어서, 상기 제1 반전도 채널 영역은 실리콘을 포함하고, 상기 제1 쌍의 반전도 외부 확산 영역들은 인 및 비소를 포함하는 그룹에서 선택된 도편트 불순물 원자를 포함하고, 상기 제2 반전도 채널 영역은 실리콘을 포함하고, 상기 제2 쌍의 반전도 외부 확산 영역들은 붕소 도편트 불순물 원자를 포함하는, 반도체 구조.

#### **청구항 20**

제19항에 있어서, 상기 제1 금속성 소스 및 드레인 영역들은 금속 카바이드 또는 금속 알루미나이드를 포함하는 그룹에서 선택된 재료를 포함하고, 상기 제2 금속성 소스 및 드레인 영역들은 금속 질화물, 금속 카바이드, 또는 금속 실리사이드를 포함하는 그룹에서 선택된 재료를 포함하는, 반도체 구조.

#### **청구항 21**

제14항에 있어서, 상기 기판은 벌크 기판이며, 상기 제1 및 제2 반전도 채널 영역들은 상기 벌크 기판과 연속인, 반도체 구조.

#### **청구항 22**

제14항에 있어서, 상기 기판은 절연 층을 포함하고, 상기 제1 및 제2 반전도 채널 영역들은 분리된 채널 영역인, 반도체 구조.

#### **청구항 23**

제14항에 있어서, 상기 제1 및 제2 반전도 채널 영역들 각각은 3차원 바디를 포함하고, 대응하는 게이트 전극

스택은 상기 3차원 바디의 적어도 상부 표면과 한 쪽의 측벽을 에워싸는, 반도체 구조.

## 발명의 설명

### 기술 분야

[0001] 본 발명의 실시예들은 반도체 장치 분야에 관한 것이고, 특히 금속성 소스 및 드레인 영역들을 갖는 반도체 장치 분야에 관한 것이다.

### 배경 기술

[0002] 지난 수십 년간, 집적 회로 내의 피처들(features)의 스케일링(scaling)은 계속 성장하는 반도체 산업의 배후에 있는 원동력이었다. 피처들을 좀 더 소형화하기 위한 스케일링으로 인해 반도체 칩들의 제한된 크기(real estate) 상의 기능 유닛들의 밀도가 증가하였다. 예를 들어, 트랜지스터 사이즈를 축소하면 증가한 수의 메모리 장치들이 칩에 통합될 수 있고, 이는 용량이 증대된 제품 제조로 이어진다. 그러나 보다 큰 용량에 대한 추구가 문제가 없는 것은 아니다. 각 장치의 성능을 최적화하기 위한 필요성이 점차 중요해지고 있다.

[0003] 집적 회로 장치의 제조에 있어서, 트라이-게이트(tri-gate) 트랜지스터와 같은 멀티-게이트 트랜지스터들은 장치 치수가 계속 스케일 다운(scale down)됨에 따라서 더욱 중요해지고 있다. 종래의 공정에서, 트라이-게이트 트랜지스터들은 일반적으로 벌크 실리콘 기판 또는 실리콘-온-인슐레이터(silicon-on-insulator) 기판에 제조된다. 일부 경우들에서, 벌크 실리콘 기판들은 그들의 낮은 비용 때문에 그리고 이들이 덜 복잡한 트라이-게이트 제조 공정을 가능하게 하기 때문에 선호되고 있다. 다른 경우들에서, 실리콘-온-인슐레이터 기판들은 저감 누설을 제공할 수 있기 때문에 선호되고 있다.

[0004] 벌크 실리콘 기판상에, 트라이-게이트 트랜지스터들을 제조하는 공정은 종종 금속 게이트 전극의 하부를 트랜지스터 바디(즉, "핀")의 하부에 있는 소스 및 드레인 텁(tip)들과 정렬(align)할 때 문제점들에 봉착한다. 트라이-게이트 트랜지스터가 벌크 기판에 형성될 때, 최적의 게이트 제어를 위해 그리고 쇼트-채널 효과(short-channel effects)를 줄이기 위해서 적절한 정렬이 필요하다. 예를 들어, 소스 및 드레인 연장 텁들이 금속 게이트 전극보다 깊으면, 펀치-스루(punch-through)가 발생할 수 있다. 대안적으로, 금속 게이트 전극이 소스 및 드레인 연장 텁들보다 깊으면, 원치 않는 게이트 기생 용량(gate capacitance parasitics)이 생길 수 있다.

[0005] 접촉 금속(contact metal) 개선, 도편트 활동 증가 및 반도체와 접촉 금속 간의 낮은 장벽을 포함해서 트랜지스터들의 외부 저항( $R_{ext}$ )을 개선하기 위해 많은 상이한 기법이 시도되었다. 그러나,  $R_{ext}$  저감 영역에는 아직도 중요한 개선이 필요하다.

### 발명의 내용

[0006] 본 발명의 실시예들은 금속성 소스 및 드레인 영역들을 갖는 반도체 장치들을 포함한다.

[0007] 한 실시예에서, 반도체 장치는 기판의 반전도 채널 영역(semiconducting channel region) 위에 배치된 게이트 전극 스택을 포함한다. 금속성 소스 및 드레인 영역들은 반전도 채널 영역의 양측에, 기판 위에 배치된다. 금속성 소스 및 드레인 영역들 각각은 프로필(profile)을 갖는다. 제1 반전도 외부 확산 영역(semiconducting out-diffusion region)은 반전도 채널 영역과 금속성 소스 영역 사이에 그리고 금속성 소스 영역의 프로필에 등각을 이루도록, 기판 내에 배치된다. 제2 반전도 외부 확산 영역은 반전도 채널 영역과 금속성 드레인 영역 사이에 그리고 금속성 드레인 영역의 프로필에 등각을 이루도록, 기판 내에 배치된다.

[0008] 다른 실시예에서, 반도체 구조는 N-형 반도체 장치를 포함한다. N-형 반도체 장치는 기판의 제1 반전도 채널 영역 위에 배치된 N-형 게이트 전극 스택을 포함한다. 제1 금속성 소스 및 드레인 영역들은 제1 반전도 채널 영역의 양측에, 기판 위에 배치된다. 제1 금속성 소스 및 드레인 영역들 각각은 제1 프로필을 갖는다. 제1 쪽의 반전도 외부 확산 영역은 제1 반전도 채널 영역과 제1 금속성 소스 및 드레인 영역들 중 대응하는 하나 사이에 그리고 대응하는 제1 프로필에 등각을 이루도록, 기판 내에 배치된다. 반도체 구조는 또한 P-형 반도체 장치를 포함한다. P-형 반도체 장치는 기판의 제2 반전도 채널 영역 위에 배치된 P-형 게이트 전극 스택을 포함한다. 제2 금속성 소스 및 드레인 영역들은 제2 반전도 채널 영역의 양측에, 기판 위에 배치된다. 제2 금속성 소스 및 드레인 영역들 각각은 제2 프로필을 갖는다. 제2 쪽의 반전도 외부 확산 영역은 제2 반전도 채널 영역과 제2 금속성 소스 및 드레인 영역들 중 대응하는 하나 사이에 그리고 대응하는 제2 프로필에 등각을 이루도록, 기판 내에 배치된다.

[0009] 다른 실시예에서, 반도체 장치를 제조하는 방법은 기판의 반전도 채널 영역 위에 게이트 전극 스택을 형성하는 단계를 포함한다. 반전도 채널 영역의 양측에서 기판의 한 쪽의 부분이 제거된다. 이후, 반전도 채널 영역의 양측에 한 쪽의 반전도 영역이 형성된다. 이후, 반전도 영역 쌍이 제거된다. 이후, 반전도 채널 영역의 양측에 금속성 소스 및 드레인 영역들이 형성된다.

### 도면의 간단한 설명

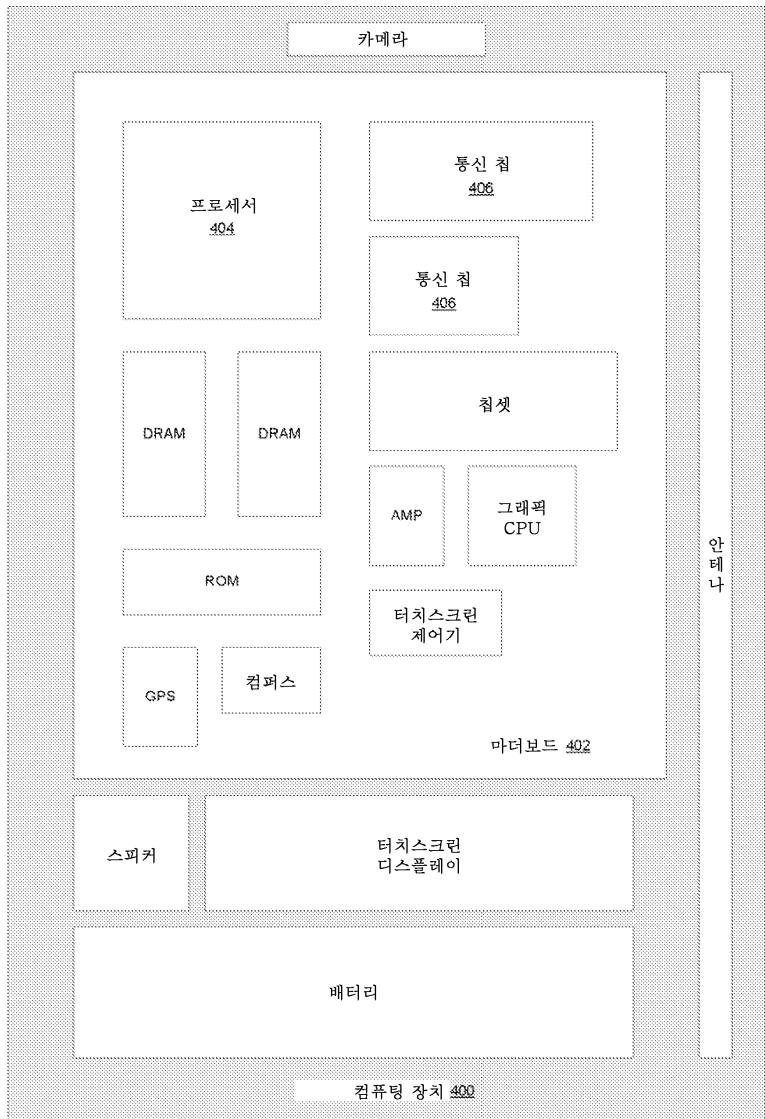

[0010] 도 1a는 본 발명의 실시예에 따른 반도체 장치(100 또는 100')의 평면도를 도시하고 있다.

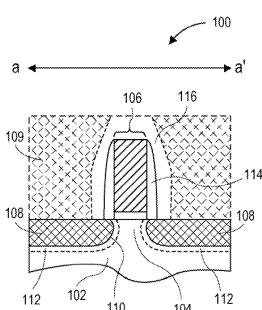

도 1b는 본 발명의 실시예에 따른, a-a'축을 따라서 취한, 도 1a의 반도체 장치(100)의 단면도를 보여주고 있다.

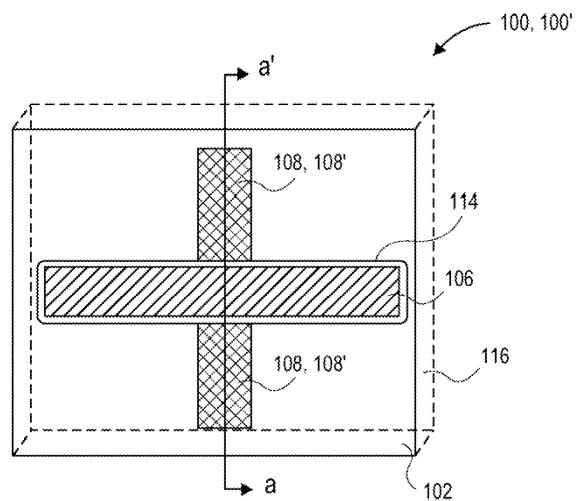

도 1bb는 본 발명의 실시예에 따른, a-a'축을 따라서 취한, 도 1a의 반도체 장치(100')의 단면도를 보여주고 있다.

도 2a는 본 발명의 실시예에 따른, 반전도 채널 영역 위에 형성된 게이트 전극 스택을 나타내는 단면도를 보여주고 있다.

도 2b는 본 발명의 실시예에 따른 게이트 전극 스택 아래에 놓이는, 기판 내에 배치된 반전도 채널 영역의 양측에 오목 영역들(recessed regions)을 제공하기 위해서 도 2a의 기판의 한 쪽의 부분을 제거하는 것을 나타내는 단면도를 도시하고 있다.

도 2c는 본 발명의 실시예에 따른, 도 2b의 오목 영역들 내에 한 쪽의 반전도 영역을 형성하는 것을 나타내는 단면도를 도시하고 있다.

도 2d는 본 발명의 실시예에 따른, 도 2c의 반전도 영역 쌍으로 한 쪽의 외부 확산 영역을 형성하는 것을 나타내는 단면도를 도시하고 있다.

도 2e는 본 발명의 실시예에 따른, 도 2d의 외부 확산 영역들은 남기면서, 제2 오목 영역들을 형성하기 위해 도 2c의 반전도 영역 쌍을 제거하는 것을 보여주는 단면도를 도시하고 있다.

도 2f는 본 발명의 실시예에 따른, 도 2e의 오목 영역들에 형성된 한 쪽의 금속성 소스 및 드레인 영역을 나타내는 단면도를 도시하고 있다.

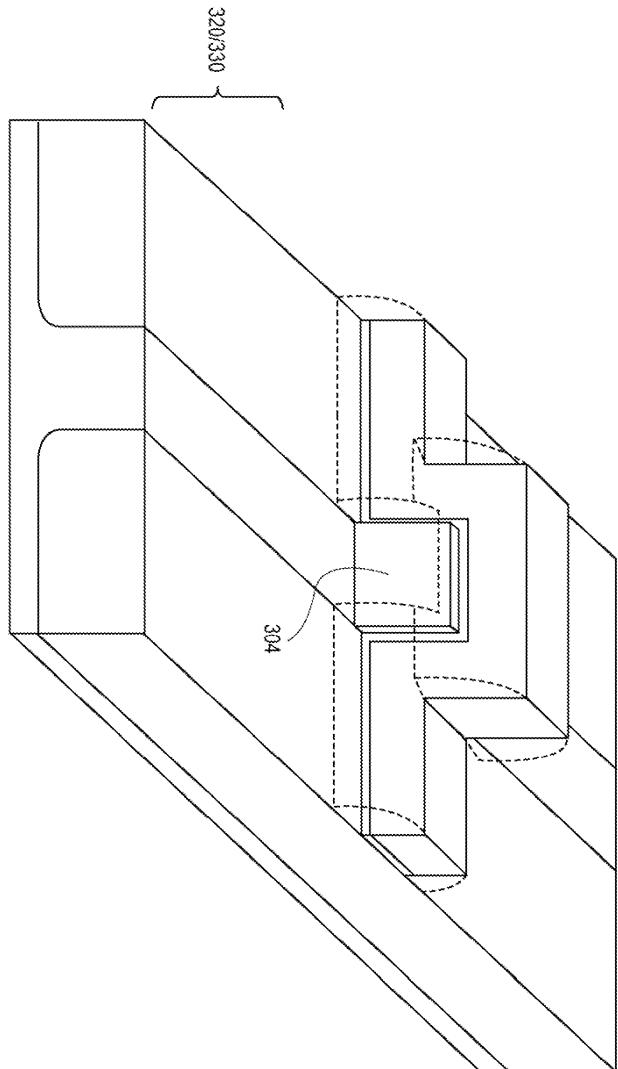

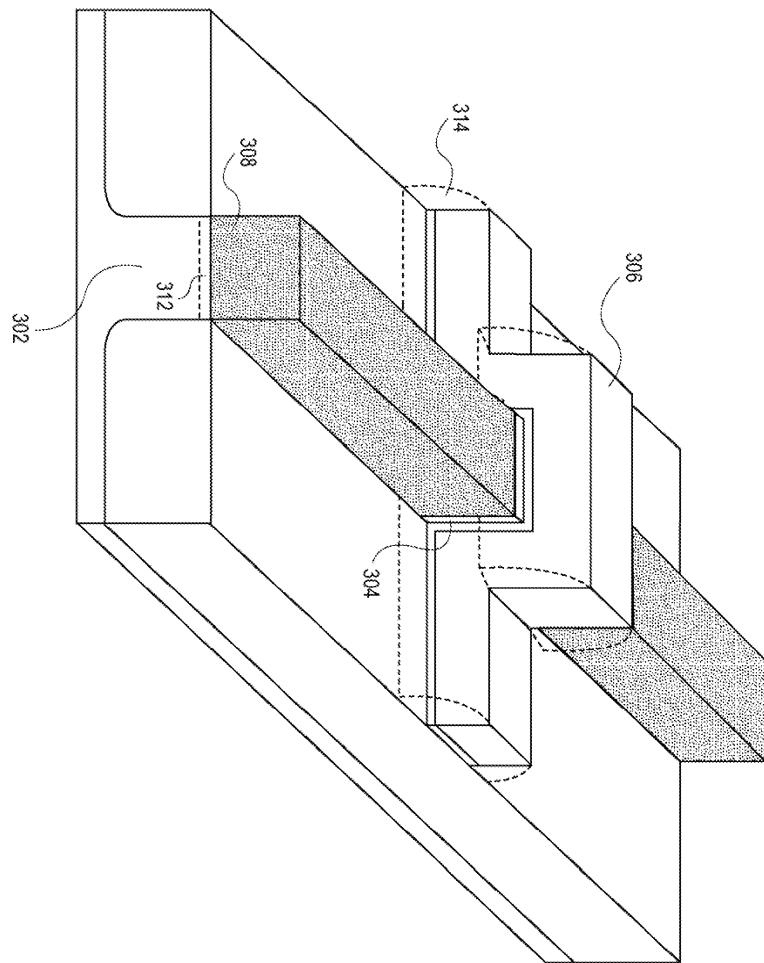

도 3a-3c는 본 발명의 실시예에 따른, 3차원 바디를 갖는 반도체 장치를 제조하는 방법에 있어서의 다양한 동작을 나타내는 앵글 뷰(angled views)를 도시하고 있다.

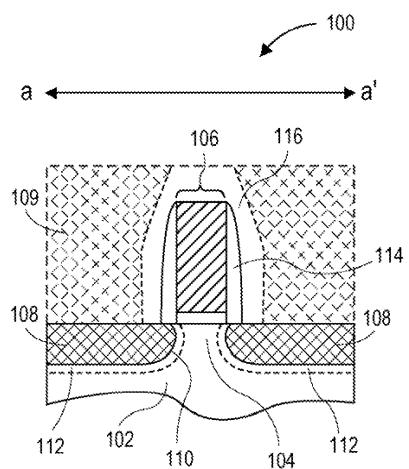

도 4는 본 발명의 일 구현에 따른 컴퓨팅 장치를 도시하고 있다.

### 발명을 실시하기 위한 구체적인 내용

[0011] 금속성 소스 및 드레인 영역들을 갖는 반도체 장치들이 기술된다. 다음의 설명에서, 본 발명의 실시예들에 대한 철저한 이해를 제공하기 위해서 구체적인 접적 및 재료 체제와 같은 수많은 구체적인 세부사항이 제시된다. 본 발명의 실시예들이 이를 구체적인 세부사항 없이도 실시될 수 있다는 것은 이 방면에 숙련된 자에게 자명할 것이다. 다른 경우들에서, 접적 회로 설계 레이아웃과 같은, 널리-공지된 피쳐들은 본 발명의 실시예들이 불필요하게 불명료해지지 않도록 상세히 기술되지 않는다. 더욱이, 도면들에 도시된 다양한 실시예들은 예시적인 표현이며 반드시 비례적으로 그려질 필요는 없음을 이해하여야 한다.

[0012] 여기에 기술된 1 이상의 실시예들은 자기-정렬(self-aligned) 금속성 소스/드레인 트랜지스터 제조에 목적을 두고 있다. 예를 들어, 금속 소스/드레인/팁 영역들은 종래의 평면 또는 트라이-게이트 장치와 통합될 수 있다. 금속 영역들은 일반적으로 구현되는 종래의 반도체 소스 및 드레인 영역들을 대체할 수 있고, 게이트 전극 스택에 자기-정렬될 수 있다. 여기에 기술된 실시예들은 또한 나노와이어 및 나노리본 장치들에 응용될 수 있다.

[0013] 한 실시예에서, 희생 소스/드레인/팁 영역들은 언더컷 에칭(undercut etch)과 뒤따르는 실리콘 게르마늄 에피택시를 이용하여 형성된다. 그러한 한 실시예에서는, 에피택설 영역들 주위에 얇고 고농도 도핑된(highly doped) 등각 접합(conformal junction)을 제공하기 위해서, 실리콘 게르마늄으로부터 도편트 불순물 원자들의 외부 확산(out-diffusion)이 실행될 수 있다. 한 실시예에서, 에피택설 영역들의 선택적 제거에 뒤이어, 금속성 소스 및 드레인 영역들이 형성된다. 금속성 소스 및 드레인 영역들의 재료는, 한 실시예에서, 최종 형성된 반도체 장치에 적절한 채널 응력(channel stress)을 유발하도록 선택된다.

- [0014] 한 실시예에서, 반도체 장치의 구동 전류는, 예를 들어, 금속성 소스 및 드레인 영역들과 소스 및 드레인 영역들의 직렬 저항을 줄임으로써 개선된다. 1 이상의 실시예들은 미드-갭(mid-gap) 금속화를 도핑되지 않은 채널들에 결합하는 새로운 장치 옵션을 가능하게 한다. 한 실시예에서, 금속 소스/드레인/팁 영역들은 고농도 도핑된 반전도 영역들(예로, 실리콘 또는 실리콘 게르마늄)을 이용하여 종래의 장치들과는 대조적으로 형성된다.

- [0015] 1 이상의 실시예들은 도핑된 반전도 영역들을 순수 금속 또는 금속 합금 영역들과 같은 금속성 영역들로 대체하는 것을 수반한다. 한 실시예에서, 직렬 저항은 그러한 금속성 영역들이 인터페이스 장벽 높이가 낮은 접촉 스킴(contact scheme)과 결합해서 이용될 때 낮아진다. 접촉 금속은 낮은 저항 미드-갭 접촉이 형성될 수 있게 하는, 도핑된 실리콘 또는 실리콘 게르마늄과는 다른 일함수를 제공하도록 선택될 수 있다. 충진 금속(fill metal) 및 공정은 대응 채널 영역에 대한 스트레서(stressor)로 작용하도록 선택될 수 있다. 이러한 접근 방식은, 적절한 에피택셜 반도체 스트레서가 통상 이용가능하지 않은 NMOS 장치들에 특별한 장점을 제공할 수 있다. 한 실시예에서, 채널과 자기-정렬된 금속 소스/드레인들이 형성되고, 등각 외부 확산 도핑 영역(conformal out-diffusion doping region)이 선택적으로 제공된다. 여기에 기술된 접근 방식을 이용해서 트라이-게이트 및 fin-FET 타입 장치들의 기생 저항을 줄일 수 있다.

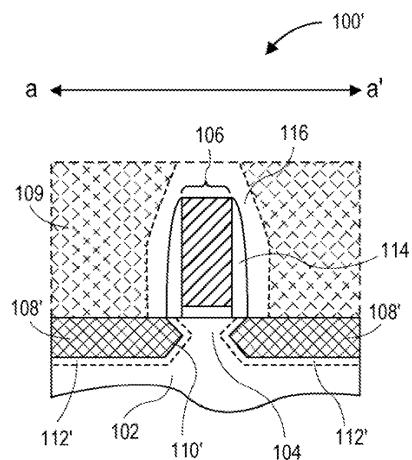

- [0016] 도 1a는 본 발명의 한 실시예에 따른, 반도체 장치(100 또는 100')의 평면도를 보여주고 있다. 도 1b는 a-a' 축을 따라서 취한, 도 1a의 반도체 장치(100)의 단면도를 보여주고 있다. 도 1bb는 a-a' 축을 따라서 취한, 도 1a의 반도체 장치(100')의 단면도를 보여주고 있다.

- [0017] 도 1a 및 도 1b 또는 도 1bb를 참조하면, 반도체 장치(100 또는 100')는 기판(102)의 반전도 채널 영역(104) 위에 배치된 게이트 전극 스택(106)을 포함한다. 금속성 소스 및 드레인 영역들(108 또는 108')은 반전도 채널 영역(104)의 양측에, 기판(102) 위에 배치된다. 금속성 소스 및 드레인 영역들(108 또는 108' 쌍) 양자는 각각 프로필(110 또는 110')을 갖는다. 한 쌍의 반전도 외부 확산 영역(112 또는 112')은 반전도 채널 영역(104)과 금속성 소스 및 드레인 영역들(108 또는 108' 쌍) 사이에, 기판(102) 내에 배치된다.

- [0018] 한 실시예에서, 반전도 외부 확산 영역들(112 또는 112')의 쌍은 금속성 소스 및 드레인 영역들(108 또는 108')의 프로필과 등각을 이룬다. 예를 들어, 도 1b를 참조하면, 일 실시예에서, 금속성 소스 및 드레인 영역들(108)은 등각 프로필(110)을 갖는다. 반전도 외부 확산 영역(112)의 쌍은 등각 프로필(110)과 등각을 이룬다. 다른 예에서, 도 1bb를 참조하면, 일 실시예에서, 금속성 소스 및 드레인 영역들(108')은 작은 면이 있는 (faceted) 프로필(110')을 갖는다. 반도체 외부 확산 영역들(112')의 쌍은 작은 면이 있는 프로필(110')과 등각을 이룬다.

- [0019] 한 실시예에서, 게이트 전극 스택(106)은 측벽 스페이서들(114)을 더 포함한다. 그러한 한 실시예에서, 금속성 소스 및 드레인 영역들(108 또는 108' 쌍) 각각의 적어도 일부는 게이트 전극 스택(106)의 측벽 스페이서(114) 아래에 배치된다. 더구나, 반전도 외부 확산 영역들(112 또는 112')의 쌍은 또한 측벽 스페이서들(114) 아래에, 그리고 가능한 게이트 전극 스택(106)의 일부 아래에 부분적으로 또는 완전히 배치될 수 있다.

- [0020] 한 실시예에서, 금속성 소스 및 드레인 영역들(108 또는 108' 쌍)은 각각 기판(102) 위에 배치된 유전체 층(116) 안에 배치된 대응하는 연속 접촉 구조에 포함된다. 예를 들어, 도 1b 및 도 1bb에 도시된 바와 같이, 쌍들(108 또는 108')의 금속성 소스 및 드레인 영역들은 각각 장치(100 또는 100')에 대한 접촉부로서 효과적으로 작용하는 연장부(109)를 갖는다. 그러한 한 실시예에서, 연장부들과 금속성 소스 및 드레인 영역들은 이하 더 상세히 기술되는 바와 같이 동시에 형성된 연속 구조이다.

- [0021] 반도체 장치(100 또는 100')는 게이트, 채널 영역 및 한 쌍의 소스/드레인 영역을 통합하는 임의 반도체 장치일 수 있다. 한 실시예에서, 반도체 장치(100 또는 100')는 예를 들어, MOS-FET 또는 MEMS(Microelectromechanical System)이며, 이에 한정되지 않는다. 한 실시예에서, 반도체 장치(100 또는 100')는 평면 또는 3차원 MOS-FET이고 분리된 장치이거나 복수의 네스티드 장치(nested device) 내의 한 장치이다. 전형적인 접적 회로에 대해 이해하듯이, N- 및 P-채널 트랜지스터들은 둘 다 단일 기판에 제조되어 CMOS 접적 회로를 형성하며 이의 반도체 구조는 이하 좀더 상세히 기술된다.

- [0022] 기판(102) 및, 그에 따라 채널 영역(104)은 제조 공정을 견딜 수 있고 전하가 이동할 수 있는 반도체 재료로 구성될 수 있다. 한 실시예에서, 기판(102)은 벌크 기판이고, 반전도 채널 영역(104)은 벌크 기판(102)과 연속이다. 한 실시예에서, 기판(102)은 인, 비소, 봉소, 또는 이들의 결합(이들에 한정되지 않음)과 같은 전하 캐리어가 도핑된 결정질 실리콘, 실리콘/게르마늄 또는 게르마늄 층으로 구성된다. 한 실시예에서, 기판(102) 내의 실리콘 원자의 농도는 97%보다 크거나, 대안적으로, 도편트 원자의 농도는 1% 미만이다. 다른 실시예에서, 기

판(102)은 별개의 결정질 기판 위에 성장된 에피택셜 층, 예를 들어, 봉소-도핑된 벌크 실리콘 모노-결정질(mono-crystalline) 기판 위에 성장된 실리콘 에피택셜 층으로 구성된다. 기판(102)은 또한, 예를 들어, 실리콘-온-인슐레이터 기판을 형성하기 위해 벌크 결정 기판과 에피택셜 층 사이에 배치된 절연 층을 포함할 수 있다. 그러한 예에서, 반전도 채널 영역(104)은 분리된 채널 영역일 수 있다. 한 실시예에서, 절연 층은 실리콘 이산화물, 실리콘 질화물, 실리콘 산질화물 또는 하이-k 유전체 층(이들에 한정되지 않음)과 같은 재료로 구성된다. 기판(102)은 대안으로 III-V족 재료로 구성될 수 있다. 한 실시예에서, 기판(102)은 갈륨 질화물, 갈륨 인화물, 갈륨 비소, 인듐 인화물, 인듐 안티몬화물, 인듐 갈륨 비소, 알루미늄 갈륨 비소, 인듐 갈륨 인화물, 또는 이들의 결합(이들에 한정되지 않음)과 같은 III-V 재료로 구성된다. 채널 영역(104)은 다수의 반도체 재료로 구성될 수 있고, 이를 각각은 부가의 도핑 원자를 포함할 수 있다. 일 실시예에서, 기판(102)은 결정질 실리콘으로 구성되며 전하 캐리어 도편트 불순물 원자는 봉소, 비소, 인듐 또는 인(이들에 한정되지 않음)과 같은 것이다. 다른 실시예에서, 기판(102)은 III-V 재료로 구성되며 전하-캐리어 도편트 불순물 원자는 카본, 실리콘, 게르마늄, 산소, 황, 셀레늄, 또는 텔루륨(이들에 한정되지 않음)과 같은 것이다. 다른 실시예에서, 채널 영역(104)은 도핑되지 않거나 단지 저농도 도핑된다(light doped). 부가적으로, 종래의 장치 제조에 종종 이용되는 할로 도핑(halo doping)은, 한 실시예에서, 반도체 장치(100 또는 100')의 제조시에 제거될 수 있다. 한 실시예에서, 채널(104)의 재료는 기판(102)의 재료와는 상이하다는 것을 이해하여야 한다.

[0023] 한 실시예에서, 반도체 장치(100 또는 100')는 평면 장치이고, 게이트 전극 스택(106)은 반전도 채널 영역(104)의 단일 표면에만 배치된다. 다른 실시예에서, 그러나, 반도체 장치(100 또는 100')는 fin-FET 또는 트라이-게이트 장치(이들에 한정되지 않음)와 같은 비-평면 장치이다. 그러한 실시예에서, 반전도 채널 영역(104)은 3차원 바디로 구성되거나 형성된다. 그러한 한 실시예에서, 게이트 전극 스택(106)은 3차원 바디의 적어도 상부 표면과 한 쌍의 측벽을 에워싼다. 다른 실시예에서, 반전도 채널 영역(104)은 나노와이어 장치와 같은, 이산 3차원 바디가 되게 만들어진다. 그러한 한 실시예에서, 게이트 전극 스택(106)은 반전도 채널 영역(104)을 완전히 에워싼다.

[0024] 반전도 채널 영역(104)에 대한 3차원 바디의 경우에, 이산이든 비-이산(non-discrete)이든, 반전도 채널 영역(104)은 벌크 기판으로 제조될 수 있고, 반전도 채널 영역(104)은 벌크 기판과 연속이다. 대안으로, 반도체 채널 영역(104)은 스타팅 반도체-온-인슐레이터 기판(starting semiconductor-on-insulator substrate)으로 제조될 수 있다. 다른 실시예에서, 반도체 채널 영역(104)은 직접 벌크 기판으로 형성될 수 있고, 로컬 산화를 이용하여 전기 절연 하부 영역들을 형성한다. 다른 대안적인 실시예에서, 구조(100)는 직접 벌크 기판으로 형성되고 도핑을 이용하여 전기 절연 활성 영역들을 형성한다. 그러한 한 실시예에서, 오메가-FET 탑입 구조가 형성된다. 한 실시예에서, 나오와이어의 경우에, 반전도 채널 영역(104)은 와이어 또는 리본과 같은 크기로 형성될 수 있고, 각각을 이루거나 더 둥근 코너(squared-off or rounder corners)를 가질 수 있다.

[0025] 게이트 전극 스택(106)은 게이트 전극 및 하부의 게이트 유전체 층을 포함할 수 있다. 한 실시예에서, 게이트 전극 스택(106)의 게이트 전극은 금속 게이트로 구성되고 게이트 유전체 층은 하이-k 재료로 구성된다. 예를 들어, 한 실시예에서, 게이트 유전체 층은 하프늄 산화물, 하프늄 산질화물, 하프늄 실리케이트, 란타늄 산화물, 지르코늄 산화물, 지르코늄 실리케이트, 탄탈륨 산화물, 바륨 스트론튬 티탄산염, 바륨 티탄산염, 스트론튬 티탄산염, 이트륨 산화물, 알루미늄 산화물, 납 스칸듐 탄탈륨 산화물, 납 아연 니오브산염, 또는 이들의 결합(이들에 한정되지 않음)과 같은 재료로 구성된다. 더욱이, 게이트 유전체 층의 일부는 반도체 채널 영역(104)의 상부 수개의 층으로 형성된 네이티브 산화물(native oxide)의 층을 포함할 수 있다. 한 실시예에서, 게이트 유전체 층은 상부 하이-k 부분과 반도체 재료의 산화물로 구성된 하부 부분으로 구성된다. 한 실시예에서, 게이트 유전체 층은 하프늄 산화물의 상부 부분과 실리콘 이산화물 또는 실리콘 산질화물의 하부 부분으로 구성된다.

[0026] 일 실시예에서, 게이트 전극은 금속 질화물, 금속 카바이드, 금속 실리케이트, 금속 알루미나이드, 하프늄, 지르코늄, 티타늄, 탄탈륨, 알루미늄, 루테늄, 팔라듐, 플래티늄, 코발트, 니켈 또는 전도 금속 산화물(이들에 한정되지 않음)과 같은 금속 층으로 구성된다. 특정 실시예에서, 게이트 전극은 금속 일함수-설정 층 위에 형성된 비-일함수-설정 층진 재료로 구성된다. 한 실시예에서, 게이트 전극은 P-형 재료로 구성된다. 다른 실시예에서, 게이트 전극은 N-형 재료로 구성된다. 다른 실시예에서, 게이트 전극은 미드-캡 재료로 구성된다. 그러한 특정 실시예에서, 대응하는 채널 영역은 도핑되지 않거나 단지 저농도 도핑된다.

[0027] 본 발명의 실시예에 따르면, 소스 및 드레인들(108 또는 108' 쌍)은 "전도(conducting)"로서 기술된다. 용어 금속성은 예를 들어, 채널 영역 및 외부 확산 영역에 이용되는 바와 같이, 반전도와 구별된다. 금속성 소스 및 드레인 영역들은 도핑된 반도체 재료들과는 대조되는 것으로 금속성인 재료들로 구성된 영역들이다. 그래서,

한 실시예에서, 금속성 소스 및 드레인 영역들(108 또는 108')은 반전도인 것으로 이해되는 도핑된 반도체 재료와는 대조되는 것으로, 금속성 종으로 구성된다. 일례로, 소스 및 드레인 영역들(108 또는 108')(및, 적용가능하다면, 연장 또는 접촉 영역(109))은 금속 질화물, 금속 카바이드, 금속 실리사이드, 금속 알루미나이드, 하프늄, 지르코늄, 티타늄, 탄탈륨, 알루미늄, 루테늄, 팔라듐, 플래티넘, 코발트, 니켈 또는 전도 금속 산화물, 예로, 루테늄 산화물(이들에 한정되지 않음)과 같은 전도 재료로 구성된다. 그러한 한 실시예에서, 금속성 소스 및 드레인 영역들(108 또는 108')은 금속 카바이드 또는 금속 알루미나이드(이들에 한정되지 않음)와 같은 N-형 전도 재료로 구성된다. 그러한 다른 실시예에서, 금속성 소스 및 드레인 영역들(108 또는 108')은 금속 카바이드 또는 금속 알루미나이드(이들에 한정되지 않음)와 같은 P-형 전도 재료로 구성된다. 금속성 소스 및 드레인 영역들(108 또는 108')은 단일 금속 종 또는 합금 종과 같은 단일 재료로 구성될 수 있다. 대안으로, 티타늄 질화물 또는 탄탈륨 질화물과 같은, 얇은 전도 라이너 필름(liner film)이 먼저 형성되고 나서 단일 금속 종 또는 합금 종과 같은 충진 재료가 형성될 수 있다.

[0028] 이와 같이, 한 실시예에서, 금속성 소스 및 드레인 영역들(108 또는 108')은 금속 종으로 제조된다. 금속 종은 니켈 또는 코발트와 같은 순수 금속일 수 있거나, 또는 금속-금속 합금 또는 금속-반도체 합금(예를 들어, 실리사이드 재료 등)과 같은 합금일 수 있다. 그러나, 금속성 소스 및 드레인 영역들(108 또는 108')은, 반전도 나머지 소스 및 드레인 영역 맨 위에 가로 놓이는(overlying) 실리사이드 재료가 형성되도록 실리콘 소스 및 드레인 영역의 상부 부분이 금속에 의해 소모되는(consumed) 실리사이드 공정으로 형성된 소스 및 드레인 영역과 구별된다. 즉, 실리사이드 재료가 소스 및 드레인 영역들(108 또는 108') 전체에 가능한 것으로 열거되어 있을지도라도, 한 실시예에서, 그러한 실리사이드는, 실리콘 소스/드레인 영역의 일부의 소모(consumption)를 통해서 형성되는 것과는 대조적으로, 이미 형성된 실리사이드 금속성 재료로서 퇴적된다. 그러한 소모로 인해 구조는 거칠어지고 공차 제어 손실(loss of tolerance control)이 따를 수 있다.

[0029] 한 실시예에서, 금속성 소스 및 드레인 영역들(108 또는 108')은 반전도 채널 영역(104)에 단축으로 응력을 준다(uniaxially stress). 일례로, 금속성 소스 및 드레인 영역들(108 또는 108')은 상승된 온도에서 형성되고, 제조에 뒤이은 냉각시에 반전도 채널 영역(104)에 인장 단축 변형(tensile uniaxial strain)을 제공한다. 대안 실시예에서, 그러나, 금속성 소스 및 드레인 영역들(108 또는 108')은 제조 후의 반전도 채널 영역(104)에 압축 단축 변형(compressive uniaxial strain)을 제공한다.

[0030] 프로필(110)은 먼저 기판(102) 내에 에칭-아웃 영역(etch-out region)을 형성함으로써 형성될 수 있고 그에 의해서 영향을 받을 수 있다. 에칭-아웃 영역들은 기판(102)의 일부를 선택적으로 제거하고 게이트 전극 스택(106) 및/또는 스페이서들(114)을 언더컷(undercut)하는데 적합한 기법에 의해서 형성될 수 있다. 일 실시예에서, 에칭-아웃 영역들은 건식 에칭 공정, 습식 에칭 공정 또는 이들의 결합으로 기판(102)의 노출된 부분들을 에칭함으로써 형성된다. 일 실시예에서, 에칭-아웃 영역들은, 도 1b에 프로필(110)로 도시된 바와 같이, 둥근 코너를 갖는 등방성 에칭-아웃 영역들을 형성하기 위해 NF<sub>3</sub> 또는 SF<sub>6</sub>(이들에 한정되지 않음)와 같은 가스로 생성된 플라즈마를 이용하는 건식 플라즈마 에칭에 의해 형성된다. 대안 실시예에서, 에칭-아웃 영역들은 NH<sub>4</sub>OH 또는 테트라메틸암모늄 수산화물(tetramethylammonium hydroxide)을 이용하는 습식 에칭에 의해 형성된다. 습식 에칭은 에칭 속도가 높은 결정 밀도의 방향으로는 상당히 느리다는 점에서 비등방성일 수 있다. 예를 들어, 특정 실시예에서, 습식 에칭은, 도 1bb에 플로필(110')로 도시된 바와 같이, 작은 면이 있는 프로필을 갖는 에칭-아웃 영역들을 제공하기 위해 (100) 실리콘 기판 내의 <111> 결정면들에 의해서 저지된다. 게이트 전극 스택(106) 아래의 언더컷의 크기는 먼저 간단한 건식 에칭을 실행한 후 비등방성 습식 에칭 공정을 실행함으로써 증가할 수 있다.

[0031] 한 실시예에서, 반도체 장치(100 또는 100')는 N-형 장치이고, 반전도 채널 영역(104)은 실리콘으로 구성되고, 반전도 외부 확산 영역들(112 또는 112')의 쌍은 인 또는 비소(이들에 한정되지 않음)와 같은 도편트 불순물 원자로 형성된다. 다른 실시예에서, 반도체 장치(100 또는 100')는 P-형 장치이고, 반전도 채널 영역(104)은 실리콘으로 구성되며, 반전도 외부 확산 영역들(112 또는 112')의 쌍은 봉소 도편트 불순물 원자로 형성된다.

[0032] 한 실시예에서, 측벽 스페이서들(114)은 실리콘 이산화물, 실리콘 카바이드, 실리콘 산질화물 또는 실리콘 질화물(이들에 한정되지 않음)과 같은 절연성 유전체 재료로 구성된다. 마찬가지로, 유전체 층(116)은 실리콘 이산화물, 실리콘 카바이드, 실리콘 산질화물 또는 실리콘 질화물(이들에 한정되지 않음)과 같은 절연성 유전체 재료로 구성된다. 그러한 유전체 층(116)은, 일부 상황에서는, 층간 유전체 층 또는 ILD0 층이라 칭해질 수 있다.

[0033] 위에서 간략히 언급한 바와 같이, CMOS 구조가 형성될 수 있다. 좀 더 구체적으로, N-형 및 P-형 장치들은 둘다

동일한 기판에 형성될 수 있다. 본 발명의 예시적인 실시예에서, 장치 쌍 중 하나를 보여주고 있는 반도체 장치(100 또는 100')에서, 반도체 구조는 N-형 반도체 장치를 포함하고 있다. N-형 반도체 장치는 기판의 제1 반전도 채널 영역 위에 배치된 N-형 게이트 전극 스택을 포함한다. 제1 금속성 소스 및 드레인 영역들은 제1 반전도 채널 영역의 양측에, 기판 위에 배치된다. 제1 금속성 소스 및 드레인 영역들 각각은 제1 프로필을 갖는다. 제1 쌍의 반전도 외부 확산 영역은 제1 반전도 채널 영역과 제1 금속성 소스 및 드레인 영역들 중 대응하는 것 사이에, 기판 내에 배치된다. 제1 쌍의 반전도 외부 확산 영역은 대응하는 제1 프로필과 등각을 이룬다.

[0034] 반도체 구조는 또한 P-형 반도체 장치를 포함한다. P-형 반도체 장치는 기판의 제2 반전도 채널 영역 위에 배치된 P-형 게이트 전극 스택을 포함한다. 제2 금속성 소스 및 드레인 영역들은 제2 반전도 채널 영역의 양측에, 기판 위에 배치된다. 제2 금속성 소스 및 드레인 영역들 각각은 제2 프로필을 갖는다. 제2 쌍의 반전도 외부 확산 영역은 제2 반전도 채널 영역과 제2 금속성 소스 및 드레인 영역들 중 대응하는 것 사이에, 기판 내에 배치된다. 제2 쌍의 반전도 외부 확산 영역은 대응하는 제2 프로필과 등각을 이룬다.

[0035] 한 실시예에서, 제1 또는 제2 소스 및 드레인 영역 쌍들 중 하나는 등근 프로필을 갖고, 대응하는 제1 또는 제2 쌍의 반전도 외부 확산 영역들은 등근 프로필과 등각을 이룬다. 다른 실시예에서, 제1 또는 제2 금속성 소스 및 드레인 영역 쌍들 중 하나는 작은 면이 있는 프로필을 갖고, 대응하는 제1 또는 제2 쌍의 반전도 외부 확산 영역은 작은 면이 있는 프로필과 등각을 이룬다. 한 실시예에서, N-형 또는 P-형 게이트 전극 스택들 중 하나는 측벽 스페이서들을 포함하고, 대응하는 제1 또는 제2 금속성 소스 및 드레인 영역 쌍 각각의 적어도 일부는 N-형 또는 P-형 게이트 전극 스택의 측벽 스페이서 아래에 배치된다. 한 실시예에서, 제1 또는 제2 금속성 소스 및 드레인 영역 쌍은 기판 위에 배치된 유전체 층 안에 배치된 한 쌍의 연속 접촉 구조 내에 포함된다. 한 실시예에서, 제1 금속성 소스 및 드레인 영역들은 제1 반전도 채널 영역에 단축으로 응력을 주며, 제2 금속성 소스 및 드레인 영역들은 제2 반전도 채널 영역에 단축으로 응력을 준다.

[0036] 한 실시예에서, 제1 반전도 채널 영역은 실리콘으로 구성되고, 제1 쌍의 반전도 외부 확산 영역은 인 또는 비소, 또는 이를 양자의 도편트 불순물 원자로 형성된다. 이 실시예에서, 제2 반전도 채널 영역은 또한 실리콘으로 구성되고, 제2 쌍의 반전도 외부 확산 영역은 봉소 도편트 불순물 원자로 형성된다. 그러한 한 실시예에서, 제1 금속성 소스 및 드레인 영역들은 금속 카바이드 또는 금속 알루미나이드(이들에 한정되지 않음)와 같은 N-형 전도 재료로 구성되고, 제2 금속성 소스 및 드레인 영역들은 금속 질화물, 금속 카바이드, 또는 금속 실리사이드(이들에 한정되지 않음)와 같은 P-형 전도 재료로 구성된다.

[0037] 한 실시예에서, 기판은 별크 기판이고, 제1 및 제2 반전도 채널 영역들은 별크 기판과 연속이다. 다른 실시예에서, 기판은 절연 층을 포함하고, 제1 및 제2 반전도 채널 영역은 분리된 채널 영역들이다. 한 실시예에서, 제1 및 제2 반전도 채널 영역들은 각각 3차원 바디를 포함하거나 그 안에 형성되며, 대응하는 게이트 전극 스택은 3차원 바디의 적어도 상부 표면과 한 쌍의 측벽을 에워싼다.

[0038] 다른 양태에서, 전도 소스 및 드레인 영역들을 갖는 반도체 장치를 제조하는 방법들이 제공된다. 예를 들어, 도 2a-2f는 본 발명의 실시예에 따른, 반도체 장치를 제조하는 방법의 다양한 동작을 나타내는 단면도를 도시하고 있다.

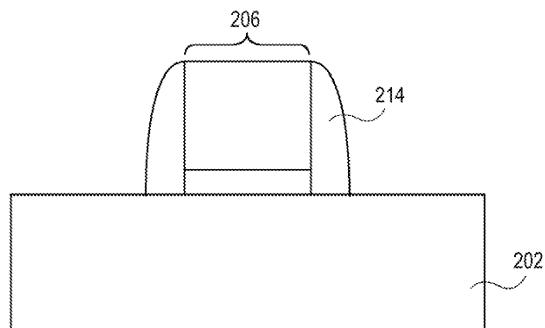

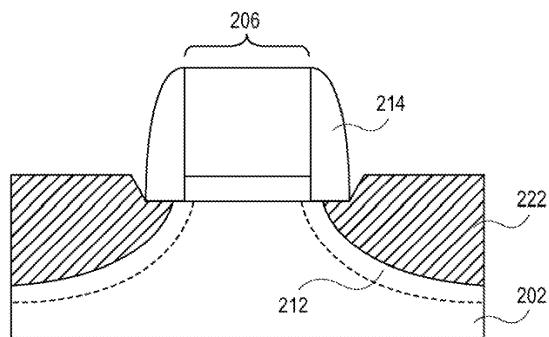

[0039] 도 2a를 참조하면, 반도체 장치를 제조하는 방법은 기판(202)의 반전도 채널 영역 위에 게이트 전극 스택(206)을 형성하는 단계를 포함한다. 스페이서들(214)은 도 2a에 도시된 바와 같이 게이트 전극 스택(206)의 측벽들을 따라서 형성될 수 있다. 게이트 전극 스택(206), 기판(202) 및 대응 채널 영역, 및 스페이서들(214)은 위에서 기술된 게이트 전극 스택(106), 기판(102) 및 대응 채널 영역(104), 및 스페이서들(114)과 같거나 유사한 재료 및 배열로 구성될 수 있다. 한 실시예에서, 게이트 전극 스택(206)은 이미 형성된 영구 게이트 유전체 층 및 게이트 전극 쌍이다. 다른 실시예에서, 그러나, 게이트 전극 스택(206)은 후속 대체 게이트 또는 게이트-라스트 처리 스킁(subsequent replacement gate or gate-last processing scheme)에서 최종 이용을 위한 플레이스홀더(placeholder) 스택 또는 단일 층이다.

[0040] 도시되지 않았을지라도, 선택적인 실시예에서, 한 쌍의 팁 연장부(tip extension)는 이 스테이지에서 전하-캐리어 도편트 불순물 원자를 기판(202) 내에 주입함으로써 형성될 수 있다. 그러한 경우에, 게이트 전극 스택(206)은 자기-정렬 팁 연장부들이 형성되도록 기판(202)의 일부를 마스킹하는 작용을 할 수 있다. 일 실시예에서, 봉소, 비소, 인, 인듐 또는 이들의 결합이 기판(202) 내로 주입되어 그러한 팁 연장부들이 형성된다.

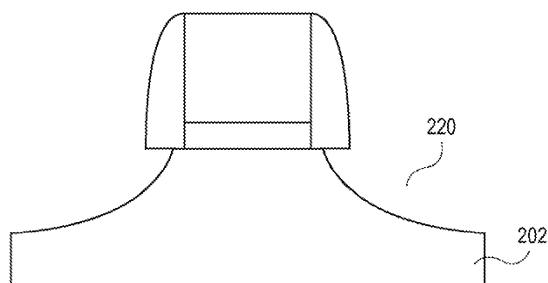

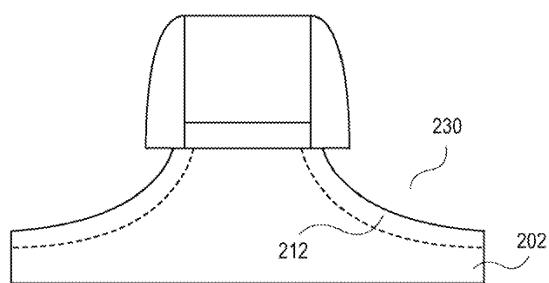

[0041] 도 2b를 참조하면, 기판(202)의 한 쌍의 부분은 게이트 전극 스택(206) 아래에 놓여 있는 기판(202) 내에 배치된 반전도 채널 영역의 양측에, 오목 영역들(220)이 제공되도록 제거된다. 오목 영역들(220)은 건식 에칭 또는

습식 에칭 공정과 같은, 존재하는 다른 반도체 피처들에 유해한 영향을 주지 않고 기판(202)의 일부를 제거하는 임의 적합한 기법에 의해 형성될 수 있다. 일 실시예에서, 오목 영역들(220)은  $\text{NF}_3$ ,  $\text{HBr}$ ,  $\text{SF}_6/\text{Cl}$  또는  $\text{Cl}_2$ 를 이용하는 건식 플라즈마 에칭에 의해서 또는  $\text{NH}_4\text{OH}$  또는 테트라메틸암모늄 수산화물을 이용하는 습식 에칭에 의해서 형성된다. 일 실시예에서, 게이트 전극 스택(206)은 자기-정렬 오목 영역들(220)이 형성되도록 오목 영역들(220)의 형성을 가이드(guide)한다. 일 실시예에서, 오목 영역들(220)은, 도 2b에 도시되어 있으며 도 1b에 연관해서 기술된 바와 같이, 둥근 코너를 갖게 형성된다. 다른 실시예에서, 그러나, 오목 영역들(220)은 도 1bb에 연관해서 기술된 바와 같이, 작은 면이 있는 코너들을 갖게 형성된다.

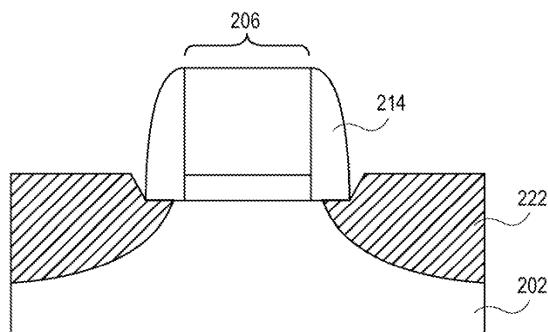

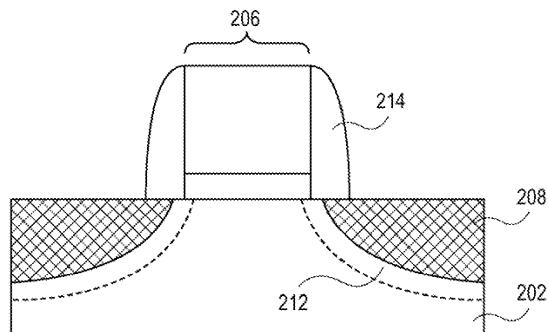

[0042] 도 2c를 참조하면, 한 쌍의 반전도 영역(222)은 오목 영역들(220) 내에 형성되는데, 예를 들어, 기판(202) 내에 형성된 반전도 채널 영역의 양측에 에피택셜 형성된다. 도 2d를 참조하면, 한 쌍의 외부 확산 영역(212)은 게이트 전극 스택(206) 아래에 배치된 반전도 채널 영역의 양측에, 기판(202) 내에 형성된다.

[0043] 본 발명의 실시예에 따르면, 외부 확산 영역들(212)의 쌍은 반전도 영역들(222)로 형성되고 반전도 영역들(222)과 등각을 이룬다. 그러한 한 실시예에서, 최종 형성된 반도체 장치는 N-형 반도체 장치이다. 반도체 채널 영역은 실리콘으로 구성되고, 반전도 영역들(222)의 쌍을 형성하는 단계는 실리콘 게르마늄 반전도 영역들의 쌍을 형성하는 단계를 포함한다. 그러한 특정 실시예에서는, 외부 확산 영역들(212)의 쌍은 인 또는 비소 도편트 불순물 원자로 형성된다. 그러한 다른 실시예에서, 최종 형성된 반도체 장치는 P-형 반도체 장치이다. 반전도 채널 영역은 실리콘으로 구성되고, 반전도 영역들(222)의 쌍을 형성하는 단계는 실리콘/실리콘 게르마늄 스택 반전도 영역들의 쌍을 형성하는 단계를 포함한다. 그러한 특정 실시예에서, 외부 확산 영역들(212)의 쌍은 봉소 도편트 불순물 원자로 형성된다. 반전도 영역(222)은 도핑(인 시투(*in situ*))으로 성장될 수 있고 또는 성장 공정 후에 영역들(222)에 도핑이 주입될 수 있고, 또는 둘 다 가능하다.

[0044] 한 실시예에서, 반전도 영역들(222)의 재료는 내부의 불순물 원자의 확산 속도를 기반으로 등각 또는 본질적으로 등각인 외부 확산 영역(212)이 제공되도록 선택된다. 예를 들어, 한 실시예에서, 실리콘 게르마늄은 실리콘 기판 내에 인 또는 비소 외부 확산 영역들(212)이 형성되도록 반전도 영역(222)으로서 이용된다. 인 또는 비소는 실리콘 안에서보다 실리콘 게르마늄 안에서 더 빠르게 확산하며, 이는 대응 외부 확산 영역의 모양이 실리콘 게르마늄 반전도 영역(222)에 등각이 되게 한다. 다른 예에서, 한 실시예에서, 실리콘은 실리콘 기판 내에 봉소 외부 확산 영역들(212)이 형성되도록 반전도 영역(222)으로서 이용된다. 봉소은 실리콘 안에서 신속하게 확산하며, 이는 대응 외부 확산 영역의 모양이 실리콘 반전도 영역(222)에 등각이 되게 한다. 그러나, 실리콘 게르마늄의 얇은 층은, 도 2e에 연관해서 실행되는 바와 같이, 실리콘 반전도 영역(222)의 제거 동안 에칭 정지로서 차후 이용을 위해 실리콘 기판과 실리콘 반전도 영역(222) 사이에 이용될 수 있다.

[0045] 도 2e를 참조하면, 반전도 영역들(222)의 쌍은 오목 영역들(230)이 제공되도록 제거되지만, 외부 확산 영역들(212)은 기판(202) 내에 유지된다. 그래서, 한 실시예에서, 반전도 영역들(222)의 쌍은 외부 확산 형성을 위해 도편트 불순물 원자를 전달하기 위한 희생 재료로서 이용된다. 그러한 한 실시예에서는, 반직관적으로(counter-intuitively), 희생 실리콘 게르마늄 반전도 영역은 N-형 장치를 위해 인 또는 비소 도편트 불순물 원자를 제공하는데 이용된다. 그러한 한 실시예에서, 희생 실리콘 게르마늄 반전도 영역은 압축 응력으로 반전도 채널 영역에 단축으로 응력을 주며, 이는 통상 N-형 장치에는 바람직하지 않다. 그러나, 희생 실리콘 게르마늄 반전도 영역이 제거되기 때문에, 단축 압축 응력은 장치 제조의 완성 전에 경감된다.

[0046] 한 실시예에서, 실리콘 게르마늄 반전도 영역(222)은, 실리콘 기판(202)은 에칭하지 않으면서 반전도 영역들(222)을 선택적으로 제거하는 습식 에칭을 이용하여 선택적으로 에칭된다. 예를 들어, 카복실산/질산/HF 화학적 성질, 및 구연산/질산/HF와 같은 에칭 화학적 성질은, 실리콘 게르마늄 반전도 영역들(222)을 선택적으로 에칭하는데 이용될 수 있다. 실리콘 제거의 경우에, 실리콘 게르마늄의 얇은 층은, 위에서 언급한 바와 같이, 에칭 정지 층으로서 이용될 수 있다. 그래서, 한 실시예에서는, 실리콘 반전도 영역들(222)은 실리콘 게르마늄에칭 정지 층을 에칭하지 않으면서 실리콘 반전도 영역들(222)을 선택적으로 제거하는 습식 에칭을 이용하여, 실리콘 게르마늄에칭 정지 층 상에서 정지하도록 선택적으로 에칭된다. 예를 들어, 암모늄 수산화물 및 포타슘 수산화물을 포함해서, 수성 수산화물 화학적 성질들과 같은 그러한 식각 화학적 성질들은, 실리콘 반전도 영역들(222)을 선택적으로 에칭하는데 이용될 수 있다. 실리콘 게르마늄에칭 정지 층은 이후, 예를 들어, 카복실산/질산/HF 화학적 성질 또는 구연산/질산/HF에 의해서 제거될 수 있다.

[0047] 도 2f를 참조하면, 한 쌍의 금속성 소스 및 드레인 영역(208)은 오목 영역들(230) 내에 형성되는데, 예를 들어, 기판(202) 내에 형성된 반전도 채널 영역의 양측에 형성된다. 금속성 소스 및 드레인 영역들(208)의 쌍은 위에

서 기술된 금속성 소스 및 드레인 영역들(108)의 쌍과 같거나 유사한 재료 및 배열로 구성될 수 있다.

[0048] 도 2e 및 2f에는 도시되어 있지 않고 도 1b 및 도 1bb에 연관해서 기술되어 있지만, 반전도 영역들(222)을 제거하고 금속성 소스 및 드레인 영역들(208)의 쌍을 형성하기 전에, 위에서 기술된 유전체 층(116)과 같은 유전체 층을 먼저 형성한 다음 접촉 홀들(contact holes)을 통해 반전도 영역들(222)이 노출되도록 패턴화할 수 있다. 반전도 영역들(222)이 제거되고 나서 금속성 소스 및 드레인 영역들(208)의 쌍이 접촉 홀들을 통해 형성된다. 사실, 좀더 정교한 실시예에서, 다른 희생 재료는 반전도 영역들(222)을 대체하는데 이용될 수 있고 최종에는 위에 형성된 접촉 홀들을 통해서 제거된다. 어느 경우에든, 접촉부 형성과 함께, 금속성 소스 및 드레인 형성은 금속을 접촉 홀 개구부(contact hole opening)에 퇴적함으로써 완료된다. 한 실시예에서는, 얇은 인터페이스 금속이 원자 층 증착(atomic layer deposition; ALD)을 이용하여 등각으로 퇴적되고 1 이상의 접촉 층진 금속이, 예를 들어, 화학 기상 증착(CVD), 원자 층 증착(ALD), 또는 금속 리플로우를 이용함으로써 퇴적되어 접촉부 형성이 완료되는 다중-작업 접근 방식이 이용된다. 다른 인터페이스 엔지니어링 접근 방식들은 인터페이스의 실리콘 측의 도핑 레벨에 따라서 원하는 인터페이스 접촉 저항을 성취하는데 이용될 수 있다. 층진 금속 및 처리는 장치 성능의 개선을 위해서 장치의 채널에 인장이나 압축 응력을 유도하기 위해 선택될 수 있다. 한 실시예에서, 접촉 및 소스/드레인 층진은, 예를 들어, 하이-k 게이트 유전체 층의 고온 어닐링(hight temperature anneal)을 포함할 수 있는 대체 게이트 공정 이후에 실행된다.

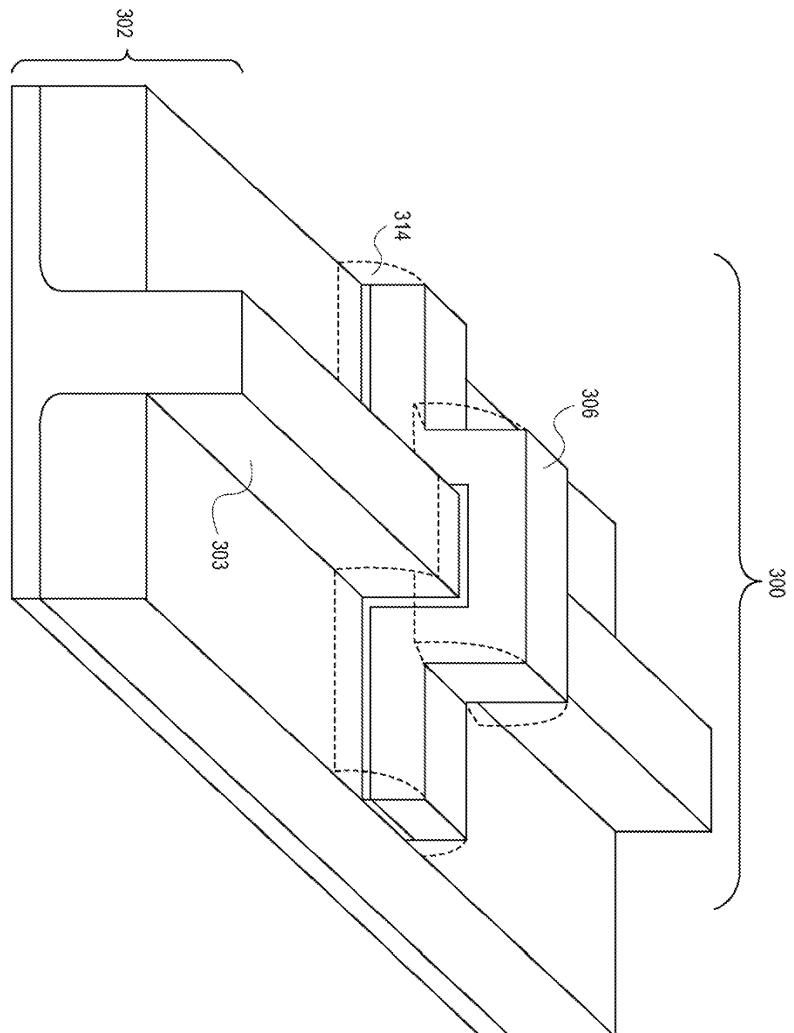

[0049] 본 발명의 실시예들은 비-평면 MOS-FET에 적용될 수 있다. 예를 들어, 트라이-게이트 장치와 같은, 3차원 아키텍처를 갖는 장치는 위에 기술된 공정으로부터 이익을 얻을 수 있다. 도 3a-3c는 본 발명의 실시예에 따른, 3차원 바디를 갖는 반전도 장치를 제조하는 방법에서 다양한 작업을 표현하는 앵글 뷰를 보여주고 있다.

[0050] 도 3a를 참조하면, 벌크-기판 트라이-게이트 MOS-FET(300)의 기초가 형성된다. 트라이-게이트 MOS-FET(300)은 반전도 바디(303)를 갖는 3차원 기판(302)을 포함한다. 게이트 전극 스택(306)은 3차원 반전도 채널 영역(304)(도 3b에 도시되어 있음)이 형성되도록 반전도 바디(303) 주위에 형성된다. 게이트 전극 스택(306)은 한 쌍의 게이트 분리 스페이서(314)에 의해 보호된다.

[0051] 도 3b를 참조하면, 반전도 바디(303)의 부분들은 3차원 채널 영역(304)은 남겨두면서, 예칭 아웃 영역들(320)이 형성되도록 제거된다. 또한 도 3b에 도시된 바와 같이, 이후 희생 반전도 영역들은 오목 영역(320)에 형성되고, 이웃-확산 영역들을 전달하는데 이용되고, 오목 영역들(330)이 형성되도록 제거될 수 있다.

[0052] 도 3c를 참조하면, 금속성 소스 및 드레인 영역들(308)은 오목 영역들(330) 내에 형성된다. 또한 외부 확산 영역들(312)이 도시되어 있다. 이와 같이 금속성 소스/드레인 영역들을 포함하는 트라이-게이트 MOS-FET 장치를 형성하는 방법이 기술되었다. 트라이-게이트 MOS-FET는 이 방면에 알려져 있는 종래의 처리 단계들에 의해 집적 회로에 통합될 수 있다.

[0053] 따라서, 본 발명의 1 이상의 실시예는 평면 또는 트라이-게이트 또는 fin-FET 제조 공정을 위해 종래의 MOSFET 공정 플로우의 일부 이용을 포함한다. 선택적으로, 형성된 금속성 소스/드레인 영역들과 트라이-게이트 또는 fin-FET 장치 내의 게이트 간의 임의의 기생 용량을 최소화하기 위해, 후속 측면 에피택셜 성장이 한정되도록 편 스페이서 유전체를 적소에 남겨둘 수 있다. NMOS 및 PMOS 장치 타입의 경우, 한 실시예에서, 소스/드레인/팁 영역들로부터 실리콘을 제거하기 위해 언더컷 에칭이 이용되며, 실리콘 게르마늄은 소스/드레인 개구부 안에 에피택셜 성장된다. 소스/드레인 영역들과 트라이-게이트 또는 fin-FET 장치 내의 게이트 간의 최종 기생 용량을 최소화하기 위해, 실리콘 게르마늄 에피택셜 성장은 종래의 PMOS 플로우에서 통상 실행되는 것보다 덜 이용될 수 있다. 예를 들어, 실리콘 게르마늄으로 오리지널 편 영역만을 층진하는 것으로 충분할 수 있다.

[0054] 선택적으로, 한 실시예에서, 접촉부 주위에 등각 도핑이 필요하다면, 실리콘 게르마늄 에피택셜 막이 도핑으로 성장될 수 있거나 또는 이 막은 에피택시 후에 도편트가 주입될 수 있다. 이후 장치는 어닐링되어 실리콘 내로 도핑이 이루어지고 그 결과 얇은 등각의 고농도 도핑된 영역(외부 확산 영역)이 형성된다. 예를 들어, NMOS 장치의 경우, 비소 도핑이 이용될 수 있다. 실리콘 게르마늄 내의 비소 확산도는 매우 높기 때문에, 이는 급속하게 실리콘 게르마늄 내로 재분배되고 에워싸는 실리콘 내로 고르게 외부 확산된다.

[0055] 이와 같이, 본 발명의 실시예들은 금속성 소스 및 드레인 영역들을 갖는 반도체 장치를 제조하기 위한 방법을 포함한다. 그러한 방법으로 형성된 구조는 종래의 구조에 비해 개선(저감)된  $R_{ext}$ 를 제공할 수 있다. 실험 결과는 희생 소스 및 드레인 영역들로부터의 외부 확산 도핑이 희생 소스 및 드레인 영역들의 제거 후에도 남아있음을 보여주었다. 외부 확산 영역들은  $R_{ext}$  이슈를 더 경감하는데 도움을 줄 수 있다.

- [0056] 도 4는 본 발명의 일 구현에 따른 컴퓨팅 장치(400)를 도시하고 있다. 컴퓨팅 장치(400)는 보드(402)를 수용하고 있다. 보드(402)는 프로세서(404) 및 적어도 하나의 통신 칩(406)(이들에 한정되지 않음)을 포함해서 다수의 컴포넌트를 포함할 수 있다. 프로세서(404)는 보드(402)에 물리적 전기적으로 연결된다. 몇몇 실시예들에서, 적어도 하나의 통신 칩(406)은 또한 보드(402)에 물리적 전기적으로 연결된다. 추가 실시예들에서, 통신 칩(406)은 프로세서(404)의 일부이다.

- [0057] 컴퓨팅 장치(400)는, 그의 응용에 따라서, 보드(402)에 물리적 전기적으로 연결될 수 있거나 연결되지 않을 수 있는 다른 컴포넌트들을 포함할 수 있다. 이들 다른 컴포넌트들은 휘발성 메모리(예로, DRAM), 비-휘발성 메모리(예로, ROM), 플래시 메모리, 그래픽 프로세서, 디지털 신호 프로세서, 암호 프로세서, 칩셋, 안테나, 디스플레이, 터치스크린 디스플레이, 터치스크린 제어기, 배터리, 오디오 코덱, 비디오 코덱, 전력 증폭기, GPS(global positioning system) 장치, 컴퍼스(compass), 가속도계, 자이ロ스코프, 스피커, 카메라, 및 대용량 저장 장치(예로, 하드 디스크 드라이브, 컴팩 디스크(CD), DVD(digital versatile disk) 등)를 포함하지만 이들에 한정되는 것은 아니다.

- [0058] 통신 칩(406)은 컴퓨팅 장치(400)와의 데이터 전달을 위한 무선 통신을 가능하게 한다. 용어 "무선" 및 그의 파생어는 비-고체 매체를 통한 변조된 전자기 방사의 이용을 통해서 데이터를 통신할 수 있는 회로, 장치, 시스템, 방법, 기법, 통신 채널 등을 기술하는데 이용될 수 있다. 이 용어는 연계된 장치들이 어떠한 배선도 포함하지 않음을 암시하지는 않지만, 일부 실시예에서는 그렇지 않을 수도 있다. 통신 칩(406)은 Wi-Fi(IEEE 802.11 계열), WiMAX(IEEE 802.16 계열), IEEE 802.20, 롱텀 에볼루션(LTE), Ev-DO, HSPA+, HSUPA+, EDGE, GSM, GPRS, CDMA, TDMA, DECT, 블루투스, 이들의 파생물은 물론이고 3G, 4G, 5G, 그 이상으로 표기되는 임의 다른 무선 프로토콜(이들에 한정되지 않음)을 포함해서 다수의 무선 표준 또는 프로토콜 중 임의 것을 구현할 수 있다. 컴퓨팅 장치(400)는 복수의 통신 칩(406)을 포함할 수 있다. 예를 들어, 제1 통신 칩(406)은 Wi-Fi 및 블루투스와 같은 단거리 무선 통신 전용일 수 있고, 제2 통신 칩(406)은 GPS, EDGE, GPRS, CDMA, WiMAX, LTE, Ev-DO 등과 같은 장거리 무선 통신 전용일 수 있다.

- [0059] 컴퓨팅 장치(400)의 프로세서(404)는 프로세서(404) 내에 패키지된 집적 회로 다이를 포함한다. 본 발명의 몇몇 실시예들에서, 프로세서의 집적 회로 다이는 본 발명의 구현에 따라 구축된 MOS-FET 트랜지스터들과 같은 1 이상의 장치를 포함한다. 용어 "프로세서"는 레지스터 및/또는 메모리로부터의 전자 데이터를 처리하여 그 전자 데이터를 레지스터 및/또는 메모리에 저장될 수 있는 다른 전자 데이터로 변환하는 임의의 장치 또는 장치의 일부를 나타낼 수 있다.

- [0060] 통신 칩(406)은 또한 통신 칩(406) 내에 패키지된 집적 회로 다이를 포함한다. 본 발명의 다른 구현에 따르면, 통신 칩의 집적 회로 다이는 본 발명의 구현에 따라 구축된 MOS-FET 트랜지스터와 같은 1 이상의 장치를 포함한다.

- [0061] 추가 구현들에서, 컴퓨터 장치(400) 안에 수용된 다른 컴포넌트는 본 발명의 구현에 따라 구축된 MOS-FET 트랜지스터와 같은 1 이상의 장치를 포함하는 집적 회로 다이를 포함할 수 있다.

- [0062] 다양한 구현에서, 컴퓨팅 장치(400)는 랩톱, 넷북, 노트북, 울트라북, 스마트폰, 태블릿, PDA(personal digital assistant), 울트라 모바일 PC, 모바일 폰, 데스크톱 컴퓨터, 서버, 프린터, 스캐너, 모니터, 셋-톱 박스, 엔터테인먼트 제어 유닛, 디지털 카메라, 휴대용 뮤직 플레이어, 또는 디지털 비디오 레코더일 수 있다. 추가 구현들에서, 컴퓨팅 장치(400)는 데이터를 처리하는 임의 다른 전자 장치일 수 있다.

- [0063] 이와 같이, 금속성 소스 및 드레인 영역들을 갖는 반도체 장치가 개시되었다. 한 실시예에서, 반도체 장치는 기판의 반전도 채널 영역 위에 배치된 게이트 전극 스택을 포함한다. 금속성 소스 및 드레인 영역들은 반전도 채널 영역의 양측에, 기판 위에 배치된다. 금속성 소스 및 드레인 영역들 각각은 프로필을 갖는다. 제1 반전도 외부 확산 영역은 반전도 채널 영역과 금속성 소스 영역 사이에, 그리고 금속성 소스 영역의 프로필에 등각을 이루도록, 기판 내에 배치된다. 제2 반전도 외부 확산 영역은 반전도 채널 영역과 금속성 드레인 영역 사이에, 그리고 금속성 드레인 영역의 프로필에 등각을 이루도록, 기판 내에 배치된다. 일 실시예에서, 금속성 소스 및 드레인 영역들은 각각 기판 위에 배치된 유전체 층 안에 배치된 대응하는 연속 접촉 구조 내에 포함된다.

도면

도면 1a

도면 1b

도면1bb

도면2a

도면2b

도면2c

도면2d

도면2e

도면2f

도면3a

도면3b

도면3c

#### 도면4