(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년06월02일

(11) 등록번호 10-1524527

(24) 등록일자 2015년05월26일

(51) 국제특허분류(Int. Cl.)

G11B 5/187 (2006.01)

(21) 출원번호 10-2013-0147612

(22) 출원일자 2013년11월29일

심사청구일자 2013년11월29일

(65) 공개번호 10-2014-0070469

(43) 공개일자 2014년06월10일

(30) 우선권주장

13/689,337 2012년11월29일 미국(US)

(56) 선행기술조사문현

JP2011227987 A

US08120874 B2

(73) 특허권자

시게이트 테크놀로지 엘엘씨

미국 캘리포니아 95104 쿠퍼티노 사우쓰 디 엔자

블리바드 10200

(72) 발명자

린빌, 에릭 쉐인

미국 55379 미네소타 새코피 원체스터 애비뉴 735

수, 지엔화미국 55311 미네소타 메이플 그로브 66 플레이스

노스 16941

(뒷면에 계속)

(74) 대리인

특허법인 남엔드남

전체 청구항 수 : 총 10 항

심사관 : 권영학

(54) 발명의 명칭 테이퍼링된 측면 실드 측벽들을 갖는 데이터 기록기

**(57) 요약**

데이터 기록기는 일반적으로 리딩 및 트레일링 에지들을 접속하는 연속하는 제 1 테이퍼 각도 및 폴 측벽을 갖는 기록 폴로 적어도 구성될 수 있다. 기록 폴은 기록 폴 및 측면 실드 사이의 가장 가까운 포인트인 실드 텁에 테이퍼링된 제 1 및 제 2 실드 측벽들로 구성된 측면 실드에 인접하게 위치될 수 있다.

**대 표 도 - 도1**

(72) 발명자

메로체, 에릭 로저

미국 55337 미네소타 번스빌 홀리 레인 1101

인, 후아킹

미국 55347 미네소타 에덴 프레리 산디 포인트 로드 12600

천, 용화

미국 55431 미네소타 블루밍턴 모르간 씨클 10548

## 명세서

### 청구범위

#### 청구항 1

대향하는 제 1 및 제 2 폴 측벽들을 가지는 기록 폴을 포함하는 장치로서,

상기 제 1 및 제 2 폴 측벽들은 각각 연속적인 제 1 테이퍼 각으로 연장되어 에어 베어링 표면(ABS) 상에서 리딩(leading) 에지 및 트레일링(trailing) 에지를 연결시키고,

상기 리딩 및 트레일링 에지들은 상기 기록 폴을 통해 연장하는 길이 방향 축에 의해 이등분 되고, 상기 제 1 및 제 2 폴 측벽들은 상기 길이 방향 축을 중심으로 대칭적으로 정렬되며,

상기 기록 폴은 상기 ABS 상에서 실드 팁(shield tip)에 테이퍼링되는(tapered) 제 1 및 제 2 실드 측벽들로 구성된 측면 실드에 인접하고,

상기 제 1 및 제 2 실드 측벽들은 상기 길이 방향 축에 평행하지 않으며,

상기 실드 팁은 상기 리딩 및 트레일링 에지들 사이에 위치되고,

상기 실드 팁은 상기 ABS 상에서 상기 기록 폴 및 상기 측면 실드 사이의 가장 가까운 포인트인,

장치.

#### 청구항 2

삭제

#### 청구항 3

제 1 항에 있어서,

상기 제 1 및 제 2 실드 측벽들은 상기 길이 방향 축에 대하여 대향 각도들로 상기 실드 팁으로부터 연장되는,

장치.

#### 청구항 4

삭제

#### 청구항 5

제 1 항에 있어서,

상기 제 1 및 제 2 실드 측벽들은 상기 길이 방향 축에 대하여 상이한 제 2 테이퍼 각도 및 제 3 테이퍼 각도로

상기 실드 팁으로부터 연장되는,

장치.

#### 청구항 6

삭제

#### 청구항 7

삭제

#### 청구항 8

삭제

### 청구항 9

삭제

### 청구항 10

삭제

### 청구항 11

대향하는 제 1 및 제 2 폴 측벽들을 가지는 기록 폴을 포함하는 자기 엘리먼트로서,

상기 제 1 및 제 2 폴 측벽들은 각각 연속적인 제 1 테이퍼 각으로 연장되어 에어 베어링 표면(ABS) 상에서 리딩(leading) 에지 및 트레일링(trailing) 에지를 연결시키고,

대향하는 상기 제 1 및 제 2 폴 측벽들은 상기 리딩 및 트레일링 에지들을 이등분하는 상기 기록 폴의 길이 방향 축을 중심으로 대칭적이고,

상기 기록 폴은 상기 ABS 상에서 실드 팁(shield tip)에 테이퍼링되는(tapered) 제 1 및 제 2 실드 측벽들로 각각 구성된 제 1 및 제 2 측면 실드들로부터 분리되고, 상기 제 1 및 제 2 측면 실드들 사이에 배치되고,

상기 제 1 및 제 2 측면 실드들의 각각의 실드 팁은 상기 리딩 및 트레일링 에지들 사이에 위치되고, 상기 ABS 상에서 상기 기록 폴 및 관련된 측면 실드 사이의 가장 가까운 포인트이며,

상기 제 1 및 제 2 측면 실드들 각각의 제 1 실드 측벽들은 상기 길이 방향 축에 평행하지 않은,

자기 엘리먼트.

### 청구항 12

제 11 항에 있어서,

상기 제 1 및 제 2 측면 실드들은 상이한 총수의 실드 측벽들을 갖는,

자기 엘리먼트.

### 청구항 13

제 11 항에 있어서,

상기 측면 실드들 중 적어도 하나는 상이한 자기 모멘트들을 갖는 다수의 총들을 포함하는,

자기 엘리먼트.

### 청구항 14

제 13 항에 있어서,

상기 다수의 총들은 상이한 두께들을 갖는,

자기 엘리먼트.

### 청구항 15

제 13 항에 있어서,

상기 다수의 총들 중 제 1 총은 제 1 자기 모멘트를 갖고, 상기 리딩 에지 근위에 위치되고, 상기 제 1 자기 모멘트는 상기 다수의 총들 중 제 2 총의 제 2 자기 모멘트보다 더 큰,

자기 엘리먼트.

### 청구항 16

삭제

**청구항 17**

제 11 항에 있어서,

상기 제 1 및 제 2 측면 실드들 중 적어도 하나의 제 2 실드 측벽은 상기 리딩 에지로부터 다운트랙의 평면으로 연장되는,

자기 엘리먼트.

**청구항 18**

삭제

**청구항 19**

삭제

**청구항 20**

제 11 항에 있어서,

상기 제 1 및 제 2 측면 실드들 각각의 제 2 실드 측벽은 상기 길이 방향 축에 평행하지 않고, 또한 수직하지도 않은,

자기 엘리먼트.

**발명의 설명****기술 분야**

[0001] 다양한 실시예들은 일반적으로 높은 데이터 비트 밀도 데이터 저장 환경들에서 사용될 수 있는 데이터 기록기에 관한 것이다.

**발명의 내용**

[0002] 다양한 실시예들에 따라, 기록 폴(write pole)은 폴 측벽(sidewall) 및 리딩 및 트레일링 에지들을 접속하는 연속 제 1 테이퍼 각도를 가질 수 있다. 기록 폴은, 기록 폴 및 측면 실드 사이의 가장 가까운 포인트인 실드 텁에 테이퍼링되는 제 1 및 제 2 실드 측벽들로 구성된 측면 실드에 인접하게 위치될 수 있다.

**도면의 간단한 설명**

[0003] 도 1은 다양한 실시예들에 따라 구성 및 동작되는 예시적인 데이터 저장 디바이스의 상면 블록도.

도 2는 도 1의 데이터 저장 디바이스에서 사용될 수 있는 예시적인 자기 엘리먼트의 단면 블록도.

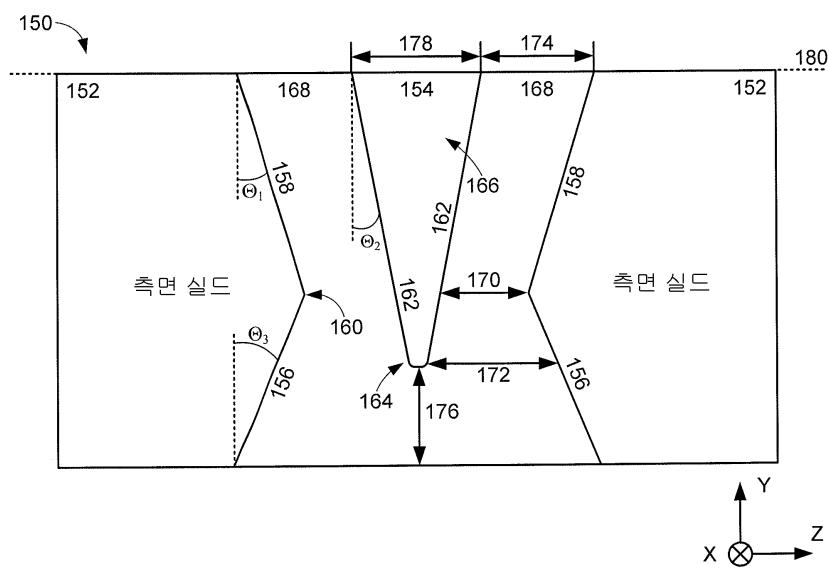

도 3은 일부 실시예들에 따라 구성된 예시적인 자기 엘리먼트의 부분의 ABS 뷰 블록도.

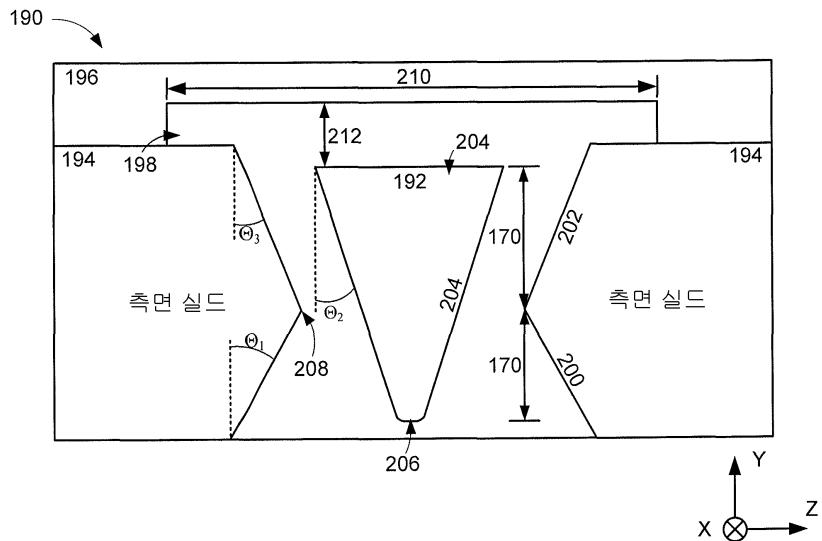

도 4는 다양한 실시예들에 따라 구성된 예시적인 자기 엘리먼트의 부분의 ABS 뷰 블록도.

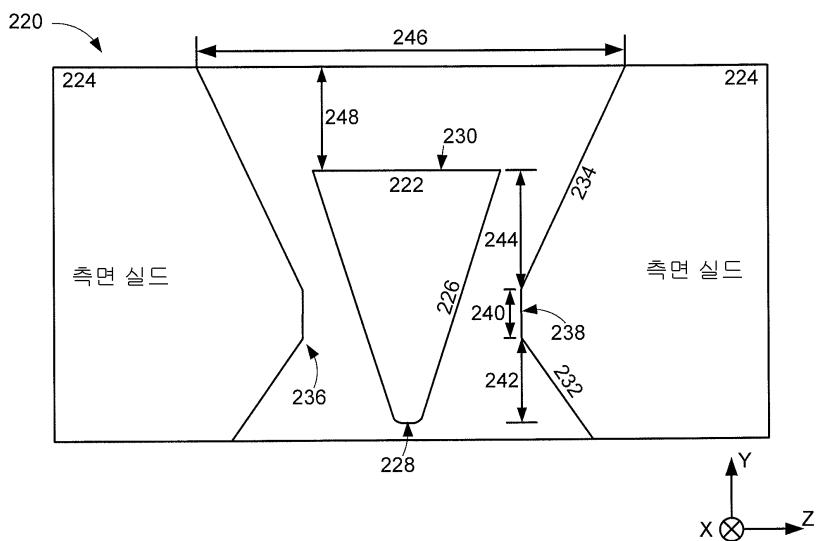

도 5는 다양한 실시예들에 따라 구성된 예시적인 자기 엘리먼트의 부분의 ABS 뷰 블록도.

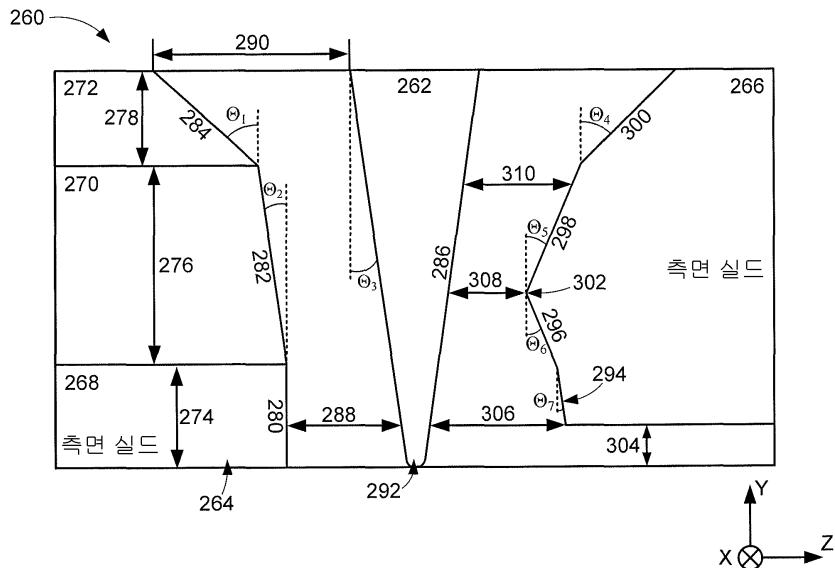

도 6은 일부 실시예들에 따라 구성된 예시적인 자기 엘리먼트의 부분의 ABS 뷰 블록도.

도 7은 다양한 실시예들에 따라 구성된 예시적인 자기 엘리먼트 제조 루틴에 대한 흐름도.

**발명을 실시하기 위한 구체적인 내용**

[0004] 데이터 저장 디바이스들이 더 큰 데이터 용량 및 더 빠른 데이터 액세스 레이트들을 향해 진보함에 따라, 다양한 디바이스 컴포넌트들의 물리적 크기 및 허용 오차들이 감소되기 때문에, 잘못된 자속의 자기 실딩은 제조 및 동작 성능 장애들의 중대한 소스가 되고 있다. 데이터 비트들이 파풀레이팅되는 데이터 트랙들의 최소화가 인접 트랙 간섭(ATI)의 형태의 특정 동작 장애를 제기할 수 있지만, 기록 폴 및 자기 저항 적층물과 같은 자기 액세스 피쳐에 인접하게 측면 자기 실드들을 위치시키는 것은 액세스 피쳐의 자기 규모를 감소시킴으로써 ATI를 완화할 수 있다. 그러나, 자기 실드들이 자기 액세스 피쳐에 대해 의도된 자화로 인해 포화되기 때문에, 측면

자기 실드들의 부가는 자기장 및 자기 경사도(magnetic gradient) 손실이 발생할 수 있다. 따라서, 자기장 및 경사도를 감소시키지 않고 감소된 폼 팩터(form factor) 데이터 저장 디바이스들로 구현될 수 있는 자기 실드 구성들에 대한 계속적인 산업 요구가 존재한다.

[0005] 따라서, 다양한 실시예들은 일반적으로 폴 측벽 및 리딩 및 트레일링 에지들을 접속하는 연속적인 제 1 테이퍼 각도를 갖는 기록 폴로 자기 엘리먼트를 구성하는 것에 관한 것일 수 있고, 기록 폴 및 측면 실드 사이의 가장 가까운 포인트인 실드 텁에 테이퍼링된 제 1 및 제 2 실드 측벽들로 구성된 측면 실드에 인접하게 위치된다. 기록 폴에 관련하여 실드 텁으로부터 실드 측벽들의 각도 배향 및 실드 텁의 위치는 미리 결정된 자기 규모를 제공하도록 선택적으로 튜닝될 수 있다. 그러한 튜닝된 자기 실드 구성들은 데이터 비트 액세스에 기여하는 대신에 실드들을 포화시키는 자속을 부가적으로 완화할 수 있다.

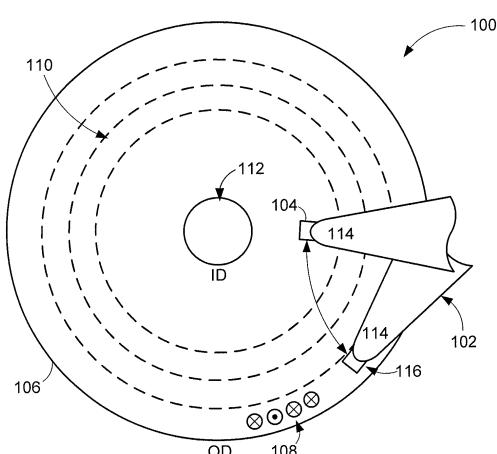

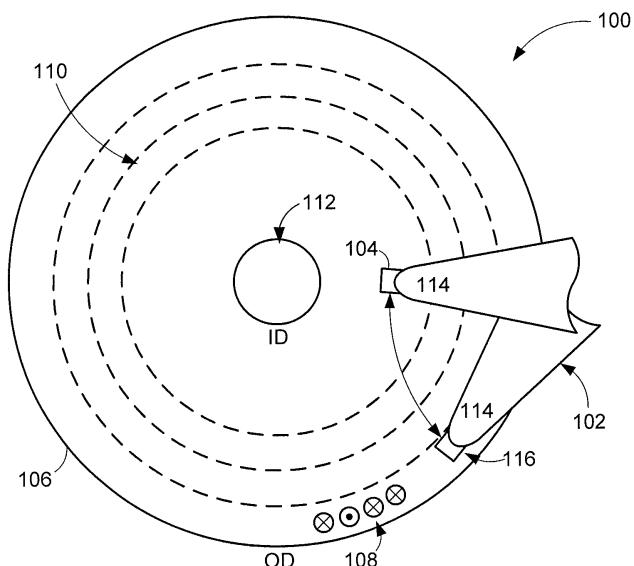

[0006] 적어도 하나의 튜닝된 자기 실드가 비제한적인 다양한 환경들에서 실시될 수 있지만, 도 1은 일반적으로 다양한 실시예들에 따라 튜닝된 자기 엘리먼트를 사용할 수 있는 예시적인 데이터 저장 디바이스(100)의 상면 블록도를 예시한다. 작동 어셈블리(102)가 저장된 데이터 비트들(108)이 미리 결정된 데이터 트랙들(110) 상에 위치되는 자기 매체들(106) 상의 다양한 위치들 위에 트랜스듀싱 헤드(104)를 위치시킬 수 있는 비제한적인 구성으로 데이터 저장 디바이스(100)가 도시된다. 저장 매체들(106)은, 트랜스듀싱 헤드(104)를 포함하는 헤드 짐벌(gimbal) 어셈블리(HGA)(116)를 매체들(106)의 미리 결정된 부분 위에 위치시키기 위해 작동 어셈블리(102)의 슬라이더 부분(114)이 비행하는 에어 베어링 표면(ABS)을 생성하기 위해 사용 동안에 회전하는 하나 이상의 스판들 모터들(112)에 부착될 수 있다.

[0007] 트랜스듀싱 헤드(104)는 자기 기록기, 자기 응답 판독기, 및 자기 실드들과 같은 하나 이상의 트랜스듀싱 엘리먼트들로 구성될 수 있고, 트랜스듀싱 엘리먼트들은 각각 저장 매체들(106)의 선택된 데이터 트랙들(110)로부터 데이터를 판독 및 프로그래밍하도록 동작한다. 이러한 방식으로, 작동 어셈블리(102)의 제어된 모션은 데이터를 기록, 판독 및 재기록하기 위해 저장 매체들 표면들 상에 정의된 데이터 트랙들(110)과 트랜스듀서들의 정렬에 대응한다. 데이터 비트들(108)이 더 작은 반경 폭들을 갖는 데이터 트랙들(100)에 더 조밀하게 위치하게 됨에 따라, 헤드(104)는 인접한 데이터 트랙들(110) 상의 데이터 비트들로부터 자속을 부주의하게 수신할 수 있고, 이것은 데이터 저장 디바이스(100)의 성능을 저하시키는 자기 잡음 및 간섭을 유도할 수 있다.

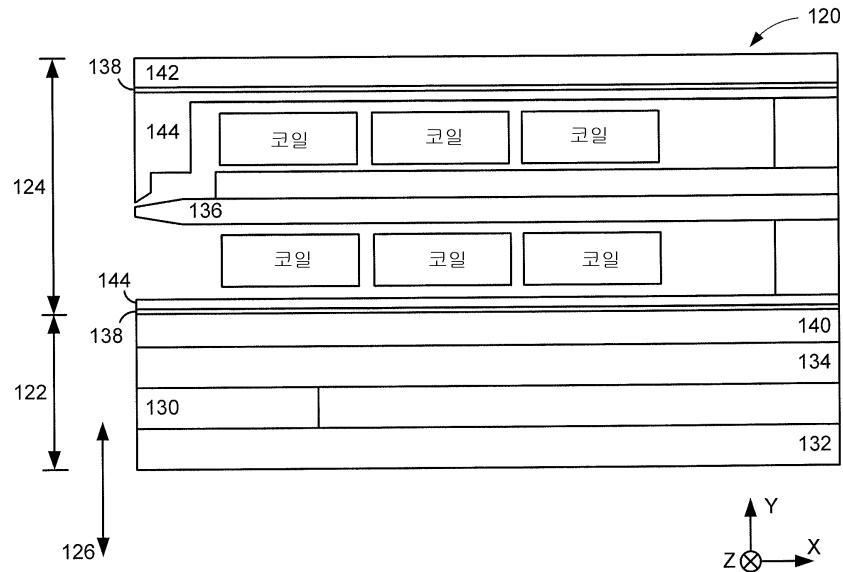

[0008] 도 2는 감소된 폼 팩터 데이터 트랙들 및 더 조밀하게 패킹된 데이터 비트들의 효과들을 완화시키기 위해 자기 실딩으로 구성된 예시적인 자기 엘리먼트(120)의 단면 블록도를 디스플레이한다. 도시된 바와 같이, 자기 엘리먼트(120)는, 도 1의 매체들(106)과 같은 인접한 저장 매체들에 데이터를 기록하거나 이로부터 데이터를 리트리브(retrieve)하도록 개별적으로 또는 동시에 동작할 수 있는 자기 판독기(122) 및 기록기(124)와 같은 하나 이상의 데이터 액세스 엘리먼트들을 포함할 수 있다. 각각의 자기 엘리먼트(122 및 124)는, 데이터 트랙(126)을 따라 대응하는 데이터 매체로부터 데이터를 판독하고 이에 데이터를 기록하도록 작동하는 다양한 실드들 및 트랜스듀싱 엘리먼트로 구성된다.

[0009] 자기 판독 엘리먼트(122)는 리딩 및 트레일링 실드들(132 및 134) 사이에 배치된 자기 저항층(130)을 갖는다. 한편, 기록 엘리먼트(124)는 미리 결정된 자기 배향을 인접한 저장 매체들에 전해주기 위해 기록 회로를 생성하는 적어도 하나의 리턴 폴(138) 및 기록 폴(136)을 갖는다. 도 2에 도시된 기록 엘리먼트(124)의 비제한적인 구성에서, 2 개의 리턴 폴들(138)은 각각, 폴들(136 및 138)로부터의 자속이 기록 엘리먼트(124)의 바운드들을 넘어 확장하는 것을 방지하는 각각 접촉하게 인접한 비자기 캡 층(140) 및 트레일링 실드(142)이다. 각각의 리턴 폴(138)은 기록 폴들(136 및 138)의 자기 분리를 유지하는 절연 물질(144)과 추가로 접촉한다.

[0010] 자기 엘리먼트(120)의 실드들은 도 1의 비트들(108)과 같은 직면한(encountering) 외부 비트들의 타이밍에 관련하여 그들의 위치를 특징으로 할 수 있다. 다시 말해서, 트랜스듀싱 엘리먼트들(122 및 124) 전에 외부 비트들과 직면하는 실드들은 "리딩" 실드들이고, 반면에 트랜스듀싱 엘리먼트들 후에 비트들을 보는 실드들은 "트레일링" 실드들이다. 그러한 특징화는, 자기 엘리먼트(120) 및 외부 비트들에 대한 이동의 방향에 의존하여, 실드들이 리딩 또는 트레일링 중 어느 하나 및 업트랙 또는 다운트랙 중 어느 하나일 수 있다는 점에서 트랜스듀싱 엘리먼트들의 "업트랙" 또는 "다운트랙" 사이의 차이로 확장된다.

[0011] 자기 엘리먼트(120)는 자속이 업트랙 및 다운트랙 자기 비트들에 도달하는 것을 일으시키는 Y 축을 따라 위치된 복수의 실드 층들을 갖지만, 증가된 데이터 비트 밀도들은 Z 축을 따라 부가적인 실딩에 대응하는 더 빽빽한 데이터 트랙들(126)을 초래하였다. 기록 폴(136)에 관련하여 Z 축에서 측면 실드들의 부가는 감소된 데이터 트랙(126) 폭에 맞추기 위해 기록 폴(136)의 자기 규모에 부응할 수 있지만, 자화가 기록 폴을 통해 흐르는 대신에 측면 실드들을 포화시키기 때문에, 그러한 부가는 자기장 진폭 및 경사도를 감소시킬 수 있다. 자기장에서의

감소는 기록 풀(136)의 자기 민감도 및 데이터 프로그래밍 효율을 동작적으로 감소시킬 수 있고, 이것은 기록 풀이 인접한 데이터 트랙들(126)의 데이터 비트들을 부주의로 프로그래밍하기 때문에 저하된 선형 데이터 비트 밀도 용량 및 증가된 측면 트랙 소거 기회들을 초래할 수 있다.

[0012] 도 3은 다양한 실시예들에 따라 기록 풀(154)의 대향 측면들 상에서 튜닝된 측면 실드들(152)을 사용하는 예시적인 자기 엘리먼트(150)의 부분의 ABS 뷰 블록도를 제공한다. 각각의 측면 실드(152)는 실드 텁(160)에 테이퍼링된 제 1 실드 측벽(156) 및 제 2 실드 측벽(158)으로 구성되고, 한편 기록 풀(154)은 풀 바디(166)로부터 업트랙에 위치된 풀 텁(164)에 테이퍼링된 풀 측벽들(162)을 갖는다. 도 3은 일반적으로, 자기 엘리먼트(150)의 바닥 부분이 업트랙이고 엘리먼트(150)의 상부 평면에서 다운트랙 부분 전에 데이터 비트와 직면할 미리 결정된 트랙과 정렬되는 것으로 예시한다는 것이 이해되어야 한다.

[0013] 풀 측벽(162) 각도( $\Theta_2$ )와 매칭시키기 위해 실드 측벽(158) 각도( $\Theta_1$ )를 구성함으로써 풀 바디(166)로부터 풀 텁(164)까지의 균일한 기록 캡(168)을 갖는 측면 실드들(152)을 구성하는 것은 기록 풀(154)에 대해 제어된 자기 규모를 제공할 수 있지만, 기록 풀(154)을 통해 전송되는 대신에 측면 실드들(152)을 포화시키기 위해 자속에 대한 도관을 제공할 수 있다. 그러한 자기에 관하여 고려해볼 때, 하나 이상의 측면 실드(152)는, 도시된 바와 같이, 실드 텁(160)이 기록 풀(154) 및 측면 실드(152) 사이의 가장 가까운 포인트에 있도록 구성될 수 있다. Y 축을 따라 실드 텁(160)의 수직 위치 및 각각의 실드 측벽들(156 및 158)의 테이퍼 각도들( $\Theta_1$  &  $\Theta_3$ )을 튜닝하기 위한 능력은, 기록 풀(154) 및 측면 실드들(152) 사이에 용이한 자기 도관들을 제공하지 않고 기록 풀(154)의 자기 규모를 제어할 수 있다.

[0014] 비제한적인 예로서, 각각의 측면 실드(152)는, 실드 텁(160)이 풀 텁(164) – 리딩 에지로서 특징될 수 있음 – 및 풀 바디(166) – 트레일링 에지로서 특징될 수 있음 – 사이에 위치되도록 구성될 수 있고, 실드 측벽들(156 및 158)은, 풀 측벽(162)으로부터 실드 텁(160)까지의 거리(170)가 풀 측벽(162)으로부터 제 1 실드 측벽(156) 또는 제 2 실드 측벽(158)까지의 거리(172 및 174) 중 하나보다 더 작도록 실드 텁(160)으로부터 상이한 방향들 및 각도들( $\Theta_1$  &  $\Theta_3$ )로 각각 연장된다. 다양한 실시예들은 측면 트랙 소거 및 인접한 트랙 간섭 모두를 감소시키도록 기록 풀(154)의 자기 규모를 구성하기 위해 거리(174)를 거리(170)의 두 배로 및 거리(172)보다 더 크게 튜닝한다.

[0015] 풀 텁(164) 근위에 프린지(fringe) 자기장들의 존재는 측면 트랙 소거 조건에서 인접한 데이터 트랙들의 부주의한 프로그래밍에 기여할 수 있다. 그러한 조건은, 풀 텁(164)으로부터 미리 결정된 거리(176) – 평면(180)에서 풀 바디(166)의 미리 결정된 폭(178)보다 더 클 수 있음 – 만큼 업트랙을 연장시키기 위해 적어도 실드 측벽들(156)의 길이를 조절함으로써 완화될 수 있다. 실드(156, 158) 및 풀 측벽들(162)의 테이퍼 각도들( $\Theta_1$ ,  $\Theta_2$ , &  $\Theta_3$ ) 및 실드 텁(160)의 위치와 같은 매우 다양한 튜닝 가능한 자기 엘리먼트 특성들을 사용하여, 기록 풀(154)의 자기 규모는, 특히, 감소된 폼 팩터, 높은 데이터 비트 밀도 저장 디바이스들에서 데이터 기록 성능을 증가시킬 수 있는 다수의 상이한 형상들로 조작될 수 있다.

[0016] 도 4는 일부 실시예들에 따라 다양한 구조적 피쳐들로 튜닝되는 예시적인 자기 엘리먼트(190)의 부분의 ABS 뷰 블록도를 예시한다. 자기 엘리먼트(190)는, 레터박스(198), 실드 측벽들(200 및 202) 및 풀 측벽들(204)과 같은 자기 규모 변경 피쳐들로 각각 구성된 측벽 실드들(194) 및 트레일링 실드(196) 사이에 배치된 기록 풀(192)을 갖는다. 기록 풀(192)은 선형 트레일링 에지(204) 및 만곡된 리딩 에지 풀 텁(206)으로 구성되고, 실드 텁(208)은 선형 트레일링 에지(204) 및 만곡된 리딩 에지 풀 텁(206) 사이에 위치되고, 실드 측벽들(200 및 202)은 선형 트레일링 에지(204) 및 만곡된 리딩 에지 풀 텁(206)으로부터 리딩(206) 및 트레일링(204) 에지를 의 바운드들을 넘어 각각의 측벽(200 및 202)을 취하는 길이들로 연장된다.

[0017] 도 3의 실드 및 풀 측벽들과 마찬가지로, 다양한 측벽들(200, 202 및 204)은 리딩 에지(206), 트레일링 에지(204) 및 실드 텁(208)에서 상이한 실드-투-풀 거리들을 허용하는 무제한의 다양한 각도들( $\Theta_1$ ,  $\Theta_2$ , &  $\Theta_3$ )로 튜닝될 수 있다. 다양한 측벽들의 튜닝된 각도들 및 측면 실드(194)와 기록 풀(192) 사이의 캡의 크기와 상관 없이, 기록 풀(192)로부터 다운트랙에 레터박스(198)의 포함은, 풀(192)로부터의 자속 손실을 최소화하면서 적절한 자기 실딩을 제공할 수 있고, 이것은 기록 필드 경사도, 진폭 및 이득을 증가시킨다. 레터박스(198)가 부분적으로 측면(194) 및 트레일링(196) 실드들로 형성되는 것으로 디스플레이되지만, 그러한 구성은 측면(194) 또는 트레일링(196) 실드들 중 어느 하나의 부분으로서 레터박스를 전체적으로 통합하기 위해, 마음대로, 변경될 수 있다.

[0018]

레터박스(198)의 위치 및 형상은 기록 폴(192)의 경사도 및 자기 실딩 및 기록 필드 이득 사이의 균형을 제공하기 위해 다양한 실시예들에서 튜닝될 수 있다. 즉, 기록 폴(198)로부터의 거리(212) 및 폭(210)은 기록 폴(192)에 대한 미리 결정된 실딩 및 자기 성능 특성들을 제공하기 위해, 연속적으로 곡선적 및 직사각형과 같은 전체 형상과 함께 튜닝될 수 있다. 튜닝된 레터박스(198)의 부가는, 표유 전계들(stray fields)이 적어도 기록 폴(192)에 가장 가까운 가장 긴 측벽을 갖는 튜닝된 실드 측벽들(200 및 202)에 의해 제공되는 형상 이방성(anisotropy)에 의해 감소되기 때문에 자기 오버슈트를 감소시킬 수 있다. 레터박스(198)는 측면 트랙 소거를 감소시키고 자기 전이 곡률을 증가시키기 위해 기록 폴(192)의 각각의 리딩(206) 및 트레일링(204) 에지들로부터 실드 텁(208)의 리딩(214) 및 트레일링(216) 거리에 의해 제공된 실드 텁(208)의 튜닝된 위치에 의해 보상될 수 있다.

[0019]

측면 실드들(194), 기록 폴(192) 및 레터박스(198)의 구성들이 기록 폴(192)의 선택된 위치들에 대해 미리 결정된 근접도로 실딩 물질을 위치시키고, 자기적으로 절연 물질이 실드들(194 및 196) 및 기록 폴(192) 사이에 배치되도록 허용할 수 있지만, 다양한 자기 엘리먼트(190) 컴포넌트들은, 최적화된 자기 기록 필드들을 제공하면서, 기록 폴(192)의 자기 규모를 조작하도록 형상, 물질, 크기 및 위치에 대해 추가로 튜닝될 수 있다. 도 5는 일반적으로 다양한 실시예들에 따라 튜닝된 예시적인 자기 엘리먼트(220)의 부분의 ABS 뷰 블록도를 디스플레이 한다. 자기 엘리먼트(220)는, 2 개보다 많은 실드 측벽들을 제공하기 위해 각각 튜닝되는 측면 실드들(224) 사이에 배치된 기록 폴(222)을 갖는다.

[0020]

도시된 바와 같이, 기록 폴(222)은 리딩(228) 및 트레일링(230) 에지들을 접속하는 대면 폴 측벽들(226)을 갖는 실질적으로 사다리꼴 형상을 갖는다. 각각의 측면 실드(224)는 텁 측벽(238)으로 구성되는 실드 텁(236)으로부터 미리 결정된 각도들로 테이퍼링하는 제 1 실드 측벽(232) 및 제 2 실드 측벽(234)으로 구성된다. 도 4의 실드 텁(208)과 비교하여, 실드 텁(236)은 2 개의 표면들의 포인트가 아니라 대신에 다른 실드 측벽들(232 및 234)을 접속하는 미리 결정된 길이(240)를 갖는 표면과 만난다. 텁 측벽(238)에 대한 선형 표면, 또는 대안적으로 일부 실시예들에서 연속적으로 곡선적 표면의 사용은, 기록 폴(222)과 측면 실드들(224) 사이의 기록 캡이 폴 측벽(226)에 관련하여 미리 결정된 거리들(242 및 244)에서 변동하도록 허용하는 또 다른 튜닝 가능한 구조적 표면을 제공한다.

[0021]

텅 측벽(238)의 형상 및 위치는, 실드 측벽들(232 및 234)이 포인트에서 만나는 경우에, 제 1 실드 측벽(232) 및 제 2 실드 측벽(234)이 실드 측벽들을 기록 폴(222)에 너무 가깝게 할 각도들로 테이퍼링 및 연장되도록 허용할 수 있다. 예를 들면, 텁 측벽(238)의 길이는 제 2 실드 측벽이, 텁 측벽(238)의 길이(240)가 존재하지 않는 경우보다 기록 폴(222)의 트레일링 에지(230)까지의 미리 결정된 거리를 제공하기 위해 더 적은 각도로 실드 텁(236)으로부터 연장되도록 허용할 수 있다. 그러한 더 적은 실드 측벽 각도들은, 일부 실시예들에서, 기록 폴(222)로부터 미리 결정된 다운트랙 거리(248)에 미리 결정된 측면 실드 폭(246)을 형성하기 위해 사용될 수 있고, 이것은 측면(224) 및/또는 트레일링 실드들로의 레터박스의 부가적인 제조 없이 레터박스형 기록 필드 이득 및 경사도 최적화를 생성할 수 있다.

[0022]

다양한 실드 및 폴 측벽들을 튜닝함으로써 가능한 매우 다양한 실딩 구성들은 기록 폴(222)의 대향 측면들 상의 미러링 구조들로 제한되지 않는다. 도 6은 일반적으로 예시적인 자기 엘리먼트(260)가 일부 실시예들에 따라 구성된 상이한 측면 실드(264 및 266) 구성들을 사용하여 기록 폴(262)의 자기 규모를 제어하도록 튜닝될 수 있는 방법을 예시한다. 자기 엘리먼트(260)의 ABS 뷰는 상이한 자기 실딩 특성들 및 구조적 배향들을 갖는 다수의 상이한 물질들의 적층으로서 구성된 제 1 측면 실드(264)를 디스플레이한다.

[0023]

도 6에 도시된 예에서, 제 1 측면 실드(264) 각각이 Y 축을 따라 상이한 두께들(274, 276 및 278) 및 폴 측벽(286)( $\Theta_3$ )에 관련하여 상이한 각도들( $\Theta_1$  &  $\Theta_2$ )로 배향된 상이한 실드 측벽들(280, 282 및 284)을 갖는 제 1 실드층(268), 제 2 실드층(270) 및 제 3 실드층(272)을 갖는다. 일부 실시예들은, 기록 폴(262)의 트레일링 에지와 측면 실드(264) 사이의 트레일링 거리(290)의 절반인 기록 폴(262)의 리딩 에지와 측면 실드(264) 사이의 리딩 거리(288)를 제공하기 위한 실드 측벽들(280, 282 및 284)을 구성한다. 트레일링 거리(290)의 절반으로서 리딩 거리(288)를 구성하는 것은 최소 인접 트랙 간섭에 대해 최적화된 기록 필드를 제공할 수 있다.

[0024]

제 1 측면 실드(264) 및 기록 폴(262) 사이의 증가하는 기록 캡은 상이한 자석 모멘트들을 나타내는 물질들의 사용에 의해 보완될 수 있다. 예를 들면, 제 1 층(268)은 2.4 테슬라와 같은 제 1 미리 결정된 모멘트로 구성될 수 있고, 반면에 제 2 층(270)은 1.4 테슬라와 같은 상이한 제 2 미리 결정된 모멘트를 갖고, 제 3 층(272)은 1.0 테슬라와 같은 상이한 제 3 미리 결정된 모멘트로 구성된다. 상이한 층들(268, 270 및 272)의 다양한 자기 모멘트들은, 표유 자기장들이 특히 리딩 폴 텁(292) 근위에서 제어되기 때문에 기록 필드 손실을 최소화할

수 있다. 기록 폴(262)에 대한 크기, 위치 및 다양한 측면 실드(264) 적층의 물질을 튜닝하기 위한 능력은, 기록 폴(262)의 자기 특성들 및 자기 규모의 정밀한 명료도(articulation)를 허용할 수 있는 부가적인 튜닝 양상을 제공한다.

[0025] 다수의 상이한 실드 층들(268, 270 및 272) 및 물질의 사용이 정밀한 튜닝 능력을 제공할 수 있지만, 부가적인 제조 복잡성 및 프로세싱은 적층된 측면 실드 구성의 효과들에 제거할 수 있다. 제 2 측면 실드(266)는, 단일 층 및 물질이 기록 폴(262) 및 제 2 측면 실드(266) 사이의 가장 가까운 포인트인 실드 텁(302)을 생성하기 위해 상이한 각도 배향들( $\Theta_4$ ,  $\Theta_5$ ,  $\Theta_6$ , &  $\Theta_7$ )로 구성된 복수의 실드 측벽들(294, 296, 298 및 300)로 구성될 수 있는 방법을 디스플레이한다.

[0026] 실드 텁(302)의 위치는 폴 측벽(286)의 임의의 미리 결정된 부분 근위에 위치될 수 있지만, 그러한 미리 결정된 부분은 측면 실드가 리딩 폴 텁(292)으로부터 다운트랙으로 평면을 연장시킬 때 기록 폴(262)의 트레일링 부분을 더 향할 수 있다. 즉, 실드 텁(302)의 위치는 측면 실드(266)가 연장되는 다운트랙 거리(304)에 응하여 선택될 수 있다. 그러한 다운트랙 거리(304)는 미리 결정된 인접 트랙 간섭 및 측면 트랙 소거 완화를 제공하기 위해 자기 실딩과 기록 필드 이득 및 경사도를 밸런싱하도록 리딩(306), 텁(308) 및 트레일링(310) 거리를 추가로 변경할 수 있다.

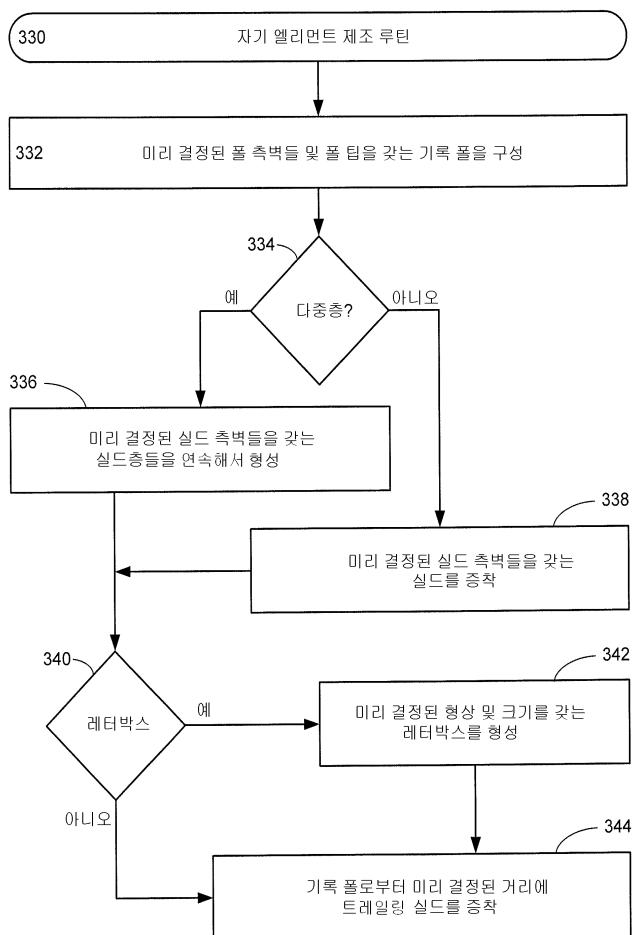

[0027] 기록 필드 및 데이터 비트 프로그래밍 성능을 최적화하기 위해 가능한 다양한 비제한적인 측면 실드 구성을 통해, 자기 엘리먼트의 구조는 자기 동작을 튜닝하기 위한 일련의 일반적 및 특정 결정들을 겪을 수 있다. 도 7은 자기 엘리먼트의 자기 기록 필드 성능 및 자기 실딩을 튜닝하기 위해 다양한 실시예들에 따라 실시되는 예시적인 자기 엘리먼트 제조 루틴(330)을 제공한다. 초기에, 루틴(330)은 단계(332)에서 미리 결정된 형상을 갖는 기록 폴, 측벽들 및 폴 텁을 구성한다.

[0028] 결정(334)은 측면 실드들 중 하나 또는 양자가 다중-층 적층으로서 구성되는지 여부를 결정한다. 복수의 상이한 측면 실드 층들이 결정(334)으로부터 활용되는 것이면, 단계(336)는 미리 결정적 물질들, 두께들 및 실드 측벽 각도 배향들을 갖는 각각의 측면 실드 층을 연속적으로 형성한다. 이와 대조적으로, 단계(338)는 단일 측면 실드 층을 증착하고, 그로부터 연장되는 미리 결정된 수의 실드 측벽들을 갖는 실드 텁을 형성한다. 다양한 실시예들은 기록 폴의 리딩 및 트레일링 에지들을 넘어 연장되도록 실드 측벽들을 구성하고, 다른 실시예들은 리딩 에지로부터 폴 측벽의 길이의 10 %, 30 % 또는 50 %와 같이 기록 폴의 미리 결정된 부분 근위에 실드 텁을 위치시킨다.

[0029] 기록 폴의 대향 측면들 상의 측면 실드들의 형성은 단계들(336 및 338) 중 어느 하나를 한번 또는 여러 번 수행함으로써 달성될 수 있다는 것이 유의되어야 한다. 기록 폴의 대향 측면들 상의 측면 실드들의 형성은, 도 4의 레터박스(198)와 같은 레터박스의 포함이 고려되는 결정(340)으로 루틴(330)을 진행시킨다. 단계(342)는 직사각형, 사다리꼴 및 직사각형 형상들과 같은 미리 결정된 형상, 미리 결정된 크기 및 기록 폴로부터의 미리 결정된 거리를 갖는 레터박스를 형성한다. 그러한 레터박스 구조는, 단계(344)에서 후속으로 증착되는 트레일링 실드 및 측면 실드들 중 하나 또는 양자의 프로세싱을 통합할 수 있다. 즉, 레터박스는 측면 또는 트레일링 실드들로 전체적으로 통합되거나, 측면 및 트레일링 실드들 양자에 의해 제공되는 표면들의 조합으로 구성될 수 있다.

[0030] 레터박스가 결정(340)에서 자기 엘리먼트에 통합되지 않는 경우에, 단계(344)는 내부 레터박스 개구를 형성하지 않고 기록 폴로부터 미리 결정된 거리에 트레일링 실드를 증착한다. 루틴(330)의 다양한 결정들 및 단계들을 통해, 자기 엘리먼트는 다양한 측면 실드 측벽들, 거리들 및 실드 텁 위치들의 튜닝된 구성을 통해 자기 실딩과 기록 필드 성능을 밸런싱함으로써 성능에 대해 최적화될 수 있다. 예를 들면, 실드 텁의 위치 및 테이퍼링된 실드 측벽들은, 측면 트랙 소거 및 인접한 트랙 간섭과 같은 부주의한 성능 특성들의 감소되거나 최소화된 위험과 조합하여 더 많거나 더 적은 자기 실딩을 제공하기 위해 기록 폴에 대해 다양한 위치들에서 구성될 수 있다.

[0031] 그러나, 도 7에 도시된 루틴(330)의 다양한 단계들 및 결정들이 생략, 변경 및 부가될 수 있기 때문에, 그 다양한 결정들 및 단계들이 요구되지 않거나 제한되지 않는다는 것이 유의되어야 한다. 예로서, 결정(334) 및 단계들(336 및 338)은 기록 폴의 대향 측면들 상에 위치된 측면 실드들을 구성하기 위해 유사한 또는 상이한 결과들로 여러 번 수행될 수 있다.

[0032] 미리 결정된 자기 실딩 및 데이터 비트 프로그래밍 성능을 제공하도록 튜닝될 수 있는 과다한 측면 실드 구조적 파라미터들은 기록 폴의 자기 규모를 제어할 수 있는 방대한 가능한 측면 실드 구성을 예시한다. 그러한 측

면 실드 구성을 갖는 고조된 자기장 성능을 제공하도록 튜닝될 수 있고, 반면에 다른 구성들은 잘못된 자기장들 및 측면 실드들의 자기 포화로부터 기인한 부주의한 성능 조건들을 최소화하도록 튜닝될 수 있다. 기록 폴에 관련하여 측면 실드들의 다양한 구조적 양상들을 튜닝함으로써 다양한 성능 특성들을 밸런싱하기 위한 능력은, 특히, 증가된 데이터 비트 밀도, 감소된 품 팩터 데이터 저장 디바이스들에 적응하는 것에 관련하여 측면 실드 구조의 다용성(versatility)을 전달한다.

[0033]

또한, 실시예들이 자기 프로그래밍에 관한 것이지만, 청구된 발명은 데이터 저장 디바이스 애플케이션들을 포함하는 임의의 수의 다른 애플리케이션들에서 용이하게 사용될 수 있다는 것이 인지될 것이다. 본 발명의 다양한 실시예들의 다수의 특성들 및 구성들이 다양한 실시예들의 구조 및 기능의 세부 사항들과 함께 앞선 설명에 제시되었지만, 이러한 상세한 설명은 단지 예시적이며, 특히 첨부된 청구항들이 표현되는 용어들의 폭넓은 일반적인 의미에 의해 표시되는 최대 범위로 본 발명의 원리를 내에서 부분들의 구조 및 배열들에 관하여 변화들이 상세히 이루어질 수 있다는 것이 이해될 것이다. 예를 들면, 특정 엘리먼트들은 본 기술의 범위 및 사상으로부터 벗어나지 않고 특정 애플리케이션에 의존하여 변동할 수 있다.

## 도면

### 도면1

도면2

도면3

도면4

도면5

## 도면6

## 도면7