(12) 发明专利

(10) 授权公告号 CN 114762113 B

(45) 授权公告日 2024.11.01

(21) 申请号 201980102690.2

(74) 专利代理机构 北京集佳知识产权代理有限公司 11227

(22) 申请日 2019.12.05

专利代理人 王海奇

(65) 同一申请的已公布的文献号

申请公布号 CN 114762113 A

(51) Int.CI.

H01L 27/04 (2006.01)

(43) 申请公布日 2022.07.15

(56) 对比文件

(85) PCT国际申请进入国家阶段日

CN 104752337 A, 2015.07.01

2022.06.01

JP 2009124667 A, 2009.06.04

(86) PCT国际申请的申请数据

审查员 袁芳

PCT/JP2019/047688 2019.12.05

(87) PCT国际申请的公布数据

W02021/111604 JA 2021.06.10

(73) 专利权人 株式会社索思未来

权利要求书3页 说明书15页 附图25页

地址 日本神奈川县

(72) 发明人 冈本淳 武野纮宣 王文桢

(54) 发明名称

半导体装置

(57) 摘要

半导体装置包括第1芯片以及第2布线层，第1芯片具有基板、形成在所述基板的第1面上的第1布线层，第2布线层形成在所述基板的所述第1面的相反侧的第2面上。所述第2布线层具有提供第1电源电位的第1电源线、提供第2电源电位的第2电源线、提供第3电源电位的第3电源线、连接于所述第1电源线与所述第2电源线之间的第1开关、设置在所述第1电源线或所述第3电源线的一方上的第2开关。所述第1芯片具有被设置在所述第1电源线与所述第3电源线之间的第1电路。

1.一种半导体装置,其特征在于,包括:

第1芯片,具有基板、形成在所述基板的第1面上的第1布线层;以及

第2布线层,形成在所述基板的所述第1面的相反侧的第2面上,

所述第2布线层包括:

第1电源线,提供第1电源电位;

第2电源线,提供第2电源电位;

第3电源线,提供第3电源电位;

第1开关,连接于所述第1电源线与所述第2电源线之间;以及

第2开关,被设置在所述第1电源线或所述第3电源线的一方上,

所述第1芯片具有被设置在所述第1电源线与所述第3电源线之间的第1电路。

2.根据权利要求1所述的半导体装置,其特征在于,

所述第2开关被设置在所述第1电源线上。

3.根据权利要求1所述的半导体装置,其特征在于,

所述第2开关包括:

第1端子,位于所述第1电路侧;以及

第2端子,位于所述第1端子的相反侧,

所述第1芯片包括第2电路,所述第2电路连接于所述第2端子与所述第1电源线或所述第3电源线的另一方之间。

4.根据权利要求3所述的半导体装置,其特征在于,

所述第2电路包括:

第1控制缓冲器,控制所述第1开关;以及

第2控制缓冲器,控制所述第2开关。

5.根据权利要求1所述的半导体装置,其特征在于,

所述第2布线层包括:

第4电源线,提供第4电源电位;

第3开关,连接于所述第3电源线与所述第4电源线之间;以及

第4开关,被设置在所述第1电源线或所述第3电源线的另一方上,

所述第1电路连接于所述第4电源线与所述第2电源线之间。

6.根据权利要求1所述的半导体装置,其特征在于,

所述第2布线层包括:

第4电源线,提供第4电源电位;

第3开关,连接于所述第3电源线与所述第4电源线之间;以及

第4开关,被设置在所述第1电源线或所述第3电源线的另一方上,

所述第1电路连接于所述第4电源线与所述第2电源线之间,

所述第2开关包括:

第1端子,位于所述第1电路侧;以及

第2端子,位于所述第1端子的相反侧,

所述第4开关包括:

第3端子,位于所述第1电路侧;以及

第4端子，位于所述第3端子的相反侧，

所述第1芯片具有连接于所述第2端子与所述第4端子之间的第2电路。

7. 根据权利要求6所述的半导体装置，其特征在于，

所述第4开关被设置在所述第3电源线上，

所述第2开关被设置在所述第1电源线上。

8. 根据权利要求6所述的半导体装置，其特征在于，

所述第2电路包括：

第1控制缓冲器，控制所述第1开关；

第2控制缓冲器，控制所述第2开关；

第3控制缓冲器，控制所述第3开关；以及

第4控制缓冲器，控制所述第4开关。

9. 根据权利要求1所述的半导体装置，其特征在于，

所述第3电源线是提供接地电位的接地布线。

10. 根据权利要求1所述的半导体装置，其特征在于，

所述第1电源线具有第1布线以及第2布线，

所述第2电源线具有第3布线，

所述第2开关被设置在所述第1布线与所述第2布线之间，

所述第1开关被设置在所述第2布线与所述第3布线之间。

11. 根据权利要求10所述的半导体装置，其特征在于，

所述第1布线以及所述第2布线在俯视下沿着第1方向延伸，

多个所述第2开关沿着所述第1方向配置。

12. 根据权利要求11所述的半导体装置，其特征在于，

所述第2布线以及所述第3布线在俯视下沿着所述第1方向延伸，

多个所述第2布线与所述第3布线在俯视下沿着与所述第1方向不同的第2方向交替配置，

多个所述第1开关被配置在所述第2布线与所述第3布线之间。

13. 根据权利要求12所述的半导体装置，其特征在于，

所述第3电源线具有被配置在所述第1布线、所述第2布线以及所述第3布线的上方，并在俯视下沿着所述第2方向延伸的第4布线，

所述第1电源线具有连接于所述第1布线并被配置在所述第1布线的上方，并在俯视下沿着所述第2方向延伸的第5布线，

所述第2电源线具有连接于所述第3布线并被配置在所述第2布线以及所述第3布线的上方，并在俯视下沿着所述第2方向延伸的第6布线，

所述第5布线沿着所述第2方向被配置在所述第6布线的延长线上。

14. 根据权利要求10所述的半导体装置，其特征在于，

所述第1布线在俯视下围绕着包含所述第1电路的第1区域配置，

所述第2布线的至少一部分在俯视下与所述第1区域重叠配置。

15. 根据权利要求1至14中的任一项所述的半导体装置，其特征在于，

所述第2布线层具有彼此叠层的多个子布线层，

所述第2开关被设置在所述多个子布线层。

## 半导体装置

### 技术领域

[0001] 本发明涉及一种半导体装置。

### 背景技术

[0002] 半导体装置包含各种电路区域,作为电路区域之一例有标准单元区域。标准单元区域包含各种逻辑电路。向半导体装置提供VDD的电源电位时,标准单元区域的逻辑电路被提供VVDD的电源电位,有时在VDD的电源线与VVDD的电源线之间连接晶体管等的开关。

[0003] 开关进行对逻辑电路的晶体管提供VVDD电源电位的开/关切换。通过使用电路,在无需使逻辑电路动作的时候可切断电源供给,抑制在构成逻辑电路的晶体管中产生的漏电流,降低消耗电力。

[0004] 另外,已有人提出在主半导体芯片的背面贴合包含布线的从属半导体芯片,通过从属半导体芯片的布线向主半导体芯片的晶体管提供电源电位的技术。这种技术也被称为BS-PDN (backside-power delivery network)。

[0005] <现有技术文献>

[0006] <专利文献>

[0007] 专利文献1:美国专利申请公开第2015/0162448号说明书

[0008] 专利文献2:美国专利第9754923号说明书

[0009] 专利文献3:美国专利申请公开第2018/0145030号说明书

[0010] 专利文献4:美国专利第8530273号说明书

[0011] 专利文献5:(日本)专利第6469269号公报

### 发明内容

[0012] <本发明要解决的问题>

[0013] 目前为止,关于在包含布线的从属半导体芯片内设置开关时的具体结构,尚未进行详细的研究。

[0014] 本发明的目的在于提供一种能够适当地设置开关的半导体装置。

[0015] <用于解决问题的手段>

[0016] 本公开的技术所涉及的半导体装置包括第1芯片以及第2布线层,所述第1芯片具有基板以及形成在所述基板的第1面上的第1布线层,所述第2布线层形成在所述基板的所述第1面的相反侧的第2面上,所述第2布线层包括提供第1电源电位的第1电源线、提供第2电源电位的第2电源线、提供第3电源电位的第3电源线、连接于所述第1电源线与所述第2电源线之间的第1开关、设在所述第1电源线或所述第3电源线的一方上的第2开关,所述第1芯片具有设在所述第1电源线与所述第3电源线之间的第1电路。

[0017] <发明的效果>

[0018] 根据本发明的技术,能够适当地设置开关。

## 附图说明

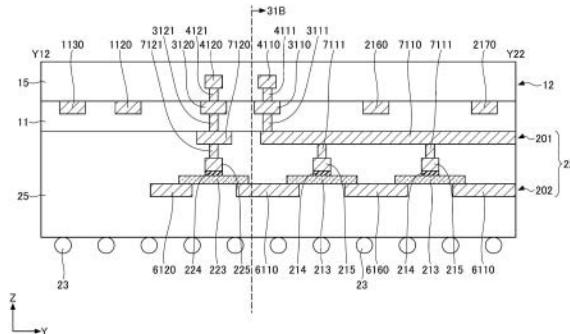

- [0019] 图1是表示本发明所适用的半导体装置的概要的剖面图。

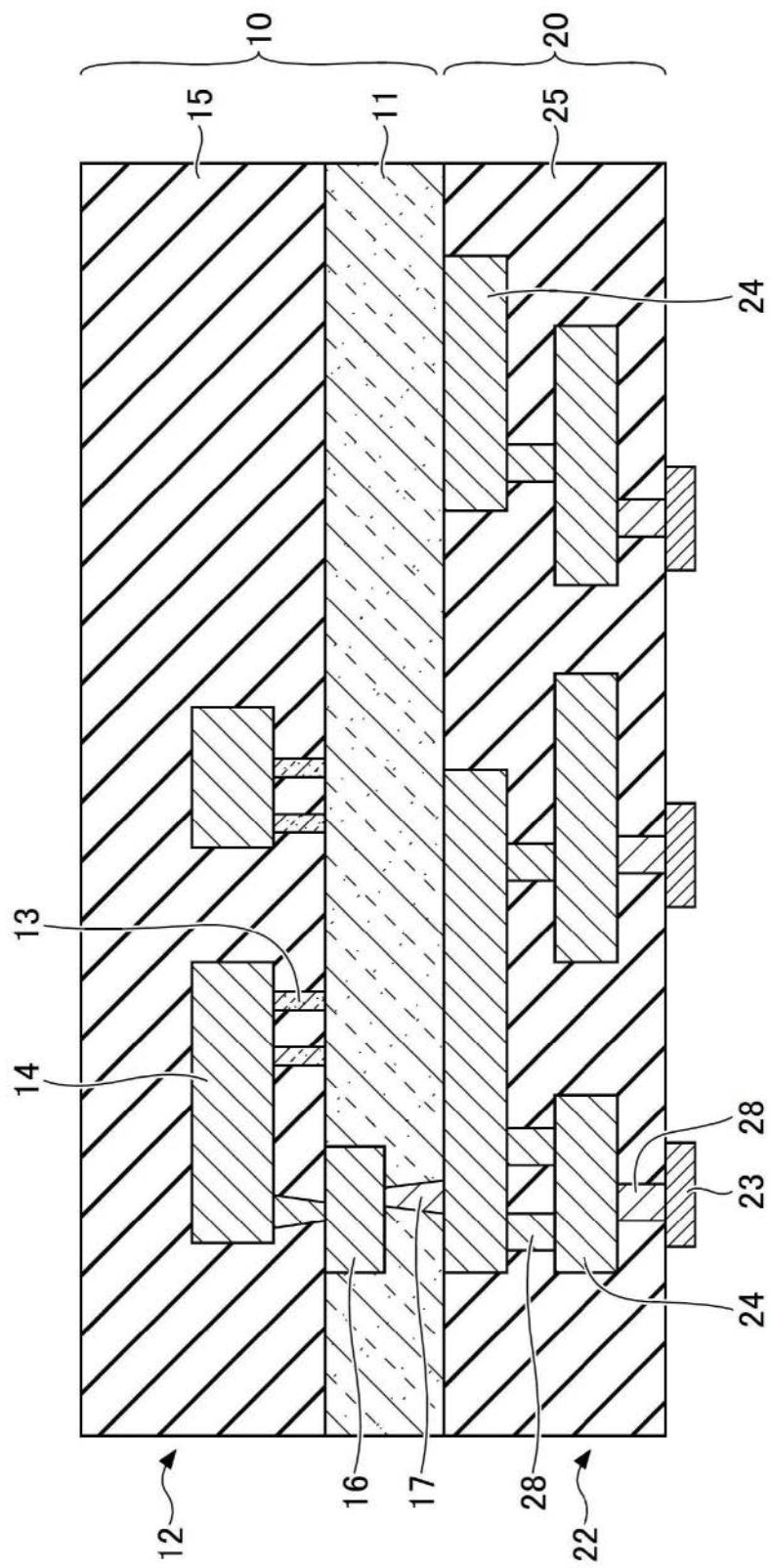

- [0020] 图2是表示第1芯片的布局的图。

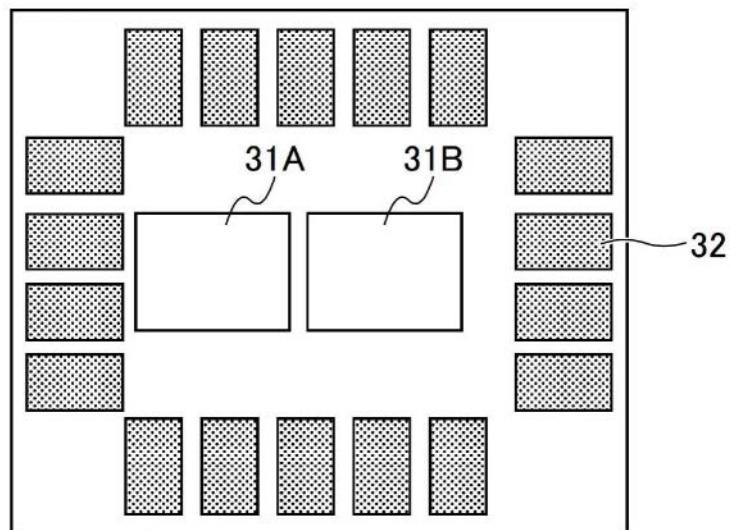

- [0021] 图3是表示半导体装置所包含的电路的一例的结构的电路图。

- [0022] 图4是表示缓冲器的结构的电路图。

- [0023] 图5是表示缓冲器的一例的平面结构的模式图。

- [0024] 图6是表示逆变器的结构的电路图。

- [0025] 图7是表示逆变器的平面结构的模式图。

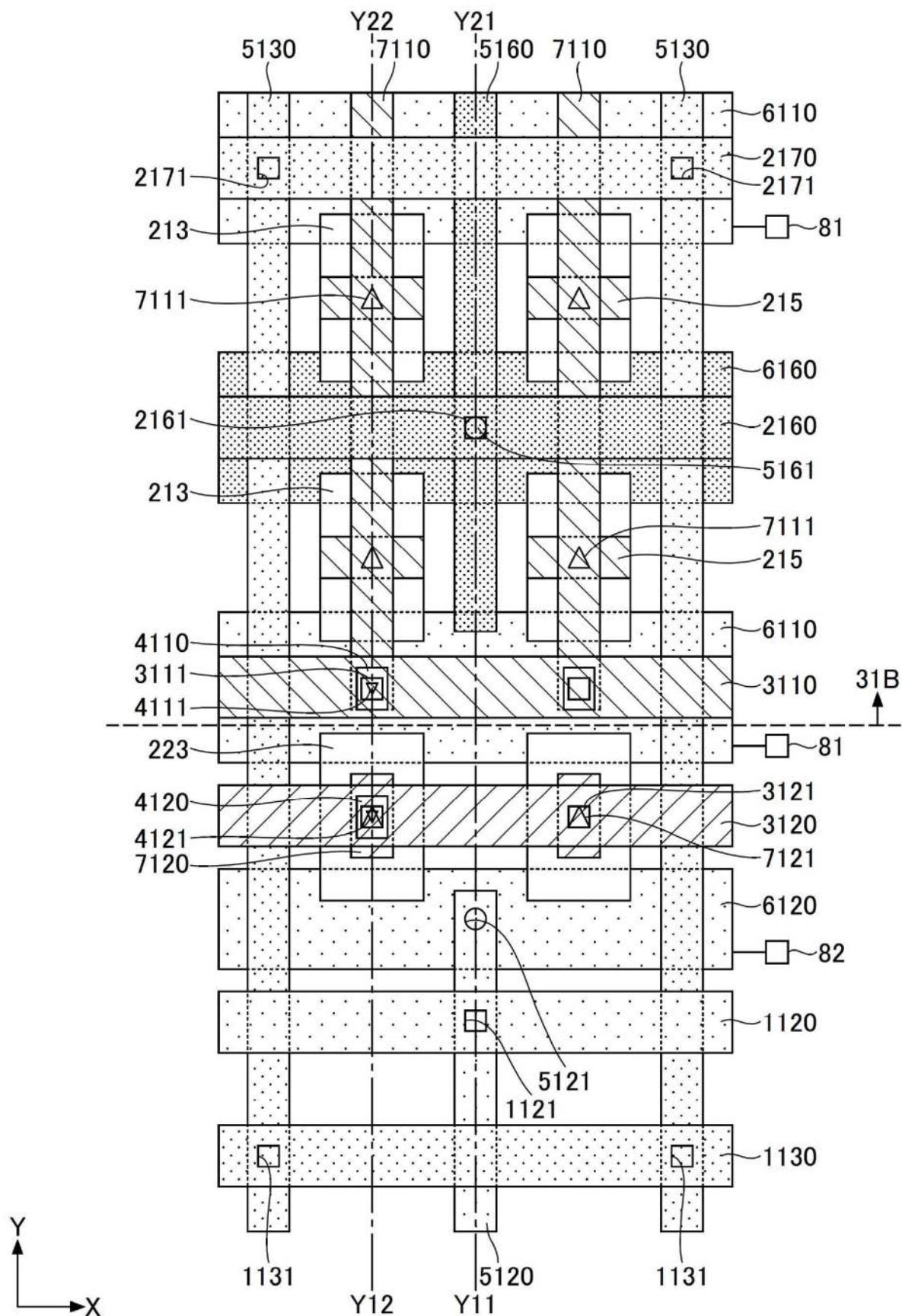

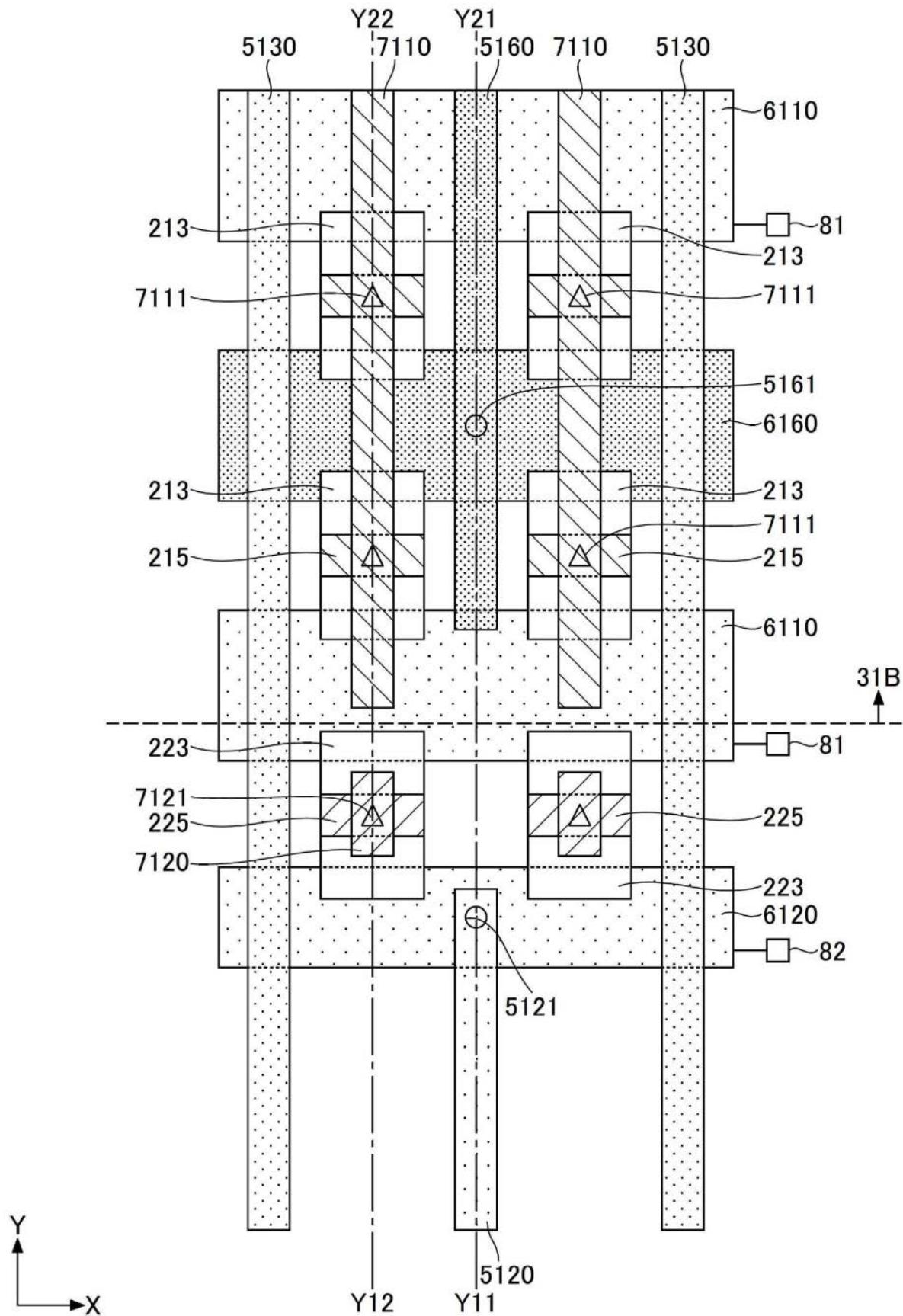

- [0026] 图8是表示第1实施方式的半导体装置的平面结构的模式图(其1)。

- [0027] 图9是表示第1实施方式的半导体装置的平面结构的模式图(其2)。

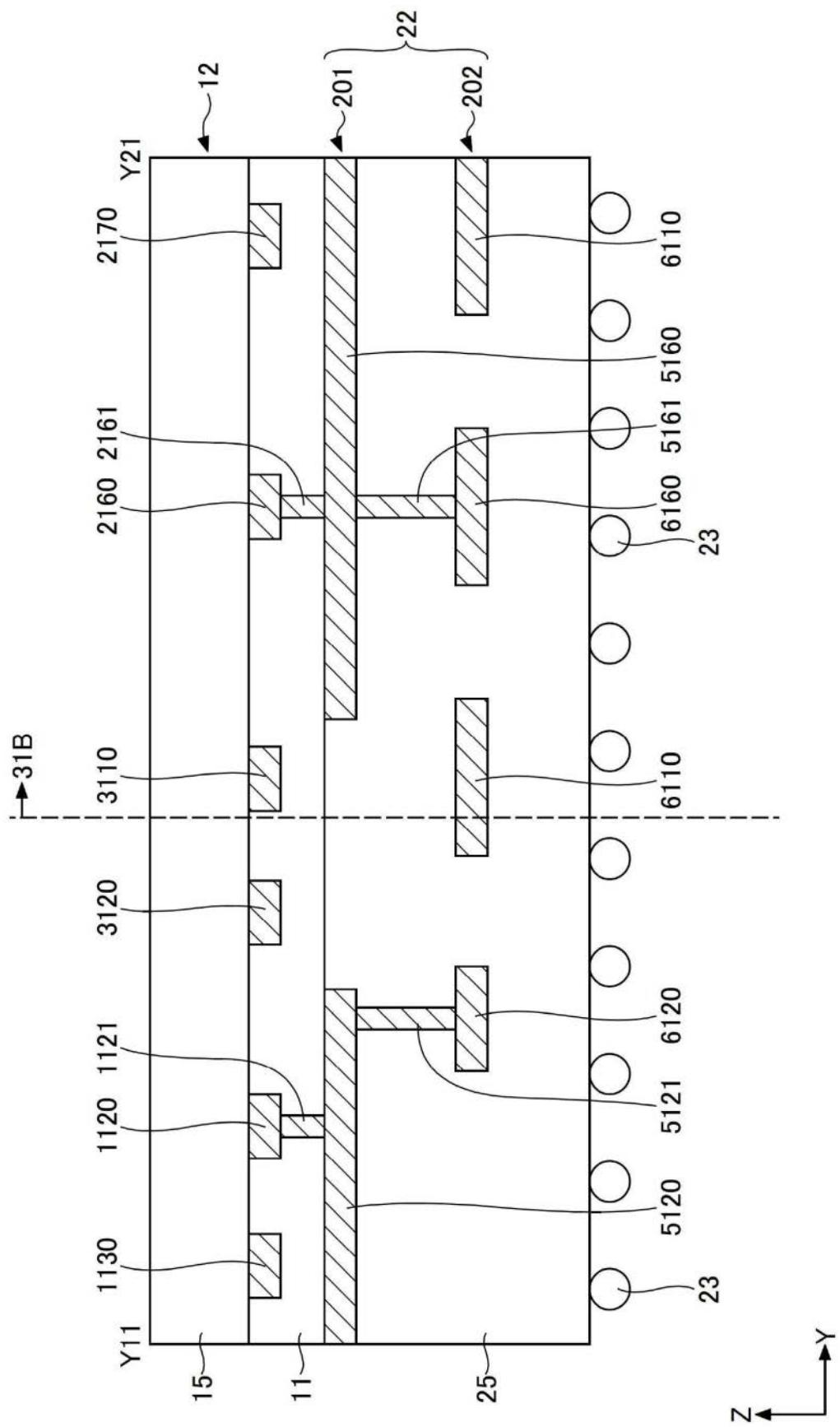

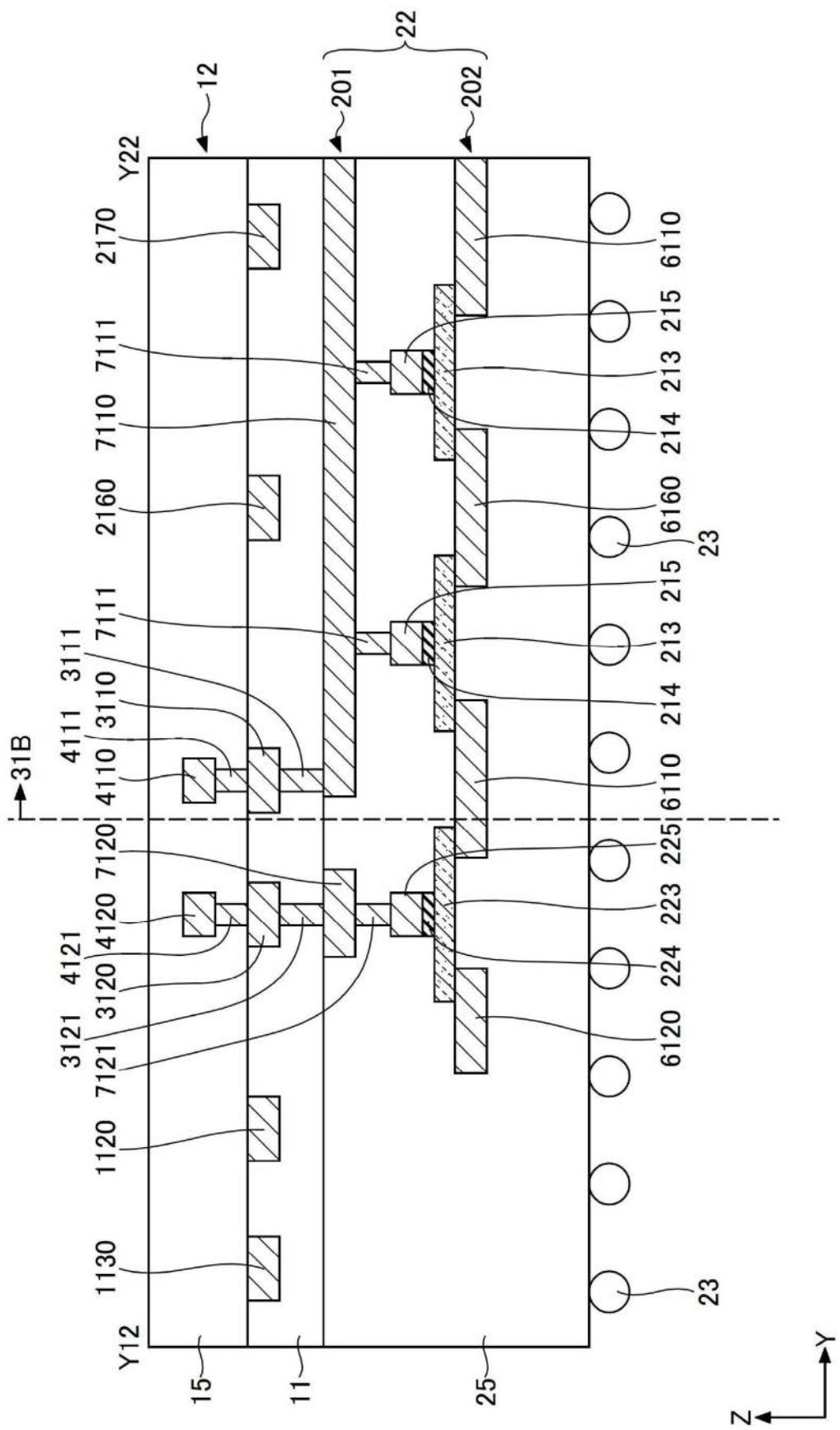

- [0028] 图10是表示第1实施方式的半导体装置的剖面图(其1)。

- [0029] 图11是表示第1实施方式的半导体装置的剖面图(其2)。

- [0030] 图12是表示第1实施方式的第1变形例的半导体装置的平面结构的模式图。

- [0031] 图13是表示第1实施方式的第2变形例的半导体装置的平面结构的模式图。

- [0032] 图14是表示第1实施方式的第3变形例的半导体装置的平面结构的模式图。

- [0033] 图15是表示第1实施方式的第4变形例的半导体装置的平面结构的模式图。

- [0034] 图16是表示第1实施方式的第5变形例的半导体装置的平面结构的模式图(其1)。

- [0035] 图17是表示第1实施方式的第5变形例的半导体装置的平面结构的模式图(其2)。

- [0036] 图18是表示第1实施方式的第6变形例的半导体装置的平面结构的模式图。

- [0037] 图19是表示第2实施方式的半导体装置的平面结构的模式图(其1)。

- [0038] 图20是表示第2实施方式的半导体装置的平面结构的模式图(其2)。

- [0039] 图21是表示第2实施方式的半导体装置的剖面图(其1)。

- [0040] 图22是表示第2实施方式的半导体装置的剖面图(其2)。

- [0041] 图23是表示开关晶体管的剖面结构的例子的剖面图(其1)。

- [0042] 图24是表示开关晶体管的剖面结构的例子的剖面图(其2)。

- [0043] 图25是表示开关晶体管的剖面结构的例子的剖面图(其3)。

## 具体实施方式

[0044] 以下,参照附图对实施方式进行具体的说明。并且,在本说明书以及附图中,对实质上具有相同功能结构的结构要素,通过附加相同的符号有时会省略重复说明。另外,在以下的说明中,将与基板的表面平行并且彼此正交的两个方向设为X方向、Y方向,将垂直于基板的表面的方向设为Z方向。另外,本公开中所说的配置一致,并非是严格地排除制造上的偏差所致的不一致情况,即使是制造上的偏差导致配置有偏移的情况,也可视为配置一致。

[0045] (本公开应用的半导体装置的概要)

[0046] 首先,关于本公开适用的半导体装置的概要进行说明。图1是表示本公开适用的半导体装置的概要的剖面图。图1所示的半导体装置包含第1芯片10以及第2芯片20。

[0047] 第1芯片10例如是半导体芯片,包括基板11以及第1布线层12。基板11例如是硅基板,在基板11的表面侧形成有晶体管等的半导体元件。晶体管例如是源极、漏极以及沟道包含鳍13的FinFET。第1布线层12形成在基板11的表面上,包含布线14以及绝缘层15。布线14

的一部分连接于鳍13。另外,例如在基板11的表面侧,形成有与布线14连接的电源线16,基板11上设置有从电源线16到基板11的背面的孔17。孔17例如是硅穿孔(through-silicon via:TSV)。在此,如图1所示,布线14的一部分呈孔形状,可连接于电源线16。并且,布线14以及电源线16的材料例如是铜、钨、钴、钌、钼等。

[0048] 第2芯片20例如是半导体芯片,与第1芯片10的基板11的背面相对配置。第2芯片20例如包含第2布线层22以及垫23。第2布线层22包含布线24以及绝缘层25。第2布线层22的顶面例如与第1芯片10的基板11的背面相对而置。即,基板11位于第1布线层12与第2布线层22之间。第2布线层22,如图1所示,可具有多个布线24。多个布线24可通过第2布线层22上设置的孔28进行连接。垫23例如是与布线基板或板等连接的外部连接端子。布线24的一部分连接于孔17。垫23被设置在第2布线层22的背面,通过孔28连接于布线24。通过垫23进行对第2布线层22的电源电位提供或信号传递。并且,布线24以及孔28的材料例如是铜、钨、钴、钌、钼等。

[0049] 第2芯片20可以具有与第1芯片10同等程度的尺寸,也可以具有大于第1芯片10的尺寸。另外,垫23可以在与第1芯片10相对侧的第2芯片20的面上,俯视下被设置在第1芯片10的外侧。以下,本说明书中的俯视是指对第1芯片10的主面的俯视。

[0050] 第2布线层22可以是在基板11的背面上形成布线24以及绝缘层25等而设置的结构。第2布线层22也可以形成在具有TSV的第2基板上,还可以在第2基板的背面设置有垫23。

[0051] 另外,图1的剖面图表示半导体装置的概要,详情如图10、图11等所示。

[0052] 接下来,关于第1芯片10的布局进行说明。图2是表示第1芯片10的布局的图。

[0053] 如图2所示,第1芯片10包含第1电源域31A、第2电源域31B以及输入输出(I/O)单元区域32。I/O单元区域32例如被配置在第1电源域31A以及第2电源域31B的周围。第1电源域31A的数量以及第2电源域31B的数量可以是2以上。

[0054] [半导体装置包含的电路]

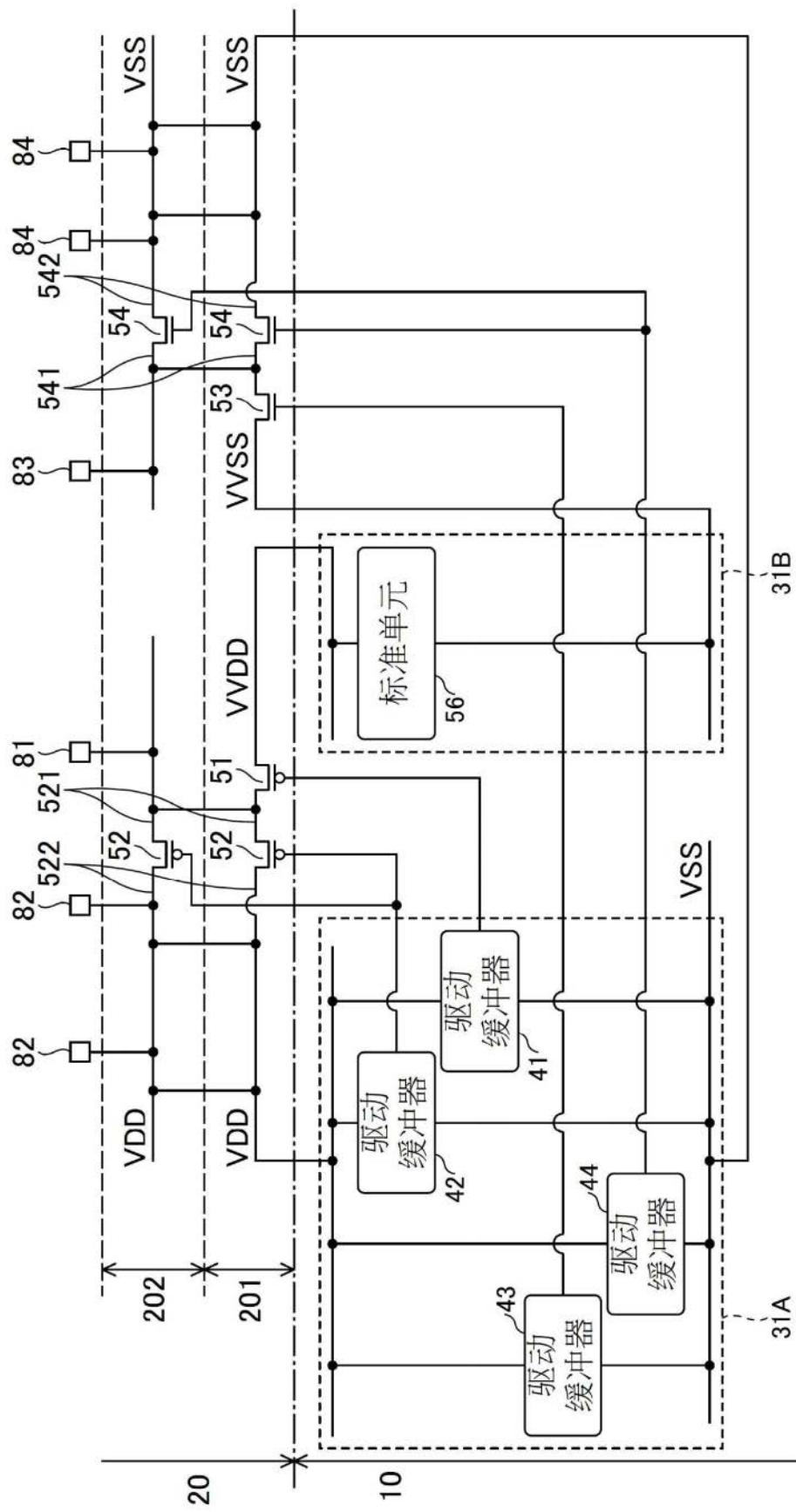

[0055] 以下,关于半导体装置包含的电路进行说明。图3是表示半导体装置包含的电路的一例结构的电路图。

[0056] 如图3所示,半导体装置在第1电源域31A内具有第1驱动缓冲器41、第2驱动缓冲器42、第3驱动缓冲器43、第4驱动缓冲器44。半导体装置在第2电源域31B内具有标准单元56。半导体装置具有提供VDD的电源电位的VDD布线、提供VVDD的电源电位的VVDD布线、提供VSS的电源电位的VSS布线、提供VVSS的电源电位的VVSS布线。例如,VSS的电源电位为接地电位,VSS布线为接地布线。

[0057] 第1电源域31A内的第1~第4驱动缓冲器41~44被提供VDD的电源电位以及VSS的电源电位。

[0058] 第2电源域31B内的标准单元56被提供VVDD的电源电位以及VVSS的电源电位。标准单元56例如包含NAND电路、逆变器等各种逻辑电路。标准单元56还可以包含SRAM(Static Random Access Memory)或宏单元。另外,在图3中,可以不设置VVDD布线,而是以VDD布线取而代之连接于标准单元56,或者,可以不设置VVSS布线,而是以VSS布线取而代之连接于标准单元56。在此情况下,标准单元56被提供VVDD的电源电位以及VSS的电源电位,或者被提供VDD的电源电位以及VVSS的电源电位。

[0059] 半导体装置具有第1开关晶体管51、第2开关晶体管52、第3开关晶体管53以及第4

开关晶体管54。

[0060] 第1开关晶体管51例如是P沟道MOS晶体管。例如,来自第1驱动缓冲器41的控制信号被输入到第1开关晶体管51的栅极。第1开关晶体管51的源极(VDD连接部)连接于VDD布线,漏极(VVDD连接部)连接于VVDD布线。

[0061] 第2开关晶体管52例如是P沟道MOS晶体管。例如,来自第2驱动缓冲器42的控制信号被输入到第2开关晶体管52的栅极。第2开关晶体管52被设置在VDD布线上。第2开关晶体管52的第一端子(漏极)521连接于第1开关晶体管51的源极。第1端子521以及第1开关晶体管51的源极与第1电源垫81连接。第1电源垫81被提供来自外部的VDD的电源电位。第2开关晶体管52的第二端子(源极)522与第2电源垫82连接。第2电源垫82被提供来自外部的VDD的电源电位。

[0062] 第3开关晶体管53例如是N沟道MOS晶体管。例如,来自第3驱动缓冲器43的控制信号被输入到第3开关晶体管53的栅极。第3开关晶体管53的源极(VSS连接部)连接于VSS布线,漏极(VVSS连接部)连接于VVSS布线。

[0063] 第4开关晶体管54例如是N沟道MOS晶体管。例如,来自第4驱动缓冲器44的控制信号被输入到第4开关晶体管54。第4开关晶体管54被设置在VSS布线上。第4开关晶体管54的第一端子(漏极)541连接于第3开关晶体管53的源极。第1端子541以及第3开关晶体管53的源极与第3电源垫83连接。第3电源垫83被提供来自外部的VSS的电源电位。第4开关晶体管54的第二端子(源极)542与第4电源垫84连接。第4电源垫84被提供来自外部的VSS的电源电位。

[0064] 第1~第4驱动缓冲器41~44连接于控制电路(未图示),第1~第4开关晶体管51~54的动作通过第1~第4驱动缓冲器41~44受到控制电路的控制。例如,控制电路被设置在第1电源域31A内,控制电路被提供VDD的电源电位以及VSS的电源电位。由控制电路进行第1开关晶体管51的开/关切换,以控制VDD布线与VVDD布线之间的导通。由控制电路进行第3开关晶体管53的开/关切换,以控制VSS布线与VVSS布线之间的导通。由控制电路进行第2以及第4开关晶体管52以及54的开/关切换,以控制第1电源域31A与第2电源域31B之间的导通。

[0065] 第2布线层22具有第1子布线层201与第2子布线层202,详情后述。第1子布线层201相对于第2子布线层202而言位于第1芯片10侧。在第1实施方式中,第1~第4开关晶体管51~54被设置在第2子布线层202。

[0066] 第1~第4开关晶体管51~54可由薄膜晶体管(thin film transistor:TFT)构成,也可以是微机电系统(micro electro mechanical systems:MEMS)开关。

[0067] [第1~第4驱动缓冲器41~44]

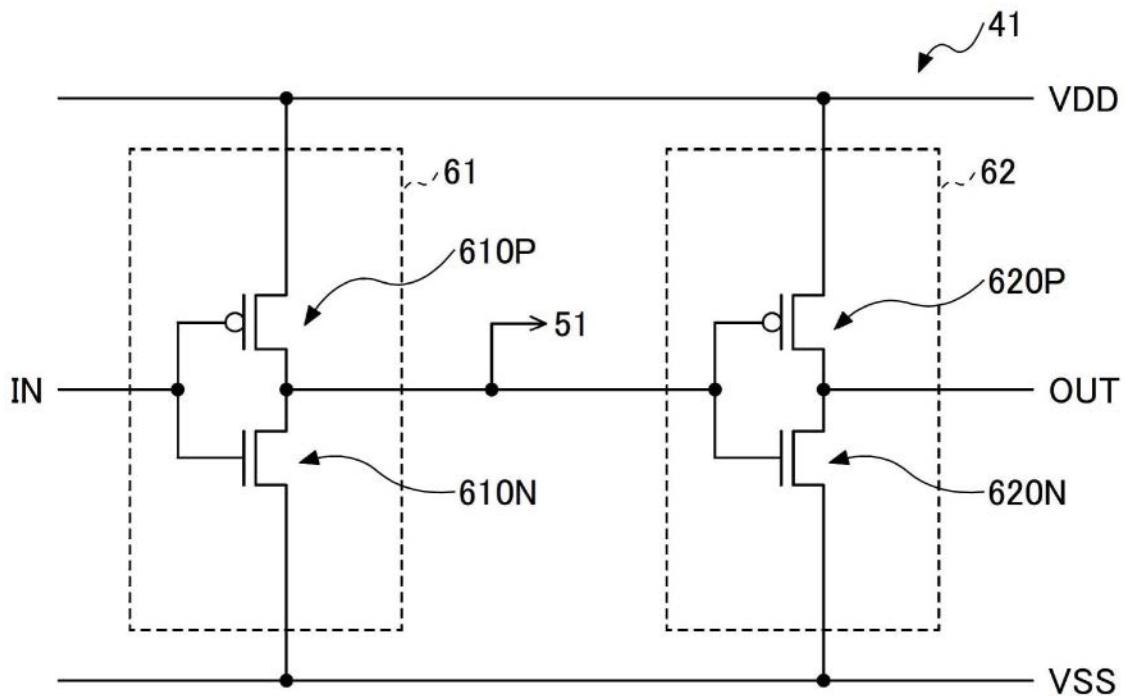

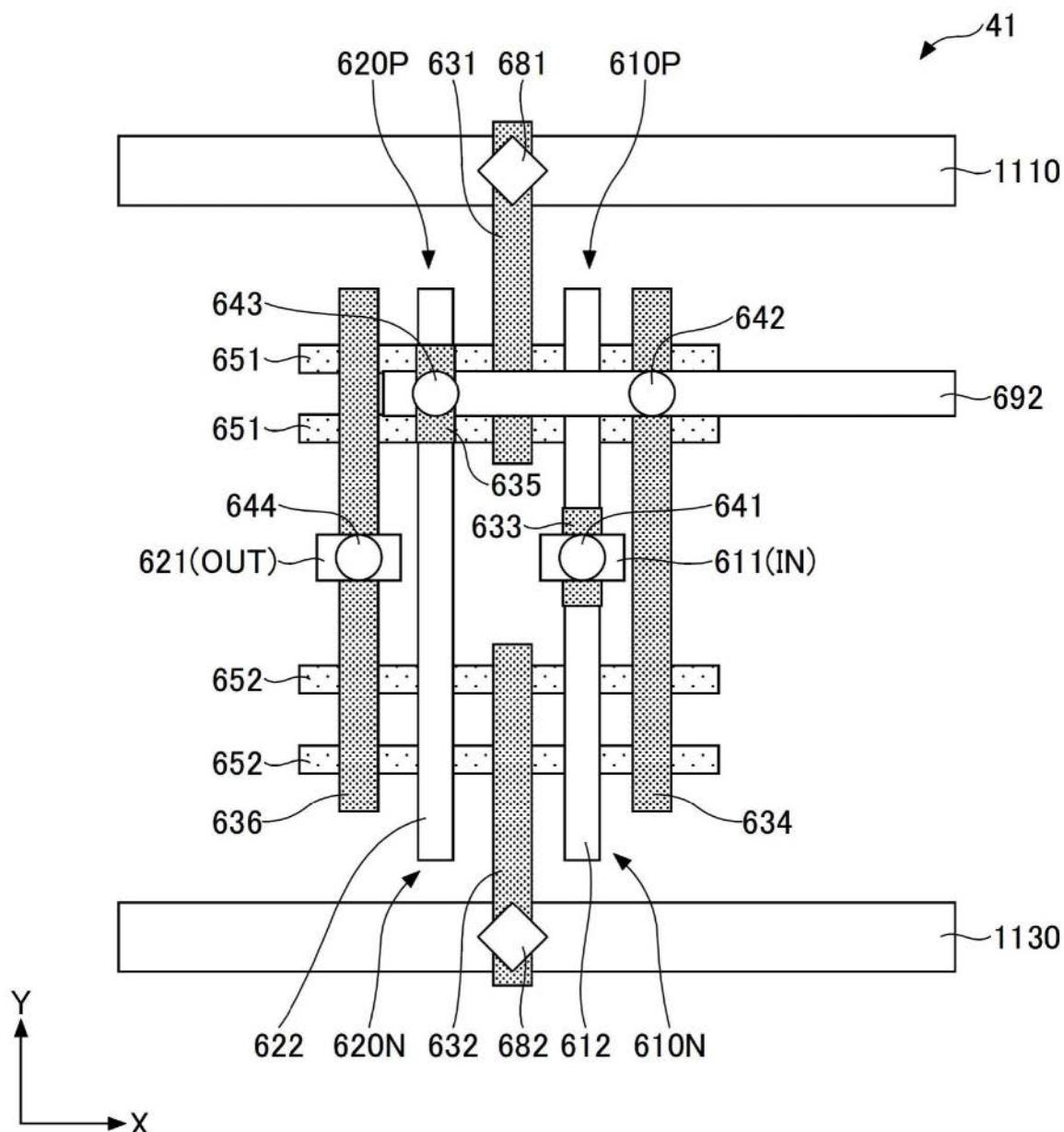

[0068] 以下,关于第1~第4驱动缓冲器41~44的结构进行说明。图4是表示第1驱动缓冲器41的结构的电路图。图5是表示第1驱动缓冲器41的一个例子的平面结构的模式图。

[0069] 如图4所示,第1驱动缓冲器41具有逆变器61以及逆变器62。输入信号IN被输入到逆变器61,逆变器61的输出被输入到逆变器62,并由逆变器62输出输出信号OUT。逆变器61包含P沟道MOS晶体管610P以及N沟道MOS晶体管610N。逆变器62包含P沟道MOS晶体管620P以及N沟道MOS晶体管620N。

[0070] 在图5所示的一个例子中,例如,设置有相当于VDD布线的电源线1110、相当于VSS布线的电源线1130。电源线1110以及1130沿着X方向延伸。在电源线1110的电源线1130侧,设置有沿着X方向延伸的半导体的鳍651。例如设置有2条鳍651。在鳍651的电源线1130侧,

设置有沿着X方向延伸的半导体的鳍652。例如设置有2条鳍652。设置有局部布线631,其通过孔681连接于电源线1110,并沿着Y方向延伸,连接于鳍651。设置有局部布线632,其通过孔682连接于电源线1130,并延伸Y方向延伸,连接于鳍652。在局部布线631以及632的X方向正侧,设有与鳍651以及652连接的局部布线634。在局部布线631以及632的X方向负侧,设有与鳍651以及652连接的局部布线636。

[0071] 在局部布线631与局部布线634之间,以及在局部布线632与局部布线634之间,设有通过栅极绝缘膜(未图示)与鳍651以及652交叉的栅极电极612。在局部布线631与局部布线636之间,以及在局部布线632与局部布线636之间,设有通过栅极绝缘膜(未图示)与鳍651以及652交叉的栅极电极622。栅极电极612通过局部布线633以及孔641连接于布线611。栅极电极622通过局部布线635以及孔643连接于布线692。布线692还连接于局部布线634。局部布线636通过孔644连接于布线621。输入信号IN被输入到布线611,由布线621输出输出信号OUT(参照图4)。

[0072] 布线692也可以连接于第1开关晶体管51的栅极。取代布线692,也可以是布线611或布线621的任一方连接于第1开关晶体管51的栅极。即,逆变器61的输出也可以被输入到第1开关晶体管51的栅极。取代逆变器61的输出,也可以是逆变器61的输入或逆变器62的输出的任一方连接于第1开关晶体管51的栅极。

[0073] 第2~第4驱动缓冲器42~44可具有与第1驱动缓冲器41相同的结构。

[0074] 在此,逆变器61以及62的结构为一例,例如,逆变器61以及62所包含的P沟道MOS晶体管以及N沟道MOS晶体管也可以是2对以上。

[0075] [标准单元56]

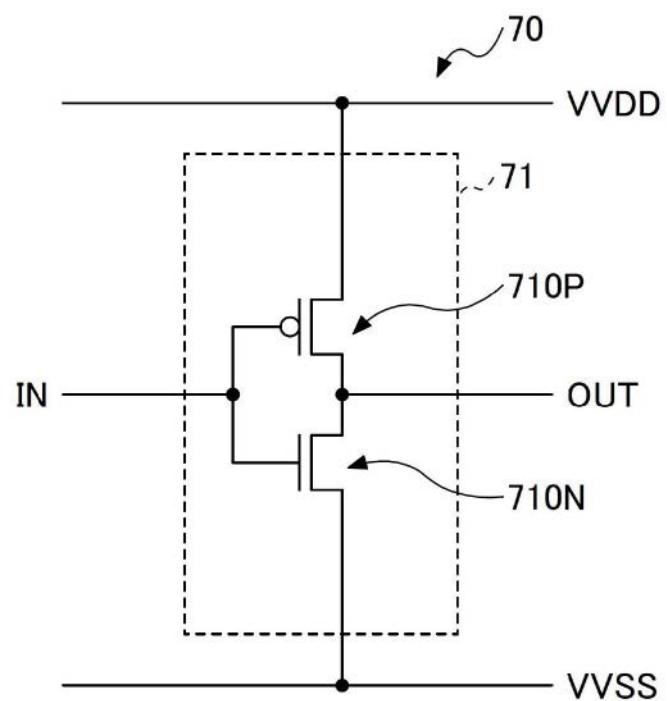

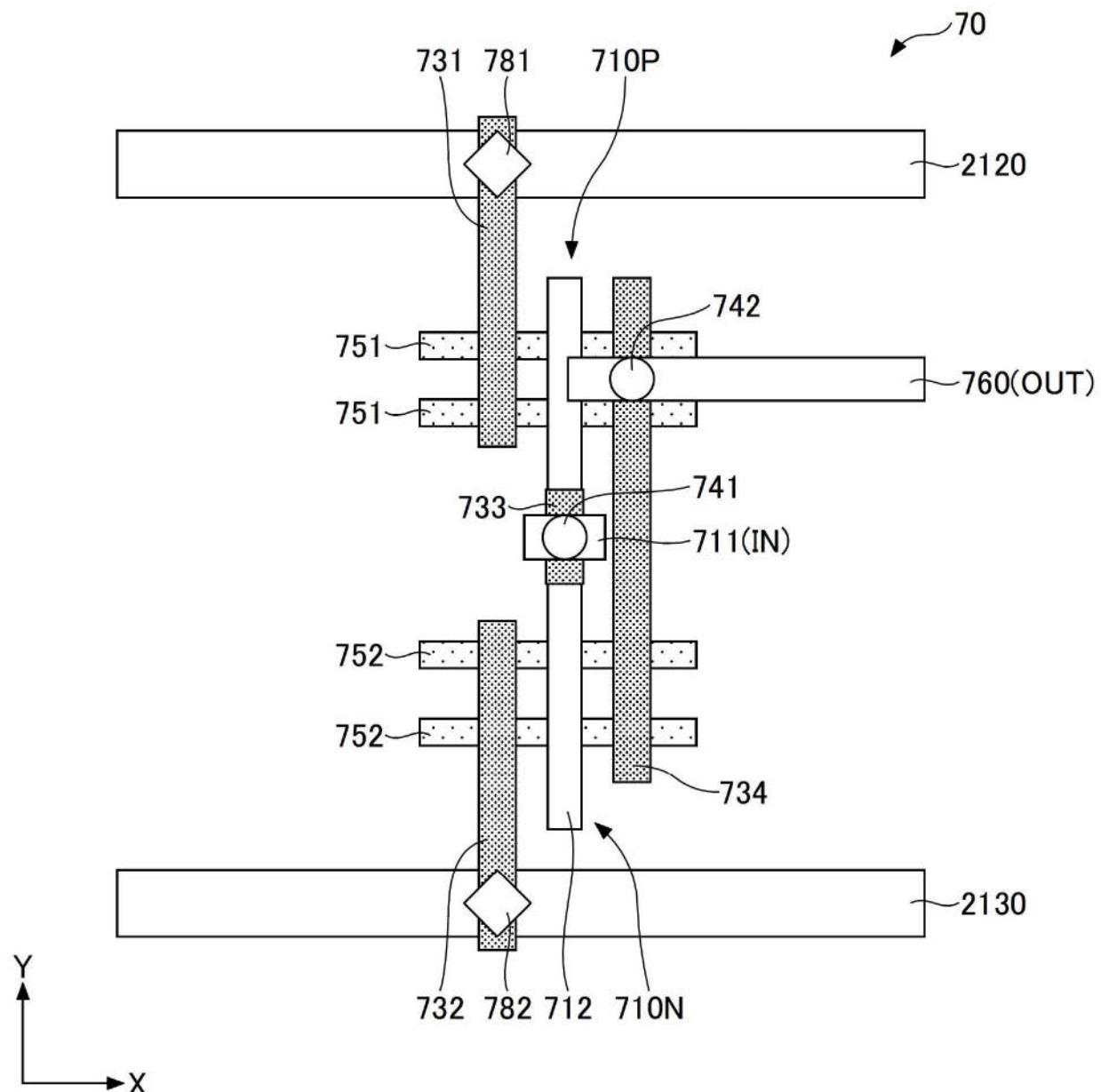

[0076] 以下,作为标准单元56包含的电路之一例,关于逆变器的结构进行说明。图6是表示逆变器的结构的电路图。图7是表示逆变器的平面结构的模式图。

[0077] 如图6所示,逆变器70包含P沟道MOS晶体管710P以及N沟道MOS晶体管710N。

[0078] 例如图7所示,设置有相当于VVDD布线的电源线2120以及相当于VVSS布线的电源线2130。电源线2120以及2130沿着X方向延伸。在电源线2120的电源线2130侧,设置有沿着X方向延伸的半导体的鳍751。例如设置有2条鳍751。在鳍751的电源线2130侧,设置有沿着X方向延伸的半导体的鳍752。例如设置有2条鳍752。设置有局部布线731,其通过孔781连接于电源线2120,并沿着Y方向延伸,连接于鳍751。设置有局部布线732,其通过孔782连接于电源线2130,并沿着Y方向延伸,连接于鳍752。在局部布线731以及732的X方向正侧,设置有与鳍751以及752连接的局部布线734。电源线2120以及2130可以设置横跨3个以上的区域的电路。即,可以设置所谓的多高度(multi-height)的电路。

[0079] 在局部布线731与局部布线734之间,以及在局部布线732与局部布线734之间,设置有通过栅极绝缘膜(未图示)与鳍751以及752交叉的栅电极712。栅电极712通过局部布线733以及孔741连接于布线711。局部布线734通过孔742连接于布线760。输入信号IN输入到布线711,布线760输出输出信号OUT(参照图6)。

[0080] 在图5以及图7中例示了采用鳍的晶体管(FinFET),此外还可以在缓冲器等的逻辑电路设置平面型的晶体管、互补场效应晶体管(Complementary Field Effect Transistor:CFET)、使用纳米线的晶体管等。

[0081] 在此,至少设置有VVDD布线或VVSS布线的任一方既可。例如,设置有VVDD布线时,

可以设置VSS布线,非VVSS布线。在此情况下,可以不设置第3驱动缓冲器43与第3开关晶体管53的组合。另外,例如,设置有VVSS布线时,可以设置VDD布线,非VVDD布线。在此情况下,可以不设置第1驱动缓冲器41与第1开关晶体管51的组合。

[0082] 另外,设置有第2驱动缓冲器42与第2开关晶体管52的组合或者第4驱动缓冲器44与第4开关晶体管54的组合的任一方时,可以不设置另一方。例如,若设置有第2驱动缓冲器42与第2开关晶体管52的组合,可使不设置第4驱动缓冲器44与第4开关晶体管54的组合。

[0083] (第1实施方式)

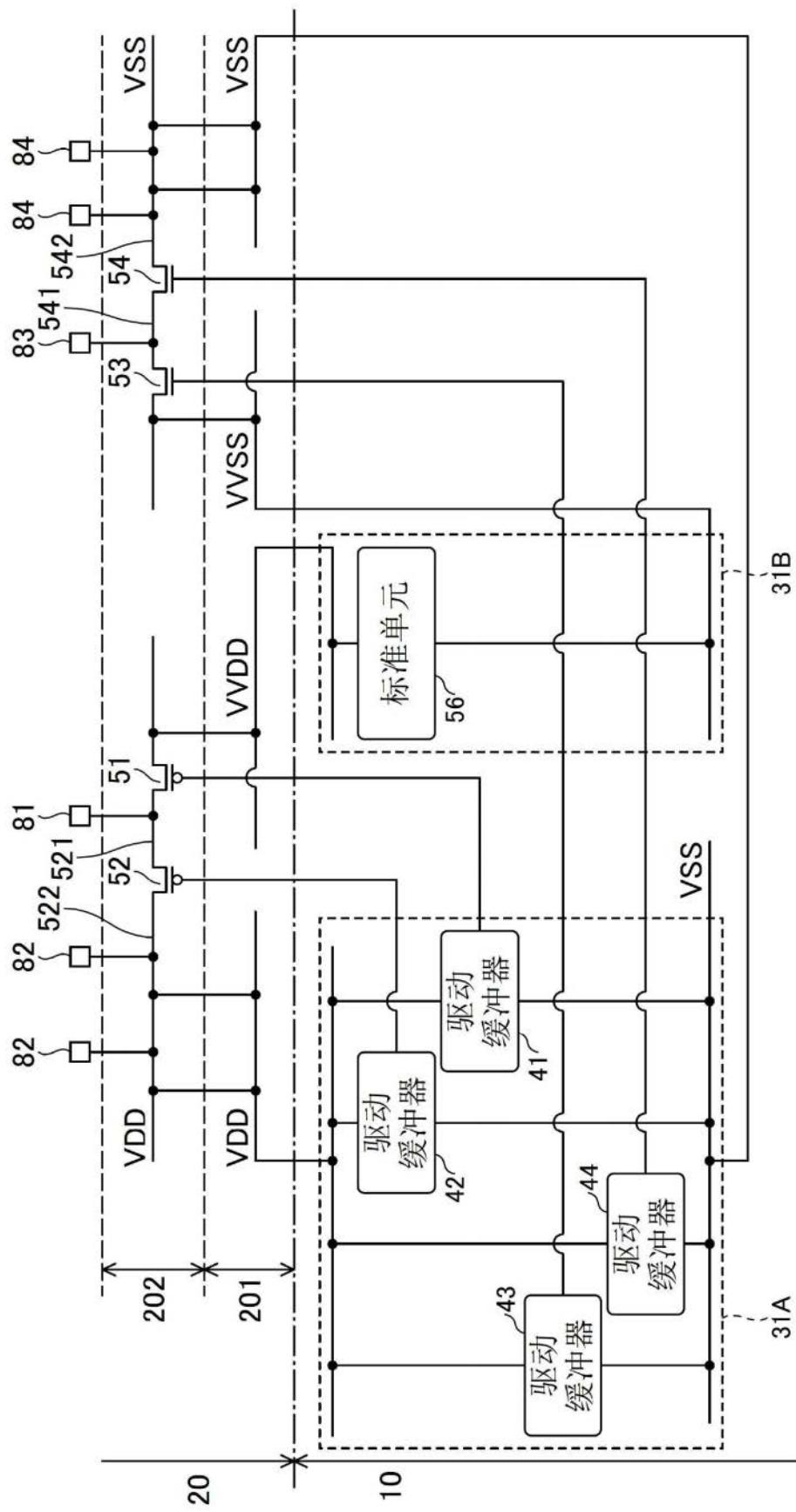

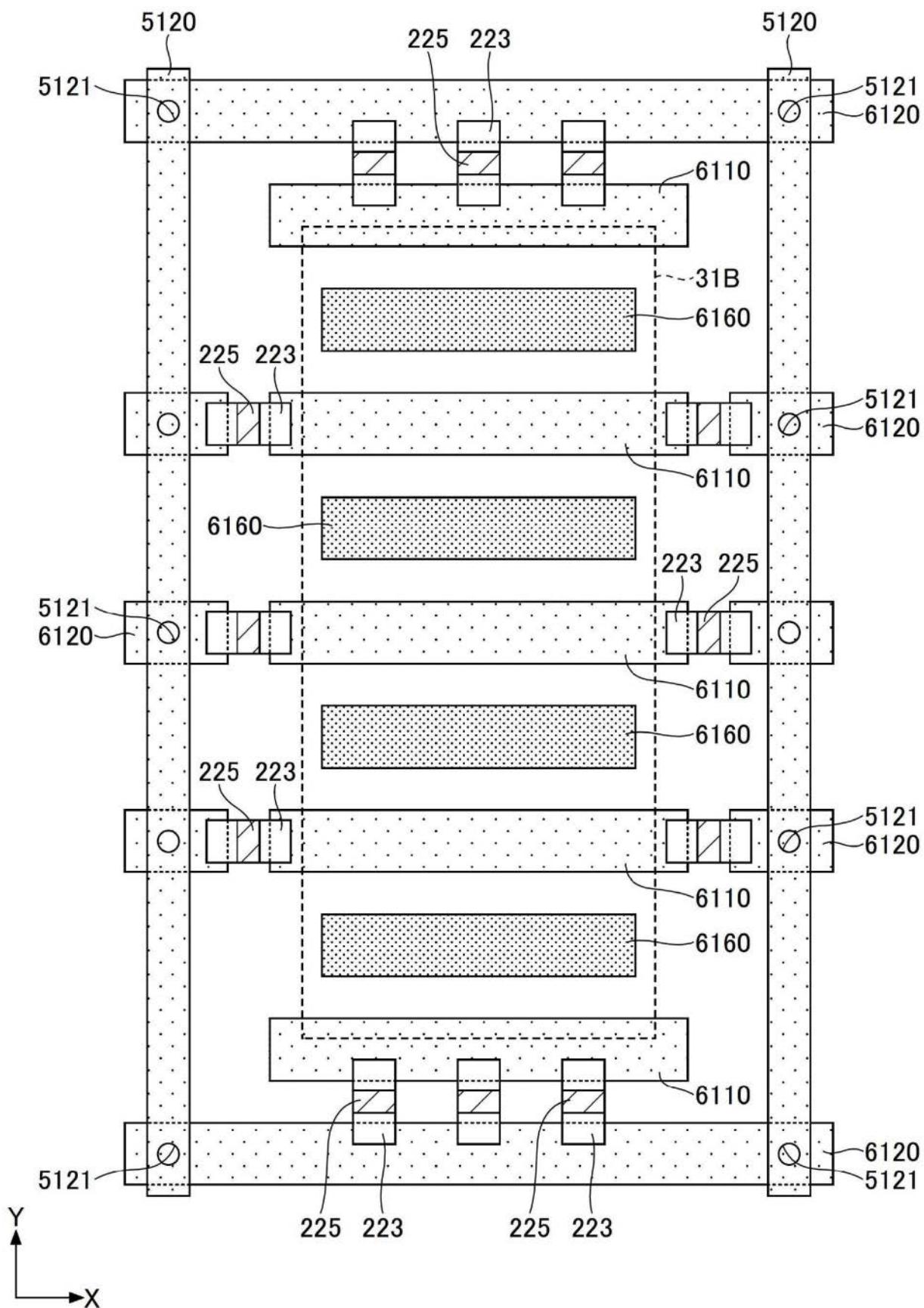

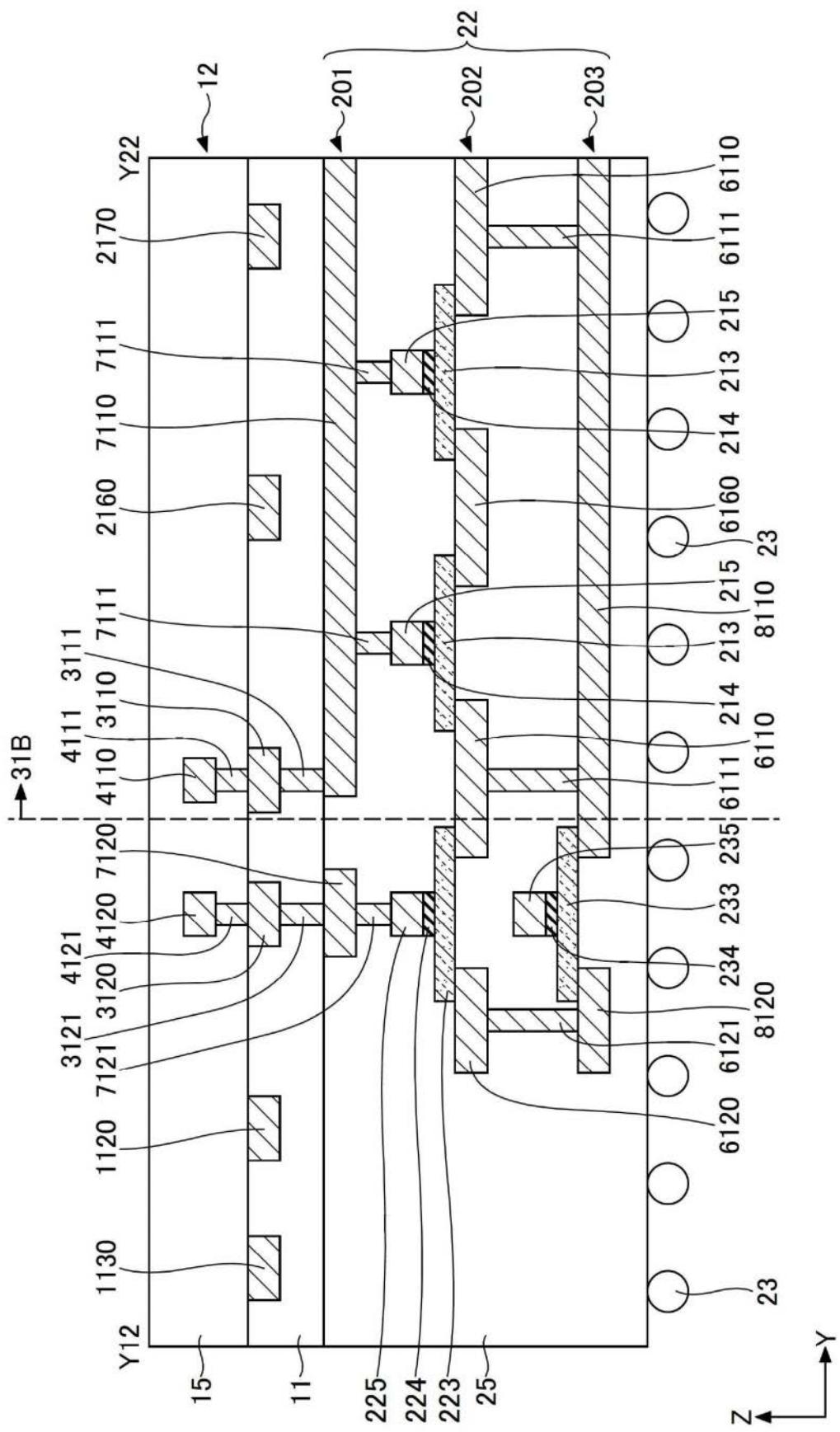

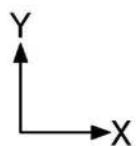

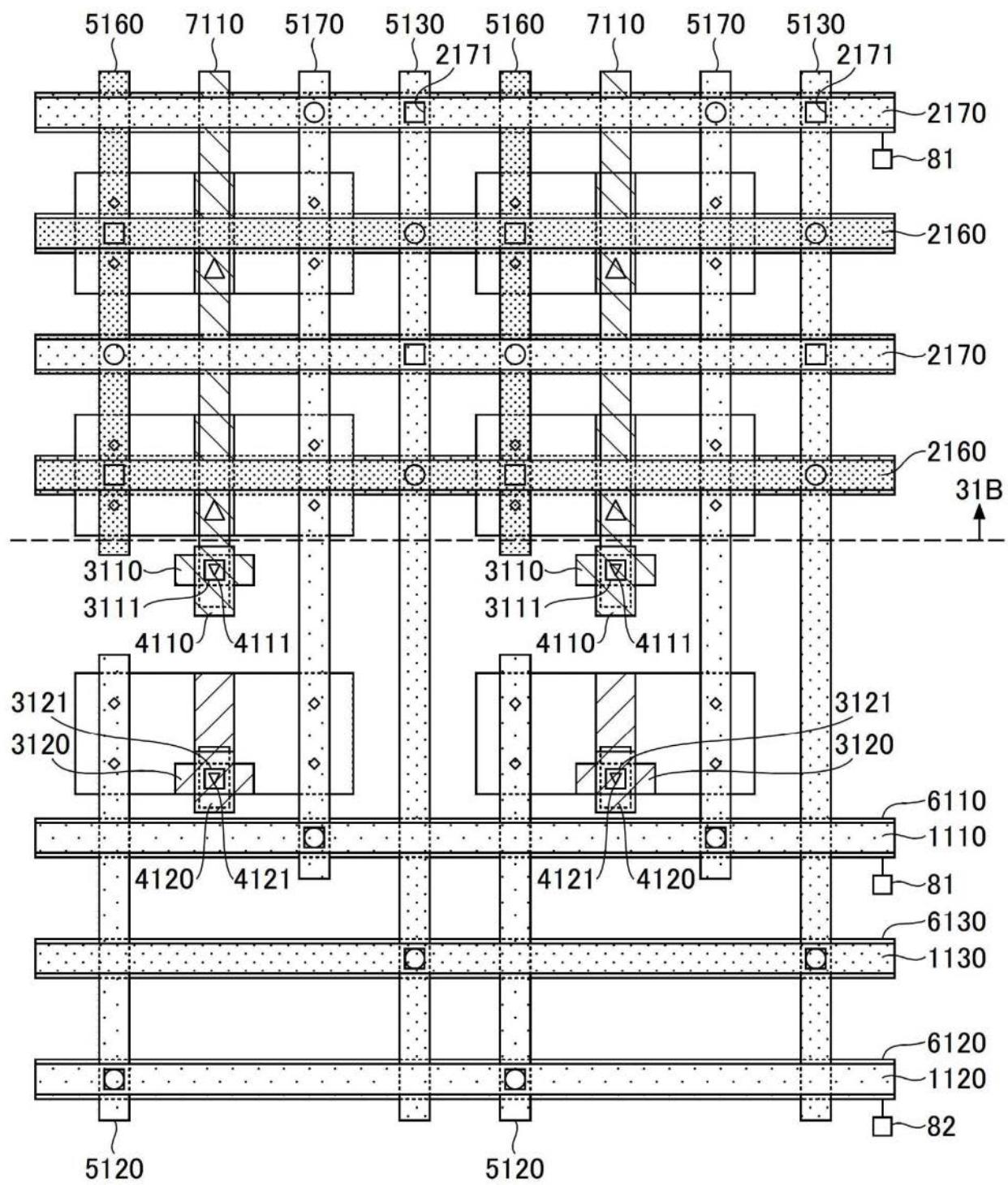

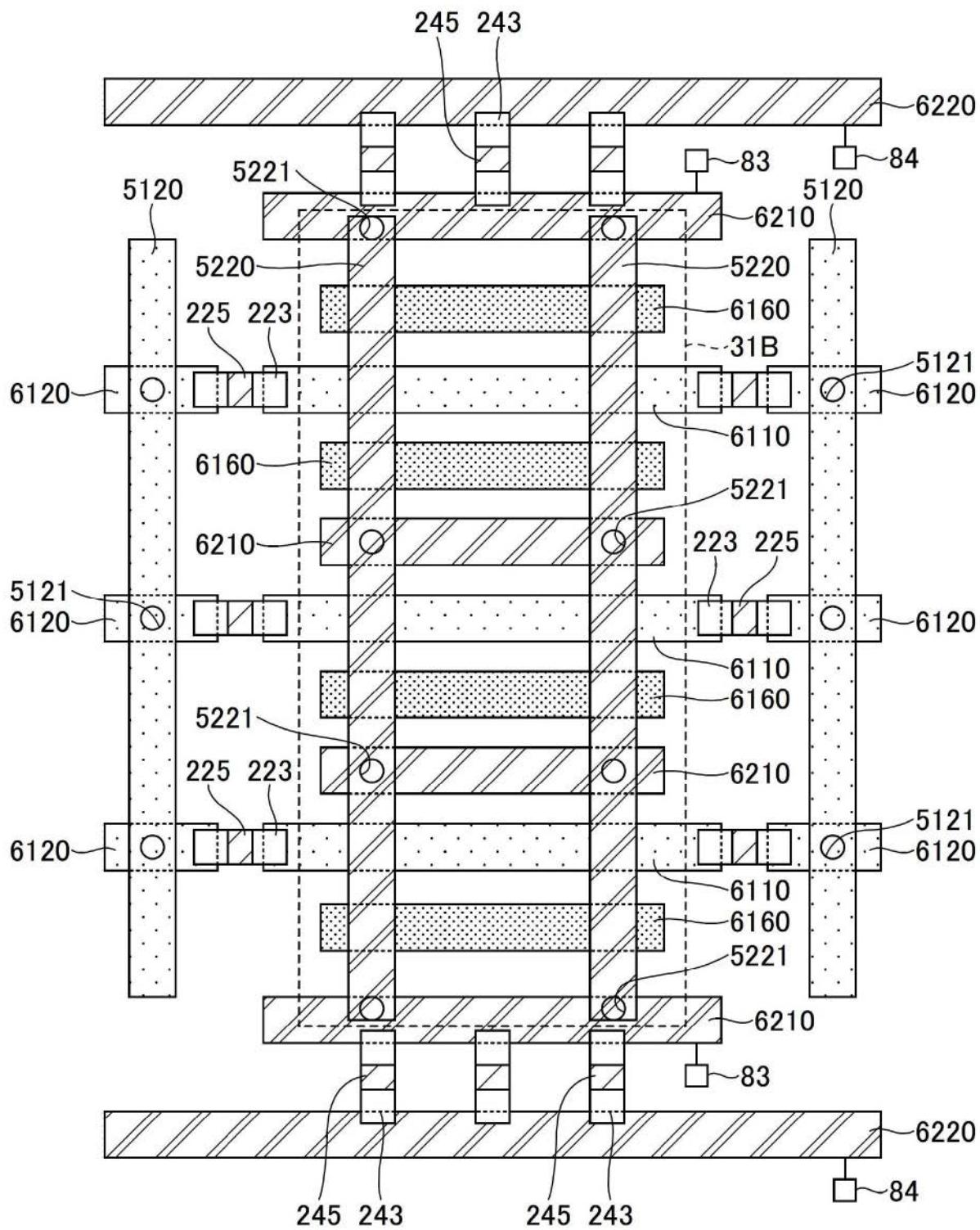

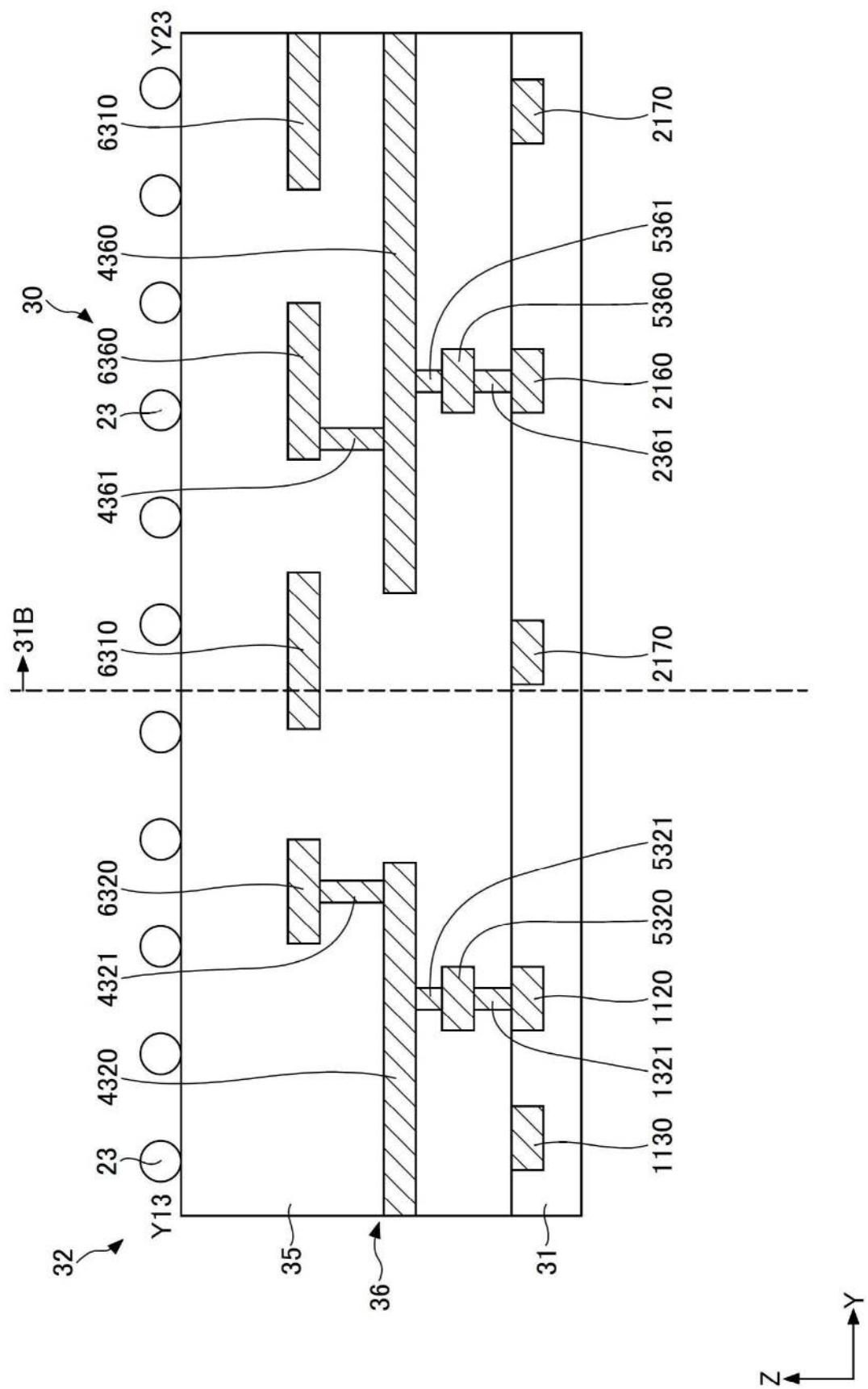

[0084] 在此,关于第1实施方式进行说明。第1实施方式中,未设置图3所示的电路中的VVSS布线、第3驱动缓冲器43、第3开关晶体管53、第4开关晶体管54。图8以及图9是表示第1实施方式的半导体装置的平面结构的模式图。图10以及图11是表示第1实施方式的半导体装置的剖面图。图8表示第1芯片10以及第2芯片20的内部结构,图9表示第2芯片的内部结构。图10相当于沿着图8以及图9中的Y11-Y21线的剖面图,图11相当于沿着图8以及图9中的Y12-Y22线的剖面图。

[0085] [第1芯片10]

[0086] 第1芯片10包含沿着X方向延伸的控制信号线3110。在图8的例子中,第1芯片10包含被配置在控制信号线3110的Y方向正侧并沿着X方向延伸的电源线2160、沿着X方向延伸的电源线2170。在图8的例子中,电源线2160相对于电源线2170而言位于控制信号线3110侧。例如,电源线2160相当于VVDD布线,电源线2170相当于VSS布线。控制信号线3110连接于第1驱动缓冲器41与第1开关晶体管51的栅极之间。电源线2160与电源线2170也可以是多组交替配置。电源线2160与电源线2170被配置在第2电源域31B内。控制信号线3110也可以配置在第2电源域31B内。

[0087] 在图8的例子中,第1芯片10包含被配置在控制信号线3110的Y方向负侧并沿着X方向延伸的控制信号线3120、沿着X方向延伸的电源线1120、沿着X方向延伸的电源线1130。在图8的例子中,控制信号线3120相对于电源线1120而言位于控制信号线3110侧,电源线1120相对于电源线1130而言位于控制信号线3110侧。例如,电源线1120相当于电连接于第2电源垫82的VDD布线,电源线1130相当于VSS布线。控制信号线3120连接于第2驱动缓冲器42与第2开关晶体管52的栅极之间。控制信号线3120、电源线1120以及电源线1130被配置在第2电源域31B外。并且,各控制信号线以及各电源线的配置并不限定于图8的例子,可有适当变更。

[0088] 如图10以及图11所示,基板11上形成有沿着X方向延伸的多个槽,控制信号线3110、电源线2160、电源线2170、控制信号线3120、电源线1120以及电源线1130形成在这些槽内。具有这种结构的电源线2160、电源线2170、电源线1120以及电源线1130也被称为BPR(Buried Power Rail)。在基板11的表面还可以形成元件分离膜(未图示)。例如采用STI(Shallow Trench Isolation)法形成元件分离膜。元件分离膜的表面与基板11的表面可以是同一面,也可以不是同一面。

[0089] 图8~图11中虽未图示,在第2电源域31B内,在电源线2160与电源线2170之间连接标准单元56等的电路。

[0090] 另外,图8~图11中虽未图示,第1电源域31A被配置在第2电源域31B外,在第1电源域31A内,在电源线1120与电源线1130之间连接第1驱动缓冲器41、第2驱动缓冲器42以及这

些的控制电路等的电路。

[0091] 第1布线层12包含控制信号线3110、电源线2160、电源线2170、控制信号线3120、配置在电源线1120以及电源线1130之上方的控制信号线4110以及4120。在第1布线层12形成有用于连接控制信号线4110与控制信号线3110的孔4111、用于连接控制信号线4120与控制信号线3120的孔4121。孔4111形成在控制信号线4110的下方，孔4121形成在控制信号线4120的下方。

[0092] 在基板11形成有穿通至基板11的背面的孔1121、1131、2161、2171、3111以及3121。孔1121被形成在电源线1120的下方，孔1131被形成在电源线1130的下方，孔2161被形成在电源线2120的下方，孔2171被形成在电源线2170的下方。孔3111被形成在控制信号线3110的下方，孔3121被形成在控制信号线3120的下方。

[0093] [第2芯片20]

[0094] 如图10以及图11所示，第2芯片20例如具有绝缘层25、形成在绝缘层25的表层部的第一子布线层201、形成在绝缘层25的内部的第二子布线层202。

[0095] 第1子布线层201包含电源线5120、电源线5130、电源线5160、控制信号线7110、控制信号线7120。电源线5120、电源线5130、电源线5160、控制信号线7110、控制信号线7120沿着Y方向延伸。例如，在俯视下与第2电源域31B重叠的区域内，电源线5160位于2个控制信号线7110之间，控制信号线7110位于电源线5130与电源线5160之间。例如，电源线5130从电源线2160以及2170的下方延续形成至电源线1130的下方。例如，电源线5160被形成在俯视下与第2电源域31B重叠的区域内。例如，电源线5120在俯视下与第2电源域31B重叠的区域内，形成在电源线5160的延长线上。例如，电源线5120相当于电连接于第2电源垫82的VDD布线，电源线5130相当于VSS布线，电源线5160相当于VVDD布线。

[0096] 第2子布线层202包含电源线6110、电源线6120、电源线6160。电源线6110、电源线6120、电源线6160沿着X方向延伸。例如，电源线6110位于电源线2170的下方，电源线6160位于电源线2160的下方。电源线6120具有在俯视下与电源线5120重叠的部分。在绝缘层25形成有用于连接电源线5120与电源线6120的孔5121、用于连接电源线5160与电源线6160的孔5161。例如，电源线6110相当于电连接于第1电源垫81的VDD布线，电源线6120相当于电连接于第2电源垫82的VDD布线，电源线6160相当于VVDD布线。

[0097] 在绝缘层25的俯视下与第2电源域31B重叠的区域内，形成有俯视下与相邻的成对的电源线6110与6160重叠的多个半导体层213。半导体层213连接于电源线6110以及6160。在半导体层213上形成有栅极绝缘膜214，在栅极绝缘膜214上形成有栅极电极215。栅极绝缘膜214与半导体层213以及栅极电极215相接。栅极电极215在俯视下位于电源线6110与电源线6160之间。在绝缘层25形成有用于连接控制信号线7110与各栅极电极215的孔7111。半导体层213、栅极绝缘膜214、栅极电极215被包含在第1开关晶体管51。

[0098] 在绝缘层25形成有俯视下与相邻的成对的电源线6110与6120重叠的多个半导体层223。在此，半导体层223可以配置在俯视下与第2电源域31B重叠的区域外，也可以配置在区域内。半导体层223连接于电源线6110以及6120。在半导体层223上形成有栅极绝缘膜224，在栅极绝缘膜224上形成有栅极电极225。栅极绝缘膜224与半导体层223以及栅极电极225相接。栅极电极225在俯视下位于电源线6110与电源线6120之间。在绝缘层25形成有用于连接控制信号线7120与各栅极电极225的孔7121。半导体层223、栅极绝缘膜224、栅极电

极225包含于第2开关晶体管52。

[0099] 通过设置在第2芯片20的背面的多个垫23，提供来自外部的VDD的电源电位以及VSS的电源电位。另外，经半导体装置处理后的信号通过多个垫23被输入到外部。

[0100] 在具有这种结构的第1实施方式的半导体装置中，标准单元56无需动作时，第1开关晶体管51为关状态。即，使电源线6110与电源线6160之间成为非导通的控制信号被输入到栅极电极215。其结果，电源线6160(VVDD布线)与第1电源垫81以及第2电源垫82成为绝缘状态，电源线6110(VDD布线)对电源线6160(VVDD布线)的电源电位提供会被切断。

[0101] 另外，欲使标准单元56动作时，在使第2开关晶体管52成为关状态之后，使第1开关晶体管51成为开状态。即，使电源线6110与电源线6120之间成为非导通的控制信号被输入到栅极电极225之后，使电源线6110与电源线6160之间成为导通的控制信号会被输入到栅极电极215。其结果，在电源线6120(VDD布线)与电源线6110(VDD布线)成为绝缘的状态下，电源线6160(VVDD布线)通过电源线6110(VDD布线)电连接于第1电源垫81，向电源线6160(VVDD布线)提供VDD的电源电位。

[0102] 电源线6160(VVDD布线)若被提供VDD的电源电位，标准单元56即会开始动作。此时，第2开关晶体管52若成为了开状态，第2电源垫82会向第2电源域31B提供VDD的电源电位，伴随着急速的电源电位提供会产生噪声，该噪声可能会波及第1电源域31A。这种急速的电源电位的提供也被称为突流(Rush current)。对此，在本实施方式中，第2开关晶体管52为关状态，能够抑制突流，抑制噪声的发生。

[0103] 标准单元56开始动作之后，提供给第2电源域31B的VDD电源电位的变动稳定后，第2开关晶体管52称为开状态。即，使电源线6110与电源线6120之间导通的控制信号被输入到栅极电极225。其结果，第1电源域31A以及第2电源域31B被提供稳定的VDD的电源电位。

[0104] 如上所述，根据本实施方式，能够抑制突流进入动作中的区域所致的噪声带来的影响。

[0105] (第1实施方式的第1变形例)

[0106] 以下，关于第1实施方式的第1变形例进行说明。第1变形例主要是第2开关晶体管的布局不同于第1实施方式。图12是表示第1实施方式的第1变形例的半导体装置的平面结构的模式图。图12中主要表示第1变形例与第1实施方式不同的部分，其他部分省略图示。

[0107] 如图12所示，在第1变形例中，在俯视下的第2电源域31B的Y方向正侧以及Y方向负侧均配置有沿着X方向延伸的电源线6120。并且，在俯视下与第2电源域31B重叠的区域外，形成有俯视下与在Y方向上相邻的成对的电源线6110以及6120重叠的多个半导体层223。在半导体层223上形成有栅极绝缘膜224(参照图11)以及栅极电极225。半导体层223、栅极绝缘膜224、栅极电极225包含于第2开关晶体管52。

[0108] 另外，在俯视下与第2电源域31B重叠的区域内配置有沿着X方向延伸的多个电源线6110。在俯视下的第2电源域31B的X方向正侧以及X方向负侧，在这些电源线6110的延长线上均配置有沿着X方向延伸的电源线6120。并且，在俯视下与第2电源域31B重叠的区域外，形成有俯视下与在X方向上相邻的成对的电源线6110以及6120重叠的个半导体层223。在半导体层223上形成有栅极绝缘膜224(参照图11)以及栅极电极225。半导体层223、栅极绝缘膜224、栅极电极225包含于第2开关晶体管52。

[0109] 在俯视下的第2电源域31B的X方向正侧以及X方向负侧均配置有沿着Y方向延伸的

电源线5120。俯视下电源线5120与多个电源线6120正交，电源线5120以及与该电源线5120正交的电源线6120通过孔5121相连接。

[0110] 另外，在图12的第2开关晶体管52中，省略了孔7121以及控制信号线7120等的图示。即，在各个第2开关晶体管52中，配置有孔7121以及控制信号线7120等。并且，图12中虽未图示，在Y方向上相邻的电源线6110与电源线6160之间连接有第1开关晶体管51。

[0111] 其他结构与第1实施方式相同。

[0112] 通过第1变形例也能够获得与第1实施方式相同的效果。

[0113] 在此，无需在第2电源域31B的X方向正侧、X方向负侧、Y方向正侧、Y方向负侧全都配置第2开关晶体管52。仅在第2电源域31B的X方向正侧以及X方向负侧配置第2开关晶体管52即可。另外，也可以仅在第2电源域31B的Y方向正侧以及Y方向负侧配置第2开关晶体管52。

[0114] 另外，电源线6110、6120的一部分也可以不直接连接于第2开关晶体管52，而是通过其他布线连接于第2开关晶体管52。

[0115] (第1实施方式的第2变形例)

[0116] 以下，关于第1实施方式的第2变形例进行说明。第2变形例主要是第2开关晶体管的布局不同于第1实施方式。图13是表示第1实施方式的第2变形例的半导体装置的平面结构的模式图。图13中主要表示第2变形例与第1实施方式不同的部分，省略其他部分的图示。

[0117] 如图13所示，第2变形例中，第1变形例的多个电源线6110的X方向正侧的端部彼此连接，以及，第1变形例的多个电源线6110的X方向负侧的端部彼此连接。即，电源线6110具有梯状的平面形状。电源线6110在俯视下具有环状部分，以及在环状部分的内侧沿着X方向延伸并与环状部分连接的部分。另外，在电源线6110的环状部分的外侧，配置有俯视下呈环状的电源线6120。

[0118] 俯视下与在Y方向上相邻并成对的电源线6110的一部分以及6120的一部分重叠的半导体层223，以沿着X方向延伸的方式形成。在半导体层223上形成有沿着X方向延伸的栅极绝缘膜224(参照图11)以及栅极电极225。半导体层223、栅极绝缘膜224、栅极电极225包含于第2开关晶体管52。

[0119] 另外，俯视下与在X方向上相邻并成对的电源线6110的一部分以及6120的一部分重叠的半导体层223，以沿着Y方向延伸的方式形成。在半导体层223上形成有沿着Y方向延伸栅极绝缘膜224(参照图11)以及栅极电极225。半导体层223、栅极绝缘膜224、栅极电极225包含于第2开关晶体管52。

[0120] 并且，在图13的第2开关晶体管52中，省略了孔7121以及控制信号线7120等的图示。即，在各个第2开关晶体管52中，配置有孔7121以及控制信号线7120等。另外，图13中虽未图示，在Y方向上相邻的电源线6110与电源线6160之间连接有第1开关晶体管51。

[0121] 其他结构与第1实施方式相同。

[0122] 通过第2变形例也能够获得与第1实施方式相同的效果。

[0123] 在此，电源线6110也可以不具有环状部分，而是具有沿着X方向延伸的部分以及沿着Y方向延伸部分，配置有沿着X方向延伸的半导体层223以及沿着Y方向延伸半导体层223。另外，电源线6120也可以不具有环状的平面形状，而是具有沿着X方向延伸的部分以及沿着Y方向延伸部分，配置有沿着X方向延伸的半导体层223以及沿着Y方向延伸半导体层223。

[0124] 另外,第1开关晶体管51所包含的半导体层213、栅极绝缘膜214以及栅极电极215也可以沿着X方向延伸。

[0125] (第1实施方式的第3变形例)

[0126] 以下,关于第1实施方式的第3变形例进行说明。第3变形例主要是第2布线层22的结构不同于第1实施方式。图14是表示第1实施方式的第3变形例的半导体装置的剖面图。图14中主要表示第3变形例与第1实施方式不同的部分,省略了其他部分的图示。

[0127] 如图14所示,第3变形例中,第2布线层22在第2子布线层202的下方还包含第3子布线层203。即,第3子布线层203被形成在比第2子布线层202更远离第1芯片10的位置。第3子布线层203包含例如电源线8110以及电源线8120。电源线8110与电源线8120沿着Y方向延伸的电源线8110具有俯视下与电源线6110重叠的部分。电源线8120具有俯视下与电源线6120重叠的部分。在绝缘层25形成有用于连接电源线6110与电源线8110的孔6111、用于连接电源线6120与电源线8120的孔6121。例如,电源线8110相当于电连接于第1电源垫81的VDD布线,电源线8120相当于电连接于第2电源垫82的VDD布线。

[0128] 在绝缘层25的俯视下与第2电源域31B重叠的区域外,形成有俯视下与相邻且成对的电源线8110以及8120重叠的多个半导体层233。半导体层233连接于电源线8110以及8120。在半导体层233上形成有栅极绝缘膜234,在栅极绝缘膜234上形成有栅极电极235。栅极绝缘膜234与半导体层233以及栅极电极235相接。栅极电极235在俯视下位于电源线8110与电源线8120之间。在绝缘层25形成有用于连接控制信号线7120与栅极电极235的孔等(未图示)。半导体层233、栅极绝缘膜234、栅极电极235包含于第2开关晶体管52。

[0129] 其他结构与第1实施方式相同。

[0130] 通过第3变形例也能够获得与第1实施方式相同的效果。通过第3变形例,能够进一步稳定电源电位。

[0131] 在此,也可以不设置半导体层233、栅极绝缘膜234以及栅极电极235。

[0132] (第1实施方式的第4变形例)

[0133] 以下,关于第1实施方式的第4变形例进行说明。第4变形例主要是第2布线层22的结构不同于第1实施方式。图15是表示第1实施方式的第4变形例的半导体装置所包含的电路的一例结构的电路图。图15中主要表示第4变形例与第1实施方式不同的部分,省略其他部分的图示。

[0134] 如图15所示,第4变形例中的第2布线层22包含第1子布线层201与第2子布线层202。并且,第1开关晶体管51以及第3开关晶体管53被配置在第1子布线层201。另外,第2开关晶体管52以及第4开关晶体管54被配置在第1子布线层201以及第2子布线层202的两者。

[0135] 通过具有这种电路结构的第4变形例,也能够获得与第1实施方式相同的效果。

[0136] (第1实施方式的第5变形例)

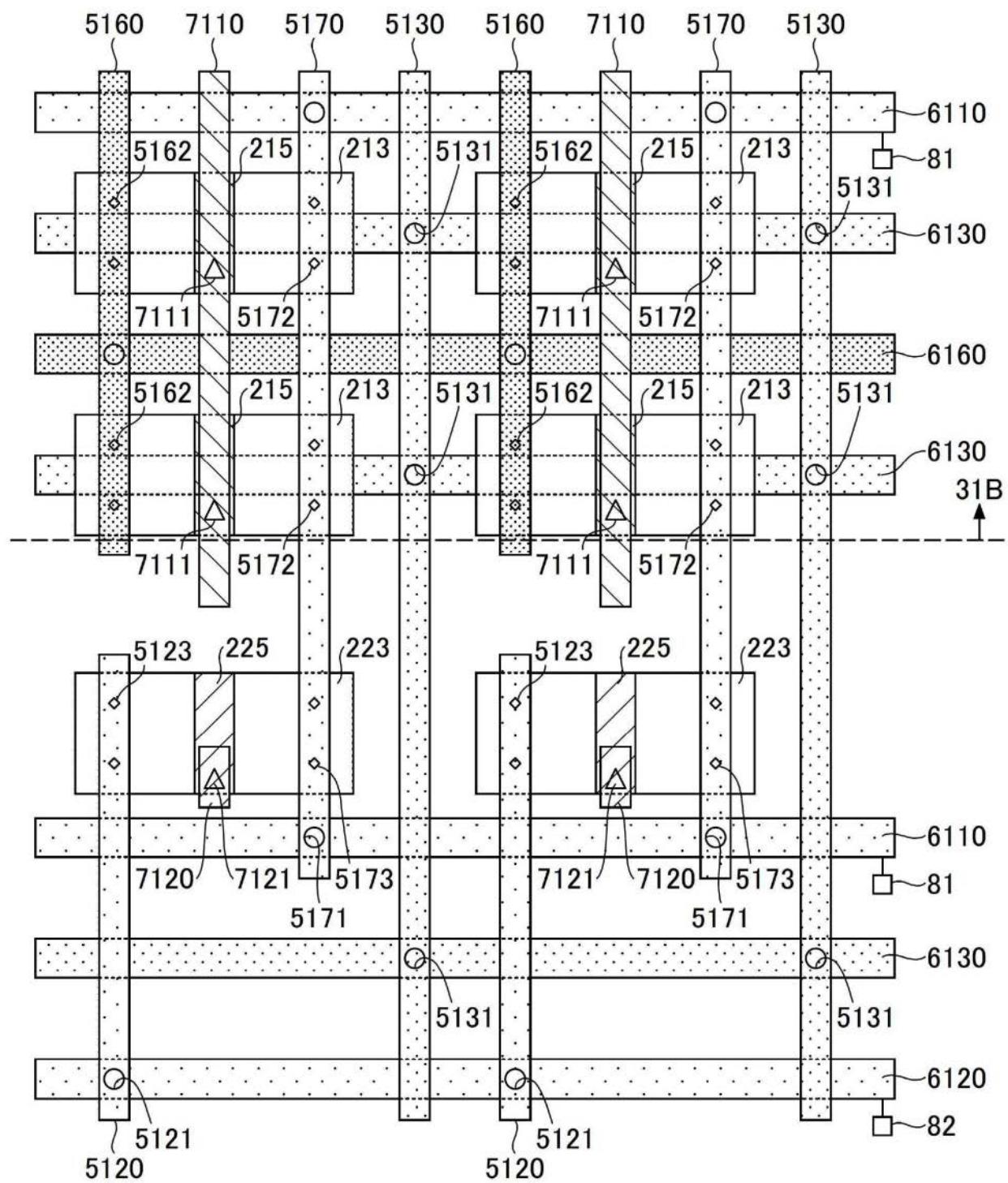

[0137] 以下,关于第1实施方式的第5变形例进行说明。第5变形例主要是开关晶体管的结构不同于第1实施方式。图16以及图17是表示第1实施方式的第5变形例的半导体装置的平面结构的模式图。图16表示第1芯片10以及第2芯片20的内部结构,图17表示第2芯片20的内部结构。图16以及图17中主要表示第5变形例与第1实施方式不同的部分,省略其他部分的图示。

[0138] 如图16以及图17所示,第5变形例中的第2子布线层202具有沿着X方向延伸的电源

线6130。例如,电源线6130相当于VSS布线。电源线6130在俯视下与电源线5130正交,电源线5130以及与该电源线5130正交的电源线6130通过孔5131项连接。

[0139] 第1子布线层201具有沿着Y方向延伸的电源线5170。例如,电源线5170相当于电连接于第1电源垫81的VDD布线。例如,电源线5170与电源线6110正交,电源线5170以及与该电源线5170正交的电源线6110通过孔5171项连接。

[0140] 在俯视下与第2电源域31B重叠的区域内,在电源线5160与电源线5170之间配置有控制信号线7110。半导体层213以在俯视下与电源线5160、控制信号线7110、电源线5170重叠的方式被形成在电源线6130的上方。在控制信号线7110的下方,在半导体层213上形成有栅极绝缘膜214(参照图11)以及栅极电极215。栅极电极215通过孔7111连接于控制信号线7110。另外,半导体层213在栅极电极215的X方向负侧通过孔5162连接于电源线5160,在栅极电极215的X方向正侧通过孔5172连接于电源线5170。孔5162被形成在电源线5160的下方,孔5172被形成在电源线5170的下方。

[0141] 在俯视下与第2电源域31B重叠的区域外,在电源线5120与电源线5170之间配置有控制信号线7120。半导体层223以俯视下与电源线5120、控制信号线7120、电源线5170重叠的方式形成。在控制信号线7120的下方,在半导体层223上形成有栅极绝缘膜224(参照图11)以及栅极电极225。栅极电极225通过孔7121连接于控制信号线7120。另外,半导体层223在栅极电极225的X方向负侧通过孔5123连接于电源线5120,在栅极电极225的X方向正侧通过孔5173连接于电源线5170。孔5123被形成在电源线5120的下方,孔5173被形成在电源线5170的下方。

[0142] 其他结构与第1实施方式相同。

[0143] 通过第5变形例也能够获得与第1实施方式相同的效果。

[0144] 在此,也可以采用如第1变形例(参照图12)或第2变形例(参照图13)的平面结构。另外,也可以在第2子布线层202形成第1开关晶体管51以及第2开关晶体管52。

[0145] (第1实施方式的第6变形例)

[0146] 以下,关于第1实施方式的第6变形例进行说明。第6变形例主要是包含第4开关晶体管的这一点不同于第1实施方式。图18是表示第1实施方式的第6变形例的半导体装置的平面结构的模式图。图18中主要表示第6变形例与第1实施方式不同的部分,省略其他部分的图示。

[0147] 第6变形例的半导体装置除了第1开关晶体管51以及第2开关晶体管52之外,还设置有第4开关晶体管54。

[0148] 如图18所示,在第6变形例中,在俯视下的第2电源域31B的Y方向正侧以及Y方向负侧均配置有沿着X方向延伸的电源线6220。另外,在俯视下与第2电源域31B重叠的区域内,配置有沿着X方向延伸的多个电源线6210。电源线6210以及6220包含于第2子布线层202。例如,电源线6210相当于电连接于第3电源垫83的VSS布线,电源线6220相当于电连接于第4电源垫84的VSS布线。并且,在俯视下与第2电源域31B重叠的区域外,与俯视下在Y方向上相邻并成对的电源线6210以及6220重叠的多个半导体层243。在半导体层243上形成有栅极绝缘膜(未图示)以及栅极电极245。半导体层243、栅极绝缘膜(未图示)、栅极电极245包含于第4开关晶体管54。

[0149] 第1子布线层201具有沿着Y方向延伸的电源线5220。例如,电源线5220相当于VSS

布线。电源线5220在俯视下与多个电源线6210正交，电源线5220以及与该电源线5220正交的电源线6210通过孔5221相连接。

[0150] 另外，在图18的第2开关晶体管52中，省略了孔7121以及控制信号线7120等的图示。即，在各个第2开关晶体管52配置有孔7121以及控制信号线7120等。在图18的第4开关晶体管54中，省略了与栅极电极245连接的孔以及控制信号线等的图示。即，在各个第4开关晶体管54配置有孔以及控制信号线等。另外，图18中虽未图示，在Y方向上相邻的电源线6110与电源线6160之间连接有第1开关晶体管51。

[0151] 其他结构与第1实施方式相同。

[0152] 在具有上述结构的第6变形例的半导体装置中，在无需使标准单元56动作时，第1开关晶体管51成为关状态。其结果，电源线6160(VVDD布线)与第1电源垫81以及第2电源垫82绝缘，电源线6110(VDD布线)对电源线6160(VVDD布线)的电源电位提供会被切断(参照图8～图11)。

[0153] 另外，欲使标准单元56进行动作时，在第2开关晶体管52以及第4开关晶体管54成为关状态之后后，第1开关晶体管51成为开状态。即，使电源线6110与电源线6120之间成为非导通的控制信号被输入到栅极电极225，使电源线6210与电源线6220之间成为非导通的控制信号被输入到栅极电极245之后，使电源线6110与电源线6160之间成为导通的控制信号被输入到栅极电极215。其结果，在电源线6120(VDD布线)与电源线6110(VDD布线)成为绝缘，且电源线6220(VSS布线)与电源线6210(VSS布线)成为绝缘的状态下，VDD的电源电位被提供给电源线6160(VVDD布线)。

[0154] VDD的电源电位被提供给电源线6160(VVDD布线)之后，标准单元56开始动作。此时，若第2开关晶体管52以及第4开关晶体管54的两者都是开状态，来自第2电源垫82的VDD的电源电位也被提供给第2电源域31B，随着急速的电源电位提供会产生噪声，该噪声可能会影响到第1电源域31A。这种急速的电源电位的提供也被称为突流。相对而言，本实施方式中的第2开关晶体管52以及第4开关晶体管54的两者均为关状态，因此，能够抑制突流对动作中的区域造成影响。另外，第2开关晶体管52以及第4开关晶体管54为关状态，因此，相比于第2开关晶体管52或第4开关晶体管54中的仅一方为关状态的情况而言，更能够抑制噪声的发生。

[0155] 标准单元56开始动作之后，提供给第2电源域31B的VDD电源电位的变动变得稳定时，第2开关晶体管52以及第4开关晶体管54成为开状态。即，使电源线6110与电源线6120之间导通的控制信号被输入到栅极电极225，使电源线6210与电源线6220之间导通的控制信号被输入到栅极电极245。其结果，会有稳定的VDD电源电位被提供给第1电源域31A以及第2电源域31B。

[0156] 如上所述，通过第6变形例也能够抑制随着突流产生噪声的现象。

[0157] 在其他实施方式以及变形例中也可以设置第2开关晶体管52的同时加设第4开关晶体管54。若设有第4开关晶体管54，可以不设置第2开关晶体管52。

[0158] 另外，除了第1开关晶体管51之外，还可以加设第3开关晶体管53。若设有第3开关晶体管53，可以不设置第1开关晶体管51。

[0159] (第2实施方式)

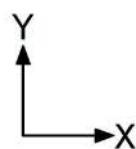

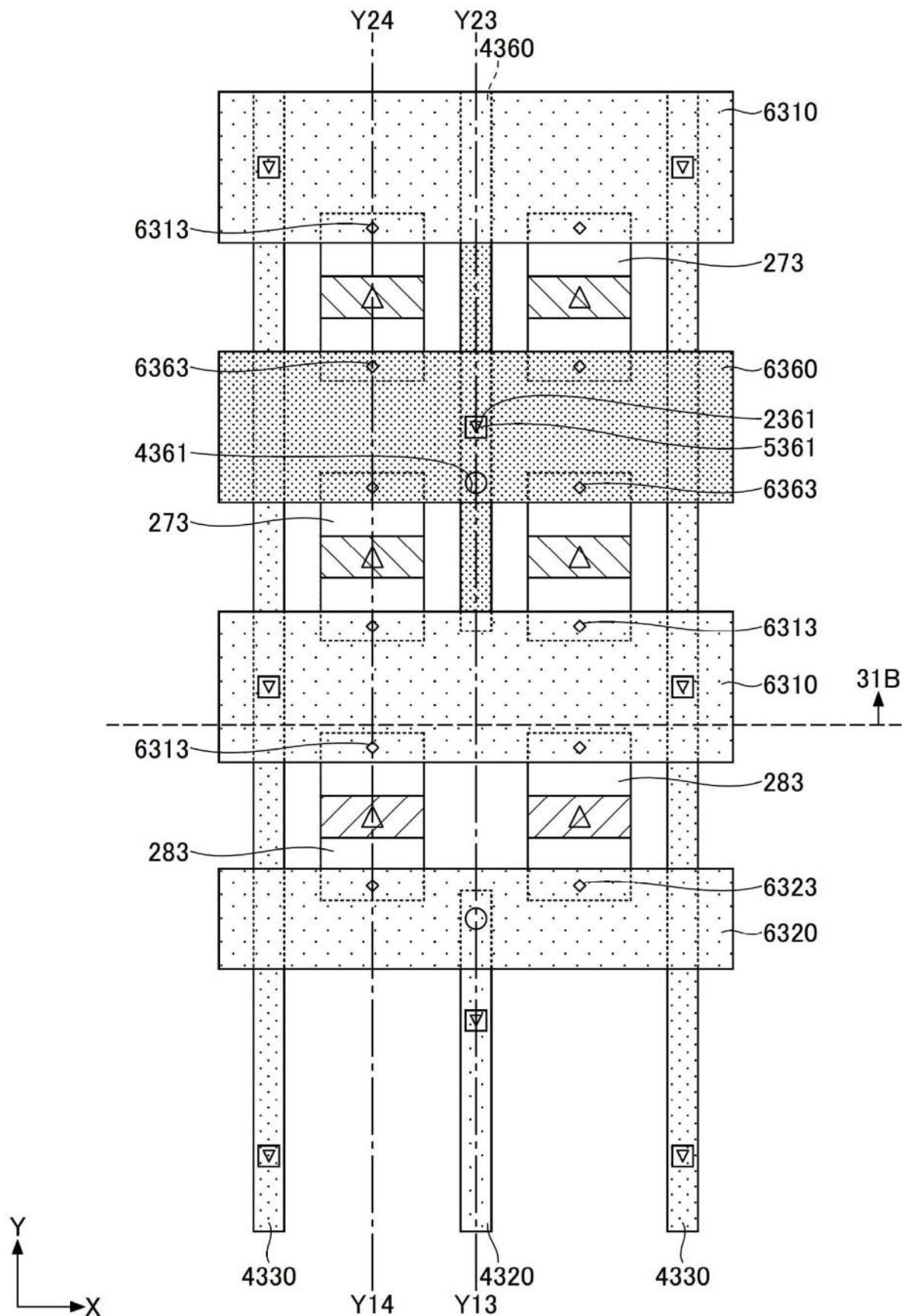

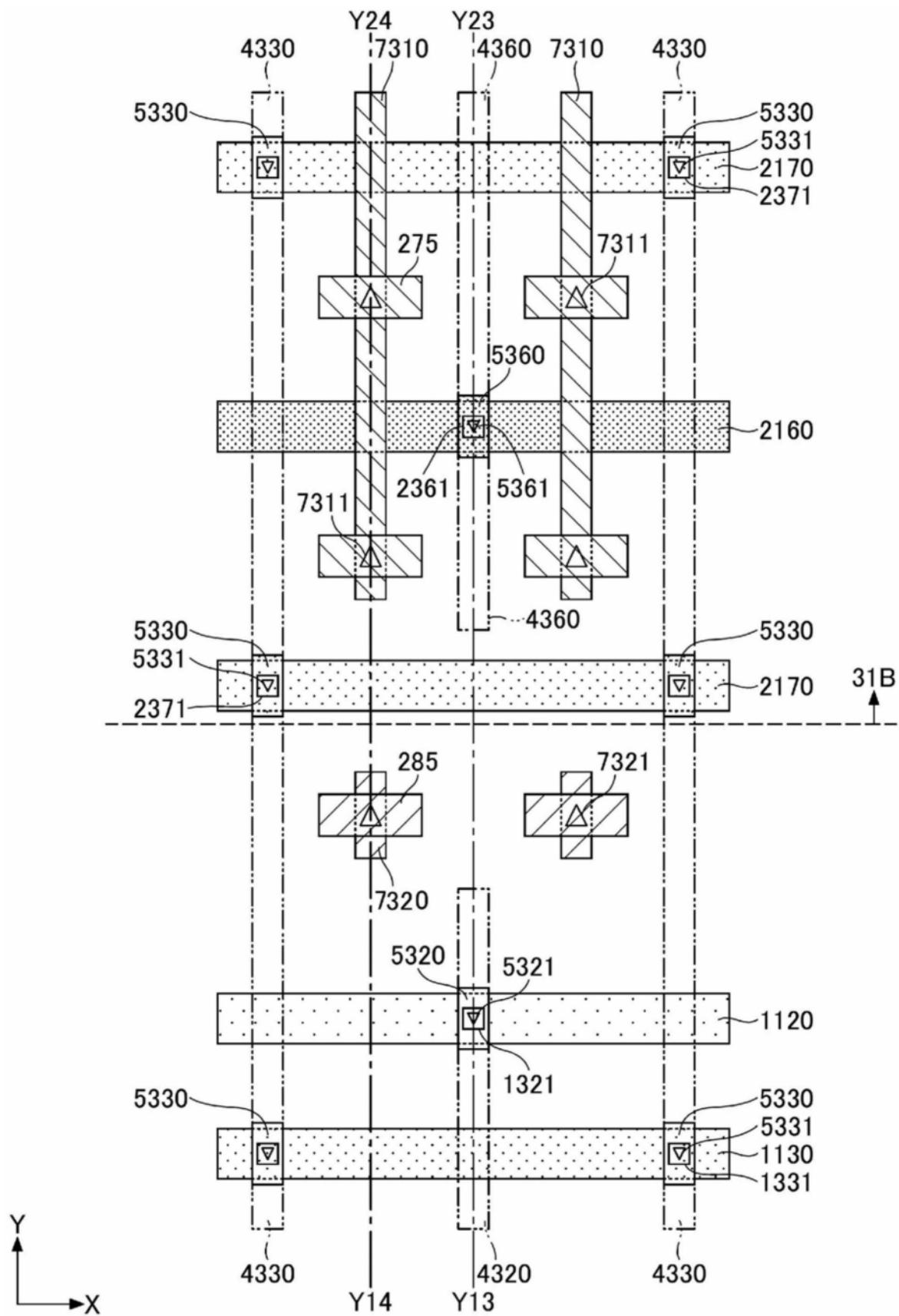

[0160] 接下来，关于第2实施方式进行说明。第2实施方式主要是开关晶体管的配置不同

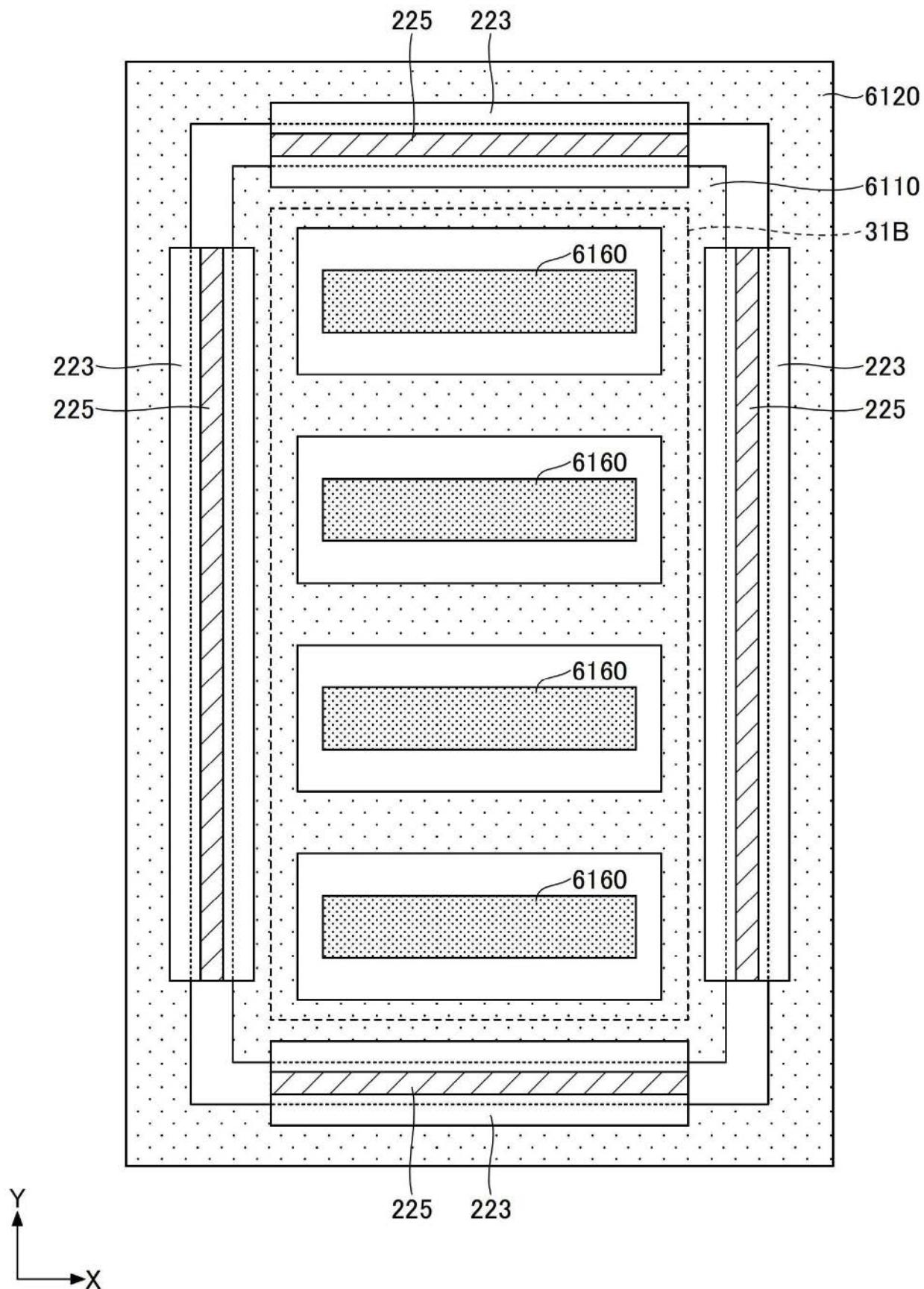

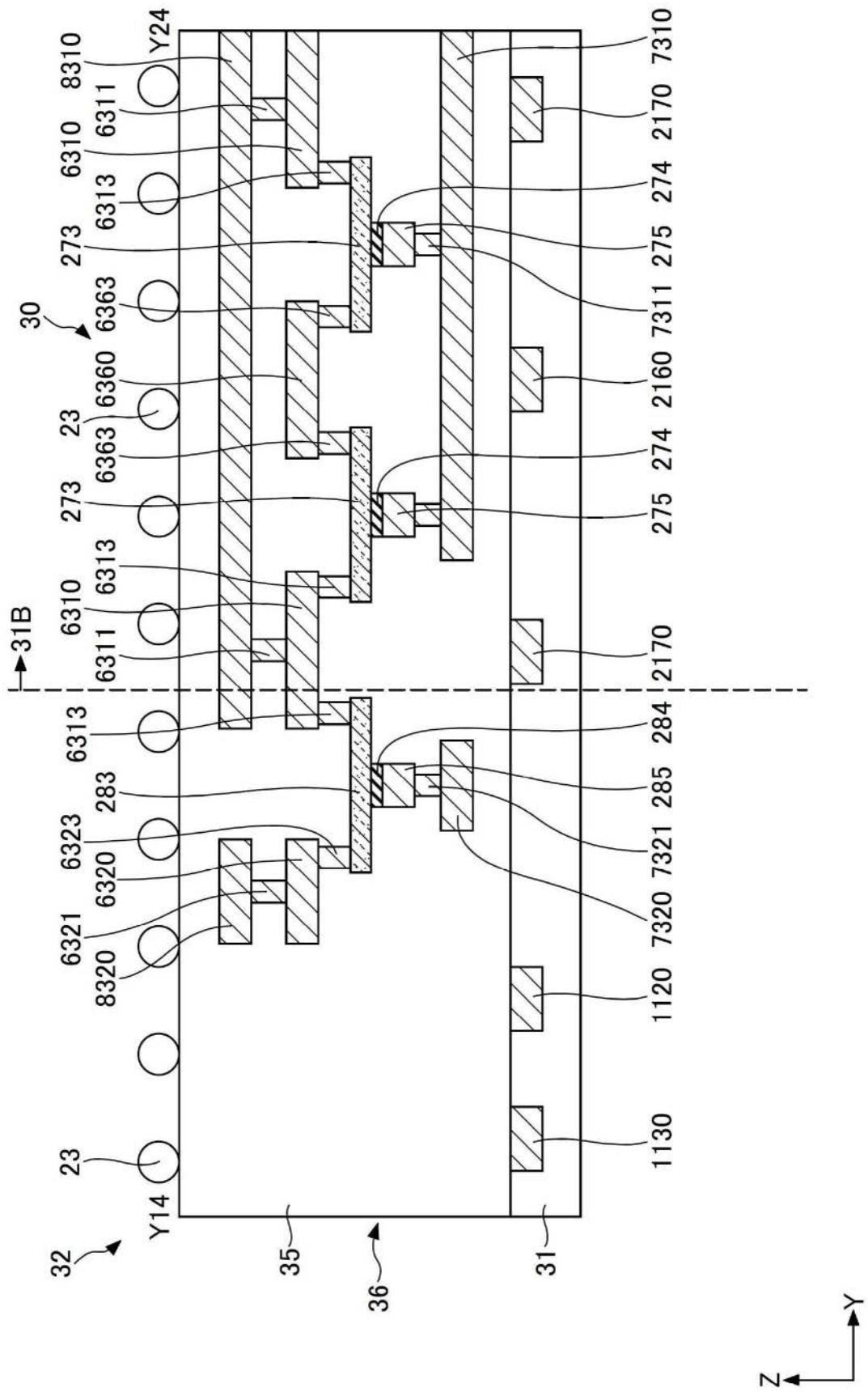

于第1实施方式。图19以及图20是表示第2实施方式的半导体装置的平面结构的模式图。图21以及图22是表示第2实施方式的半导体装置的剖面图。图19主要表示上层侧的电源线,图20主要表示下层侧的电源线。图21相当于沿着图19以及图20中的Y13-Y23线的剖面图,图22相当于沿着图19以及图20中的Y14-Y24线的剖面图。

[0161] 第2实施方式的半导体装置由单一的芯片30构成。芯片30包括基板31、基板31上的布线层36。布线层36包括绝缘层35、形成在绝缘层35内的多个电源线以及孔。

[0162] 芯片30包括沿着X方向延伸的电源线2160、沿着X方向延伸的电源线2170。例如,电源线2160相当于VVDD布线,电源线2170相当于VSS布线。可以有多组电源线2160与电源线2170交替配置。电源线2160与电源线2170被配置在第2电源域31B内。

[0163] 芯片30包括被配置在电源线2160以及2170的Y方向负侧且沿着X方向延伸的电源线1120以及沿着X方向延伸的电源线1130。电源线1120相对于电源线1130而言位于电源线2170侧。例如,电源线1120相当于电连接于第2电源垫82的VDD布线,电源线1130相当于VSS布线。

[0164] 如图21以及图22所示,在基板31形成有沿着X方向延伸的多个槽,电源线2160、电源线2170、电源线1120以及电源线1130被形成在这些槽内。

[0165] 图19~图22中虽未图示,在第2电源域31B内,标准单元56等的电路连接于电源线2160与电源线2170之间。

[0166] 另外,图19~图22中虽未图示,在第2电源域31B外配置有第1电源域31A,在第1电源域31A内,第1驱动缓冲器41、第2驱动缓冲器42以及这些控制电路等的电路连接于电源线1120与电源线1130之间。

[0167] 布线层36包含控制信号线7310、控制信号线7320、电源线5320、电源线5330以及电源线5360。控制信号线7310、控制信号线7320、电源线5320、电源线5330以及电源线5360沿着Y方向延伸。电源线5320在俯视下与电源线1120正交,电源线5330在俯视下与电源线1130或2170正交,电源线5360在俯视下与电源线2160正交。在绝缘层35形成有用于连接电源线5320与电源线1120的孔1321、用于连接电源线5330与电源线1130的孔1331。在绝缘层35形成有用于连接电源线5330与电源线2170的孔2371、用于连接电源线5360与电源线2160的孔2361。控制信号线7310在俯视下与电源线2160以及2170正交。

[0168] 在电源线2170的上方形成有电源线6310,在电源线2160的上方形成有电源线6360。电源线6310以及6360沿着X方向延伸。在绝缘层35的俯视下与第2电源域31B重叠的区域内,形成有俯视下与相邻并成对的电源线6310以及6360重叠的多个半导体层273。在半导体层273下方形成有栅极绝缘膜274,在栅极绝缘膜274下方形成有栅极电极275。栅极绝缘膜274与半导体层273以及栅极电极275相接。栅极电极275俯视下位于电源线6310与电源线6360之间。在绝缘层35形成有用于连接半导体层273与电源线6310的孔6313、用于连接半导体层273与电源线6360的孔6363、用于连接控制信号线7310与各栅极电极275的孔7311。半导体层273、栅极绝缘膜274、栅极电极275包含于第1开关晶体管51。

[0169] 俯视下在电源线1120与电源线2170之间,在与电源线6310以及6360相同的子布线层形成有电源线6320。电源线6320沿着X方向延伸。在绝缘层35,在俯视下与第2电源域31B重叠的区域外,形成有与俯视下相邻并成对的电源线6310以及6320重叠的多个半导体层283。在半导体层283下方形成有栅极绝缘膜284,在栅极绝缘膜284下方形成有栅极电极

285。栅极绝缘膜284与半导体层283以及栅极电极285相接。栅极电极285在俯视下位于电源线6310与电源线6320之间。在绝缘层35形成有用于连接半导体层283与电源线6310的孔6313、用于连接半导体层283与电源线6320的孔6323、用于连接控制信号线7320与各栅极电极285的孔7321。半导体层283、栅极绝缘膜284、栅极电极285包含于第2开关晶体管52。

[0170] 在电源线5360与电源线6360之间形成有沿着Y方向延伸的电源线4360。在绝缘层35形成有用于连接电源线6360与电源线4360的孔4361、用于连接电源线4360与电源线5360的孔5361。

[0171] 在电源线5320与电源线6320之间形成有沿着Y方向延伸的电源线4320。在绝缘层35形成有用于连接电源线6320与电源线4320的孔4321、用于连接电源线4320与电源线5320的孔5321。

[0172] 在沿着Y方向排列的多个电源线5330的上方形成有沿着Y方向延伸的电源线4330。电源线4330例如被形成在与电源线4320以及4360同一个子布线层上。在绝缘层35形成有用于连接电源线4330与电源线5330的孔5331。

[0173] 图19以及图20中虽未图示,可以在电源线6310以及6360的上方形成沿着Y方向延伸的电源线8310,也可以形成用于连接电源线8310与电源线6310的孔6311。另外,可以在电源线6320的上方形成电源线8320,也可以形成用于连接电源线8320与电源线6320的孔6321。

[0174] 在第2实施方式中,欲使标准单元56动作时,在第2开关晶体管52成为关状态之后,第1开关晶体管51成为开状态。即,使电源线6310与电源线6320之间成为非导通的控制信号被输入到栅极电极285之后,使电源线6310与电源线6360之间成为导通的控制信号被输入到栅极电极275。

[0175] VDD的电源电位被提供给电源线6360(VVDD布线),标准单元56开始动作。此时,本实施方式中的第2开关晶体管52为关状态,因此,能够抑制突流,抑制产生噪声。

[0176] 标准单元56开始动作之后,提供给第2电源域31B的VDD电源电位的变动变得稳定时,第2开关晶体管52成为开状态。即,使电源线6310与电源线6320之间导通的控制信号被输入到栅极电极285。其结果,第1电源域31A以及第2电源域31B被提供稳定的VDD电源电位。

[0177] 如上所述,通过本实施方式也能够抑制伴随突流产生的噪声。

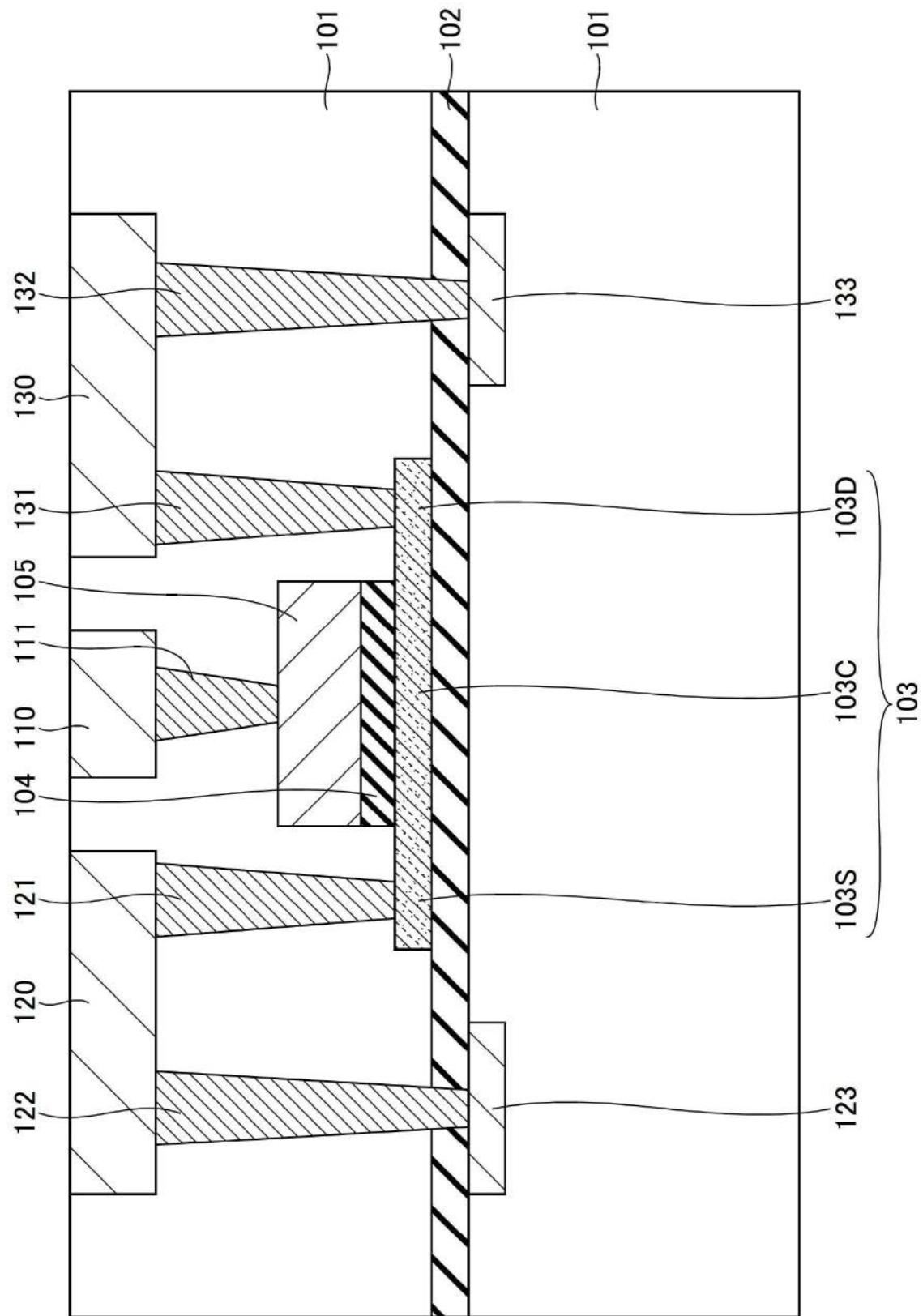

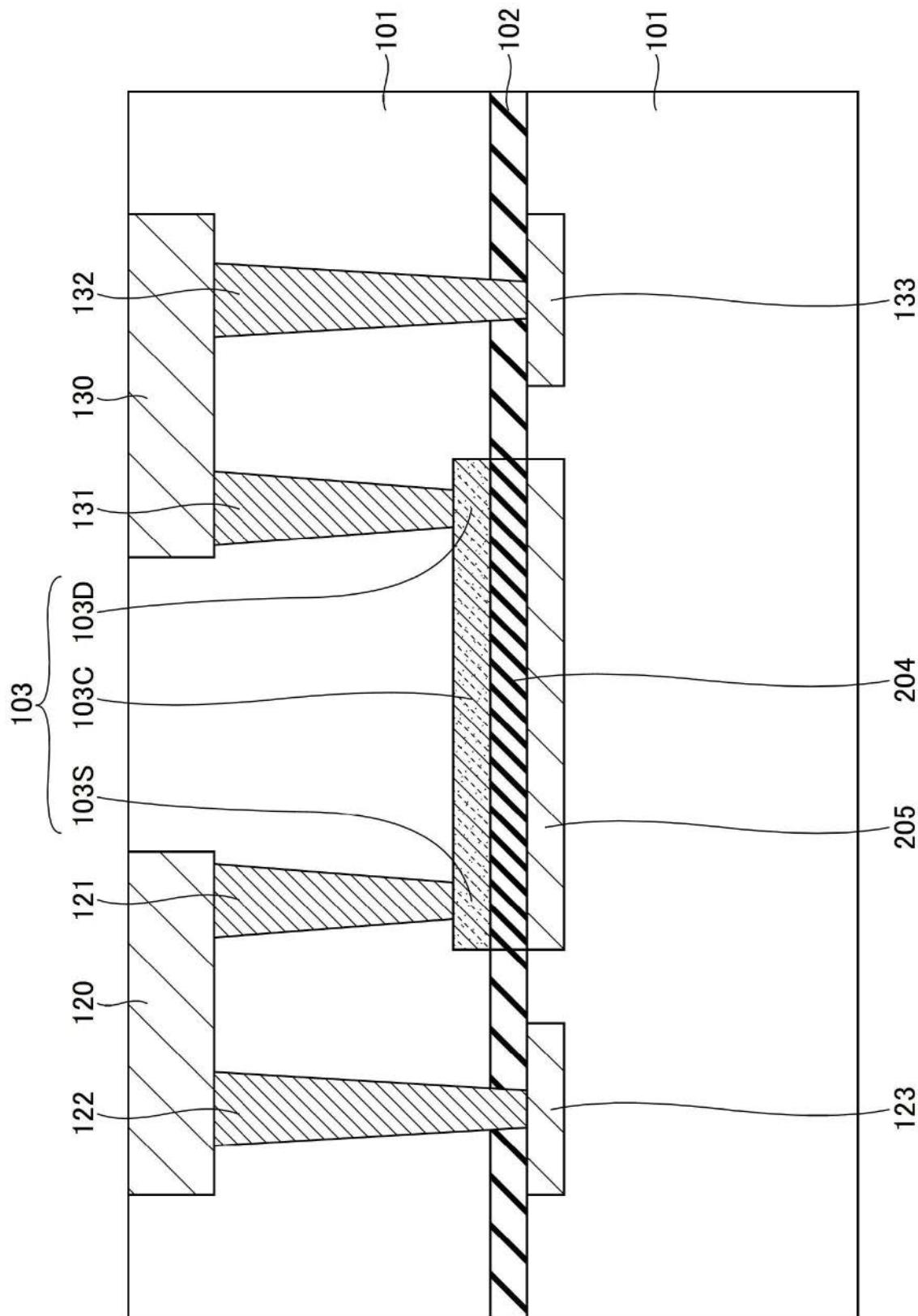

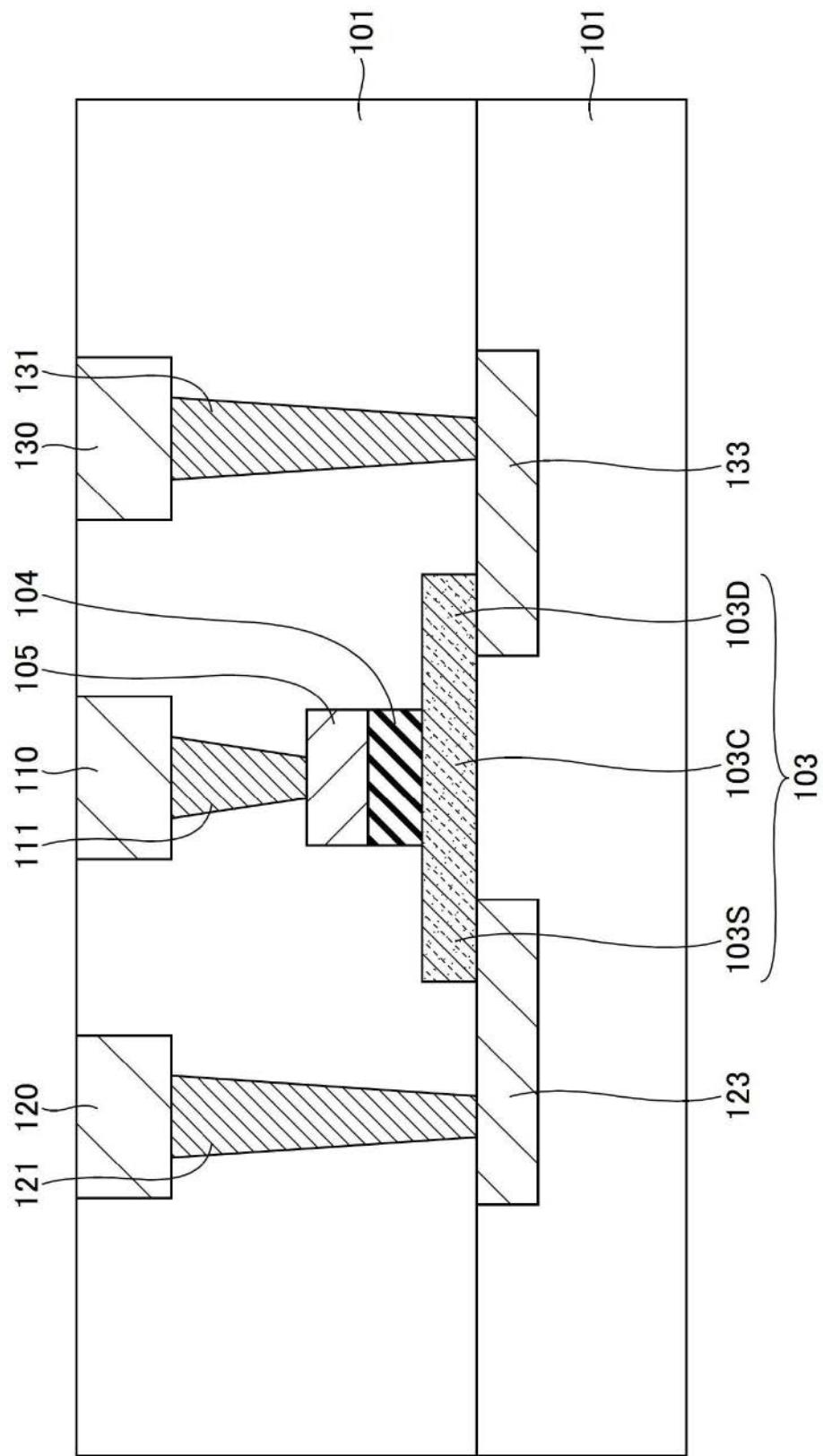

[0178] 在此,关于开关晶体管的剖面结构的概要进行说明。图23~图25是表示开关晶体管的剖面结构的例子的剖面图。

[0179] 图23所示的第1例中,在绝缘层101中设置有基底绝缘膜102,在基底绝缘膜102上设置有半导体层103、栅极绝缘膜104以及栅极电极105。在绝缘层101的表层部设置有控制信号线110、相当于VDD布线的电源线120、相当于VVDD布线的电源线130。半导体层103具有沟道103C、夹着沟道103C的源极103S以及漏极103D。电源线120与源极103S通过孔121连接,电源线130与漏极103D通过孔131连接。在基底绝缘膜102的下方,设置有相当于VDD布线的电源线123、相当于VVDD布线的电源线133。电源线120与电源线123通过孔122连接,电源线130与电源线133通过孔132连接。控制信号线110通过孔111连接于栅极电极105。

[0180] 在图24所示的第2例中,在基底绝缘膜102设置有栅极绝缘膜204,在栅极绝缘膜204的上方设置有半导体层103,在栅极绝缘膜204的下方设置有栅极电极205。其他结构与第1例相同。

[0181] 在图25所示的第3例中,电源线123被设置成连接于半导体层103的源极103S的下面的方式,电源线133被设置成连接于半导体层103的漏极103D的下面的方式。电源线120通过孔121连接于电源线123,电源线130通过孔131连接于电源线133。其他结构与第1例相同。

[0182] 基底绝缘膜的材料例如是氧化硅、氮化硅、碳化硅、氧氮化硅、氧碳化硅等。半导体层的材料例如是InGaZnO (IGZO)、ZnO、ZnSnO、InZnO等。栅极绝缘膜的材料例如是SiO<sub>2</sub>、SiO<sub>x</sub>N<sub>y</sub>、SiN、Al<sub>2</sub>O<sub>3</sub>等。栅电极的材料例如是钼、钛、铬、钽、镁、银、钨、铝、铜、钕、钌、钪等的金属。栅电极的材料可以是石墨烯等。

[0183] 若是根据栅电极与半导体层的叠层关系以及半导体层与VDD布线的连接关系的观点将上述各实施方式中设置的第1～第4开关晶体管51～54分类为第1～第3例,结果如下。即,第1实施方式、第1实施方式的第1～第4变形例以及第1实施方式的第6变形例中设置的第1～第4开关晶体管51～54被分类为第3例。第1实施方式的第5变形例中设置的第1～第4开关晶体管51～54被分类为第1例。第2实施方式中设置的第1～第4开关晶体管51～54被分类为第2例。

[0184] 以上,根据各实施方式对本发明行了说明,但本发明并不限定于上述实施方式中给出的要件。关于上述点,允许在不违背本发明主旨的范围内进行变更,可根据其应用形态适当地决定。

[0185] 符号说明

[0186] 10 第1芯片

[0187] 20 第2芯片

[0188] 31A、31B 电源域

[0189] 41、42、43、44 驱动缓冲器

[0190] 51、52、53、54 开关晶体管

[0191] 56 标准单元。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

冬18

图19

图20

图21

图22

图23

图24

图25