(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5681789号

(P5681789)

(45) 発行日 平成27年3月11日(2015.3.11)

(24) 登録日 平成27年1月16日(2015.1.16)

|              |                          |

|--------------|--------------------------|

| (51) Int.Cl. | F 1                      |

| HO4J 99/00   | (2009.01) HO4J 15/00     |

| HO4W 28/06   | (2009.01) HO4W 28/06 110 |

| HO4W 72/04   | (2009.01) HO4W 72/04 136 |

| HO4B 7/04    | (2006.01) HO4B 7/04      |

請求項の数 28 (全 12 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-507911 (P2013-507911)  |

| (86) (22) 出願日 | 平成22年9月21日 (2010.9.21)        |

| (65) 公表番号     | 特表2013-529008 (P2013-529008A) |

| (43) 公表日      | 平成25年7月11日 (2013.7.11)        |

| (86) 国際出願番号   | PCT/SE2010/051011             |

| (87) 国際公開番号   | W02011/136710                 |

| (87) 国際公開日    | 平成23年11月3日 (2011.11.3)        |

| 審査請求日         | 平成25年8月21日 (2013.8.21)        |

| (31) 優先権主張番号  | PCT/CN2010/000595             |

| (32) 優先日      | 平成22年4月30日 (2010.4.30)        |

| (33) 優先権主張国   | 中国 (CN)                       |

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 598036300<br>テレフォンアクチーボラゲット エル エ<br>ム エリクソン (パブル)<br>スウェーデン国 ストックホルム エスー<br>164 83 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                                                             |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                                                             |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                                                             |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                                                             |

| (74) 代理人  | 100130409<br>弁理士 下山 治                                                              |

最終頁に続く

(54) 【発明の名称】下りリンク制御シグナリングのための送信機、受信機及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

下りリンク制御情報 (DCI) フォーマットのメッセージを送信することによって、送信機 (100) からの下りリンク送信で使用される送信ランク値を受信機 (140) に知らせるための、前記送信機 (100) における方法 (200) であって、

前記 DCI フォーマットは、1 ビットの新規データ・インジケータ (NDI) (14) と、1 ビットのスクランブリング識別子 (SI) (16) と、無効化または有効化された複数のトランスポート・ブロック (TB) (12) とを含み、

前記方法は、

3 から 8 までの前記送信ランク値を默示的に示すように前記 1 ビットのスクランブリング識別子 (16) と一緒に符号化されている 2 つの追加ビット (20) を、前記 DCI フォーマットで送信するステップ (210) を含むことを特徴とする方法。

## 【請求項 2】

前記 DCI フォーマットは、8 × 8 多入力・多出力 (MIMO) 送信をサポートするよう変更された、3 G P P T S 3 6 . 2 1 2 v 9 . 0 . 0 で規定されている DCI フォーマット 2B に基づいており、

前記変更は、前記 2 つの追加ビット (20) の DCI フォーマット 2B への追加を含むことを特徴とする請求項 1 に記載の方法。

## 【請求項 3】

前記スクランブリング識別子(16)は、異なるマルチユーザMIMO(MU-MIMO)ディメンジョンングのために使用されることを特徴とする請求項2に記載の方法。

【請求項4】

2つの符号分割多重グループにおける4つの復調参照信号ポートが、1つのスクランブリング系列とともにシグナリングされることを特徴とする請求項2に記載の方法。

【請求項5】

1つの符号分割多重グループにおけるポート7及び8と別の符号分割多重グループにおけるポート9及び10とが使用されることを特徴とする請求項4に記載の方法。

【請求項6】

複数の前記ポートは、ランク1及びランク2メッセージ用の前記スクランブリング識別子(16)を使用してシグナリングされることを特徴とする請求項5に記載の方法。 10

【請求項7】

複数の前記ポートは、前記2つの追加ビット(20)のいずれかまたは両方を使用してシグナリングされることを特徴とする請求項6に記載の方法。

【請求項8】

1つの符号分割多重グループにおける4つの復調参照信号ポートが、1つのスクランブリング系列とともにシグナリングされることを特徴とする請求項2に記載の方法。

【請求項9】

1つの符号分割多重グループにおけるポート7、8、11及び13が使用されるとともに、長さ4の直交カバー符号が適用されることを特徴とする請求項8に記載の方法。 20

【請求項10】

前記直交カバー符号の長さは、ランク1及びランク2用の前記スクランブリング識別子(16)を使用してシグナリングされることを特徴とする請求項9に記載の方法。

【請求項11】

前記直交カバー符号の長さは、前記2つの追加ビット(20)のいずれかまたは両方を使用してシグナリングされることを特徴とする請求項9に記載の方法。

【請求項12】

前記2つの追加ビット(20)は、他の送信シナリオをシグナリングするために使用されることを特徴とする請求項1に記載の方法。

【請求項13】

前記他の送信シナリオは、シングルセル・マルチユーザ多入力・多出力(MU-MIMO)、協調マルチポイント(CoMP)及びリレー/ヘテロジニアス・ネットワーク(HeiNet)から成るグループから選択されることを特徴とする請求項12に記載の方法。 30

【請求項14】

下りリンク送信で使用される送信ランク値を受信機(140)によって判定することを可能にするための、前記受信機(140)における方法(300)であって、

1ビットの新規データ・インジケータ(NDI)(14)と、1ビットのスクランブリング識別子(SI)(16)と、無効化または有効化された複数のトランスポート・ブロック(TB)(12)と、3から8までの前記送信ランク値を默示的に示すように前記1ビットのスクランブリング識別子(16)と一緒に符号化されている2つのビット(20)とを含む下りリンク制御情報(DCI)フォーマットのメッセージを受信するステップ(310)と、

前記DCIフォーマット及び前記示された送信ランク値に従ってデータを受信するように前記受信機(140)を設定するステップ(320)とを含むことを特徴とする方法。 40

【請求項15】

送信機(100)からの下りリンク送信で使用される送信ランク値を受信機(140)に知らせるよう機能する、前記送信機(100)であって、

下りリンク制御情報(DCI)フォーマットのメッセージを送信するように、送信回路 50

(Tx) に指示するよう機能する処理回路 (120) を備え、

前記 D C I フォーマットは、1 ビットの新規データ・インジケータ (N D I) (14) と、1 ビットのスクランブリング識別子 (S I) (16) と、無効化または有効化された複数のトランスポート・ブロック (T B) (12) と、2 つの追加ビット (20) とを含み、

前記 1 ビットのスクランブリング識別子 (16) 及び前記 2 つの追加ビット (20) は、3 から 8 までの前記送信ランク値を默示的に示すように一緒に符号化されていることを特徴とする送信機。

【請求項 1 6】

前記 D C I フォーマットは、8 × 8 多入力・多出力 (M I M O) 送信をサポートするように変更された、3 G P P T S 3 6 . 2 1 2 v 9 . 0 . 0 で規定されている D C I フォーマット 2 B に基づいており、

前記変更は、前記 2 つの追加ビット (20) の D C I フォーマット 2 B への追加を含むことを特徴とする請求項 1 5 に記載の送信機。

【請求項 1 7】

前記送信機 (100) は、前記スクランブリング識別子 (16) を、異なるマルチユーナ M I M O (M U - M I M O) ディメンジョニングのために使用することを特徴とする請求項 1 6 に記載の送信機。

【請求項 1 8】

前記送信機 (100) は、2 つの符号分割多重グループにおける 4 つの復調参照信号ポートを、1 つのスクランブリング系列とともにシグナリングすることを特徴とする請求項 1 6 に記載の送信機。

【請求項 1 9】

前記送信機 (100) は、1 つの符号分割多重グループにおけるポート 7 及び 8 と別の符号分割多重グループにおけるポート 9 及び 1 0 とを使用することを特徴とする請求項 1 8 に記載の送信機。

【請求項 2 0】

前記送信機 (100) は、複数の前記ポートを、ランク 1 及びランク 2 メッセージ用の前記スクランブリング識別子 (16) を使用してシグナリングすることを特徴とする請求項 1 9 に記載の送信機。

【請求項 2 1】

前記送信機 (100) は、複数の前記ポートを、前記 2 つのビット (20) のいずれかまたは両方を使用してシグナリングすることを特徴とする請求項 1 9 に記載の送信機。

【請求項 2 2】

前記送信機 (100) は、1 つの符号分割多重グループにおける 4 つの復調参照信号ポートを、1 つのスクランブリング系列とともにシグナリングすることを特徴とする請求項 1 6 に記載の送信機。

【請求項 2 3】

前記送信機 (100) は、1 つの符号分割多重グループにおけるポート 7、8、11 及び 13 を使用するとともに、長さ 4 の直交カバー符号を適用することを特徴とする請求項 2 2 に記載の送信機。

【請求項 2 4】

前記送信機 (100) は、前記直交カバー符号の長さを、ランク 1 及びランク 2 用の前記スクランブリング識別子 (16) を使用してシグナリングすることを特徴とする請求項 2 3 に記載の送信機。

【請求項 2 5】

前記送信機 (100) は、前記直交カバー符号の長さを、前記 2 つのビット (20) のいずれかまたは両方を使用してシグナリングすることを特徴とする請求項 2 3 に記載の送信機。

【請求項 2 6】

前記送信機 (100) は、前記 2 つのビット (20) を、他の送信シナリオをシグナリング

10

30

40

50

するためにも使用することを特徴とする請求項15に記載の送信機。

【請求項27】

前記他の送信シナリオは、シングルセル・マルチユーザ多入力・多出力（MIMO）、協調マルチポイント（CoMP）及びリレー／ヘテロジニアス・ネットワーク（HetNet）から成るグループから選択されることを特徴とする請求項26に記載の送信機。

【請求項28】

下りリンク送信で使用される送信ランク値を判定するよう機能する受信機（140）であつて、

1ビットの新規データ・インジケータ（NDI）（14）と、1ビットのスクランブリング識別子（SI）（16）と、無効化または有効化された複数のトランスポート・ブロック（TB）（12）と、3から8までの前記送信ランク値を默示的に示すように前記1ビットのスクランブリング識別子（16）と一緒に符号化されている2つのビット（20）とを含む下りリンク制御情報（DCI）フォーマットのメッセージを受信するよう機能する受信回路（Rx）と、

前記DCIフォーマット及び前記示された送信ランク値に従ってデータを受信するよう前に記受信機（140）を設定するよう機能する処理回路（160）とを備えることを特徴とする受信機。

【発明の詳細な説明】

【技術分野】

20

【0001】

本発明は、全体として、送信機、受信機及びそれらの方法に関するものであり、特に、LTE-Advanced下りリンク送信モード用の制御シグナリング設計のような、例えばLTE-Advanced用の下りリンク制御シグナリング設計に関するものである。

【背景技術】

【0002】

第3世代パートナシップ・プロジェクト（3GPP）は、UMTS（ユニバーサル・モバイル・テレコミュニケーション・システム）及びLTE（ロング・ターム・エボリューション）の標準化に関与している。LTEは、下りリンク及び上りリンクの両方で高いデータレートに達することが可能な高速のパケットベース通信を実現するための技術である。LTEは、UMTSに対して、次世代のモバイル通信システムと考えられている。高いデータレートをサポートするために、LTEは、最大20MHzのシステム帯域幅を許容する。LTEは、更に、異なる複数の周波数帯域で動作可能であるとともに、少なくともFDD（周波数分割複信）及びTDD（時分割複信）で動作可能である。LTEで使用される変調技術または伝送方法は、OFDM（直交周波数分割多重）として知られている。

30

【0003】

次世代モバイル・テレコミュニケーション・システム、例えば、IMT-advanced（国際モバイル・テレコミュニケーション）、及びLTEの進化形であるLTE-Advancedの少なくともいずれかについては、最大100MHzの帯域幅のサポートが検討されている。LTE及びLTE-Advancedの両方では、無線基地局は、eNBまたはeNodeBとして知られており、「e」は進化型（evolved）を表す。更には、高いデータレートをユーザ装置に提供するために、ブリコーディング/ビームフォーミング技術によって複数のアンテナを使用可能である。このため、LTE及びLTE-Advancedは、両方ともMIMO（多入力・多出力）無線システムの例である。MIMO及びOFDMベースのシステムの他の例は、WiMAX（マイクロ波アクセスのための世界的な相互運用）である。

40

【0004】

3GPPリリース10（Rel-10）、例えば技術仕様（Technical Specification）36.814 V1.5.0（2009-11）として規定されたLTE-Advanced

50

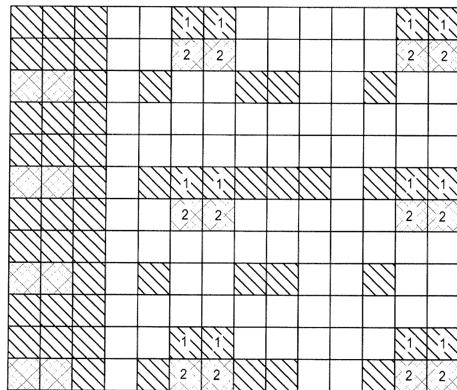

cedでは、30bps/Hzという、LTE-Advancedの下りリンク・ピーク・スペクトル効率を実現するために、高度な8×8高次MIMOを使用して、最大8レイヤの送信がサポートされる。リリース10では、最大8つの（復調RSまたはDM-RSと称される）UE固有の参照信号が、チャネル復調を目的として導入されることも合意されている。これまでに、図1に示すように、通常のCP（サイクリック・プレフィックス）を有するDM-RSランク1～8パターンが決定されている。

#### 【0005】

CDM+FDM（符号及び周波数分割多重）によって多重化される、合計で8つのDM-RSポートが定義されている。DM-RSのオーバヘッドは同一となり、即ち、レイヤごとに12個のリソースエレメント（RE）となる。最大で2つのCDMグループがサポートされる。各CDMグループは、最大で4つのDM-RSポートを有する。DM-RSポートのナンバリングは、CDMグループ1：ポート7/8/11/13、及び、CDMグループ2：ポート9/10/12/14として定義されている。直交カバー符号（OCC：Orthogonal cover codes）が、時間領域のみにわたって定義されている。

#### 【0006】

図1は、最大でランク8送信をサポートするDM-RSパターンを図示している。リリース9のデュアルレイヤ・ビームフォーミング、即ち、下りリンク送信モード8（TM8）の場合、（数値「1」で示される）CDMグループ1のみが使用される一方、（数値「2」で示される）CDMグループ2に対して留保されたREは、データ送信用に使用される。

10

20

#### 【0007】

下りリンク制御情報（DCI）フォーマット2Bは、3GPP TS 36.212 v9.0.0（2009-12）において定義されており、その開示を本明細書では援用する。DCIフォーマット2Bは、最大で2つのスクランブリング系列とともにDM-RSポート7/8が動的に割り当てられる、シングルユーザ（SU）ケース及びマルチユーザ（MU）ケースについてのトランスペアレント構成だけでなく、ランク1とランク2との間の動的なランク・アダプテーションを可能にする。図2は、DCIフォーマット2Bで搬送される一部の情報によって默示的に示される、異なる複数のアプリケーション・ケースをリストしたテーブル10を図示している。無効化/有効化されたトランスポート・ブロック（TB）12と、1ビットの新規データ・インジケータ（NDI）14と、1ビットのスクランブリング識別子（SI）16によって、情報が符号化される。これらのビットは、「メッセージ」列にリストされている情報を符号化する。

30

#### 【発明の概要】

#### 【0008】

本願で開示及びクレームされている1つ以上の実施形態によれば、リリース10の機能、例えば、シングルセルMIMO、CoMP、または場合によってはリレー/HetNetをサポートするために、DCIフィーマット2Bの最小限の拡張が提案される。

#### 【0009】

開示した実施形態では、リリース10のMIMO送信をサポートするために、リリース10において新たなDCIフォーマットが提案される。一部の実施形態では、最大8のランクをシグナリングするために、ランク1及びランク2という重要なケースについて異なるMU-MIMOディメンジョニングをサポートすると同時に、SIビット16を再利用することによって、2つの特別なビットのみが、それ以外はフォーマット2Bと一致するDCIフォーマットに対して導入される。この新たなDCIフォーマットは、場合によっては、シングルセルの下りリンク送信だけでなく、他の何らかのリリース10の機能、例えばCoMPまたはリレー/HetNetをサポートできる。

40

#### 【0010】

一実施形態は、DCIフォーマットのメッセージをシグナリングすることによって、送信機からの下りリンク送信で使用されるシグナリング・レイヤの数を受信機に知らせるための、送信機における方法に関連している。DCIフォーマットで送信されるのは、下り

50

リンク送信で使用されるレイヤの数を示す2つのビットである。

【0011】

他の実施形態は、下りリンク送信で使用されるレイヤの数を受信機によって判定することを可能にするための、受信機における方法に関連している。レイヤの数を示す2つのビットを含むDCIフォーマットでメッセージが受信される。受信機は、DCI及びレイヤの数に従ってデータを受信するように設定される。

【0012】

更に他の実施形態は、送信機からの下りリンク送信で使用されるシグナリング・レイヤの数を受信機に知らせるよう機能する送信機に関連している。送信機は、下りリンク送信におけるレイヤの数を示す2つのビットを含むDCIフォーマットのメッセージをシグナリングするように機能するシグナリング回路を備える。

【0013】

更に他の実施形態は、下りリンク送信で使用されるレイヤの数を判定するよう機能する受信機に関連している。受信機は、レイヤの数を示す2つのビットを含むDCIフォーマットのメッセージを受信するよう機能する受信回路を備える。受信機は、更に、DCI及びレイヤの数に従ってデータを受信するように受信機を設定するよう機能する処理回路を備える。

【図面の簡単な説明】

【0014】

【図1】最大でランク8の送信をサポートする、先行技術のDM-RSパターンの機能ブロック図。

20

【図2】先行技術のDCIフォーマット2Bに従ったDCIビットの符号化と、シグナリングされるアプリケーション・ケースとを図示するテーブル。

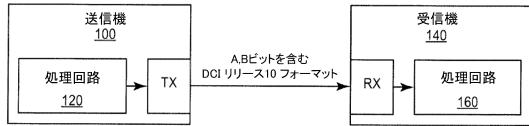

【図3】本発明の一実施形態に従って送信機がCDIビットを送信する無線通信ネットワークにおける、送信機及び受信機の機能ブロック図。

【図4】本発明の一実施形態に係る、DCIビットの1つの符号化と、シグナリングされるアプリケーション・ケースとを図示するテーブル。

【図5】本発明の他の実施形態に係る、DCIビットの1つの符号化と、シグナリングされるアプリケーション・ケースとを図示するテーブル。

【図6】本発明の更に他の実施形態に係る、DCIビットの1つの符号化と、シグナリングされるアプリケーション・ケースとを図示するテーブル。

30

【図7】本発明の更に他の実施形態に係る、DCIビットの1つの符号化と、シグナリングされるアプリケーション・ケースとを図示するテーブル。

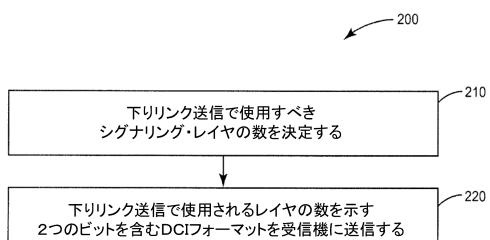

【図8】送信機からの下りリンク送信で使用されるシグナリング・レイヤの数を受信機に知らせる、送信機による方法のフロー図。

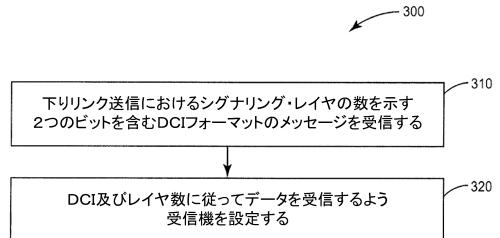

【図9】送信機からの下りリンク送信で使用されるシグナリング・レイヤの数を判定する、受信機による方法のフロー図。

【発明を実施するための形態】

【0015】

上述のように、リリース10は8レイヤ送信をサポートする。TM8は、リリース9として規定されたままである。DCIフォーマット2Bには、いくつかの不足があり、結果として、新たなDCIフォーマットがリリース10に対して必要となる。第1に、最大で8レイヤの送信をサポートするため、適切なデータ復調用にUEに対してランクを知らせる必要があることである。DCIフォーマット2Bでは、これを直接的には規定しておらず、むしろ、1つのTB12が無効化されているか否かによってランク1または2を示唆する。第2に、リリース10におけるMU-MIMOディメンジョニング(dimensioning)によれば、ランク1~2は、SU/MUに適用可能である一方、ランク3~8は、SUのみに対して定義されていることである。これは、SU及びMUが2レイヤまでの送信について同一の範囲を有するリリース9 TM8とは異なる。第3に、新たなDCIフォーマットが、シングルセルMIMOだけでなく、協調マルチポイント(CoMP:Coordina

40

50

ted Multipoint)、または場合によってはリレー (relaying) / ヘテロジニアス・ネットワーク (HetNet : heterogeneous network) のために使用されうることである。最後の検討事項は、リリース 9 TM 8 はリリース 10 の 8 レイヤ送信のサブセットとなるため、DCI フォーマット 2B は、新たな DCI フォーマットにおいて可能な限り再利用されるべきであるということである。

#### 【0016】

本書では、種々のアプリケーションまたは検討事項に適用される、本発明の種々の実施形態を提示する。本書では、提案する DCI フォーマット、例えば、1 ビットの NDI 14、1 ビットの SI 16、無効化 / 有効化された TB 12、並びに、A 及び B と表記される 2 つの追加ビット 20 を説明するために、ペイロードの一部のみを説明する。当然ながら、他の目的のための更なるビット・フィールドも存在する。

#### 【0017】

図 3 は、(チャネル品質または構成に基づいて) 下りリンク送信で使用すべきレイヤの数を決定するよう機能する処理回路 120 を備える、無線基地局のような送信機 100 を図示している。レイヤ数 (即ち、ランク値) が決定されると、送信機 100 は、送信回路 (Tx) を介して、ランク値を示す情報を、3GPP リリース 10 に適合した DCI フォーマットで、ユーザ装置のような受信機 140 に送信する。一部の実施形態では、リリース 10 の DCI フォーマットは、フォーマット 2B の拡張であり、ランク値を示すために使用される 2 つのビット A、B を含む。受信機 140 は、受信回路 (Rx) を介して、DCI フォーマットの情報を受信して、受信機は、当該情報から、送信に使用されたレイヤの数を処理回路 160 において判定する。

#### 【0018】

送信機 100 は、下りリンク制御情報 (DCI) フォーマットのメッセージを送信するように送信回路 (Tx) に指示するよう機能する処理回路 120 を備え、DCI フォーマットは、送信ランク値とも称されるレイヤ数を示す 2 つのビット (A, B) を含む。

#### 【0019】

受信機 140 は、レイヤ数を示す 2 つのビットを含む DCI フォーマットのメッセージを受信するよう構成された受信回路 (Rx) と、下りリンク制御情報及びレイヤ数に従ってデータを受信するよう受信機 140 を設定するよう機能する処理回路 160 とを備える。

#### 【0020】

無線通信ネットワークにおける送信機 100 と受信機 140 との間のシグナリングを可能にするための、本書で説明する仕組みは、本書で説明する実施形態の機能を実行するためのコンピュータプログラム・コードとともに、送信機 100 内の処理回路 120 または受信機 140 内の処理回路 160 のような、1 つ以上のプロセッサを通じて実装されうる。上述のプログラム・コードは、例えば、送信機 100 または受信機 140 においてそれぞれ処理回路 120、160 にロードされた場合に本発明の実施形態を実行するコンピュータプログラム・コードを含む、機械可読データ記憶媒体の形式で、コンピュータプログラムとしても提供されうる。このような機械可読データ記憶媒体の 1 つは、CD-ROM ディスクの形式でもよい。当然ながら、他の適切なデータ記憶媒体には、不揮発性メモリ、磁気ディスク等が含まれてもよい。コンピュータプログラム・コードは、更に、純正のプログラム・コードとしてサーバ上で提供され、送信機 100 または受信機 140 にダウンロードされてもよい。

#### 【0021】

##### ランク・シグナリング用の SI

図 4 のテーブル 18 は、両方のトランスポート・ブロック 12 が有効化された場合に、ランク 2 のみが SU / MU であり、ランク 3 ~ 8 は SU のみであることを図示している。この場合、一実施形態によれば、シグナリング・オーバヘッドは、新たに定義されたビット A, B 20 とともに 1 ビットの SI 16 を使用することによって低減され、これにより、(1 ビット SI 16 は SU ケース用には使用されないため) ランク値 3 ~ 8 を UE

10

20

30

40

50

に默示的に知らせる。ランク 2 の送信は、ハイブリッド S U / M U である。一実施形態では、1 ビット S I 1 6 は、同時にスケジューリングされた (co-scheduled) 複数の U E を区別するために使用される。この実施形態では、値 (0, 0) の新たな 2 ビット 2 0 は、U E に対してランク値 2 を一意に知らせるために使用される。図 4 は、2 ビット 2 0 及び 1 ビット S I 1 6 の、1 つの代表的な符号化を図示しており、他の符号化は本発明の範囲内である。

【 0 0 2 2 】

M U - M I M O ディメンジヨニング用の S I

上述の実施形態に加えて、リリース 1 0 の U E に対して、より複雑な S U / M U ケースを知らせる（例えば、D M - R S ポートまたは C D M グループの通知）ために、新たなビット 2 0 を、ランク 1 ~ 2 用に効率的に使用することも可能である。 10

【 0 0 2 3 】

図 5 のテーブル 2 2 には、2 つの D M - R S ポートが、2 つのスクランブリング系列とともにシグナリングされる、第 1 のケースを図示している。なお、最初の 5 行は D C I フォーマット 2 B と同一であり、1 ビット S I 1 6 は C D M - 1 におけるポート 7 / 8 をシグナリングするために使用される。このケースでは、2 つの新たなビット 2 0 は、ランク 1 には使用されずに留保される。図 5 は、ランク 3 ~ 8 をシグナリングするための、2 つのビット 2 0 及び 1 ビットの S I 1 6 の 1 つの代表的な符号化を図示しており、他の符号化は本発明の範囲内である。 20

【 0 0 2 4 】

図 6 のテーブル 2 4 には、2 つの C D M グループにおける 4 つの D M - R S ポートが、1 つのスクランブリング系列とともにシグナリングされる、第 2 のケースを図示している。このケースでは、C D M - 1 におけるポート 7 / 8 と C D M - 2 におけるポート 9 / 1 0 とが使用され、長さ 2 の O C C が適用される。一実施形態では、最初の 1 0 行のランク 1 / 2 メッセージは、ポートのシグナリング用に 1 ビット S I 1 6 を使用してもよい。他の実施形態では、当該ポートは、新たなビット 2 0 を利用することによってシグナリングされる。同時にスケジューリングされた複数の U E には直交するポートが割り当てられるため、リリース 9 及びリリース 1 0 の同時にスケジューリングされた複数の U E は、同一のスクランブリング系列を用いたとしても、有効化されうる。したがって、1 ビット S I 1 6 は、フリーであるとともに、同時にスケジューリングされた U E 間の更なる区別はもはや必要ないため、ポートのシグナリングのために使用されうる。このため、スクランブリング系列の使用が制限される。他の実施形態では、新たなビット 2 0 のうちの A ビットあるいは B ビットが、スクランブリング系列の制限を解除するために、1 ビット S I 1 6 と同じことを行うように利用されうる。図 6 は、2 つのビット 2 0 及び 1 ビット S I 1 6 の 1 つの代表的な符号化を図示しており、他の符号化は本発明の範囲内である。 30

【 0 0 2 5 】

図 7 のテーブル 2 6 には、C D M グループ 1 における 4 つの D M - R S ポートが 1 つのスクランブリング系列とともにシグナリングされる、第 3 のケースを図示している。このケースでは、C D M - 1 のポート 7 / 8 / 1 1 / 1 3 が使用され、長さ 4 の O C C が適用される。一実施形態では、最初の 1 0 行のランク 1 / 2 メッセージは、O C C 長をシグナリングするために 1 ビット S I 1 6 を使用してもよい。テーブル 2 6 は、図 6 のテーブル 2 4 と同一であるが、1 ビット S I 1 6 の再使用についての説明が異なる。他の実施形態では、新たなビット 2 0 のうちの A ビットあるいは B ビットが、スクランブリング系列の制限を解除するために、1 ビット S I 1 6 と同じことを行うように利用されうる。図 7 は、2 つのビット 2 0 及び 1 ビット S I 1 6 の 1 つの代表的な符号化を図示しており、他の符号化は本発明の範囲内である。 40

【 0 0 2 6 】

図 8 は、e N B のような、無線通信ネットワーク内の送信機によって、受信機にシグナリング・レイヤ情報を送信する方法 2 0 0 を図示している。送信機は、下りリンク送信で使用すべきシグナリング・レイヤの数を決定し（ブロック 2 1 0）、次に、下りリンク送 50

信で使用されるレイヤの数を示す2つのビット20を含むDCIフォーマットを受信機に送信する(ブロック220)。種々の実施形態では、上述のように、2つのビット20は、シグナリング・レイヤ情報に加えて種々の情報を伝えるために、SI16のような、既存のDCIフォーマット2Bビットと一緒に符号化されてもよい。

#### 【0027】

図9は、UEのような、無線通信ネットワーク内の受信機によって、シグナリング・レイヤ情報を受信する方法300を図示している。受信機は、下りリンク送信におけるシグナリング・レイヤの数を示す2つのビット20を含むDCIフォーマットのメッセージを受信して(ブロック310)、次に、DCI及びレイヤ数に従ってデータを受信するよう、受信回路Rxを設定する(ブロック320)。種々の実施形態では、上述のように、2つのビット20は、シグナリング・レイヤ情報に加えて種々の情報を伝えるために、SI16のような、既存のDCIフォーマット2Bビットと一緒に符号化されてもよい。

10

#### 【0028】

##### MU-MIMOディメンジョンング用のSI

なお、上記の実施形態では、一部の例(例えばランク1)では、2つの新たなビット20は留保される。一実施形態において、これらの例では、2つの新たなビット20は、他のアプリケーション・シナリオ、特に、主としてランク1を対象としたシナリオをシグナリングするために利用されうる。このようなシナリオには、例として、かつ、限定することなく、シングルセルMU-MIMO、CoMP、またはリレー/HetNetが含まれる。シグナリング情報によって、留保されたビットの任意の符号化に従って、それらのシナリオのうちの1つにおいて下りリンク送信が行われるかどうかをUEに対して伝えることが可能であり、これは、当業者によって、特定のアプリケーションに対して容易に導かれうるとともに、本開示の教示に含まれる利点を有する。

20

#### 【0029】

DCIフォーマット2Bに基づく、かつ、リリース10のMIMO送信をサポートするために2つの新たなビット20を使用する、リリース10用の新たなDCIフォーマットは、上述の実施形態によれば、数々の効果をもたらす。まず、既存の1ビットSI16を使用し、かつ、2つの新たなビット20のみを導入して、一緒に符号化することによって、2レイヤを上回る(実際には、8レイヤもの)ランク値を默示的に知らせることが可能である。標準規格のDCIフォーマット2Bを、可能な最大限まで再使用することが可能である。次に、異なるMU-MIMOディメンジョンングのサポートについて、ランク1及びランク2という重要なケースに対してスクランブリングの通知をそれでも許容しつつ、効率的に制御シグナリングを省くために、1ビットSI16を可能な限り再使用することが可能である。最後に、提案したリリース10用のDCIフォーマットは、SUアプリケーションとMUアプリケーションとを区別することが可能であるとともに、ランク1のケースにおける他の可能性のあるリリース10の機能(例えば、CoMP、リレー、及びHetNet)のために使用可能である。

30

#### 【0030】

当然ながら、本発明は、本発明の本質的な特徴から逸脱することなく、本書で具体的に説明した手法以外の手法で実施されてもよい。本発明の実施形態は、あらゆる点で例示的であり、かつ、限定的ではないと解釈されるべきであり、添付の特許請求の範囲の意義及び均等の範囲内で生じるあらゆる変更が本発明に包含されることを意図している。

40

【図1】

1 1 1 1

2 2 2 2

CDMグループ1: 最大4レイヤ

CDMグループ2: 最大4レイヤ

FIG. 1

先行技術

【図2】

| TB-1 | TB-2 | NDI<br>(1ビット) | SI<br>(1ビット) | メッセージ                                      |

|------|------|---------------|--------------|--------------------------------------------|

| 有効化  | 無効化  | 0 (TB-2内)     | 0又は1         | SU/MU, ランク-1, ポート-7<br>スクランブリング系列: 0又は1    |

| 有効化  | 無効化  | 1 (TB-2内)     | 0又は1         | SU/MU, ランク-1, ポート-8<br>スクランブリング系列: 0又は1    |

| 無効化  | 有効化  | 0 (TB-1内)     | 0又は1         | SU/MU, ランク-1, ポート-7<br>スクランブリング系列: 0又は1    |

| 無効化  | 有効化  | 1 (TB-1内)     | 0又は1         | SU/MU, ランク-1, ポート-8<br>スクランブリング系列: 0又は1    |

| 有効化  | 有効化  | 0又は1          | 0又は1         | SU/MU, ランク-2, ポート-7/8,<br>スクランブリング系列: 0又は1 |

FIG. 2

先行技術

【図3】

FIG. 3

【図4】

| TB-1 | TB-2 | NDI<br>(1ビット) | SI<br>(1ビット) | 2ビット<br>(A, B) | メッセージ                 |

|------|------|---------------|--------------|----------------|-----------------------|

| 有効化  | 有効化  | 0又は1          | 0又は1         | (0,0)          | SU/MU, ランク-2, ポート-7/8 |

| 有効化  | 有効化  | 0又は1          | 0            | (0,1)          | SU, ランク-3, ポート-7-9    |

| 有効化  | 有効化  | 0又は1          | 0            | (1,0)          | SU, ランク-4, ポート-7-10   |

| 有効化  | 有効化  | 0又は1          | 0            | (1,1)          | SU, ランク-5, ポート-7-11   |

| 有効化  | 有効化  | 0又は1          | 1            | (0,1)          | SU, ランク-6, ポート-7-12   |

| 有効化  | 有効化  | 0又は1          | 1            | (1,0)          | SU, ランク-7, ポート-7-13   |

| 有効化  | 有効化  | 0又は1          | 1            | (1,1)          | SU, ランク-8, ポート-7-14   |

FIG. 4

【図5】

| TB-1 | TB-2 | NDI<br>(1ビット) | SI<br>(1ビット) | 2ビット<br>(A, B) | メッセージ                                      |

|------|------|---------------|--------------|----------------|--------------------------------------------|

| 有効化  | 無効化  | 0             | 0又は1         | (x,x)          | SU/MU, ランク-1, ポート-7,<br>スクランブリング系列: 0又は1   |

| 有効化  | 無効化  | 1             | 0又は1         | (x,x)          | SU/MU, ランク-1, ポート-8,<br>スクランブリング系列: 0又は1   |

| 無効化  | 有効化  | 0             | 0又は1         | (x,x)          | SU/MU, ランク-1, ポート-7,<br>スクランブリング系列: 0又は1   |

| 無効化  | 有効化  | 1             | 0又は1         | (x,x)          | SU/MU, ランク-1, ポート-8,<br>スクランブリング系列: 0又は1   |

| 有効化  | 有効化  | 0又は1          | 0又は1         | (0,0)          | SU/MU, ランク-2, ポート-7/8,<br>スクランブリング系列: 0又は1 |

| 有効化  | 有効化  | 0又は1          | 0            | (0,1)          | SU, ランク-3, ポート-7-9                         |

| 有効化  | 有効化  | 0又は1          | 0            | (1,0)          | SU, ランク-4, ポート-7-10                        |

| 有効化  | 有効化  | 0又は1          | 0            | (1,1)          | SU, ランク-5, ポート-7-11                        |

| 有効化  | 有効化  | 0又は1          | 1            | (0,1)          | SU, ランク-6, ポート-7-12                        |

| 有効化  | 有効化  | 0又は1          | 1            | (1,0)          | SU, ランク-7, ポート-7-13                        |

| 有効化  | 有効化  | 0又は1          | 1            | (1,1)          | SU, ランク-8, ポート-7-13                        |

FIG. 5

【図6】

| TB-1 | TB-2 | NDI<br>(1ビット) | SI<br>(1ビット) | 2ビット<br>(A, B) | メッセージ                                         |

|------|------|---------------|--------------|----------------|-----------------------------------------------|

| 有効化  | 無効化  | 0             | 0            | (x,x)          | SU/MU, ランク-1, ポート-7 (C1),<br>スクランブリング系列: 0    |

| 有効化  | 無効化  | 1             | 0            | (x,x)          | SU/MU, ランク-1, ポート-8 (C1),<br>スクランブリング系列: 0    |

| 有効化  | 無効化  | 0             | 1            | (x,x)          | SU/MU, ランク-1, ポート-9 (C2),<br>スクランブリング系列: 1    |

| 有効化  | 無効化  | 1             | 1            | (x,x)          | SU/MU, ランク-1, ポート-10 (C2),<br>スクランブリング系列: 1   |

| 無効化  | 有効化  | 0             | 0            | (x,x)          | SU/MU, ランク-1, ポート-7, (C1)<br>スクランブリング系列: 0    |

| 無効化  | 有効化  | 1             | 0            | (x,x)          | SU/MU, ランク-1, ポート-8 (C1),<br>スクランブリング系列: 0    |

| 無効化  | 有効化  | 0             | 1            | (x,x)          | SU/MU, ランク-1, ポート-9 (C2),<br>スクランブリング系列: 1    |

| 無効化  | 有効化  | 1             | 1            | (x,x)          | SU/MU, ランク-1, ポート-10 (C2),<br>スクランブリング系列: 1   |

| 有効化  | 有効化  | 0又は1          | 0            | (0,0)          | SU/MU, ランク-2, ポート-7/8 (C1),<br>スクランブリング系列: 0  |

| 有効化  | 有効化  | 0又は1          | 1            | (0,0)          | SU/MU, ランク-2, ポート-9/10 (C2),<br>スクランブリング系列: 1 |

| 有効化  | 有効化  | 0又は1          | 0            | (0,1)          | SU, ランク-3, ポート-7-9                            |

| 有効化  | 有効化  | 0又は1          | 0            | (1,0)          | SU, ランク-4, ポート-7-10                           |

| 有効化  | 有効化  | 0又は1          | 0            | (1,1)          | SU, ランク-5, ポート-7-11                           |

| 有効化  | 有効化  | 0又は1          | 1            | (0,1)          | SU, ランク-6, ポート-7-12                           |

| 有効化  | 有効化  | 0又は1          | 1            | (1,0)          | SU, ランク-7, ポート-7-13                           |

| 有効化  | 有効化  | 0又は1          | 1            | (1,1)          | SU, ランク-8, ポート-7-13                           |

FIG. 6

SIIによってポートを割り当てる

【図7】

| TB-1 | TB-2 | NDI<br>(1ビット) | SI<br>(1ビット) | 2ビット<br>(A, B) | メッセージ                                        |

|------|------|---------------|--------------|----------------|----------------------------------------------|

| 有効化  | 無効化  | 0             | 0            | (x,x)          | SU/MU_ランク-1_ポート-7 (C1).<br>スクランブリング系列: 0     |

| 有効化  | 無効化  | 1             | 0            | (x,x)          | SU/MU_ランク-1_ポート-8 (C1).<br>スクランブリング系列: 0     |

| 有効化  | 無効化  | 0             | 1            | (x,x)          | SU/MU_ランク-1_ポート-11 (C1).<br>スクランブリング系列: 1    |

| 有効化  | 無効化  | 1             | 1            | (x,x)          | SU/MU_ランク-1_ポート-13 (C1).<br>スクランブリング系列: 1    |

| 無効化  | 有効化  | 0             | 0            | (x,x)          | SU/MU_ランク-1_ポート-7. (C1)<br>スクランブリング系列: 0     |

| 無効化  | 有効化  | 1             | 0            | (x,x)          | SU/MU_ランク-1_ポート-8 (C1).<br>スクランブリング系列: 0     |

| 無効化  | 有効化  | 0             | 1            | (x,x)          | SU/MU_ランク-1_ポート-11 (C1).<br>スクランブリング系列: 1    |

| 無効化  | 有効化  | 1             | 1            | (x,x)          | SU/MU_ランク-1_ポート-13 (C1).<br>スクランブリング系列: 1    |

| 有効化  | 有効化  | 0又は1          | 0            | (0,0)          | SU/MU_ランク-2_ポート-7/8 (C1).<br>スクランブリング系列: 0   |

| 有効化  | 有効化  | 0又は1          | 1            | (0,0)          | SU/MU_ランク-2_ポート-11/13 (C1).<br>スクランブリング系列: 1 |

| 有効化  | 有効化  | 0又は1          | 0            | (0,1)          | SU_ランク3_ポート-7-9                              |

| 有効化  | 有効化  | 0又は1          | 0            | (1,0)          | SU_ランク4_ポート-7-10                             |

| 有効化  | 有効化  | 0又は1          | 0            | (1,1)          | SU_ランク5_ポート-7-11                             |

| 有効化  | 有効化  | 0又は1          | 1            | (0,1)          | SU_ランク6_ポート-7-12                             |

| 有効化  | 有効化  | 0又は1          | 1            | (1,0)          | SU_ランク7_ポート-7-13                             |

| 有効化  | 有効化  | 0又は1          | 1            | (1,1)          | SU_ランク8_ポート-7-14                             |

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

---

フロントページの続き

(72)発明者 フー， ヤン

中華人民共和国 ベイジン， 100102， チャオヤン ディストリクト， ライズ イース

ト ストリート ナンバー5， エリクソン タワー

(72)発明者 アステリー， デーヴィッド

スウェーデン国 ブロンマ エスイー-168 56， ストボウスヴェーゲン 22

(72)発明者 イングレン， ジョージ

スウェーデン国 スンドビーベリ エスイー-174 62， クロノゴーズヴェーゲン 44

(72)発明者 ソン， シンファ

中華人民共和国 ベイジン， 100102， チャオヤン ディストリクト， ライズ イース

ト ストリート ナンバー5， エリクソン タワー

審査官 岡 裕之

(56)参考文献 特表2013-509789 (JP, A)

米国特許出願公開第2011/0103324 (US, A1)

InterDigital Communications et al., Discussion on transparency of LTE-A MU-MIMO, 3GPP

R1-102091, 2010年 4月16日

Samsung, DL transmission modes for Rel-10, 3GPP R1-102208, 2010年 4月16日

3GPP TS 36.212 V9.1.0, 2010年 3月, pp.43-56, 60, 61

Mitsubishi Electric, Uplink DM-RS design, 3GPP R1-102238, 2010年 4月16日

(58)調査した分野(Int.Cl., DB名)

H04J 99/00

H04B 7/04

H04W 28/06

H04W 72/04