(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6231396号

(P6231396)

(45) 発行日 平成29年11月15日(2017.11.15)

(24) 登録日 平成29年10月27日(2017.10.27)

(51) Int.Cl.

F 1

|                   |                  |      |       |      |

|-------------------|------------------|------|-------|------|

| <b>H01L 29/78</b> | <b>(2006.01)</b> | H01L | 29/78 | 652N |

| <b>H01L 29/12</b> | <b>(2006.01)</b> | H01L | 29/78 | 652T |

| <b>H01L 29/06</b> | <b>(2006.01)</b> | H01L | 29/78 | 652P |

|                   |                  | H01L | 29/78 | 653A |

|                   |                  | H01L | 29/78 | 652F |

請求項の数 7 (全 17 頁) 最終頁に続く

(21) 出願番号

特願2014-23869 (P2014-23869)

(22) 出願日

平成26年2月10日 (2014.2.10)

(65) 公開番号

特開2015-153787 (P2015-153787A)

(43) 公開日

平成27年8月24日 (2015.8.24)

審査請求日

平成28年7月4日 (2016.7.4)

(73) 特許権者 000003207

トヨタ自動車株式会社

愛知県豊田市トヨタ町1番地

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(73) 特許権者 000003609

株式会社豊田中央研究所

愛知県長久手市横道41番地の1

(74) 代理人 110000110

特許業務法人快友国際特許事務所

(72) 発明者 高谷 秀史

愛知県豊田市トヨタ町1番地 トヨタ自動

車株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置及び半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板を有する半導体装置であって、

前記半導体基板内であってその表面に露出しているn型の第1領域と、

前記第1領域の下側に配置されているp型の第2領域と、

前記第2領域の下側に配置されており、前記第2領域によって前記第1領域から分離されているn型の第3領域と、

前記表面に形成されており、前記第1領域及び前記第2領域を貫通して前記第3領域に達する複数のゲートトレンチと、

前記ゲートトレンチ内に配置されている第1絶縁層と、

前記ゲートトレンチ内に配置されており、前記第1絶縁層を介して前記第2領域に対向しているゲート電極と、

前記ゲートトレンチの下端に接するp型の第4領域と、

前記表面に形成されており、前記表面を平面視したときに前記複数のゲートトレンチが形成されている領域の周囲を一巡する終端トレンチと、

前記終端トレンチ内に配置されている第2絶縁層と、

前記終端トレンチの下端に接しており、前記第3領域によって前記第2領域から分離されているp型の下端p型領域と、

前記終端トレンチよりも外周側に形成されており、前記終端トレンチに接しており、前記表面に露出しているp型の外周p型領域と、

10

20

前記外周 p 型領域よりも外周側に形成されており、前記表面に露出している p 型の複数のガードリング領域と、

前記終端トレンチよりも外周側に形成されており、前記第 3 領域と繋がっており、前記外周 p 型領域を前記複数のガードリング領域から分離しており、前記複数のガードリング領域を互いから分離している n 型の外周 n 型領域、

を有し、

前記表面に段差部が形成されていることによって、前記表面が、第 1 表面と、前記第 1 表面から突出する第 2 表面を有しており、

前記終端トレンチが、前記第 2 表面に形成されており、

前記外周 p 型領域が、前記第 2 表面から前記第 1 表面に跨る範囲に露出しており、

10

前記複数のガードリング領域が、前記第 1 表面に露出している、

半導体装置。

#### 【請求項 2】

前記ガードリング領域が、A 1 を含有する請求項 1 の半導体装置。

#### 【請求項 3】

半導体基板を有する半導体装置であって、

前記半導体基板内であってその表面に露出している n 型の第 1 領域と、

前記第 1 領域の下側に配置されている p 型の第 2 領域と、

前記第 2 領域の下側に配置されており、前記第 2 領域によって前記第 1 領域から分離されている n 型の第 3 領域と、

20

前記表面に形成されており、前記第 1 領域及び前記第 2 領域を貫通して前記第 3 領域に達する複数のゲートトレンチと、

前記ゲートトレンチ内に配置されている第 1 絶縁層と、

前記ゲートトレンチ内に配置されており、前記第 1 絶縁層を介して前記第 2 領域に対向しているゲート電極と、

前記ゲートトレンチの下端に接する p 型の第 4 領域と、

前記表面に形成されており、前記表面を平面視したときに前記複数のゲートトレンチが形成されている領域の周囲を一巡する終端トレンチと、

前記終端トレンチ内に配置されている第 2 絶縁層と、

前記終端トレンチの下端に接する p 型の下端 p 型領域と、

30

前記終端トレンチよりも外周側に形成されており、前記終端トレンチに接しており、前記表面に露出している p 型の外周 p 型領域と、

前記外周 p 型領域よりも外周側に形成されており、前記表面に露出している p 型の複数のガードリング領域と、

前記終端トレンチよりも外周側に形成されており、前記第 3 領域と繋がっており、前記外周 p 型領域を前記複数のガードリング領域から分離しており、前記複数のガードリング領域を互いから分離している n 型の外周 n 型領域、

を有し、

前記表面に段差部が形成されていることによって、前記表面が、第 1 表面と、前記第 1 表面から突出する第 2 表面を有しており、

40

前記終端トレンチが、前記第 2 表面に形成されており、

前記外周 p 型領域が、前記第 2 表面から前記第 1 表面に跨る範囲に露出しており、

前記複数のガードリング領域が、前記第 1 表面に露出しており、

前記終端トレンチと前記段差部の間の間隔が、10 μm 以上である、

半導体装置。

#### 【請求項 4】

半導体基板を有する半導体装置であって、

前記半導体基板内であってその表面に露出している n 型の第 1 領域と、

前記第 1 領域の下側に配置されている p 型の第 2 領域と、

前記第 2 領域の下側に配置されており、前記第 2 領域によって前記第 1 領域から分離さ

50

れている n 型の第 3 領域と、

前記表面に形成されており、前記第 1 領域及び前記第 2 領域を貫通して前記第 3 領域に達する複数のゲートトレンチと、

前記ゲートトレンチ内に配置されている第 1 絶縁層と、

前記ゲートトレンチ内に配置されており、前記第 1 絶縁層を介して前記第 2 領域に対向しているゲート電極と、

前記ゲートトレンチの下端に接する p 型の第 4 領域と、

前記表面に形成されており、前記表面を平面視したときに前記複数のゲートトレンチが形成されている領域の周囲を一巡する終端トレンチと、

前記終端トレンチ内に配置されている第 2 絶縁層と、

前記終端トレンチの下端に接する p 型の下端 p 型領域と、

前記終端トレンチよりも外周側に形成されており、前記終端トレンチに接しており、前記表面に露出している p 型の外周 p 型領域と、

前記外周 p 型領域よりも外周側に形成されており、前記表面に露出している p 型の複数のガードリング領域と、

前記終端トレンチよりも外周側に形成されており、前記第 3 領域と繋がっており、前記外周 p 型領域を前記複数のガードリング領域から分離しており、前記複数のガードリング領域を互いから分離している n 型の外周 n 型領域、

を有し、

前記表面に段差部が形成されていることによって、前記表面が、第 1 表面と、前記第 1 表面から突出する第 2 表面を有しており、

前記終端トレンチが、前記第 2 表面に形成されており、

前記外周 p 型領域が、前記第 2 表面から前記第 1 表面に跨る範囲に露出しており、

前記複数のガードリング領域が、前記第 1 表面に露出しており、

前記外周 p 型領域のうちの外周側の端部であって前記表面に露出する領域が、A 1 の濃度が B の濃度よりも高い A 1 高濃度領域であり、前記外周 p 型領域のうちの前記 A 1 高濃度領域に隣接する領域が、B の濃度が A 1 の濃度よりも高い B 高濃度領域である、

半導体装置。

#### 【請求項 5】

前記 A 1 高濃度領域の幅が、前記各ガードリング領域の幅よりも広い請求項 4 の半導体装置。 30

#### 【請求項 6】

半導体基板を有する半導体装置であって、

前記半導体基板内であってその表面に露出している n 型の第 1 領域と、

前記第 1 領域の下側に配置されている p 型の第 2 領域と、

前記第 2 領域の下側に配置されており、前記第 2 領域によって前記第 1 領域から分離されている n 型の第 3 領域と、

前記表面に形成されており、前記第 1 領域及び前記第 2 領域を貫通して前記第 3 領域に達する複数のゲートトレンチと、

前記ゲートトレンチ内に配置されている第 1 絶縁層と、

前記ゲートトレンチ内に配置されており、前記第 1 絶縁層を介して前記第 2 領域に対向しているゲート電極と、

前記ゲートトレンチの下端に接する p 型の第 4 領域と、

前記表面に形成されており、前記表面を平面視したときに前記複数のゲートトレンチが形成されている領域の周囲を一巡する終端トレンチと、

前記終端トレンチ内に配置されている第 2 絶縁層と、

前記終端トレンチの下端に接する p 型の下端 p 型領域と、

前記終端トレンチよりも外周側に形成されており、前記終端トレンチに接しており、前記表面に露出している p 型の外周 p 型領域と、

前記外周 p 型領域よりも外周側に形成されており、前記表面に露出している p 型の複数

10

20

30

40

50

のガードリング領域と、

前記終端トレンチよりも外周側に形成されており、前記第3領域と繋がっており、前記外周p型領域を前記複数のガードリング領域から分離しており、前記複数のガードリング領域を互いから分離しているn型の外周n型領域、

を有し、

前記表面に段差部が形成されていることによって、前記表面が、第1表面と、前記第1表面から突出する第2表面を有しており、

前記終端トレンチが、前記第2表面に形成されており、

前記外周p型領域が、前記第2表面から前記第1表面に跨る範囲に露出しており、

前記複数のガードリング領域が、前記第1表面に露出しており、

10

前記下端p型領域の一部が、前記終端トレンチよりも内周側に広がっており、

前記終端トレンチよりも内周側に広がっている前記下端p型領域の前記一部が、前記終端トレンチの下端よりも上側に広がっていない、

半導体装置。

#### 【請求項7】

半導体基板を有する半導体装置を製造する方法であって、

前記半導体装置が、

前記半導体基板内であってその表面に露出しているn型の第1領域と、

前記第1領域の下側に配置されているp型の第2領域と、

前記第2領域の下側に配置されており、前記第2領域によって前記第1領域から分離されているn型の第3領域と、

20

前記表面に形成されており、前記第1領域及び前記第2領域を貫通して前記第3領域に達する複数のゲートトレンチと、

前記ゲートトレンチ内に配置されている第1絶縁層と、

前記ゲートトレンチ内に配置されており、前記第1絶縁層を介して前記第2領域に対向しているゲート電極と、

前記ゲートトレンチの下端に接するp型の第4領域と、

前記表面に形成されており、前記表面を平面視したときに前記複数のゲートトレンチが形成されている領域の周囲を一巡する終端トレンチと、

前記終端トレンチ内に配置されている第2絶縁層と、

30

前記終端トレンチの下端に接するp型の下端p型領域と、

前記終端トレンチよりも外周側に形成されており、前記終端トレンチに接しており、前記表面に露出しているp型の外周p型領域と、

前記外周p型領域よりも外周側に形成されており、前記表面に露出しているp型の複数のガードリング領域と、

前記終端トレンチよりも外周側に形成されており、前記第3領域と繋がっており、前記外周p型領域を前記複数のガードリング領域から分離しており、前記複数のガードリング領域を互いから分離しているn型の外周n型領域、

を有し、

前記表面に段差部が形成されていることによって、前記表面が、第1表面と、前記第1表面から突出する第2表面を有しており、

40

前記終端トレンチが、前記第2表面に形成されており、

前記外周p型領域が、前記第2表面から前記第1表面に跨る範囲に露出しており、

前記複数のガードリング領域が、前記第1表面に露出しており、

前記方法が、

n型層上にp型層を成長させる工程と、

前記p型層の一部を除去することで、前記n型層が露出している表面と、前記p型層が露出しており、前記n型層が露出している表面よりも突出する表面を形成する工程と、

前記n型層が露出している前記表面から前記p型層が露出している前記表面に跨る範囲にp型不純物を注入することによって、前記外周p型領域を形成する工程と、

50

前記 n 型層が露出している前記表面に p 型不純物を注入することによって、前記ガードリング領域を形成する工程と、

前記 p 型層が露出している前記表面に前記終端トレンチを形成する工程、

を有する方法。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書が開示する技術は、半導体装置に関する。

【背景技術】

【0002】

特許文献 1 に開示の半導体装置は、MOSFET と、MOSFET の周囲に形成されている複数の終端トレンチを有する。各終端トレンチは、MOSFET が形成されている領域を囲むように環状に伸びている。各終端トレンチ内には、絶縁層が配置されている。また、各終端トレンチの底面に接する範囲の半導体層には、p 型フローティング領域が形成されている。MOSFET がオフする際には、MOSFET のボディ領域から外周側（終端トレンチが形成されている領域）に向かって空乏層が伸びる。最も内側の終端トレンチの下側の p 型フローティング領域まで空乏層が伸びると、その p 型フローティングから外周側に向かってさらに空乏層が伸びる。これによって、空乏層が隣の p 型フローティング領域まで伸びると、その p 型フローティング領域からさらに外周側に空乏層が伸びる。このように、空乏層は、各 p 型フローティング領域を経由しながら、MOSFET が形成されている領域の周囲に広く広がる。これによって、半導体装置の耐圧が向上される。

10

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2008 - 135522 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、上述したタイプの半導体装置に対する耐圧の要求がますます高まっている。従来は、上述した p 型フローティング領域は、終端トレンチを形成した後に終端トレンチの底面に p 型不純物を注入し、その後、注入した p 型不純物を半導体層内に拡散させることで形成される。しかしながら、半導体の材料や、他の製造工程の各種条件によっては、p 型不純物の拡散距離が短くなり、各 p 型フローティング領域の間の間隔を十分に狭めることができない場合がある。このような場合、当該間隔の領域に十分に空乏層を伸展させることができないことが困難となる。各終端トレンチの間の間隔を狭くすることで各 p 型フローティング領域の間の間隔を狭めることも考え得るが、加工精度の問題等により各終端トレンチ間の間隔を狭くすることには限界がある。従来の終端トレンチの構造では、耐圧の向上に限界があった。したがって、本明細書では、より高耐圧を実現可能な半導体装置を開示する。

20

【課題を解決するための手段】

【0005】

本明細書は、半導体基板を有する半導体装置を開示する。この半導体装置は、前記半導体基板内であってその表面に露出している n 型の第 1 領域と、前記第 1 領域の下側に配置されている p 型の第 2 領域と、前記第 2 領域の下側に配置されており、前記第 2 領域によつて第 1 領域から分離されている n 型の第 3 領域と、前記表面に形成されており、前記第 1 領域及び前記第 2 領域を貫通して前記第 3 領域に達する複数のゲートトレンチと、前記ゲートトレンチ内に配置されている第 1 絶縁層と、前記ゲートトレンチ内に配置されており、前記第 1 絶縁層を介して前記第 2 領域に対向しているゲート電極と、前記ゲートトレンチの下端に接する p 型の第 4 領域と、前記表面に形成されており、前記表面を平面視したときに前記複数のゲートトレンチが形成されている領域の周囲を一巡する終端トレンチと、前記終端トレンチ内に配置されている第 2 絶縁層と、前記終端トレンチの下端に接す

40

50

る p 型の下端 p 型領域と、前記終端トレンチよりも外周側に形成されており、前記終端トレンチに接しており、前記表面に露出している p 型の外周 p 型領域と、前記外周 p 型領域よりも外周側に形成されており、前記表面に露出している p 型の複数のガードリング領域と、前記終端トレンチよりも外周側に形成されており、前記第 3 領域と繋がっており、前記外周 p 型領域を前記複数のガードリング領域から分離しており、前記複数のガードリング領域を互いから分離している n 型の外周 n 型領域を有する。

#### 【 0 0 0 6 】

なお、本明細書において、外周側とは、複数のゲートトレンチが形成されている領域から遠ざかる方向を意味する。また、上述した下端 p 型領域は、上述した外周 p 型領域と繋がっていてもよいし、外周 p 型領域から分離されていてもよい。

10

#### 【 0 0 0 7 】

この半導体装置では、第 1 領域、第 2 領域、第 3 領域、第 4 領域及びゲート電極によってスイッチング素子が形成されている。スイッチング素子がオフすると、第 2 領域から第 3 領域内に空乏層が広がる。空乏層がゲートトレンチの下端に達すると、空乏層が第 4 領域に到達する。すると、第 4 領域からも第 3 領域内に空乏層が広がる。これによって、スイッチング素子が形成されている領域における耐圧が確保される。また、空乏層が、第 2 領域から第 3 領域内に広がる空乏層が終端トレンチの下端に達すると、空乏層が下端 p 型領域に到達する。すると、空乏層が、下端 p 型領域及び外周 p 型領域から外周 n 型領域内に延びる。外周 p 型領域から伸びる空乏層が、外周 p 型領域の隣のガードリング領域に到達すると、そのガードリング領域から隣のガードリング領域に向かってさらに空乏層が伸びる。空乏層は、各ガードリング領域を経由して外周側に向かって広がる。これによって、外周側の領域に空乏層が広く伸展し、耐圧が確保される。このように、この半導体装置では、半導体基板の表面に露出するガードリングによって、空乏層の伸展を促進することができる。また、ガードリング領域は半導体基板の表面に露出する範囲に形成されているため、高精度に形成することができる。このため、ガードリング領域の間の間隔を容易に狭くすることができる。このため、この半導体装置では、ガードリング領域によって十分な耐圧を確保することができる。

20

#### 【 0 0 0 8 】

上述した半導体装置においては、前記表面に段差部が形成されていることによって、前記表面が、第 1 表面と、第 1 表面から突出する第 2 表面を有していてもよい。前記終端トレンチが、前記第 2 表面に形成されていてもよい。前記外周 p 型領域が、前記第 2 表面から前記第 1 表面に跨る範囲に露出していてもよい。前記複数のガードリング領域が、前記第 1 表面に露出していてもよい。また、この場合、前記終端トレンチと前記段差部の間の間隔が、 $10 \mu m$  以上あってもよい。

30

#### 【 0 0 0 9 】

上述したいずれかの半導体装置においては、前記外周 p 型領域のうちの外周側の端部であって前記表面に露出する領域が、A 1 の濃度が B の濃度よりも高い A 1 高濃度領域であり、前記外周 p 型領域のうちの前記 A 1 高濃度領域に隣接する領域が、B の濃度が A 1 の濃度よりも高い B 高濃度領域であってもよい。この場合、前記 A 1 高濃度領域の幅が、前記各ガードリング領域の幅よりも広くてもよい。なお、上記の幅は、内周側から外周側に向かう方向における寸法を意味する。

40

#### 【 0 0 1 0 】

このような構成によれば、外周 p 型領域における漏れ電流を抑制することができる。

#### 【 0 0 1 1 】

上述したいずれかの半導体装置において、前記下端 p 型領域の一部が、前記終端トレンチよりも内周側に広がっており、前記終端トレンチよりも内周側に広がっている前記下端 p 型領域の前記一部が、前記終端トレンチの下端よりも上側に広がっていなくてもよい。

#### 【 0 0 1 2 】

上述したいずれかの半導体装置において、前記ガードリング領域が、A 1 を含有してもよい。

50

## 【0013】

このような構成によれば、より高精度にガードリング領域を形成することができる。

## 【0014】

上述した段差を有する半導体装置は、以下の方法によって製造してもよい。この方法は、n型層上にp型層を成長させる工程と、前記p型層の一部を除去することで、前記n型層が露出している表面と、前記p型層が露出しており、前記n型層が露出している表面よりも突出する表面を形成する工程と、前記n型層が露出している前記表面から前記p型層が露出している前記表面に跨る範囲にp型不純物を注入することによって、前記外周p型領域を形成する工程と、前記n型層が露出している前記表面にp型不純物を注入することによって、前記ガードリング領域を形成する工程と、前記p型層が露出している前記表面に終端トレンチを形成する工程を有する。10

## 【図面の簡単な説明】

## 【0015】

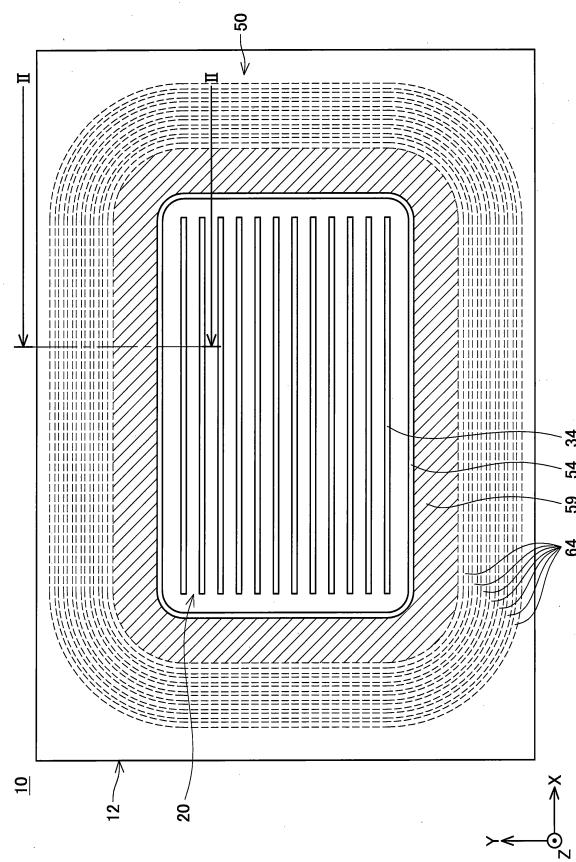

【図1】半導体装置10の平面図。

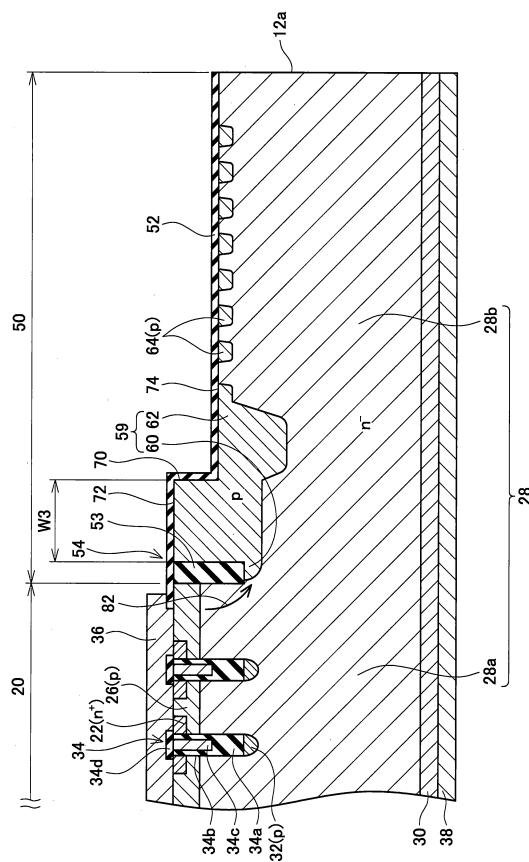

【図2】図1のI—I-I—I線における縦断面図。

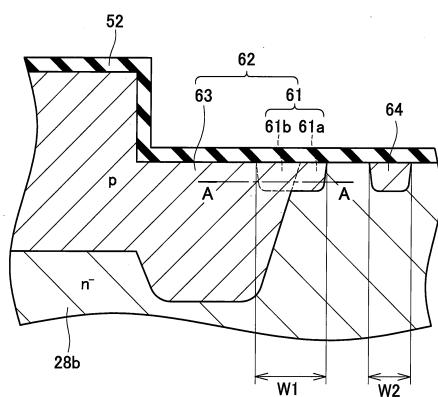

【図3】外周p型領域62の拡大断面図。

【図4】図3のA-A線における不純物濃度分布を示すグラフ。

【図5】半導体装置10の製造工程の説明図。

【図6】半導体装置10の製造工程の説明図。

【図7】半導体装置10の製造工程の説明図。20

【図8】半導体装置10の製造工程の説明図。

【図9】半導体装置10の製造工程の説明図。

【図10】半導体装置10の製造工程の説明図。

【図11】幅W3とDS耐圧の関係を示すグラフ。

【図12】第1変形例の半導体装置の図2に対応する縦断面図。

【図13】第2変形例の半導体装置の図2に対応する縦断面図。

【図14】第3変形例の半導体装置の図2に対応する縦断面図。

【図15】第4変形例の半導体装置の図2に対応する縦断面図。

## 【発明を実施するための形態】

## 【0016】

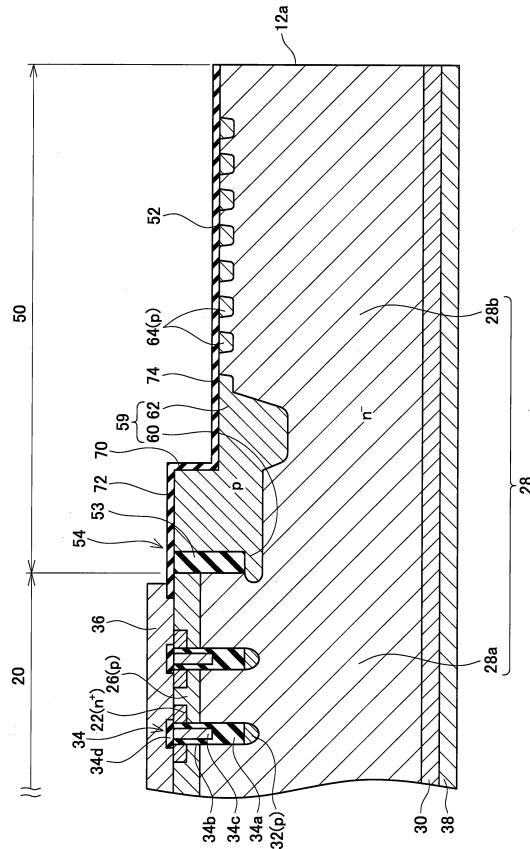

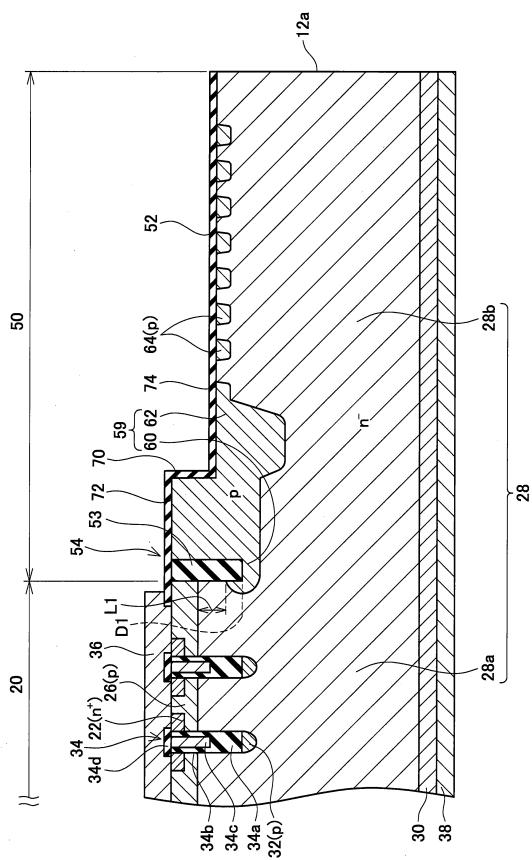

図1に示すように、実施例1に係る半導体装置10はSiC(シリコンカーバイド)からなる半導体基板12を有している。半導体基板12は、MOSFET領域20と、外周領域50を有している。MOSFET領域20には、MOSFETが形成されている。なお、図1では、図の見易さを考慮して、MOSFET領域20内にゲートトレンチ34のみを示している。外周領域50は、MOSFET領域20の外側の領域である。本実施例では、外周領域50は、MOSFET領域20と半導体基板12の端面12aとの間の領域である。外周領域50には、耐圧構造が形成されている。なお、図1では、図の見易さを考慮して、外周領域50内に終端トレンチ54と、境界部p型領域59と、ガードリング領域64のみを示している。30

## 【0017】

図2に示すように、MOSFET領域20内には、ソース領域22、ボディ領域26、ドリフト領域28、ドレイン領域30、p型フローティング領域32、ゲートトレンチ34、ソース電極36、ドレイン電極38が形成されている。40

## 【0018】

ソース領域22は、MOSFET領域20内に複数個形成されている。ソース領域22は、高濃度にn型不純物を含むn型領域である。ソース領域22は、半導体基板12の上面に露出する範囲に形成されている。

## 【0019】

ボディ領域26は、ソース領域22の側方及び下側に形成されており、ソース領域22に接している。ボディ領域26は、p型領域である。ボディ領域26は、ソース領域2250

が形成されていない位置において半導体基板 12 の上面に露出している。

【0020】

ドリフト領域 28 は、低濃度に n 型不純物を含む n 型領域である。ドリフト領域 28 の n 型不純物濃度は、ソース領域 22 の n 型不純物濃度よりも低い。ドリフト領域 28 は、ボディ領域 26 の下側に形成されている。ドリフト領域 28 は、ボディ領域 26 に接しており、ボディ領域 26 によってソース領域 22 から分離されている。

【0021】

ドレイン領域 30 は、高濃度に n 型不純物を含む n 型領域である。ドレイン領域 30 の n 型不純物濃度は、ドリフト領域 28 の n 型不純物濃度よりも高い。ドレイン領域 30 は、ドリフト領域 28 の下側に形成されている。ドレイン領域 30 は、ドリフト領域 28 に接しており、ドリフト領域 28 によってボディ領域 26 から分離されている。ドレイン領域 30 は、半導体基板 12 の下面に露出する範囲に形成されている。10

【0022】

ゲートトレンチ 34 は、MOSFET 領域 20 内に複数個形成されている。ゲートトレンチ 34 は、半導体基板 12 の上面に形成された溝である。各ゲートトレンチ 34 は、ソース領域 22 とボディ領域 26 を貫通し、ドリフト領域 28 に達するように形成されている。図 1 に示すように、複数のゲートトレンチ 34 は、互いに平行に伸びている。図 2 に示すように、各ゲートトレンチ 34 内には、ボトム絶縁層 34a と、ゲート絶縁膜 34b と、ゲート電極 34c が形成されている。ボトム絶縁層 34a は、ゲートトレンチ 34 の底部に形成された厚い絶縁層である。ボトム絶縁層 34a の上側のゲートトレンチ 34 の側面は、ゲート絶縁膜 34b によって覆われている。ボトム絶縁層 34a の上側のゲートトレンチ 34 内には、ゲート電極 34c が形成されている。ゲート電極 34c は、ゲート絶縁膜 34b を介して、ソース領域 22、ボディ領域 26 及びドリフト領域 28 と対向している。ゲート電極 34c は、ゲート絶縁膜 34b 及びボトム絶縁層 34a によって、半導体基板 12 から絶縁されている。ゲート電極 34c の上面は、絶縁層 34d によって覆われている。20

【0023】

p 型フローティング領域 32 は、半導体基板 12 内であって、各ゲートトレンチ 34 の底面（すなわち、下端）に接する範囲に形成されている。p 型フローティング領域 32 の周囲は、ドリフト領域 28 に囲まれている。各 p 型フローティング領域 32 は、ドリフト領域 28 によって、互いに分離されている。また、各 p 型フローティング領域 32 は、ドリフト領域 28 によって、ボディ領域 26 から分離されている。30

【0024】

ソース電極 36 は、MOSFET 領域 20 内の半導体基板 12 の上面に形成されている。ソース電極 36 は、ソース領域 22 及びボディ領域 26 と導通している。

【0025】

ドレイン電極 38 は、半導体基板 12 の下面に形成されている。ドレイン電極 38 は、ドレイン領域 30 と導通している。

【0026】

上述したドリフト領域 28 及びドレイン領域 30 は、外周領域 50 まで広がっている。ドリフト領域 28 とドレイン領域 30 は、半導体基板 12 の端面 12a まで広がっている。また、ドレイン電極 38 は、外周領域 50 を含む半導体基板 12 の下面全体に形成されている。また、外周領域 50 内の半導体基板 12 の上面は、絶縁層 52 によって覆われている。以下では、MOSFET 領域 20 内のドリフト領域 28 を、素子部ドリフト領域 28a と呼び、外周領域 50 内のドリフト領域 28 を、外周部ドリフト領域 28b と呼ぶ場合がある。40

【0027】

外周領域 50 内の半導体基板 12 の表面には、段差部 70 が形成されている。段差部 70 によって、半導体基板 12 の表面が、中央部側の表面 72 と、端面 12a 側の表面 74 に区画されている。表面 72 は、表面 74 に対して上側に突出している。このため、表面50

7 2 に対応する部分では、表面 7 4 に対応する部分よりも、半導体基板 1 2 の厚みが厚い。上述した M O S F E T 領域 2 0 は、表面 7 2 に対応する部分（厚みが厚い部分）に形成されている。段差部 7 0 の高さは、ボディ領域 2 6 の厚みよりも大きい。したがって、ボディ領域 2 6 の下端よりも、表面 7 4 が下側（裏面側）に位置している。

#### 【 0 0 2 8 】

外周領域 5 0 内の半導体基板 1 2 の表面 7 2 には、終端トレンチ 5 4 が形成されている。終端トレンチ 5 4 内には、絶縁層 5 3 が形成されている。終端トレンチ 5 4 は、ボディ領域 2 6 に隣接する位置に形成されている。終端トレンチ 5 4 は、ゲートトレンチ 3 4 と略同じ深さを有している。従って、絶縁層 5 3 は、ボディ領域 2 6 よりも深い位置では、素子部ドリフト領域 2 8 a に接している。図 1 に示すように、終端トレンチ 5 4 は、半導体基板 1 2 の表面を平面視したときに、M O S F E T 領域 2 0 の周囲を一巡するように伸びている。したがって、ボディ領域 2 6 は、絶縁層 5 3 によって、外周領域 5 0 内のいずれの p 型領域からも分離されている。すなわち、本実施例では、終端トレンチ 5 4 に囲まれた領域が M O S F E T 領域 2 0 である。

#### 【 0 0 2 9 】

図 2 に示すように、終端トレンチ 5 4 の下端（すなわち、底面）に接する位置に、下端 p 型領域 6 0 が形成されている。本実施例では、下端 p 型領域 6 0 は、M O S F E T 領域 2 0 内には形成されていない。また、終端トレンチ 5 4 よりも外周側の領域であって、終端トレンチ 5 4 に接する位置には、外周 p 型領域 6 2 が形成されている。外周 p 型領域 6 2 は、表面 7 2 に露出する位置から表面 7 4 に露出する位置に跨って形成されている。外周 p 型領域 6 2 は、表面 7 2 、段差部 7 0 及び表面 7 4 に露出している。また、外周 p 型領域 6 2 は、終端トレンチ 5 4 の下端よりも深い位置まで広がっている。図示するように、本実施例では、下端 p 型領域 6 0 と外周 p 型領域 6 2 が繋がっている。下端 p 型領域 6 0 と外周 p 型領域 6 2 は 1 つの p 型領域であるので、以下ではこれらをまとめて境界部 p 型領域 5 9 と呼ぶ場合がある。すなわち、境界部 p 型領域 5 9 は、終端トレンチ 5 4 の下端に露出する位置、表面 7 2 に露出する位置及び表面 7 4 に露出する位置に跨って延びる p 型領域である。図 1 に示すように、境界部 p 型領域 5 9 は、終端トレンチ 5 4 に沿って、M O S F E T 領域 2 0 の周囲を一巡するように形成されている。図 2 に示すように、境界部 p 型領域 5 9 の下側には、外周部ドリフト領域 2 8 b が形成されている。

#### 【 0 0 3 0 】

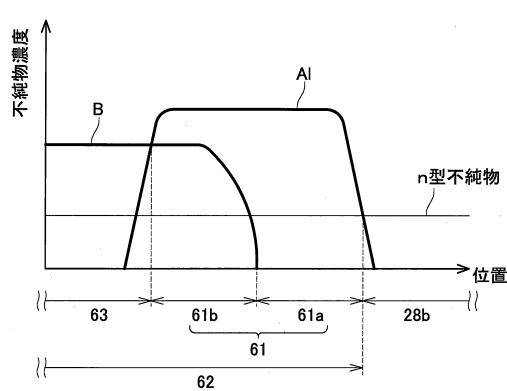

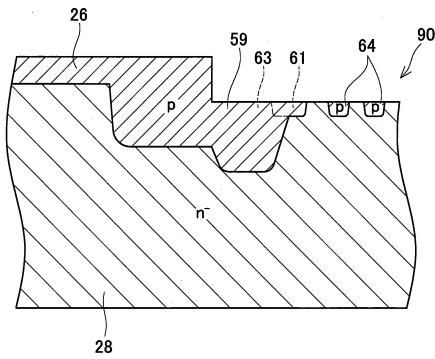

図 3 は、外周 p 型領域 6 2 の外周端近傍の拡大断面図を示している。図示するように、外周 p 型領域 6 2 は、A 1 (アルミニウム) 高濃度領域 6 1 と、B (ボロン) 高濃度領域 6 3 を有している。A 1 高濃度領域 6 1 は B よりも A 1 の濃度が高い p 型領域であり、B 高濃度領域 6 3 は A 1 よりも B の濃度が高い p 型領域である。外周 p 型領域 6 2 は、制御不能な誤差レベルを除いて、B と A 1 以外の p 型不純物を含有していない。A 1 高濃度領域 6 1 は、外周 p 型領域 6 2 が表面 7 4 に露出する範囲のうち、外周 p 型領域 6 2 の外周端に形成されている。B 高濃度領域 6 3 は、A 1 高濃度領域 6 1 以外の外周 p 型領域 6 2 内に形成されている。外周 p 型領域 6 2 の大部分は、B 高濃度領域 6 3 によって構成されている。図 4 は、外周 p 型領域 6 2 の外周端近傍における不純物濃度分布（図 3 の A - A 線に沿った不純物濃度分布）を示している。図 3、4 において、領域 6 1 a は、A 1 を含有するとともに、B を含有しない領域である。領域 6 1 b は、A 1 と B を含有しており、A 1 の濃度が B の濃度よりも高い領域である。A 1 高濃度領域 6 1 は、領域 6 1 a と領域 6 1 b によって構成されている。図 3 に示す A 1 高濃度領域 6 1 の幅 W 1 (すなわち、内周側から外周側に向かう方向における寸法) は、後述するガードリング領域 6 4 のそれぞれの幅 W 2 よりも広い。なお、上記の幅 W 1 、W 2 は、内周側から外周側に向かう方向における寸法を意味する。

#### 【 0 0 3 1 】

図 2 に示すように、外周 p 型領域 6 2 の外周側には、複数のガードリング領域 6 4 が形成されている。各ガードリング領域 6 4 は、p 型領域であり、表面 7 4 に露出する範囲に形成されている。各ガードリング領域 6 4 は、浅い範囲にのみ形成されている。したがつ

10

20

30

40

50

て、各ガードリング領域 6 4 の下端は、外周 p 型領域 6 2 の下端よりも上側（表面側）に位置している。各ガードリング領域 6 4 の下側には、外周部ドリフト領域 2 8 b が形成されている。最も内周側（MOSFET 領域 2 0 側）のガードリング領域 6 4 と外周 p 型領域 6 2 の間には、外周部ドリフト領域 2 8 b が形成されている。外周部ドリフト領域 2 8 b によって、最も内周側のガードリング領域 6 4 が外周 p 型領域 6 2 から分離されている。また、各ガードリング領域 6 4 の間には、外周部ドリフト領域 2 8 b が形成されている。外周部ドリフト領域 2 8 b によって、各ガードリング領域 6 4 が互いから分離されている。各ガードリング領域 6 4 は、p 型不純物として A 1 を含有している。各ガードリング領域 6 4 は、制御不可能な誤差レベルを除いて、A 1 以外の p 型不純物を含有していない。

10

### 【 0 0 3 2 】

次に、半導体装置 1 0 の動作について説明する。半導体装置 1 0 を動作させる際には、ドレイン電極 3 8 とソース電極 3 6 の間にドレイン電極 3 8 がプラスとなる電圧が印加される。さらに、ゲート電極 3 4 c に対してゲートオン電圧が印加されることで、MOSFET 領域 2 0 内の MOSFET がオンする。すなわち、ゲート電極 3 4 c に対向している位置のボディ領域 2 6 にチャネルが形成され、ソース電極 3 6 から、ソース領域 2 2 、チャネル、ドリフト領域 2 8 、ドレイン領域 3 0 を経由して、ドレイン電極 3 8 に向かって電流が流れる。ゲート電極 3 4 c へのゲートオン電圧の印加を停止すると、チャネルが消失し、MOSFET がオフする。MOSFET がオフすると、ボディ領域 2 6 とドリフト領域 2 8 の境界部の p n 接合からドリフト領域 2 8 内に空乏層が広がる。空乏層が MOSFET 領域 2 0 内の p 型フローティング領域 3 2 に到達すると、p 型フローティング領域 3 2 からもドリフト領域 2 8 内に空乏層が広がる。これによって、2つの p 型フローティング領域 3 2 の間のドリフト領域 2 8 が効果的に空乏化される。このため、MOSFET 領域 2 0 内における電界集中が抑制される。これによって、MOSFET 領域 2 0 内における高い耐圧が実現される。

20

### 【 0 0 3 3 】

また、上述した p n 接合から伸びる空乏層は、図 2 の矢印 8 2 に示すように、終端トレンチ 5 4 の下側の境界部 p 型領域 5 9 にも到達する。すると、境界部 p 型領域 5 9 からドリフト領域 2 8 内に空乏層が広がる。ゲートトレンチ 3 4 と終端トレンチ 5 4 の間のドリフト領域 2 8 は、ゲートトレンチ 3 4 の下側の p 型フローティング領域 3 2 から広がる空乏層と終端トレンチ 5 4 の下側の境界部 p 型領域 5 9 （すなわち、下端 p 型領域 6 0 ）から広がる空乏層によって空乏化される。このとき、ゲートトレンチ 3 4 の深さと終端トレンチ 5 4 の深さが略等しい（すなわち、p 型フローティング領域 3 2 の深さ方向の位置と下端 p 型領域 6 0 の深さ方向の位置が略等しい）ため、ゲートトレンチ 3 4 と終端トレンチ 5 4 の間のドリフト領域 2 8 において等電位線が横方向（表面 7 2 と平行な方向）に伸びる。これによって、終端トレンチ 5 4 の近傍における電界集中が抑制される。

30

### 【 0 0 3 4 】

また、境界部 p 型領域 5 9 は、終端トレンチ 5 4 の下端に接する範囲から半導体基板 1 2 の表面 7 4 に接する位置まで広がっている。このため、表面 7 4 の近傍では、境界部 p 型領域 5 9 から最も内周側のガードリング領域 6 4 に向かって空乏層が広がる。空乏層が最も内周側のガードリング領域 6 4 に到達すると、そのガードリング領域 6 4 からその隣のガードリング領域 6 4 に空乏層が伸展する。このように、空乏層が、各ガードリング領域 6 4 を順次経由して外周側に広がる。このため、外周領域 5 0 内に空乏層が広く伸展する。これによって、外周領域 5 0 内における高い耐圧が実現される。

40

### 【 0 0 3 5 】

このように、この半導体装置では、終端トレンチ 5 4 の下側の境界部 p 型領域 5 9 が p 型フローティング領域 3 2 と同様に深い位置に設けられることによって、MOSFET 領域 2 0 の外周端近傍における電界集中が抑制される。また、終端トレンチ 5 4 よりも外周側において境界部 p 型領域 5 9 が終端トレンチ 5 4 の底面から半導体基板 1 2 の表面 7 4 まで伸びていることで、表面 7 4 近傍の浅い範囲内にのみ形成されたガードリング領

50

域 6 4 に空乏層が到達することが可能となっている。その結果、複数のガードリング領域 6 4 によって外周領域 5 0 における空乏層の伸展が促進される。また、各ガードリング領域 6 4 が互いから分離されているため、外周領域 5 0 内において電位が比較的均等に分布することができる。このため、外周領域 5 0 における高い耐圧が実現されている。

#### 【 0 0 3 6 】

また、この半導体装置では、外周 p 型領域 6 2 の外周端であって、表面 7 4 に露出する範囲に、A 1 高濃度領域 6 1 が形成されている。このように A 1 高濃度領域 6 1 が形成されることによって、外周 p 型領域 6 2 の表面近傍を通る漏れ電流を抑制することができる。

#### 【 0 0 3 7 】

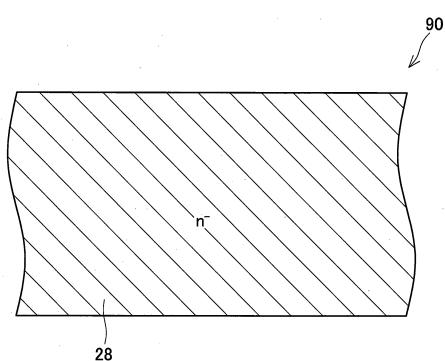

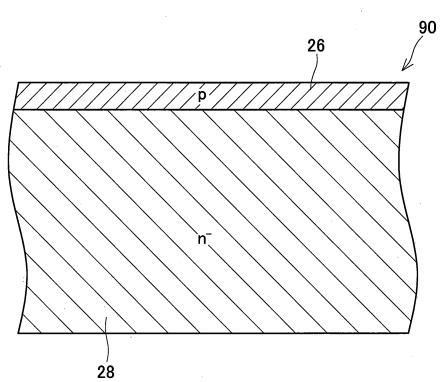

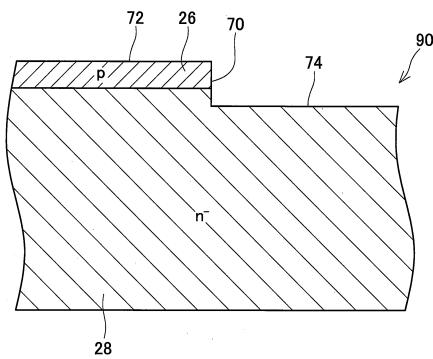

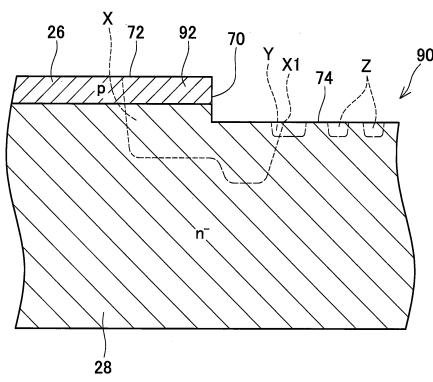

次に、半導体装置 1 0 の製造方法について説明する。まず、図 5 に示すように n 型層 2 8 のみからなる半導体ウエハ 9 0 を準備する。n 型層 2 8 は、ドリフト領域 2 8 となる領域である。次に、図 6 に示すように、n 型層 2 8 の表面に、エピタキシャル成長によって p 型層 2 6 を形成する。p 型層 2 6 は、ボディ領域 2 6 となる領域である。次に、所定範囲内の半導体ウエハ 9 0 の表面を部分的にエッティングする。ここでは、エッティングした範囲において、図 7 に示すように p 型層 2 6 が除去され、n 型層 2 8 が露出するようにエッティングを行う。これによって、半導体ウエハ 9 0 の表面に段差部 7 0 が形成される。段差部 7 0 によって、半導体ウエハ 9 0 の表面が、表面 7 2 と表面 7 4 に区画される。

#### 【 0 0 3 8 】

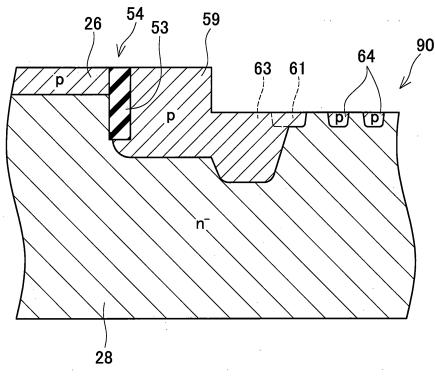

次に、境界部 p 型領域 5 9 に対するイオン注入を行う。すなわち、まず、半導体ウエハ 9 0 の表面のうちの段差部 7 0 を含む範囲（すなわち、表面 7 2 から表面 7 4 に跨る範囲）に B を注入する。ここでは、B の注入エネルギーを調節することによって、図 8 の注入範囲 X に示すように、浅い位置から比較的深い位置まで B が分布するように B を注入する。次に、半導体ウエハ 9 0 の表面 7 4 のうちの注入範囲 X の外周端 X 1 の含む範囲（すなわち、図 8 の注入範囲 Y ）に、A 1 を注入する。ここでは、A 1 の注入エネルギーを低く設定することで、半導体ウエハ 9 0 の表面 7 4 近傍にのみ A 1 が注入されるように A 1 を注入する。

#### 【 0 0 3 9 】

次に、ガードリング領域 6 4 に対するイオン注入を行う。すなわち、半導体ウエハ 9 0 の表面 7 4 のうちの注入範囲 Y よりも外周側（各ガードリング領域 6 4 に対応する注入範囲 Z ）に、A 1 を注入する。ここでは、A 1 の注入エネルギーを低く設定することで、半導体ウエハ 9 0 の表面 7 4 近傍にのみ A 1 が注入されるように A 1 を注入する。なお、注入範囲 Z の幅は、注入範囲 Y の幅よりも狭い。

#### 【 0 0 4 0 】

次に、半導体ウエハ 9 0 を熱処理することで、注入した A 1 と B を拡散させると共に活性化させる。これによって、図 9 に示すように、境界部 p 型領域 5 9 とガードリング領域 6 4 を形成する。このとき、B は A 1 よりも S i C 中における拡散係数が大きいため、B の分布範囲が広がる。すなわち、注入範囲 X に比べて、拡散後の B が分布する範囲はかなり広くなる。上述したように A 1 の注入範囲 Y の幅を広くしておくと、B の分布範囲が拡大しても、境界部 p 型領域 5 9 の外周端に A 1 高濃度領域 6 1 を容易に配置することができる。また、ガードリング領域 6 4 は、半導体ウエハ 9 0 の表面 7 4 近傍の浅い位置に形成されるため、ガードリング領域 6 4 を高精度に形成することができる。特に、ガードリング領域 6 4 に注入される A 1 は S i C 中における拡散係数が低いので、ガードリング領域 6 4 をより高精度に形成することができる。したがって、各ガードリング領域 6 4 の間の間隔を狭小化することができる。さらに、外周 p 型領域 6 2 とガードリング領域 6 4 の間の間隔も狭小化することができる。

#### 【 0 0 4 1 】

次に、図 1 0 に示すように、外周 p 型領域 6 2 の端部（A 1 高濃度領域 6 1 とは反対側の端部）に終端トレンチ 5 4 を形成し、終端トレンチ 5 4 内に絶縁層 5 3 を形成する。

#### 【 0 0 4 2 】

10

20

30

40

50

その後、MOSFET領域20内の構造を形成し、その他の必要な構造（拡散層、電極、絶縁層等）を形成することで、図1の半導体装置10が完成する。なお、上述した製造方法の各工程の順序は、適宜変更することができる。また、MOSFET領域20内の構造を、外周領域50内の構造より先に形成してもよいし、外周領域50内の構造と並行して形成してもよい。

#### 【0043】

以上に説明したように、この製造方法によれば、各ガードリング領域64の間の間隔を狭小化することができる。また、外周p型領域62とガードリング領域64の間の間隔も狭小化することができる。したがって、この半導体装置10では、外周領域50に空乏層が伸びやすい。このため、この方法によれば、外周領域50の耐圧が高い半導体装置10を製造することができる。10

#### 【0044】

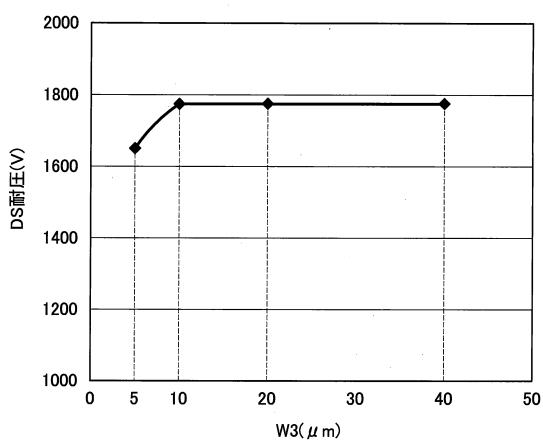

なお、図11は、終端トレンチ54と段差部70の間の間隔W3（図2参照）と、半導体装置10のDS間耐圧（ドレインソース間の耐圧）との関係を示している。図示するように、間隔W3が10μm未満となると、DS間耐圧が急激に低下する。このため、間隔W3は10μm以上であることが好ましい。

#### 【0045】

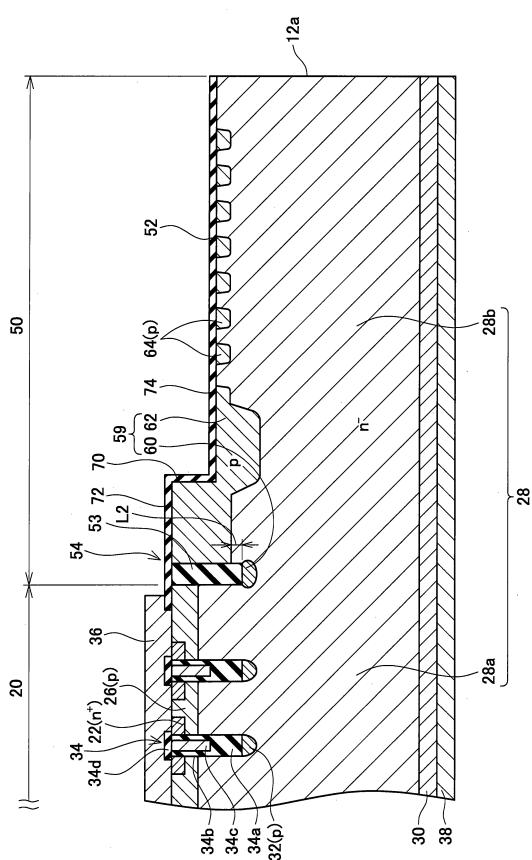

また、上述した実施例の半導体装置10では、終端トレンチ54の下側の境界部p型領域59（すなわち、下端p型領域60）が、MOSFET領域20側に形成されていなかった。しかしながら、図12に示すように、下端p型領域60の一部が、終端トレンチ54よりもMOSFET領域20側に突出していてもよい。このような構成によれば、ゲートトレンチ34と終端トレンチ54の間のドリフト領域28をより空乏化し易くなる。なお、この場合、その突出している部分が、終端トレンチ54の下端よりも上側（ボディ領域26側）にはみ出していないことが好ましい。すなわち、図13のように下端p型領域60の一部がMOSFET領域20内において終端トレンチ54の下端の深さD1よりも上側に位置していると、下端p型領域60とボディ領域26の間の距離L1が短くなる。距離L1が短くなると、DS間耐圧が低下する。このため、MOSFET領域20内に位置する下端p型領域60は、終端トレンチ54の下端よりも下側にのみ存在することが好ましい。但し、場合によっては、下端p型領域60の一部を深さD1よりも上側に配置し、距離L1を最適化することで、DS間耐圧を確保してもよい。20

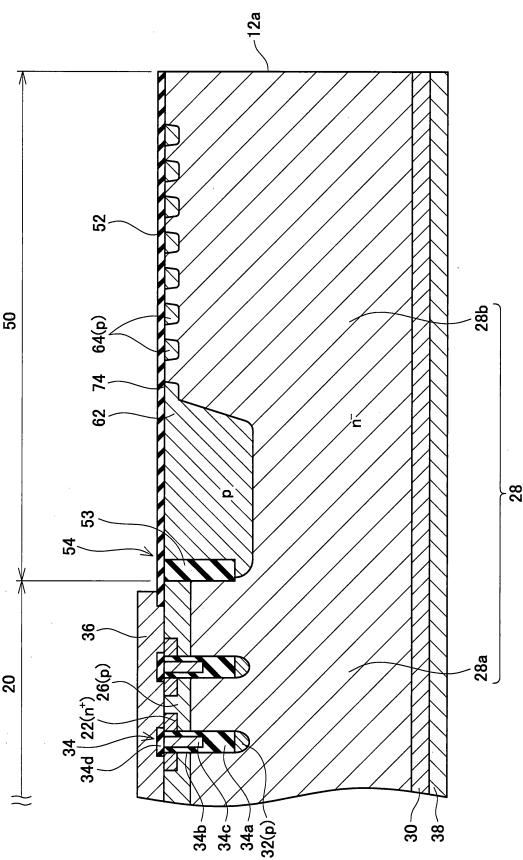

#### 【0046】

また、上述した半導体装置10では、半導体基板12の表面に段差部70が形成されていたが、図14に示すように半導体基板12の表面がフラットであってもよい。なお、図14の半導体装置のボディ領域26は、イオン注入により形成される。エピタキシャル成長とは異なり、イオン注入によれば、ボディ領域26を半導体ウエハの表面の必要な領域内にのみ形成することができる。したがって、図14の半導体装置の製造工程では、上述した実施例で説明したp型層26（ボディ領域26）の一部をエッティングする工程（すなわち、段差部70を形成する工程）を実施する必要がない。したがって、図14の半導体装置では、半導体基板12の表面がフラットとなっている。30

#### 【0047】

また、上述した実施例では、下端p型領域60が外周p型領域62と繋がっていた。しかしながら、図15に示すように、下端p型領域60が外周p型領域62から分離されていてもよい。図15では、外周p型領域62が終端トレンチ54よりも浅い範囲に形成されている。このため、ドリフト領域28によって、下端p型領域60が外周p型領域62から分離されている。このような構成でも、下端p型領域60と外周p型領域62の間の距離L2が、下端p型領域60から外周p型領域62まで空乏層が伸展可能な距離に設定されていれば、上述した実施例と同様に外周領域50の耐圧を確保することができる。なお、空乏層を伸展させるために、距離L2は、 $L_2 = \{2(V_{bi} - V) / q \cdot N_b\}^{1/2}$ の数式を満たすように設定されていることが好ましい。ここで、Vはドリフト領域28の誘電率であり、V<sub>bi</sub>は下端p型領域60とドリフト領域28の間の内蔵電位である4050

り、V は印加電圧であり、q は電気素量であり、N<sub>b</sub> はドリフト領域 28 の n 型不純物濃度である。

#### 【 0 0 4 8 】

また、上述した実施例では、MOSFET を有する半導体装置について説明したが、MOSFET に代えて IGBT 等の他の素子が形成されていてもよい。また、上述した実施例では、半導体基板 12 が SiC により構成されていたが、Si 等の他の材質によって構成された半導体基板を使用してもよい。

#### 【 0 0 4 9 】

以上、本発明の具体例を詳細に説明したが、これらは例示にすぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例をさまざまに変形、変更したものが含まれる。10

本明細書または図面に説明した技術要素は、単独あるいは各種の組み合わせによって技術的有用性を發揮するものであり、出願時請求項記載の組み合わせに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

#### 【 符号の説明 】

##### 【 0 0 5 0 】

|    |               |    |

|----|---------------|----|

| 10 | ：半導体装置        | 20 |

| 12 | ：半導体基板        |    |

| 20 | ：MOSFET 領域    |    |

| 22 | ：ソース領域        |    |

| 26 | ：ボディ領域        |    |

| 28 | ：ドリフト領域       |    |

| 30 | ：ドレイン領域       |    |

| 32 | ：p 型フローティング領域 |    |

| 34 | ：ゲートトレンチ      |    |

| 36 | ：ソース電極        |    |

| 38 | ：ドレイン電極       | 30 |

| 50 | ：外周領域         |    |

| 54 | ：終端トレンチ       |    |

| 59 | ：境界部 p 型領域    |    |

| 60 | ：下端 p 型領域     |    |

| 62 | ：外周 p 型領域     |    |

| 64 | ：ガードリング領域     |    |

| 70 | ：段差部          |    |

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/06 | 3 0 1 V |

| H 01 L | 29/06 | 3 0 1 G |

| H 01 L | 29/06 | 3 0 1 M |

| H 01 L | 29/06 | 3 0 1 D |

(72)発明者 斎藤 順

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

(72)発明者 添野 明高

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

(72)発明者 濱田 公守

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

(72)発明者 水野 祥司

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 青井 佐智子

愛知県長久手市横道41番地の1 株式会社豊田中央研究所内

(72)発明者 渡辺 行彦

愛知県長久手市横道41番地の1 株式会社豊田中央研究所内

審査官 杉山 芳弘

(56)参考文献 特開2012-054378 (JP, A)

特開平10-098188 (JP, A)

特開平11-074524 (JP, A)

特開2010-147222 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 06

H 01 L 29 / 12

H 01 L 29 / 78