(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6777742号

(P6777742)

(45) 発行日 令和2年10月28日(2020.10.28)

(24) 登録日 令和2年10月12日(2020.10.12)

(51) Int.Cl.

H01L 21/60 (2006.01)

H01L 33/62 (2010.01)

F 1

H01L 21/60 311S

H01L 21/92 604B

H01L 33/62

請求項の数 9 (全 10 頁)

(21) 出願番号 特願2018-532495 (P2018-532495)

(86) (22) 出願日 平成28年4月26日 (2016.4.26)

(65) 公表番号 特表2018-529238 (P2018-529238A)

(43) 公表日 平成30年10月4日 (2018.10.4)

(86) 國際出願番号 PCT/CN2016/080209

(87) 國際公開番号 WO2017/041491

(87) 國際公開日 平成29年3月16日 (2017.3.16)

審査請求日 平成30年10月30日 (2018.10.30)

(31) 優先権主張番号 201510579955.1

(32) 優先日 平成27年9月11日 (2015.9.11)

(33) 優先権主張国・地域又は機関

中国(CN)

(73) 特許権者 518083548

ケ クアン

中華人民共和国 518023 グアンド

ン シエンチェン ルオフー ディストリ

クト ノース バオアン ロード ナンバ

-3039

(74) 代理人 110000578

名古屋国際特許業務法人

(72) 発明者 ケ クアン

中華人民共和国 518023 グアンド

ン シエンチェン ルオフー ディストリ

クト ノース バオアン ロード ナンバ

-3039

最終頁に続く

(54) 【発明の名称】 フリップチップのパッケージ方法

## (57) 【特許請求の範囲】

## 【請求項 1】

フリップチップのパッケージ方法であって、パッケージ基板の表面に金属層が設けられており、

フリップチップの周囲にパッケージ基板を設置するステップ S<sub>1</sub> と、

フリップチップの電極表面とパッケージ基板の金属層が設けられた表面に金属導電膜をコーティングするステップ S<sub>2</sub> と、

金属導電膜の表面にフォトレジストを塗布するステップ S<sub>3</sub> と、

マスクアライナにおいて、フォトリソグラフィプレート上の電極構造とフリップチップの電極構造をアライメントして露光及び現像し、フリップチップの電極表面とパッケージ基板の表面が同一領域にあるフォトレジスト構造モールドを得ると共に、フリップチップの電極間の絶縁箇所をフォトレジストが被覆するようにするステップ S<sub>4</sub> と、

前記金属導電膜を電極とし、前記フォトレジスト構造モールド内におけるフリップチップの電極表面およびパッケージ基板の表面に同時に金属を電鋳して、前記フォトレジスト構造モールド内を前記金属で覆われるようになり、フリップチップの電極とパッケージ基板との間の前記金属による電気的な接続を実現するステップ S<sub>5</sub> と、

ステップ S<sub>4</sub> で前記絶縁箇所を被覆するフォトレジストおよびフォトレジストで被覆される金属導電膜を除去するステップ S<sub>6</sub> とを含むことを特徴とする、フリップチップのパッケージ方法。

## 【請求項 2】

10

前記金属導電膜は、フリップチップの電極表面およびパッケージ基板の表面の上方に位置するクロム導電層と、前記クロム導電層の上方に位置する金導電層とを含むことを特徴とする、請求項1に記載のパッケージ方法。

【請求項3】

前記金導電層は、厚さが20～400nmであり、前記クロム導電層は、厚さが20～400nmであることを特徴とする、請求項2に記載のパッケージ方法。

【請求項4】

ステップS<sub>3</sub>において、シャロートレンチ方式で前記フォトレジストを塗布することを特徴とする、請求項1～3のいずれか一項に記載のパッケージ方法。

【請求項5】

ステップS<sub>3</sub>において、スピン方式で、200～6000回転／分の回転速度で前記フォトレジストを塗布することを特徴とする、請求項1～3のいずれか一項に記載のパッケージ方法。

10

【請求項6】

前記電鋳した金属は、銅、ニッケルまたは金であることを特徴とする、請求項1～5のいずれか一項に記載のパッケージ方法。

【請求項7】

ステップS<sub>6</sub>は、

ゾル溶液で前記絶縁箇所を被覆しているフォトレジストを溶解するステップS<sub>6</sub><sub>1</sub>と、金腐食液によりフォトレジストで被覆されている金導電層を腐食するステップS<sub>6</sub><sub>2</sub>と

20

、クロム腐食液により金導電層で被覆されているクロム導電層を腐食するステップS<sub>6</sub><sub>3</sub>とを含むことを特徴とする、請求項2または3に記載のパッケージ方法。

【請求項8】

前記フリップチップの電極表面に金属層を設置することを特徴とする、請求項1～7のいずれか一項に記載のパッケージ方法。

【請求項9】

前記フリップチップの電極表面に金属層を設置しないことを特徴とする、請求項1～7のいずれか一項に記載のパッケージ方法。

30

【発明の詳細な説明】

【発明の詳細な説明】

【0001】

本出願は、出願日が2015年9月11日である中国特許出願CN201510579955.1の優先権を主張する。本出願は、前記中国特許出願の全文を引用する。

【技術分野】

【0002】

本発明は、フリップチップのパッケージ方法に関し、特に、電鋳技術によるフリップチップのパッケージ方法に関する。

【背景技術】

【0003】

フリップチップ技術の発展、特に半導体LED(発光ダイオード)照明の普及に伴い、半導体LEDチップに、一般的に共晶材、ソルダーペースト、銀ペーストという3つのダイボンド方式を利用するフリップパッケージが用いられる傾向があった。フリップチップにおける正極と負極との間の距離が極めて大きくなることはないので、いずれの方式であっても高精密なダイボンドが必要になる。フリップ共晶技術は、高価な製造設備や材料によってコストが高く、コストパフォーマンスの利点が示されず、また、ソルダーペーストおよび銀ペーストによるパッケージ方式のいずれも信頼性が低いこと及び熱伝導性が悪いことにより、ハイパワーのフリップチップパッケージに使用されないので、フリップLED技術が登場して以来、時間が長く経過したが、様々な要因に制限されてあまり普及されなかった。

40

50

**【0004】**

このような3つの既存のフリップチップパッケージの結合方式の他に、新たに出現した電磁パルス溶接結合方式があり、例えば、中国特許出願「フリップチップパッケージ方法」（公開番号がCN103094135Aである）に記述されたこのような結合方式のメリットは、チップ電極と基板電極との間が原子的に連続されてハイパワーのフリップチップの放熱に非常に役立つことにあるが、研発過程において、電磁パルス溶接方式による結合の場合にチップ電極と基板電極とのアライメント精度がパッケージ効率および製品に影響を及ぼす重要な要因になることを発見した。また、その他のパッケージ方式として、例えば、中国特許出願「フリップチップのパッケージ方法及び装置」（公開番号がCN104658929Aである）では、使用するチップと金属基板との結合を実現した上、更にレーザー切断などによって金属基板をチップ上での電極間の絶縁領域に沿って、対応するチップの電極間の電気接続の切断することを実現するようにチップの電極間の電気接続を切断する方法があるが、該方法によれば、この切断操作によってチップに大きな応力を発生させるおそれがあり、金属の切断操作のみであるが、すでに固定されている2つの電極によってチップに悪影響を及ぼす可能性がある。

**【発明の概要】****【0005】**

本発明の解決しようとする技術的課題は、従来技術におけるフリップチップの既存パッケージ結合方式に存在する多くの欠陥を克服するためのフリップチップのパッケージ方法を提供することにある。

**【0006】**

本発明は、以下のような技術的手段によって前記技術的課題を解決する。

本発明は、フリップチップの電極表面およびパッケージ基板の表面に同時に金属を電鋳し、フリップチップの電極とパッケージ基板との間の前記金属による接続を実現することを含むことを特徴とする、フリップチップのパッケージ方法を提供する。

**【0007】**

好ましくは、前記フリップチップのパッケージ方法は、

フリップチップの周囲にパッケージ基板を設置するステップS<sub>1</sub>と、

好ましくは、フリップチップがパッケージ基板に埋め込まれ且つフリップチップの電極表面とパッケージ基板の表面が同一平面にあるようにし、

フリップチップの電極表面とパッケージ基板の表面に金属導電膜をコーティングするステップS<sub>2</sub>と、

金属導電膜の表面にフォトレジストを塗布するステップS<sub>3</sub>と、

マスクアライナにおいて、フォトリソグラフィプレート上での電極構造とフリップチップの電極構造をアライメントしてフォトエッチングし、露光及び現像した後に、フリップチップの電極表面とパッケージ基板の表面が同一領域にあるフォトレジスト構造モールドを得ると共に、フリップチップの電極間の絶縁箇所をフォトレジストが被覆するようにするステップS<sub>4</sub>と、

前記金属導電膜を電極とし、前記フォトレジスト構造モールド内におけるフリップチップの電極表面およびパッケージ基板の表面に同時に前記金属を電鋳して、前記フォトレジスト構造モールド内を前記金属で覆われるようにして、フリップチップの電極とパッケージ基板との間の前記金属による接続を実現するステップS<sub>5</sub>と、

ステップS<sub>4</sub>で前記絶縁箇所を被覆するフォトレジストおよびフォトレジストで被覆される金属導電膜を除去するステップS<sub>6</sub>とを含む。

**【0008】**

好ましくは、ステップS<sub>6</sub>の後に、

前記パッケージ基板を除去するステップS<sub>7</sub>を更に含む。

好ましくは、ステップS<sub>1</sub>は、

フリップチップの電極表面とシリコンチップの表面が接するように、シリコンチップの表面に複数のフリップチップをアレイ状に配列するステップS<sub>11</sub>と、

10

20

30

40

50

フリップチップのアレイ表面に有機ガラスを鋳込み、有機ガラスの表面を平らにして有機ガラスを硬化乾燥させることにより、パッケージ基板になる有機シートを形成するステップ S<sub>1-2</sub> と、

フリップチップがパッケージ基板に埋め込まれ且つフリップチップの電極表面とパッケージ基板の表面が同一平面にあるように、シリコンチップを除去するステップ S<sub>1-3</sub> とを含む。

【0009】

好ましくは、ステップ S<sub>1-1</sub>において、隣接する 2 つのフリップチップ間の距離が 6 m m である。

好ましくは、ステップ S<sub>1-2</sub>において、有機シートの厚さが 2 m m である。

10

【0010】

好ましくは、ステップ S<sub>1-3</sub>において、研削や化学方式でシリコンチップを除去する。

好ましくは、前記金属導電膜は、フリップチップの電極表面およびパッケージ基板の表面の上方に位置するクロム導電層と、前記クロム導電層の上方に位置する金導電層とを含む。

【0011】

好ましくは、前記金導電層は、厚さが 20 ~ 400 nm であり、好ましくは、50 nm であり、前記クロム導電層は、厚さが 20 ~ 400 nm であり、好ましくは、20 nm である。

【0012】

20

好ましくは、前記フォトレジストは、AZ4620 フォトレジスト、AZ-50XT フォトレジスト、SU8 フォトレジスト或は PMMA (有機ガラス) フォトレジストである。但し、上記のフォトレジストのいずれも市販により入手することができる。

【0013】

好ましくは、ステップ S<sub>3</sub>において、シャロートレンチ方式で前記フォトレジストを塗布する。

好ましくは、ステップ S<sub>3</sub>において、スピニ方式で、200 ~ 6000 回転 / 分の回転速度、好ましくは、1000 回転 / 分の回転速度で前記フォトレジストを塗布する。

【0014】

30

好ましくは、前記金属は、銅、ニッケルまたは金である。

好ましくは、ステップ S<sub>6</sub> は、

ゾル溶液で前記絶縁箇所を被覆しているフォトレジストを溶解するステップ S<sub>6-1</sub> と、金腐食液によりフォトレジストで被覆されている金導電層を腐食するステップ S<sub>6-2</sub> と、

クロム腐食液により金導電層で被覆されているクロム導電層を腐食するステップ S<sub>6-3</sub> とを含む。

【0015】

好ましくは、前記フリップチップの電極表面に金属層を設置するか或いは設置しない。

好ましくは、前記パッケージ基板の表面に金属層を設置するか或いは設置しない。

【0016】

40

本発明の肯定的、進歩的な効果は、本発明は電鋳とリソグラフィー技術を利用することにより、電極構造のチップにおける位置精度を正確に保つことによって、フリップチップ電極間の微細なピッチへの要求を満たすと共に、厚膜フォトレジストプロセスを用い、電極と基板の間に良好な金属接続を実現でき、それにより、ハイパワーのフリップチップからの熱量をタイムリーに放出することができ、熱抵抗を効率的に低下させると共に、プロセスを簡略化して、生産効率を向上させることにある。

【図面の簡単な説明】

【0017】

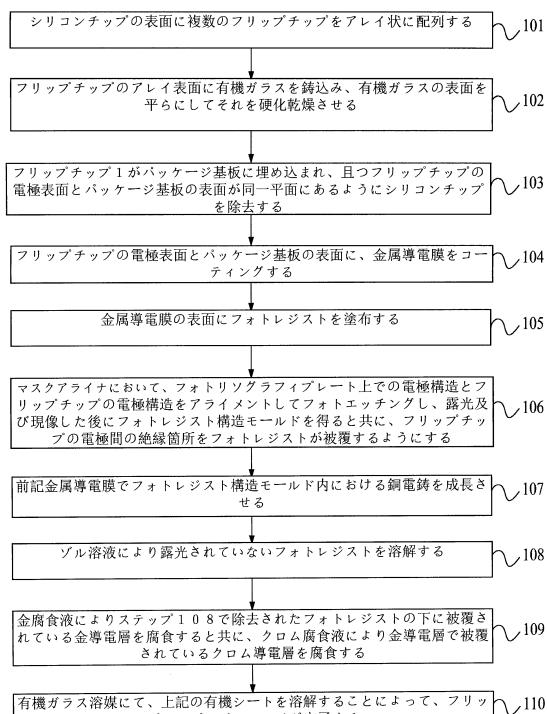

【図 1】図 1 は、本発明の実施例 1 に係るフリップチップのパッケージ方法のフローチャートである。

50

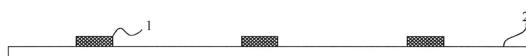

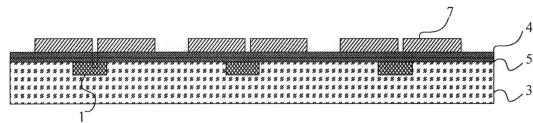

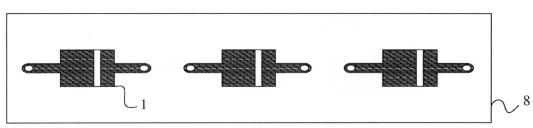

【図2】図2は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ101を行った後に得られた中間製品の構造模式図である。

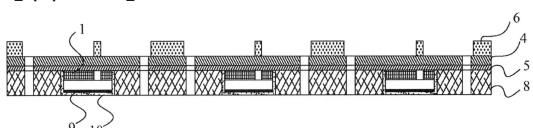

【図3】図3は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ102を行った後に得られた中間製品の構造模式図である。

【図4】図4は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ103を行った後に得られた中間製品の構造模式図である。

【図5】図5は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ104を行った後に得られた中間製品の構造模式図である。

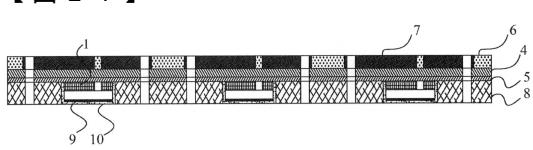

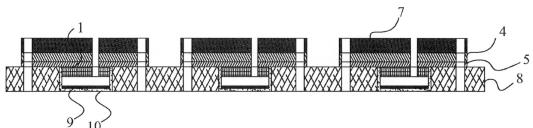

【図6】図6は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ105を行った後に得られた中間製品の構造模式図である。

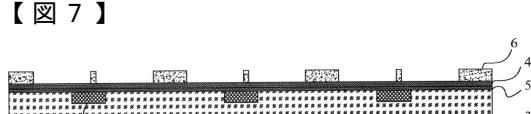

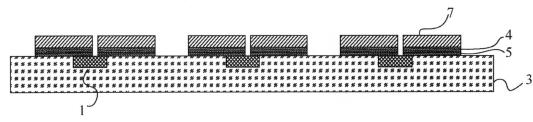

【図7】図7は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ106を行った後に得られた中間製品の構造模式図である。

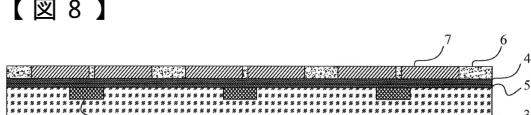

【図8】図8は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ107を行った後に得られた中間製品の構造模式図である。

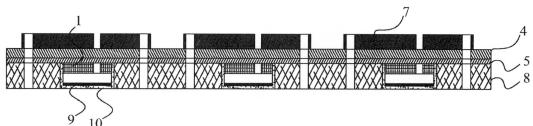

【図9】図9は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ108を行った後に得られた中間製品の構造模式図である。

【図10】図10は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ109を行った後に得られた中間製品の構造模式図である。

【図11】図11は、本発明の実施例1に係るフリップチップのパッケージ方法においてステップ110を行った後に得られた製品の構造模式図である。

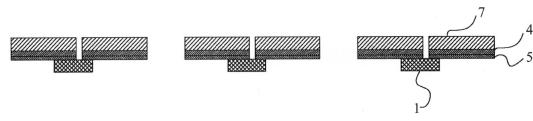

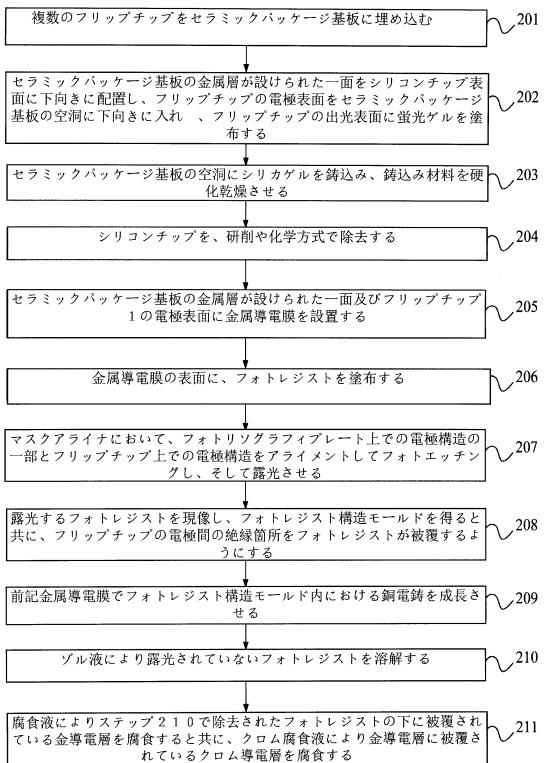

【図12】図12は、本発明の実施例2に係るフリップチップのパッケージ方法のフローチャートである。

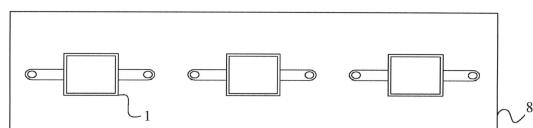

【図13】図13は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ201を行った後に得られた中間製品の平面図である。

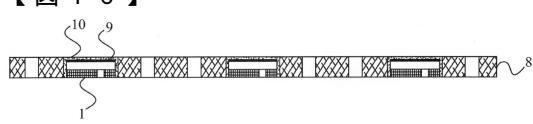

【図14】図14は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ201を行った後に得られた中間製品の側面図である。

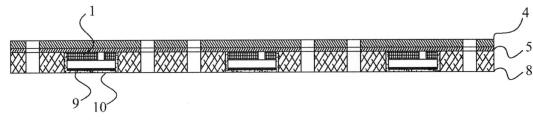

【図15】図15は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ202を行った後に得られた中間製品の構造模式図である。

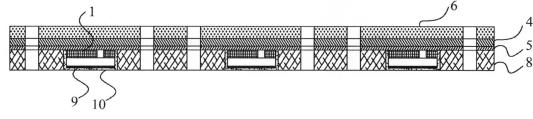

【図16】図16は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ203を行った後に得られた中間製品の構造模式図である。

【図17】図17は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ205を行った後に得られた中間製品の構造模式図である。

【図18】図18は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ206を行った後に得られた中間製品の構造模式図である。

【図19】図19は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ208を行った後に得られた中間製品の平面図である。

【図20】図20は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ208を行った後に得られた中間製品の側面図である。

【図21】図21は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ209を行った後に得られた中間製品の構造模式図である。

【図22】図22は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ210を行った後に得られた中間製品の構造模式図である。

【図23】図23は、本発明の実施例2に係るフリップチップのパッケージ方法においてステップ211を行った後に得られた製品の構造模式図である。

【発明を実施するための形態】

【0018】

以下、実施例により本発明を更に説明するが、それにより本発明は前記実施例の範囲に制限されるものではない。

実施例1

図1に示すように、本実施例によるフリップチップのパッケージ方法は以下のステップ

10

20

30

40

50

を含む。

【0019】

ステップ101であって、フリップチップ1の電極表面とシリコンチップ2の表面が接するように、シリコンチップ2の表面に複数のフリップチップ1をアレイ状に配列し、隣接する2つのフリップチップ1間の距離は6mmが好ましく、ステップ101を行った後に得られた中間製品の構造模式図が図2に示す通りであり、

ステップ102であって、フリップチップ1のアレイ表面に有機ガラス3を鋳込み、2mmの厚さの有機シートを1つ形成するように有機ガラス3の表面を平らにしてそれを硬化乾燥させ、前記有機シートをパッケージ基板とし、ステップ102を行った後に得られた中間製品の構造模式図が図3に示す通りであり、

ステップ103であって、フリップチップ1がパッケージ基板に埋め込まれ、且つフリップチップの電極表面とパッケージ基板の表面が同一平面にあるように、シリコンチップ2を除去し、具体的に研削や化学方式で除去し、それにより、フリップチップ1のアレイ埋め込み型パッケージ基板を得ると共に、フリップチップ1の電極表面がパッケージ基板の表面に十分に重ね合うようになり、ステップ103を行った後に得られた中間製品の構造模式図が図4に示す通りであり、

ステップ104であって、電鋳プロセスの電極として、フリップチップ1の電極表面とパッケージ基板の表面に、フリップチップ1の電極表面およびパッケージ基板の表面の上方に位置するクロム導電層5と該クロム導電層5の上方に位置する金導電層4を含む金属導電膜をコーティングし、好ましくは、上記の金導電層4の厚さが50nmであり、上記のクロム導電層5の厚さが20nmであり、ステップ104を行った後に得られた中間製品の構造模式図が図5に示す通りであり、

ステップ105であって、金属導電膜の表面（具体的には、上記の金導電層4）にフォトレジスト6を塗布し、本実施例の前記フォトレジストはAZ4620フォトレジストであり、具体的にスピンドル方式で1000回転/分の回転速度で前記AZ4620フォトレジストを塗布し、そして、90°のオープンでベーキングし、ステップ105を行った後に得られた中間製品の構造模式図が図6に示す通りであり、

ステップ106であって、マスクアライナにおいて、フォトリソグラフィプレート上の電極構造とフリップチップ1の電極構造をアライメントしてフォトエッチングし、露光及び現像した後に、フリップチップ1の電極表面とパッケージ基板の表面が同一領域にあるフォトレジスト構造モールドを得ると共に、フリップチップ1の電極間の絶縁箇所をフォトレジスト6が被覆するようにし、ステップ106を行った後に得られた中間製品の構造模式図が図7に示す通りであり、

ステップ107であって、前記金属導電膜でフォトレジスト構造モールド内における銅電鋳を成長させ、具体的な操作は、前記金属導電膜を電極とし、前記フォトレジスト構造モールド内におけるフリップチップ1の電極表面およびパッケージ基板の表面に同時に金属銅7を電鋳し、時間及び成長速度を制御することにより、フリップチップ1の電極表面と対応するパッケージ基板が同一領域にあるフォトレジスト構造モールド内を金属銅7で覆われるよう確保し、フリップチップ1の電極とパッケージ基板との間の金属銅7による接続を実現し、ステップ107を行った後に得られた中間製品の構造模式図が図8に示す通りであり、

ステップ108であって、ゾル溶液により露光されていないフォトレジスト6を溶解し、ステップ108を行った後に得られた中間製品の構造模式図が図9に示す通りであり、

ステップ109であって、金腐食液によりステップ108で除去されたフォトレジストの下に被覆されている金導電層を腐食すると共に、クロム腐食液により金導電層で被覆されているクロム導電層を腐食することによって、フリップチップ電極間の電気接続を切断し、ステップ109を行った後に得られた中間製品の構造模式図が図10に示す通りであり、

ステップ110であって、有機ガラス溶媒にて、上記の有機シート（即ち、パッケージ基板）を溶解することによって、フリップチップ2のパッケージを完了し、ステップ11

10

20

30

40

50

0を行った後に得られた製品の構造模式図が図11に示す通りである。

【0020】

なお、本実施例において、上記のフリップチップは、具体的に、LEDフリップチップであってもよく、具体的な実施過程において、上記のフリップチップ1の電極表面自体は金属層を設置してもよく、設置しなくてもよく、上記のパッケージ基板の表面自体も金属層を設置してもよく、設置しなくてもよい。

【0021】

実施例2

本実施例と実施例1の相違は、本実施例では前記パッケージ基板としてセラミックパッケージ基板を利用することにあり、図12に示すように、本実施例によるフリップチップのパッケージ方法は以下のステップを含む。

【0022】

ステップ201であって、複数のフリップチップ1をセラミックパッケージ基板8に埋め込み、本実施例の前記フリップチップは具体的には1mmの長さ、1mmの幅、0.35mmの厚さのLEDフリップチップであり、型番は具体的にはCREEDA1000であり、具体的な操作は、フリップチップ1の厚さよりもやや大きい厚さ(約0.6mm)のセラミックパッケージ基板8を設置し、それぞれのセラミックパッケージ基板8のユニット中心に、チップの形状に一致するがサイズが少し大きい空洞切欠きを設け、セラミックパッケージ基板8の一側面に、フリップチップ1の2つの電極に対応し且つ互いに絶縁した金属層及び金属層に金属で接続されたスルーホールを設置することにより外部ヒートシンクとし、ステップ201を行った後に得られた中間製品の平面図および側面図のそれぞれは図13および14に示す通りである。

ステップ202であって、セラミックパッケージ基板8の金属層が設けられた一面をシリコンチップ表面に下向きに配置し、フリップチップ1の電極表面をセラミックパッケージ基板8の空洞に下向きに入れ、フリップチップ1の出光表面に蛍光ゲル9を塗布し、或いは蛍光膜を設置してもよく、ステップ202を行った後に得られた中間製品の構造模式図が図15に示す通りであり、

ステップ203であって、セラミックパッケージ基板8の空洞にシリカゲル10を鋳込み、鋳込み材料を硬化乾燥させることにより、フリップチップ1とセラミックパッケージ基板8をシリカゲル10で固定し、ステップ203を行った後に得られた中間製品の構造模式図が図16に示す通りであり、

ステップ204であって、シリコンチップを、研削や化学方式で除去することで、フリップチップ1がシリカゲル10によりセラミックパッケージ基板8に固定されたアレイを得ると共に、フリップチップ1の電極表面がセラミックパッケージ基板8の表面に十分に重ね合うようになり、

ステップ205であって、セラミックパッケージ基板8の金属層が設けられた一面及びフリップチップ1の電極表面に同様に金導電層4とクロム導電層5とを含む前記金属導電膜を設置し、具体的な設置は実施例1のステップ104と同様であり、ステップ205を行った後に得られた中間製品の構造模式図が図17に示す通りであり

ステップ206であって、金属導電膜の表面(具体的に、前記金導電層4)に、フォトレジスト6を塗布し、行う方式は実施例1のステップ105と同様であり、ステップ206を行った後に得られた中間製品の構造模式図が図18に示す通りであり、

ステップ207であって、マスクアライナにおいて、フォトリソグラフィプレート上の電極構造の一部とフリップチップ1上の電極構造をアライメントしてフォトエッチングし、そして、フリップチップ1の一方の電極Nと対応するセラミックパッケージ基板8の表面金属が一方の領域内にあり、他方の電極Pの対応するセラミックパッケージ基板8の表面金属が他方の領域内にあるように露光させ、

ステップ208であって、露光したフォトトレジストを現像し、単一のフリップチップの電極表面と対応するセラミックパッケージ基板8の表面が同一領域にあるフォトトレジスト構造モールドを得ると共に、フリップチップ1の電極間の絶縁箇所をフォトトレジスト6が

10

20

30

40

50

被覆するようにし、ステップ 208 を行った後に得られた中間製品の平面図および側面図はそれぞれ図 19 および 20 に示す通りであり、

ステップ 209 であって、前記金属導電膜でフォトレジスト構造モールド内における銅電鋳を成長させ、具体的な操作は実施例 1 のステップ 107 と同様であり、ステップ 209 を行った後に得られた中間製品の構造模式図が図 21 に示す通りであり、

ステップ 210 であって、ゾル溶液により露光されていないフォトレジスト 6 を溶解し、ステップ 210 を行った後に得られた中間製品の構造模式図が図 22 に示す通りであり、

ステップ 211 であって、腐食液によりステップ 210 で除去されたフォトレジストの下に被覆されている金導電層を腐食すると共に、クロム腐食液により金導電層に被覆されているクロム導電層を腐食することによって、フリップチップ電極間の電気接続を切断し、ステップ 211 を行った後に得られた製品の構造模式図が図 23 に示す通りである。

10

### 【0023】

以上は本発明の具体的な実施形態を記述したが、これらは例示的な説明に過ぎず、本発明の保護範囲は添付された請求の範囲によって限定されることは当業者ならば理解すべきである。当業者は、本発明の原理や主旨を逸脱しない限り、それらの実施形態について様々な変更、修正を行うことができ、それらの変更、修正のいずれも本発明の保護範囲に含まれる。

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

【図 15】

【図 16】

【図 17】

【図 18】

【図 19】

【図 20】

【図 21】

【図 22】

【図 23】

---

フロントページの続き

(72)発明者 イ フーティン

中華人民共和国 100049 ベイジン ジンシャン ディストリクト ユークアン ロード

ナンバー 19 ピー

(72)発明者 パン ミン

中華人民共和国 210008 チャンスー ナンジン シエンワー ディストリクト ジンシャ

ンホー ロード ナンバー 33-2 ルーム 602

審査官 安田 雅彦

(56)参考文献 国際公開第2011/093454 (WO, A1)

国際公開第2014/034024 (WO, A1)

特開2010-062430 (JP, A)

特開2009-164221 (JP, A)

特開2004-048012 (JP, A)

特開2013-117390 (JP, A)

国際公開第2013/145071 (WO, A1)

特開2012-256769 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60 - 607

H01L 21/768

H01L 23/52 - 538

H01L 23/12 - 15

H01L 33/48 - 64

H05K 1/18

H05K 3/18

H05K 3/30 - 34

H05K 3/46