(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5312453号

(P5312453)

(45) 発行日 平成25年10月9日(2013.10.9)

(24) 登録日 平成25年7月12日(2013.7.12)

(51) Int.Cl.

HO3K 19/0175 (2006.01)

F 1

HO3K 19/00 101Q

HO3K 19/00 101S

請求項の数 15 (全 22 頁)

(21) 出願番号 特願2010-510622 (P2010-510622)

(86) (22) 出願日 平成20年6月6日 (2008.6.6)

(65) 公表番号 特表2010-529759 (P2010-529759A)

(43) 公表日 平成22年8月26日 (2010.8.26)

(86) 國際出願番号 PCT/CA2008/001069

(87) 國際公開番号 WO2008/148197

(87) 國際公開日 平成20年12月11日 (2008.12.11)

審査請求日 平成23年1月20日 (2011.1.20)

(31) 優先権主張番号 60/942,798

(32) 優先日 平成19年6月8日 (2007.6.8)

(33) 優先権主張国 米国(US)

(73) 特許権者 593138296

モーセッド・テクノロジーズ・インコーポ

レイテッド

M o s a i d T e c h n o l o g i e s

I n c o r p o r a t e d

カナダ国 ケイ2ケイ 2エックス1 オ

ンタリオ, オタワ, ハインズ・ロード 1

1, スイート 203

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

最終頁に続く

(54) 【発明の名称】入力／出力バッファの動作インピーダンス制御

## (57) 【特許請求の範囲】

## 【請求項 1】

結合型駆動及び終端回路であつて：

第1の複数のトランジスタを有する可変インピーダンス・プルアップ回路網、

第2の複数のトランジスタを有する可変インピーダンス・プルダウン回路網、

前記プルアップ回路網の終端構成を設定する第1の複数の制御ビット、

前記プルダウン回路網の終端構成を設定する第2の複数の制御ビット、

前記プルアップ回路網の駆動構成を設定する第3の複数の制御ビット、

前記プルダウン回路網の駆動構成を設定する第4の複数の制御ビット、

を有し、

前記回路は、前記可変インピーダンス・プルアップ回路網が前記第1の複数の制御ビットに基づきプルアップ回路網終端インピーダンスを有するよう構成され、前記可変インピーダンス・プルダウン回路網が前記第2の複数の制御ビットに基づきプルダウン回路網終端インピーダンスを有するよう構成され、該プルアップ回路網及び該プルダウン回路網は共同して分割終端として動作する終端動作モードを有し、

前記回路は、

ハイ出力を駆動するために、前記プルアップ回路網が前記第3の複数の制御ビットに基づきオンに切り替えられたとき特定のインピーダンスを生成するよう構成され、

ロー出力を駆動するために、前記プルダウン回路網が前記第4の複数の制御ビットに基づきオンに切り替えられたとき特定のインピーダンスを生成するよう構成される、

10

20

駆動動作モードを有し、

前記プルアップ回路網及び前記プルダウン回路網のそれぞれは、オンに切り替えられたトランジスタの数を変化させることにより、所望のインピーダンスを有するよう構成され、

前記第1乃至第4の複数の制御ビットは、互いに独立である、

ことを特徴とする回路。

【請求項2】

コア・ロジック、

対応するI/Oパッドをそれぞれ有する複数のI/O(入力/出力)、

I/O毎に、対応する請求項1に記載の結合型駆動及び終端回路、

を有し、

10

該結合型駆動及び終端回路は、前記コア・ロジックからの出力を生成し、前記コア・ロジックへの外部入力を終端するよう動作する、

ことを特徴とするコア・ロジック。

【請求項3】

前記プルアップ及びプルダウン回路網は、駆動動作モードと終端動作モードとの間で転換するときに、2つのインピーダンス設定の間で動的に切り替えられる、

ことを特徴とする請求項2記載の装置。

【請求項4】

I/O毎に、AND-OR-ANDロジックを有し、ハイへの駆動を示す第1の入力と

ローへの駆動を示す第2の入力と終端を示す第3の入力とを受信し、相応して2つのインピーダンス設定の間で切り替えるプリドライバ・ロジック、

を更に有する請求項2、3の何れか一項記載の装置。

20

【請求項5】

基準インピーダンスに対して前記インピーダンスを較正する較正ロジック、

と結合する請求項1に記載の回路。

【請求項6】

コア・ロジック、

対応する入力パッドをそれぞれ有する複数の入力、

対応する出力パッドをそれぞれ有する複数の出力、

30

恒久的に終端モードになるようにされた、入力パッド毎の対応する請求項1、5の何れか一項記載の結合型駆動及び終端回路、

恒久的に駆動モードになるようにされた、出力パッド毎の対応する請求項1記載の結合型駆動及び終端回路、

を有する装置。

【請求項7】

前記複数の制御ビットは、トランジスタ当たり1ビットを有する、請求項1に記載の結合型駆動及び終端回路。

【請求項8】

前記プルアップ回路網は、並列に共に結合された複数のトランジスタを有し、

40

前記プルアップ回路網の可変インピーダンスは、前記複数のトランジスタのうちの特定の数を選択的にオンに切り替えることにより制御され、

前記プルダウン回路網は、並列に共に結合された複数のトランジスタを有し、

前記プルダウン回路網の可変インピーダンスは、前記複数のトランジスタのうちの特定の数を選択的にオンに切り替えることにより制御される、

ことを特徴とする請求項1、5の何れか一項に記載の結合型駆動及び終端回路。

【請求項9】

請求項1、5、8の何れか一項に記載の結合型駆動及び終端回路、

較正の実行で用いられる前記結合型駆動及び終端回路の少なくとも一部の複製、

を有する装置。

50

## 【請求項 10】

- (1) データ出力が論理ハイのとき、駆動モードのためにプルアップ回路網を較正する段階、

(2) データ出力が論理ローのとき、駆動モードのためにプルダウン回路網を較正する段階、

(3) 終端モードのためにプルアップ回路網を較正する段階、

(4) 終端モードのためにプルダウン回路網を較正する段階、

の 4 段階で実行される較正を制御する制御部、

を更に有する請求項 9 に記載の装置。

## 【請求項 11】

前記プルアップ回路網は複数の p 型 M O S F E T トランジスタを有し、

前記プルダウン回路網は複数の n 型 M O S F E T トランジスタを有し、

当該装置は、

- (1) n 型素子の出力インピーダンスを較正し、データ出力が論理ローのとき、駆動モードのために何個の前記 n 型トランジスタがイネーブルされるべきかを決定する段階、

(2) p 型素子の出力インピーダンスを較正し、データ出力が論理ハイのとき、駆動モードのために何個の前記 p 型トランジスタがイネーブルされるべきかを決定する段階、

(3) n 型素子の終端を較正し、終端モードのために何個の前記 n 型トランジスタがイネーブルされるべきかを決定する段階、

(4) p 型素子の終端を較正し、終端モードのために何個の前記 p 型トランジスタがイネーブルされるべきかを決定する段階、

の 4 段階で実行される較正を制御する制御部、

を更に有する請求項 9 に記載の装置。

## 【請求項 12】

前記プルアップ回路網及び前記プルダウン回路網は、全体が n 型トランジスタ又は p 型トランジスタでそれぞれ形成され、

当該装置は：

- (1) データ出力が論理ハイのとき、駆動モードのためにプルアップ回路網を較正する段階、

(2) 終端モードのためにプルアップ回路網を較正する段階、

の 2 段階で実行される較正を制御する制御部、

を更に有する請求項 9 に記載の装置。

## 【請求項 13】

前記オンに切り替えられたトランジスタの数は、温度計コードを用いて徐々に変化される、

ことを特徴とする請求項 1 に記載の装置。

## 【請求項 14】

前記温度計コードに変換されるオンに切り替えられたトランジスタの数を、グレイコードを用いて符号化する、

ことを特徴とする請求項 13 に記載の装置。

## 【請求項 15】

結合型駆動及び終端を提供する方法であつて：

終端モードで、可変インピーダンス・プルアップ回路網を第 1 の複数の制御ビットに基づきプルアップ回路網終端インピーダンスを有するよう構成し、可変インピーダンス・プルダウン回路網を第 2 の複数の制御ビットに基づきプルダウン回路網終端インピーダンスを有するよう構成し、該プルアップ回路網及び該プルダウン回路網は分割終端として共同して動作し、該プルアップ回路網及び該プルダウン回路網のそれぞれは同一のインピーダンスを提供するよう大きさの定められた複数のトランジスタを有し、該プルアップ回路網及び該プルダウン回路網のそれぞれはオンに切り替えられたトランジスタの数を徐々に変化させることにより、所望のインピーダンスを有するよう構成される段階、

駆動モードで、ハイ出力を駆動するために、前記プルアップ回路網を第 3 の複数の制御

10

20

30

40

50

ビットに基づき第1の駆動インピーダンスを生成するよう構成する段階、

前記駆動モードで、ロー出力を駆動するために、前記プルダウン回路網を第4の複数の制御ビットに基づき第2の駆動インピーダンスを生成するよう構成する段階、

を有し、

前記第1乃至第4の複数の制御ビットは、互いに独立である、方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力／出力バッファの動作インピーダンス制御に関する。

【背景技術】

【0002】

同期型ダイナミック・ランダム・アクセス・メモリ(SDRAM)メモリ制御部は、パソコン・コンピュータ内で並びに通常、マイクロプロセッサ及びSDRAMが製品内に組み込まれ制御機能及び該製品のユーザ・インターフェースを定める多様な電子製品内で用いられている。SDRAMメモリ制御部は、プログラムを動作させるときに、マイクロプロセッサに高速SDRAMへの効率的なアクセスを可能にする。

【0003】

チップ製造者は、シリコン技術の電気的性能及び経済的效果を益々向上させながら、シリコン・プロセスの形状を容赦なく縮小するので、システムに適用するときに、クロック・レート及びデータ・レートが新たな生成と重なってしまうような、チップ間の物理インターフェースにおける深刻な信号の完全性問題が生じる。高いクロック・レートでは、信号の完全性は、主にメモリ制御チップとSDRAMチップとの間の相互接続における伝送線の影響により、屢々損なわれてしまう。

【0004】

反射、減衰、クロストーク及びグラウンド・バウンスを含む伝送線の影響は、全てチップ間の相互接続における信号品質を低下させてしまう。チップ間相互接続における反射は、正しく管理されないと、高速システム内の信号の完全性を完全に破壊しうる。

【0005】

全ての伝送線は、導体の形状及び該導体の周囲にある絶縁材の誘電率により定められる特性インピーダンス及び特有の信号速度を有する。伝送線を往復して伝搬する信号の反射は、制御されないと、存続不可能な点まで信号品質を低下させうる。しかしながら、伝送線の一端を駆動する回路の信号源インピーダンス及び該伝送線の他端にある終端インピーダンスが該伝送線の特性インピーダンスと整合している場合は、如何なる信号反射も伝送線内で生じない。半導体回路、通常はCMOS(相補型金属酸化膜半導体)トランジスタを用い、プリント基板(PCB)のトレース上で信号をオフチップで駆動し、該プリント基板上の他のチップの半導体回路により受信されるようにするとき、該トレースの受信端が伝送線のインピーダンスと厳密に整合する特定のインピーダンスで終端されない場合、重大な信号反射が屢々生じる。

【0006】

以前は、高速信号は、PCBトレースの特性インピーダンスより遙かに低い出力インピーダンスを有するI/O(入力／出力)バッファで駆動されていた。PCBトレースは、該トレースの特性インピーダンスに整合する抵抗値を有する固定抵抗を用いて終端されていた。幾つかの用途では、信号の完全性を向上するために、固定抵抗も駆動バッファと直列に配置されていた。DDR(ダブル・データ・レート)SDRAMの出現は、信号源インピーダンスと終端インピーダンスを内部化する方法の発見へと半導体産業を導き、これらの新しいメモリ・システム内のPCBトレースのインピーダンスを整合するために必要な固定外部抵抗を配置した。動機は、常に価格低下及び省電力化である。整合した終端インピーダンスが存在する場合、DDRメモリ・システムで良好な信号の完全性が得られることが明確に実証された。終端が伝送線の端へ伝搬する信号を吸収する限り、如何なる反射も生じない。これらのシステムでは、伝送線を駆動する回路の信号源インピーダンスは

10

20

30

40

50

、意図的に P C B トレースの特性インピーダンスよりも低くされ、より良好な雑音排除性のためにより大きな信号の振れを生成した。

【 0 0 0 7 】

C M O S I / O 回路は、特定の条件下で伝送線インピーダンスと非常に良好に整合するよう設計されうるが、回路について期待されるプロセス、電圧及び温度 ( P V T ) の全範囲に渡り 2 : 1 を屡々超える大きなインピーダンス変化を示す。P V T 变化に対抗するため、回路設計者は、オフチップ・ドライブ ( O f f - C h i p D r i v e : O C D ) 及びオンダイ・ターミネーション ( O n - D i e T e r m i n a t i o n : O D T ) のために幾らかの調整機能を組み込んできた。

【 0 0 0 8 】

今日では、特に、高速通信機ロジック ( H S T L ) 及び D D R の応用で、設定可能な出力インピーダンスのための多くの解決法が用いられている。多くの場合には、出力インピーダンス制御のためにわずか 2 つの設定しかない。多くの場合に、出力インピーダンスは、基準インピーダンスに対して動的に設定されない。

【先行技術文献】

【非特許文献】

【 0 0 0 9 】

【特許文献 1】米国特許第 5 , 1 0 7 , 2 3 0 号明細書

【特許文献 2】米国特許第 5 , 1 3 4 , 3 1 1 号明細書

【特許文献 3】米国特許第 5 , 1 9 4 , 7 6 5 号明細書

【特許文献 4】米国特許第 5 , 4 5 7 , 4 0 7 号明細書

【特許文献 5】米国特許第 5 , 6 6 6 , 0 7 8 号明細書

【特許文献 6】米国特許第 5 , 9 5 5 , 8 9 4 号明細書

【特許文献 7】米国特許第 6 , 0 2 1 , 0 7 1 号明細書

【特許文献 8】米国特許第 6 , 0 4 9 , 2 2 1 号明細書

【特許文献 9】米国特許第 6 , 0 6 0 , 9 0 7 号明細書

【特許文献 10】米国特許第 6 , 0 8 7 , 8 4 7 号明細書

【特許文献 11】米国特許第 6 , 1 1 8 , 3 1 0 号明細書

【特許文献 12】米国特許第 6 , 1 6 6 , 5 6 3 号明細書

【特許文献 13】米国特許第 6 , 2 5 5 , 8 7 4 号明細書

【特許文献 14】米国特許第 6 , 2 7 5 , 0 6 2 号明細書

【特許文献 15】米国特許第 6 , 3 0 7 , 4 2 4 号明細書

【特許文献 16】米国特許第 6 , 3 2 6 , 8 0 2 号明細書

【特許文献 17】米国特許第 6 , 5 0 1 , 2 9 3 号明細書

【特許文献 18】米国特許第 6 , 5 0 9 , 7 5 7 号明細書

【特許文献 19】米国特許第 6 , 8 6 4 , 7 0 4 号明細書

【特許文献 20】米国特許第 6 , 8 8 5 , 9 5 9 号明細書

【特許文献 21】米国特許第 6 , 8 9 4 , 5 2 9 号明細書

【特許文献 22】米国特許第 7 , 1 1 9 , 5 4 9 号明細書

【特許文献 23】米国特許第 7 , 1 3 5 , 8 8 4 号明細書

【特許文献 24】米国特許第 7 , 4 1 7 , 4 5 2 号明細書

【特許文献 25】米国特許出願第 2 0 0 4 - 0 1 8 3 5 6 5 A 1 号明細書

【特許文献 26】米国特許出願第 2 0 0 5 - 0 2 2 6 0 8 0 A 1 号明細書

【特許文献 27】米国特許出願第 2 0 0 6 - 0 2 2 6 8 6 8 A 1 号明細書

【特許文献 28】米国特許出願第 2 0 0 6 - 0 2 5 5 8 3 0 A 1 号明細書

【特許文献 29】米国特許出願第 2 0 0 7 - 0 0 5 7 6 9 1 A 1 号明細書

【特許文献 30】米国特許出願第 2 0 0 7 - 0 1 2 6 4 6 6 A 1 号明細書

【特許文献 31】米国特許出願第 2 0 0 7 - 0 1 2 6 4 6 7 A 1 号明細書

【非特許文献 1】 J e d e c S t a n d a r d , D D R 2 S D R A M S p e c i f i c a t i o n , J E S D 7 9 - 2 E ( R e v i s i o n o f J E S D 7 9 - 2 D )

10

20

30

40

50

, Apr. 2008, J ed e c S o l i d S t a t e T e c h n o l o g y A s s o c i a t i o n

【非特許文献2】J ed e c S t a n d a r d , S t u b S e r i e s T e r m i n a t e d L o g i c f o r 1 . 8 V ( S S T L \_ 1 8 ) , J E S D 8 - 1 5 A , A d d e n d u m 1 5 t o J E S D 8 S e r i e s ( R e v i s i o n o f J E S D 8 - 1 5 ) , S e p . 2 0 0 3 , J ed e c S o l i d S t a t e T e c h n o l o g y A s s o c i a t i o n

【非特許文献3】E I A / J ed e c S t a n d a r d , S t u b S e r i e s T e r m i n a t e d L o g i c f o r 3 . 3 V o l t s ( S S T L \_ 3 ) , E I A / J E S D 8 - 8 , A u g . 1 9 9 6 , E l e c t r o n i c I n d u s t r i e s A s s o c i a t i o n , E n g i n e e r i n g D e p a r t m e n t

【非特許文献4】J ed e c S t a n d a r d , D D R 2 S D R A M S p e c i f i c a t i o n , J E S D 7 9 - 2 B ( R e v i s i o n o f J E S D 7 9 - 2 A ) , J a n . 2 0 0 5 , J ed e c S o l i d S t a t e T e c h n o l o g y A s s o c i a t i o n

【非特許文献5】J ed e c S t a n d a r d , S t a b S e r i e s T e r m i n a t e d L o g i c f o r 2 . 5 V ( S S T L \_ 2 ) , J E S D 8 - 9 B ( R e v i s i o n o f J E S D 8 - 9 A ) , M a y 2 0 0 2 , J ed e c S o l i d S t a t e T e c h n o l o g y A s s o c i a t i o n

【非特許文献6】S u p p l e m e n t a r y E u r o p e a n S e a r c h R e p o r t , E u r o p e a n P a t e n t A p p l i c a t i o n N o . 0 8 7 5 7 2 0 5 . 3 , J u l . 1 6 , 2 0 1 0

### 【発明の概要】

【発明が解決しようとする課題】

#### 【0010】

本発明は、入力／出力バッファの動作インピーダンス制御を行うシステム及び方法を提供する。

#### 【課題を解決するための手段】

#### 【0011】

##### ＜要約＞

第1の広範な態様によると、本発明は結合型駆動及び終端回路を提供する。当該開路は：可変インピーダンス・プルアップ回路網；可変インピーダンス・プルダウン回路網；前記プルアップ回路網の構成を設定する少なくとも1つの制御入力；前記プルダウン回路網の構成を設定する少なくとも1つの制御入力；前記可変インピーダンス・プルアップ回路網がプルアップ回路網終端インピーダンスを有するよう構成され；前記可変インピーダンス・プルダウン回路網がプルダウン回路網終端インピーダンスを有するよう構成され；該プルアップ回路網及び該プルダウン回路網は共同して分割終端として動作する終端動作モードを有する装置；ハイ出力を駆動するために、前記プルアップ回路網がオンに切り替えられたとき特定のインピーダンスを生成するよう構成され；ロー出力を駆動するために、前記プルダウン回路網がオンに切り替えられたとき特定のインピーダンスを生成するよう構成される；駆動モードを有する装置；を有する。

#### 【0012】

幾つかの実施例では、装置は、コア・ロジック；対応するI/Oパッドをそれぞれ有する複数のI/O（入力／出力）；I/O毎に、対応する上記結合型駆動及び終端回路；を有し、該結合型駆動及び終端回路は、前記コア・ロジックからの出力を生成し、前記コア・ロジックへの外部入力を終端するよう動作する。

#### 【0013】

幾つかの実施例では、前記プルアップ及びプルダウン回路網は、駆動モードと終端モードとの間で転換するときに、2つのインピーダンス設定の間で動的に切り替えられ。

#### 【0014】

10

20

30

40

50

幾つかの実施例では、当該装置は、I/O毎に、AND-OR-ANDロジックを有し、ハイへの駆動を示す第1の入力とローへの駆動を示す第2の入力と終端を示す第3の入力とを受信し、相応して2つのインピーダンス設定の間で切り替えるプリドライバ・ロジック；を更に有する。

【0015】

幾つかの実施例では、当該回路は、基準インピーダンスに対して前記インピーダンスを較正する較正ロジック；と結合される。

【0016】

幾つかの実施例では、装置は、コア・ロジック；対応する入力パッドをそれぞれ有する複数の入力；対応する出力パッドをそれぞれ有する複数の出力；恒久的に終端モードになるようにされた、入力パッド毎の対応する上記結合型駆動及び終端回路；恒久的に駆動モードになるようにされた、出力パッド毎の対応する上記結合型駆動及び終端回路；を有する。

10

【0017】

幾つかの実施例では、装置は、上記結合型駆動及び終端回路；前記結合型駆動及び終端回路が駆動モード又は終端モードであるかに応じて前記制御入力を生成する制御部；を有する。

【0018】

幾つかの実施例では、前記プルアップ回路網は、並列に共に結合された複数のトランジスタを有し；前記プルアップ回路網の前記可変インピーダンスは、前記複数のトランジスタのうちの特定の数を選択的にオンに切り替えることにより制御され；前記プルダウン回路網は、並列に共に結合された複数のトランジスタを有し；前記プルダウン回路網の前記可変インピーダンスは、前記複数のトランジスタのうちの特定の数を選択的にオンに切り替えることにより制御される；ことを特徴とする。

20

【0019】

幾つかの実施例では、装置は、上記結合型駆動及び終端回路；キャリブレーションの実行で用いられる前記結合型駆動及び終端回路の少なくとも一部の複製；を有する。

【0020】

幾つかの実施例では、装置は、(1)データ出力が論理ハイのとき、駆動モードのためにプルアップ回路網を較正する段階；(2)データ出力が論理ローのとき、駆動モードのためにプルダウン回路網を較正する段階；(3)終端モードのためにプルアップ回路網を較正する段階；(4)終端モードのためにプルダウン回路網を較正する段階；の4段階で実行される較正を制御する制御部；を更に有する。

30

【0021】

幾つかの実施例では、前記プルアップ回路網は複数のp型MOSFETトランジスタを有し、前記プルダウン回路網は複数のn型MOSFETトランジスタを有し、当該装置は、(1)n型素子の出力インピーダンスを較正し、データ出力が論理ローのとき、駆動モードのために何個の前記n型トランジスタがイネーブルされるべきかを決定する段階；(2)p型素子の出力インピーダンスを較正し、データ出力が論理ハイのとき、駆動モードのために何個の前記p型トランジスタがイネーブルされるべきかを決定する段階；(3)n型素子の終端を較正し、終端モードのために何個の前記n型トランジスタがイネーブルされるべきかを決定する段階；(4)p型素子の終端を較正し、終端モードのために何個の前記p型トランジスタがイネーブルされるべきかを決定する段階；の4段階で実行される較正を制御する制御部；を更に有する。

40

【0022】

幾つかの実施例では、前記プルアップ回路網及び前記プルダウン回路網は、全体がn型トランジスタ又はp型トランジスタでそれぞれ形成され、当該装置は：(1)データ出力が論理ハイのとき、駆動モードのためにプルアップ回路網を較正する段階；(2)終端モードのためにプルアップ回路網を較正する段階；の2段階で実行される較正を制御する制御部；を更に有する。

50

## 【0023】

幾つかの実施例では、前記プルアップ回路網は複数のp型MOSFETトランジスタを有し、前記プルダウン回路網は複数のn型MOSFETトランジスタを有し、当該装置は：(1)n型素子の出力インピーダンスを較正し、データ出力が論理ローのとき、駆動モードのために何個の前記n型トランジスタがイネーブルされるべきかを決定する段階；(2)n型素子の終端を較正し、終端モードのために何個の前記n型トランジスタがイネーブルされるべきかを決定する段階；の2段階で実行される較正を制御する制御部；を更に有する。

## 【0024】

幾つかの実施例では、当該装置は、共通の較正值を各結合型駆動及び終端回路に渡す相互接続；を更に有する。幾つかの実施例では、前記相互接続は、1又は複数の温度計コードを用いて前記較正值を供給する、ことを特徴とする。

10

## 【0025】

幾つかの実施例では、前記プルアップ回路網は複数のp型トランジスタを有し、前記プルダウン回路網は複数のn型トランジスタを有し、前記相互接続は：データ出力が論理ローのとき、駆動モードのために何個の前記n型トランジスタがイネーブルされるべきかを設定する第1の較正值；データ出力が論理ハイのとき、駆動モードのために何個の前記p型トランジスタがイネーブルされるべきかを設定する第2の較正值；終端モードのために何個の前記n型トランジスタがイネーブルされるべきかを設定する第3の較正值；終端モードのために何個の前記p型トランジスタがイネーブルされるべきかを設定する第4の較正值；を供給する；ことを特徴とする。

20

## 【0026】

幾つかの実施例では、装置は、複数の上記結合型駆動及び終端回路；共通の較正值を各結合型駆動及び終端回路に渡す相互接続；各結合型駆動及び終端回路に存在し、特定の結合型駆動及び終端回路が論理ローを出力するか若しくは論理ハイを出力する駆動モードであるか又は終端モードであるかに応じて、前記較正值のうちの1つを選択的に適用するブリドライバ；を有する。

## 【0027】

別の広範な態様によると、本発明は、終端トランジスタを兼ねる駆動トランジスタ；を有する結合型ODT(オンダイ終端)及び OCD(オフチップ駆動)回路を提供する。

30

## 【0028】

別の広範な態様によると、本発明は、少なくとも1つのプルダウン・トランジスタに結合された少なくとも1つのプルアップ・トランジスタ；該プルアップ・トランジスタ及び該プルダウン・トランジスタの間に結合された入力；を有し、該少なくとも1つのプルダウン・トランジスタ及び該少なくとも1つのプルアップ・トランジスタは、該入力を終端するよう動作する、ことを特徴とするオンチップ終端回路を提供する。

## 【0029】

幾つかの実施例では、前記少なくとも1つのプルアップ・トランジスタは、選択的にイネーブルされうる第1の複数のトランジスタを有し、前記少なくとも1つのプルダウン・トランジスタは、選択的にイネーブルされうる第2の複数のトランジスタを有し、前記第1及び第2の複数のトランジスタのうちのイネーブルされる数は、当該回路の終端インピーダンスを設定する、ことを特徴とする。

40

## 【0030】

別の広範な態様によると、本発明は、結合型駆動及び終端を提供する方法を提供する。当該方法は：終端動作モードで、プルアップ回路網終端インピーダンスを有するよう可変インピーダンス・プルアップ回路網を構成し、プルダウン回路網終端インピーダンスを有するよう可変インピーダンス・プルダウン回路網を構成し、該プルアップ回路網及び該プルダウン回路網は、分割終端として共同して動作する段階；駆動動作モードで、ハイ出力を駆動するために、前記プルアップ回路網を第1の駆動インピーダンスを生成するよう構成する段階；前記駆動動作モードで、ロー出力を駆動するために、前記プルダウン回路網

50

を第 2 の駆動インピーダンスを生成するよう構成する段階；を有する。

【0031】

幾つかの実施例では、当該方法は：前記終端モードと前記駆動モードとの間で動作モードを選択する段階；を更に有する。

【0032】

幾つかの実施例では、プルアップ終端インピーダンスを有するよう前記プルアップ回路網を構成する段階は、該プルアップ回路網を形成する複数のトランジスタのうちの特定数を選択的にオンに切り替える段階を有し；プルダウン終端インピーダンスを有するよう前記プルダウン回路網を構成する段階は、該プルダウン回路網を形成する複数のトランジスタのうちの特定数を選択的にオンに切り替える段階を有する；ことを特徴とする。幾つかの実施例では、当該方法は：前記プルアップ終端インピーダンス、前記プルダウン終端インピーダンス、前記第 1 の駆動インピーダンス及び前記第 2 の駆動インピーダンスを較正するために更に較正を実行する段階；を更に有する。

10

【0033】

幾つかの実施例では、較正を実行する段階は：データ出力が論理ハイのとき、駆動モードのために前記プルアップ回路網を較正する段階；データ出力が論理ローのとき、駆動モードのために前記プルダウン回路網を較正する段階；終端モードのために前記プルアップ回路網を較正する段階；終端モードのために前記プルダウン回路網を較正する段階；を更に有する、ことを特徴とする。

20

【0034】

幾つかの実施例では、較正を実行する段階は：データ出力が論理ハイのとき、駆動モードのために前記プルアップ回路網を較正し、第 1 の較正結果を生成する段階；該第 1 の較正結果を用いて、データ出力が論理ローのとき、駆動モードのために前記プルダウン回路網を較正する段階；終端モードのために前記プルアップ回路網を較正し、第 2 の較正結果を生成する段階；該第 2 の較正結果を用いて、終端モードのために前記プルダウン回路網を較正する段階；を有する、ことを特徴とする。

【0035】

本発明の実施例は、添付の図面を参照してより詳細に説明される。

【図面の簡単な説明】

【0036】

30

【図 1】従来のセル構造と本発明の実施例により提供されるセル構造とのフロアの比較である。

【図 2 A】本発明の実施例により提供される結合型オンチップ駆動 / オンダイ・ターミネーションのブロック図である。

【図 2 B】本発明の実施例により提供される、クワッド・データ・レートの用途に適した結合型オンチップ駆動 / オンダイ・ターミネーションのブロック図である。

【図 2 C】どのようにキャリブレーションが実行されうるかを説明する回路図である。

【図 2 D】本発明の実施例により提供される、DDR3 の用途に適した結合型オンチップ駆動 / オンダイ・ターミネーションのブロック図である。

【図 3】本発明の実施例により提供される I / O セル構造の詳細なブロック図である。

40

【図 4 A】図 3 のコア・ロジック機能の論理図である。

【図 4 B】図 4 A の論理図の真理値表である。

【図 5】結合型の駆動及び終端を提供する方法のフローチャートである。

【図 6】図 5 の方法を較正する第 1 の方法のフローチャートである。

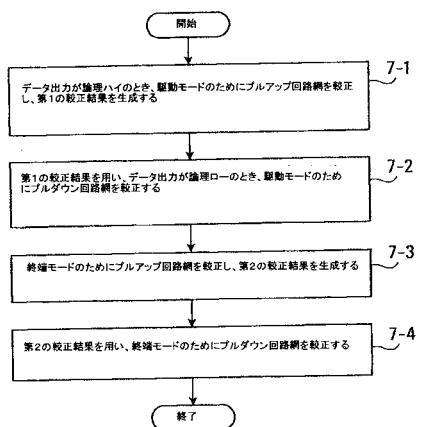

【図 7】図 5 の方法を較正する第 2 の方法のフローチャートである。

【発明を実施するための形態】

【0037】

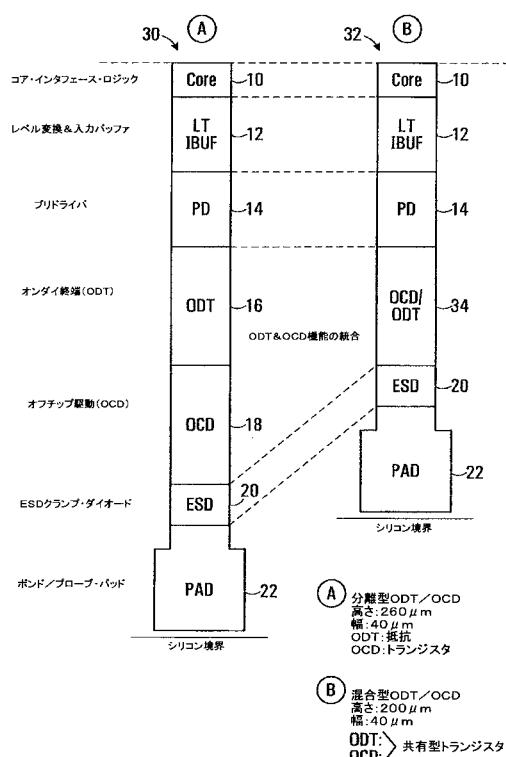

図 1 を参照すると、2 つの異なる DDR 入力 / 出力 (I / O) セル構造のフロアプランが示される。通常、従来のセル構造 30 は、コア・インターフェース・ロジック 10、レベル変換及び入力バッファ 12、プリドライバ 14、オンダイ・ターミネーション (ODT

50

) 16、オフチップ・ドライバ(OC'D)18、静電放電(ES'D)クランプ・ダイオード20及びボンド／プローブ・パッド22を有する。例えば、非特許文献1を参照のこと。

【0038】

概ね、本発明の実施例により提供されるセル構造32も、コア10、レベル変換及び入力バッファ12、プリドライバ14、ES'D20及びパッド22を有する。しかしながら、本実施例では、オンダイ・ターミネーション16及びオフチップ・ドライバ18は別個の要素ではなく、結合されたオフチップ・ドライバ／オンダイ駆動(OC'D／OD'T)34が提供される。

【0039】

図1のセルI/O構造32は、SDRAMメモリ素子のようなメモリ素子に結合されるメモリ制御部のI/Oとして用いられることを目的としているが、I/O構造は、実際のメモリ素子自体及び例えばCPU、FPGA、制御部、メモリ等を含む任意の高速CMOSチップ間相互接続での他の用途も考えられる。

【0040】

留意すべき点は、従来の構造30では、別個のOD'T及びOC'Dが存在し、例えば可能な実装に特有の寸法は高さ260μm及び幅40μmになることである。OD'T16は、通常、抵抗を用いて実施され、OC'D18は、通常、トランジスタを用いて実施される。

【0041】

新規なセル構造32では、結合型OD'T／OC'Dが存在し、例えば可能な実装に特有の寸法はセル構造が全体で高さ200μmを有することである。OD'T及びOC'Dは、共有トランジスタを用いて実施される。

【0042】

図1は、OC'D／OD'T機能がセル構造内に実施された特定の例である。概して、本例で提供される結合型OC'D／OD'T回路は、終端及び駆動の両方を必要とする如何なるセル構造内で用いられてもよい。更に別の実施例では、結合型OC'D／OD'T回路は、専用の終端及び駆動機能を有するセル内に、それぞれ設計及び試験の簡略化のために利用されている同じ回路の別の存在と共に実施される。

【0043】

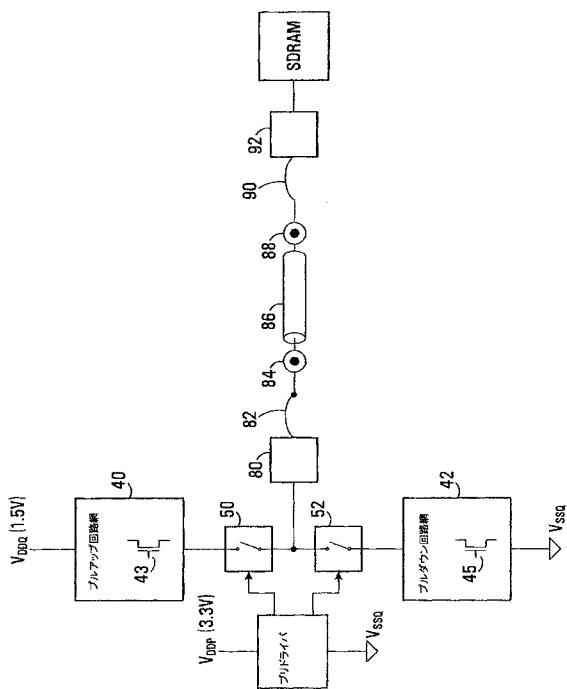

図2Aを参照すると、結合型OC'D／OD'Tの簡易ブロック図が示される。図示のように、可変抵抗プルアップ回路網40は、可変抵抗プルダウン回路網42にそれぞれスイッチ50、52を介して結合されている。スイッチ50は、閉じられると、プルアップ回路網40をI/Oパッド46及びES'D構造(図示されない)に結合する。スイッチ50は、OD'T／OC'Dプルアップ回路網の全体に動的なオン／オフ制御を提供する入力41を有する。スイッチ52は、閉じられると、プルダウン回路網42をI/Oパッド46及びES'D構造に結合する。同様に、スイッチ52は、OD'T／OC'Dプルダウン回路網の全体に動的なオン／オフ制御を提供する入力43を有する。

【0044】

制御41は、OD'T及びOC'D機能のそれぞれに対してプルアップ回路網を高速でオン及びオフに切り替えることを可能にする。同様に、制御43は、OD'T及びOC'D機能のそれぞれに対してプルダウン回路網を高速でオン及びオフに切り替えることを可能にする。第1及び第2のオン／オフ制御41、43は、出力を生成するか又は入力を受信するために、プルアップ及びプルダウン抵抗回路網をオン又はオフに動的に切り替える。

【0045】

通常、パッド46は、PCBトレースを介してSDRAMのようなメモリ素子(図示されない)に結合される。プルアップ回路網40は、OD'T及びOC'Dのそれぞれに対してインピーダンス制御入力を提供する制御入力48を有する。プルダウン回路網42は、OD'T及びOC'Dのそれぞれに対してインピーダンス制御を提供する制御入力53を有する。入力バッファ51も示される。入力バッファは、パッド46からの信号を受信し、該信号をコア(図示されない)へ受信回路(図示されない)を介して転送するよう結合される。

10

20

30

40

50

## 【0046】

可変抵抗回路網40、42の両者は、主として、可変抵抗を有するトランジスタ回路網である。幾つかの実施例では、これらの可変抵抗回路網は、回路の入り及び切りを切り替えてそれにより該回路のオン状態の抵抗値を変化させうるトランジスタのセットを有する。回路網のオフ状態の抵抗値は、実質的に、漏れ電流のみを示す開回路の抵抗値である。幾つかの実施例では、第1及び第2の抵抗制御(48、53)は準静的制御である。準静的制御では、特定の較正された抵抗値に設定されると、抵抗回路網の動作条件が抵抗値を有意に変化させない限り、再び状態を変更する必要がない。再較正の状態で、抵抗制御の状態は変化し、異なる動作条件に対して所望の抵抗値を達成しうる。

## 【0047】

10

ODTモードで動作するために、第1及び第2のオン/オフ制御41、43は、プルアップ回路網40及びプルダウン回路網42をそれぞれオンに切り替える。更に、インピーダンス制御入力48、53は、プルアップ回路網40及びプルダウン回路網42の抵抗値を終端のために較正された値に設定するために用いられる。受信した信号は、パッド46を介して入力され、入力バッファ51を通過し、回路の残りの部分(図示されない)へ渡される。プルアップ回路網内及びプルダウン回路網内の両方のトランジスタを同時にオンに切り替えることにより、出力ドライバは、分割終端抵抗回路網のインピーダンス動作を生成するために用いられる。換言すると、制御部の出力トランジスタは、入力信号を終端するために用いられる。

## 【0048】

20

OCDモードで動作するために、論理ハイ(High)が出力されるべきとき、制御入力41、43は、プルアップ回路網40をオンに切り替え、プルダウン回路網42をオフに切り替える。更に、インピーダンス制御48はプルアップ回路網40の抵抗値をプルアップ回路網を駆動するために較正された値に設定するために用いられる。論理ロー(Low)が出力されるべきとき、制御入力41、43は、プルダウン回路網42をオンに切り替え、プルアップ回路網40をオフに切り替える。更に、インピーダンス制御入力53はプルダウン回路網40の抵抗値をプルダウン回路網を駆動するために較正された値に設定するために用いられる。留意すべき点は、OCD及びODT機能は相互に排他的であることである。

## 【0049】

30

クワッド・データ・レート(QDR)SRAM(静的ランダム・アクセス・メモリ)は、独立した入力及び出力パッドを有する種類のSRAMである。共通I/Oセル設計の別個の存在は入力及び出力の両方に用いられ、それにより設計を単純にできるので、統合型ODT/OCDはこれらの素子を結合するために更に適用されうる。本例では、所与の結合型OCD/ODTの存在は、恒久的にODT又はOCDの一方になるよう設計される。

## 【0050】

図2Bは、図1と同様の統合型ODT/OCD機能がクワッド・データ・レート(QDR)SRAM制御部のために用いられ、QDR SRAMと電気経路を通じて通信する特定の例を示す。図示した例では、電気経路は、制御部からSRAMまでに、制御部のチップ・ボンドパッド80、制御部のパッケージ・リード82、ボール84、回路基板トレース86、別のボール88、SRAMのパッケージ・リード90及びSRAMのチップ・ボンドパッド92を有する。図は原寸に比例していない。原寸では、通常、回路基板トレース86は電気経路の全ての他の要素よりもかなり長い。電気経路は、完全な総合接続ノードとして動作しない。従って幾らかの寄生抵抗、インダクタンス及びキャパシタンスが、高速信号に深刻な伝送線の影響を与えうる該電気経路に関連付けられる。留意すべき点は、追加の受信回路(例えば、受信バッファ等)は図示されないが、少なくともODTに用いられている回路の存在のために存在している。

## 【0051】

出力インピーダンスは、オンに切り替えられているQDR出力ドライバ内のトランジスタの数に関して逆に変化する。図2Bに戻ると、概して、プルアップ回路網40内に少な

40

50

くとも幾つかの（例えば 16）N MOS トランジスタ 43 が存在し、プルダウン回路網 42 内にも同数の N MOS トランジスタ 45 が存在する。幾つかの実施例では、キャリブレーションを目的として、プルアップ回路網 40 のみがオンに切り替えられればよい。何故なら、回路網 A 内及び B 内の両方のトランジスタは、同一種類（本例では N MOS）であり、キャリブレーション電圧（ $V_o = V_{DDQ} / 2$ ）で同一のプルアップ及びプルダウンインピーダンスを提供するような大きさに設計されているからである。

#### 【0052】

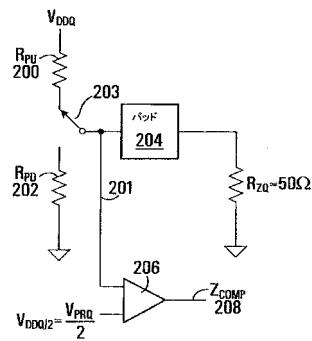

図 2C を参照すると、同一種類のトランジスタにより形成されるプルアップ回路網及びプルダウン回路網を有する回路内でどのようにキャリブレーションが実行されるかの例であるモデルが示される。I/O セルの複製がキャリブレーションの目的に用いられる。プルアップ回路網は  $R_{PU} 200$  として示され、プルダウン回路網は  $R_{PD} 202$  として示される。切り替えは、 $R_{PU}$  が常に接続され、 $R_{PD}$  が常に切断されるようにされる。これは、単一のスイッチ 203 として示されるが、図 2A のスイッチ 50、52 と等価な 1 対のスイッチを用いて及び / 又は可変抵抗プルアップ回路網及びプルダウン回路網を実施するトランジスタを用いて、開かれている図 2A のスイッチ 50 及び閉じられているスイッチ 52 と等価に  $R_{PU}$  を接続して、実施されてもよい。複製回路は、パッド 204 を通じて、図示された例では 50 である基準抵抗  $R_{ZQ}$  に結合される。複製回路の出力 201 は、アナログ比較器 206 の 1 つの入力にも結合される。アナログ比較器 206 は、図示された例では  $V_{DDQ} / 2$  に設定された基準電圧に結合された第 2 の入力を有する。アナログ比較器 206 の出力  $Z_{COMP} 208$  は、回路の出力 201 が基準電圧よりも低いときローであり、回路の出力 201 が基準電圧よりも高いときハイである。出力  $Z_{COMP} 208$  は、出力  $V_o 201$  が基準電圧と等しいとき不定である。出力インピーダンスを較正するために、 $R_{PU} 200$  は、（回路構成を変化させることにより、例えば抵抗値に貢献するトランジスタの数を変化させることにより） $Z_{COMP} 208$  が「0」から「1」に切り替わるまで変化される。この変化が生じると、出力電圧は基準電圧を超え、回路構成は実際の I/O セルの出力インピーダンスの設定に使用されると判明する。留意すべき点は、出力  $V_o 201$  が  $V_{DDQ} / 2$  に非常に近いとき、同一の電流を有する各抵抗の両端の電圧が等しいので、プルアップ抵抗の値は較正抵抗  $R_{ZQ}$  の値に非常に近いことである。

#### 【0053】

幾つかの実施例では、アナログ比較器 206 は、DDR 入力バッファを用いて実施される。このようなバッファは、精度や利得よりも速度のために設計された特殊なアナログ比較器である。このようなアナログ比較器の出力は、デジタルであり、該アナログ比較器の複数のアナログ入力の相対値に依存して、ある論理レベルから別の論理レベルへ急に切り替わるように設計される。

#### 【0054】

例えば、出力インピーダンスを較正し、図 2C に示された 50 の抵抗に整合するようにするために、オンに切り替えられたトランジスタの数は、基準駆動プルアップ回路網のプルアップ・トランジスタのゲートに印加される選択 / イネーブル信号を変化させることにより、出力  $V_o 201$  が  $V_{DDQ} / 2$  より大きいが可能な限り近くなるまで、徐々に変化されうる。QDR 出力ドライバの適正な較正はこの設定になり、基準 QDR 出力ドライバが設定されると、出力ドライバのトランジスタの正しい数（X）は、較正基準ドライバの設定を共有する全ての QDR ドライバ内で、通常動作中はオンに切り替えられる。例えば、プルアップ回路網内の  $X = 16$  個のトランジスタが伝送線がハイに駆動されるときオンに切り替えられ、プルダウン回路網内の  $X = 16$  個のトランジスタが伝送線がローに駆動されているときオフに切り替えられる。

#### 【0055】

図 2B のプルアップ回路網及びプルダウン回路網は、両方とも n 型トランジスタを有する。これは、QDR 用途に特に適する。以上に詳細に説明したように、これは、簡単な較正を実行することを可能にする。より詳細には、同一種類のトランジスタで形成されたブ

10

20

30

40

50

ルアッパ回路網及びプルダウン回路網を特徴とする如何なる実装においても、較正値はプルアッパ回路網及びプルダウン回路網に対して同一なので、プルアッパ及びプルダウン回路網の一方又は他方のみしか、ODT及びOCDのそれぞれについて較正される必要がない。

#### 【0056】

図2A及び2Bの例では、プルアッパ回路網は該プルアッパ回路網をイネーブルする切り替え素子から分離して示され、プルダウン回路網は該プルダウン回路網をイネーブルする切り替え素子から分離して示される。しかしながら、幾つかの実施例では、切り替え機能は、プルアッパ及びプルダウン回路網の一部を形成するトランジスタにより実施される。

10

#### 【0057】

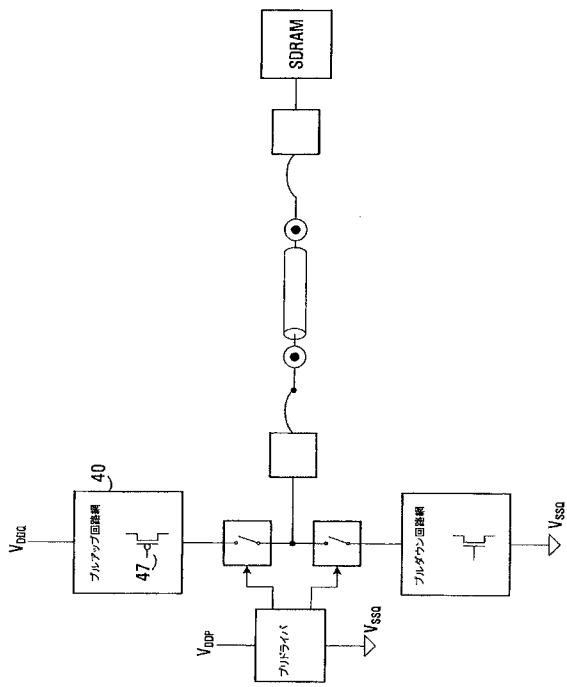

図2DはDDR3制御部のための出力ドライバの例を示す。DDR3出力ドライバは、図2Bに示されたQDR制御部出力ドライバに多少似ているが、プルアッパ回路網40がNMOSトランジスタではなくPMOSトランジスタ47を有する。このため、PMOS及びNMOSトランジスタが異なる抵抗特性を有しうるので、プルアッパ回路網及びプルダウン回路網の較正を別個に実行しなければならない。また、ODTモード動作のために受信バッファ(図示されない)もある。DDR3では、各I/Oは、入力及び出力モードの両方で相互排他的な時間の間に動作する。

#### 【0058】

プルアッパ回路網内及びプルダウン回路網内の両方のトランジスタを同時にオンに切り替えることにより、DDR3出力ドライバは、分割終端抵抗回路網のインピーダンス動作を生成するために用いられる。換言すると、DDR3制御部の出力トランジスタは、入力信号を終端するために用いられる。

20

#### 【0059】

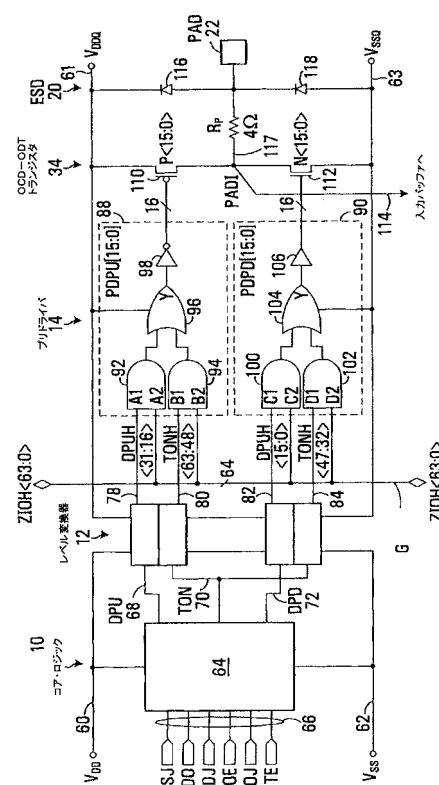

図3を参照して、図1のセル構造32と合致するI/Oセル構造の詳細な実施が以下に説明される。以下に記載されるように、図3の回路は、試験を目的とするテスト入力及び通常の入力を有するとして示される。理解されるべき点は、テスト入力及び対応する回路が該回路の通常動作に影響を与えることなく省略されうことである。図1と共に要素は同様の参照符号を有する。特に、回路は、コア・ロジック10、レベル変換器12、プリドライバ14、プルアッパp型トランジスタP<15:0>110及びプルダウンn型トランジスタN<15:0>112を有する結合型OCD/ODTトランジスタ34、ESDクランプ・ダイオード116及びESDクランプ・ダイオード118を有するESD20並びにパッド120を有するとして示される。本例では、プリドライバ14は、16個のプルアッパ・トランジスタ110を駆動する16個のプリドライバ88及び16個のプルダウン・トランジスタ112を駆動するプリドライバ90を有すると仮定するが、この数は実装時固有である。

30

#### 【0060】

プルアッパ・トランジスタ110は、PAD内部ネット(PADI)と付された点でプルダウン・トランジスタ112に結合される。また、PADIをパッド22に結合する抵抗R<sub>p</sub>117も示される。抵抗R<sub>p</sub>は、出力トランジスタを拡散ESD効果から保護するために用いられる広いレイアウト面積の拡散抵抗である。抵抗は、出力トランジスタへのESD電流を制限する。該ESD電流は、大きすぎると、トランジスタのスナップ・バックを生じ、トランジスタを損傷しうる。このトランジスタを配置することにより、スナップ・バックの発生を防ぐ。抵抗R<sub>p</sub>はPAD-ESD構造20の一部である。PADIは、入力バッファ(図示されない)にも114で結合される。

40

#### 【0061】

回路は、V<sub>DD60</sub>、V<sub>SS62</sub>、V<sub>DDQ61</sub>及びV<sub>SSQ63</sub>のための結合部を有する。これらはI/Oセルの電源線端子である。電源線は、シリコン・チップの周辺に沿って配置されたI/Oセルに電力を分配するために用いられる金属バスである。V<sub>DDQ</sub>は、例えば公称でDDR1では2.5V、DDR2では1.8V及びDDR3では1.5

50

$V$  に設定される I/O 電源に結合される。 $V_{SSQ}$  は、 $V_{DDQ}$  電源の I/O 接地帰路である。 $V_{DD}$  端子は、現代の深サブミクロン技術では、通常、1.0 乃至 1.2 ボルトの範囲内の電圧に設定されるコア電源に結合される。 $V_{SS}$  は、 $V_{DD}$  電源のコア接地帰路である。両方とも公称 0.0 ボルトであるが、 $V_{SSQ}$  及び  $V_{SS}$  は別個のオンダイ接地網である。2つの接地は、コアを I/O 切り替え雑音から絶縁するために分離される。

#### 【0062】

コア・ロジック 10 は、SJ、DO、DJ、OE、OJ、TE を有する入力 66 を受信する回路 64 を有する。これらの入力の機能は以下の通りである。

#### 【0063】

SJ は、ローのとき通常の入力 (DO 及び OE) を選択し、ハイのときテスト入力 (DJ 及び OJ) を選択する。

#### 【0064】

DO は、 $OE = 1$  のときパッドへの通常のデータ出力である。パッドは  $DO = 1$  のときハイであり、パッドは  $DO = 0$  のときローである。

#### 【0065】

DJ は、 $OJ = 1$  のときパッドへのテスト・データ出力である。パッドは  $DJ = 1$  のときハイであり、パッドは  $DJ = 0$  のときローである。

#### 【0066】

OE は、通常の出力イネーブルである。 $OE = 1$  のとき、オフチップ駆動 (OCD) はイネーブルされ、オンダイ終端 (ODT) はディスエーブルされる。 $OE = 0$  のとき、OCD はディスエーブルされ (トリステート)、ODT は  $TE = 1$  ならばイネーブルされる。

#### 【0067】

OJ は、テスト出力イネーブルであり、OE と同一の機能を有する。

#### 【0068】

TE は、終端イネーブルである。これは、パッド・ドライバ・トランジスタを分割終端として動作させる。 $TE = 1$  のとき、終端は、OCD がトリステート (OE (又は OJ) = 1) のときオンに切り替わる。これは、通常、駆動のみの用途ではローであり、データ I/O 用途ではハイである。

#### 【0069】

コア・ロジック 64 の出力は、以下のように動作する DPU68、TON70 及び DPD72 を有する。

#### 【0070】

DPU は駆動プルアップ制御である。これがハイのとき、駆動プルアップ・トランジスタがオンに切り替えられる。ローのとき、駆動プルアップ・トランジスタはオフに切り替えられる。DPD は駆動プルダウン制御である。これがハイのとき、駆動プルダウン・トランジスタがオンに切り替えられる。ローのとき、駆動プルダウン・トランジスタはオフに切り替えられる。

#### 【0071】

TON は終端オン制御である。ハイのとき、プルアップ及びプルダウン・トランジスタの両方がイネーブルされ、一緒にオンに切り替えられ、OE 又は OJ がローになるとき分割終端を形成する。ローのとき、終端機能は完全にディスエーブルされ、OE 又は OJ の状態により影響されない。

#### 【0072】

3つの出力 DPU68、TON70 及び DPD72 は、レベル変換器 12 への入力である。レベル変換器 12 は、I/O プリドライバ 88、90 を駆動するために用いられる DPU68、TON70 及び DPD72 を高電位にしたものである DPUH78、TONH80、DPDH82 及び TONH84 を有する。

#### 【0073】

64 ビットのインピーダンス制御バスがあり、プルアップ・トランジスタ 110 及びブ

10

20

30

40

50

ルダウン・トランジスタ 112 を制御するために用いられる ZIOH < 63 : 0 > として参照される。インピーダンス制御バス ZIOH は、どのように図 2 A のインピーダンス制御入力が実施されうるかの特定の例である。各プリドライバは、以下に詳細に説明するように、インピーダンス制御バスの特定のビット並びにレベル変換された出力 DPUH78 、 TONH80 、 DPDH82 及び TONH84 の特定のビットを受信する。 ZIOH < 63 : 0 > は以下を有する。

【 0074 】

OCD モードでプルアップ・トランジスタ 110 を制御し、トランジスタ毎に 1 ビットを有する 16 ビットの ZIOH < 31 : 16 > 。

【 0075 】

ODT モードでプルアップ・トランジスタ 110 を制御し、トランジスタ毎に 1 ビットを有する 16 ビットの ZIOH < 63 : 48 > 。

【 0076 】

OCD モードでプルダウン・トランジスタ 112 を制御し、トランジスタ毎に 1 ビットを有する 16 ビットの ZIOH < 15 : 0 > 。 ODT モードでプルダウン・トランジスタ 112 を制御し、トランジスタ毎に 1 ビットを有する 16 ビットの ZIOH < 47 : 32 > 。

【 0077 】

各プリドライバ 88 は、 AND ゲート 92 及び AND ゲート 94 を有する。 AND ゲート 92 、 94 は、 OR ゲート 96 に結合される出力をそれぞれ有する。 OR ゲート 96 は、対応する反転バッファ 98 を通る出力を有する。反転バッファ 98 の出力は、複数のプルアップ・トランジスタ 110 のうちの 1 つのゲートを駆動する。 AND ゲート 92 は、 DPUH78 (A1) 及び ZIOH < 31 : 16 > の複数のビットのうちの 1 つ (A2) を受信する。 AND ゲート 94 は、 TONH80 (B1) 及び ZIOH < 63 : 48 > の複数のビットのうちの 1 つ (B2) を受信する。

【 0078 】

同様に、各プリドライバ 90 は、 AND ゲート 100 及び AND ゲート 102 を有する。 AND ゲート 100 、 102 は、 OR ゲート 104 に結合される出力をそれぞれ有する。 OR ゲート 104 は、対応する非反転バッファ 106 を通る出力を有する。非反転バッファ 106 の出力は、複数のプルアップ・トランジスタ 120 のうちの 1 つのゲートを駆動する。 AND ゲート 100 は、 DPDH82 (C1) 及び ZIOH < 15 : 0 > の複数のビットのうちの 1 つ (C2) を受信する。 AND ゲート 102 は、 TONH84 (D1) 及び ZIOH < 47 : 32 > の複数のビットのうちの 1 つ (D2) を受信する。

【 0079 】

AND - OR - AND ロジックは、プリドライバ 88 、 90 内に組み込まれ、駆動及び終端インピーダンスの独立した制御のために高速マルチプレクサとして動作する。 AND - OR - AND ロジックは、駆動するとき任意の数のプルアップ及びプルダウン・トランジスタをオン及びオフに交互に切り替え、終端するとき任意の数のプルアップ及びプルダウン・トランジスタをオン及びオフに一緒に切り替えることを可能にする。プリドライバ・ロジックは、 ZIOH < 63 : 0 > により選択されていない全ての OCD / ODT トランジスタ 34 をオフに切り替え、それらが切り替わるのを防ぐ。選択された OCD / ODT トランジスタのみが高速で切り替わる。

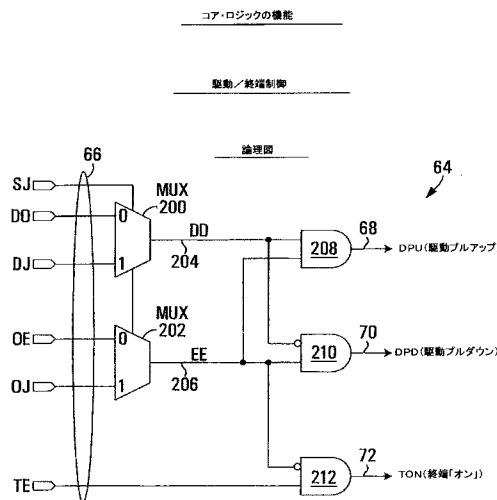

【 0080 】

図 4 A に、図 3 の回路 64 の実施の詳細な例が示される。図 3 のように、入力 68 ( SJ 、 DO 、 DJ 、 OE 、 OJ 、 TE を有する) 及び出力 DPU68 、 DPDU70 及び TON72 がある。 DO 及び DJ は、出力 DD204 を生成する第 1 のマルチプレクサ 200 への入力である。 OE 及び OJ は、出力 EEE206 を生成する第 2 のマルチプレクサ 202 への入力である。 DD204 は、 AND ゲート 208 の第 1 の入力及び AND ゲート 210 の反転入力に結合される。 AND ゲート 208 の出力は DPU68 である。 EEE206 は、 AND ゲート 208 の第 2 の入力及び AND ゲート 210 の第 2 の入力に結合され

10

20

30

40

50

る。ANDゲート210の出力はD P D 7 0である。EE206は、ANDゲート212の第1の反転入力にも結合される。TEは、ANDゲート212の第2の入力に結合される。ANDゲート212の出力はT O N 7 2である。

#### 【0081】

概して、図4Bの214に示されるように、回路64の真理値表は、どのようにD P U、D P D及びT O NがS J、D O、D J、O E、O J及びT Eに応じて生成されるかを示す。

#### 【0082】

プリドライバ88、90は、レベル変換されたD P U H、T O N H、T P D Hに応じて動作する。通常動作(S J = 0)は、類似するテスト動作と対立するものとして説明される。

10

#### 【0083】

##### <O C Dモード>

O C Dモード動作では、O Eはハイになり出力をイネーブルする。T Eの状態は、O Eがハイである限り関係ない。D Oは、生成されるべき出力を反映して如何なる瞬間も0又は1になる。D Oが1のとき(行216、217)、複数のプルアップ・トランジスタ110のうちの対応する1つは、Z I O H < 31 : 16 >の各「1」に対してプリドライバ88によりオンに切り替えられる。同様に、D Oが0のとき(行218、219)、複数のプルダウン・トランジスタ112のうちの対応する1つは、Z I O H < 15 : 0 >の各「1」に対してオフに切り替えられる。

20

#### 【0084】

##### <O D Tモード>

アクティベートされているO D Tモードを生じさせる唯一の入力の組は次の通りである。O Eがローになり出力をディスエーブルし、T E = 1になりO D Tをイネーブルする(T O N = 1)。これは、真理値表214の行220である。T O Nが1なら、複数のプルアップ・トランジスタ110のうちの対応する1つは、プリドライバ88によりZ I O H < 63 : 48 >の各「1」に対してオフに切り替えられ、複数のプルダウン・トランジスタ112のうちの対応する1つは、Z I O H < 47 : 32 >の各「1」に対してオフに切り替えられる。

30

#### 【0085】

##### <較正>

幾つかの実施例では、較正機構は、O D T及びO C Dモードに用いられるべき適切なトランジスタ数を識別するために、特に何個のプルアップ及び/又はプルダウン・トランジスタがこれらのモードのそれぞれでオフに切り替えられるべきかを識別するために提供される。幾つかの実施例では、較正は、装置の動作中に、周期的に、動的に実行され、変化する動作条件下での調整を可能にする。

#### 【0086】

幾つかの実施例では、4段階の較正が次の通り実行される。

(1) n型素子の出力インピーダンスの較正：これは、D Oが0のとき、何個のn型トランジスタ112がO C Dモード中にイネーブルされるべきかを決定する。

40

(2) p型素子の出力インピーダンスの較正：これは、D Oが1のとき、何個のp型トランジスタ110がO C Dモード中にイネーブルされるべきかを決定する。

(3) n型素子の終端の較正：これは、何個のn型トランジスタ112がO D T中にイネーブルされるべきかを決定する。

(4) p型素子の終端の較正：これは、何個のp型トランジスタ110がO D T中にイネーブルされるべきかを決定する。

#### 【0087】

より一般的には、プルアップ回路網の較正及びプルダウン回路網の較正は、同様の方法で実行されうる。説明された回路は、大部分は、ピン毎に複製される。しかしながら、幾つかの実施例では、較正はピン毎に実行されない。むしろ、較正は1回実行され、同一の

50

較正結果が全てのピンに適用されうることが期待される。この期待は、複数のピンの結合型O C D / O D Tに用いられているトランジスタが、同一の集積回路の部分であり、従つて同様の特性を有する場合に妥当である。幾つかの実施例では、結合型O C D / O D Tの複製は、全てのI / Oの較正を目的として用いられる。

【0088】

結合型O C D / O D T内に含まれるトランジスタの数は、プログラム可能な所望の範囲に応じて及びトランジスタの抵抗 / 駆動特性に応じて選択されうる。幾つかの実施例では、トランジスタのセットが用いられ、30乃至90の範囲のプログラム可能な範囲を提供するが、これは勿論、実装時固有である。

【0089】

幾つかの実施例では、制御部はグレイコードを用いて抵抗値を符号化し、温度計コード出力に変換される。温度計コードの各コードワードは、単一の0のセット又は複数の1に続く単一の0のセット又はコードワードを満たす複数の0を有する。このような温度計コードの使用は、連続するトランジスタのセット（プルアップ又はプルダウン）がイネーブルされるのを保証する。特定の例では、4ビット・コードが用いられ、16個の可能な順列の1つを示す。該順列の1つは、トランジスタ毎に1ビットを有する16ビットの温度計コードに変換される。インピーダンス・コード（ZIOH<63:0>）が変化している間にドライバ出力が生じるという誤動作を防ぐために、2進から温度計への方式ではなくグレイから温度計への復号化方式が用いられる。

【0090】

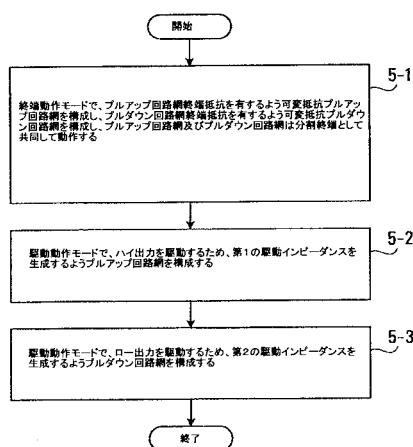

示された例は全て結合型O C D / O D T回路に関する。より一般的には、結合型駆動及び終端を提供する回路が提供される。図5は、結合型の駆動及び終端を提供する方法のフローチャートである。当該方法は、段階501で開始する。段階5-1では、終端動作モードで、プルアップ回路網終端抵抗を有するように可変抵抗プルアップ回路網を設定し、プルダウン回路網終端抵抗を有するよう可変抵抗プルダウン回路網を設定し、プルアップ回路網及びプルダウン回路網は分割終端として共同して動作する。段階5-2では、駆動動作モードで、ハイ出力を駆動するために、第1の駆動インピーダンスを生成するようにプルアップ回路網を設定する。段階5-3では、駆動動作モードで、ロー出力を駆動するために、第2の駆動インピーダンスを生成するようにプルダウン回路網を設定する。図5の段階を実行する順序は、明らかに駆動と終端の順序及び駆動モード中に駆動されているデータの両方に依存する。

【0091】

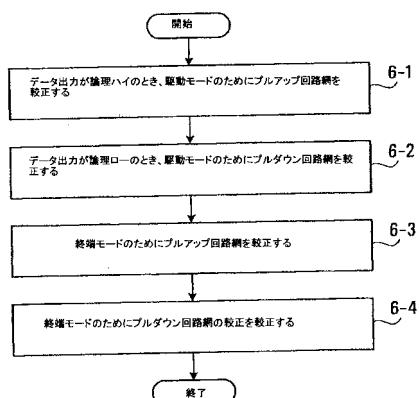

図6は、図5の方法を較正する第1の方法のフローチャートである。当該方法は段階6-1で開始する。段階6-1では、データ出力が論理ハイのとき、駆動モードのためにプルアップ回路網を較正する。当該方法は段階6-2へ続く。段階6-2では、データ出力が論理ローのとき、駆動モードのためにプルダウン回路網を較正する。当該方法は段階6-3へ続く。段階6-3では、終端モードのためにプルアップ回路網を較正する。当該方法は段階6-4へ続く。段階6-4では、終端モードのためにプルダウン回路網を較正する。

【0092】

図7は、図5の方法を較正する第2の方法のフローチャートである。当該方法は段階7-1で開始する。段階7-1では、データ出力が論理ハイのとき、駆動モードのためにプルアップ回路網を較正し、第1の較正結果を生成する。当該方法は段階7-2へ続く。段階7-2では、データ出力が論理ローのとき、第1の較正結果を用い駆動モードのためにプルダウン回路網を較正する。これは、プルダウン回路網及びプルアップ回路網に用いられるトランジスタが同一のプロセスを用いて形成され、当然に同一の較正が両トランジスタに用いられうることを前提とする。当該方法は段階7-3へ続く。段階7-3では、終端モードのためにプルアップ回路網を較正し、第2の較正結果を生成する。当該方法は段階7-4へ続く。段階7-4では、第2の較正結果を用い終端モードのためにプルダウン回路網を較正する。

10

20

30

40

50

## 【0093】

記載した実施例は、可変抵抗プルアップ回路網、可変抵抗プルダウン回路網、終端抵抗及び基準抵抗を参照した。より一般的には、実施例は、可変インピーダンス・プルアップ回路網、可変インピーダンス・プルダウン回路網、終端インピーダンス及び基準インピーダンスを用いてもよい。

## 【0094】

上述の教示を踏まえ本発明の多くの変更及び変形が可能である。従って、本発明は、本願明細書に特に記載された以外にも、特許請求の範囲内で実施されうることが理解されるべきである。

## 【0095】

本出願は2007年6月8日出願の米国特許仮出願番号60/942,798号に基づく優先権を主張するものであり、米国特許出願番号60/942,798号の全内容を本出願に援用する。

10

【図1】

【図2B】

【図2C】

【図2D】

【図3】

【図4A】

【図4B】

真理値表

214

| S.J | 入力  |     |     |       |     | 出力    |       |       | PADにおける効果                         | モード       |

|-----|-----|-----|-----|-------|-----|-------|-------|-------|-----------------------------------|-----------|

|     | D.O | D.J | D.E | D.O.J | T.E | D.P.U | D.P.D | T.O.N |                                   |           |

| 0   | X   | X   | 0   | X     | 0   | 0     | 0     | 0     | フローティング<br>駆動: L(ロー)<br>駆動: H(ハイ) | 通常の<br>高速 |

|     | 0   | X   | 1   | X     | 0   | 0     | 1     | 0     |                                   |           |

|     | 1   | X   | 1   | X     | 0   | 1     | 0     | 0     | 終端「オン」<br>駆動: L(ロー)<br>駆動: H(ハイ)  |           |

| 1   | X   | X   | 0   | X     | 1   | 0     | 0     | 1     | フローティング<br>駆動: L(ロー)<br>駆動: H(ハイ) | 試験        |

|     | X   | 0   | X   | 1     | X   | 0     | 0     | 1     |                                   |           |

|     | 1   | X   | 1   | X     | 1   | 1     | 0     | 0     | 終端「オン」<br>駆動: L(ロー)<br>駆動: H(ハイ)  |           |

論理状態 X, 0, 1:

X—D.D.N. (D.C.R.E.) 入力, 不定出力

0—値: ロー (Low); ポーラ化作用

1—真: ハイ (High); アサート作用

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 ミラー, ブルース

カナダ国 ケイ2エス 1ビ-6 オンタリオ, スティックヴィル, フーンバンク・ロード 6

066

審査官 宮島 郁美

(56)参考文献 特開2005-130217 (JP, A)

特開2003-133943 (JP, A)

特開2005-065249 (JP, A)

米国特許出願公開第2007/0126466 (US, A1)

米国特許出願公開第2006/0226868 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H03K19/00, 19/01-19/082, 19/092-19/096