(12) 特許協力条約に基づいて公開された国際出願

(19) 世界知的所有権機関

国際事務局

(43) 国際公開日

2015年12月23日 (23.12.2015)

W I P O | P C T

(10) 国際公開番号

WO 2015/194128 A1

(51) 国際特許分類 :

|                       |                      |

|-----------------------|----------------------|

| G09F 9/00 (2006.01)   | H05B 33/10 (2006.01) |

| G09F 9/30 (2006.01)   | H05B 33/14 (2006.01) |

| H01L 21/768 (2006.01) | H05B 33/22 (2006.01) |

| H01L 51/50 (2006.01)  | H05B 33/26 (2006.01) |

| H05B 33/04 (2006.01)  |                      |

53 10072 大阪府大阪市北区豊崎三丁目2番1号

淀川5番館6F Osaka (JP).

(81) 指定国(表示のない限り、全ての種類の国内保護が可<sup>能</sup>): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) 国際出願番号 :

PCT/JP20 15/002895

(22) 国際出願日 :

2015年6月10日 (10.06.2015)

(25) 国際出願の言語 :

日本語

(26) 国際公開の言語 :

日本語

(30) 優先権データ :

特願 2014-126381 2014年6月19日 (19.06.2014) JP

(84)

(71) 出願人 株式会社 JOLED (JOLED INC.) [JP/JP];

〒1010054 東京都千代田区神田錦町三丁目23

番地 Tokyo (JP).

(72) 発明者 阿部 裕樹 (ABE, Ymiki).

(74) 代理人 :特許業務法人 ナカジマ知的財産総合

事務所 (NAKAJIMA & ASSOCIATES IP FIRM); 〒

(81) 指定国(表示のない限り、全ての種類の広域保護が可<sup>能</sup>): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), ユーラシア (AM, AZ, BY, KG, KZ, RU, TJ, TM), ヨーロッパ (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

[続葉有]

(54) Title: METHOD FOR MANUFACTURING ACTIVE-MATRIX DISPLAY PANEL, AND ACTIVE-MATRIX DISPLAY

(54) 発明の名称 :アクティブマトリクス型表示パネルの製造方法とアクティブマトリクス型表示パネル

(57) Abstract: A manufacturing method according to one embodiment comprises sequentially forming a thin-film transistor (TFT) layer, a planarization layer (110), and a display element part on a substrate. In forming the TFT layer, an upper electrode (108) is covered, and a passivation layer (109) is formed so as to adjoin the planarization layer. In forming the display element part, a lower electrode is formed so as to adjoin the planarization layer. In connecting the upper electrode of the TFT layer and the lower electrode of the display element part, a contact hole (110a) is first opened in the planarization layer until the passivation layer is exposed at the bottom. Dry etching using a fluorine-containing gas is subsequently applied to the passivation layer exposed at the bottom of the contact hole, whereby a contact hole (109a) in which the upper electrode is exposed at the bottom is opened. A liquid-repellent film (121) that contains fluorine in the composition thereof is formed on the inner wall surface that faces the contact hole in the passivation layer. The lower electrode is then formed along the inner wall surface of the passivation layer and the planarization layer that faces the contact hole.

(57) 要約:

[続葉有]

## 添付公開書類：

— 国際調査報告 (条約第 21 条(3))

---

一様に係る製造方法は、基板上に TFT 層、平坦化層 (110)、表示素子部を順に形成する。TFT 層の形成では、上部電極 (108) を被覆し、平坦化層と境界を接する状態で、パッシベーション層 (109) を形成する。表示素子部の形成では、平坦化層と境界を接する状態で下部電極を形成する。TFT 層の上部電極と表示素子部の下部電極との接続では、先ず、底にパッシベーション層が露出するまで、平坦化層にコンタクト孔 (110a) を開設する。次に、コンタクト孔の底に露出するパッシベーション層に対して、フッ素を含むガスを用いたドライエッチングにより、底に上部電極が露出するコンタクト孔 (109a) を開設する。その後、パッシベーション層におけるコンタクト孔を臨む内壁面に対し、組成中にフッ素を含む撥液膜 (121) を形成する。そして、コンタクト孔を臨む平坦化層およびパッシベーション層の内壁面に沿って、下部電極を形成する。

## 明 細 書

### 発明の名称 :

アクティブマトリクス型表示パネルの製造方法とアクティブマトリクス型表示パネル

### 技術分野

[0001] 本発明は、アクティブマトリクス型表示パネルの製造方法とアクティブマトリクス型表示パネルに関し、TFT層の電極と表示素子部の電極との間に介挿された2層の絶縁層に対し、電極間コンタクトのためのコンタクト孔形成に係る技術に関する。

### 背景技術

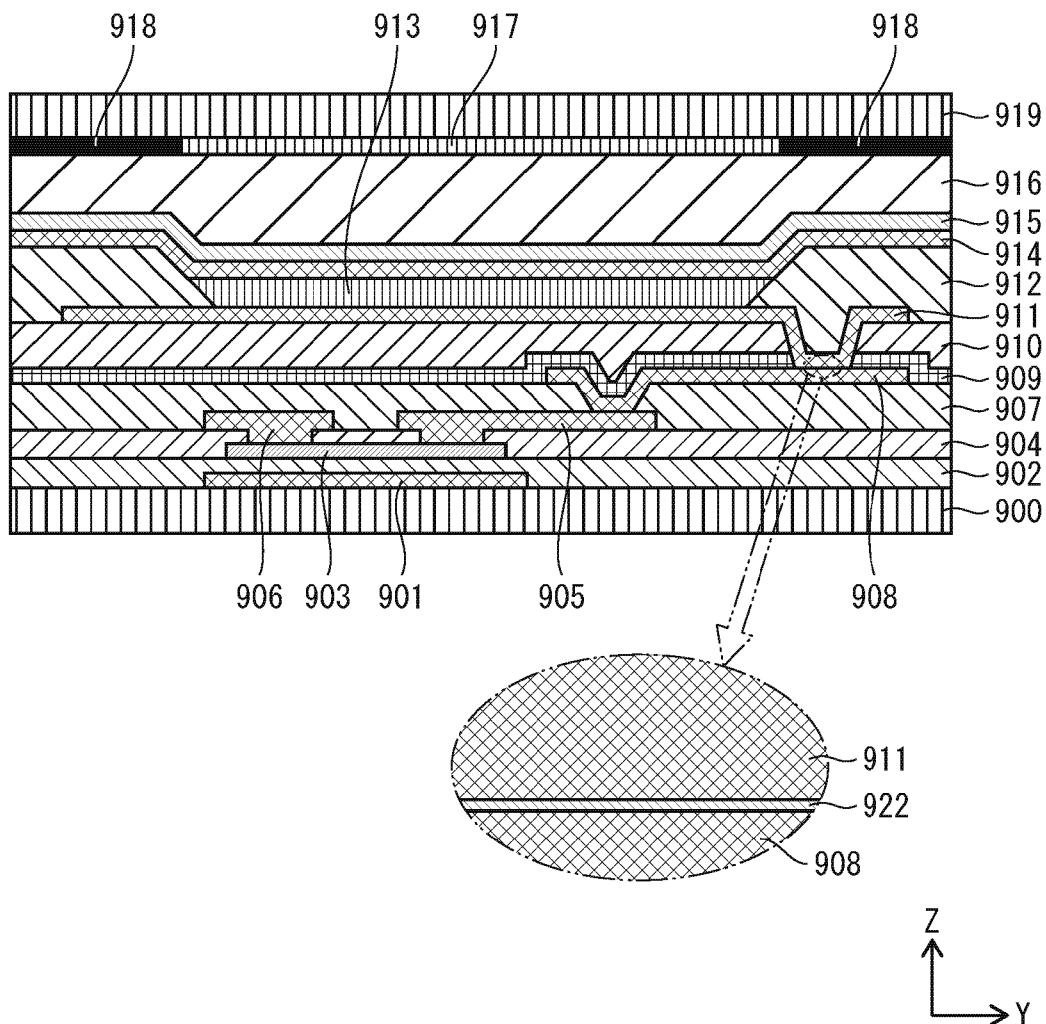

[0002] 現在において、液晶表示パネルが広く普及している。また、有機EL（Electro Luminescence）表示パネルの実用化に向けた開発が進められている。これらの表示パネルにおいては、各画素の駆動制御を、発光部の下方に形成されたTFT（Thin Film Transistor）により行う、アクティブマトリクス型が採用されることが多い（特許文献 2, 3）。一例として、図14を用い有機EL表示パネルの製造方法の概略について説明する。

[0003] 図14に示すように、基板900の上面にTFT層を形成する。TFT層は、基板900の側から、ゲート電極901、ゲート絶縁層902、チャネル層903、チャネル保護層904、ソース電極905およびドレイン電極906、層間絶縁層907、上部電極908、パッシベーション層909が順に形成された構成を有する。

[0004] 次に、TFT層におけるパッシベーション層909の上に、平坦化層910を挟んだ状態で、有機発光部（表示素子部）を形成する。有機発光部は、パッシベーション層909の側から、アノード911、バンク912、有機発光機能層913、カソード914、封止層915が順に形成された構成を有する。

[0005] 次に、有機発光部の上に、樹脂層916を挟んだ状態で、カラーフィルタ基板（C F 基板）を配置する。C F 基板は、基板919の下面に、カラーフィルタ層917とブラックマトリクス層918とが形成された構成を有する。

[0006] ここで、TFT層における上部電極908はソース電極905と接続されており、また、パッシベーション層909および平坦化層910に開設されたコンタクト孔を通してアノード911とも接続されている。コンタクト孔の開設は、リソグラフィにより平坦化層910にコンタクト孔を開設した後、コンタクト孔が開設された平坦化層910をマスクとして、ドライエッチングによりパッシベーション層909に連通するコンタクト孔を開設するという手順を以ってなされる。

## 先行技術文献

### 特許文献

[0007] 特許文献1：特開2004—363034号公報

特許文献2：特開2007\_95515号公報

特許文献3：特開2008\_198491号公報

### 発明の概要

### 発明が解決しようとする課題

[0008] しかしながら、図14の二点鎖線で囲んだ一部拡大部分に示すように、従来技術に係る製造方法を用い製造した表示パネルでは、コンタクト孔の底部において、TFT層における上部電極908とアノード911との間に、金属酸化膜922が形成されてしまうことがある。このように上部電極908とアノード911との間に金属酸化膜922が介挿されしまうと、上部電極908とアノード911との間の接続不良を生じ、表示パネルの表示品質が低下してしまう。

[0009] 本発明は、上記のような問題の解決を図ろうとなされたものであって、TFT層の電極と表示素子部の電極との間に介挿された2層の絶縁層に対しコ

ンタク ト孔を開設しながら、良好な電極間接続を図ることができるアクティブマトリクス型表示パネルの製造方法とアクティブマトリクス型表示パネルを提供することを目的とする。

### 課題を解決するための手段

- [001 0] 本発明の一態様に係るアクティブマトリクス型表示パネルの製造方法は、(i) 基板上にTFT層を形成する工程と、(ii) TFT層上に平坦化層を形成する工程と、(iii) 平坦化層上に表示素子部を形成する工程と、を備える。

- [001 1] (i) TFT層を形成する工程には、ソース電極もしくはドレイン電極、またはその一方の電極に接続された接続用電極の何れかの電極を被覆するパッシベーション層を、平坦化層と境界を接する状態で形成するサブ工程が含まれる。

- [001 2] (ii) 表示素子部を形成する工程には、平坦化層と境界を接する状態で下部電極を形成するサブ工程が含まれる。

- [001 3] 上記何れかの電極と下部電極との接続は、次の工程を経てなされる。

- [0014] (iv - 1) 底部にパッシベーション層が露出するまで、平坦化層にコンタクト孔を開設する。

- [001 5] (iv - 2) 平坦化層に開設したコンタクト孔の底部に露出するパッシベーション層に対して、フッ素を含むガスを用いたドライエッチングにより、平坦化層のコンタクト孔に連通し、底部に上記何れかの電極が露出するコンタクト孔を開設する。

- [001 6] (iv - 3) コンタクト孔の底に上記何れかの電極が露出した後、パッシベーション層におけるコンタクト孔を臨む内壁面に対し、組成中にフッ素を含む撥液膜を形成する。

- [001 7] そして、下部電極を形成するサブ工程において、コンタクト孔を臨む平坦化層およびパッシベーション層の内壁面に沿って、下部電極を形成する。

### 発明の効果

- [001 8] 上記態様に係る製造方法では、フッ素を含むガスでコンタクト孔を開設す

るので、上記 (iv\_2) のパッシベーション層へのコンタクト孔の開設後では、少なくとも平坦化層におけるコンタクト孔を臨む内壁面に、組成中にフッ素を含む撥液膜が形成される。このため、仮に平坦化層およびパッシベーション層のコンタクト孔内に水分が入った場合でも、撥液膜により、コンタクト孔を臨む内壁面および底に露出する上記何れかの電極の表面への水分の濡れを抑制することができる。

[0019] 上記態様に係る製造方法を用いれば、コンタクト孔の底に露出する上記何れかの電極の表面に酸化被膜が形成されることを効果的に抑制することができる。

[0020] 従って、TFT層の電極と表示素子部の電極との間に介挿された2層の絶縁層 (パッシベーション層と平坦化層) に対しコンタクト孔を開設しながら、良好な電極間接続を図ることができるアクティブマトリクス型表示パネルを製造することができる。

### 図面の簡単な説明

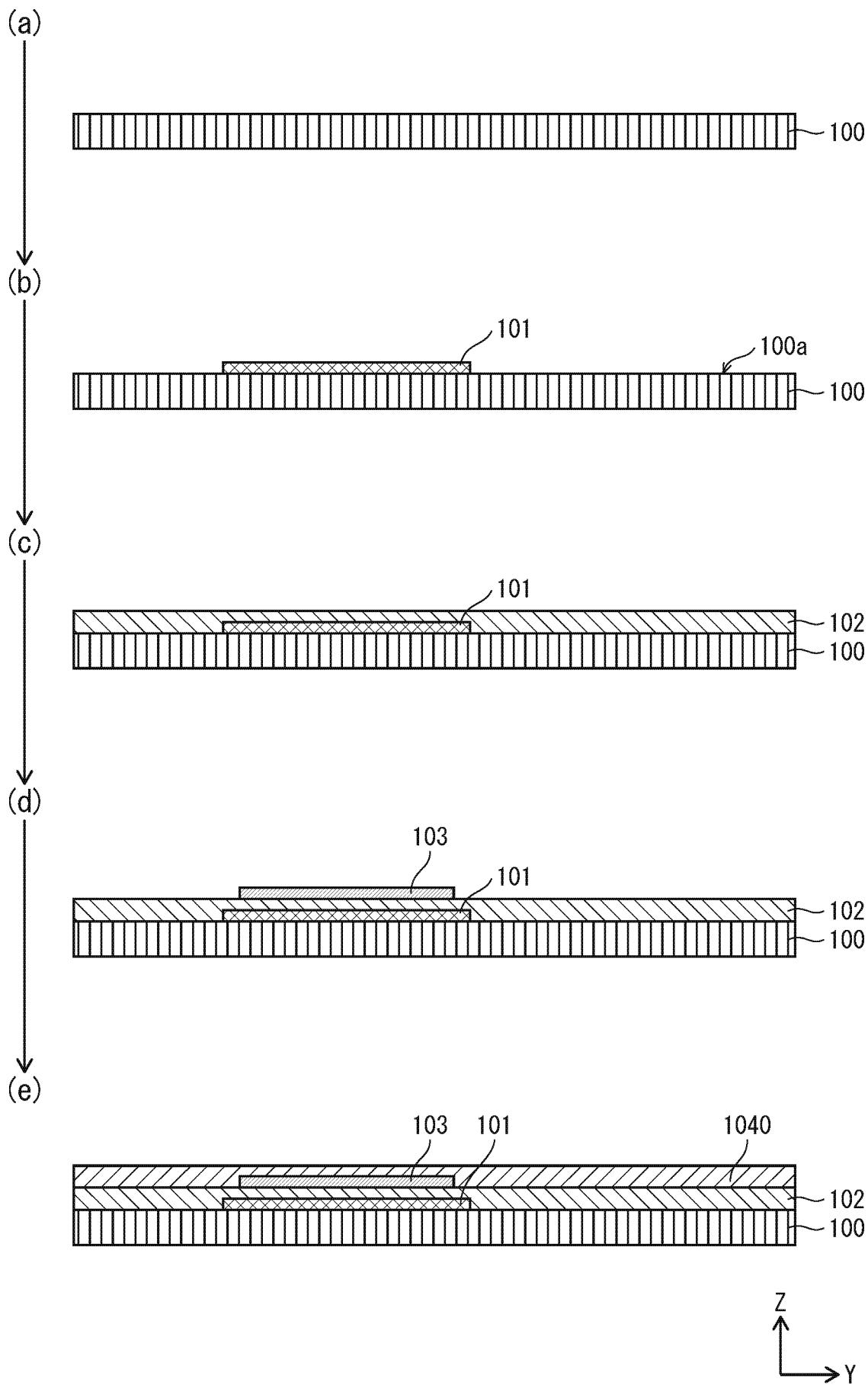

[0021] [図1] (a) 部～(e) 部は、本発明の実施の形態に係る表示パネル10の製造過程を順に示す模式断面図である。

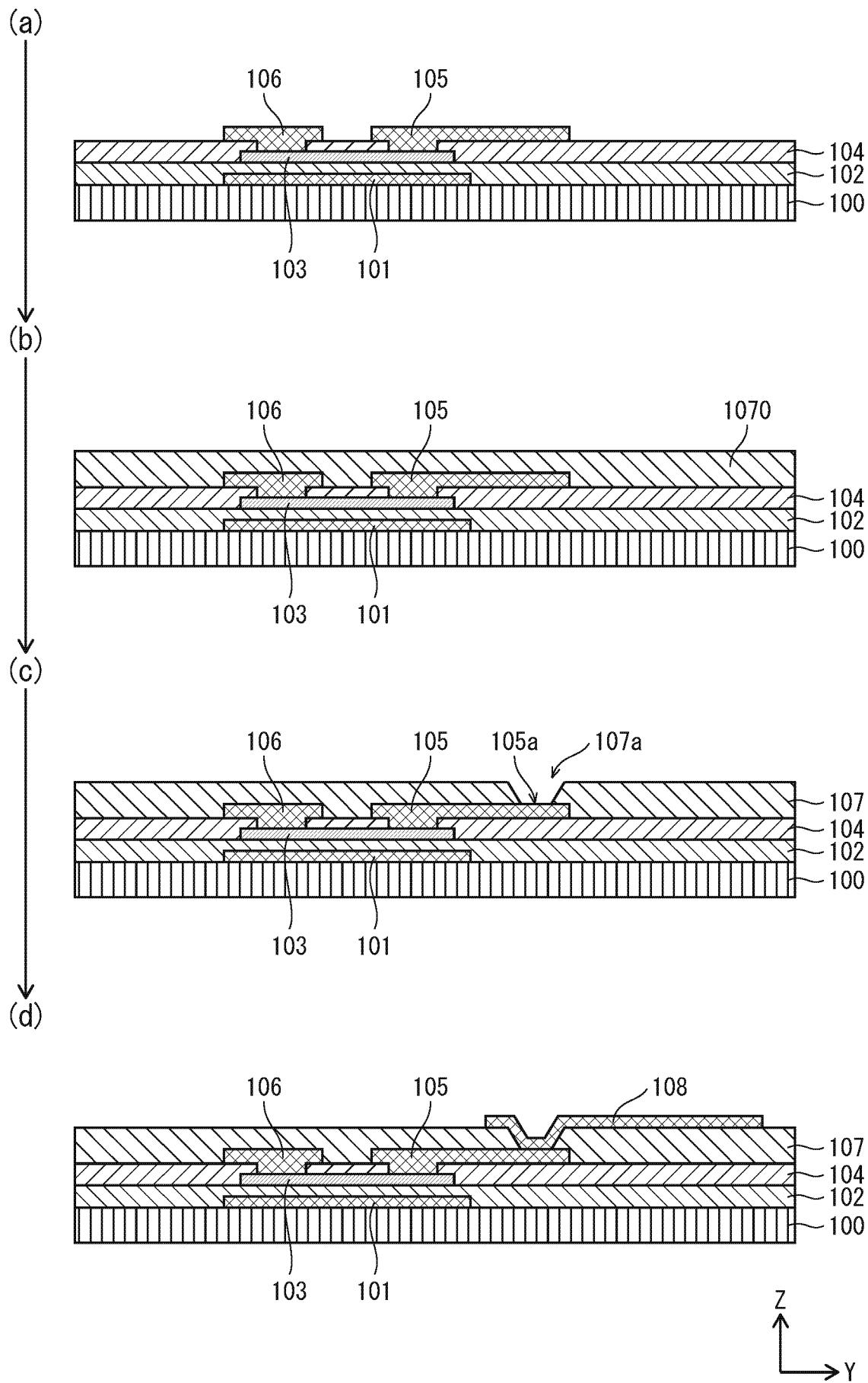

[図2] (a) 部～(d) 部は、本発明の実施の形態に係る表示パネル10の製造過程を順に示す模式断面図である。

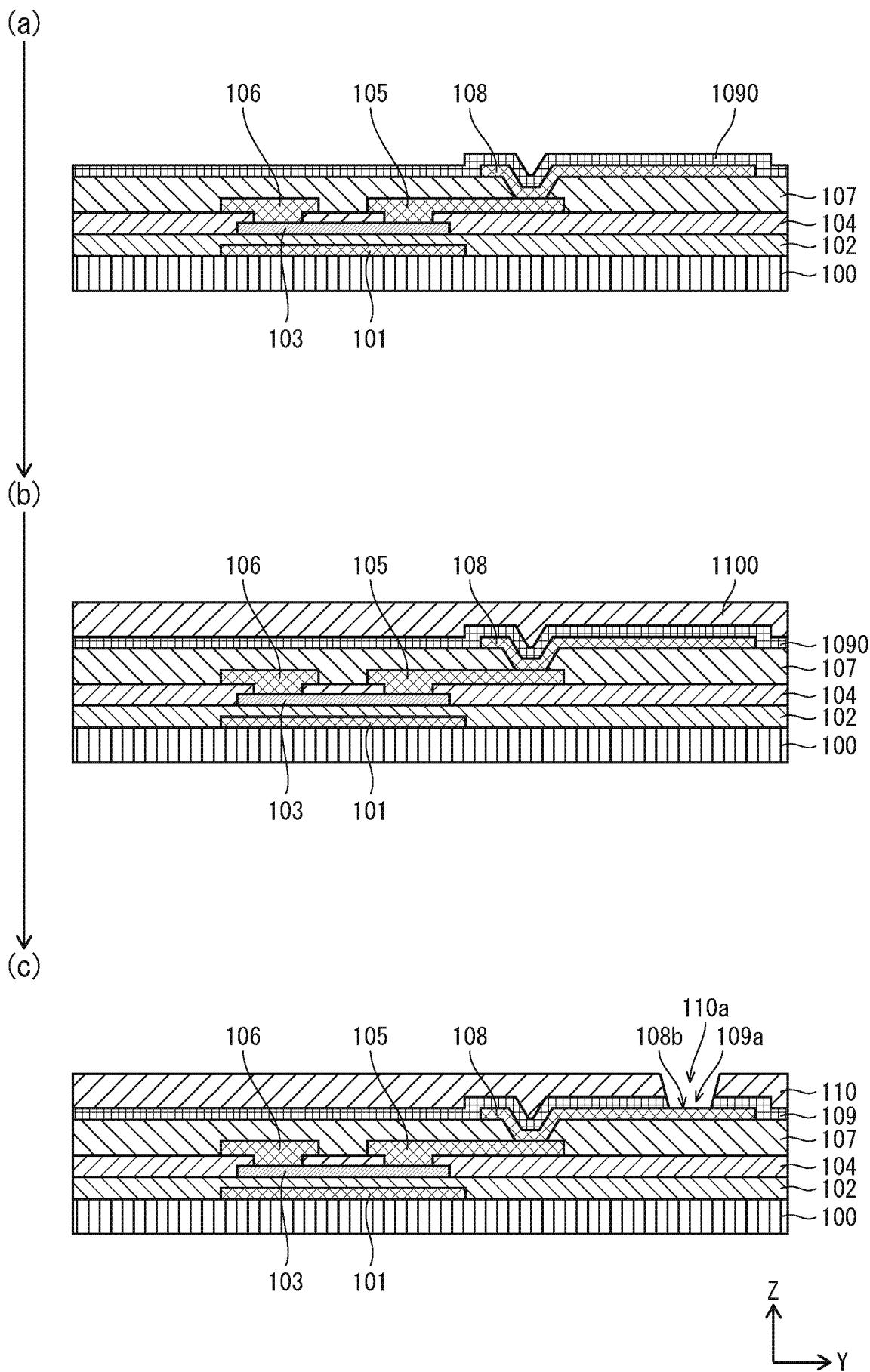

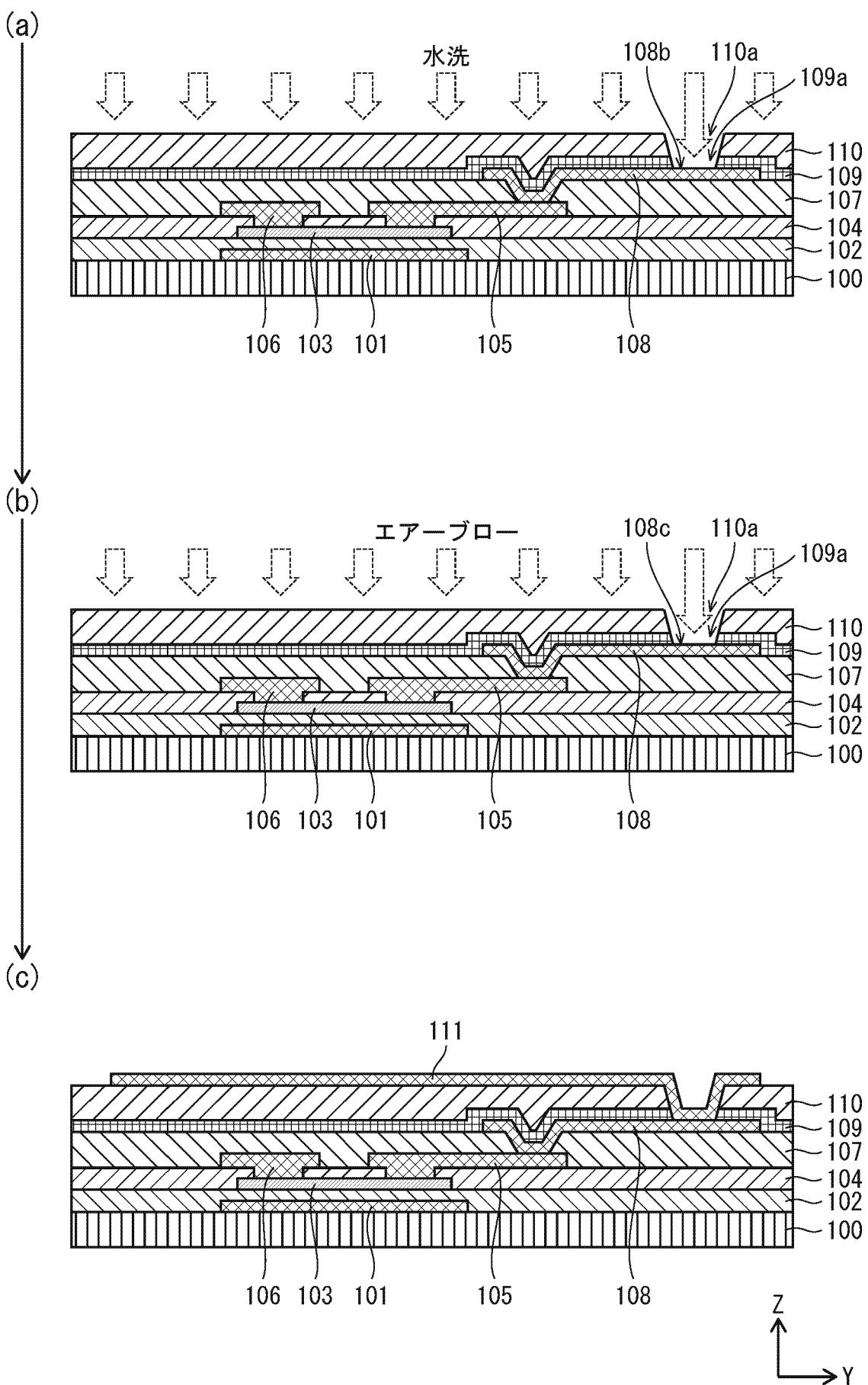

[図3] (a) 部～(c) 部は、本発明の実施の形態に係る表示パネル10の製造過程を順に示す模式断面図である。

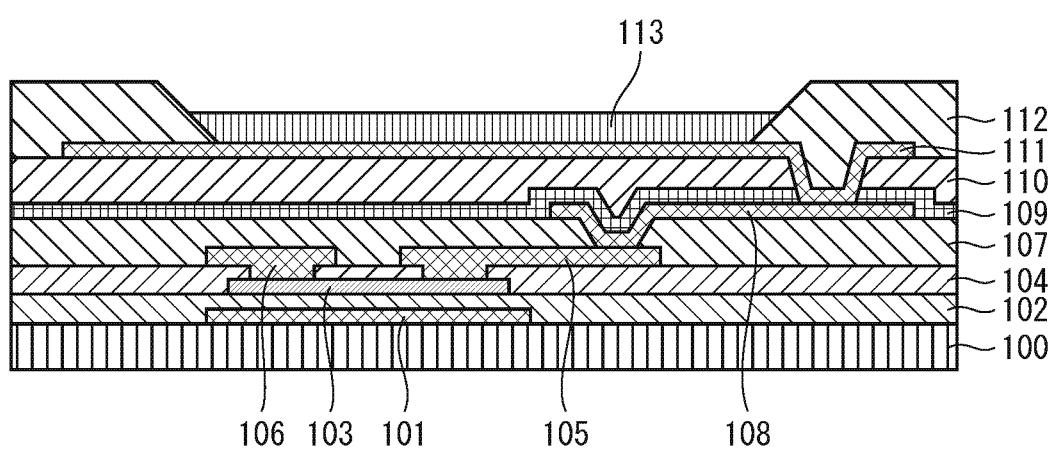

[図4] (a) 部～(c) 部は、本発明の実施の形態に係る表示パネル10の製造過程を順に示す模式断面図である。

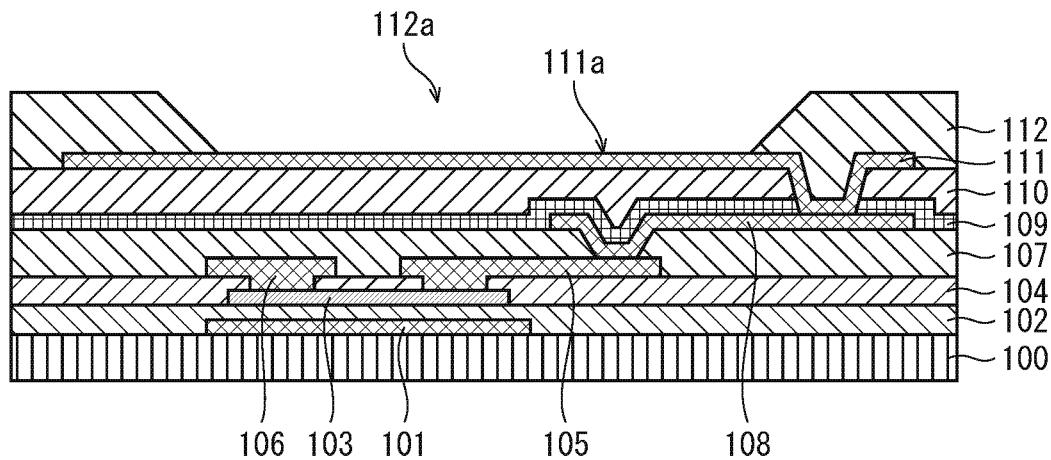

[図5] (a) 部～(c) 部は、本発明の実施の形態に係る表示パネル10の製造過程を順に示す模式断面図である。

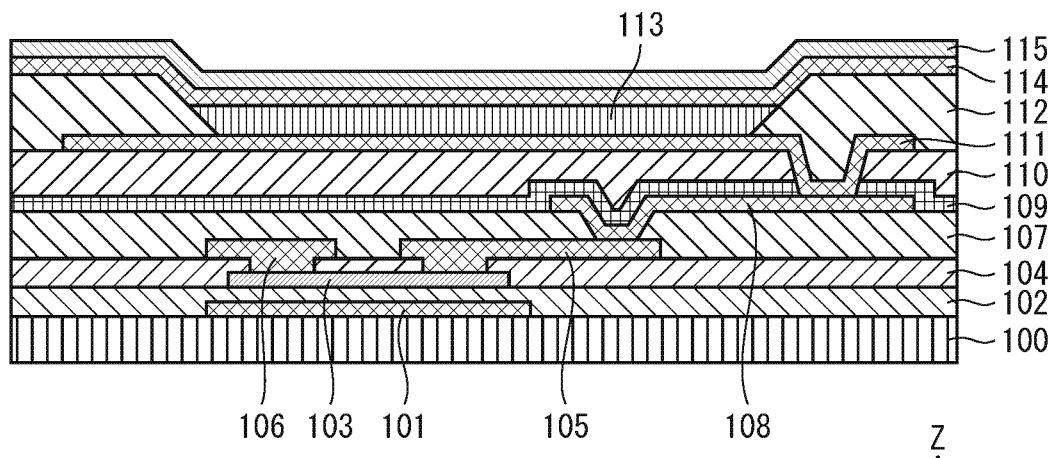

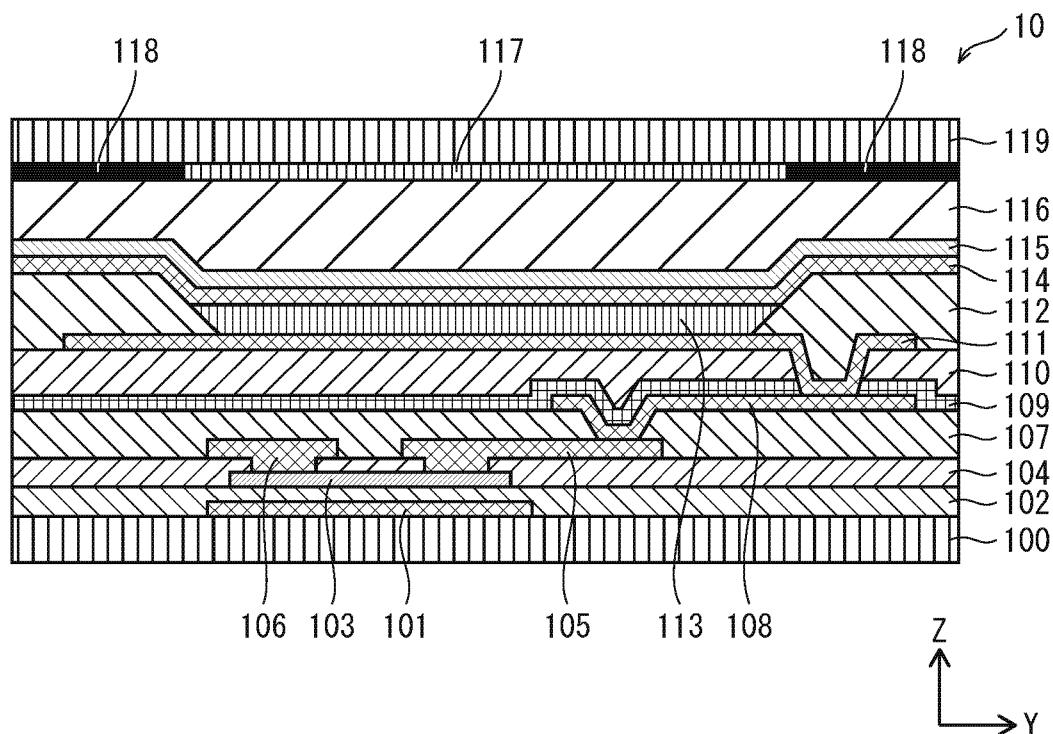

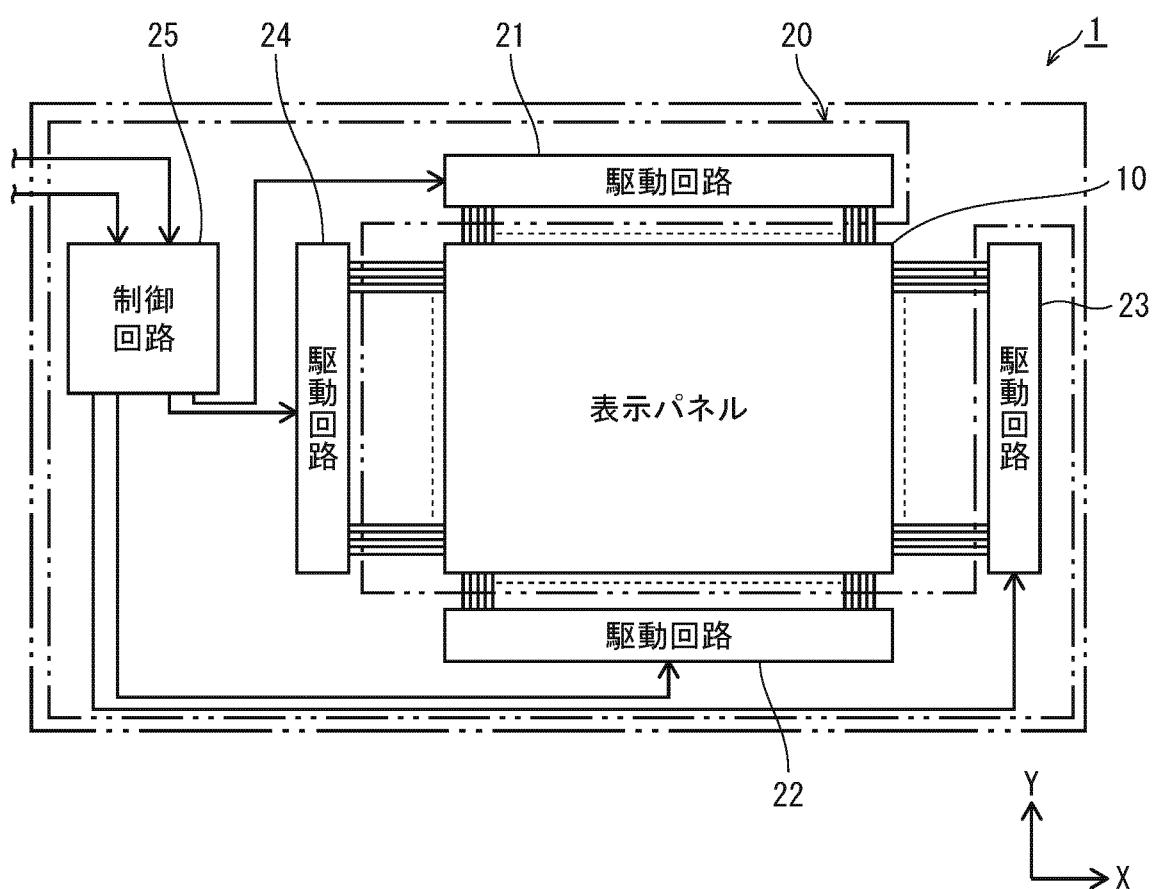

[図6] (a) は、本発明の実施の形態に係る完成した表示パネル10の構成を示す模式断面図であり、(b) は、本発明の実施の形態に係る表示パネル10を用いて形成した表示装置1の構成を示す模式プロック図である。

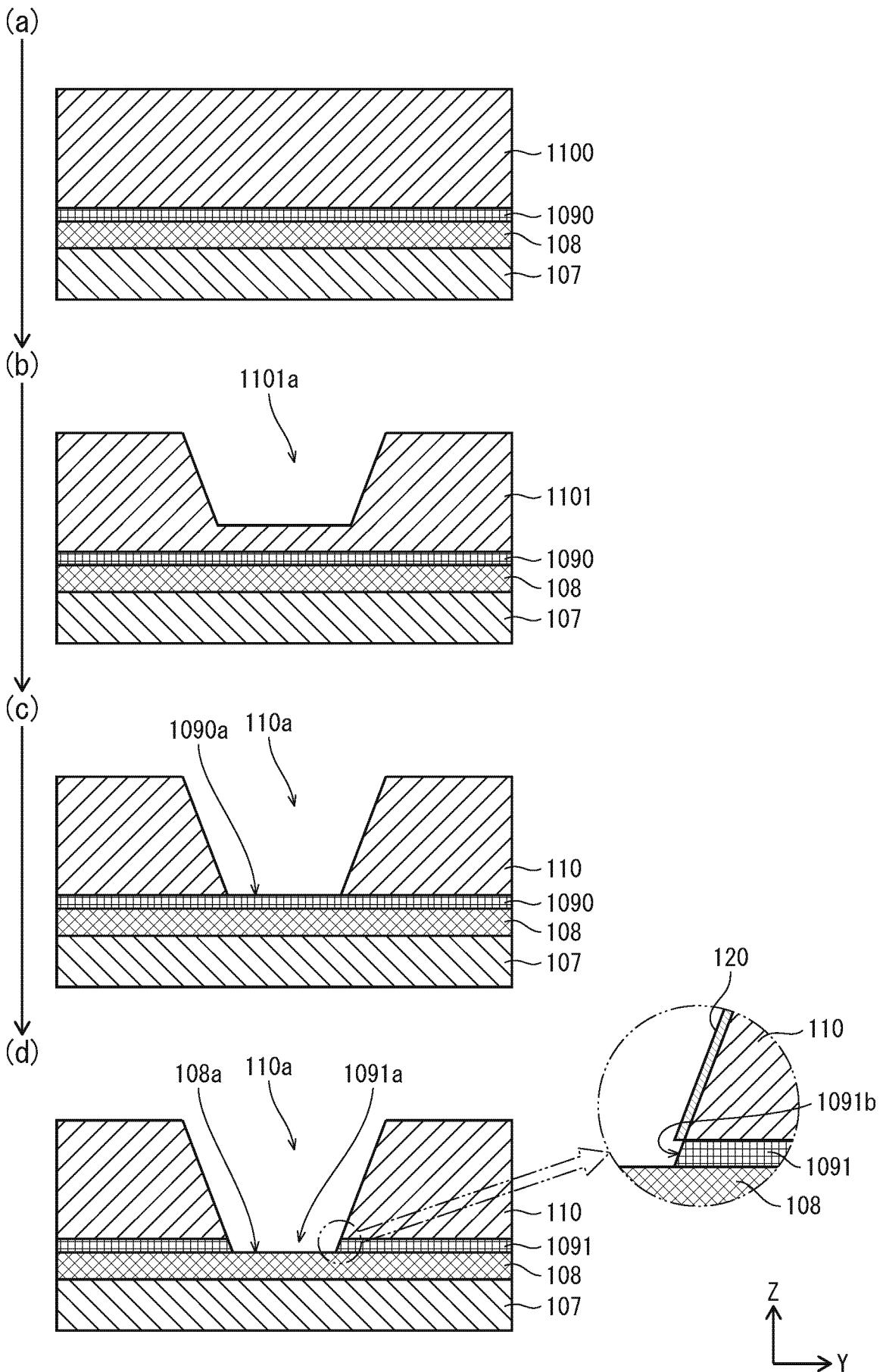

[図7] (a) 部～(d) 部は、実施例に係るパッシベーション層1090およ

び平坦化層 1100 へのコンタクト孔形成に係る過程を順に示す模式断面図である。

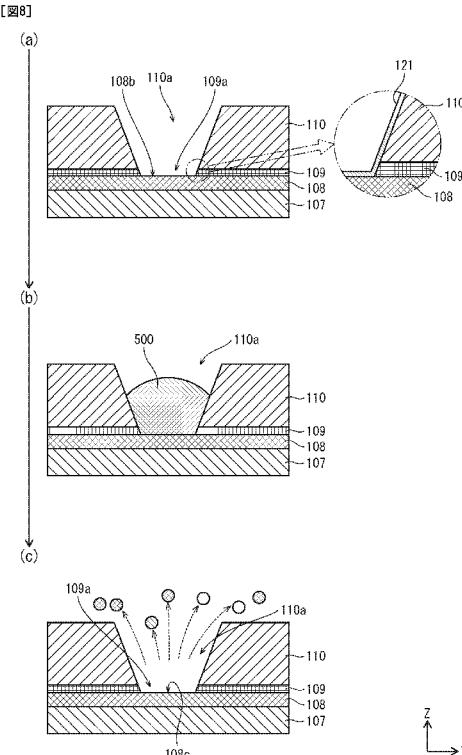

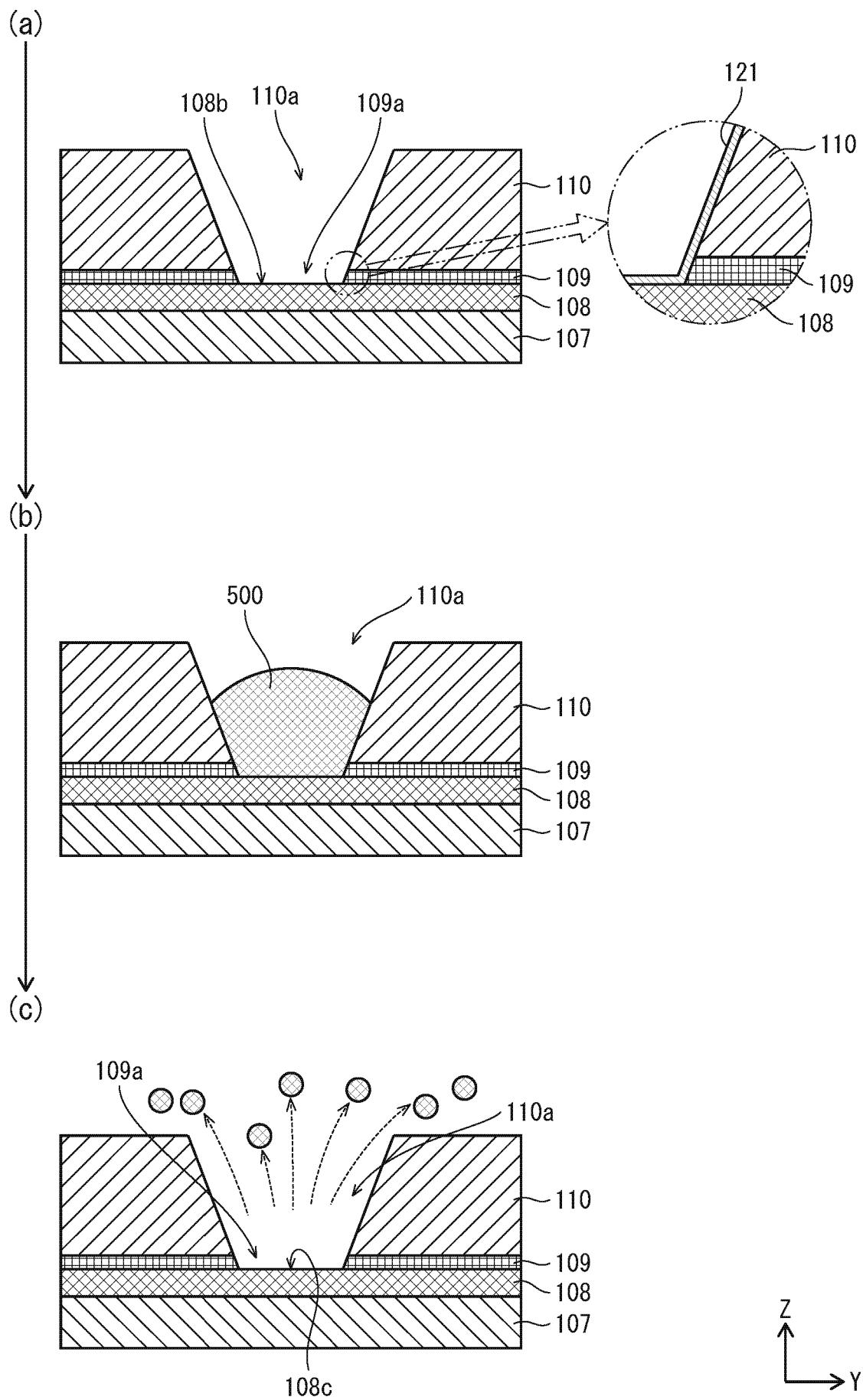

[図8] (a) 部～(c) 部は、実施例に係るパッシベーション層 1090 および平坦化層 1100 へのコンタクト孔形成に係る過程を順に示す模式断面図である。

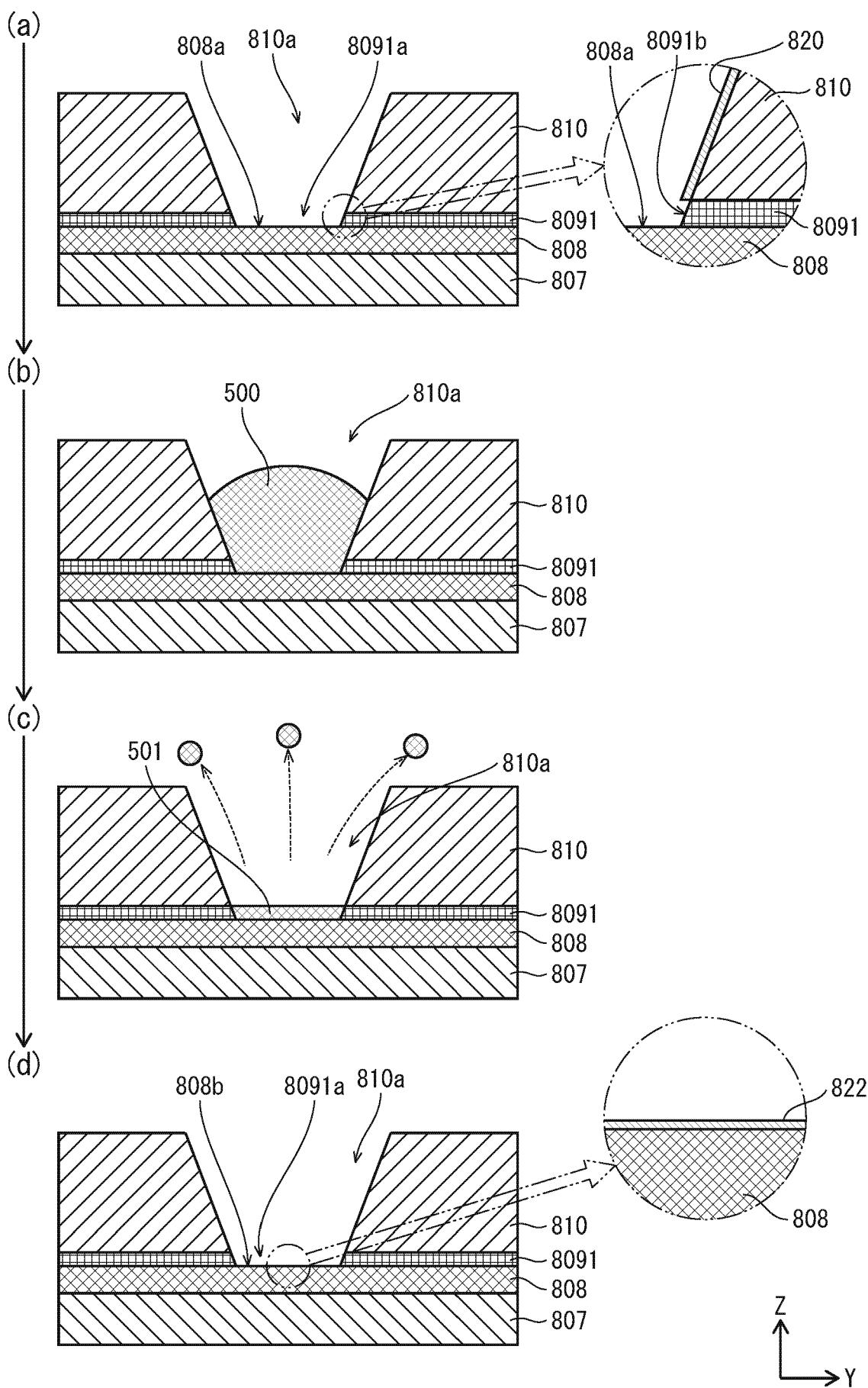

[図9] (a) 部～(d) 部は、比較例に係るコンタクト孔形成に係る過程を順に示す模式断面図である。

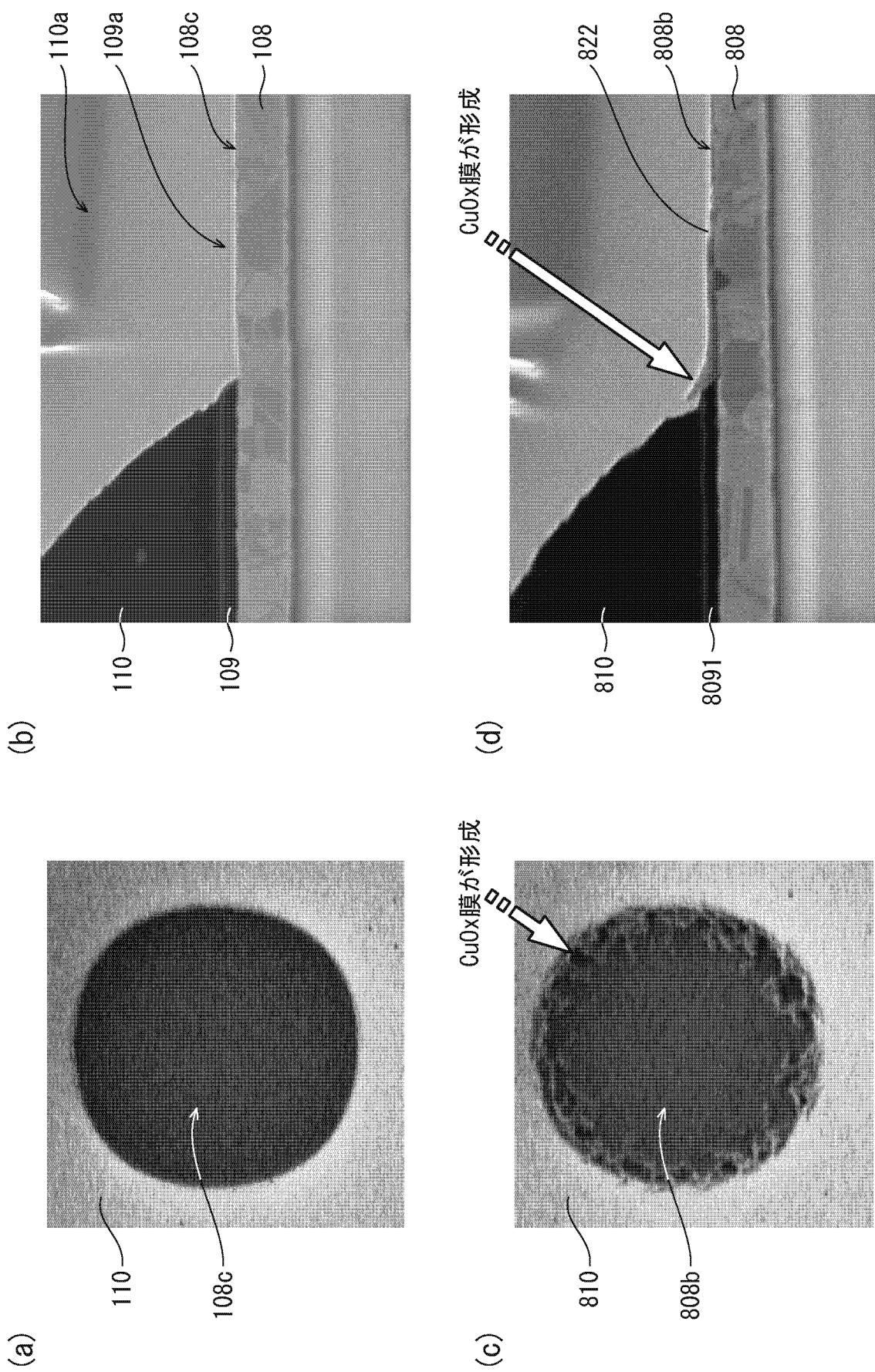

[図10] (a) は、実施例に係る製造方法を用い形成したコンタクト孔およびその周辺を平面視にて示す画像であり、(b) は、その断面を示す画像であり、(c) は、比較例に係る製造方法を用い形成したコンタクト孔およびその周辺を平面視にて示す画像であり、(d) は、その断面を示す画像である。

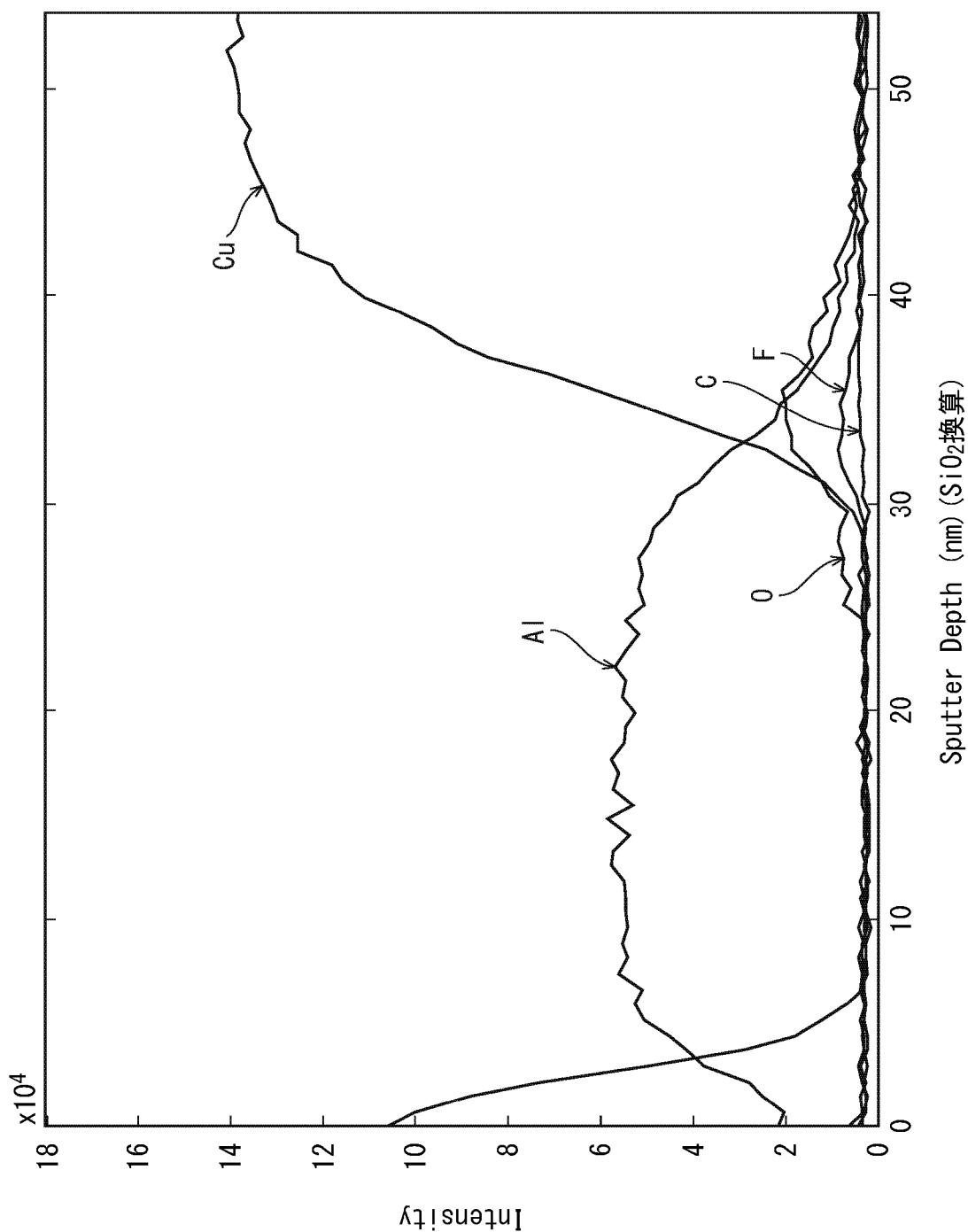

[図11] コンタクト孔の底に露出する上部電極 108 の組成を示すグラフである。

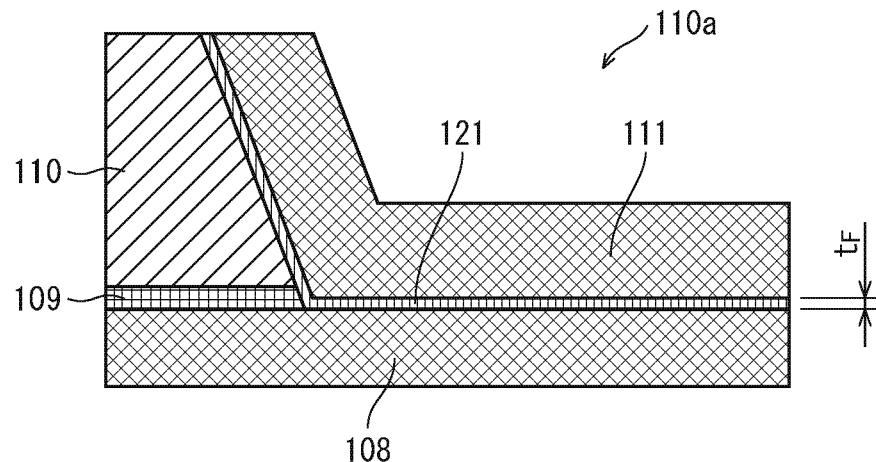

[図12] (a) は、本発明の実施の形態に係る条件で形成した場合のコンタクト孔の周辺を示す模式断面図であり、(b) は、比較例に係る条件で形成した場合のコンタクト孔の周辺を示す模式断面図である。

[図13] 変形例に係る表示パネル 15 の一部構成を示す模式断面図である。

[図14] 従来技術に係る表示パネルの構成を示す模式断面図である。

## 発明を実施するための形態

[0022] [本発明の各態様に至った経緯]

本発明者等は、図 14 の二点鎖線で囲んだ部分に示すような問題、即ち、TFT 層における上部電極 908 とアノード電極 911 との間に金属酸化膜 922 が介插し、これにより上部電極 908 とアノード 911 とのコンタクト不良が生じるメカニズムを次のように解明した。

[0023] 表示パネルの製造過程では、TFT 層を形成し、平坦化層 910 を形成した後に、上部電極 908 とアノード 911 とのコンタクトを図るためにコンタクト孔を開設することになる。コンタクト孔の開設は、リソグラフィ（露

光・現像)により平坦化層910にコンタクト孔を開設した後、ドライエッティングにより、平坦化層910のコンタクト孔の底部に露出するパッシベーション層909にコンタクト孔を開設することでなされる。そして、ドライエッティング後に、例えば、純水などを用いて孔内および平坦化層910表面などを洗浄する。

[0024] 洗浄後には、ドライエアーなどで水分の除去を図る。このとき、コンタクト孔を臨む平坦化層910の内壁面は先にコンタクト孔の開設が行われ、パッシベーション層909へのコンタクト孔開設の間もフッ素を含むエッティングガスに晒されているため、表面にフッ化膜が形成されるに至っている。これに対して、コンタクト孔を臨むパッシベーション層909の内壁面には、ほとんどフッ化膜が形成されていない状態となっているものと推定される。これは、従来の製造方法では、パッシベーション層909にコンタクト孔が開設され、底に上部電極908の表面が露出した時点でエッティングを終了していたため、パッシベーション層909におけるコンタクト孔を臨む内壁面は余りフッ素に晒されていないためであると考えられるためである。

[0025] 上記のように、パッシベーション層909におけるコンタクト孔を臨む内壁面へのフッ化膜の形成がほとんどなされない状況下で、水を用いた洗浄を行った場合、ドライエアーでのプローによつてもコンタクト孔の底に水が残ることがあるものと考えられる。そして、このコンタクト孔の底に残った水により、上部電極908の表面が酸化され、金属酸化膜922が形成されるに至るものであると考察した。

#### [本発明の各態様]

本発明の一態様に係るアクティブマトリクス型表示パネルの製造方法は、

(i) 基板上にTFT層を形成する工程と、(ii) TFT層上に平坦化層を形成する工程と、(iii) 平坦化層上に表示素子部を形成する工程と、

、

を備える。

[0027] (i) TFT層を形成する工程には、ソース電極もしくはドレイン電極、

またはその一方の電極に接続された接続用電極の何れかの電極（以下、「上部電極等」と記載する。）を被覆するパッシベーション層を、平坦化層と境界を接する状態で形成するサブ工程が含まれる。

- [0028] (i i) 表示素子部を形成する工程には、平坦化層と境界を接する状態で下部電極を形成するサブ工程が含まれる。

- [0029] 上部電極等と下部電極との接続は、次の工程を経てなされる。

- [0030] (i v - 1) 底にパッシベーション層が露出するまで、平坦化層にコンタクト孔を開設する。

- [0031] (i v - 2) 平坦化層に開設したコンタクト孔の底部に露出するパッシベーション層に対して、フッ素を含むガスを用いたドライエッティングにより、平坦化層のコンタクト孔に連通し、底に上部電極等が露出するコンタクト孔を開設する。

- [0032] (i v - 3) コンタクト孔の底に上部電極等が露出した後、パッシベーション層におけるコンタクト孔を臨む内壁面に対し、組成中にフッ素を含む撥液膜を形成する。

- [0033] そして、下部電極を形成するサブ工程において、コンタクト孔を臨む平坦化層およびパッシベーション層の内壁面に沿って、下部電極を形成する。

- [0034] 上記様に係る製造方法では、フッ素を含むガスでコンタクト孔を開設するので、上記(i v - 2)のパッシベーション層へのコンタクト孔の開設後では、少なくとも平坦化層におけるコンタクト孔を臨む内壁面に、組成中にフッ素を含む撥液膜が形成される。このため、仮に平坦化層およびパッシベーション層のコンタクト孔内に水分が入った場合でも、撥液膜により、コンタクト孔を臨む内壁面および底に露出する上部電極等への水分の濡れを抑制することができる。

- [0035] 上記様に係る製造方法を用いれば、コンタクト孔の底に露出する上部電極等の表面に酸化被膜が形成されることを効果的に抑制することができる。

- [0036] 従って、TFT層の上部電極と表示素子部の下部電極との間に介挿された2層の絶縁層（パッシベーション層と平坦化層）に対しコンタクト孔を開設

しながら、良好な電極間接続を図ることができるアクティブマトリクス型表示パネルを製造することができる。

[0037] なお、上記において、「組成中にフッ素を含む撥液膜」とは、必ずしもフッ化物で膜が構成されている様に限定されない。撥液膜中にフッ素が含まれていればよい。

[0038] 本発明の別態様に係るアクティブマトリクス型表示パネルの製造方法では、上記方法において、撥液膜の形成について、パッシベーション層のコンタクト孔の底に上部電極等の表面が露出した後、さらにパッシベーション層におけるコンタクト孔を臨む内壁面をフッ素を含むエッチングガスに晒すことにより行われる。

[0039] このようにコンタクト孔の底に上部電極等の表面が露出した後、さらにフッ素を含むガス(例えば、 $\text{CF}_4$ )に内壁面を晒す(オーバーエッチングを行う)ことにより、パッシベーション層におけるコンタクト孔を臨む内壁面にも撥液膜が形成される。よって、別の工程を実行しなくても、撥液膜の形成ができ、製造コストの上昇を抑えながら、上記効果を得ることができる。

[0040] また、本発明の別態様に係るアクティブマトリクス型表示パネルの製造方法では、上記方法において、コンタクト孔の開設を開始してから、コンタクト孔の底に上部電極等の表面が露出するまでの時間を $T_0$ とし、撥液膜の形成のために、パッシベーション層におけるコンタクト孔を臨む内壁面をガスに晒す時間を $T_1$ とするとき、次の関係を満たす。

$$[数1] \quad 70\% \times T_0 \leq T_1 \leq 150\% \times T_0$$

上記[数1]の関係を満たすように時間 $T_1$ を規定することにより、コンタクト孔内の水滴の残存を防ぎ、上部電極等の表面の酸化を防ぎながら、上部電極等と下部電極との間に介挿されることになるフッ素を含む膜の膜厚を制限して、TFT層の上部電極等と表示素子部の下部電極との良好なコンタクトを確保することができる。

[0041] 換言すると、本発明の別態様に係るアクティブマトリクス型表示パネルの製造方法では、上記方法において、撥液膜の形成後において、コンタクト孔

の底に露出する上部電極等の表面に、フッ素を含む電極被膜が形成されてなり、撥液膜の形成のために、パッシベーション層におけるコンタクト孔を臨む内壁面をガスに晒す時間んを、電極被膜の膜厚が3 [nm] 以下となるよう規定する。これにより、上部電極等と下部電極との良好なコンタクトをとることができる。

[0042] 本発明の別態様に係るアクティブマトリクス型表示パネルの製造方法では、上記方法の撥液膜の形成後、下部電極の形成前において、さらに次の工程を含む。

[0043] (i v - 4) コンタクト孔内を含む平坦化層およびパッシベーション層の表面を水を含む洗浄液で洗浄する。

[0044] (i v - 5) コンタクト孔内を含む平坦化層およびパッシベーション層の表面に対し、エアーまたはガスを吹き付けて、コンタクト孔内を含む平坦化層およびパッシベーション層の表面に残る洗浄液を除去する。

[0045] 本態様に係る製造方法では、上記 (i v - 2) のパッシベーション層へのコンタクト孔の開設後、上記 (i v - 4) の洗浄の前に、上記 (i v - 3) のように、パッシベーション層におけるコンタクト孔を臨む内壁面に撥液膜を形成する。このため、上記 (i v - 4) で平坦化層およびパッシベーション層のコンタクト孔内に入った洗浄液が、上記 (i v - 5) のエアー等の吹き付けにより、コンタクト孔内から確実に除去される。よって、本態様のように、洗浄液で洗浄する工程を含む場合においても、上記 (i v - 5) のエアー等の吹き付け後に洗浄液がコンタクト孔内に残留しにくく、コンタクト孔の底に露出する上部電極等の表面に酸化被膜が形成されることを効果的に抑制することができる。

[0046] 本発明の別態様に係るアクティブマトリクス型表示パネルの製造方法では、上記方法において、上部電極等は、銅 (Cu) もしくはCu合金を用い形成する。これにより、配線抵抗を低減することができ、良好な表示品質の表示パネルを製造することができる。

[0047] 本発明の一態様に係るアクティブマトリクス型表示パネルは、基板上に、

TFT層、平坦化層、および表示素子部がこの順に形成されてなる構成を有する。

[0048] TFT層には、ソース電極もしくはドレイン電極、またはその一方の電極に接続された接続用電極の何れかの電極（上部電極等）と、当該上部電極等を被覆し、平坦化層と境界を接するパッシベーション層とが含まれている。

[0049] また、表示素子部には、平坦化層と境界を接する状態で形成されてなる下部電極が含まれている。

[0050] 下部電極は、平坦化層およびパッシベーション層を連続して貫通するコンタクト孔を通し、平坦化層およびパッシベーション層におけるコンタクト孔を臨む内壁面に沿って一部が形成されることにより、コンタクト孔の底で上部電極等に対して電気的に接続されている。

[0051] 平坦化層およびパッシベーション層におけるコンタクト孔を臨む内壁面と、下部電極との間には、フッ素を含む膜が介挿されており、コンタクト孔の底において、下部電極と前記何れかの電極との間には、フッ素を含む電極被膜が介挿されている。

[0052] 上記態様に係る製造方法を用い製造されたアクティブマトリクス型表示パネルでは、上記のような構成を有することになる。よって、この構成を有するアクティブマトリクス型表示パネルでは、上部電極等と下部電極との間の良好なコンタクトが図られ、高い表示品質を実現することができる。

[0053] 本発明の別態様に係るアクティブマトリクス型表示パネルでは、上記構成において、電極被膜の膜厚が、3 [nm] 以下である。このように電極被膜の膜厚を3 [nm] 以下（例えば、2 [nm] ~3 [nm]）に規定することで、上部電極等と下部電極との良好なコンタクトをとることができる。

#### [実施の形態]

##### 1. 表示パネル10およびこれを含む表示装置1の製造方法

本発明の実施の形態に係る表示パネル10およびこれを含む表示装置1の製造方法について、図面を用い説明する。なお、以下では、表示パネル10の製造方法について、(1) TFT層の形成工程、(2) 平坦化層の形成工

程、(3) 表示素子部の形成工程に便宜的に分けて説明を行う。

#### (1) TFT層の形成工程

先ず、TFT層の形成工程について、図1の(a)部～(e)部、図2の(a)部～(d)部、および図3の(a)部を用い説明する。

- [0055] 図1の(a)部に示すように、基板100を準備する。

- [0056] 図1の(b)部に示すように、準備した基板100のZ軸方向上側の主面100aに対し、各トランジスタ素子部に対応してゲート電極101を形成する。ゲート電極101の形成は、基板100の主面100aに対して、メタルスパッタリング法を用いて銅(Cu)からなる金属膜とモリブデン(Mo)からなる金属膜とを積層形成し、その上にホトリソグラフィー法を用いてレジストパターンを形成した後、ウエットエッチングを行い、レジストパターンを除去することでなされる。

- [0057] なお、添付図面では、模式的に一つのトランジスタ素子部のみを図示しているが、表示パネル10には、複数のトランジスタ素子部が形成されてなる。

- [0058] 図1の(c)部に示すように、ゲート電極101および基板100の主面100aにおける露出部分を被覆するように、ゲート絶縁層102を積層形成する。ゲート絶縁層102の形成は、プラズマCVD(Chemical Vapour Deposition)法あるいはスパッタリング法を用い、SiO膜とSiN膜とを順に積層形成することでなされる。

- [0059] 図1の(d)部に示すように、ゲート絶縁層102上におけるゲート電極101の上方に相当する領域にチャネル層103を形成する。チャネル層103の形成は、スパッタリング法を用い、酸化物半導体膜を形成し、ホトリソグラフィー法およびウエットエッチング法を用いてパターニングすることでなされる。

- [0060] 図1の(e)部に示すように、チャネル層103およびゲート絶縁層102を被覆するように、チャネル保護層1040を積層形成する。チャネル保護層1040の形成は、プラズマCVD法あるいはスパッタリング法を用い

、S i O膜を成膜し、成膜後にドライエアーまたは酸素雰囲気下で、成膜温度以上の温度でアニール処理を施すことによりなされる。アニール処理は、チャネル層103の酸素欠陥を修復し、半導体特性を維持するためになされるものである。

[0061] 図2の(a)部に示すように、チャネル保護層104に対してチャネル層103に到達するコンタクト孔を開設した後、各コンタクト孔を通してチャネル層103に一部接触するソース電極105およびドレイン電極106を形成する。チャネル層104へのコンタクト孔の開設は、ホトリソグラフィ一法およびドライエッチング法を用いることでなされる。

[0062] ソース電極105およびドレイン電極106の形成は、スパッタリング法を用い、銅マンガン(CuMn)膜と、Mo膜とを積層した後、ホトリソグラフィー法およびウエットエッチング法を用いパターニングすることでなされる。

[0063] 図2の(b)部に示すように、ソース電極105、ドレイン電極106、およびチャネル保護層104の露出部分を被覆するように、層間絶縁層1070を形成する。層間絶縁層1070の形成は、プラズマCVD法あるいはスパッタリング法を用い成膜した後、ドライエアーまたは酸素雰囲気下でアニール処理を施すことによりなされる。アニール処理を行う目的は、上記同様に、チャネル層103の半導体特性を維持するためのものである。

[0064] 図2の(c)部に示すように、層間絶縁層107におけるソース電極105の一部上方に相当する部分にコンタクト孔107aを開設し、底にソース電極105の表面105aの一部が露出するようとする。そして、図2の(d)部に示すように、層間絶縁層107におけるコンタクト孔107aを臨む内壁面を含む、層間絶縁層107の表面の一部に上部電極108を形成する。

[0065] 層間絶縁層1070の成膜は、プラズマCVD法あるいはスパッタリング法を用いなされ、層間絶縁層107へのコンタクト孔107aの開設は、ドライエッチング法を用いなされる。また、上部電極108の形成は、スパッ

ターリング法を用い金属膜を形成した後、ホトリソグラフィー法およびウェットエッチング法を用いなされる。

[0066] 図3の(a)部に示すように、上部電極108および層間絶縁層107における露出部分を被覆するように、パッシベーション層1090を形成する。パッシベーション層1090の形成は、プラズマCVD法あるいはスパッタリング法を用いなされる。

[0067] 以上のような過程を経て、基板100上にTFT層が形成される。

## (2) 平坦化層の形成工程

次に、平坦化層の形成、および平坦化層へのコンタクト孔開設について、図3の(b)部～(c)部および図4の(a)部～(b)部を用い説明する。

[0068] 図3の(b)部に示すように、パッシベーション層1090を被覆するように、平坦化層1100を積層形成する。平坦化層1100の形成は、有機材料を塗布し硬化させた後、z軸方向上側の主面を平坦化することでなされる。

[0069] 図3の(c)部に示すように、平坦化層110およびパッシベーション層109に対して、互いに連続するコンタクト孔110a, 109aを開設する。平坦化層110へのコンタクト孔110aの開設には、リソグラフィ(露光・現像)を用い、パッシベーション層109へのコンタクト孔109aの開設には、ドライエッティング法を用いる。そして、コンタクト孔109aの底に上部電極108の表面108aの一部が露出するまで行う。

[0070] 図4の(a)部に示すように、平坦化層110のZ軸方向上側の主面、およびコンタクト孔110a, 109a内について、純水を用い洗浄を行う(水洗)。なお、洗浄の際には、洗浄液である純水は、上部電極108の表面108bにも接触することになる。

[0071] 図4の(b)部に示すように、水洗後の平坦化層110のZ軸方向上側の主面、およびコンタクト孔110a, 109a内について、エアープローにより洗浄液の除去を行う。なお、洗浄液の除去の際には、コンタクト孔11

0 a, 109 a の底に露出する上部電極 108 の表面 108 c の水滴も除去できるように、エアーノズルを走査する。

### (3) 表示素子部の形成

次に、平坦化層 110 上への表示素子部の形成について、図4の(c)部、図5の(a)部～(c)部および図6(a)を用いて説明する。

- [0072] 図4の(c)部に示すように、平坦化層 110 上、およびコンタクト孔 10 a, 109 a 内にアノード 111 を形成する。アノード 111 の形成は、スパッタリング法あるいは真空蒸着法を用い金属膜を成膜した後、ホトリソグラフィー法およびエッチング法を用いて、各素子に対応したパターニングを行うことでなされる。

- [0073] なお、アノード 111 上にホール注入層やホール輸送層などが形成されることもあるが、説明を省略する。

- [0074] 図5の(a)部に示すように、アノード 111 の表面 111 a における外縁部に対し、各表示素子部を規定する開口 112 a を囲繞するバンク 112 を形成する。バンク 112 の形成は、まずアノード 111 上に、スピニコート法などを用いてバンク 112 の構成材料膜を成膜し、パターニングにより開口 112 a を開設することで形成される。バンク 112 への開口 112 a の開設は、構成材料膜上にマスクを配置して露光し、その後に現像することでなされる。

- [0075] 図5の(b)部に示すように、バンク 112 で囲繞された開口 112 a に対して、有機発光層を含む有機発光機能層 113 を形成し、図5の(c)部に示すように、有機発光機能層 113 上およびバンク 112 の頂面上を被覆するように、カソード 114 および封止層 115 を順に成膜する。なお、図では、有機発光機能層 113 を一層構成で図示しているが、有機発光層を含む複数層が積層されてなる構成となっていてもよい。これらの有機層は、印刷法を用い形成される。

- [0076] カソード 114 および封止層 115 の形成は、スパッタリング法などを用いなされる。

[0077] 最後に、図6(a)に示すように、別途で作成しておいたカラーフィルタパネル(CFパネル)を、間に樹脂層116を挟んだ状態で貼り合わせることで、アクティブマトリクス型の表示パネル10が完成する。なお、CFパネルは、基板119のZ軸方向下側の主面にカラーフィルタ層117およびブラックマトリクス層118を形成してなるパネルである。

#### (4) 表示装置1の形成

次に、図6(b)に示すように、上記のような過程を経て完成した表示パネル10に対して、駆動・制御回路部20を接続することで表示装置1が完成する。駆動・制御回路部20は、一例として、4つの駆動回路21～24と、1つの制御回路25とから構成されている。ただし、駆動・制御回路部20の構成については、これに限られるものではない。例えば、駆動回路についても、表示パネル10の外周2辺に沿って、4つの駆動回路あるいは2つの駆動回路が配置されていてもよく、さらには、外周1辺に沿って全ての駆動回路が配置されていてもよい。

### 2. 各部の構成材料

#### (1) 基板100, 119

基板100, 119の構成材料としては、例えば、ガラス基板、石英基板、シリコン基板、硫化モリブデン、銅、亜鉛、アルミニウム、ステンレス、マグネシウム、鉄、ニッケル、金、銀などの金属基板、ガリウム砒素基などの半導体基板、プラスチック基板等を採用することができる。

[0078] プラスチック基板としては、熱可塑性樹脂、熱硬化性樹脂いずれの樹脂を用いてもよい。例えば、ポリエチレン、ポリプロピレン、エチレン-プロピレン共重合体、エチレン-酢酸ビニル共重合体(EVA)等のポリオレフィン、環状ポリオレフィン、変性ポリオレフィン、ポリ塩化ビニル、ポリ塩化ビニリデン、ポリスチレン、ポリアミド、ポリイミド(PD)、ポリアミドイミド、ポリカーボネート、ポリ-(4-メチルベンゼンテニ-1)、アイオノマー、アクリル系樹脂、ポリメチルメタクリレート、アクリルースチレン共

重合体（A S樹脂）、ブタジエンースチレン共重合体、ポリオ共重合体（E V O H）、ポリエチレンテレフタレート（P E T）、ポリプロピレンテレフタレート、ポリエチレンナフタレート（P E N）、プリシクロヘキサンテレフタレート（P C T）等のポリエステル、ポリエーテル、ポリエーテルケトン、ポリエーテルスルホン（P E S）、ポリエーテルイミド、ポリアセタール、ポリフエニレンオキシド、変形ポリフエニレンオキシド、ポリアリレート、芳香族ポリエステル（液晶ポリマー）、ポリテトラフルオロエチレン、ポリフッ化ビニリデン、その他フッ素系樹脂、スチレン系、ポリオレフィン系、ポリ塩化ビニル系、ポリウレタン系、フッ素ゴム系、塩素化ポリエチレン系等の各種熱可塑性エラストマー、エポキシ樹脂、エノール樹脂、ユリア樹脂、メラミン樹脂、不飽和ポリエステル、シリコーン樹脂、ポリウレタン等、またはこれらを主とする共重合体、ブレンド体、ポリマーアロイ等が挙げられ、これらのうち1種、または2種以上を積層した積層体を用いることができる。

[0079] (2) ゲート電極 101

ゲート電極101の構成材料としては、例えば、銅（C u）を含み構成されている。例えば、銅（C u）からなる層とモリブデン（M o）からなる層との積層体を採用することができる。

[0080] ただし、ゲート電極101の構成については、これに限定されず、例えば、C u単層や、C u/Wの積層体などを採用することもできるし、次のような材料を採用することも可能である。

[0081] それ以外に採用することが可能な材料としては、クロム（C r）、アルミニウム（A l）、タンタル（T a）、ニオブ（N b）、銀（A g）、金（A u）、プラチナ（P t）、パラジウム（P d）、インジウム（I n）、ニッケル（N i）、ネオジム（N d）などの金属もしくはそれらの合金、または、酸化亜鉛、酸化スズ、酸化インジウム、酸化ガリウムなどの導電性金属酸化物もしくは酸化インジウムスズ（I T O）、酸化インジウム亜鉛（I z O）、酸化アルミニウム亜鉛（A Z O）、酸化ガリウム亜鉛（G Z O）などの

導電性金属複合酸化物、または、ポリアニリン、ポリピロール、ポリチオフェン、ポリアセチレンなどの導電性高分子もしくはそれらに、塩酸、硫酸、スルホン酸などの酸、六フッ化リン、五フッ化ヒ素、塩化鉄などのルイス酸、ヨウ素などのハロゲン原子、ナトリウム、カリウムなどの金属原子などのドーパントを添加したもの、もしくは、カーポンブラックや金属粒子を分散した導電性の複合材料などが挙げられる。また、金属微粒子とグラファイトのような導電性粒子を含むポリマー混合物を用いてもよい。これらは、1種または2種以上を組み合わせて用いることもできる。

[0082] (3) ゲート絶縁層 102

ゲート絶縁層 102 の構成としては、例えば、酸化シリコン (SiO<sub>2</sub>) と窒化シリコン (SiN<sub>x</sub>) との積層体を採用することができる。ただし、ゲート絶縁層 102 の構成は、これに限定されるものではなく、ゲート絶縁層 102 の構成材料としては、例えば、電気絶縁性を有する材料であれば、公知の有機材料や無機材料のいずれも用いることができる。

[0083] 有機材料としては、例えば、アクリル系樹脂、エボノール系樹脂、フッ素系樹脂、エポキシ系樹脂、イミド系樹脂、ノボラック系樹脂などを用い形成することができる。

[0084] また、無機材料としては、例えば、酸化ケイ素、酸化アルミニウム、酸化タンタル、酸化ジルコニア、酸化セリウム、酸化亜鉛、酸化コバルトなどの金属酸化物、窒化ケイ素、窒化アルミニウム、窒化ジルコニア、窒化セリウム、窒化亜鉛、窒化コバルト、窒化チタン、窒化タンタルなどの金属窒化物、チタン酸バリウムストロンチウム、ジルコニアチタン酸鉛などの金属複合酸化物が挙げられる。これらは、1種または2種以上組み合わせて用いることができる。

[0085] さらに、表面処理剤 (ODTS OTS HMDS βPTS) などでその表面を処理したものも含まれる。

[0086] (4) チャネル層 103

チャネル層 103 の構成としては、アモルファス酸化インジウムガリウム

亜鉛 (I G Z O) からなる層を採用することができる。チャネル層 103 の構成材料は、これに限定されるものではなく、インジウム (In)、ガリウム (Ga)、亜鉛 (Zn) から選択される少なくとも一種を含む酸化物半導体を採用することができる。

[0087] また、チャネル層 103 の層厚については、例えば、20 [nm] ~ 200 [nm] の範囲とすることができます、表示パネル 10 に形成されている全てのチャネル層 103 で層厚が同一である必要はなく、一部が異なるように設定することもできる。

[0088] (5) チャネル保護層 104

チャネル保護層 104 の構成としては、酸化シリコン (SiO) からなる層を採用することができる。ただし、チャネル保護層 104 の構成材料は、これに限定されるものではなく、例えば、酸窒化シリコン (SiON)、窒化シリコン (SiN)、あるいは酸化アルミニウム (AlOx) を用いることができる。また、上記のような材料を用いた層を複数積層することで構成することもできる。

[0089] また、チャネル保護層 104 の層厚については、例えば、50 [nm] ~ 500 [nm] の範囲とすることができます。

[0090] (6) ソース電極 105 および ドレイン電極 106

ソース電極 105 および ドレイン電極 106 の構成としては、銅マンガン (CuMn) とモリブデン (Mo) との積層体を採用することができる。

[0091] なお、ソース電極 105 および ドレイン電極 106 の層厚については、例えば、100 [nm] ~ 500 [nm] の範囲とすることができます。

[0092] (7) 層間絶縁層 107

層間絶縁層 107 の構成としては、酸化シリコン (SiO) からなる層を採用することができる。

[0093] (8) 上部電極 108

上部電極 108 の構成としては、ソース電極 105 および ドレイン電極 106 などと同様に、銅マンガン (CuMn) とモリブデン (Mo) との積層

体を採用することができる。ここで、上部電極 108においては、Cuからなる層がZ軸方向上部となる構成となっている。

[0094] (9) パッシベーション層 109

パッシベーション層 109の構成としては、窒化シリコン(SiN)からなる層を採用することができる。

[0095] なお、パッシベーション層 109の層厚については、例えば、50 [nm] ～150 [nm] の範囲、例えば、100 [nm] とすることができる。

[0096] (10) 平坦化層 110

平坦化層 110の構成は、ポリイミドからなる層を採用することができる。ただし、ポリイミドからなる層以外にも、ポリアミド、アクリル系樹脂材料などの有機化合物からなる層を採用することもできる。

[0097] なお、平坦化層 110の層厚については、4.0 [ $\mu\text{m}$ ] ～5.0 [ $\mu\text{m}$ ] の範囲、例えば、4.5 [ $\mu\text{m}$ ] とすることができる。

[0098] (11) アノード 111

アノード 111は、銀(Ag)またはアルミニウム(Al)を含む金属材料から構成されている。トップエミッション型の本実施の形態に係る表示パネル 10の場合には、その表面部が高い反射性を有することが好ましい。

[0099] なお、アノード 111については、上記のような金属材料からなる単層構造だけではなく、金属層と透明導電層との積層体を採用することもできる。透明導電層の構成材料としては、例えば、酸化インジウムスズ(ITO)や酸化インジウム亜鉛(IzO)などを用いることができる。

[0100] なお、本実施の形態では、アノード 111と有機発光層との間の機能層、例えば、ホール注入層などについては図示および説明を省略しているが、これら機能層を挿入した構成を採用することもできる。

[0101] 例えば、ホール注入層を採用する場合には、その構成材料として、例えば、銀(Ag)、モリブデン(Mo)、クロム(Cr)、バナジウム(V)、タンクステン(W)、ニッケル(Ni)、イリジウム(Ir)などの酸化物、あるいは、PEDOT(ポリチオフェンとポリスチレンスルホン酸との混

合物 ) などの導電性ポリマー材料を採用することができる。

[01 02] なお、金属酸化物からなるホール注入層を採用する場合には、P E D O Tなどの導電性ポリマー材料を用いる場合に比べて、ホールを安定的に、またはホールの生成を補助して、有機発光層に対しホールを注入する機能を有し、大きな仕事関数を有する、という観点から有効である。

[01 03] (12) バンク112

バンク112は、樹脂等の有機材料を用い形成されており絶縁性を有する。バンク112の形成に用いる有機材料の例としては、アクリル系樹脂、ポリイミド系樹脂、ノボラック型フェノール樹脂等があげられる。バンク112は、有機溶剤耐性を有することが好ましい。さらに、バンク112は、製造工程中において、エッチング処理、ベーク処理など施されることがあるので、それらの処理に対して過度に変形、変質などをしないような耐性の高い材料で形成されることが好ましい。また、表面に撥水性をもたせるために、表面をフッ素処理することもできる。

[01 04] なお、バンク112を親液性の材料を用い形成した場合には、バンク112の表面と有機発光層の表面との親液性/撥液性の差異が小さくなり、有機発光層を形成するために有機物質を含んだインクを、バンク112が規定する開口部内に選択的に保持させることが困難となってしまうためである。

[01 05] さらに、バンク112の構造については、図6(a)に示すような一層構造だけでなく、二層以上の多層構造を採用することもできる。この場合には、層毎に上記材料を組み合わせることもできるし、層毎に無機材料と有機材料とを用いることもできる。

[01 06] (13) 有機発光機能層113

有機発光機能層113における有機発光層としては、ホールと電子とが注入され再結合されることにより励起状態が生成され発光する機能を有する。有機発光層の形成に用いる材料は、湿式印刷法を用い成膜できる発光性の有機材料を用いることが必要である。

[01 07] 具体的には、例えば、特許公開公報(日本国・特開平5\_163488号

公報)に記載のオキシノイド化合物、ペリレン化合物、クマリン化合物、アザクマリン化合物、オキサゾール化合物、オキサジアゾール化合物、ペリノン化合物、ピロロピロール化合物、ナフタレン化合物、アントラセン化合物、フルオレン化合物、フルオランテン化合物、テトラセン化合物、ピレン化合物、コロネン化合物、キノロン化合物及びアザキノロン化合物、ビラゾリン誘導体及びピラゾロン誘導体、ローダミン化合物、クリセン化合物、フエンントレン化合物、シクロヘンタジエン化合物、スチルベン化合物、ジフェニルキノン化合物、スチリル化合物、ブタジエン化合物、ジシアノメチレンピラン化合物、ジシアノメチレンチオピラン化合物、フルオレセイン化合物、ピリリウム化合物、チアピリリウム化合物、セレナピリリウム化合物、テルロピリリウム化合物、芳香族アルダジエン化合物、オリゴフェニレン化合物、チオキサンテン化合物、アンスラセン化合物、シアニン化合物、アクリジン化合物、8-ヒドロキシキノリン化合物の金属錯体、2-ビピリジン化合物の金属錯体、シッフ塩とIII族金属との錯体、オキシン金属錯体、希土類錯体などの蛍光物質で形成されることが好ましい。

[01 08] なお、有機発光層とカソード114との間に、電子輸送層を挿入することができる。

[01 09] 電子輸送層は、カソード114から注入された電子を有機発光層へ輸送する機能を有し、例えば、オキサジアゾール誘導体(OXD)、トリアゾール誘導体(TAZ)、フェナンスロリン誘導体(BCP、Bphen)などを用い形成されている。

[01 10] (14) カソード114

カソード114は、例えば、酸化インジウムスズ(ITO)若しくは酸化インジウム亜鉛(IZO)などを用い形成される。本実施の形態のように、トップエミッション型の本実施の形態に係る表示パネル10の場合においては、光透過性の材料で形成されることが必要となる。光透過性については、透過率が80[%]以上とすることが好ましい。

[01 11] (15) 封止層115

封止層 115 は、有機発光層などの有機層が水分に晒されたり、空気に晒されたりすることを抑制する機能を有し、例えば、窒化シリコン (SiN) 、酸窒化シリコン (SiON) などの材料を用い形成される。また、窒化シリコン (SiN) 、酸窒化シリコン (SiON) などの材料を用い形成された層の上に、アクリル樹脂、シリコーン樹脂などの樹脂材料からなる封止樹脂層を設けてもよい。

[01 12] 封止層 115 は、トップエミッション型である本実施の形態に係る表示パネル 10 の場合においては、光透過性の材料で形成されることが必要となる。

[01 13] (16) カラーフィルタ層 117

カラーフィルタ層 117 としては、赤色 (R) 、緑色 (G) 、青色 (B) の各色の波長域の可視光を選択的に透過する、公知の材料から構成される。例えば、アクリル樹脂をベースに形成されている。

[01 14] (17) ブラックマトリクス層 118

ブラックマトリクス層 118 は、例えば、光吸収性および遮光性に優れる黒色顔料を含む紫外線硬化樹脂材料から構成されている。具体的な紫外線硬化樹脂材料としては、例えば、アクリル樹脂等がある。

### 3. コンタクト孔 110a , 109a の開設

次に、上記のような製造過程の内、平坦化層 110 およびパッシベーション層 109 へのコンタクト孔 110a , 109a の開設工程について、図 7 から図 9 を用い詳細説明を行う。

[01 15] 図 7 の (a) 部～(d) 部、および図 8 の (a) 部～(c) 部は、図 3 の (b) 部～(c) 部、および図 4 の (a) 部～(b) 部の工程を詳細に示す実施例に係る各工程での模式断面図であって、図 9 の (a) 部～(d) 部は、その比較例に係る対応する工程での模式断面図である。

[01 16] (実施例)

図 7 の (a) 部に示すように、表示パネル 10 の製造過程において、層間絶縁層 107 、上部電極 108 、パッシベーション層 1090 、および平坦

化層 1100 を Z 軸方向下側から順に積層形成する。このとき、本実施例では、パッシベーション層 1090 の層厚を 100 [nm] とし、平坦化層 1100 の層厚を 4.5 [ $\mu\text{m}$ ] としている。

[0117] 構成材料については、パッシベーション層 1090 が SiN であり、平坦化層 1100 がポリイミドである。また、上部電極 108 については、Z 軸方向下側から Mo 層と CuMn 層とが順に積層された積層体である。

[0118] 次に、図 7 の (b) 部に示すように、リソグラフィにより平坦化層 1101 の表面側からコンタクト孔 1101a を開設してゆく。

[0119] 図 7 の (c) 部に示すように、コンタクト孔 1101a の底部にパッシベーション層 1090 の表面 1090a が露出するまで、平坦化層 110 へのコンタクト孔 1101a の開設を行う。

[0120] 次に、図 7 の (d) 部に示すように、コンタクト孔 1101a が開設された平坦化層 110 をマスクとして、ドライエッチングによりパッシベーション層 1091 にコンタクト孔 1091a の開設を行う。ドライエッチングの条件は、次の通りである。

[0121]  $C_F_4 / O_2 = 1080 / 120$  [sccm]

Pressure = 15 ~ 50 [mTorr] (例えば、30 [mTorr])

Source, Bias = 3000 [W]

なお、上記条件中におけるガス流量の単位 (scm) については、温度 0 [°C] で 1013 [hPa] (1 [atm]) での値である。

[0122] ドライエッチングにより、パッシベーション層 1091 のコンタクト孔 1091a の底部には、上部電極 108 の表面 108a が露出する。このとき、二点鎖線で囲んだ部分に示すように、パッシベーション層 1091 におけるコンタクト孔 1091a を臨む内壁面 1091a には、殆どフッ化膜は形成されていない。一方、平坦化層 110 におけるコンタクト孔 1101a を臨む側壁には、フッ化膜 120 が形成される。

[0123] なお、本実施例では、コンタクト孔 1101a, 1091a のアスペクト比は

、 略 100 % である。

[01 24] 図 8 の (a) 部に示すように、本実施例に係る製造方法では、パッシベーション層 109 に対するコンタクト孔 109a の開設がなされた後、オーバーエッティング処理を行う。これにより、二点鎖線で囲んだ部分に示すように、平坦化層 110 およびパッシベーション層 109 におけるコンタクト孔 110a, 109a を臨む内壁面は、フッ化膜 121 で被覆されるに至る。なお、上部電極 108 におけるコンタクト孔 109a の底に露出する表面についても、フッ化膜 121 で被覆（フッ素を含む電極被膜が形成）されることになる。

[01 25] なお、本明細書において「フッ化膜」とは、単に「フッ素を含む膜」というものであって、必ずしもフッ素が化合物化して存在する膜に限定されるものではない。

[01 26] ここで、オーバーエッティングの時間について、本発明者等の検討結果より、図 7 の (a) 部に示すエッティング開始から図 7 の (d) 部に示す上部電極 108 の表面 108a が露出した状態となるまでの時間を  $T_0$  とするとき、図 7 の (d) 部に示す状態になった後、図 8 の (a) 部に示す状態に至るまでの時間  $T_1$  を次のようにすることが好ましい。

[01 27] [数 2]  $70\% \times T_0 \leq T_1 \leq 150\% \times T_0$

例えば、時間  $T_0$  が 35 [sec.] と仮定した場合には、時間  $T_1$  を 24.5 [sec.] 以上 87.5 [sec.] 以下とすることができます。

[01 28] なお、上記時間  $T_1$  については、ドライエッティングの条件や、各層の構成材料などによっても異なるので、それらごとに最適な時間を規定することが好ましい。

[01 29] 続いて、図 8 の (b) 部に示すように、ドライエッティングの後に純水などによる洗浄処理を実行する。このとき、コンタクト孔 110a, 109a の内部には、水滴 500 が入り込むことがある。

[01 30] 図 8 の (b) 部に示すように、コンタクト孔 110a, 109a の内部に水滴 500 が入り込んだ場合にあっても、本実施例に係る製造方法では、エ

アーフローによりコンタクト孔 110 a, 109 a の内部の水滴 500 についても除去することができる。これは、図 8 の (a) 部に示したように、オーバーエッチング処理の実行により、平坦化層 110 およびパッシベーション層 109 のコンタクト孔 110 a, 109 a を臨む内壁面がフッ化膜 121 で被覆されることによるものである。よって、本実施例に係る製造方法では、上部電極 108 におけるコンタクト孔 110 a, 109 a の底に露出する表面 108 c への水滴の残留を防ぐことができる。

[0131] 従つて、本実施例に係る製造方法では、上部電極 108 の表面 108 c に金属酸化膜が形成されることが抑制され、アノード 111 との良好なコンタクトをとることができます。

[0132] (比較例)

一方、図 9 の (a) 部に示すように、層間絶縁層 807 および上部電極 808 が順に積層され、その上に積層されたパッシベーション層 8091 および平坦化層 810 にコンタクト孔 810 a, 8091 a を開設する。比較例においても、平坦化層 810 へのコンタクト孔 810 a の開設にはリソグラフィを用い、パッシベーション層 8091 へのコンタクト孔 8091 a の開設にはドライエッチングを用いる。

[0133] 比較例に係る製造方法では、コンタクト孔 810 a, 8091 a の底に上部電極 808 の表面 808 a が露出した時点でエッチングを終了する。二点鎖線で囲んだ部分に示すように、エッチングの終了時においては、平坦化層 810 におけるコンタクト孔 810 a を臨む内壁面はフッ化膜 820 で被覆されているが、パッシベーション層 8091 におけるコンタクト孔 8091 a を臨む内壁面には、殆どフッ化膜は積層されていない状態である。

[0134] 続いて、図 9 の (b) 部に示すように、純水などを用い洗浄を行う。この際には、上記実施例と同様に、コンタクト孔 810 a, 8091 a の内部に水滴 500 が入り込むことがある。

[0135] 次に、図 9 の (c) 部に示すように、エアープローを行うことで水滴を除去しようとするのであるが、コンタクト孔 8091 a の底部分に水滴の一部

501が残留することがある。これは、図9の(a)部における二点鎖線で囲んだ部分に示すように、パッシベーション層8091におけるコンタクト孔8091aを臨む内壁面がフッ化膜で覆われていないことによるものである。即ち、パッシベーション層8091におけるコンタクト孔8091aを臨む内壁面は、撥液性が弱く、このため、コンタクト孔8091aの底部分に入り込んだ水滴の一部501が除去されにくし。

[0136] このようにコンタクト孔8091aの内部の水滴500を除去しきれず、水滴の一部501が残留した状態(濡れた状態)では、図9の(d)部に示すように、コンタクト孔810a, 8091aの底において上部電極808の表面に金属酸化膜822が被覆されるに至る。よって、比較例に係る製造方法では、上部電極808とアノードとの良好なコンタクトをとれないことになる。

[0137] 4. コンタクト孔を臨む周囲の状態

上記実施例に係る製造方法を用いてコンタクト孔を開設した場合と、比較例に係る製造方法を用いてコンタクト孔を開設した場合について、コンタクト孔を臨む周囲の状態を説明する。

[0138] (実施例)

上記実施例に係る製造方法を用いコンタクト孔を開設した場合には、図10(a)に示すように、コンタクト孔の底に露出する上部電極108の表面108cには金属酸化膜が被覆されていることはない。図10(b)に示すように、断面を見ても、コンタクト孔110a, 109aの底には、上部電極108の表面108cが露出し、金属酸化膜の被覆はない。

[0139] (比較例)

一方、図10(c)に示すように、比較例に係る製造方法を用いコンタクト孔を開設した場合には、コンタクト孔の底に露出する上部電極808の表面808bの一部(コンタクト孔の内縁に近い部分)の上に金属酸化膜(CuO<sub>x</sub>膜)が形成されている。図10(d)に示すように、断面を見ても、コンタクト孔の底には、上部電極808の表面808bの一部を被覆するよう

に金属酸化膜 (CuO<sub>x</sub>膜) 822 が形成されている。

- [0140] 以上の結果からも、実施例に係る製造方法を用いれば、上部電極 108 とアノード 111との間の良好なコンタクトを確保することができる。

#### 4. 上部電極 108 の表面のフッ化膜 121 による被覆

上記のように、上記実施の形態に係る製造方法では、コンタクト孔 109a の開設工程において、オーバーエッチングを実行することで、上部電極 108 の表面もフッ化膜 121 で被覆されることになる (図 8 の二点鎖線で囲んだ部分を参照)。このため、上部電極 108 とアノード 111 とのコンタクトの観点から、間に介挿されることになるフッ化膜 121 について検討した。

- [0141] 先ず、図 11 に示すように、コンタクト孔 109a の底においては、上部電極 108 の表面 108a には OLF<sub>2</sub> や CuF OH が形成されていることが推定できる。

- [0142] 次に、図 12 (a) に示すように、コンタクト孔 109a の底において、上部電極 108 とアノード 111 との間に介挿されるフッ化膜 121 の膜厚 t<sub>F</sub> が 3 [nm] 以下 (例えば、2 ~ 3 nm) となるように抑えれば、上部電極 108 とアノード 111 との間の良好なコンタクトを確保するうえで問題を生じないと考えられる。換言すると、オーバーエッチングの時間 T<sub>1</sub> については、膜厚 t<sub>F</sub> が 3 [nm] 以下となるように抑えることができる時間とすることが好ましいといえる。

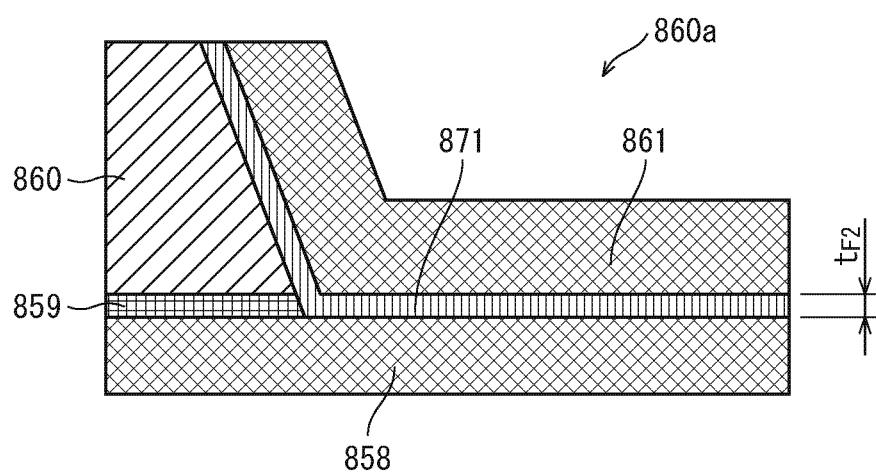

- [0143] 一方、図 12 (b) に示すように、オーバーエッチングの時間を長くしすぎると、平坦化層 860 およびパッシベーション層 859 におけるコンタクト孔 860a を臨む内壁面を被覆するフッ化膜 871 の膜厚は厚くなる。このため、上部電極 858 の表面への金属酸化膜の形成を抑制するという観点からは好ましい。

- [0144] しかしながら、図 12 (b) に示すように、上部電極 858 とアノード 861 との間に介挿されるフッ化膜 871 の膜厚 t<sub>F2</sub> が 3 [nm] を超えてしまうと、フッ化膜 871 の介在により上部電極 858 とアノード 861 との間

の良好なコンタクトをとることが困難となる。

[0145] 以上より、オーバーエッチングの時間については、上部電極 108 の上に形成されるフッ化膜 121 の膜厚レガ3 [nm] を超えない時間とすることが好ましい。

[0146] [変形例]

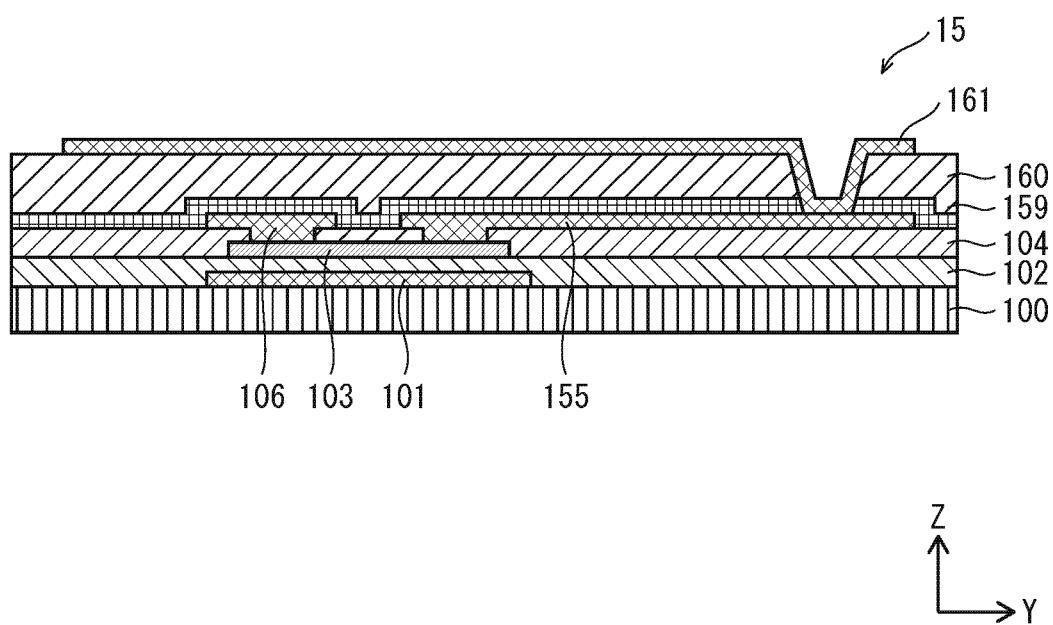

変形例に係る表示パネル 15 の構成について、図 13 を用い説明する。図 13 では、表示パネル 15 の一部構成だけを抜き出して図示している。また、図 13 においては、上記実施の形態と同じ構成部分には同一の符号を付している。

[0147] 図 13 に示すように、表示パネル 15 においては、TFT 層のソース電極 155 およびドレイン電極 106 の上を被覆するように、パッシベーション層 159 および平坦化層 160 が積層形成されている。即ち、本変形例では、ソース電極 155 とアノード 161 とが、間に上部電極を介することなく接続されている。

[0148] 本変形例に係る表示パネル 15 の製造過程でも、パッシベーション層 159 および平坦化層 160 を積層形成した後に、ソース電極 155 上の一部を露出させるコンタクト孔を開設し、その後にアノード 161 を形成する。そして、コンタクト孔の開設にあたっては、上記実施の形態と同様にオーバーエッチング処理を行い、パッシベーション層 159 および平坦化層 160 におけるコンタクト孔を臨む内壁面をフッ化膜で被覆する。これにより、コンタクト孔の底に露出するソース電極 155 の表面への金属酸化膜の形成を抑制することができる。

[0149] 従って、本変形例においても、ソース電極 155 とアノード 161 との間に良好なコンタクトをとることができる。

[0150] [その他の事項]

上記実施の形態および変形例では、SiNからなるパッシベーション層 109, 159 を採用したが、本発明は、これに限定を受けない。フッ素系のガスでドライエッチング可能な材質の層であれば採用することが可能である

。そして、複数の層を積層してなるパッジベーション層を採用することもできる。

[0151] また、上記実施の形態および変形例では、各電極材料にCuを含む金属材料を採用することとしたが、本発明は、電極材料をこれに限定するものではない。例えば、Cuの他に、アルミニウム(Al)、モリブデン(Mo)、タンクスチン(W)、チタン(Ti)などを採用することもできる。この場合にも、金属酸化膜の形成を抑制するという観点から、上記実施の形態および変形例と同様の製造方法を採用することが好ましい。

[0152] また、上記実施の形態および変形例では、コンタクト孔110a, 109aの開設後における洗浄に、純水を用いたが、本発明はこれに限定されるものではない。水を含む洗浄液を用いることができる。ただし、平坦化層110, 160にポリイミドなどの樹脂層を採用する場合においては、有機洗浄液を用いることは避けることが好ましい。洗浄時における平坦化層110, 160への洗浄液の影響を避けるためである。

[0153] また、上記実施の形態および変形例では、表示素子部の構成として、TFT層の側にアノード111, 161を配し、有機発光機能層113を挟んだ上方にカソード114を配する構成を採用したが、アノードとカソードの位置が逆転してもよい。

[0154] また、上記実施の形態および変形例では、表示パネル10, 15として有機EL表示パネルを一例として採用したが、本発明はこれに限定されるものではない。例えば、無機EL表示パネルや電界放出(FE)表示パネル、さらには液晶(LC)表示パネルなどを採用することもできる。

[0155] また、上記実施の形態および変形例では、エアープローについて、一例として、30 [mm/sec.] ~ 70 [mm/sec.] の相対速度(エアープローのノズルと基板との相対速度)を以ってドライエアーを吹き付けることとした。エアープローの温度条件などを含む各条件については、本発明の効果を得る上であまり大きく影響しないと考えられる。

[0156] また、上記実施の形態および変形例では、コンタクト孔に対する洗浄およ

びエアープローを実行することとしたが、これらは必須の要件ではない。洗浄を行わない場合においても、コンタクト孔を臨む内壁面および底に露出する上部電極等に対しては、構成中の水分や、環境中に含まれる水分などが付着することが考えられるが、本発明に係る方法を採用すれば、これらの水分による上部電極表面への酸化被膜の形成を効果的に抑制することができ、TFT層の上部電極と表示素子部のアノードなどとの良好なコンタクトをとることができること。

[01 57] また、上記変形例では、ソース電極 155 とアノード 161 を接続することとしたが、デバイス構造によってはドレイン電極 106 とアノードとを接続する構成を採用することも適宜可能である。

[01 58] また、上記実施の形態および変形例では、オーバーエッチング処理を行うことにより、パッシベーション層 109, 159 におけるコンタクト孔 109a を臨む内壁面をフッ化膜 121 で被覆することとしたが、本発明は、フッ化膜の形成をこれに限定するものではない。例えば、フッ素系のガスを別にコンタクト孔 110a, 109a の内部に充填するようにしてもよい。ただし、上記実施の形態および変形例のように、オーバーエッチング処理の実行によりフッ化膜 121 を形成することとすれば、別途の製造工程を追加する必要がなく、生産効率という観点から優れる。

[01 59] また、上記実施の形態および変形例では、平坦化層 110, 160 へのコンタクト孔の開設にリソグラフィを用いたが、本発明はこれに限定されるものではない。例えば、ドライエッチングやウエットエッチングを用いてもよい。

### 産業上の利用可能性

[01 60] 本発明は、優れた表示品質を有するアクティブマトリクス型表示装置を実現するのに有用である。

### 符号の説明

[01 61] 1. 表示装置

10、15. 表示パネル

20. 駆動・制御回路部

21～24. 駆動回路

25. 制御回路

100, 119. 基板

101. ゲート電極

102. ゲート絶縁層

103. チャネル層

104, 1040. チャネル保護層

105, 155. ソース電極

106. ドレイン電極

107, 1070. 層間絶縁層

108. 上部電極

109, 159, 1090, 1091. パッシベーション層

109a. コンタクト下孔

110, 160, 1100. 平坦化層

110a. コンタクト上孔

111, 161. アノード

112. バンク

113. 有機発光機能層

114. カソード

115. 封止層

116. 樹脂層

117. カラーフィルタ層

118. ブラックマトリクス層

120, 121. フッ化膜

500. 水滴

## 請求の範囲

- [請求項 1] 基板上に TFT 層を形成する工程と、

前記 TFT 層上に平坦化層を形成する工程と、

前記平坦化層上に表示素子部を形成する工程と、

を備え、

前記 TFT 層を形成する工程には、ソース電極もしくはドレイン電極、またはその一方の電極に接続された接続用電極の何れかの電極を被覆するパッシベーション層を、前記平坦化層と境界を接する状態で形成するサブ工程が含まれ、

前記表示素子部を形成する工程には、前記平坦化層と境界を接する状態で下部電極を形成するサブ工程が含まれ、

前記何れかの電極と前記下部電極との接続は、

底部に前記パッシベーション層の表面が露出するまで、前記平坦化層にコンタクト孔を開設し、

前記平坦化層のコンタクト孔の底部に露出するパッシベーション層に対して、フッ素を含むガスを用いたドライエッチングにより、前記平坦化層のコンタクト孔に連通し、底部に前記何れかの電極が露出するコンタクト孔を開設し、

前記コンタクト孔の底に前記何れかの電極が露出した後、前記パッシベーション層における前記コンタクト孔を臨む内壁面に対し、組成中にフッ素を含む撥液膜を形成し、

前記下部電極を形成するサブ工程で、前記コンタクト孔を臨む前記平坦化層および前記パッシベーション層の内壁面に沿って、前記下部電極を形成することによりなされる

ことを特徴とするアクティブマトリクス型表示パネルの製造方法。

前記撥液膜の形成は、前記コンタクト孔の底に前記何れかの電極の表面が露出した後、さらに前記パッシベーション層における前記コン

タクト孔を臨む内壁面を前記ガスに晒すことにより行われる

請求項 1 記載のアクティブマトリクス型表示パネルの製造方法。

[請求項3] 前記コンタクト孔の開設を開始してから、前記コンタクト孔の底に前記何れかの電極の表面が露出するまでの時間を  $T_0$  とし、

前記撥液膜の形成のために、前記パッシベーション層における前記コンタクト孔を臨む内壁面を前記ガスに晒す時間を  $T_1$  とするとき、

$$70\% \times T_0 \leq T_1 \leq 150\% \times T_0$$

の関係を満たす

請求項 2 記載のアクティブマトリクス型表示パネルの製造方法。

[請求項4] 前記撥液膜の形成後においては、前記コンタクト孔の底に露出する前記何れかの電極の表面に、フッ素を含む電極被膜が形成されてなり、

前記前記撥液膜の形成のために、前記パッシベーション層における前記コンタクト孔を臨む内壁面を前記ガスに晒す時間  $T_1$  は、前記電極被膜の膜厚が 3 nm 以下となるように規定されている

請求項 2 記載のアクティブマトリクス型表示パネルの製造方法。

[請求項5] 前記組成中にフッ素を含む撥液膜の形成後であつて、前記下部電極の形成前において、

前記コンタクト孔内を含む前記平坦化層および前記パッシベーション層の表面を水を含む洗浄液で洗浄し、

前記コンタクト孔内を含む前記平坦化層および前記パッシベーション層の表面に対し、エアーまたはガスを吹き付けて、前記コンタクト孔内を含む前記平坦化層および前記パッシベーション層の表面に残る前記洗浄液を除去する

請求項 1 記載のアクティブマトリクス型表示パネルの製造方法。

[請求項6] 前記何れかの電極は、銅もしくは銅合金を用い形成されている

請求項 1 記載のアクティブマトリクス型表示パネルの製造方法。

[請求項7] 基板上に、TFT 層、平坦化層、および表示素子部がこの順に形

成されてなるアクティブマトリクス型表示パネルであつて、

前記 TFT 層には、ソース電極もしくはドレイン電極、またはその一方の電極に接続された接続用電極の何れかの電極と、当該何れかの電極を被覆し、前記平坦化層を境界を接するパッシベーション層とが含まれております、

前記表示素子部には、前記平坦化層と境界を接する状態で形成されてなる下部電極が含まれ、

前記下部電極は、前記平坦化層および前記パッシベーション層を連続して貫通するコンタクト孔を通じ、前記平坦化層および前記パッシベーション層における前記コンタクト孔を臨む内壁面に沿って一部が形成されることにより、前記コンタクト孔の底で前記何れかの電極に対して電気的に接続されており、

前記平坦化層および前記パッシベーション層における前記コンタクト孔を臨む内壁面と、前記下部電極との間には、フッ素を含む膜が介挿されており、

前記コンタクト孔の底において、前記下部電極と前記何れかの電極との間には、フッ素を含む電極被膜が介挿されていることを特徴とするアクティブマトリクス型表示パネル。

[請求項 8] 前記電極被膜の膜厚は、3 nm 以下である

請求項 7 記載のアクティブマトリクス型表示パネル。

[図1]

[図2]

[図3]

[図4]

[図5]

(a)

(b)

(c)

[図6]

(a)

(b)

[図7]

[図8]

[図9]

[図10]

[図11]

[図12]

(a)

(b)

[図13]

[図14]

## INTERNATIONAL

## SEARCH REPORT

International application No.

PCT / JP2 015/002895

## A. CLASSIFICATION OF SUBJECT MATTER

G09F9/00 (2006.01)i, G09F9/30 (2006.01)i, H01L21/768 (2006.01)i, H01L51/50 (2006.01)i, H05B33/04 (2006.01)i, H05B33/10 (2006.01)i, H05B33/14 (2006.01)i, ^A05.833/22 (2006.01)i, H05B33/26 (2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G 0 9 F 9 / 0 0 - 9 / 4 6 , H 0 1 L 2 1 / 3 2 0 5 - 2 1 / 3 2 1 3 , 2 1 / 7 6 8 , 2 3 / 5 2 2 , 2 3 / 5 3 2 , 2 7 / 3 2 , 5 1 / 5 0 , H 0 5 B 3 3 / 0 0 - 3 3 / 2 8

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

|         |         |        |           |           |        |         |        |           |           |

|---------|---------|--------|-----------|-----------|--------|---------|--------|-----------|-----------|

| Jitsuyo | Shinan  | Koho   | 1922-1996 | Jitsuyo   | Shinan | Toroku  | Koho   | 1996-2015 |           |

| Kokai   | Jitsuyo | Shinan | Koho      | 1971-2015 | Toroku | Jitsuyo | Shinan | Koho      | 1994-2015 |

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                              | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | U S 2 0 0 2 / 0 1 9 0 2 5 3 A I ( T a k a t o s h i T SUJIMURA e l a l . ) ,<br>1 9 D e c e m b e r 2 0 0 2 ( 1 9 . 1 2 . 2 0 0 2 ) ,<br>ent ire text ; a l l drawings<br>& U S 2 0 0 3 / 0 1 9 7 1 8 0 A I & T W 5 4 8 7 3 8 B | 1-8                   |

| A         | W O 2 0 1 0 / 0 2 4 0 3 5 A I ( Sharp Corp . ) ,<br>0 4 March 2 0 1 0 ( 0 4 . 0 3 . 2 0 1 0 ) ,<br>ent ire text ; a l l drawings<br>& U S 2 0 1 1 / 0 1 5 7 5 2 6 A I & C N 1 0 2 1 1 2 9 1 3 A                                 | 1-8                   |

| A         | J P 2 0 0 2 - 2 5 0 9 3 4 A ( Sharp Corp . ) ,<br>0 6 September 2 0 0 2 ( 0 6 . 0 9 . 2 0 0 2 ) ;,<br>ent ire text ; a l l drawings<br>( Family : none )                                                                        | 1-8                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents:

"A" document defining the general state of the art which is not considered to be of particular relevance

"E" earlier application or patent but published on or after the international filing date

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"O" document referring to an oral disclosure, use, exhibition or other means

"P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

21 Augus t 2015 (21.08.15)

Date of mailing of the international search report

01 September 2015 (01.09.15)

Name and mailing address of the ISA/

Japan Patent Offi c e

3 - 4 - 3 , Kasumigas eki , Chiyoda- ku ,

Tokyo 1 0 0 - 8 9 1 5 , Japan

Authorized officer

Telephone No.

## INTERNATIONAL SEARCH REPORT

International application No.

PCT / JP2 015 / 002895

## C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                  | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | JP 2002- 098994 A (Sharp Corp .),<br>05 April 2002 (05.04.2002),<br>entire text ; all drawings<br>(Family : none )                                                                                                                                                  | 1-8                   |

| A         | JP 2005- 328037 A (Semiconductor Energy Laboratory Co., Ltd .),<br>24 November 2005 (24.11.2005),<br>entire text ; all drawings<br>6 US 2005/0214688 A1                                                                                                             | 1.- 8                 |

| A         | WO 2013/ 108598 A1 (Panasonic Corp .),<br>25 July 2013 (25.07.2013),<br>entire text ; all drawings<br>& US 2015/0001517 A1 & CN 104081879 A                                                                                                                         | 1- 8                  |

| A         | JP 2004- 318063 A (Fujitsu Display Technologies Corp .),<br>11 November 2004 (11.11.2004),<br>entire text ; all drawings<br>& JP 2009-276788 A & US 2004/0246424 A1<br>& US 2006/0114393 A1 & TW 200424727 A<br>& KR 10-0814183 B1 & CN 1534362 A<br>& CN 1955804 A | 1-8                   |

| A         | JP 2008- 020572 A (Seiko Epson Corp .),<br>31 January 2008 (31.01.2008),<br>entire text ; all drawings<br>& US 2008/0012022 A1                                                                                                                                      | 1-8                   |

## A. 発明の属する分野の分類 (国際特許分類 (IPC))

Int.Cl. G09F9/00 (2006. 01) i, G09F9/30 (2006. 01) i, H01L2 1/768 (2006. 01) i, H01L5 1/50 (2006. 01) i, H05B33/04 (2006. 01) i, H05B33/10 (2006. 01) i, H05B33/14 (2006. 01) i, H05B33/22 (2006. 01) i, H05B33/26 (2006. 01) i

## B. — 調査を行った分野

## 調査を行った最小限資料 (国際特許分類 (IPC))

Int.Cl. G09F9/00-9/46, H01L2 1/3205-21/3213, 21/768, 23/522, 23/532, 27/32, 51/50, H05B33/00-33/28

## 最小限資料以外の資料で調査を行った分野に含まれるもの

|             |        |

|-------------|--------|

| 日本国実用新案公報   | 1922-  |

| 日本国公開実用新案公報 | 1971-2 |

| 日本国実用新案登録公報 | 1996-  |

| 日本国登録実用新案公報 | 1994-2 |

国際調査で使用した電子データベース (データベースの名称、調査に使用した用語)

6年

## C. 関連すると認められる文献

| 引用文献の<br>カテゴリー* | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                             | 関連する<br>請求項の番号 |

|-----------------|---------------------------------------------------------------------------------------------------------------|----------------|

| A               | US 2002/0190253 AI (TSUJIMURA, Takatoshi et al.)<br>2002. 12. 19, 全文、全図<br>& US 2003/0197180 AI & TW 548738 B | 1-8            |

| A               | WO 2010/024035 AI (シャープ株式会社)<br>2010. 03. 04, 全文、全図<br>& US 2011/0157526 AI & CN 102112913 A                  | 1-8            |

c 欄の続きにも文献が列挙されている。

パテントファミリーに関する別紙を参照。

## \* 引用文献のカテゴリー

- 「」特に関連のある文献ではなく、一般的技術水準を示すもの

- 「」国際出願日前の出願または特許であるが、国際出願日以後に公表されたもの

- 「」優先権主張に疑義を提起する文献又は他の文献の発行日若しくは他の特別な理由を確立するために引用する文献(理由を付す)

- 「」口頭による開示、使用、展示等に言及する文献

- 「」国際出願日前で、かつ優先権の主張の基礎となる出願

## の日の後に公表された文献

- 「」国際出願日又は優先日後に公表された文献であって出願と矛盾するものではなく、発明の原理又は理論の理解のために引用するもの

- 「」特に関連のある文献であって、当該文献のみで発明の新規性又は進歩性がないと考えられるもの

- 「」特に関連のある文献であって、当該文献と他の1以上の文献との、当業者にとって自明である組合せによって進歩性がないと考えられるもの

- 「」同一パテントファミリー文献

|                                                                           |                                                                   |

|---------------------------------------------------------------------------|-------------------------------------------------------------------|

| 国際調査を完了した日<br>21. 08. 2015                                                | 国際調査報告の発送日<br>01. 09. 2015                                        |

| 国際調査機関の名称及びあて先<br>日本国特許庁 (ISA / JP)<br>郵便番号 100-8915<br>東京都千代田区霞が関三丁目4番3号 | 特許庁審査官 (権限のある職員)<br>21 4744<br>請園 信博<br>電話番号 03-3581-1101 内線 3272 |

| C(続き) . 関連すると認められる文献 |                                                                                                                                                                                                        |                |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 引用文献の<br>カテゴリー*      | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                                                                                      | 関連する<br>請求項の番号 |

| A                    | JP 2002-250934 A (シャープ株式会社)<br>2002. 09. 06, 全文、全図<br>(ファミリーなし)                                                                                                                                        | 1-8            |

| A                    | JP 2002-098994 A (シャープ株式会社)<br>2002. 04. 05, 全文、全図<br>(ファミリーなし)                                                                                                                                        | 1-8            |

| A                    | JP 2005-328037 A (株式会社半導体エネルギー研究所)<br>2005. 11. 24, 全文、全図<br>& US 2005/0214688 AI                                                                                                                      | 1-8            |

| A                    | WO 2013/108598 AI (パナソニック株式会社)<br>2013. 07. 25, 全文、全図<br>& US 2015/0001517 AI & CN 104081879 A                                                                                                         | 1-8            |

| A                    | JP 2004-318063 A (富士通ディスプレイテクノロジーズ株式会社)<br>2004. 11. 11, 全文、全図<br>& JP 2009-276788 A & US 2004/0246424 AI & US 2006/0114393 AI<br>& TW 200424727 A & KR 10-0814183 BI & CN 1534362 A<br>& CN 1955804 A | 1-8            |

| A                    | JP 2008-020572 A (セイコーエプソン株式会社)<br>2008. 01. 31, 全文、全図<br>& US 2008/0012022 AI                                                                                                                         | 1-8            |