(12)

## Veröffentlichung

der internationalen Anmeldung mit der

(87) Veröffentlichungs-Nr.: **WO 2018/220470**

in der deutschen Übersetzung (Art. III § 8 Abs. 2

IntPatÜG)

(21) Deutsches Aktenzeichen: **11 2018 002 796.1**

(86) PCT-Aktenzeichen: **PCT/IB2018/053590**

(86) PCT-Anmeldetag: **22.05.2018**

(87) PCT-Veröffentlichungstag: **06.12.2018**

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: **19.03.2020**

(51) Int Cl.: **H03K 5/08 (2006.01)**

**H01L 21/8239 (2006.01)**

**H01L 21/8242 (2006.01)**

**H01L 21/8244 (2006.01)**

**H01L 27/105 (2006.01)**

**H01L 27/108 (2006.01)**

**H01L 27/11 (2006.01)**

**H01L 29/786 (2006.01)**

**H02M 3/07 (2006.01)**

(30) Unionspriorität:

**2017-107964** 31.05.2017 JP

(74) Vertreter:

**GLAWE DELFS MOLL Partnerschaft mbB von

Patent- und Rechtsanwälten, 20148 Hamburg, DE**

(72) Erfinder:

**Matsuzaki, Takanori, Atsugi-shi, Kanagawa, JP;

Kato, Kiyoshi, Atsugi-shi, Kanagawa, JP**

**Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen.**

(54) Bezeichnung: **Vergleichsschaltung, Halbleitervorrichtung, elektronische Komponente und elektronisches Gerät**

(57) Zusammenfassung: Eine Vergleichsschaltung, in die eine zu vergleichende negative Spannung direkt eingegeben werden kann, wird bereitgestellt. Die Vergleichsschaltung beinhaltet einen ersten Eingangsanschluss, einen zweiten Eingangsanschluss, einen ersten Ausgangsanschluss und ein Differenzpaar. Die Vergleichsschaltung vergleicht eine negative Spannung und eine negative Bezugsspannung und gibt in Reaktion auf das Vergleichsergebnis von dem ersten Ausgangsanschluss eine erste Ausgangsspannung aus. Die negative Spannung wird in den ersten Eingangsanschluss eingegeben. Eine positive Bezugsspannung wird in den zweiten Eingangsanschluss eingegeben. Die positive Bezugsspannung wird derart bestimmt, dass ein Vergleich durchgeführt wird. Das Differenzpaar beinhaltet einen ersten n-Kanal-Transistor und einen zweiten n-Kanal-Transistor, die jeweils ein Gate und ein Rückgate aufweisen. Der erste Eingangsanschluss ist elektrisch mit dem Rückgate des ersten n-Kanal-Transistors verbunden. Der zweite Eingangsanschluss ist elektrisch mit dem Gate des zweiten n-Kanal-Transistors verbunden.

**Beschreibung**

## Technisches Gebiet

**[0001]** Eine Ausführungsform der vorliegenden Erfindung, die in der Beschreibung, den Zeichnungen und dem Schutzbereich der Ansprüche dieser Anmeldung (nachstehend als diese Beschreibung und dergleichen bezeichnet) offenbart ist, betrifft eine Halbleitervorrichtung, ein Betriebsverfahren dafür, ein Verwendungsverfahren dafür, ein Herstellungsverfahren dafür und dergleichen. Es sei angemerkt, dass eine Ausführungsform der vorliegenden Erfindung nicht auf das vorstehende technische Gebiet beschränkt ist.

## Stand der Technik

**[0002]** Eine Halbleitervorrichtung, bei der eine negative Spannung verwendet wird, ist bekannt. Beispielsweise ist, um einen unterschwelligen Leckstrom zu verringern, eine Substratvorspannung in einem n-Kanal-MOS-Transistor eine negative Spannung, während eine Substratvorspannung in einem p-Kanal-MOS-Transistor eine positive Spannung ist (z. B. Patentdokument 1). Bei einem Flash-Speicher wird je nach dem Betrieb eine negative Spannung verwendet (z. B. Patentdokument 2).

**[0003]** Ein negatives Potential kann durch eine Ladungspumpenschaltung erzeugt werden. Patentdokumente 2 und 3 offenbaren eine Technik zum Erzeugen von negativen Potentialen mit hoher Genauigkeit. In Patentdokumenten 2 und 3 wird eine negative Spannung, die von einer Ladungspumpenschaltung ausgegeben wird, in eine positive Spannung umgewandelt, die Differenz zwischen der positiven Spannung und einer positiven Bezugsspannung wird durch eine Vergleichsschaltung erkannt, und der Betrieb der Ladungspumpenschaltung wird auf Basis der Erkennungsergebnisse gesteuert.

**[0004]** Es sei angemerkt, dass die Erdspannung (**GND**) in dieser Beschreibung und der gleichen als 0 V angenommen wird, und die positive Spannung und die negative Spannung werden auf Basis der Erdspannung definiert.

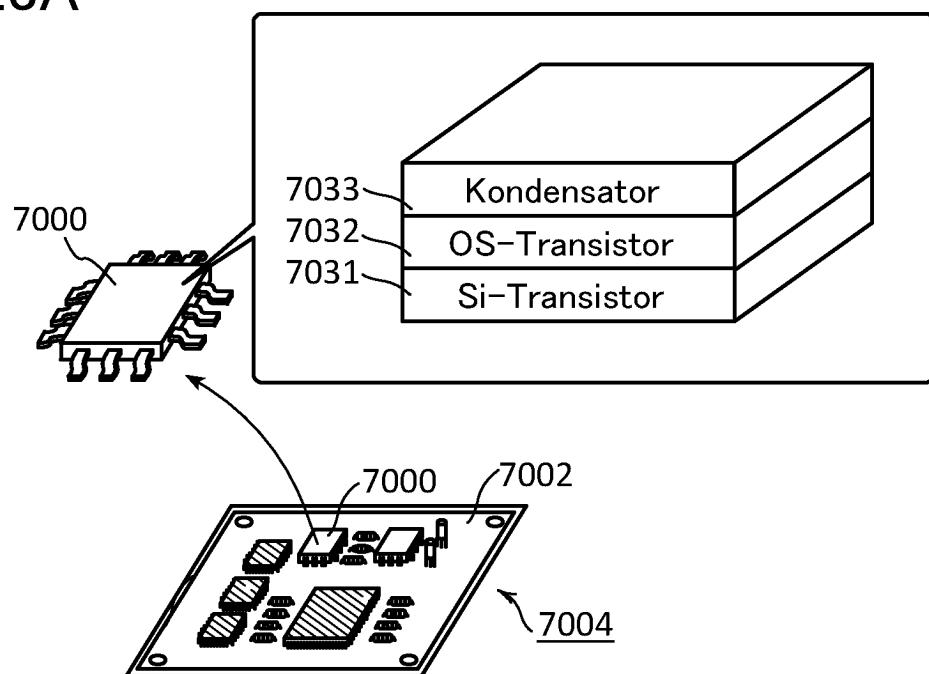

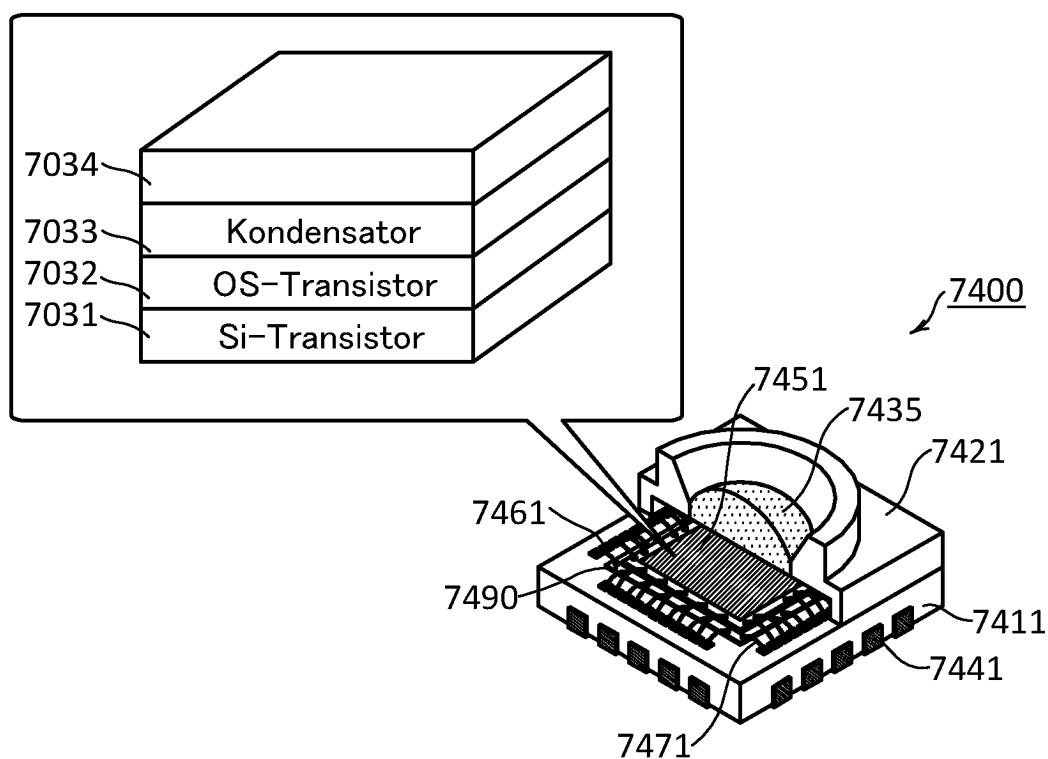

**[0005]** Ein Transistor, der ein Metalloxid in einem Kanalbildungsbereich enthält (nachstehend kann ein derartiger Transistor als Oxidhalbleitertransistor oder als OS-Transistor bezeichnet werden), ist bekannt. Verschiedene Halbleitervorrichtungen sind unter Verwendung eines Hybrid-CMOS-Prozesses für einen OS-Transistor und einen Si-Transistor hergestellt worden (z. B. Nichtpatentdokument 1). Wie in Nichtpatentdokument 1 offenbart, kann ein OS-Transistor über einem Si-Transistor angeordnet werden.

**[0006]** Ein Si-Transistor kann durch Einführen der Verunreinigung die Schwellenspannung (nachstehend in einigen Fällen als  $V_t$  bezeichnet) steuern. Eine zuverlässige Technik zum Steuern der Schwellenspannung eines OS-Transistors ist jedoch noch nicht geschafft worden. In Patentdokument 4 wird beispielsweise die Schwellenspannung eines OS-Transistors, der eine erste Gate-Elektrode (auch als Gate oder Vordergate bezeichnet) und eine zweite Gate-Elektrode (auch als Rückgate bezeichnet) beinhaltet, durch Steuern der Spannung der zweiten Gate-Elektrode gesteuert. Die Schwellenspannung des OS-Transistors, der ein n-Kanal-Transistor ist, verschiebt sich positiv, wenn eine negative Spannung in die zweite Gate-Elektrode eingegeben wird.

## [Referenzen]

## [Patentdokumente]

[Patentdokument 1] Japanische Patentoffenlegungsschrift Nr. H11-191611

[Patentdokument 2] Japanische Patentoffenlegungsschrift Nr. H7-231647

[Patentdokument 3] Japanische Patentoffenlegungsschrift Nr. H11-150230

[Patentdokument 4] Japanische Patentoffenlegungsschrift Nr. 2012-069932

## [Nichtpatentdokument]

**[0007]** [Nichtpatentdokument 1] T. Onuki et al., „Embedded Memory and ARM Cortex-M0 Core Using 60-nm C-Axis Aligned Crystalline Indium-Gallium-Zinc Oxide FET Integrated with 65-nm Si CMOS (Embedded-Speicher und ARM Cortex-M0 Kern unter Verwendung eines 60 nm c-Axis Aligned Crystalline Indium-Gallium-Zink-Oxid-FET, der mit einem 65 nm Si-CMOS integriert ist),“ Symp. VLSI Circuits Dig. Tech. Papers, S. 124-125, Jun. 2016.

## Offenbarung der Erfindung

**[0008]** Aufgaben einer Ausführungsform der vorliegenden Erfindung sind, eine Vergleichsschaltung bereitzustellen, in die eine zu vergleichende negative Spannung direkt eingegeben werden kann, eine negative Spannung mit hoher Genauigkeit zu erzeugen, den Stromverbrauch zu verringern und dergleichen.

**[0009]** Es sei angemerkt, dass eine Ausführungsform der vorliegenden Erfindung nicht unbedingt alle vorstehend beschriebenen Aufgaben erfüllen muss. Die Beschreibung einer Vielzahl von Aufgaben schließt das Vorhandensein der einzelnen Aufgabe nicht aus. Weitere Aufgaben werden aus der Erläuterung dieser Beschreibung und dergleichen ersichtlich, und derartige Aufgaben könnten Aufgaben einer Ausführungsform der vorliegenden Erfindung sein.

(1) Eine Ausführungsform der vorliegenden Erfindung ist eine Vergleichsschaltung, die einen ersten Eingangsanschluss, einen zweiten Eingangsanschluss, einen ersten Ausgangsanschluss und eine Differenzeingangsschaltung beinhaltet. Die Vergleichsschaltung vergleicht eine negative Spannung und eine negative Bezugsspannung und gibt in Reaktion auf das Vergleichsergebnis von dem ersten Ausgangsanschluss eine erste Ausgangsspannung aus. Die negative Spannung wird in den ersten Eingangsanschluss eingegeben. Eine positive Bezugsspannung wird in den zweiten Eingangsanschluss eingegeben. Die positive Bezugsspannung wird derart bestimmt, dass ein Vergleich durchgeführt wird. Die Differenzeingangsschaltung beinhaltet ein Differenzpaar aus einem ersten n-Kanal-Transistor und einem zweiten n-Kanal-Transistor. Der erste n-Kanal-Transistor und der zweite n-Kanal-Transistor weisen jeweils ein Gate und ein Rückgate auf. Eine erste Vorspannung wird in das Gate des ersten n-Kanal-Transistors eingegeben. Der erste Eingangsanschluss ist elektrisch mit dem Rückgate des ersten n-Kanal-Transistors verbunden. Der zweite Eingangsanschluss ist elektrisch mit dem Gate des zweiten n-Kanal-Transistors verbunden. Eine zweite Vorspannung wird in das Rückgate des zweiten n-Kanal-Transistors eingegeben.

(2) Bei der Ausführungsform (1) enthält ein Kanalbildungsbereich sowohl des ersten n-Kanal-Transistors als auch des zweiten n-Kanal-Transistors ein Metalloxid.

(3) Die Vergleichsschaltung nach der Ausführungsform (1) oder (2) ist eine dynamische Vergleichsschaltung. Die Differenzeingangsschaltung beinhaltet eine Latch-Schaltung, die elektrisch mit dem Differenzpaar verbunden ist.

(4) Eine Ausführungsform der vorliegenden Erfindung ist eine Halbleitervorrichtung, die eine Abwärts-Ladungspumpenschaltung, eine Treiberschaltung und die Vergleichsschaltung nach einem der Ausführungsformen (1) bis (3) beinhaltet. Ein Ausgangsanschluss der Abwärts-Ladungspumpenschaltung ist elektrisch mit dem ersten Eingangsanschluss der Vergleichsschaltung verbunden. Die erste Ausgangsspannung wird von der Vergleichsschaltung in die Treiberschaltung eingegeben. Die Treiberschaltung erzeugt gemäß der ersten Ausgangsspannung ein Taktsignal zum Betreiben der Abwärts-Ladungspumpenschaltung.

**[0010]** Nach einer Ausführungsform der vorliegenden Erfindung kann eine Vergleichsschaltung, in die eine zu vergleichende negative Spannung direkt eingegeben werden kann, bereitgestellt werden. Des Weiteren kann eine negative Spannung mit hoher

Genauigkeit erzeugt werden. Außerdem kann der Stromverbrauch verringert werden.

**[0011]** Bei einer Ausführungsform der vorliegenden Erfindung muss man nicht notwendigerweise alle vorstehend beschriebenen Wirkungen erzielen. Die Beschreibung der Vielzahl von Wirkungen schließt das Vorhandensein weiterer Wirkungen nicht aus. Bei einer Ausführungsform der vorliegenden Erfindung sind eine andere Aufgabe als die vorstehenden Aufgaben, eine andere Wirkung als die vorstehenden Wirkungen und ein neuartiges Merkmal aus der Erläuterung der Beschreibung und der Zeichnungen ersichtlich.

#### Figurenliste

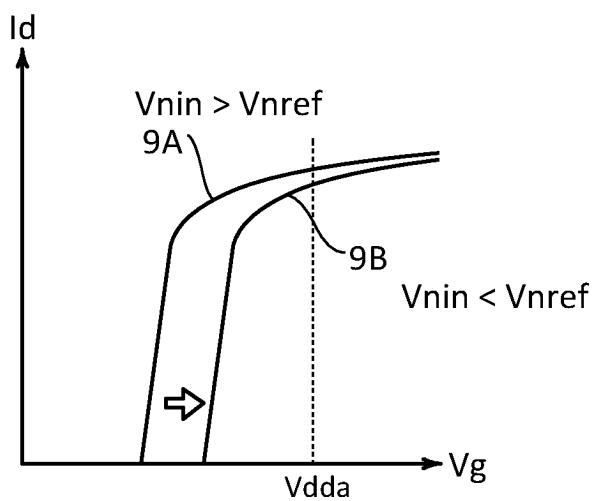

**Fig. 1A** und **Fig. 1B** sind Schaltpläne, die ein Konfigurationsbeispiel für eine Vergleichsschaltung darstellen, und **Fig. 1C** ist eine Darstellung, die Drain-Strom-Gate-Spannungs-Eigenschaften eines Transistors schematisch zeigt.

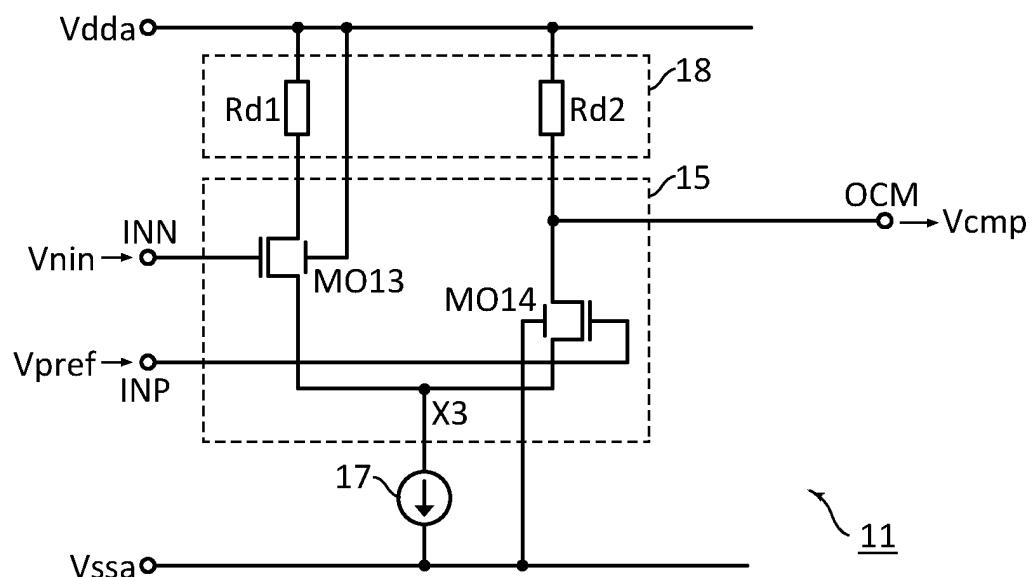

**Fig. 2** ist ein Schaltplan, der ein Konfigurationsbeispiel für eine Vergleichsschaltung darstellt.

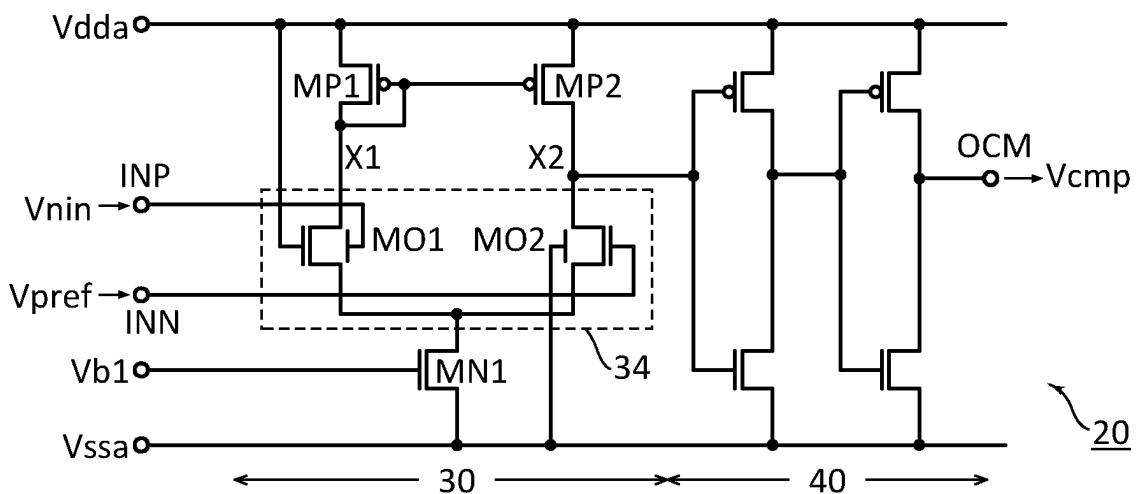

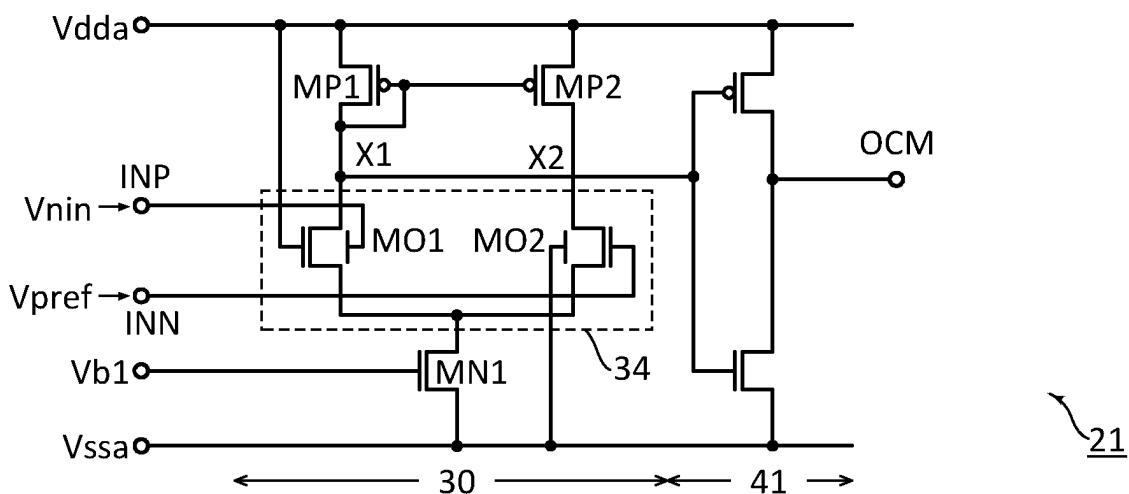

**Fig. 3A** und **Fig. 3B** sind Schaltpläne, die ein Konfigurationsbeispiel für eine Vergleichsschaltung darstellen.

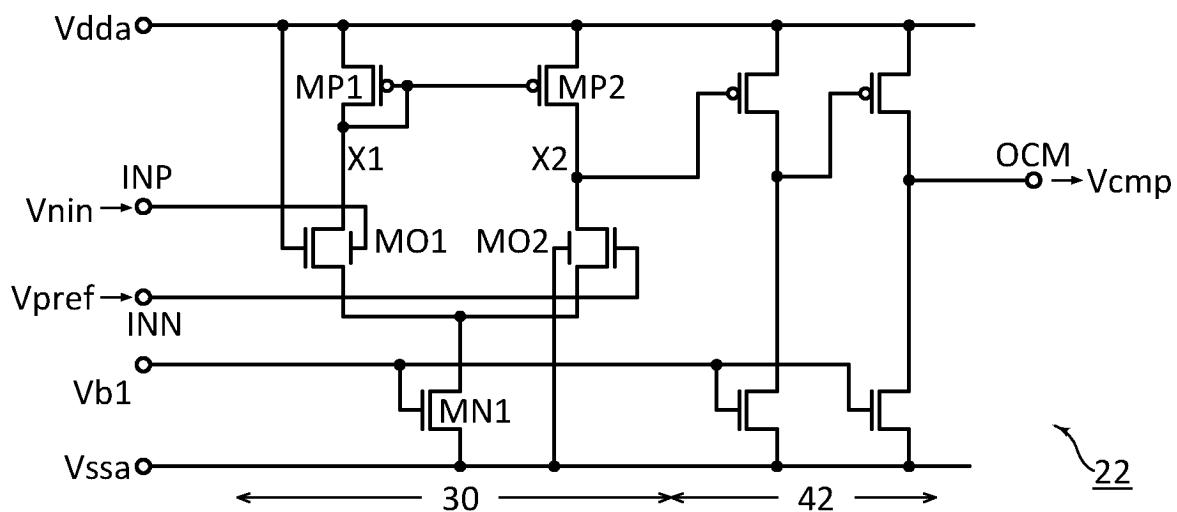

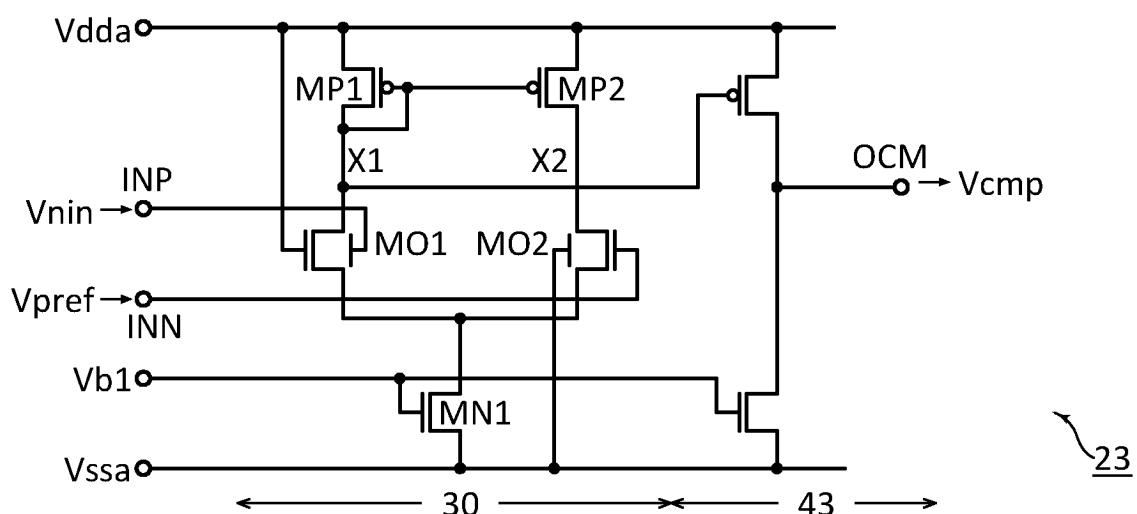

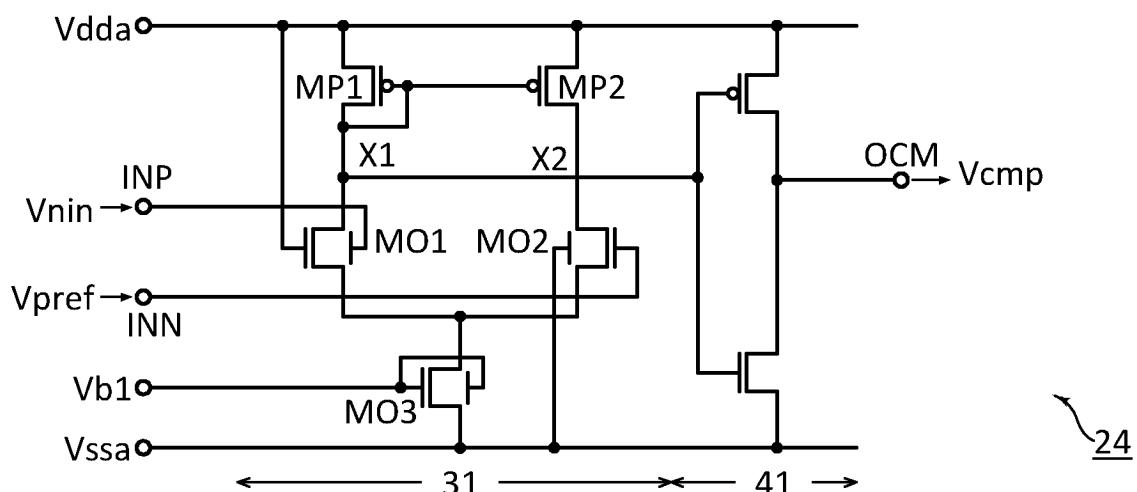

**Fig. 4A** bis **Fig. 4C** sind Schaltpläne, die jeweils ein Konfigurationsbeispiel für eine Vergleichsschaltung zeigen.

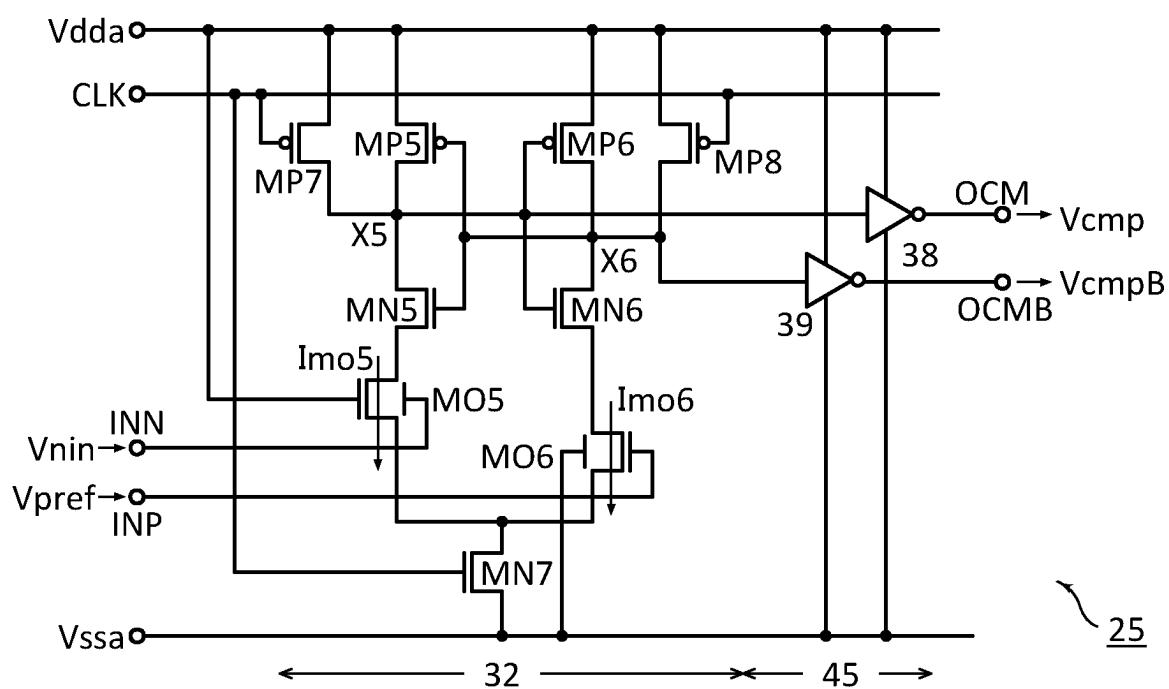

**Fig. 5** ist ein Schaltplan, der ein Konfigurationsbeispiel für eine Vergleichsschaltung darstellt.

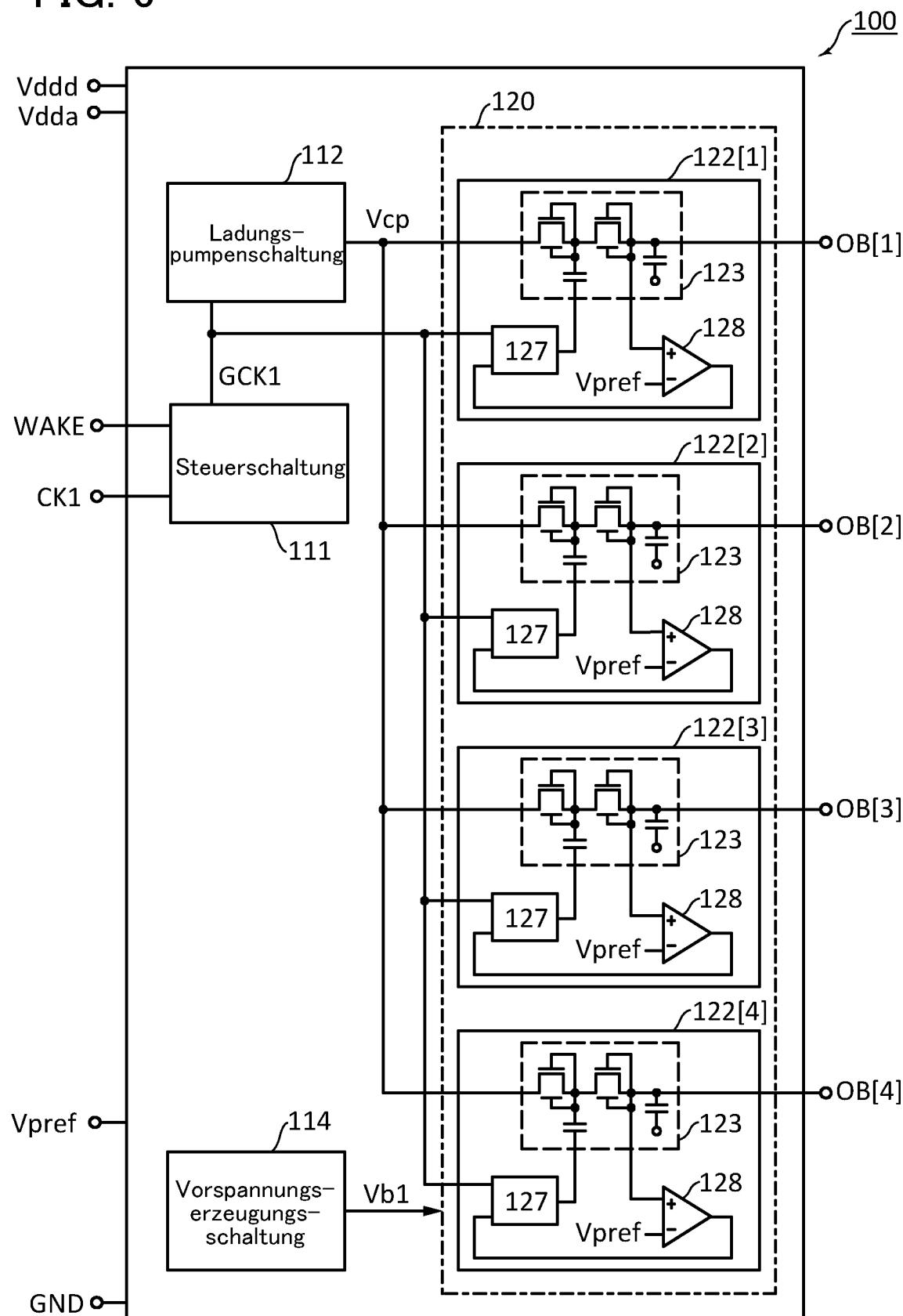

**Fig. 6** ist ein Blockdiagramm, das ein Strukturbeispiel für eine Versorgungsvorrichtung für eine negative Spannung darstellt.

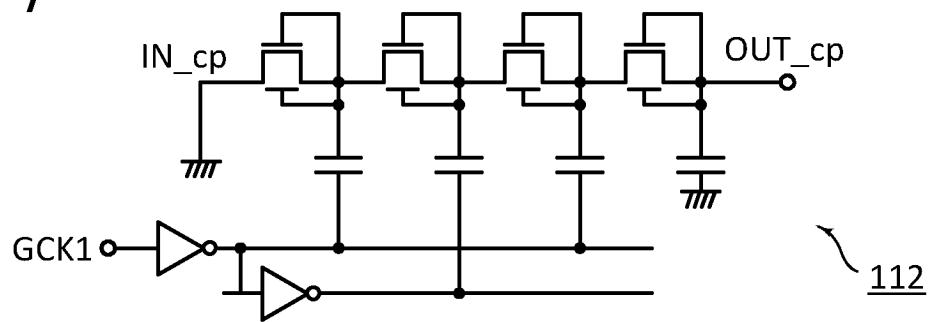

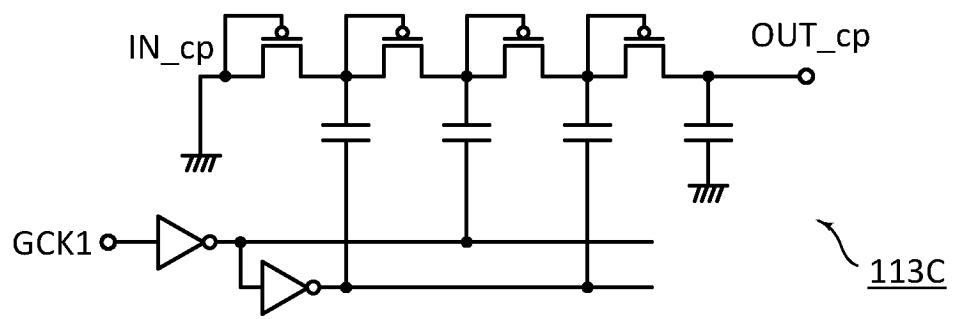

**Fig. 7** ist ein Schaltplan, der ein Konfigurationsbeispiel für eine Ladungspumpenschaltung darstellt.

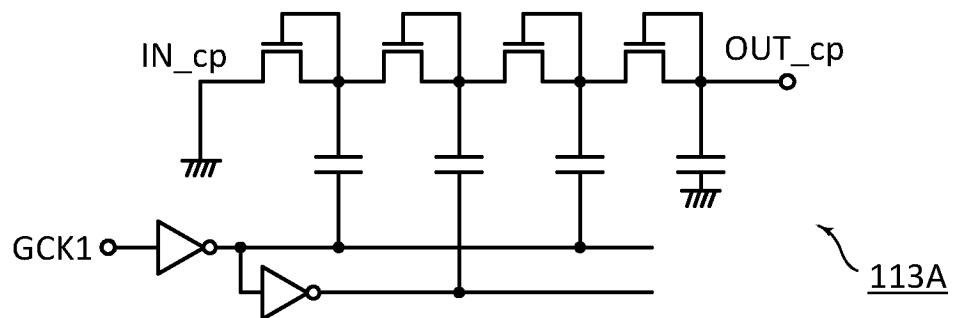

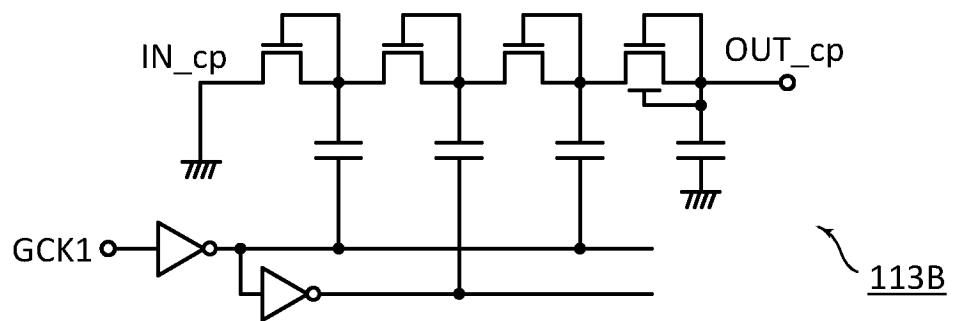

**Fig. 8A** bis **Fig. 8C** sind Schaltpläne, die jeweils ein Strukturbeispiel für eine Ladungspumpenschaltung darstellen.

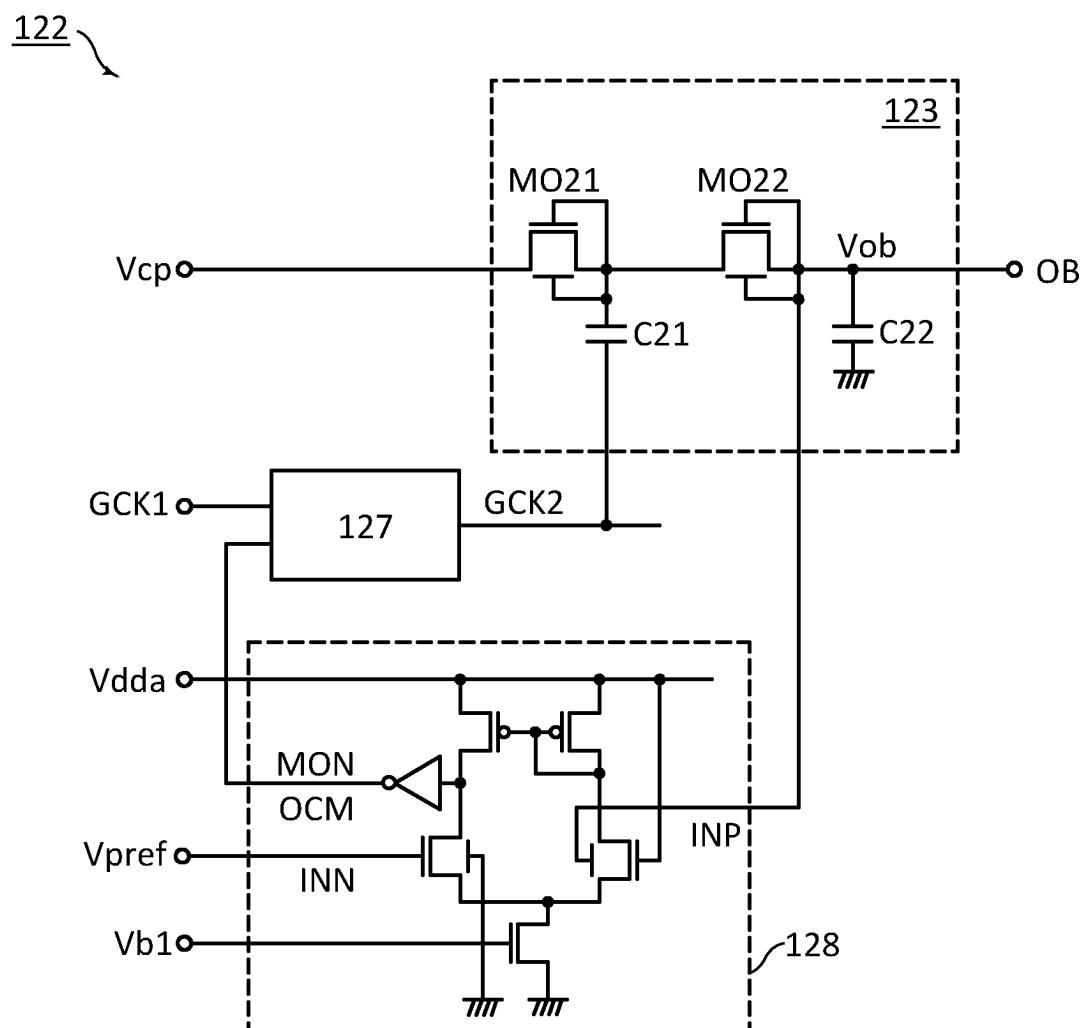

**Fig. 9A** ist ein Schaltplan, der ein Konfigurationsbeispiel für eine Halteschaltung für eine negative Spannung darstellt, und **Fig. 9B** ist eine Wahrheitstabelle einer Treiberschaltung.

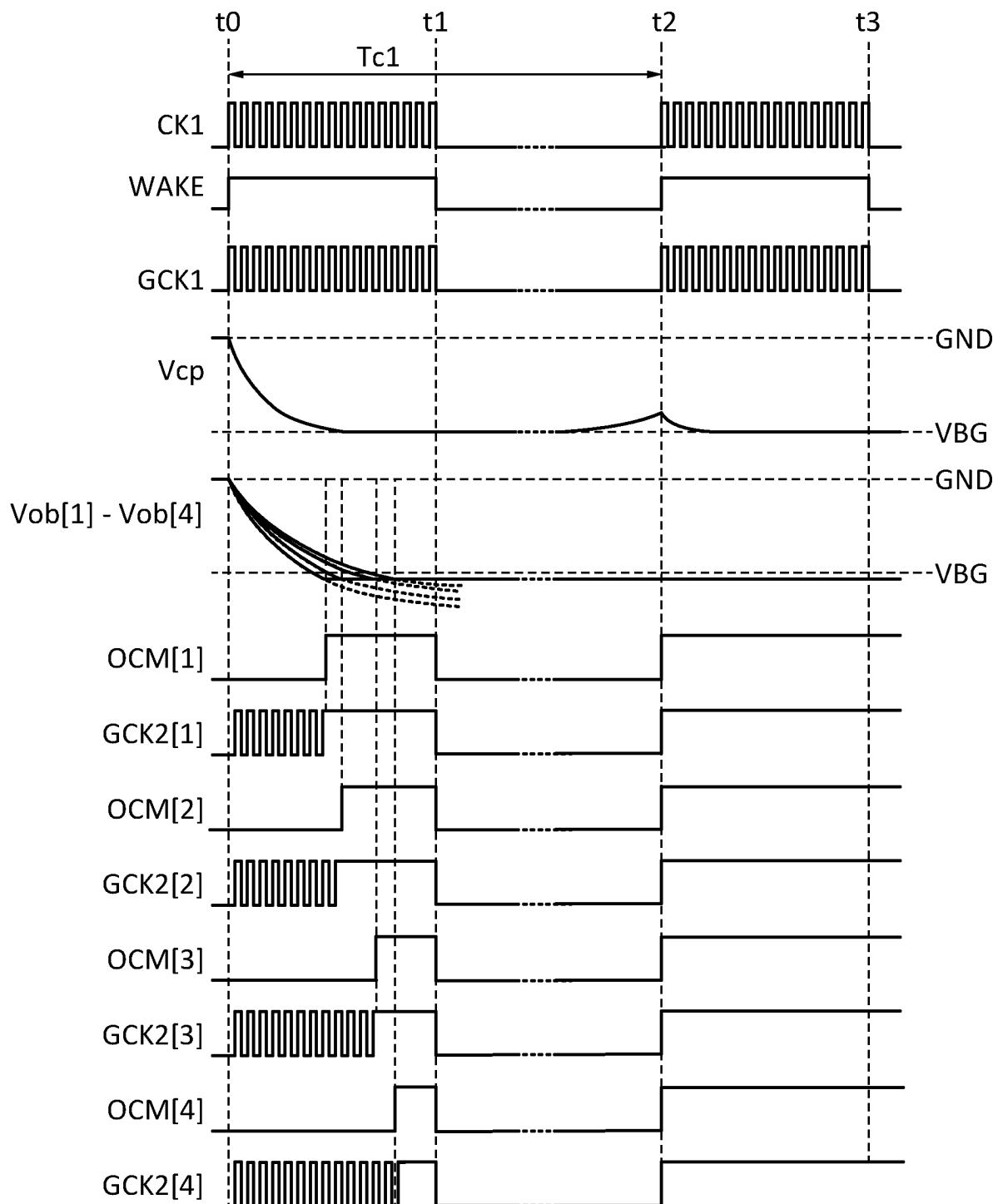

**Fig. 10** ist ein Zeitdiagramm, das ein Betriebsbeispiel für eine Versorgungsvorrichtung für eine negative Spannung zeigt.

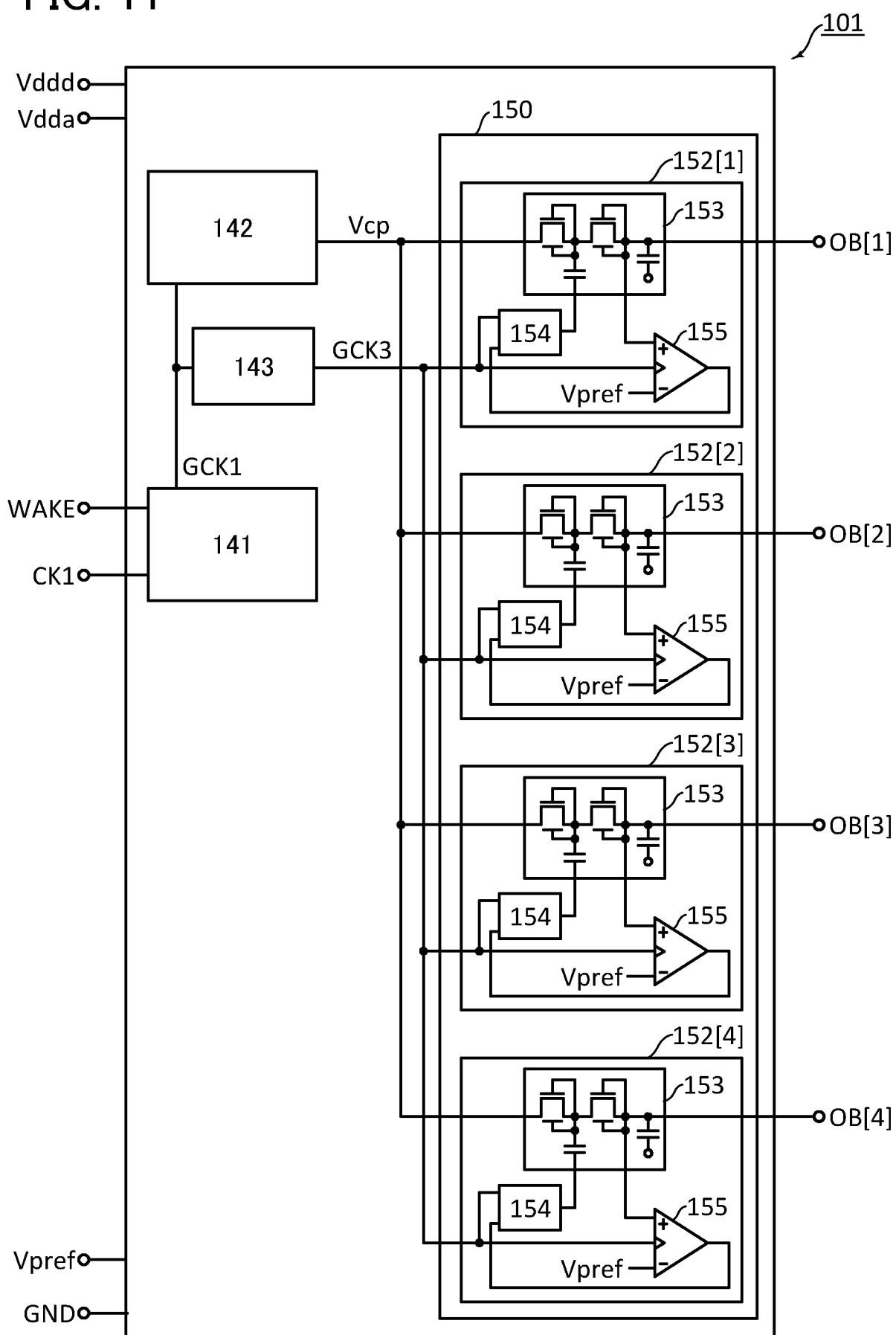

**Fig. 11** ist ein Blockdiagramm, das ein Konfigurationsbeispiel für eine Versorgungsvorrichtung für eine negative Spannung darstellt.

**Fig. 12** ist ein Schaltplan, der ein Strukturbeispiel für eine Halteschaltung für eine negative Spannung darstellt.

**Fig. 13A** und **Fig. 13B** sind Schaltpläne, die jeweils ein Konfigurationsbeispiel für eine Halteschaltung für eine negative Spannung darstellen.

**Fig. 14A** ist ein Blockdiagramm, das ein Konfigurationsbeispiel für eine Speichervorrichtung darstellt, und **Fig. 14B** ist ein Schaltplan, der ein Konfigurationsbeispiel für eine Speicherzelle darstellt.

**Fig. 15A** bis **Fig. 15F** sind Schaltpläne, die jeweils ein Konfigurationsbeispiel für eine Speicherzelle darstellen.

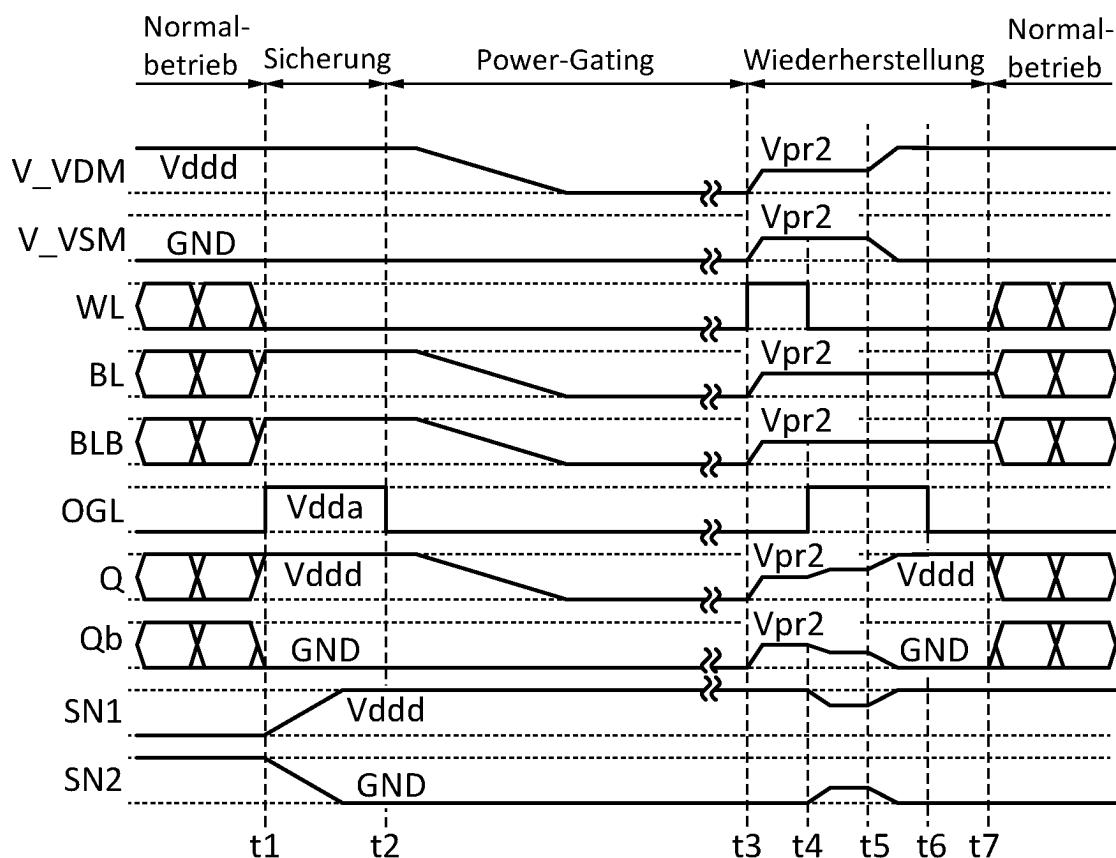

**Fig. 16A** ist ein Schaltplan, der ein Konfigurationsbeispiel für eine Speicherzelle darstellt, und **Fig. 16B** ist ein Zeitdiagramm, das ein Betriebsbeispiel für die Speicherzelle zeigt.

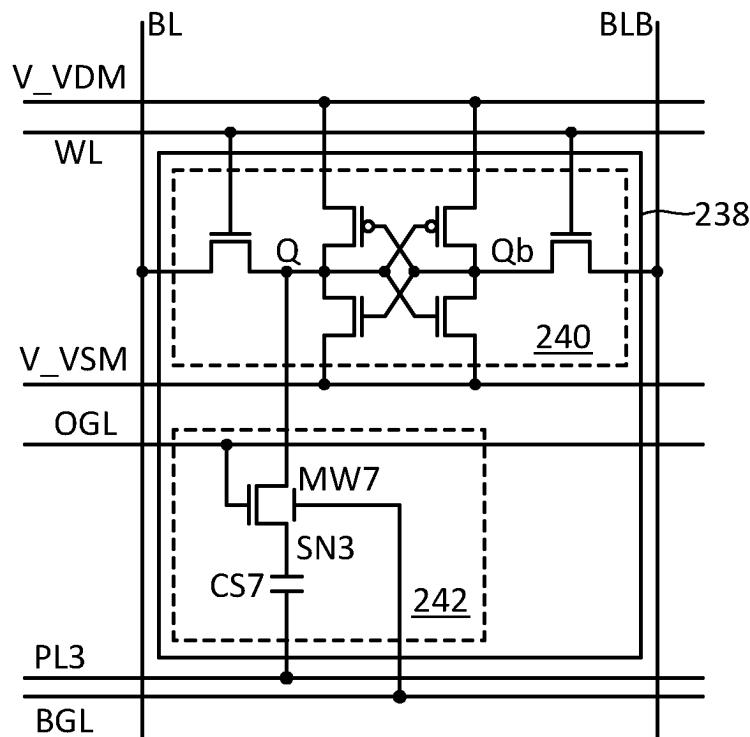

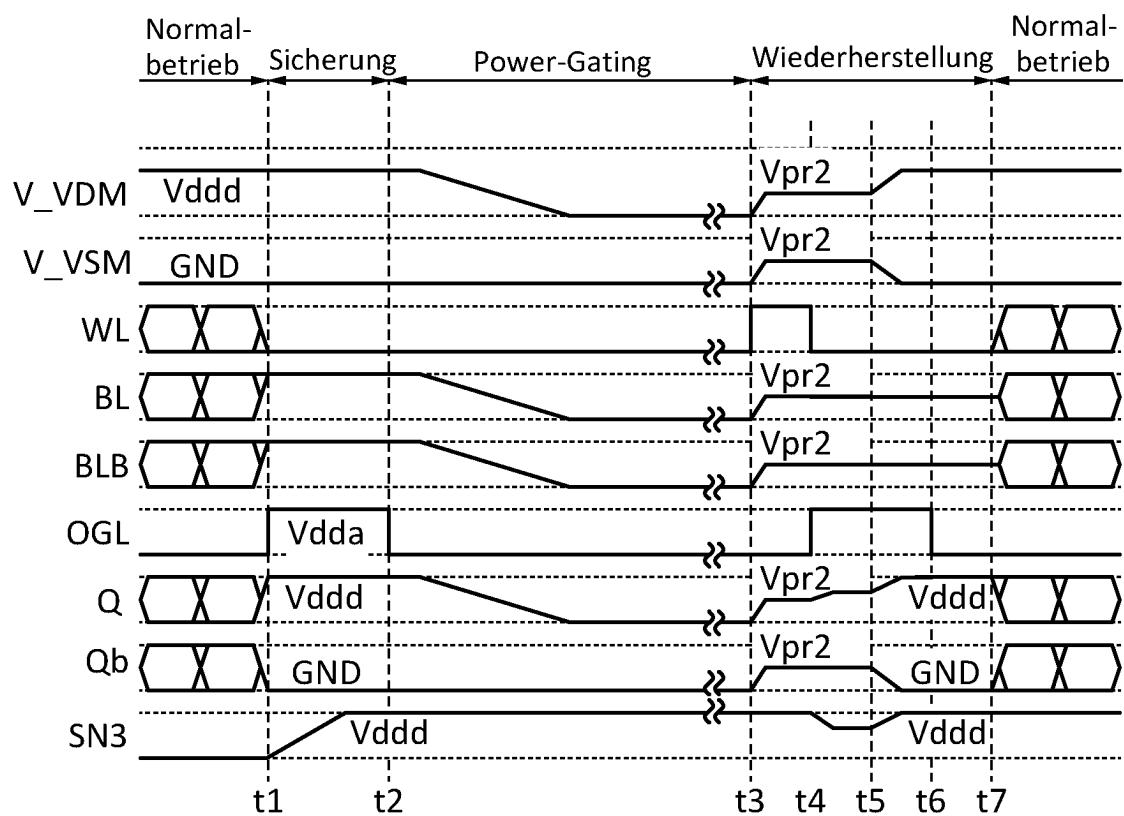

**Fig. 17A** ist ein Schaltplan, der ein Konfigurationsbeispiel für eine Speicherzelle darstellt, und **Fig. 17B** ist ein Zeitdiagramm, das ein Betriebsbeispiel für die Speicherzelle zeigt.

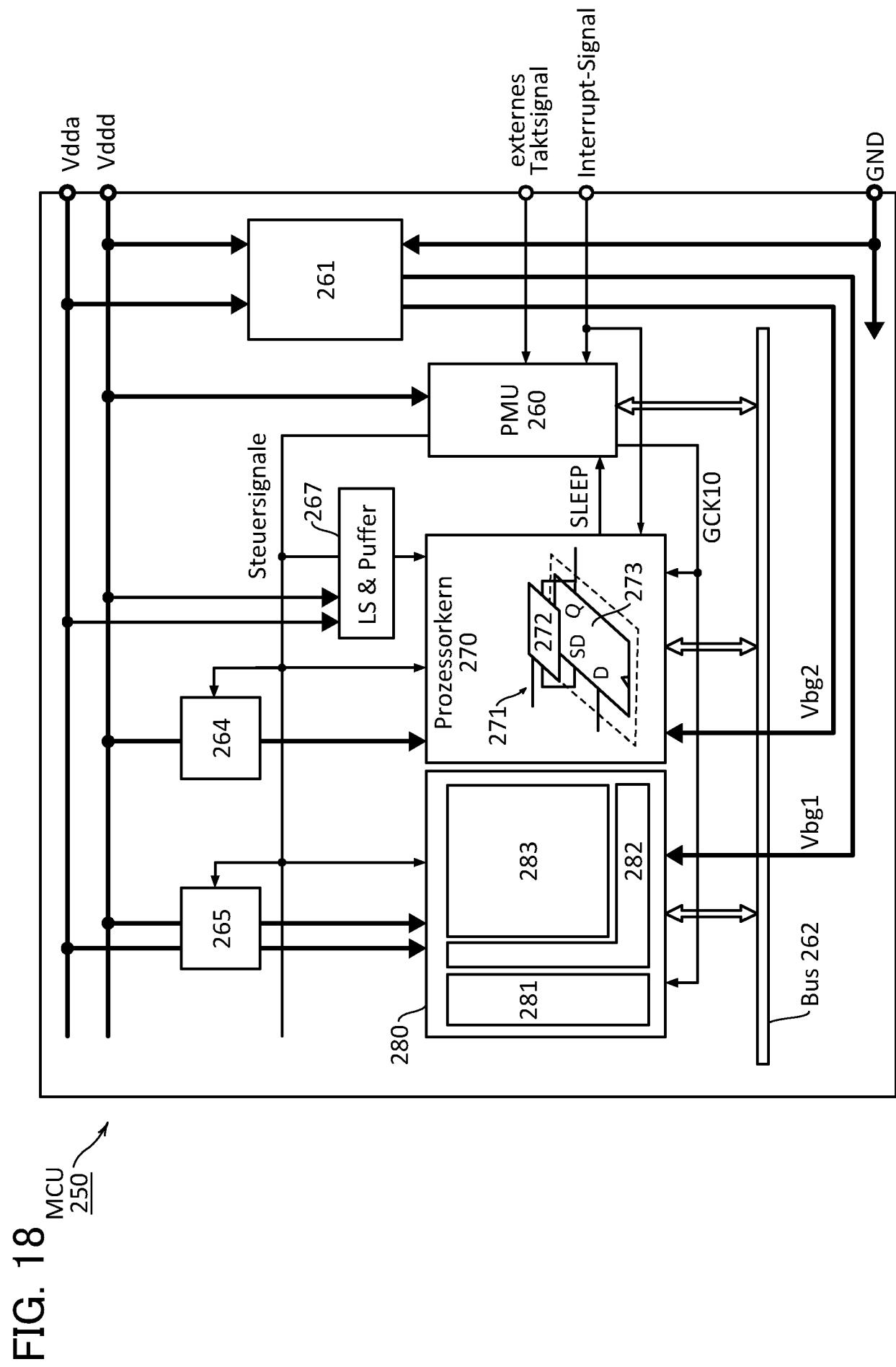

**Fig. 18** ist ein Blockdiagramm, das ein Strukturbeispiel für eine Mikrocontroller-Einheit darstellt.

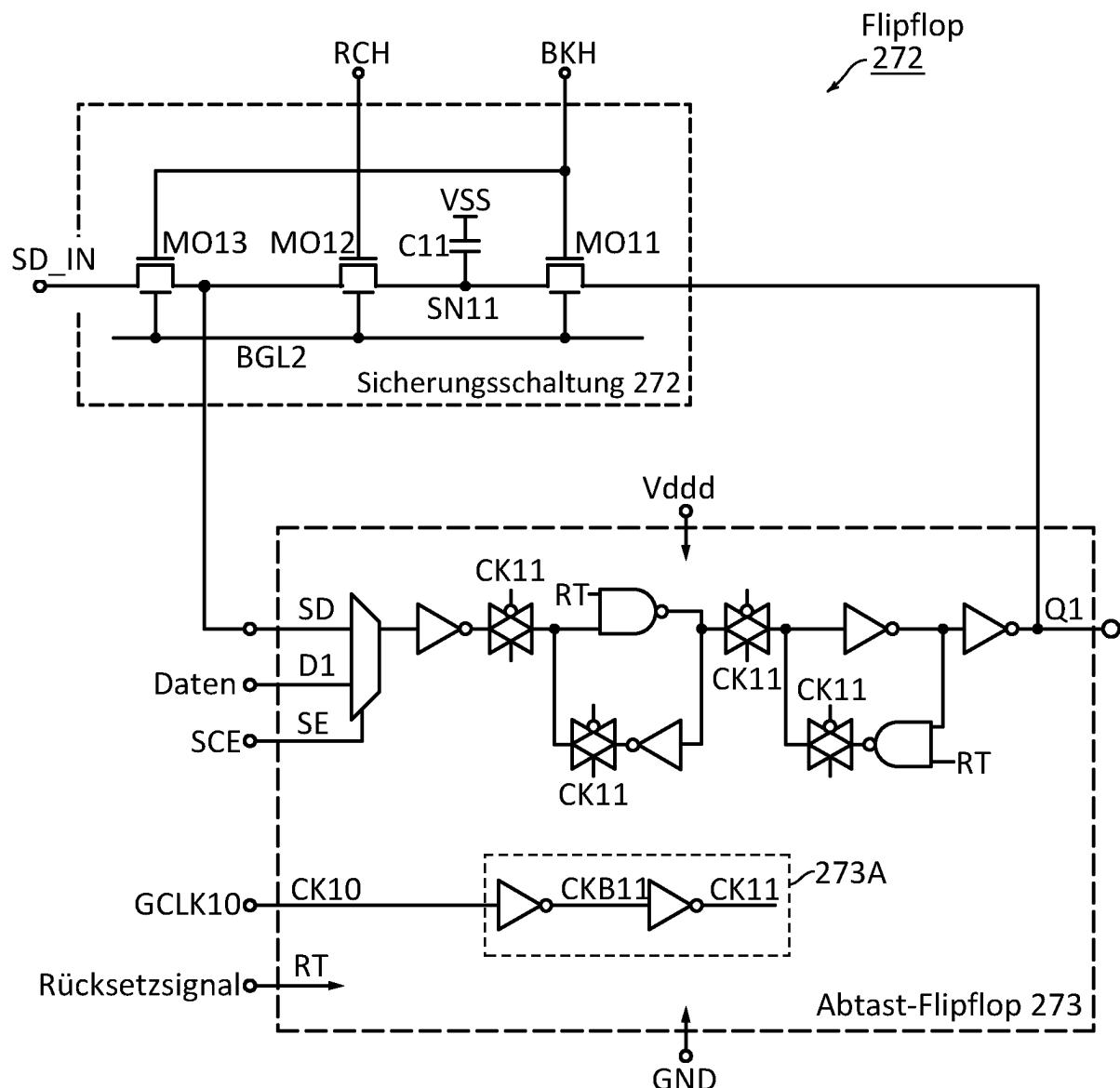

**Fig. 19** ist ein Schaltplan, der ein Strukturbeispiel für ein Flipflop darstellt.

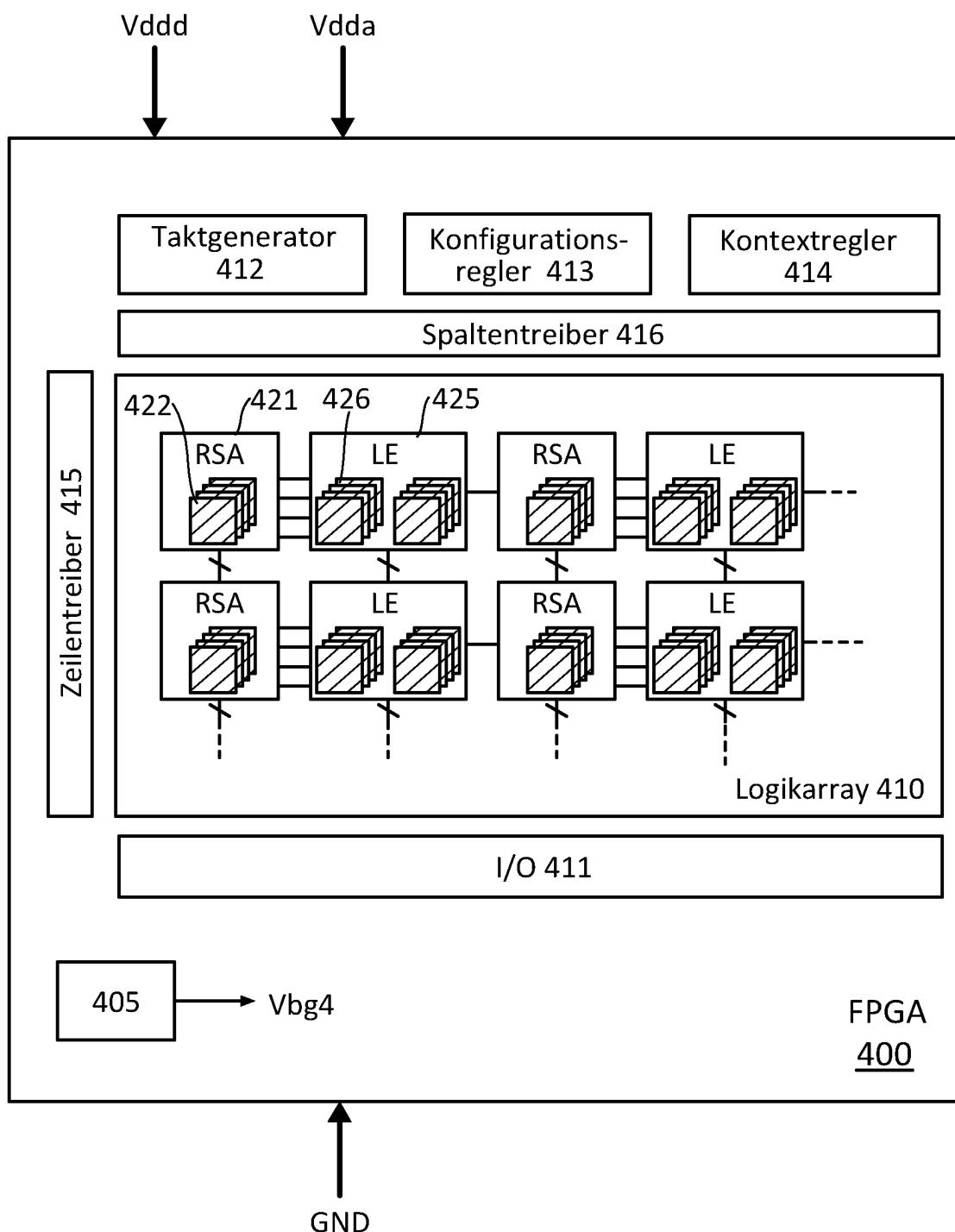

**Fig. 20** ist ein Blockdiagramm, das ein Konfigurationsbeispiel für ein FPGA darstellt.

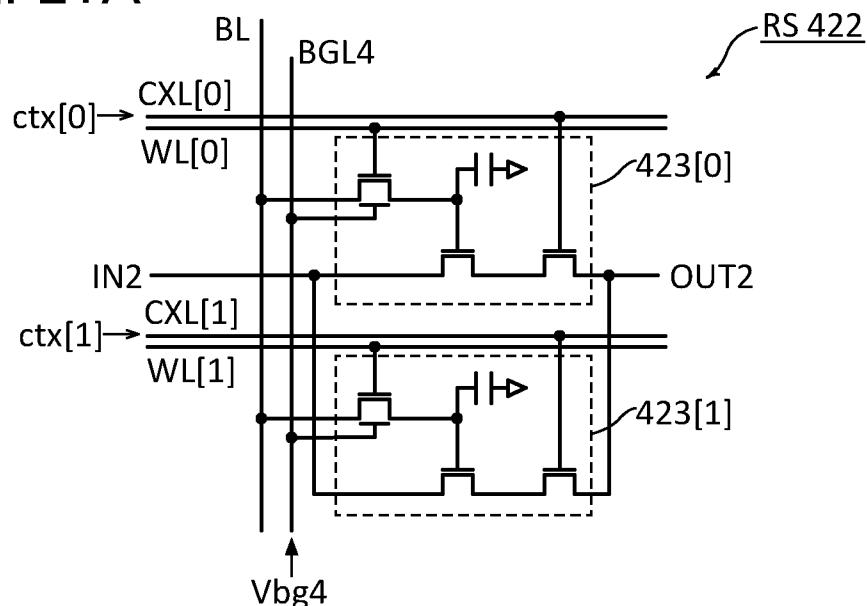

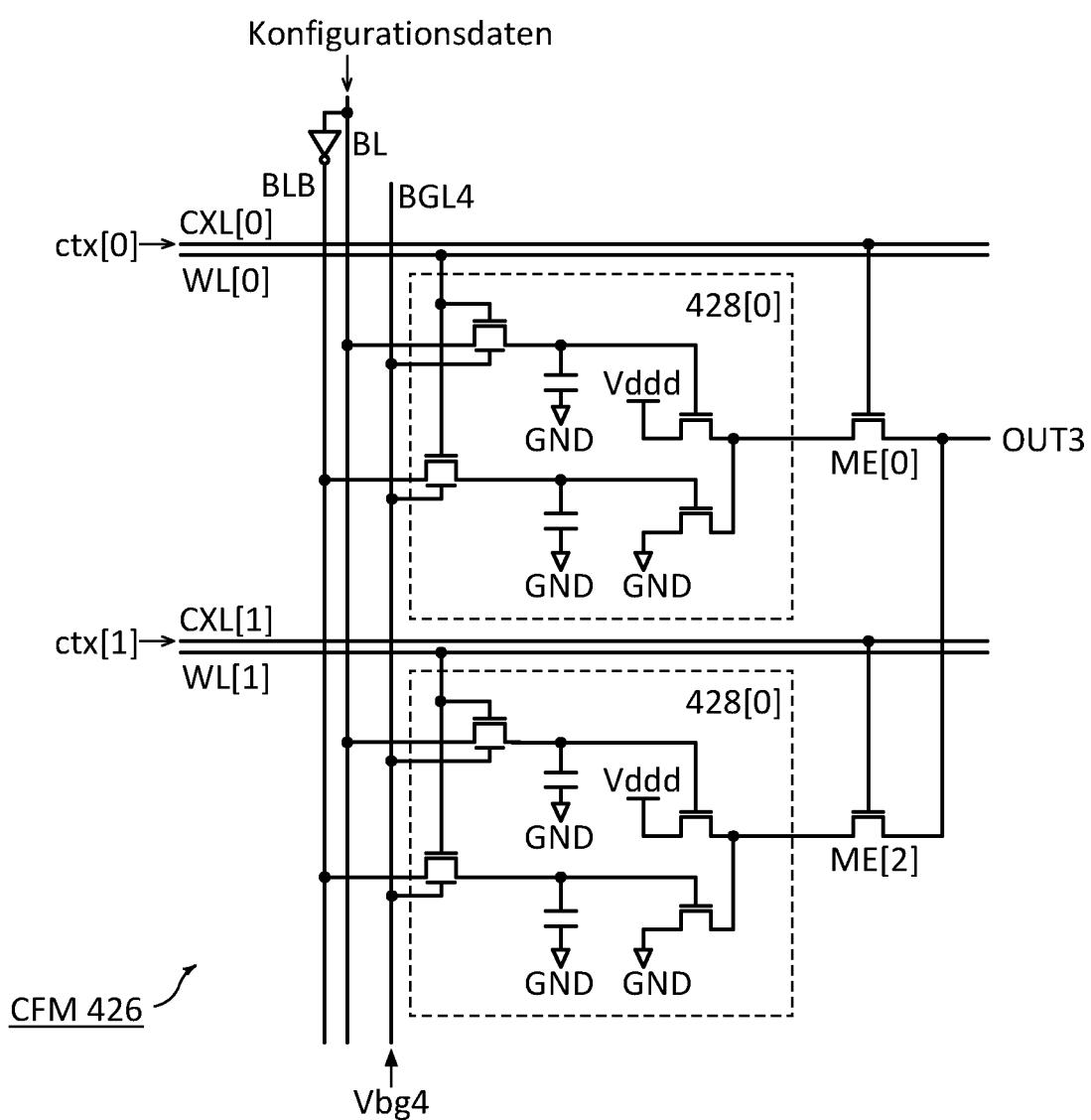

**Fig. 21A** ist ein Schaltplan, der ein Konfigurationsbeispiel für einen Routing-Schalter darstellt, und **Fig. 21B** ist ein Schaltplan, der ein Konfigurationsbeispiel für einen Konfigurationsspeicher zeigt.

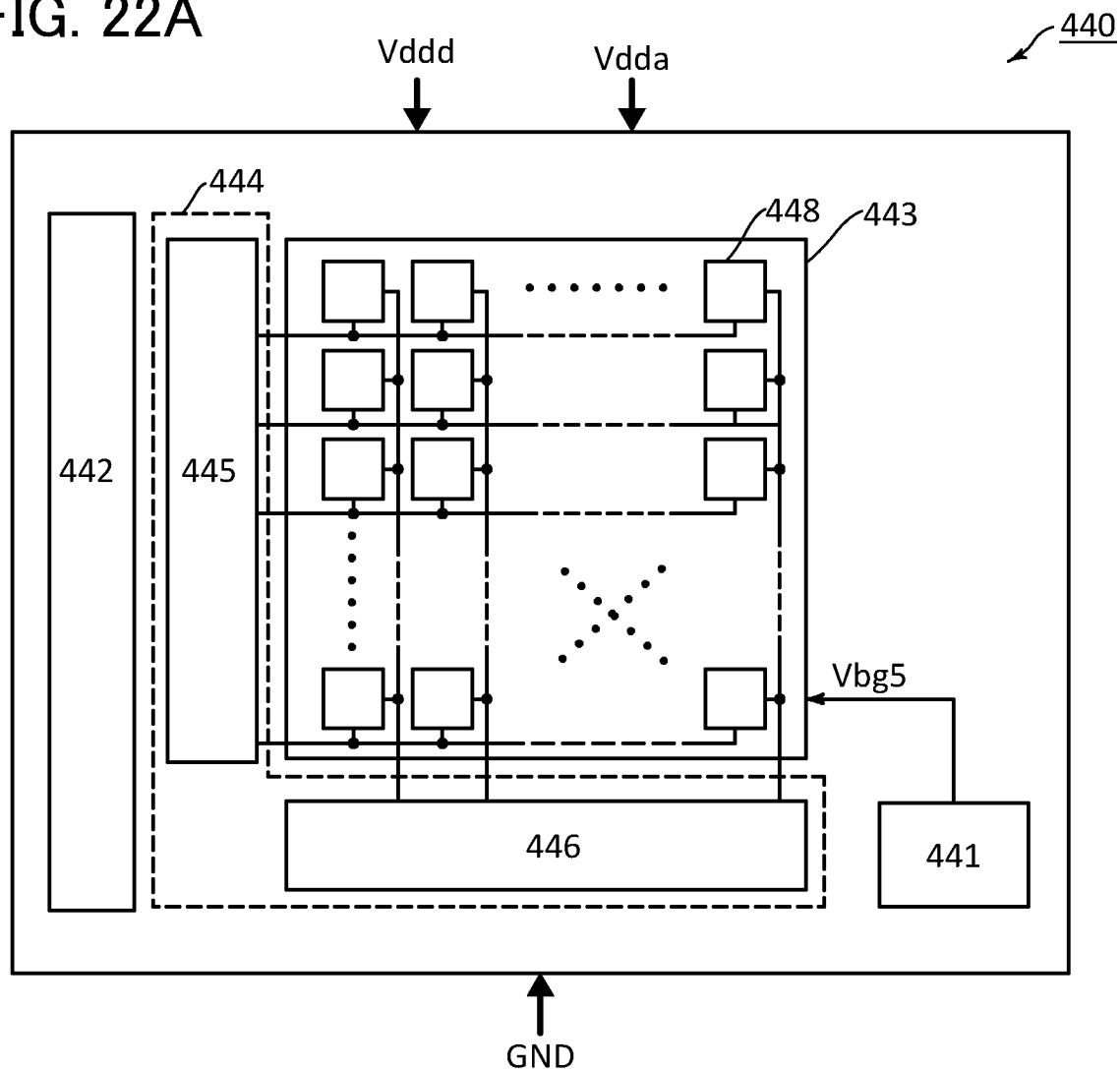

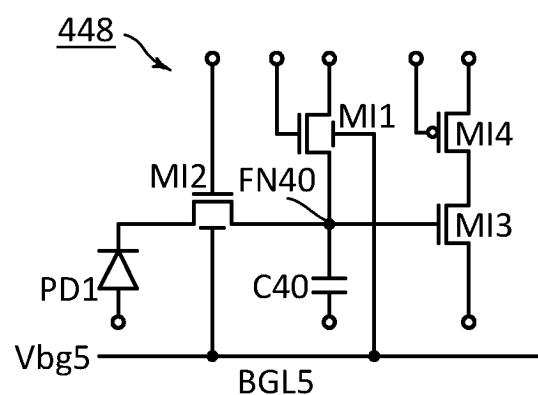

**Fig. 22A** ist ein Blockdiagramm, das ein Konfigurationsbeispiel für eine Abbildungsvorrichtung darstellt, und **Fig. 22B** ist ein Schaltplan, der ein Konfigurationsbeispiel für ein Pixel darstellt.

**Fig. 23A** und **Fig. 23B** sind schematische perspektivische Ansichten von elektronischen Komponenten.

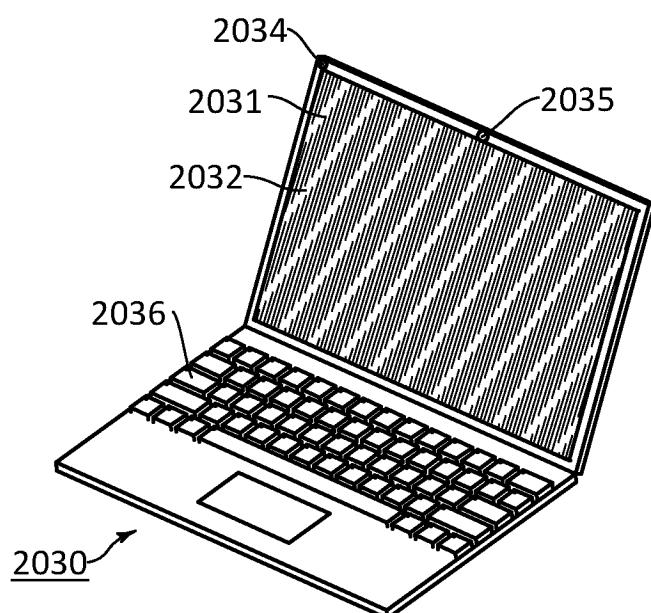

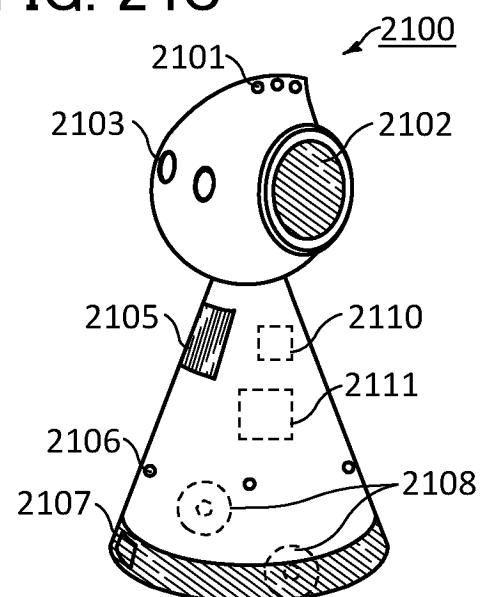

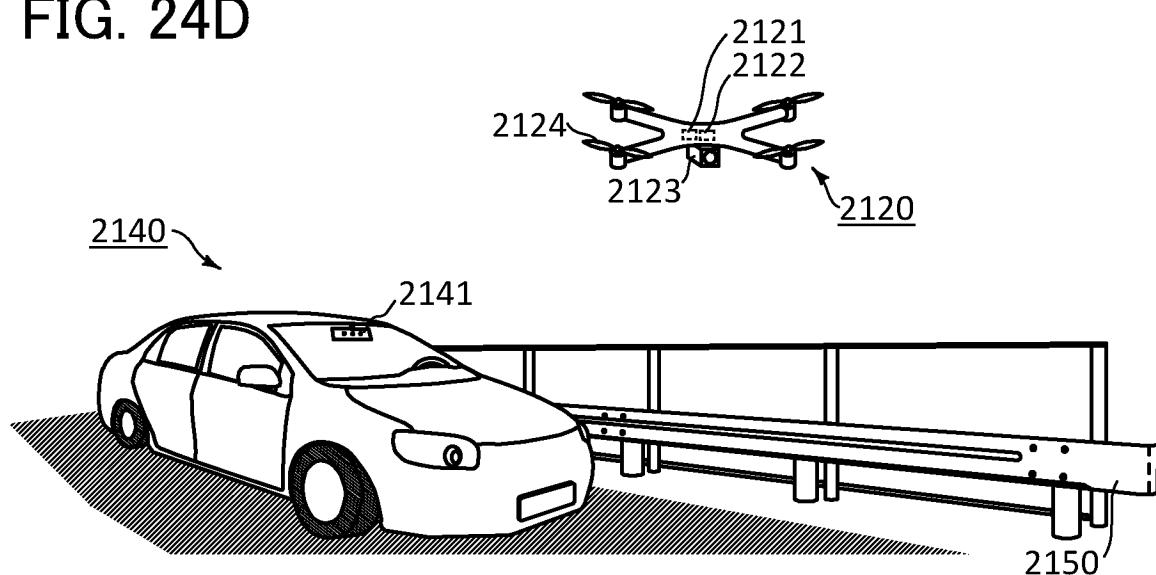

**Fig. 24A** bis **Fig. 24D** sind Darstellungen, die jeweils ein Strukturbeispiel für ein elektronisches Gerät darstellen.

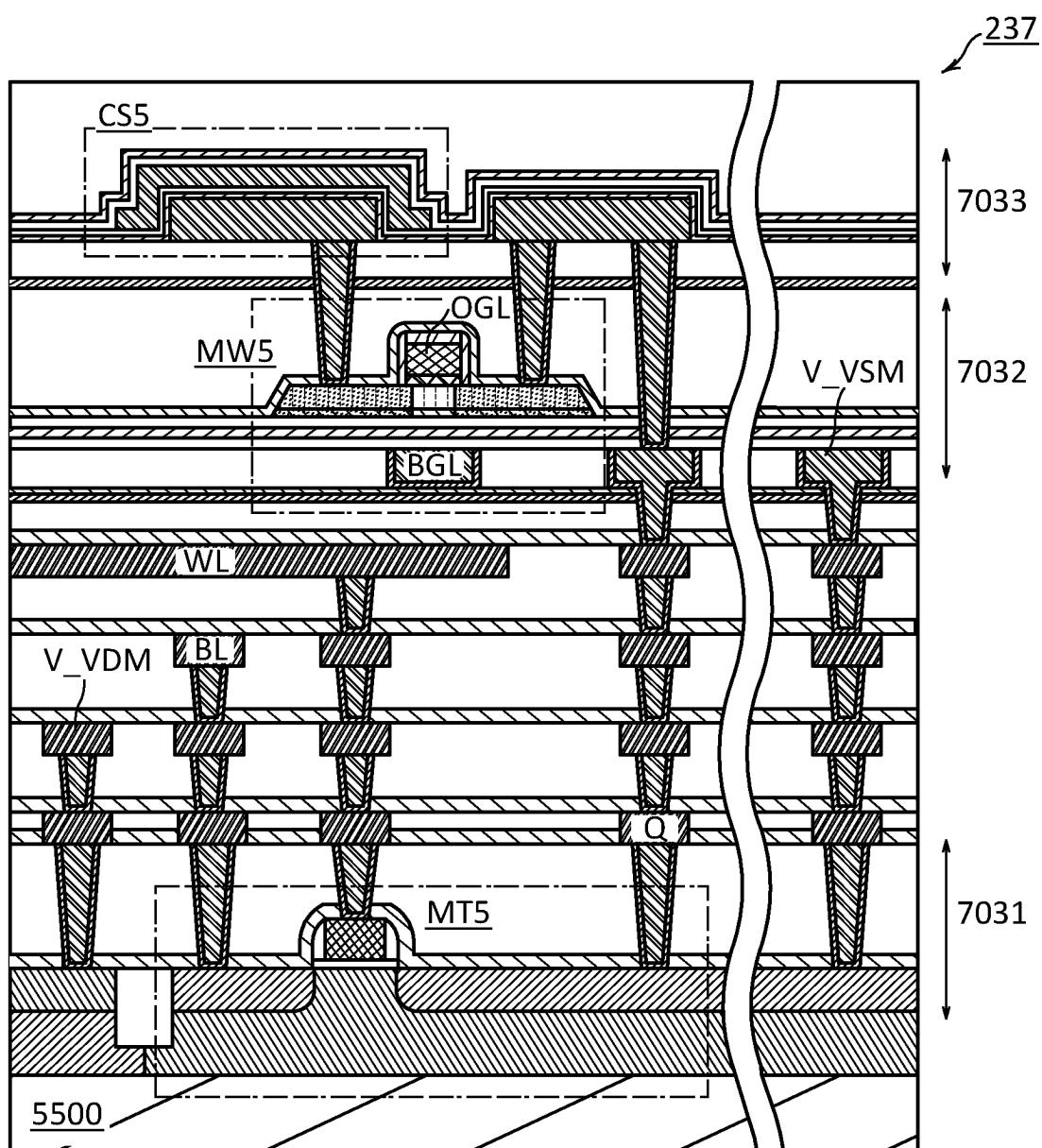

**Fig. 25** ist eine Querschnittsansicht, die ein mehrschichtiges Strukturbeispiel für einen Schaltungsabschnitt einer elektronischen Komponente darstellt.

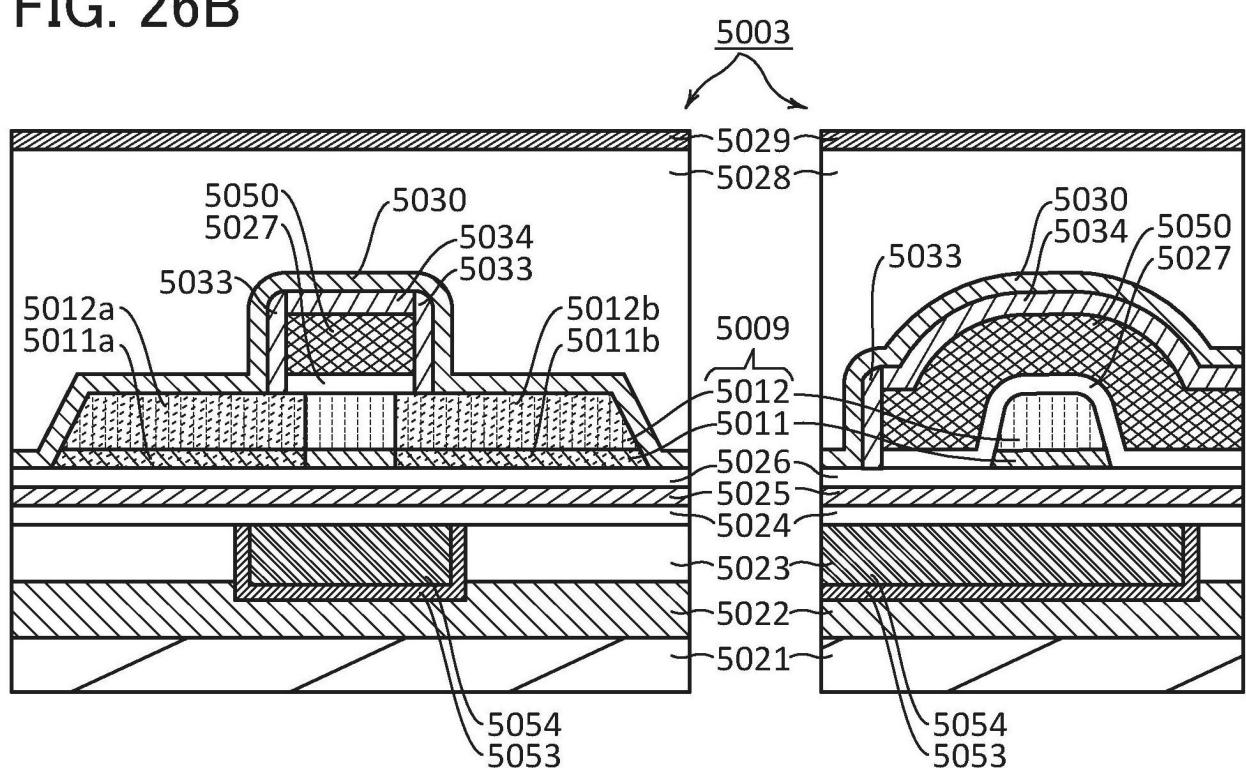

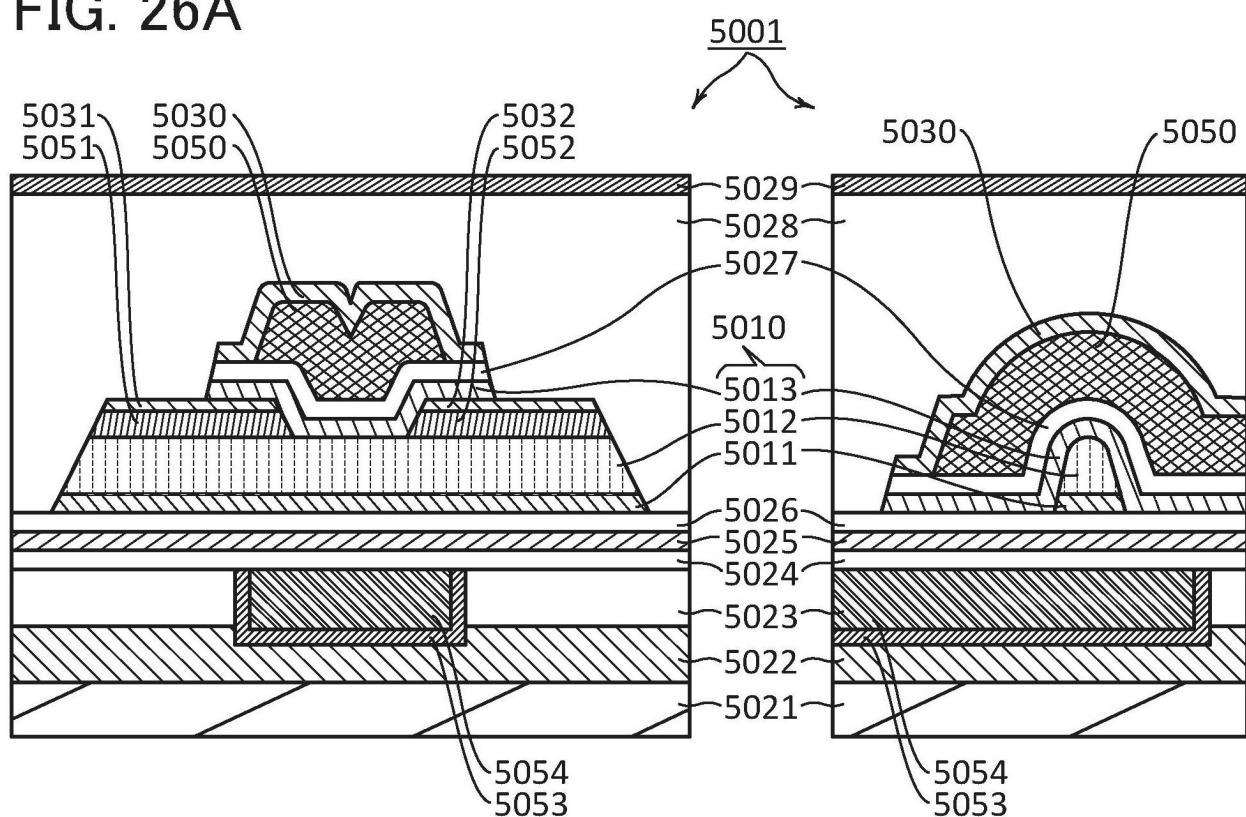

**Fig. 26A** und **Fig. 26B** sind Querschnittsansichten, die jeweils ein Strukturbeispiel für einen OS-Transistor darstellen.

#### Beste Methode zum Durchführen der Erfindung

**[0012]** Nachstehend werden Ausführungsformen der vorliegenden Erfindung beschrieben. Es sei angemerkt, dass eine Ausführungsform der vorliegen-

den Erfindung nicht auf die folgende Beschreibung beschränkt ist. Es erschließt sich Fachleuten ohne Weiteres, dass Modi und Details der vorliegenden Erfindung auf verschiedene Weise verändert werden können, ohne dabei vom Gedanken und Schutzbereich der vorliegenden Erfindung abzuweichen. Deshalb sollte eine Ausführungsform der vorliegenden Erfindung nicht als auf die Beschreibung der folgenden Ausführungsformen beschränkt angesehen werden.

**[0013]** Beliebige der nachstehend beschriebenen Ausführungsformen können je nach Bedarf kombiniert werden. In dem Fall, in dem einige Strukturbeispiele (darunter auch ein Beispiel für ein Herstellungsverfahren, ein Beispiel für ein Betriebsverfahren und dergleichen) bei einer Ausführungsform gezeigt werden, können beliebige der Strukturbeispiele je nach Bedarf miteinander kombiniert werden oder je nach Bedarf mit einem oder mehreren Strukturbeispielen, die bei den anderen Ausführungsformen beschrieben werden, kombiniert werden.

**[0014]** Bei dieser Beschreibung und dergleichen werden Ordnungszahlen, wie z. B. „erste“, „zweite“ und „dritte“, verwendet, um eine Verwechslung unter Komponenten zu vermeiden, und die Begriffe beschränken die Anzahl oder die Reihenfolge der Komponenten nicht.

**[0015]** In einigen Fällen werden die gleichen Komponenten, Komponenten, die ähnliche Funktionen aufweisen, Komponenten, die unter Verwendung des gleichen Materials ausgebildet werden, Komponenten, die gleichzeitig ausgebildet werden, und dergleichen in den Zeichnungen durch die gleichen Bezugszeichen bezeichnet, und wird ihre Beschreibung nicht wiederholt.

**[0016]** Wenn eine Vielzahl von Komponenten, die durch die gleichen Bezugszeichen bezeichnet werden, voneinander zu unterscheiden sind, wird in einigen Fällen „\_1“, „\_2“, „[n]“, „[m, n]“ oder dergleichen den Bezugszeichen hinzugefügt.

**[0017]** Bei dieser Beschreibung kann eine Stromversorgungsspannung **VDD** beispielsweise als „Spannung **VDD**“ oder „**VDD**“ abgekürzt werden. Das Gleiche gilt für weitere Komponenten (z. B. ein Signal, eine Spannung, eine Schaltung, ein Element, eine Elektrode und eine Leitung).

**[0018]** In den Zeichnungen ist die Größe, die Dicke einer Schicht, der Bereich und dergleichen in einigen Fällen der Klarheit halber übertrieben dargestellt. Deshalb ist die Größe, die Dicke einer Schicht oder der Bereich nicht auf das dargestellte Größenverhältnis beschränkt. Die Zeichnungen sind schematische Ansichten, die ideale Beispiele zeigen, und Ausführungsformen der vorliegenden Erfindung sind

nicht auf Formen oder Werte beschränkt, welche in den Zeichnungen gezeigt sind. Beispielsweise können die folgenden Schwankungen mit eingeschlossen werden: Schwankungen eines Signals, einer Spannung oder eines Stroms aufgrund eines Rauschens oder einer Zeitdifferenz.

**[0019]** In dieser Beschreibung werden in einigen Fällen Begriffe zum Beschreiben der Anordnung, wie z. B. „über“, „oberhalb“, „unter“ und „unterhalb“, der Einfachheit halber beim Beschreiben der Positionsbeziehung zwischen Komponenten unter Bezugnahme auf Zeichnungen verwendet. Die Positionsbeziehung zwischen Komponenten wird ferner nach Bedarf entsprechend einer Richtung geändert, in der eine jeweilige Komponente beschrieben wird. Deshalb gibt es keine Beschränkung bezüglich der Begriffe, die in dieser Beschreibung verwendet werden, und eine Beschreibung kann je nach Situation angemessen erfolgen.

**[0020]** Es sei angemerkt, dass ein Transistor drei Anschlüsse beinhaltet: ein Gate, eine Source und einen Drain. Ein Gate dient als Steueranschluss, der den Leitungszustand eines Transistors steuert. In Abhängigkeit von dem Typ des Transistors oder den Pegeln der Potentiale, die den Anschlüssen zugeführt werden, dient einer von zwei Eingangs-/Ausgangsanschlüssen als Source, und der andere dient als Drain. Deshalb können die Begriffe „Source“ und „Drain“ in dieser Beschreibung und dergleichen miteinander vertauscht werden. In dieser Beschreibung und dergleichen können die zwei Anschlüsse außer dem Gate als erster Anschluss und zweiter Anschluss bezeichnet werden.

**[0021]** Ein Knoten kann in Abhängigkeit von der Schaltungskonfiguration, der Bauteilstruktur oder dergleichen als Anschluss, Leitung, Elektrode, leitende Schicht, Leiter, Verunreinigungsbereich oder dergleichen bezeichnet werden. Außerdem kann ein Anschluss, eine Leitung oder dergleichen als Knoten bezeichnet werden.

**[0022]** In dieser Beschreibung und dergleichen können die Begriffe „Film“ und „Schicht“ je nach Sachlage oder Umständen ausgetauscht werden. Beispielsweise kann der Begriff „leitende Schicht“ in einigen Fällen in den Begriff „leitender Film“ umgewandelt werden. Der Begriff „Isolierfilm“ kann beispielsweise in einigen Fällen in den Begriff „Isolierschicht“ umgewandelt werden.

**[0023]** In dieser Beschreibung und dergleichen bezeichnet eine Halbleitervorrichtung eine Vorrichtung, die Halbleitereigenschaften nutzt, und bedeutet eine Schaltung, die ein Halbleiterelement (z. B. einen Transistor oder eine Diode) beinhaltet, eine Vorrichtung, die die Schaltung beinhaltet, und dergleichen. Die Halbleitervorrichtung bedeutet auch jede Vorrich-

tung, die unter Nutzung von Halbleitereigenschaften arbeiten kann. Beispielsweise sind eine integrierte Schaltung und ein Chip, der eine integrierte Schaltung beinhaltet, Beispiele für Halbleitervorrichtungen. Des Weiteren könnten eine Speichervorrichtung, eine Anzeigevorrichtung, eine Licht emittierende Vorrichtung, eine Beleuchtungsvorrichtung, ein elektronisches Gerät und dergleichen an sich Halbleitervorrichtungen sein oder könnten jeweils eine Halbleitervorrichtung beinhalten.

[Ausführungsform 1]

**[0024]** Bei dieser Ausführungsform werden eine Vergleichsschaltung, in die eine zu vergleichende negative Spannung direkt eingegeben werden kann, und eine Halbleitervorrichtung, die die Vergleichsschaltung beinhaltet, beschrieben.

<<Vergleichsschaltung>>

**[0025]** Hier wird ein Konfigurationsbeispiel für eine Vergleichsschaltung beschrieben, in der eine Differenzverstärkerschaltung verwendet wird.

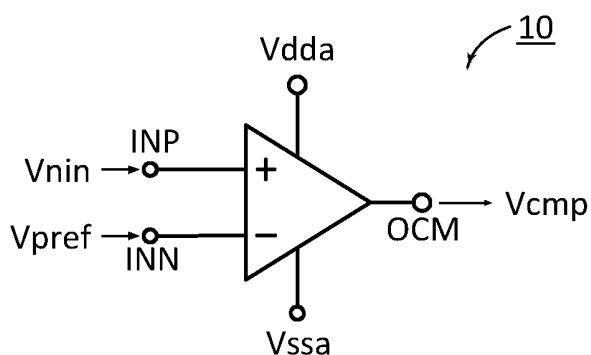

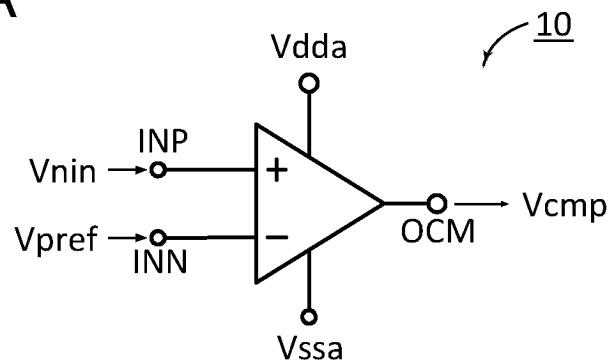

**[0026]** Fig. 1A stellt ein Beispiel für eine Vergleichsschaltung dar. Eine Vergleichsschaltung 10, die in Fig. 1A dargestellt ist, beinhaltet Anschlüsse **INN**, **INP** und **OCM**. Die Anschlüsse **INN**, **INP** und **OCM** sind ein invertierender Eingangsanschluss, ein nicht invertierender Eingangsanschluss bzw. ein Ausgangsanschluss.

**[0027]** Spannungen **Vdda** und **Vssa** werden in die Vergleichsschaltung 10 eingegeben. Bei der Spannung **Vdda** handelt es sich um eine hohe Stromversorgungsspannung. Bei der Spannung **Vssa** handelt es sich um eine niedrige Stromversorgungsspannung, wie z. B. 0 V (Erdspannung, **GND**).

**[0028]** Die Vergleichsschaltung 10 weist eine Funktion zum Vergleichen einer negativen Spannung **Vnin** mit einer negativen Bezugsspannung **Vnref** und zum Ausgeben einer Spannung **Vcmp**, die den Vergleichsergebnissen entspricht, von dem Anschluss **OCM** auf. Die negative Spannung **Vnin** wird in den Anschluss **INP** eingegeben. Nicht die negative Bezugsspannung **Vnref**, sondern eine positive Bezugsspannung **Vpref** wird in den Anschluss **INN** eingegeben. Die positive Bezugsspannung **Vpref** entspricht der negativen Bezugsspannung **Vnref**, die in eine positive Spannung umgewandelt wird. Der Wert der positiven Bezugsspannung **Vpref** wird derart bestimmt, dass die Vergleichsschaltung 10 den Vergleich durchführen kann.

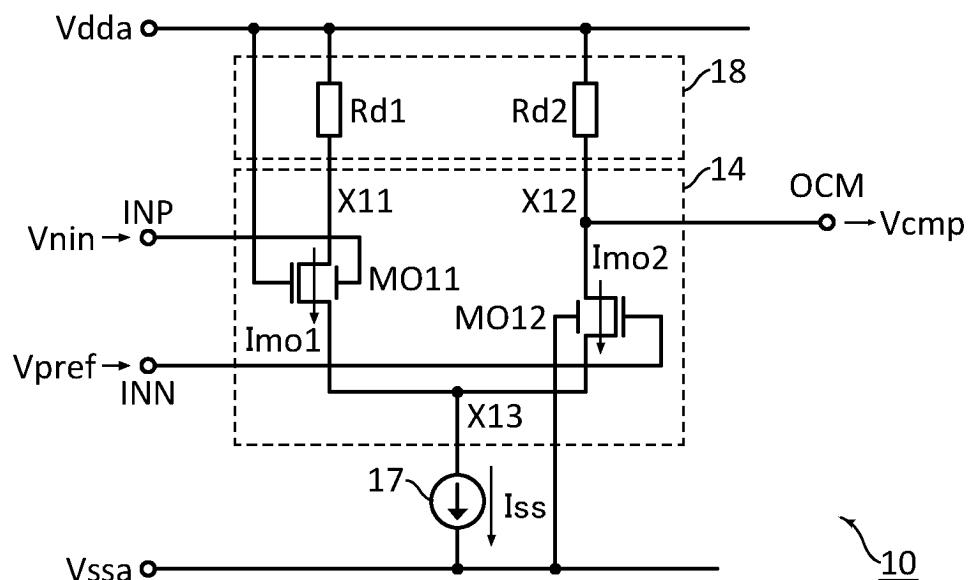

**[0029]** Fig. 1B stellt ein Beispiel für die Schaltungskonfiguration der Vergleichsschaltung 10 dar. Die Vergleichsschaltung 10 besteht aus einer Differenz-

schaltung und beinhaltet ein Differenzpaar **14**, eine Stromquelle **17** und einen Lastkreis **18**.

**[0030]** Das Differenzpaar **14** beinhaltet Transistoren **MO11** und **MO12**. Bei jedem der Transistoren **MO11** und **MO12** handelt es sich um einen OS-Transistor mit einem Rückgate. Das Rückgate des Transistors **MO11** ist elektrisch mit dem Anschluss **INP** verbunden, und die Spannung **Vdda** wird in das Gate eingegeben. Das Gate des Transistors **MO12** ist elektrisch mit dem Anschluss **INN** verbunden, und die Spannung **Vssa** wird in das Rückgate eingegeben.

**[0031]** Hier wird ein Verbindungsknoten zwischen dem Transistor **MO11** und dem Lastkreis **18** als Knoten **X11** bezeichnet, ein Verbindungsknoten zwischen dem Transistor **MO12** und dem Lastkreis **18** wird als Knoten **X12** bezeichnet, und ein Verbindungsknoten zwischen dem Transistor **MO11** und dem Transistor **MO12** wird als Knoten **X13** bezeichnet. Die Stromquelle **17** führt dem Knoten **X13** einen Strom **Iss** zu. Der Lastkreis **18** legt an die Knoten **X11** und **X12** Belastungen **Rd1** bzw. **Rd2** an.

**[0032]** Es sei angemerkt, dass in den Zeichnungen der n-Kanal-Transistor mit einem Rückgate ein OS-Transistor ist und der p-Kanal-Transistor und der n-Kanal-Transistor mit keinem Rückgate Si-Transistoren sind, sofern nicht anders festgelegt.

**[0033]** Die Spannung jedes der Knoten **X12** und **X11** wird durch eine Differenz zwischen einem Drain-Strom (**Imo1**) des Transistors **MO11** und einem Drain-Strom (**Imo2**) des Transistors **MO12** bestimmt. In dem Beispiel der **Fig. 1B**, in dem der Anschluss **OCM** elektrisch mit dem Knoten **X12** verbunden ist, liegt die Spannung **Vcmp** auf dem hohen Pegel („H“), wenn **Imo1 > Imo2** gilt, während die Spannung **Vcmp** auf dem niedrigen Pegel („L“) liegt, wenn **Imo1 < Imo2** gilt.

(Beispiel zum Einstellen der positiven Bezugsspannung **Vpref**)

**[0034]** Eine Differenz zwischen dem Strom **Imo1** und dem Strom **Imo2**, die durch das Differenzpaar **14** fließen, kann in eine Spannungsdifferenz zwischen dem Anschluss **INP** und dem Anschluss **INN** umgewandelt werden. Die positive Bezugsspannung **Vpref** kann daher gemäß der Spannungsdifferenz eingestellt werden. Insbesondere wird in dem Fall, in dem die Spannung des Anschlusses **INP**, die Gate-Spannung des Transistors **MO11** und die Rückgate-Spannung des Transistors **MO12** **Vref**, **Vdda** bzw. **Vssa** sind, eine Spannungsdifferenz zwischen dem Anschluss **INP** und dem Anschluss **INN** zu dem Zeitpunkt abgeschätzt, zu dem die Differenz zwischen **Imo1** und **Imo2** 0 Ampere ist. Der Wert der positiven Bezugsspannung **Vpref** kann aus der abgeschätzten Spannungsdifferenz eingestellt werden.

**[0035]** Indem die positive Bezugsspannung **Vpref** auf diese Weise eingestellt wird, gibt der Anschluss **OCM** die Spannung **Vcmp** auf „H“ aus, wenn **Vnin > Vref** gilt, während der Anschluss **OCM** die Spannung **Vcmp** auf „L“ ausgibt, wenn **Vnin < Vref** gilt.

**[0036]** Das Funktionsprinzip der Vergleichsschaltung **10** wird unter Bezugnahme auf **Fig. 1C** beschrieben. **Fig. 1C** zeigt schematisch Drain-Strom-Gate-Spannungs- (**Id-Vg**-) Eigenschaften des Transistors **MO11**. Eine Kurve **9A** ist die **Id-Vg**-Kurve zu dem Zeitpunkt, zu dem **Vnin > Vref** gilt. Eine Kurve **9B** ist die **Id-Vg**-Kurve zu dem Zeitpunkt, zu dem **Vnin < Vref** gilt.

**[0037]** Wenn **Vnin > Vref** gilt, gilt **Imo1 > Imo2** und daher liegt die Spannung **Vcmp** auf „H“.

**[0038]** Eine Abnahme der Rückgate-Spannung verschiebt **Vt** des Transistors **MO11** positiv. Mit anderen Worten: Eine Abnahme der negativen Spannung **Vnin** verringert den Strom **Imo1**. Wenn **Vnin < Vref** gilt, gilt **Imo1 < Imo2** und daher liegt die Spannung **Vcmp** auf „L“.

**[0039]** Als Nächstes werden Modifikationsbeispiele für das Differenzpaar beschrieben. In dem Beispiel der **Fig. 1A** werden die Spannungen **Vdda** und **Vssa** als Vorspannungen des Differenzpaars **14** verwendet, jedoch sind Vorspannungen nicht auf diese beschränkt. Durch Verwendung der Spannungen **Vdda** und **Vssa** als Vorspannungen des Differenzpaars **14** kann die Art von Spannungen reduziert werden, die in der Vergleichsschaltung **10** verwendet werden.

**[0040]** Alternativ kann das Rückgate des Transistors **MO12** elektrisch mit dem Anschluss **INP** verbunden sein, und eine Vorspannung, wie z. B. die Spannung **Vssa**, wird in das Gate eingegeben.

**[0041]** Eine Vergleichsschaltung **11**, die in **Fig. 2** dargestellt ist, beinhaltet anstelle des Differenzpaars **14** ein Differenzpaar **15**. Das Differenzpaar **15** beinhaltet Transistoren **MO13** und **MO14**. Der Anschluss **INN** ist elektrisch mit einem Gate des Transistors **MO13** verbunden. Der Anschluss **INP** ist elektrisch mit einem Gate des Transistors **MO14** verbunden. Eine Vorspannung (hier **Vdda**) wird in ein Rückgate des Transistors **MO13** eingegeben. Eine Vorspannung (hier **Vssa**) wird in ein Rückgate des Transistors **MO14** eingegeben.

**[0042]** Das Rückgate des Transistors **MO14** kann elektrisch mit dem Anschluss **INP** verbunden sein, und eine Vorspannung (z. B. **Vssa**) wird in das Gate eingegeben.

**[0043]** Die Vergleichsschaltung **10** kann ohne komplizierte Schaltungskonfiguration eine zu vergleichende negative Spannung direkt eingeben. Durch

Umwandeln einer negativen Bezugsspannung in eine positive Bezugsspannung wird mit Ausnahme der zu vergleichenden negativen Spannung ( $V_{nin}$ ) nur 0 V oder eine positive Spannung in die Vergleichsschaltung **10** eingegeben, was zu einem stabilen Betrieb der Vergleichsschaltung **10** führt. Das Gleiche gilt auch für die Vergleichsschaltung **11**.

<Vergleichsschaltungen 20 bis 25>

**[0044]** Als Nächstes werden spezifische Beispiele für eine Schaltungskonfiguration der Vergleichsschaltung beschrieben.

**[0045]** Eine Vergleichsschaltung **20**, die in **Fig. 3A** dargestellt ist, beinhaltet die Anschlüsse **INN**, **INP** und **OCM**, eine Differenzeingangsschaltung **30** und eine Ausgangsschaltung **40**.

**[0046]** Die Differenzeingangsschaltung **30** ist eine einstufige Differenzverstärkerschaltung und beinhaltet ein Differenzpaar **34** und Transistoren **MN1**, **MP1** und **MP2**.

**[0047]** Das Differenzpaar **34** weist die gleiche Schaltungskonfiguration wie diejenige des Differenzpaares **14** auf und beinhaltet Transistoren **MO1** und **MO2**. Ein Verbindungsknoten zwischen den Transistoren **MO1** und **MP1** wird als Knoten **X1** bezeichnet. Ein Verbindungsknoten zwischen den Transistoren **MO2** und **MP2** wird als Knoten **X2** bezeichnet.

**[0048]** Der Anschluss **INP** ist elektrisch mit einem Rückgate des Transistors **MO1** verbunden. Der Anschluss **INN** ist elektrisch mit einem Gate des Transistors **MO2** verbunden. Die Spannung **Vdda** wird in ein Gate des Transistors **MO1** eingegeben. Die Spannung **Vssa** wird in ein Rückgate des Transistors **MO2** eingegeben.

**[0049]** Der Transistor **MN1** dient als Stromquelle. Eine Spannung **Vb1** wird in ein Gate des Transistors **MN1** eingegeben. Bei der Spannung **Vb1** handelt es sich um eine positive Spannung.

**[0050]** Eine Stromspiegelschaltung besteht aus den Transistoren **MP1** und **MP2**. Die Stromspiegelschaltung dient als Lastkreis. Der Lastkreis kann aus den Transistoren **MP1** und **MP2** bestehen, die als Diode geschaltet sind. Alternativ können anstelle der Transistoren **MP1** und **MP2** zwei Widerstände bereitgestellt werden.

**[0051]** Die Ausgangsschaltung **40** ist elektrisch mit dem Knoten **X2** verbunden. Die Ausgangsschaltung **40** besteht aus einer zweistufigen CMOS-Inverterschaltung. Die CMOS-Inverterschaltung besteht aus Si-Transistoren.

**[0052]** Eine Vergleichsschaltung **21**, die in **Fig. 3B** dargestellt ist, ist ein Modifikationsbeispiel für die Vergleichsschaltung **20**. Eine Ausgangsschaltung **41** besteht aus einer einstufigen CMOS-Inverterschaltung. Ein Eingangsknoten der CMOS-Inverterschaltung ist elektrisch mit dem Knoten **X1** verbunden.

**[0053]** Eine Vergleichsschaltung **22**, die in **Fig. 4A** dargestellt ist, ist ein Modifikationsbeispiel für die Vergleichsschaltung **20**. Eine Ausgangsschaltung **42** der Vergleichsschaltung **22** besteht aus einer zweistufigen Sourcefolgerschaltung. Eine Vergleichsschaltung **23**, die in **Fig. 4B** dargestellt ist, ist ein Modifikationsbeispiel für die Vergleichsschaltung **22**. Eine Ausgangsschaltung **43** der Vergleichsschaltung **23** besteht aus einer einstufigen Sourcefolgerschaltung. Ein Eingangsknoten der Sourcefolgerschaltung ist elektrisch mit dem Knoten **X1** verbunden.

**[0054]** Eine Vergleichsschaltung **24**, die in **Fig. 4C** dargestellt ist, ist ein Modifikationsbeispiel für die Vergleichsschaltung **21** und beinhaltet eine Differenzeingangsschaltung **31**. Die Differenzeingangsschaltung **31** ist ein Modifikationsbeispiel für die Differenzeingangsschaltung **30** und beinhaltet anstelle des Transistors **MN1** einen Transistor **MO3**. Die Spannung **Vb1** wird in ein Gate des Transistors **MO3** eingegeben, und das Rückgate ist elektrisch mit dem Gate verbunden. Es sei angemerkt, dass eine Vorspannung (z. B. die Spannung **Vssa**) in das Rückgate des Transistors **MO3** eingegeben werden kann, und dass das Rückgate elektrisch mit dem Drain verbunden sein kann.

**[0055]** Die Vergleichsschaltungen **20** bis **24** geben die Spannung **Vcmp** auf „H“ aus, wenn  $V_{nin} > V_{nref}$  gilt, und geben die Spannung **Vcmp** auf „L“ aus, wenn  $V_{nin} < V_{nref}$  gilt. Die Beziehung zwischen dem Größenverhältnis zwischen **Vnin** und **Vref** und dem Pegel der Spannung **Vcmp** wird je nach der Schaltungskonfiguration oder dergleichen der Ausgangsschaltung angemessen geändert.

**[0056]** In der Vergleichsschaltung **20** kann der Anschluss **INP** elektrisch mit dem Gate des Transistors **MO1** verbunden sein, und eine Vorspannung (z. B. **Vdda**) kann in das Rückgate des Transistors **MO1** eingegeben werden. Der Anschluss **INN** kann elektrisch mit dem Rückgate des Transistors **MO2** verbunden sein, und eine Vorspannung (z. B. **Vssa**) kann in das Gate des Transistors **MO2** eingegeben werden. Das Gleiche kann auch für die Vergleichsschaltungen **21** bis **24** gelten.

«Dynamische Vergleichsschaltung»

**[0057]** Ein Konfigurationsbeispiel für die dynamische Vergleichsschaltung wird unter Bezugnahme auf **Fig. 5** beschrieben. Eine Vergleichsschaltung **25**, die in **Fig. 5** dargestellt ist, beinhaltet eine Differenz-

eingangsschaltung 32, eine Ausgangsschaltung 45, die Anschlüsse INN, INP und OCM sowie einen Anschluss OCMB. Die Spannungen Vdda und Vssa sowie ein Taktsignal CLK (nachstehend als Signal CLK bezeichnet) werden in die Vergleichsschaltung 25 eingegeben.

[0058] Die Vergleichsschaltung 25 vergleicht die negative Spannung Vnin mit der negativen Bezugsspannung Vnref und gibt die Spannung Vcmp und eine Spannung VcmpB, die den Vergleichsergebnissen entsprechen, von den Anschläßen OCM und OCMB aus. Die negative Spannung Vnin und die positive Bezugsspannung Vpref werden in die Anschlüsse INN bzw. INP eingegeben. Die positive Bezugsspannung Vpref wird in ähnlicher Weise wie in der Vergleichsschaltung 10 eingestellt.

[0059] Ströme Imo5 und Imo6 in der Zeichnung bedeuten Drain-Ströme der Transistoren MO5 bzw. MO6.

[0060] In der Vergleichsschaltung 25 kann die zu vergleichende negative Spannung (Vnin) in den Anschluss INN eingegeben werden, und eine Spannung von 0 V oder niedriger kann verwendet werden.

[0061] Die Differenzeingangsschaltung 32 beinhaltet die Transistoren MO5 und MO6 sowie Transistoren MN5, MN6, MN7, MP5, MP6, MP7 und MP8.

[0062] Ein Differenzpaar der Differenzeingangsschaltung 32 weist die gleiche Schaltungskonfiguration wie diejenige des Differenzpaars 34 auf und beinhaltet die Transistoren MO5 und MO6. Der Transistor MN7 dient als Stromquelle. Das Signal CLK wird in ein Gate des Transistors MN7 eingegeben.

[0063] Hier wird ein Verbindungsknoten zwischen den Transistoren MN5 und MP5 als Knoten X5 bezeichnet. Ein Verbindungsknoten zwischen den Transistoren MN6 und MP6 wird als Knoten X6 bezeichnet. Eine Latch-Schaltung besteht aus den Transistoren MN5, MP5, MN6 und MP6. Die Latch-Schaltung bestimmt auf Basis des Größenverhältnisses zwischen den Strömen Imo5 und Imo6 die Spannungspegel der Knoten X5 und X6.

[0064] Die Transistoren MP7 und MP8 sind Rücksetztransistoren. Das Ein-/Ausschalten der Transistoren MP7 und MP8 wird durch das Signal CLK gesteuert. Wenn die Transistoren MP7 und MP8 eingeschaltet sind, werden die Spannungen der Knoten X5 und X6 auf Vdda („H“) festgelegt.

[0065] Die Ausgangsschaltung 45 beinhaltet Inverterschaltungen 38 und 39. Eingangsanschlüsse der Inverterschaltungen 38 und 39 sind elektrisch mit dem Knoten X5 bzw. X6 verbunden. Ausgangsanschlüsse der Inverterschaltungen 38 und 39 sind

elektrisch mit den Anschläßen OCM bzw. OCMB verbunden.

[0066] In einer Periode, in der das Signal CLK auf „L“ liegt, führt die Vergleichsschaltung 25 das Vorladen durch. Da die Transistoren MP7 und MP8 eingeschaltet sind, werden die Knoten X5 und X6 auf „H“ festgelegt und werden die Anschlüsse OCM und OCMB auf „L“ festgelegt.

[0067] In einer Periode, in der das Signal CLK auf „H“ liegt, führt die Vergleichsschaltung 25 die Bewertung durch. Wenn eine Differenz zwischen den Strömen Imo5 und Imo6 auftritt, tritt eine Differenz zwischen der Treiberfähigkeit der zwei Inverterschaltungen auf, die in der Latch-Schaltung enthalten sind, so dass eine Spannungsdifferenz zwischen den Knoten X5 und X6 auftritt.

[0068] Wenn Vnin > Vnref gilt, gilt der Strom Imo5 > der Strom Imo6. Deshalb ist die Spannung des Knotens X5 niedriger als die Spannung des Knotens X6, und der Anschluss OCM und der Anschluss OCMB liegen auf „H“ bzw. „L“. Im Gegensatz dazu gilt, wenn Vnin < Vnref gilt, der Strom Imo5 < der Strom Imo6. Deshalb ist die Spannung des Knotens X5 höher als die Spannung des Knotens X6, und der Anschluss OCM und der Anschluss OCMB liegen auf „L“ bzw. „H“.

[0069] Da das Differenzpaar in der Vergleichsschaltung 20, die in Fig. 3A dargestellt ist, aus zwei OS-Transistoren mit Rückgates gebildet wird, kann die Spannung Vssa die Erdspannung sein. Daher ist es unnötig, eine negative Spannung in die Source des Transistors MN1 einzugeben.

[0070] Wenn eine negative Spannung in eine Source eines n-Kanal-Si-Transistors eingegeben wird, wird an eine parasitäre Diode (eine p-n-Übergang-Diode) zwischen einer p-Wanne und einem Source-Bereich eine Durchlassvorspannung angelegt. Dies verursacht einen Rückfluss des hohen Stroms von einem Substrat in den Source-Bereich. Um den Rückfluss des hohen Stroms zu verhindern, kommt eine Dreiwannenstruktur, bei der ein n-Kanal-Transistor von einem n-Wanne umgeben ist, im Allgemeinen zum Einsatz (z. B. siehe Fig. 3b und Fig. 6 in Patentdokument 3). Jedoch wird die Schaltungsfläche infolge des Dreiwannen-n-Kanal-Transistors erhöht.

[0071] Die Vergleichsschaltung 20 kann gebildet werden, ohne einen Dreiwannen-n-Kanal-Si-Transistor zu verwenden, und daher kann ihre Schaltungsfläche verringert werden. Das Gleiche gilt auch für die Vergleichsschaltungen 21 bis 25.

[0072] Wie vorstehend beschrieben, kann dank des Differenzpaars, das aus zwei n-Kanal-Transistoren mit Rückgates gebildet wird, die Vergleichsschalt-

tung bei dieser Ausführungsform, ohne komplizierte Schaltungskonfiguration, mit einer zu vergleichenden negativen Spannung versorgt werden, eine Bezugsspannung, die durch Umwandeln einer negativen Bezugsspannung in eine positive Spannung erhalten wird, verwenden und eine niedrige Stromversorgungsspannung zu 0 V (**GND**) machen. Die Vergleichsschaltung bei dieser Ausführungsform kann daher einen Vergleich mit hoher Genauigkeit zwischen einer negativen Spannung und einer negativen Bezugsspannung sowie einen stabilen Betrieb durchführen.

[Ausführungsform 2]

**[0073]** Eine Halbleitervorrichtung, die bei der Ausführungsform 1 gezeigte Vergleichsschaltung beinhaltet, wird bei dieser Ausführungsform beschrieben. Eine Vorrichtung zum Zuführen einer negativen Spannung zu der Halbleitervorrichtung wird als Beispiel beschrieben.

«Versorgungsvorrichtung 100

für eine negative Spannung»

**[0074]** Fig. 6 ist ein Blockdiagramm, das ein Strukturbispiel für eine Versorgungsvorrichtung für eine negative Spannung darstellt. Eine Versorgungsvorrichtung 100 für eine negative Spannung, die in Fig. 6 dargestellt ist, erzeugt intern eine negative Spannung und gibt die erzeugte negative Spannung an eine Vielzahl von Stromversorgungsanschlüssen aus. Die Versorgungsvorrichtung 100 für eine negative Spannung beinhaltet eine Steuerschaltung 111, eine Ladungspumpenschaltung 112, eine Vorspannungserzeugungsschaltung 114, einen Ausgangsspannungseinsteller 120 und eine Vielzahl von Anschlüssen OB. Der Anschluss OB ist ein Ausgangsanschluss für eine negative Spannung. Die Anzahl der Anschlüsse OB ist in diesem Beispiel vier aber ist nicht darauf beschränkt.

**[0075]** Um die vier Anschlüsse OB zu unterscheiden, werden Bezugszeichen [1] bis [4] verwendet. Wenn es nötig ist, einen beliebigen der Vielzahl von Anschlüssen OB zu spezifizieren, wird beispielsweise der eine als Anschluss OB[1] bezeichnet. Der Begriff „Anschluss OB“ bezeichnet einen beliebigen Anschluss OB. Das Gleiche gilt auch für andere Elemente.

**[0076]** Spannungen **Vdda**, **Vddd** und **GND**, die positive Bezugsspannung **Vpref**, ein Taktsignal **CK1** und ein Signal **WAKE** werden in die Versorgungsvorrichtung 100 für eine negative Spannung eingegeben. Es sei angemerkt, dass die Spannung **GND** 0 V (Erdspannung) ist und als niedrige Stromversorgungsspannung der Versorgungsvorrichtung 100 für eine negative Spannung verwendet wird. Die Spannung **Vddd** ist eine hohe Stromversorgungsspannung und

ist niedriger als die Spannung **Vdda**. Die Spannung **Vddd** wird in der Steuerschaltung 111 verwendet.

<Steuerschaltung 111>

**[0077]** Das Signal **WAKE** dient als Aktivierungssignal der Versorgungsvorrichtung 100 für eine negative Spannung. Die Steuerschaltung 111 steuert gemäß dem Signal **WAKE** die Ladungspumpenschaltung 112 und den Ausgangsspannungseinsteller 120. Die Steuerschaltung 111 dient hier als Gated-Taktpuffer. Die Steuerschaltung 111 erzeugt gemäß dem Signal **WAKE** ein Gated-Taktsignal **GCK1** (nachstehend als Taktsignal **GCK1** bezeichnet) aus dem Taktsignal **CK1**. Die Spannung mit niedrigem Pegel und die Spannung mit hohem Pegel des Taktsignals **CK1** ist **GND** bzw. **Vdda**.

**[0078]** Das Taktsignal **GCK1** wird sowohl in die Ladungspumpenschaltung 112 als auch in den Ausgangsspannungseinsteller 120 eingegeben.

<Ladungspumpenschaltung 112>

**[0079]** Die Ladungspumpenschaltung 112 dient als Spannungserzeugungsschaltung für eine negative Spannung. Fig. 7 stellt ein Beispiel für die Schaltungskonfiguration der Ladungspumpenschaltung 112 dar, bei der es sich um eine vierstufige Abwärts-Ladungspumpenschaltung handelt. Die Ladungspumpenschaltung 112 beinhaltet Anschlüsse **IN\_cp** und **OUT\_cp**, zwei Inverterschaltungen, vier OS-Transistoren und vier Kondensatoren. Wenn das Taktsignal **GCK1** aktiv ist, erzeugt die Ladungspumpenschaltung 112 aus der Spannung **GND**, die in den Anschluss **IN cp** eingegeben wird, die negative Spannung **Vcp** und gibt von dem Anschluss **OUT cp** die negative Spannung **Vcp** aus.

**[0080]** In dem Beispiel der Fig. 7 werden vier Transistoren in einem Transferpfad elektrischer Ladung zwischen den Anschlüssen **IN\_cp** und **OUT\_cp** bereitgestellt, aber die Anzahl von Transistoren ist nicht darauf beschränkt. Außerdem ist der Transistor, der in dem Transferpfad elektrischer Ladung bereitgestellt wird, nicht auf einen OS-Transistor beschränkt. Weitere Beispiele für eine Abwärts-Ladungspumpenschaltung, die als Ladungspumpenschaltung 112 verwendet werden kann, werden in Fig. 8A bis Fig. 8C dargestellt.

**[0081]** Eine Ladungspumpenschaltung 113A in Fig. 8A beinhaltet zwei Inverterschaltungen, vier n-Kanal-Si-Transistoren und vier Kondensatoren. Eine Ladungspumpenschaltung 113B in Fig. 8B beinhaltet drei n-Kanal-Si-Transistoren und einen OS-Transistor. Eine Ladungspumpenschaltung 113C in Fig. 8C beinhaltet zwei Inverterschaltungen, vier p-Kanal-Si-Transistoren und vier Kondensatoren.

<Vorspannungserzeugungsschaltung 114>

**[0082]** Die Vorspannungserzeugungsschaltung 114 erzeugt die Spannung **Vb1**. Die Spannung **Vb1** wird in den Ausgangsspannungseinsteller 120 eingegeben. Die Spannung **Vb1** kann ohne Vorspannungserzeugungsschaltung 114 von außen eingegeben werden.

<Ausgangsspannungseinsteller 120>

**[0083]** Der Ausgangsspannungseinsteller 120 wird bereitgestellt, um von jedem der Anschlüsse **OB** eine negative Spannung stabil auszugeben. Der Ausgangsspannungseinsteller 120 beinhaltet vier Halteschaltungen 122 für eine negative Spannung. Die Halteschaltung 122 für eine negative Spannung beinhaltet eine Ladungspumpenschaltung 123, eine Treiberschaltung 127 und eine Überwachungsschaltung 128. Die Halteschaltung 122[j] für eine negative Spannung (j ist eine ganze Zahl von 1 bis 4) steuert die Ausgangsspannung des Anschlusses **OB[j]**. **Fig. 9A** stellt ein Beispiel für die Schaltungskonfiguration der Halteschaltung 122 für eine negative Spannung dar.

<Halteschaltung 122 für eine negative Spannung>

**[0084]** Die Ladungspumpenschaltung 123 beinhaltet Transistoren **MO21** und **MO22** sowie Kondensatoren **C21** und **C22**. Die Ladungspumpenschaltung 123 verringert die Spannung **Vcp**, um eine Spannung **Vob** zu erzeugen. Die Spannung **Vob** wird von dem Kondensator **C22** gehalten. Die Spannung **Vob** wird von dem Anschluss **OB** ausgegeben.

**[0085]** Die Kapazität des Kondensators **C22** ist vorzugsweise größer als diejenige des Kondensators **C21**. Beispielsweise ist die Kapazität des Kondensators **C22** das Zwei- bis Zehnfache der Kapazität des Kondensators **C21**. Je nach der Kapazität, die für den Kondensator **C21** benötigt ist, kann der Kondensator **C21** aus einer parasitären Kapazität des Transistors **MO21** oder einer parasitären Kapazität zwischen dem Transistor **MO21** und einer Leitung oder dergleichen gebildet werden.

**[0086]** Ein Metalloxidhalbleiter weist eine Bandlücke von 2,5 eV oder mehr auf; daher ist der Sperrstrom eines OS-Transistors sehr klein. Beispielsweise kann der Sperrstrom pro Mikrometer der Kanalbreite bei Raumtemperatur (25 °C) und bei einer Source-Drain-Spannung von 3,5 V niedriger als  $1 \times 10^{-20}$  A, niedriger als  $1 \times 10^{-22}$  A oder niedriger als  $1 \times 10^{-24}$  A sein. Das heißt, dass das Ein-/Ausschaltverhältnis des Drain-Stroms größer als oder gleich 20 Stellen und kleiner als oder gleich 150 Stellen sein kann.

**[0087]** Bei einem Metalloxidhalbleiter handelt es sich um einen Halbleiter, der eine große Energielücke

aufweist und bei dem die Wahrscheinlichkeit geringer ist, dass Elektronen angeregt werden, und die effektive Masse eines Lochs groß ist. Folglich tritt bei einem OS-Transistor ein Avalanche-Durchbruch bzw. Lawinendurchbruch und dergleichen mit geringerer Wahrscheinlichkeit auf als bei einem Si-Transistor. Da eine Hot-Carrier-Degradation oder dergleichen infolge des Avalanche-Durchbruchs verhindert wird, weist der OS-Transistor eine hohe Spannungsfestigkeit zwischen dem Source und dem Drain auf.

**[0088]** Beispiele für ein Metalloxid, das in einem Kanalbildungsbereich verwendet werden kann, umfassen ein Zn-Oxid, ein Zn-Sn-Oxid, ein Ga-Sn-Oxid, ein In-Ga-Oxid, ein In-Zn-Oxid und ein In-M-Zn-Oxid (M ist Ti, Ga, Y, Zr, La, Ce, Nd, Sn oder Hf). Außerdem kann ein Oxid, das Indium und Zink enthält, eine oder mehrere Arten von Elementen enthalten, die aus Aluminium, Gallium, Yttrium, Kupfer, Vanadium, Beryllium, Bor, Silizium, Titan, Eisen, Nickel, Germanium, Zirconium, Molybdän, Lanthan, Cer, Neodym, Hafnium, Tantal, Wolfram, Magnesium und dergleichen ausgewählt werden.

**[0089]** Eine negative Spannung wird an ein Gate des Transistors **MO22** angelegt, daher ist die elektrische Verbindung eines Rückgates des Transistors **MO22** mit dem Gate effektiv, um den Abschaltstrom des Transistors **MO22** zu verringern. Das liegt daran, dass sich die Schwellenspannung des Transistors **MO22** positiv verschiebt, indem das Rückgate elektrisch mit dem Gate des Transistors **MO22** verbunden wird. Es sei angemerkt, dass der Abschaltstrom einen Drain-Strom bezeichnet, wenn die Gate-Source-Spannung des Transistors 0 V ist.

**[0090]** Deshalb ist die Tatsache, dass die Transistoren **MO21** und **MO22** OS-Transistoren mit Rückgates sind, effektiv, um eine negative Spannung lange Zeit stabil zuzuführen.

**[0091]** Da ein OS-Transistor über einem Si-Transistor angeordnet werden kann, sind die Transistoren **MO21** und **MO22**, die OS-Transistoren sind, effektiv, um die Größe der Versorgungsvorrichtung 100 für eine negative Spannung zu verringern.

**[0092]** Die Überwachungsschaltung 128 überwacht die Spannung **Vob** des Anschlusses **OB**. Die Überwachungsschaltung 128 besteht aus einer Vergleichsschaltung, in der eine Differenzverstärkerschaltung verwendet wird. Eine Vergleichsschaltung, die in **Fig. 9A** dargestellt ist, ist ein Modifikationsbeispiel für die Vergleichsschaltung 20 (siehe **Fig. 3A**). Hier beinhaltet eine Ausgangsschaltung eine CMOS-Inverterschaltung.

**[0093]** Der Anschluss **INP** ist elektrisch mit dem Anschluss **OB** verbunden. Die positive Bezugsspannung **Vpref** wird in den Anschluss **INN** eingegeben.

Der Anschluss **OCM** ist elektrisch mit einem Eingangsanschluss der Treiberschaltung **127** verbunden. Ein Signal **MON** ist die Ausgabe des Anschlusses **OCM**.

**[0094]** Eine Ausgangsspannung der Versorgungsvorrichtung **100** für eine negative Spannung wird auf eine negative Spannung **VBG** eingestellt. Die Überwachungsschaltung **128** vergleicht die Spannung **Vob** mit der negativen Spannung **VBG**, die als Referenz verwendet wird. Der Wert der positiven Bezugsspannung **Vpref** wird derart eingestellt, dass die Überwachungsschaltung **128** den Vergleich durchführen kann.

**[0095]** Hier überwacht die Überwachungsschaltung **128** die Verringerung der Spannung **Vob**. Wenn die Spannung **Vob** höher ist als die negative Spannung **VBG**, gibt die Überwachungsschaltung **128** das Signal **MON** auf „L“ aus. Wenn die Spannung **Vob** niedriger ist als die negative Spannung **VBG**, gibt die Überwachungsschaltung **128** das Signal **MON** auf „H“ aus.

**[0096]** Eine Vielzahl von positiven Bezugsspannungen kann je nach Schwankungen von Eigenschaften (z. B. Offset-Spannung) zwischen der Vielzahl von Überwachungsschaltungen **128** verwendet werden. Beispielsweise werden zwei positive Bezugsspannungen **Vpref1** und **Vpref2** mit Werten, die sich voneinander unterscheiden, in die Versorgungsvorrichtung **100** für eine negative Spannung eingegeben. Die positive Bezugsspannung **Vpref1** wird in Überwachungsschaltungen **128[1]** und **128[2]** eingegeben. Die positive Bezugsspannung **Vpref2** wird in Überwachungsschaltungen **128[3]** und **128[4]** eingegeben.

**[0097]** Die Treiberschaltung **127** führt eine logische Operation zwischen dem Signal **MON** und dem Takt signal **GCK1** durch und erzeugt ein Takt signal **GCK2** zum Betreiben der Ladungspumpenschaltung **123**. Die Treiberschaltung **127** weist eine Schaltungskonfiguration auf, bei der das Takt signal **GCK2** aktiv ist, wenn das Signal **MON** auf „L“ liegt, und das Takt signal **GCK2** in den anderen Perioden inaktiv ist. **Fig. 9B** zeigt ein Beispiel für eine Wahrheitstabelle der Treiberschaltung **127**.

«Betriebsbeispiel»

**[0098]** Das Betriebsbeispiel für die Versorgungsvorrichtung **100** für eine negative Spannung wird unter Bezugnahme auf **Fig. 10** beschrieben. **Fig. 10** ist ein Zeitdiagramm, das das Betriebsbeispiel für die Versorgungsvorrichtung **100** für eine negative Spannung zeigt. Ein Zeitpunkt wird durch **t0** und dergleichen dargestellt. Hier sind die Ausgangsspannung **Vcp** der Ladungspumpenschaltung **112** und Span-

nungen **Vob[1]** bis **Vob[4]** des Anschlusses **OB[1]** bis **OB[4]** zu dem Zeitpunkt **t0** 0 V (**GND**).

**[0099]** Bei einer Periode **Tc1** in **Fig. 10** handelt es sich um eine Zyklusperiode des Betriebs der Versorgungsvorrichtung **100** für eine negative Spannung. Das Signal **WAKE** dient als Chipaktivierungssignal der Versorgungsvorrichtung **100** für eine negative Spannung. In einer Periode, während der das Signal **WAKE** auf „H“ liegt, ist die Versorgungsvorrichtung **100** für eine negative Spannung aktiv.

**[0100]** In der Periode, während der das Signal **WAKE** auf „H“ liegt, ist das Takt signal **GCK1** aktiv, das von der Steuerschaltung **111** ausgegeben wird, und daher führt die Ladungspumpenschaltung **112** einen Abwärtsbetrieb durch. Hier wird die Ausgangsspannung **Vcp** der Ladungspumpenschaltung **112** von dem Zeitpunkt **t0** bis zum Zeitpunkt **t1** bei der negativen Spannung **VBG** gesättigt.

**[0101]** Da die Spannung **Vob[1]** zu dem Zeitpunkt **t0 GND** ist, wird ein Signal **MON[1]** auf „L“ von der Überwachungsschaltung **128[1]** ausgegeben. Auch Signale **MON[2]** bis **MON[4]** liegen auf „L“. Somit geben die Treiberschaltungen **127[1]** bis **127[4]** jeweils aktive Takt signale **GCK2[1]** bis **GCK2[4]** aus.

**[0102]** Da eine Ladungspumpenschaltung **123[1]** einen Abwärtsbetrieb durchführt, wird die Spannung **Vob[1]** verringert. Auch Ladungspumpenschaltungen **123[2]** bis **123[4]** führen einen Abwärtsbetrieb durch.

**[0103]** Schwankungen von elektrischen Eigenschaften (z. B. Schwellenspannung) der Transistoren **MO21** und **MO22** zwischen den Ladungspumpenschaltungen **123[1]** bis **123[4]** verursachen eine Differenz der Stromtreiberfähigkeit zwischen den Ladungspumpenschaltungen **123[1]** bis **123[4]**. Daher erreichen die Anschlüsse **OB[1]** bis **OB[4]** zu unterschiedlichen Zeitpunkten die negative Spannung **VBG**. Bei dieser Ausführungsform überwachen die Überwachungsschaltungen **128[1]** bis **128[4]** unabhängig die Spannungen der Anschlüsse **OB[1]** bis **OB[4]**, was Schwankungen der erhaltenen Spannungen zwischen den Anschläßen **OB[1]** bis **OB[4]** verringern kann, um diese Spannungen ungefähr gleich der negativen Spannung **VBG** zu machen.

**[0104]** Zum Beispiel wird eine Halteschaltung **122[1]** für eine negative Spannung beschrieben. Wenn die Überwachungsschaltung **128[1]** erkennt, dass die Spannung **Vob[1]** die negative Spannung **VBG** erreicht, gibt sie das Signal **MON[1]** auf „H“ an die Treiberschaltung **127[1]** aus. In Reaktion auf die Eingabe des Signals **MON[1]** auf „H“ legt die Treiberschaltung **127[1]** das Takt signal **GCK2** auf „H“ fest. Folglich stoppt die Ladungspumpenschaltung **123[1]** den

Abwärtsbetrieb, und die Spannung **Vob[1]** wird auf ungefähr die negative Spannung **VBG** eingestellt.

**[0105]** Da ein Transistor **MO22[1]** ein OS-Transistor mit sehr kleinem Sperrstrom ist, kann ein Kondensator **C22[1]** die negative Spannung **VBG** lange Zeit halten, auch wenn das Taktsignal **GCK2** inaktiv ist.

**[0106]** Halteschaltungen **122[2]** bis **122[4]** für eine negative Spannung arbeiten auf die vorstehende Weise, und Spannungen **Vob[2]** bis **Vob[4]** werden auf ungefähr die negative Spannung **VBG** eingestellt.

**[0107]** Da das Signal **WAKE** von dem Zeitpunkt **t1** bis zum Zeitpunkt **t2** auf „L“ liegt, ist die Versorgungsvorrichtung **100** für eine negative Spannung inaktiv. Hier wird Clock-Gating durchgeführt, um das Taktsignal **CK1** auf „L“ einzustellen, wodurch der Standby-Strom der Versorgungsvorrichtung **100** für eine negative Spannung verringert wird.

**[0108]** Dank der ausgezeichneten Halteeigenschaften der Halteschaltung **122** für eine negative Spannung kann eine Periode länger sein, während der das Signal **WAKE** auf „L“ liegt. Daher kann Power-Gating zum Stoppen der Zufuhr der Stromversorgungsspannungen (**Vddd**, **Vdda**) zur Versorgungsvorrichtung **100** für eine negative Spannung in der Periode durchgeführt werden. Das Power-Gating kann ferner den Stromverbrauch der Versorgungsvorrichtung **100** für eine negative Spannung verringern.

**[0109]** **Fig. 10** zeigt ein Beispiel zum Durchführen des Power-Gatings in einer Periode, während der das Signal **WAKE** auf „L“ liegt. Zu dem Zeitpunkt **t2** wird die Zufuhr der Spannungen **Vddd** und **Vdda** gestartet, das Signal **WAKE** geht auf „H“, und das Taktsignal **CK1** wird aktiviert. Der Betrieb der Versorgungsvorrichtung **100** für eine negative Spannung von dem Zeitpunkt **t2** bis zum Zeitpunkt **t3** ist dem Betrieb von dem Zeitpunkt **t0** bis zum Zeitpunkt **t1** ähnlich. In **Fig. 10** überschreiten die Spannungen **Vob[1]** bis **Vob[4]** von dem Zeitpunkt **t1** bis zum Zeitpunkt **t3** die negative Spannung **VBG** nicht. Wenn die Überwachungsschaltungen **128[1]** bis **128[4]** aktiviert werden, gehen Anschlüsse **OCM[1]** bis **OCM[4]** auf „L“ auf „H“. Deshalb befinden sich die Ladungspumpenschaltungen **123[1]** bis **123[4]** im Standby-Zustand.

**[0110]** Da die Halteschaltung **122** für eine negative Spannung die Funktion zum Steuern der Abwärtstransformation des Anschlusses **OB** und die Funktion zum Halten der Spannung des Anschlusses **OB** aufweist, kann die bestimmte negative Spannung von dem Anschluss **OB** lange Zeit stabil ausgegeben werden.

«Versorgungsvorrichtung 101 für eine negative Spannung»

**[0111]** Ein weiteres Konfigurationsbeispiel für die Versorgungsvorrichtung für eine negative Spannung wird unter Bezugnahme auf **Fig. 11**, **Fig. 12** sowie **Fig. 13A** und **Fig. 13B** beschrieben. In dem Konfigurationsbeispiel wird eine dynamische Vergleichsschaltung für eine Überwachungsschaltung für eine negative Spannung verwendet.

**[0112]** Eine Versorgungsvorrichtung **101** für eine negative Spannung, die in **Fig. 11** dargestellt ist, beinhaltet eine Steuerschaltung **141**, eine Ladungspumpenschaltung **142**, eine Teilerschaltung **143**, einen Ausgangsspannungseinsteller **150** und vier Anschlüsse **OB**. Der Ausgangsspannungseinsteller **150** beinhaltet vier Halteschaltungen **152** für eine negative Spannung.

**[0113]** Die Spannungen **Vdda**, **Vddd** und **GND**, die positive Bezugsspannung **Vpref**, die Taktsignal **CK1** und das Signal **WAKE** werden in die Versorgungsvorrichtung **101** für eine negative Spannung eingegeben.

**[0114]** Die Steuerschaltung **141** weist die gleiche Funktion wie die Steuerschaltung **111** auf. Die Steuerschaltung **141** erzeugt gemäß dem Signal **WAKE** das Taktsignal **GCK1**.

**[0115]** Die Ladungspumpenschaltung **142** weist die gleiche Schaltungskonfiguration wie die Ladungspumpenschaltung **112** auf (siehe **Fig. 7**). Die Ladungspumpenschaltung **142** führt in Reaktion auf das Taktsignal **GCK1** einen Abwärtsbetrieb durch, um die Spannung **Vcp** auszugeben.

**[0116]** Die Teilerschaltung **143** führt eine Frequenzteilung des Taktsignals **GCK1** durch, um ein Taktsignal **GCK3** zu erzeugen. Das Taktsignal **GCK3** wird in jede der vier Halteschaltungen **152** für eine negative Spannung eingegeben.

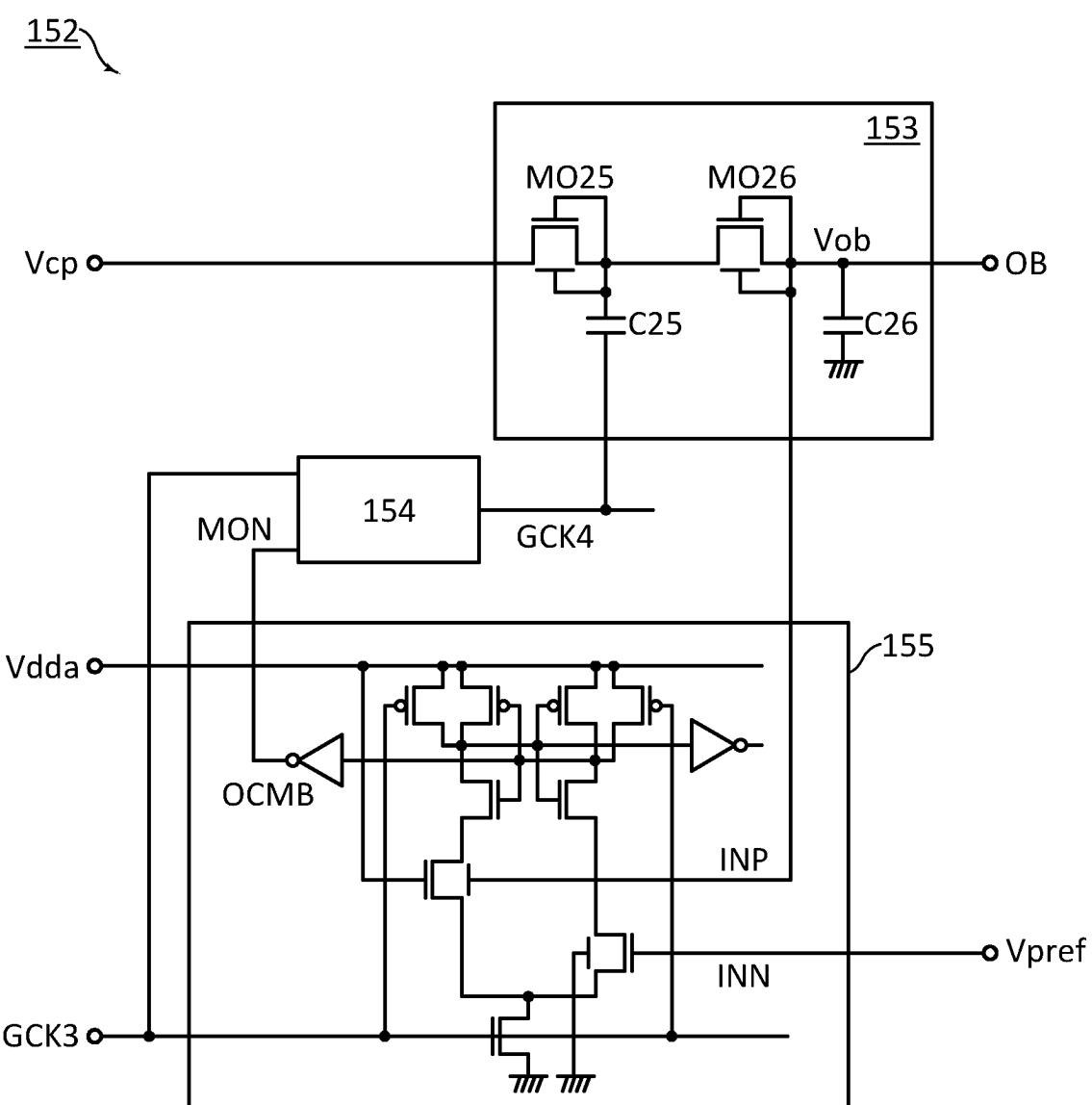

**[0117]** **Fig. 12** stellt ein Beispiel für die Schaltungskonfiguration der Halteschaltung **152** für eine negative Spannung dar. Die Halteschaltung **152** für eine negative Spannung beinhaltet eine Ladungspumpenschaltung **153**, eine Treiberschaltung **154** und eine Überwachungsschaltung **155**.

**[0118]** Die Ladungspumpenschaltung **153** weist die gleiche Schaltungskonfiguration wie die Ladungspumpenschaltung **123** auf und beinhaltet Transistoren **MO25** und **MO26** sowie Kondensatoren **C25** und **C26**.

**[0119]** Die Treiberschaltung **154** weist eine ähnliche Funktion wie die Treiberschaltung **127** auf (siehe **Fig. 9B**). Die Treiberschaltung **154** führt eine logi-

sche Operation zwischen dem Signal **MON** und dem Taktsignal **GCK3** durch und erzeugt ein Taktsignal **GCK4** zum Betreiben der Ladungspumpenschaltung **153**. Wenn das Signal **MON** auf „L“ liegt, ist das Taktsignal **GCK4** aktiv. Wenn das Signal **MON** nicht auf „L“ liegt, ist das Taktsignal **GCK4** inaktiv.

**[0120]** Die Überwachungsschaltung **155** beinhaltet die Vergleichsschaltung **25** (siehe Fig. 5). Das Taktsignal **GCK3** wird in die Überwachungsschaltung **155** eingegeben. Der Anschluss **INP** ist elektrisch mit dem Anschluss **OB** verbunden, und die positive Bezugsspannung **Vpref** wird in den Anschluss **INN** eingegeben. Der Anschluss **OCMB** ist elektrisch mit einem Eingangsanschluss der Treiberschaltung **154** verbunden.

**[0121]** Hier überwacht die Überwachungsschaltung **155** die Verringerung der Spannung **Vob**. Wenn die Spannung **Vob** höher ist als die negative Spannung **VBG**, gibt die Überwachungsschaltung **155** das Signal **MON** auf „L“ aus. Wenn die Spannung **Vob** niedriger ist als die negative Spannung **VBG**, gibt die Überwachungsschaltung **155** das Signal **MON** auf „H“ aus.

**[0122]** Die Versorgungsvorrichtung **101** für eine negative Spannung arbeitet auf ähnliche Weise wie die Versorgungsvorrichtung **100** für eine negative Spannung (siehe Fig. 10). Der Stromverbrauch der Versorgungsvorrichtung **101** für eine negative Spannung in einer Periode, während der das Signal **WAKE** auf „H“ liegt (d. h. dynamischer Stromverbrauch), ist kleiner als derjenige der Versorgungsvorrichtung **100** für eine negative Spannung.

**[0123]** In einer Periode, während der das Signal **WAKE** auf „H“ liegt, fließt ein Strom stets in die Überwachungsschaltung **128** der Versorgungsvorrichtung **100** für eine negative Spannung unabhängig von dem Pegel des Taktsignals **GCK2**. Im Gegensatz dazu wird der Ausgang **OCMB** der Überwachungsschaltung **155** in einer Periode, während der das Taktsignal **GCK3** auf „L“ liegt, auf „L“ festgelegt. Daher kann der Stromverbrauch der Überwachungsschaltung **155** kleiner als der Stromverbrauch der Überwachungsschaltung **128** sein.

**[0124]** Die Überwachungsschaltung **155** wird für jeden Anschluss **OB** bereitgestellt, so dass eine negative Spannung von jedem Anschluss **OB** stabil ausgegeben werden kann. Wenn die Anzahl von Anschlüssen **OB** zunimmt, vergrößert sich jedoch der Einfluss des Stromverbrauchs der Überwachungsschaltung **155**. Daher ist die Verringerung des Stromverbrauchs der Überwachungsschaltung **155** effektiv, um den gesamten dynamischen Stromverbrauch der Versorgungsvorrichtung **101** für eine negative Spannung zu verringern.

**[0125]** Um einen dynamischen Stromverbrauch zu verringern, wird ein Taktsignal auf eine niedrige Geschwindigkeit eingestellt. Wenn das Taktsignal **GCK1** auf eine niedrige Geschwindigkeit eingestellt wird, wird die Zeit dazu benötigt, dass die Spannung **Vcp** die negative Spannung **VBG** erreicht. Mit anderen Worten: Die Zeit, während der das Signal **WAKE** auf „H“ liegt, wird länger. Daher wird nur das Taktsignal **GCK3** auf eine niedrige Geschwindigkeit eingestellt, so dass ein dynamischer Stromverbrauch der Versorgungsvorrichtung **101** für eine negative Spannung effektiv verringert werden kann.

<Weiteres Konfigurationsbeispiel

für die Überwachungsschaltung>

**[0126]** Da die Überwachungsschaltung **155** aus einer dynamischen Vergleichsschaltung besteht, könnte das Signal **MON** des Anschlusses **OCM** instabil werden, wenn die gleiche Menge an Strom durch zwei OS-Transistoren eines Differenzpaars fließt. Als Nächstes werden Maßnahmen zur Stabilisierung des Signals **MON** unter Bezugnahme auf Fig. 13A und Fig. 13B beschrieben.

**[0127]** Fig. 13A stellt ein Beispiel dar, in dem die positive Bezugsspannung für die dynamische Vergleichsschaltung in Reaktion auf das Signal **MON** umgeschaltet wird. Fig. 13B stellt ein Beispiel dar, in dem die Stromversorgung zur Differenzeingangsschaltung der dynamischen Vergleichsschaltung in Reaktion auf das Signal **MON** gesteuert wird.

(Überwachungsschaltung 161)

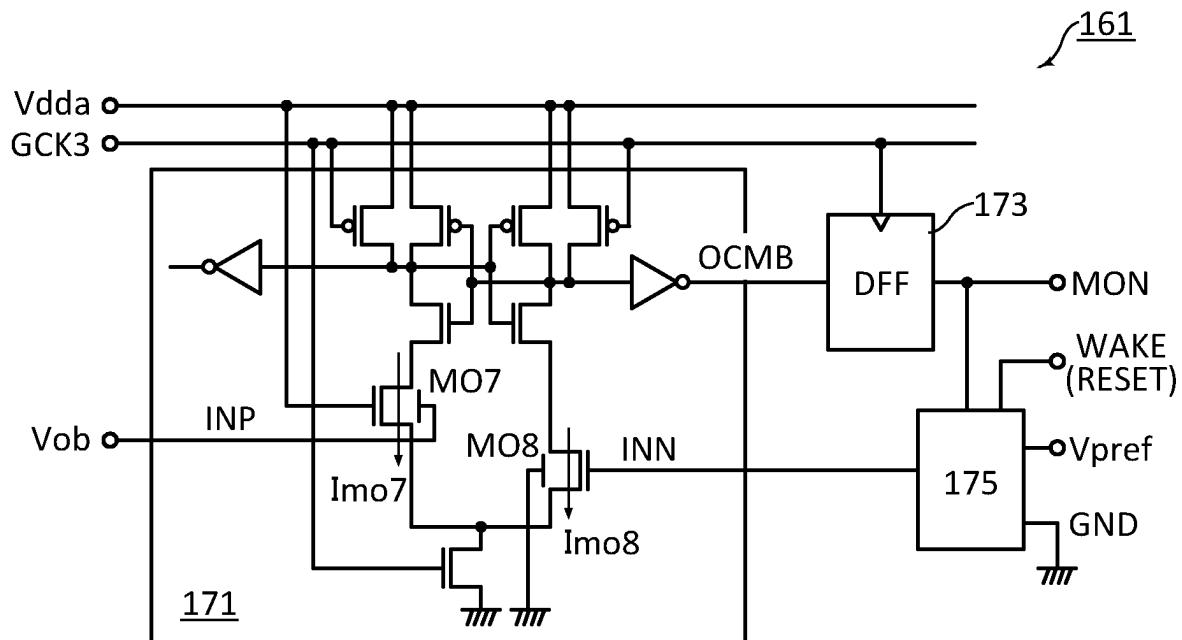

**[0128]** Eine Überwachungsschaltung **161**, die in Fig. 13A dargestellt ist, beinhaltet eine Vergleichsschaltung **171**, eine Latch-Schaltung **173** und eine Auswahlschaltung **175**.

**[0129]** Die Vergleichsschaltung **171** besteht aus der Vergleichsschaltung **25**. Ein Differenzpaar der Vergleichsschaltung **171** besteht aus Transistoren **MO7** und **MO8**. Ströme **Imo7** und **Imo8** sind Drain-Ströme der Transistoren **MO7** bzw. **MO8**.

**[0130]** Daten der Latch-Schaltung **173** werden durch die Ausgabe der Vergleichsschaltung **171** synchron mit dem Anstieg des Taktsignals **GCK3** aktualisiert. Ein Ausgangssignal der Latch-Schaltung **173** ist das Signal **MON**. Beispielsweise kann die Latch-Schaltung **173** eine Verzögerungs-Flipflop- (delay flip-flop, DFF-) Schaltung beinhalten.

**[0131]** Die Auswahlschaltung **175** wählt eine Spannung, die in den Anschluss **INN** der Vergleichsschaltung **171** eingegeben wird, aus der positiven Bezugsspannung **Vpref** und der Spannung **GND** aus. Das Signal **MON** und das Signal **WAKE** werden in die Auswahlschaltung **175** eingegeben. Das Signal **WA-**

**KE** dient als Rücksetzsignal (RESET) für die Auswahlschaltung **175**. Es sei angemerkt, dass ein Signal außer dem Signal **WAKE** als Rücksetzsignal verwendet werden kann.

[0132] Das Betriebsbeispiel für die Überwachungsschaltung **161** wird beschrieben. Wenn das Signal **WAKE** auf „L“ auf „H“ geht, wird die Auswahlschaltung **175** zurückgesetzt, um dem Anschluss **INN** die positive Bezugsspannung **Vpref** zuzuführen. Wenn das Taktignal **GCK3** aktiv ist, vergleicht die Vergleichsschaltung **171** die Spannung **Vob** des Anschlusses **OB** mit der negativen Spannung **VBG**. Wenn die Spannung **Vob** höher ist als die negative Spannung **VBG**, liegt das Signal **MON** auf „L“. Wenn das Signal **MON** auf „L“ liegt, gibt die Auswahlschaltung **175** die positive Bezugsspannung **Vpref** in den Anschluss **INN** ein.

[0133] Wenn die Spannung **Vob** niedriger als die negative Spannung **VBG** wird und das Taktignal **GCK3** auf „H“ liegt, wird ein Signal auf „H“ von dem Anschluss **OCMB** ausgegeben. Zu diesem Zeitpunkt kann der Strom **Imo7** dem Strom **Imo8** gleichen, so dass die Ausgabe des Anschlusses **OCMB** oszillieren könnte. Wenn die Auswahlschaltung **175** den Anstieg des Signals **MON** mit der vorbestimmten Häufigkeit (einmal oder mehrmals) erkennt, wird dem Anschluss **INN** die Spannung **GND** zugeführt. Dann wird der Strom **Imo8** verringert, um eine Differenz zwischen dem Strom **Imo7** und dem Strom **Imo8** zu erzeugen, so dass die Ausgabe des Anschlusses **OCMB** stabilisiert wird. Der Anschluss **OCMB** kann ein Signal auf „H“ stabil ausgeben, wenn das Taktignal **GCK3** auf „H“ liegt.

[0134] In diesem Beispiel wird die Spannung **GND** in den Anschluss **INN** eingegeben, aber es gibt keine Beschränkung bezüglich eines Signals, solange es eine Differenz zwischen den Strömen **Imo7** und **Imo8** gibt, wenn das Signal **MON** auf „H“ liegt. Eine positive Spannung, die kleiner ist als die Spannung **Vpref**, kann in den Anschluss **INN** eingegeben werden. Durch die Verwendung der Spannung **GND** steigen die Anzahl der Typen der zu verwendenden Spannung nicht an.

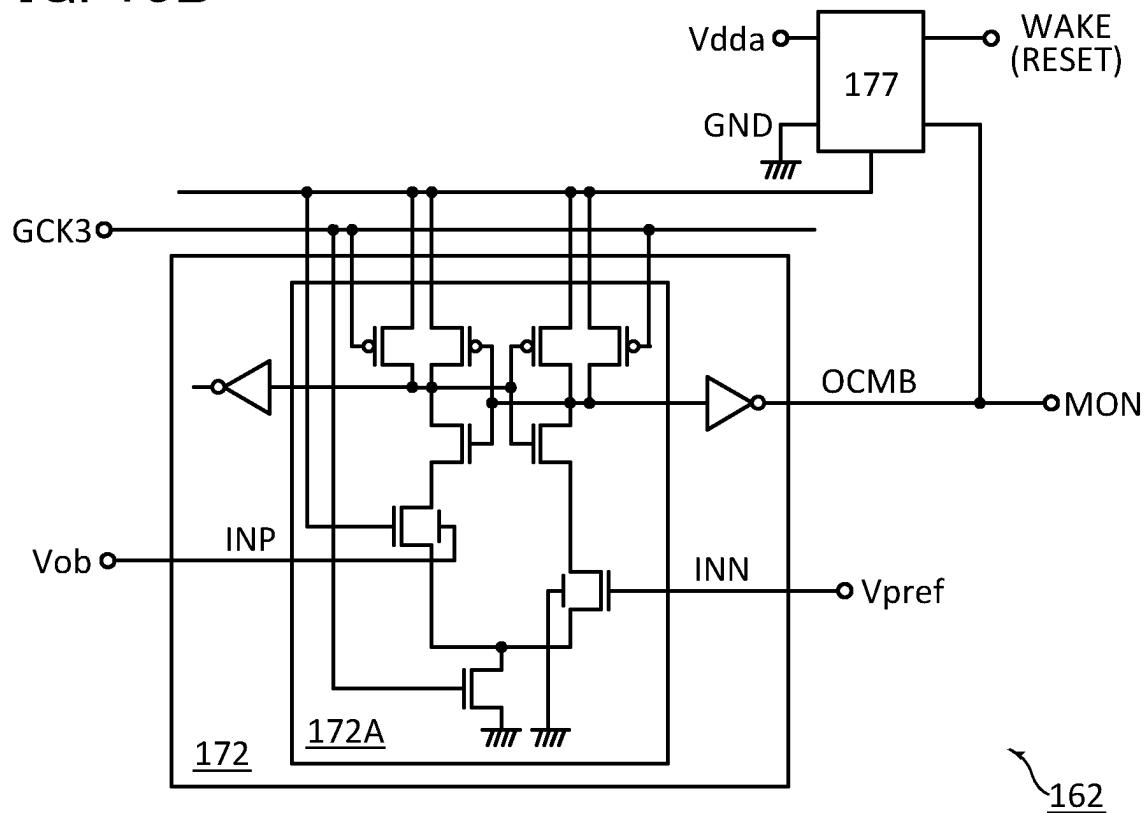

(Überwachungsschaltung 162)

[0135] Eine Überwachungsschaltung **162**, die in Fig. 13B dargestellt ist, beinhaltet eine Vergleichsschaltung **172** und eine Auswahlschaltung **177**. Die Vergleichsschaltung **172** besteht aus der Vergleichsschaltung **25**. Die Latch-Schaltung **173** kann in der Überwachungsschaltung **162** bereitgestellt werden, wie in der Überwachungsschaltung **161**.

[0136] Die Auswahlschaltung **177** steuert die Zufuhr einer hohen Stromversorgungsspannung zu einer Differenzeingangsschaltung **172A** der Vergleichs-

schaltung **172**. Die Signale **MON** und **WAKE** werden in die Auswahlschaltung **177** eingegeben. Das Signal **WAKE** dient als Rücksetzsignal der Auswahlschaltung **177**. Ein Signal außer dem Signal **WAKE** kann als Rücksetzsignal verwendet werden.

[0137] Wenn das Signal **WAKE** auf „L“ auf „H“ geht, wird die Auswahlschaltung **177** zurückgesetzt, um der Differenzeingangsschaltung **172A** die Spannung **Vdda** zuzuführen. Wenn das Taktignal **GCK3** aktiv ist, vergleicht die Vergleichsschaltung **172** die Spannung **Vob** des Anschlusses **OB** mit der negativen Spannung **VBG**. Wenn die Auswahlschaltung **177** den Anstieg des Signals **MON** mit der vorbestimmten Häufigkeit (einmal oder mehr) erkennt, wird der Differenzeingangsschaltung **172A** die Spannung **GND** zugeführt. Folglich werden zwei Inverterschaltungen in der Differenzeingangsschaltung **172A** inaktiviert, und daher oszilliert die Ausgabe der Vergleichsschaltung **172** nicht.

[0138] Die Versorgungsvorrichtung für eine negative Spannung bei dieser Ausführungsform ist zu einer Stromversorgungsschaltung für eine negative Spannung bei verschiedenen Halbleitervorrichtungen geeignet. Als Halbleitervorrichtung, bei der die Versorgungsvorrichtung für eine negative Spannung als Stromversorgungsschaltung verwendet wird, gibt es beispielsweise verschiedene Halbleitervorrichtungen, bei denen eine Substratvorspannung eine negative Spannung ist (z. B. ein DRAM und einen Bildsensor), eine Halbleitervorrichtung, die mit einer negativen Spannung betrieben wird (z. B. eine Speichervorrichtung, wie z. B. einen Flash-Speicher), und eine Halbleitervorrichtung, die einen OS-Transistor mit einem Rückgate beinhaltet. Bei der Ausführungsform 3 wird ein Strukturbeispiel für eine Halbleitervorrichtung beschrieben, die die Versorgungsvorrichtung für eine negative Spannung beinhaltet.

[Ausführungsform 3]

«Speichervorrichtung»

[0139] Hier wird eine Speichervorrichtung, deren Datenhalteabschnitt einen OS-Transistor beinhaltet, als Halbleitervorrichtung beschrieben, bei der ein OS-Transistor verwendet wird.

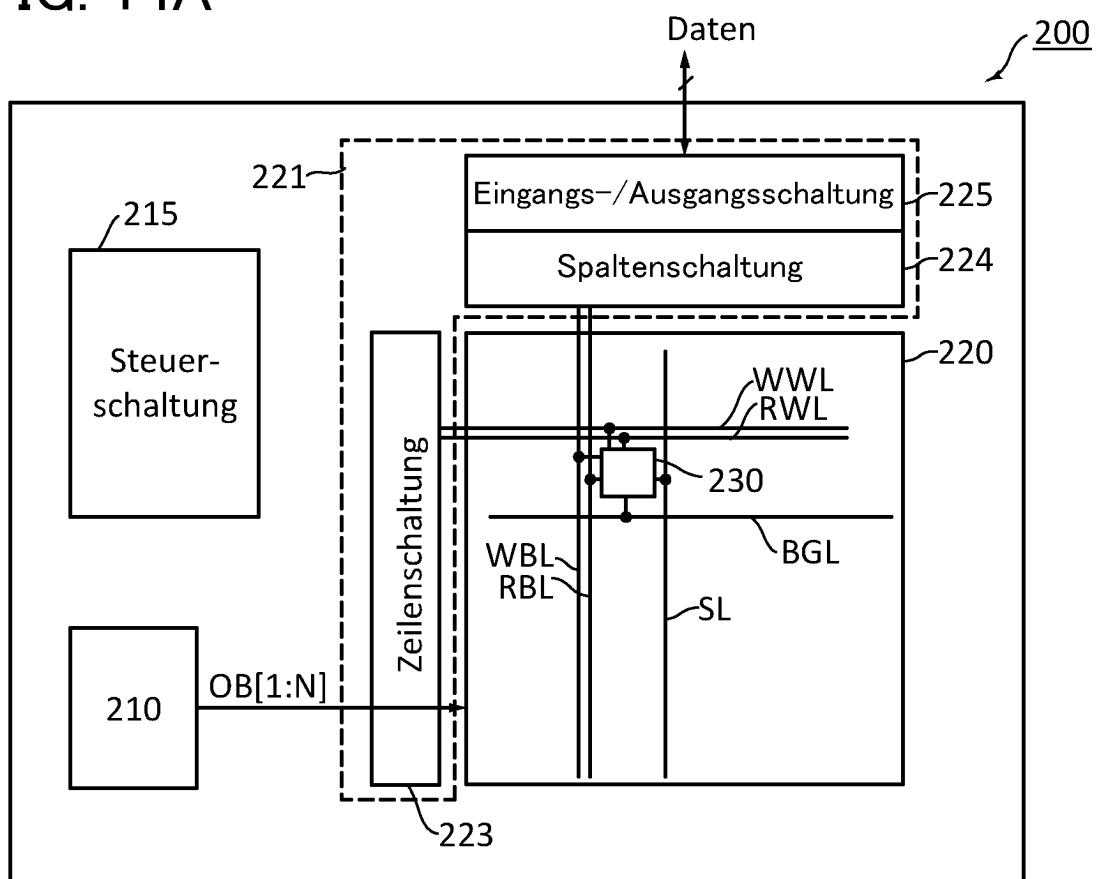

[0140] Eine Speichervorrichtung **200**, die in Fig. 14A dargestellt ist, beinhaltet eine Versorgungsvorrichtung **210** für eine negative Spannung, eine Steuerschaltung **215**, ein Speicherzellenarray **220** und eine Peripherieschaltung **221**. Die Peripherieschaltung **221** beinhaltet eine Zeilenschaltung **223**, eine Spaltenschaltung **224** und eine Eingangs-/Ausgangsschaltung **225**.

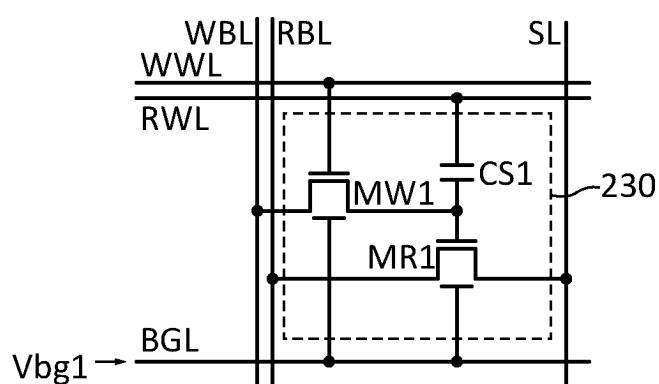

[0141] Das Speicherzellenarray **220** beinhaltet eine Speicherzelle **230**, eine Auslese-Wortleitung **RWL**,

eine Schreib-Wortleitung **WWL**, eine Auslese-Bitleitung **RBL**, eine Schreib-Bitleitung **WBL**, eine Source-Leitung **SL** und eine Leitung **BGL**. Es sei angemerkt, dass die Auslese-Wortleitung **RWL** und die Schreib-Wortleitung **WWL** als Wortleitung **RWL** bzw. Wortleitung **WWL** bezeichnet werden können. Die Auslese-Bitleitung **RBL** und die Schreib-Bitleitung **WBL** können als Bitleitung **RBL** bzw. Bitleitung **WBL** bezeichnet werden.

**[0142]** Die Steuerschaltung **215** steuert die gesamte Speichervorrichtung **200** und führt das Schreiben von Daten **WDA** und das Lesen von Daten **RDA** durch. Die Steuerschaltung **215** verarbeitet Befehlssignale (z. B. ein Chipaktivierungssignal und ein Schreibaktivierungssignal) von außen und erzeugt Steuersignale für die Peripherieschaltungen **221**.

**[0143]** Die Versorgungsvorrichtung für eine negative Spannung, die bei der Ausführungsform **2** beschrieben wird, wird als Versorgungsvorrichtung **210** für eine negative Spannung verwendet. Die Versorgungsvorrichtung **210** für eine negative Spannung beinhaltet  $N$  Anschlüsse **OB[1]** bis **OB[N]** ( $N$  ist eine ganze Zahl von 2 oder mehr). Die Anschlüsse **OB[1]** bis **OB[N]** geben jeweils eine negative Spannung  $V_{bg1}$  aus. Das Speicherzellenarray **220** ist in  $N$  Blöcke eingeteilt. Die Leitung **BGL** jedes Blocks ist elektrisch mit dem Anschluss **OB** verbunden.

**[0144]** Die Zeilenschaltung **223** weist eine Funktion zum Auswählen einer Zeile auf, auf die zugegriffen werden soll. Beispielsweise beinhaltet die Zeilenschaltung **223** einen Zeilendecoder und einen Wortleitungstreiber. Die Spaltenschaltung **224** weist eine Funktion zum Vorladen der Bitleitungen **WBL** und **RBL**, eine Funktion zum Schreiben von Daten in die Bitleitung **WBL**, eine Funktion zum Verstärken von Daten der Bitleitung **RBL**, eine Funktion zum Lesen von Daten von der Bitleitung **RBL** und der gleichen auf. Die Eingangs-/Ausgangsschaltung **225** weist eine Funktion zum Halten von Schreibdaten, eine Funktion zum Halten von Auslesedaten und der gleichen auf.

**[0145]** Die Konfiguration der Peripherieschaltungen **221** wird in Abhängigkeit von der Konfiguration, dem Ausleseverfahren, dem Schreibverfahren und der gleichen des Speicherzellenarrays **220** angemessen geändert.

<Speicherzelle 230>

**[0146]** **Fig. 14B** stellt das Beispiel für die Schaltungskonfiguration der Speicherzelle **230** dar. Die Speicherzelle **230** in diesem Beispiel ist eine 2-Transistor- (2T-) Verstärkungszelle. Die Speicherzelle **230** beinhaltet Transistoren **MW1** und **MR1** sowie einen Kondensator **CS1**. Die Transistoren **MW1** und **MR1** sind ein Schreibtransistor bzw. ein Auslesetransistor.

Die Rückgates der Transistoren **MW1** und **MR1** sind elektrisch mit der Leitung **BGL** verbunden.

**[0147]** Da der Auslesetransistor ein OS-Transistor ist, verbraucht die Speicherzelle **230** keinen Strom zum Halten von Daten. Daher ist die Speicherzelle **230** eine Speicherzelle mit geringem Stromverbrauch, die lange Zeit Daten halten kann. Die Speichervorrichtung **200** kann als nichtflüchtige Speichervorrichtung verwendet werden. Der OS-Transistor und der Kondensator können über einem Si-Transistor angeordnet werden. Demzufolge kann das Speicherzellenarray **220** über der Peripherieschaltung **221** angeordnet werden, was zu einem höherem Integrationsgrad des Speicherzellenarrays **220** führt.

**[0148]** Weitere Konfigurationsbeispiele für eine Speicherzelle werden unter Bezugnahme auf **Fig. 15A** bis **Fig. 15F** beschrieben.

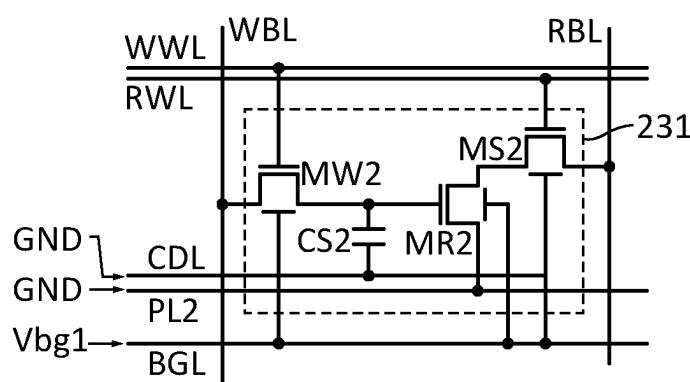

<Speicherzellen 231 bis 235>

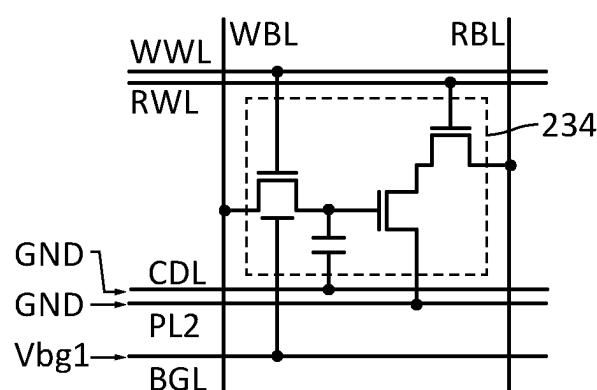

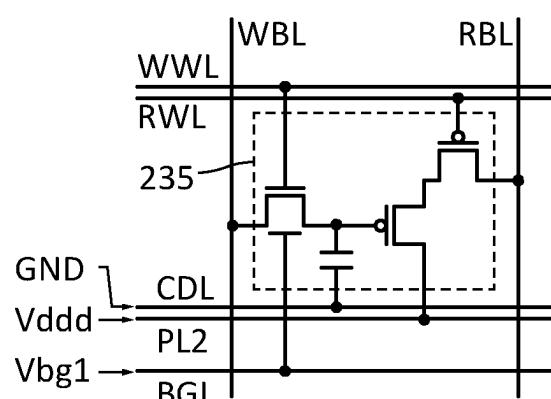

**[0149]** Eine Speicherzelle **231**, die in **Fig. 15A** dargestellt ist, ist eine 3T-Verstärkungszelle, die Transistoren **MW2**, **MR2** und **MS2** sowie einen Kondensator **CS2** beinhaltet. Die Transistoren **MW2**, **MR2** und **MS2** sind ein Schreibtransistor, ein Auslesetransistor bzw. ein Auswahltransistor. Rückgates der Transistoren **MW2**, **MR2** und **MS2** sind elektrisch mit der Leitung **BGL** verbunden. Die Speicherzelle **231** ist elektrisch mit den Wortleitungen **RWL** und **WWL**, den Bitleitungen **RBL** und **WBL**, einer Kondensatorleitung **CDL** und einer Stromversorgungsleitung **PL2** verbunden. Beispielsweise wird eine Spannung **GND** (eine niedrige Stromversorgungsspannung) in die Kondensatorleitung **CDL** und die Stromversorgungsleitung **PL2** eingegeben.

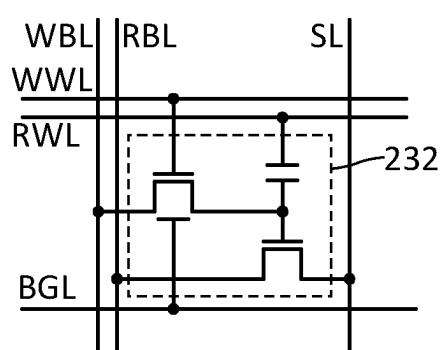

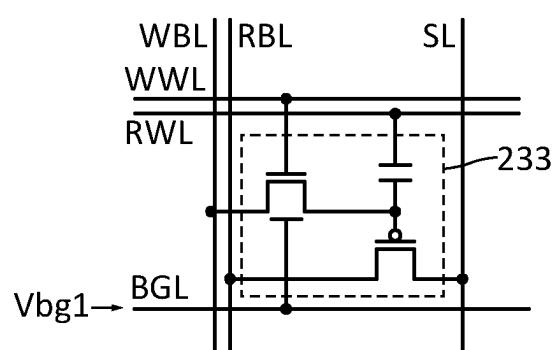

**[0150]** **Fig. 15B** und **Fig. 15C** stellen weitere Konfigurationsbeispiele für eine 2T-Verstärkungszelle dar. In einer Speicherzelle **232**, die in **Fig. 15B** dargestellt ist, wird ein n-Kanal-Si-Transistor als Auslesetransistor verwendet. In einer Speicherzelle **233**, die in **Fig. 15C** dargestellt ist, wird ein p-Kanal-Si-Transistor als Auslesetransistor verwendet.

**[0151]** **Fig. 15D** und **Fig. 15E** stellen weitere Konfigurationsbeispiele für eine 3T-Verstärkungszelle dar. In einer Speicherzelle **234**, die in **Fig. 15D** dargestellt ist, werden n-Kanal-Si-Transistoren als Auslesetransistor und Auswahltransistor verwendet. In einer Speicherzelle **235**, die in **Fig. 15E** dargestellt ist, werden p-Kanal-Si-Transistoren als Auslesetransistor und Auswahltransistor verwendet. In dem Beispiel der **Fig. 15E** wird die Spannung **Vddd** (eine hohe Stromversorgungsspannung) in die Stromversorgungsleitung **PL2** eingegeben.

**[0152]** In diesen Verstärkungszellen kann eine Bitleitung, die als beide der Auslese-Bitleitung **RBL** und

der Schreib-Bitleitung **WBL** dient, bereitgestellt werden.

<Speicherzelle 236>

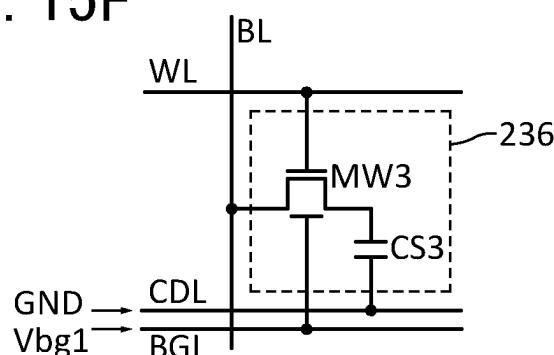

**[0153]** Fig. 15F stellt ein Beispiel für eine 1T1C- (Capacitor bzw. Kondensator) Speicherzelle dar. Eine Speicherzelle **236**, die in Fig. 15F dargestellt ist, ist elektrisch mit einer Wortleitung **WL**, einer Bitleitung **BL**, der Kondensatorleitung **CDL** und der Leitung **BGL** verbunden. Die Speicherzelle **236** beinhaltet einen Transistor **MW3** und einen Kondensator **CS3**. Ein Rückgate des Transistors **MW3** ist elektrisch mit der Leitung **BGL** verbunden.

<Speicherzelle 237>

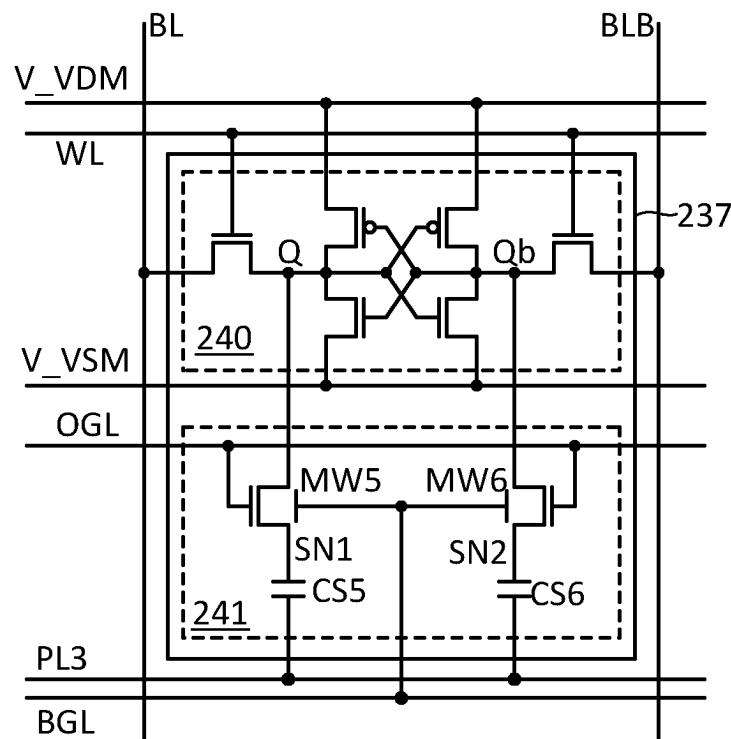

**[0154]** Eine Speicherzelle **237**, die in Fig. 16A dargestellt ist, beinhaltet eine Speicherzelle **240** und eine Sicherungsschaltung **241**. Die Speicherzelle **240** weist die gleiche Schaltungskonfiguration wie eine normale 6T-SRAM-Zelle auf.

**[0155]** Die Sicherungsschaltung **241** ist eine Schaltung zum Sichern von Daten von Knoten **Q** und **Qb**, die in der Speicherzelle **240** enthalten sind, und besteht aus zwei 1T1C-Zellen. Knoten **SN1** und **SN2** sind Halteknoten. Eine Verstärkungszelle, die aus einem Transistor **MW5** und einem Kondensator **CS5** besteht, sichert Daten des Knotens **Q**. Eine Verstärkungszelle, die aus einem Transistor **MW6** und dem Kondensator **CS6** besteht, sichert Daten eines Knotens **Qb**.

**[0156]** Da die Transistoren **MW5** und **MW6** OS-Transistoren sind, kann die Speicherzelle **240** über der Sicherungsschaltung **241** angeordnet werden. Demzufolge kann der zusätzliche Flächenverbrauch der Speicherzelle **237** infolge Zusatzes der Sicherungsschaltung **241** verringert werden. Der zusätzliche Flächenverbrauch kann null sein.

**[0157]** Die Speicherzelle **240** ist elektrisch mit Stromversorgungsleitungen **V\_VDM** und **V\_VSM**, der Wortleitung **WL** und einem Bitleitungspaar (**BL** und **BLB**) verbunden. Die Stromversorgungsleitungen **V\_VDM** und **V\_VSM** sind Stromversorgungsleitungen für **Vddd** bzw. **GND**. Die Sicherungsschaltung **241** ist elektrisch mit Leitungen **OGL** und **BGL** sowie einer Stromversorgungsleitung **PL3** verbunden. Die Spannung **GND** wird in die Stromversorgungsleitung **PL3** eingegeben.

**[0158]** Die Speicherzelle **237** in einem normalen Zustand arbeitet als SRAM-Zelle. Das Betriebsbeispiel für die Speicherzelle **237** wird unter Bezugnahme auf Fig. 16B beschrieben. Wenn auf die Speicherzelle **237** in einem vorbestimmten Zeitraum oder länger nicht zugegriffen wird, werden die Zufuhr der Spannungen **Vddd** und **GND** zu den Stromversorgungslei-

tungen **V\_VDM** und **V\_VSM** gestoppt. Bevor die Zufuhr der Spannung **Vddd** gestoppt wird, werden Daten der Knoten **Q** und **Qb** in die Sicherungsschaltung **241** geschrieben. Ein Zeitpunkt wird in Fig. 16B durch **t1**, **t2** und dergleichen dargestellt.

(Normalbetrieb)

**[0159]** Vor dem Zeitpunkt **t1** befindet sich die Speicherzelle **237** in einem normalen Betriebszustand (einem Schreibzustand oder einem Auslesezustand). Die Speicherzelle **237** arbeitet auf eine ähnliche Weise wie ein Single-Port-SRAM. Zu dem Zeitpunkt **t1** liegen die Knoten **Q**, **Qb**, **SN1** und **SN2** auf „H“, „L“, „L“ bzw. „H“.

(Sicherung)

**[0160]** Die Leitung **OGL** geht zu **t1** auf „H“, wodurch ein Sicherungsvorgang startet und die Transistoren **MW5** und **MW6** eingeschaltet werden. Die Spannung des Knotens **SN1** wird von **GND** auf **Vddd** erhöht. Die Spannung des Knotens **SN2** wird von **Vddd** auf **GND** verringert. Die Leitung **OGL** geht zu **t2** auf „L“, wodurch der Sicherungsvorgang endet. Daten des Knotens **Q** und Daten des Knotens **Qb** zu **t1** werden in den Knoten **SN1** bzw. den Knoten **SN2** geschrieben.

(Power-Gating)

**[0161]** Power-Gating startet zu **t2**. Die Spannung der Stromversorgungsleitung **V\_VDM** wird von **Vddd** auf **GND** geändert. Eine Spannungsdifferenz zwischen den Stromversorgungsleitungen **V\_VDM** und **V\_VSM** wird verringert, wodurch die Speicherzelle **240** inaktiv wird. Obwohl Daten in der Speicherzelle **240** verloren gehen, hält die Sicherungsschaltung **241** Daten kontinuierlich. Während des Power-Gatings befinden sich die Bitleitungen **BL** und **BLB** in einem potentialfreien Zustand.

(Wiederherstellung)

**[0162]** Bei einem Wiederherstellungsvorgang handelt es sich um einen Vorgang zur Wiederherstellung von Daten der Speicherzelle **240** unter Verwendung von Daten, die in der Sicherungsschaltung **241** gehalten werden. Im Wiederherstellungsvorgang dient die Speicherzelle **240** als Leseverstärker zum Erfassen von Daten in den Knoten **Q** und **Qb**.