República Federativa do Brasil

Ministério da Economia

Instituto Nacional da Propriedade Industrial

**(11) BR 112017008727-8 B1**

**(22) Data do Depósito: 04/09/2015**

**(45) Data de Concessão: 28/06/2022**

**(54) Título: ESTRUTURA DE PACOTE DE SAÍDA EM LEQUE DE ALTA DENSIDADE**

**(51) Int.Cl.: H01L 23/498.**

**(30) Prioridade Unionista:** 22/04/2015 US 14/693,820; 31/10/2014 US 62/073,804.

**(73) Titular(es):** QUALCOMM INCORPORATED.

**(72) Inventor(es):** DONG WOOK KIM; HONG BOK WE; JAE SIK LEE; SHIQUN GU.

**(86) Pedido PCT:** PCT US2015048514 de 04/09/2015

**(87) Publicação PCT:** WO 2016/069112 de 06/05/2016

**(85) Data do Início da Fase Nacional:** 26/04/2017

**(57) Resumo:** Uma estrutura de pacote de saída em leque de alta densidade inclui uma camada de contato. A camada de contato inclui uma camada de interligação condutora tendo uma primeira superfície voltada para uma pastilha ativa e uma segunda superfície voltada para uma camada de redistribuição. A estrutura de pacote de saída em leque de alta densidade tem uma camada de barreira na primeira superfície da camada interligação condutora. A estrutura de pacote de saída em leque de alta densidade pode incluir também a camada de redistribuição, a qual tem camadas condutoras de encaminhamento. As camadas condutoras de encaminhamento podem ser configuradas para acoplar uma primeira interligação condutora à camada de interligação condutora. A estrutura de pacote de saída em leque de alta densidade pode incluir adicionalmente uma primeira via acoplada ao revestimento de barreira e configurada para acoplamento com uma segunda interligação condutora à pastilha ativa.

ESTRUTURA DE PACOTE DE SAÍDA EM LEQUE DE ALTA DENSIDADE

REFERÊNCIA CRUZADA A PEDIDO RELACIONADO

[0001] Esse pedido reivindica o benefício em conformidade com 35 USC §119(e) para o Pedido de Patente Provisional dos Estados Unidos Nº 62/073.804, intitulado "HIGH DENSITY FAN OUT PACKAGE STRUCTURE" depositado em 31 de outubro de 2014 cuja revelação é aqui expressamente incorporada integralmente mediante referência.

ANTECEDENTES

CAMPO

[0002] Aspectos da presente revelação se referem aos dispositivos semicondutores e, mais especificamente, às técnicas de saída em leque de alta densidade (HDFO) para fabricação de uma estrutura de saída em leque de alta densidade.

ANTECEDENTES

[0003] O fluxo de processo para fabricação de semicondutores de circuitos integrados (ICs) pode incluir processos de extremidade inicial de linha (FEOL), de meio de linha (MOL), e de extremidade final de linha (DEOL). Os processos de extremidade inicial de linha podem incluir preparação de lâmina, isolamento, formação de cavidade, padronização de porta, espaçador, implantação de fonte/dreno e extensão, formação de siliceto, e formação de revestimento de tensão dual. O processo de meio de linha por incluir formação de contato de porta. Camadas de meio de linha podem incluir, mas não são limitadas aos contatos de meio de linha, vias ou outras camadas dentro de proximidade estreita com os transistores de dispositivos semicondutores ou outros dispositivos ativos semelhantes. Os processos de extremidade final de linha podem incluir uma série de etapas de processamento de lâmina para interligar os dispositivos semicondutores criados durante

os processos de extremidade inicial de linha e de meio de linha. A fabricação bem-sucedida de produtos modernos de chip de semicondutor envolve uma interação entre os materiais e os processos empregados.

[0004] Um intermediário é uma tecnologia de montagem de pastilha na qual o intermediário serve como uma base sobre a qual as pastilhas de semicondutor de um sistema em chip (SoC) são montadas. Um intermediário é um exemplo de uma estrutura de pacote de nível de lâmina de saída em leque. O intermediário pode incluir camadas de fixação de traços condutores e vias condutoras para encaminhar as conexões elétricas entre as pastilhas de semicondutor (por exemplo, módulos de memória e processadores) e uma placa de sistema. O intermediário pode incluir uma camada de redistribuição (RDL) que proporciona um padrão de conexão de elementos de ligação na superfície ativa de um dispositivo semicondutor (por exemplo, uma pastilha ou chip) para um padrão de conexão redistribuído que é mais adequado para conexão à placa de sistema. Na maioria das aplicações, o intermediário não inclui dispositivos ativos, tais como diodos e transistores.

[0005] A fabricação de uma estrutura de pacote de nível de lâmina pode incluir a fixação de um dispositivo semicondutor (por exemplo, uma pastilha ou chip) à estrutura de pacote de nível de lâmina de acordo com um primeiro processo de fixação de chip antes da formação da camada de redistribuição. O primeiro processo de fixação de chip, contudo, pode tornar o dispositivo semicondutor defeituoso devido à tensão sobre o dispositivo semicondutor durante a formação da camada de redistribuição e/ou devido aos defeitos associados com a camada de redistribuição.

## SUMÁRIO

[0006] Uma estrutura de pacote de saída em

leque de alta densidade pode incluir uma camada de contato. A camada de contato inclui uma camada de interligação condutiva tendo uma primeira superfície voltada para uma pastilha ativa e uma segunda superfície voltada para uma camada de redistribuição. A estrutura de pacote de saída em leque de alta densidade tem uma camada de barreira na primeira superfície da camada de interligação condutiva. A estrutura de pacote de saída em leque de alta densidade também pode incluir a camada de redistribuição tendo camadas condutoras de encaminhamento. As camadas condutoras de encaminhamento podem ser configuradas para acoplar uma primeira interligação condutora à camada de interligação condutora. A estrutura de pacote de saída em leque de alta densidade pode incluir adicionalmente uma primeira via acoplada ao revestimento de barreira e configurada para acoplamento com uma segunda interligação condutora para a pastilha ativa.

[0007] Um método de fabricar uma estrutura de pacote de saída em leque de alta densidade pode incluir a fabricação de uma camada de contato sobre um substrato portador. A camada de contato pode incluir uma camada de interligação condutora tendo um revestimento de barreira em uma primeira superfície. O método pode incluir também a fabricação de uma camada de redistribuição (RDL). A camada de redistribuição pode incluir camadas condutoras de encaminhamento configuradas para acoplar uma primeira interligação condutora à camada de interligação condutora. O método pode incluir adicionalmente o depósito de um material condutor dentro de uma abertura na camada de contato para formar uma primeira via disposta no revestimento de barreira após a remoção do substrato portador. O método também pode incluir fixar uma pastilha ativa à via utilizando uma segunda interligação condutora.

O revestimento de barreira na primeira superfície da camada de interligação condutora pode estar voltado para a pastilha ativa.

[0008] Uma estrutura de pacote de saída em leque de alta densidade pode incluir uma camada de contato. A camada de contato inclui uma camada de interligação condutora tendo uma primeira superfície voltada para uma pastilha ativa. A estrutura de pacote de saída em leque de alta densidade tem uma camada de barreira na primeira superfície da camada de interligação condutora. A estrutura de pacote de saída em leque de alta densidade também pode incluir meios para acoplar uma primeira interligação condutora à camada de interligação condutora. A segunda superfície da camada de interligação condutora pode estar voltada para o meio de acoplamento. A estrutura de pacote de saída em leque de alta densidade pode incluir adicionalmente uma primeira via acoplada ao revestimento de barreira e configurada para se acoplar com uma segunda interligação condutora à pastilha ativa.

[0009] Isso delineou, mais propriamente de forma ampla, as características e vantagens técnicas da presente revelação para que a descrição detalhada a seguir possa ser mais bem entendida. Características e vantagens adicionais da revelação serão descritas abaixo. Deve ser considerado, por aqueles versados na arte, que essa revelação pode ser utilizada, prontamente, como uma base para modificar ou projetar outras estruturas para realização dos mesmos propósitos da presente revelação. Também deve ser percebido por aqueles versados na arte que tais construções equivalentes não se afastam dos ensinamentos da revelação conforme apresentados nas reivindicações anexas. As características novéis, que são consideradas como características da revelação, tanto em

relação à sua organização como ao método de operação, em conjunto com objetivos e vantagens adicionais, serão mais bem entendidas a partir da descrição seguinte quando considerada em conexão com as figuras anexas. Deve ser expressamente entendido, contudo, que cada uma das figuras é provida apenas com o propósito de ilustração e descrição e não com o propósito de definição dos limites da presente revelação.

#### BREVE DESCRIÇÃO DOS DESENHOS

[0010] Para um entendimento mais completo da presente revelação, faz-se agora referência à descrição seguinte tomada em conjunto com os desenhos anexos.

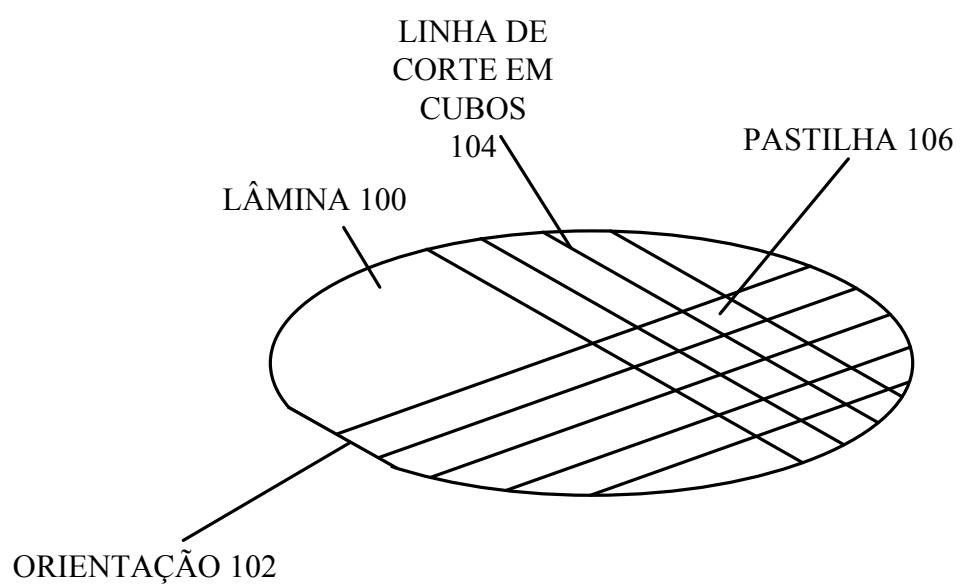

[0011] A Figura 1 ilustra uma vista em perspectiva de uma lâmina de semicondutor em um aspecto da presente revelação.

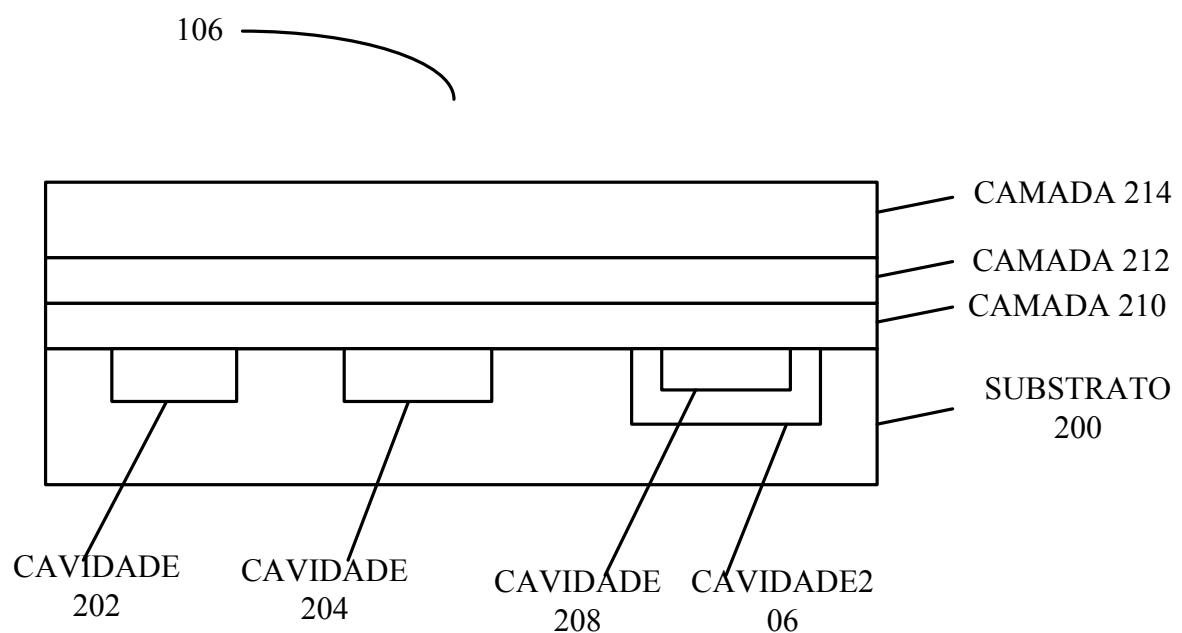

[0012] A Figura 2 ilustra uma vista em seção transversal de uma pastilha de acordo com um aspecto da presente revelação.

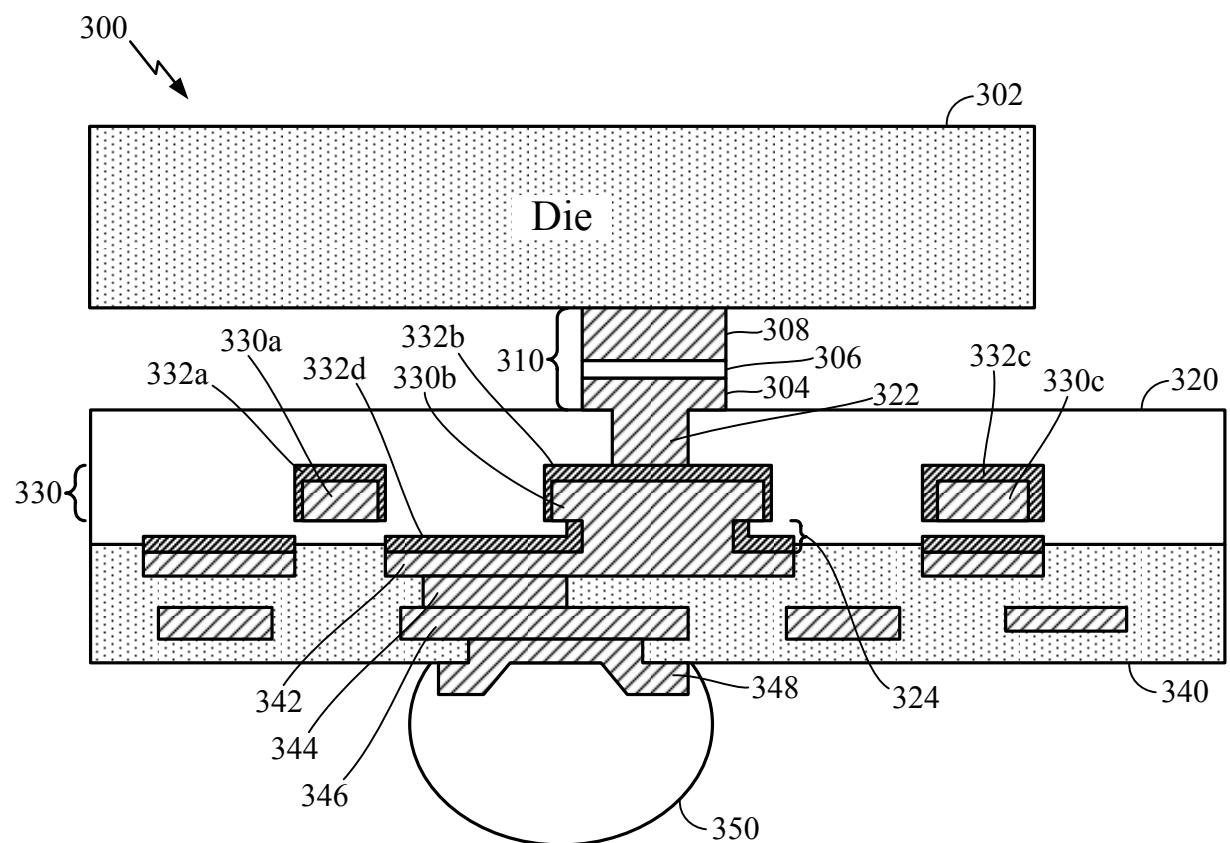

[0013] A Figura 3 ilustra uma estrutura de pacote de saída em leque de alta densidade de acordo com um aspecto da presente revelação.

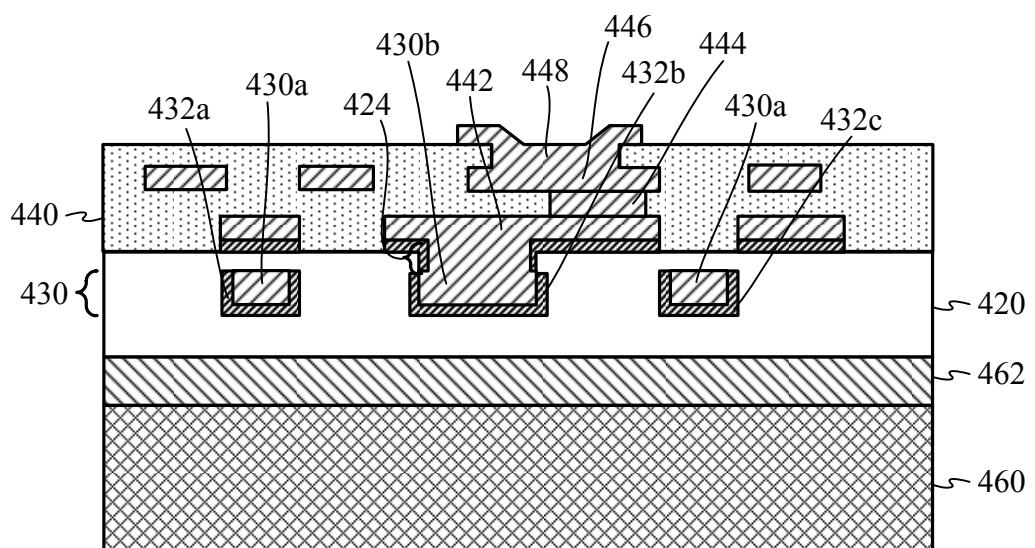

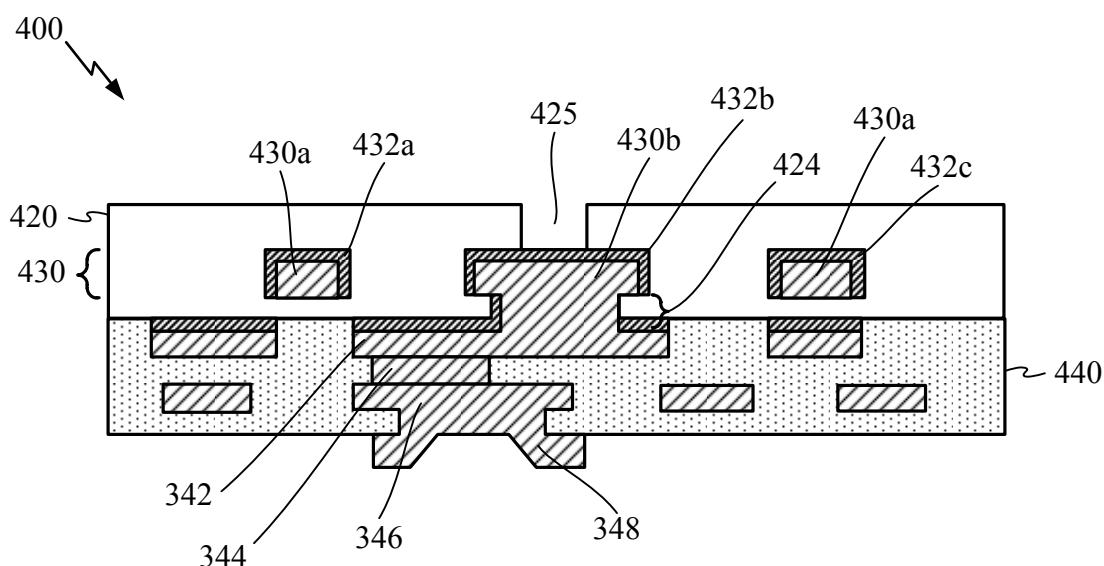

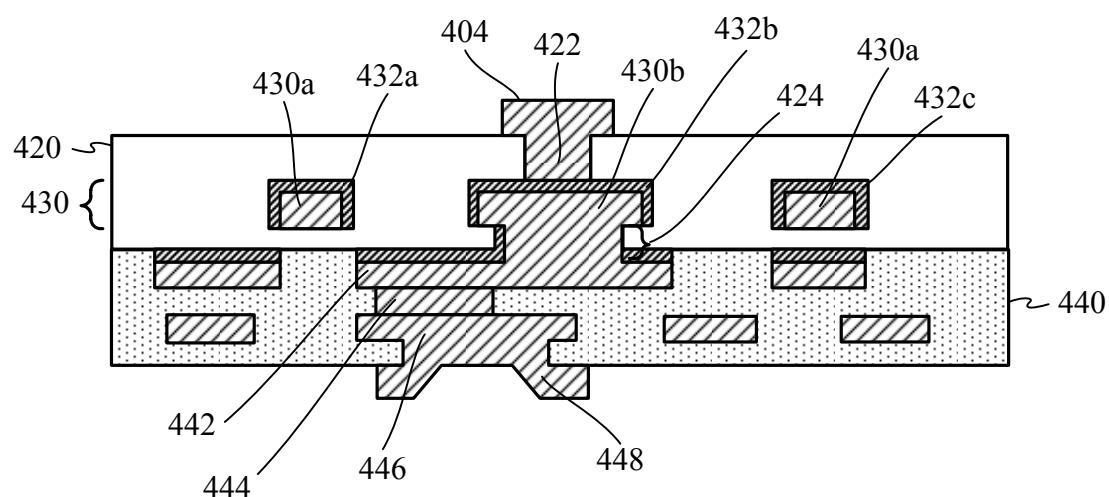

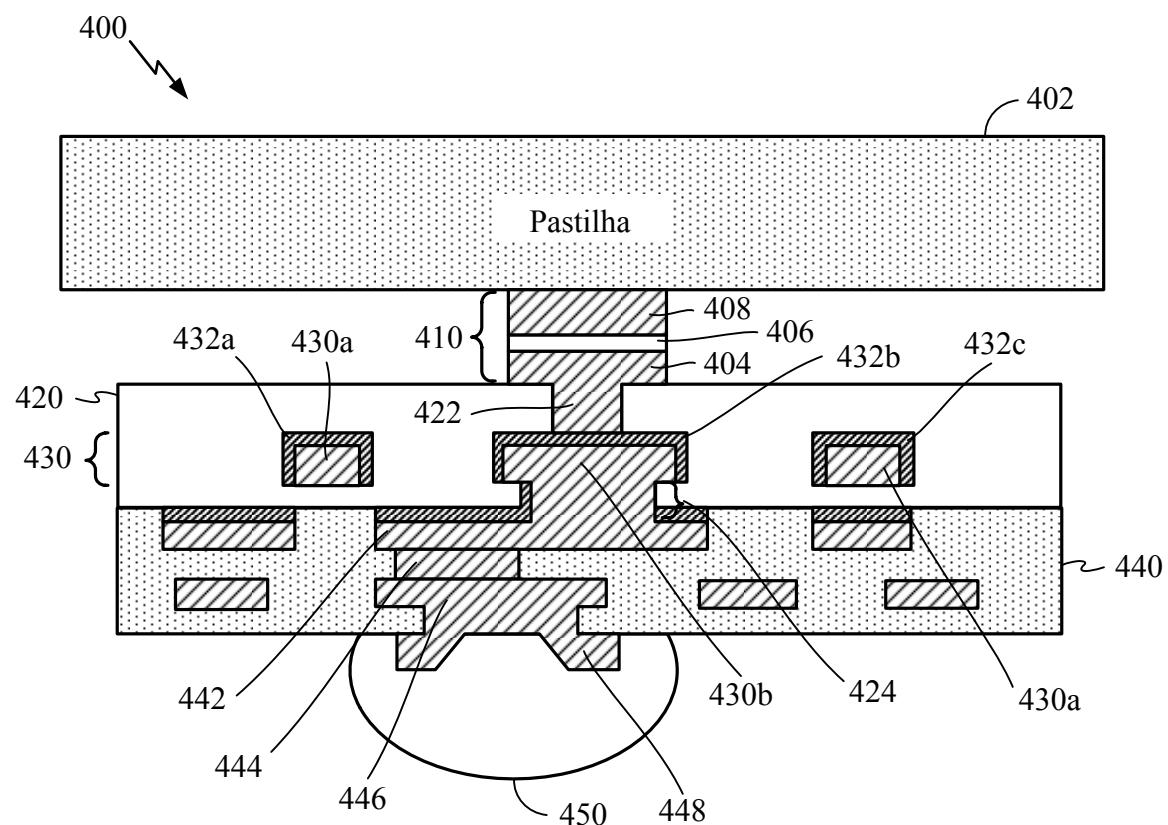

[0014] As Figuras 4A-4M ilustram uma estrutura de pacote de saída em leque de alta densidade em vários estágios de fabricação de acordo com um aspecto da presente revelação.

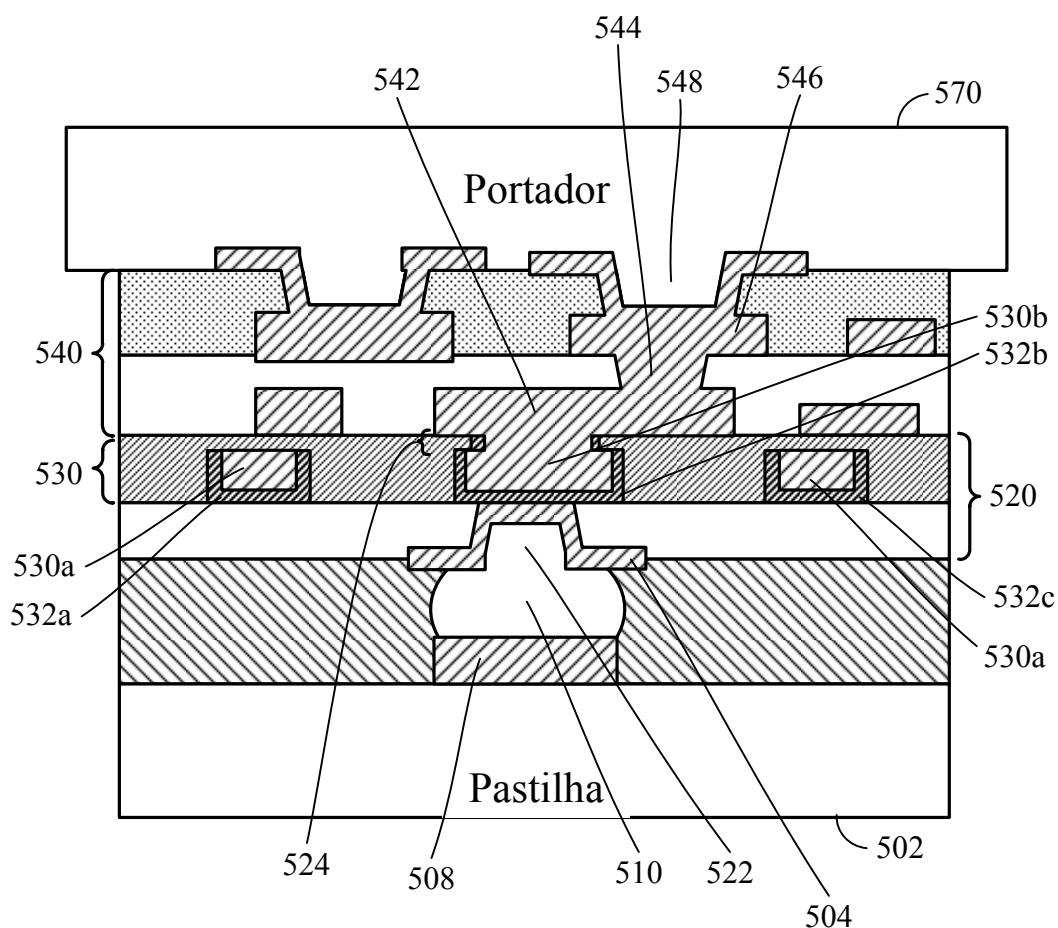

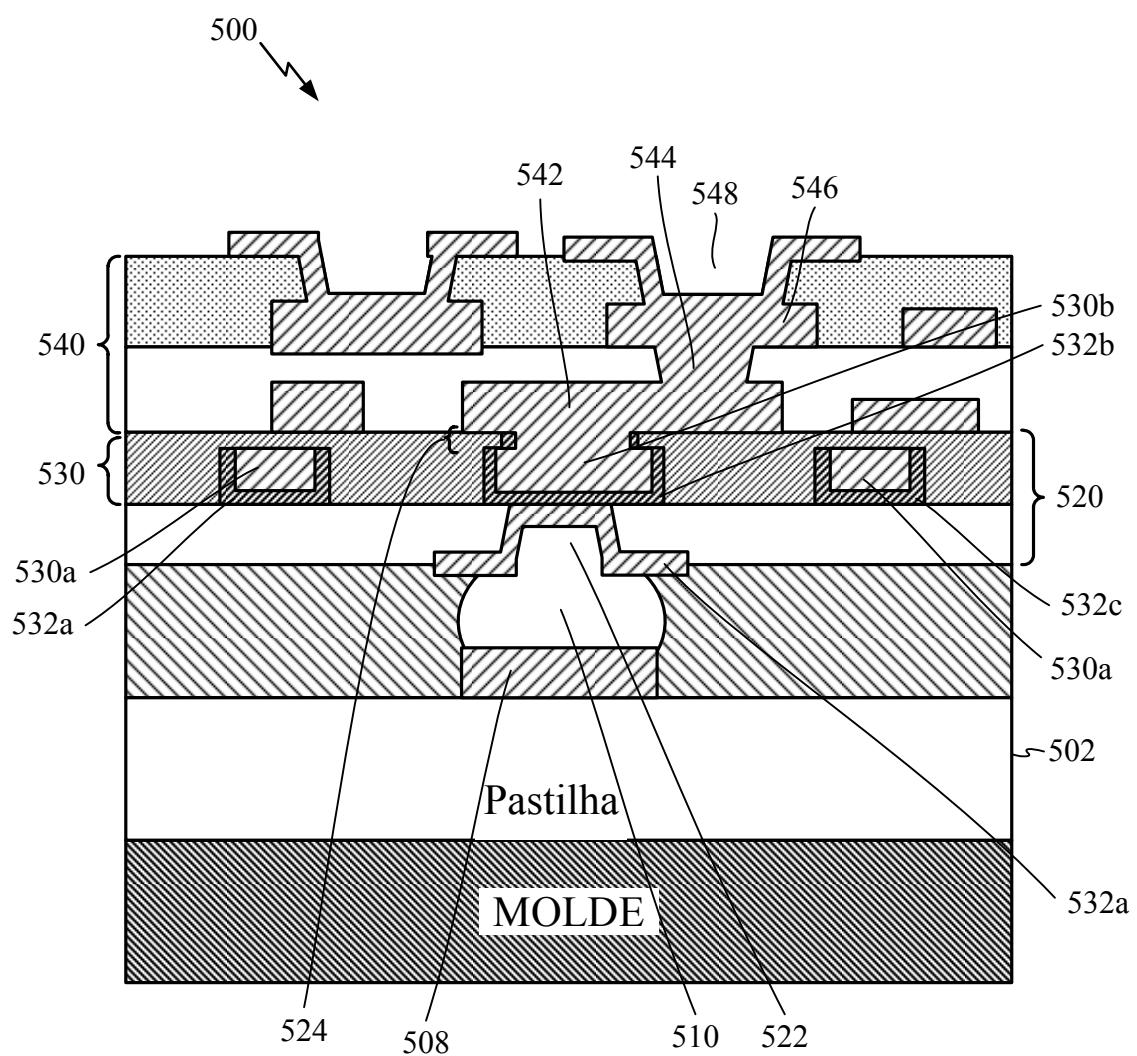

[0015] As Figuras 5A-5F ilustram uma estrutura de pacote de saída em leque de alta densidade em vários estágios de fabricação de acordo com um aspecto da presente revelação.

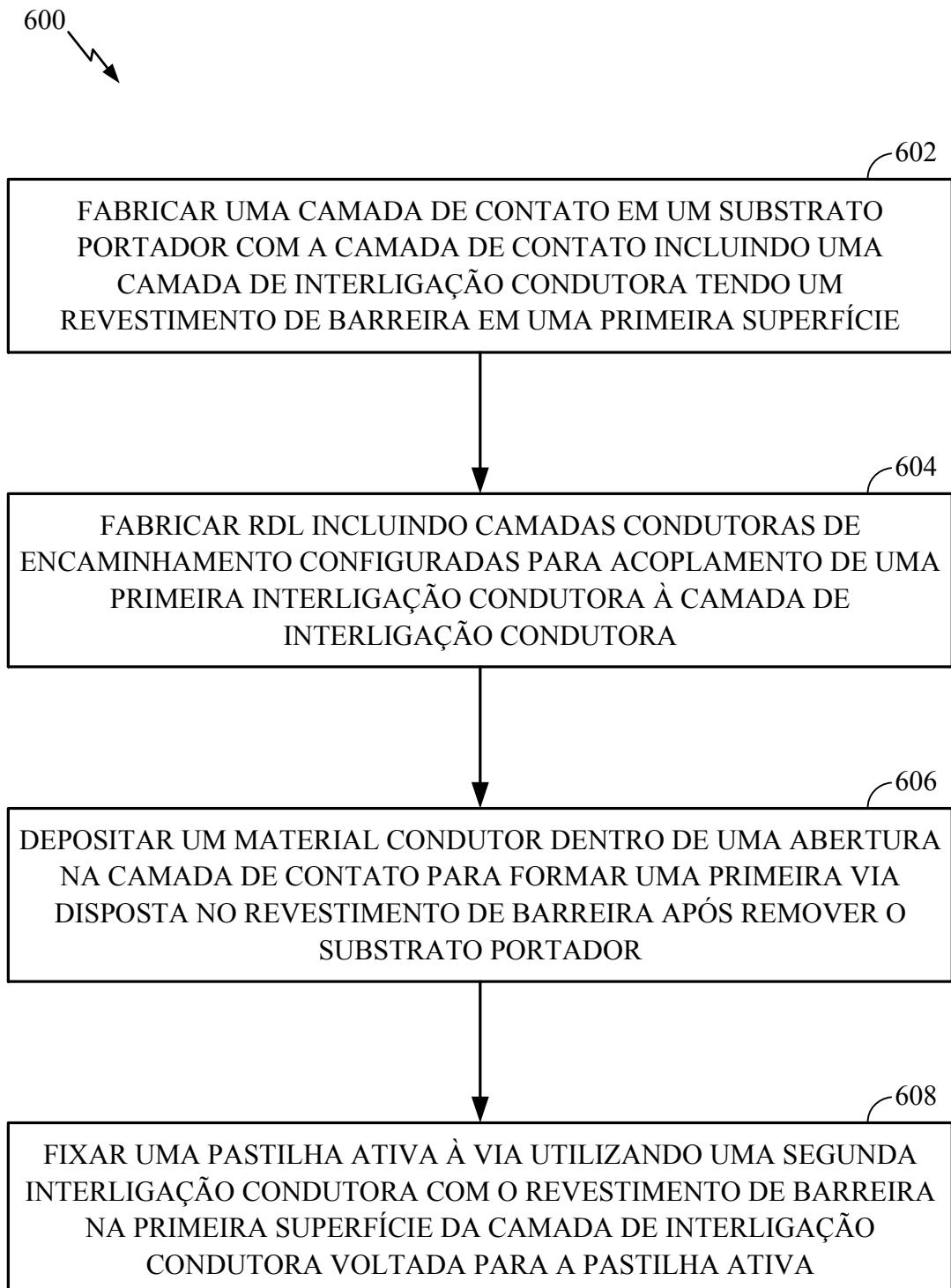

[0016] A Figura 6 é um diagrama de fluxo de processo ilustrando um método para fabricação de uma estrutura de pacote de saída em leque de alta densidade de acordo com aspecto da presente revelação.

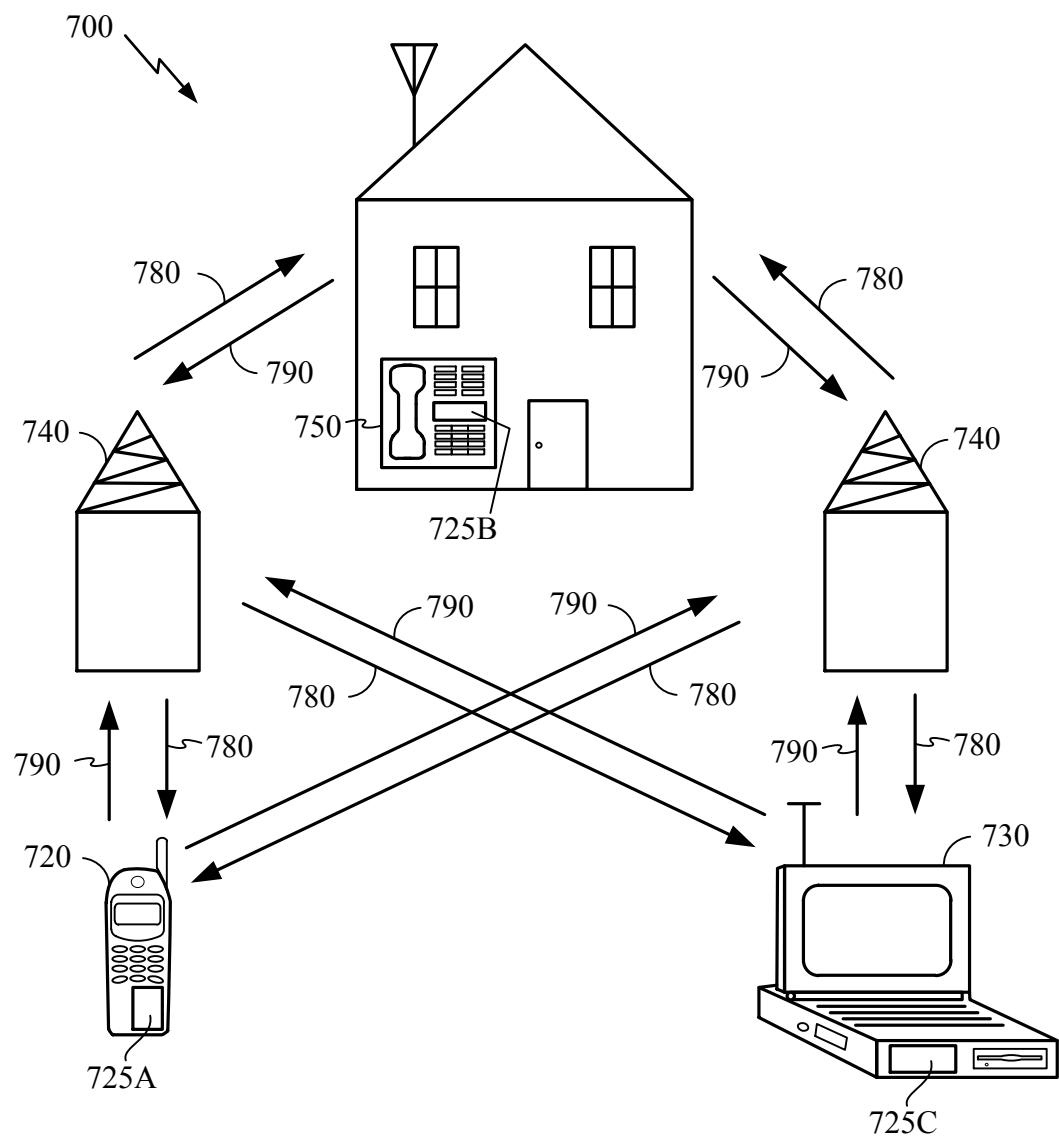

[0017] A Figura 7 é um diagrama de blocos mostrando um sistema de comunicação sem fio exemplar no qual uma configuração da revelação pode ser vantajosamente empregada.

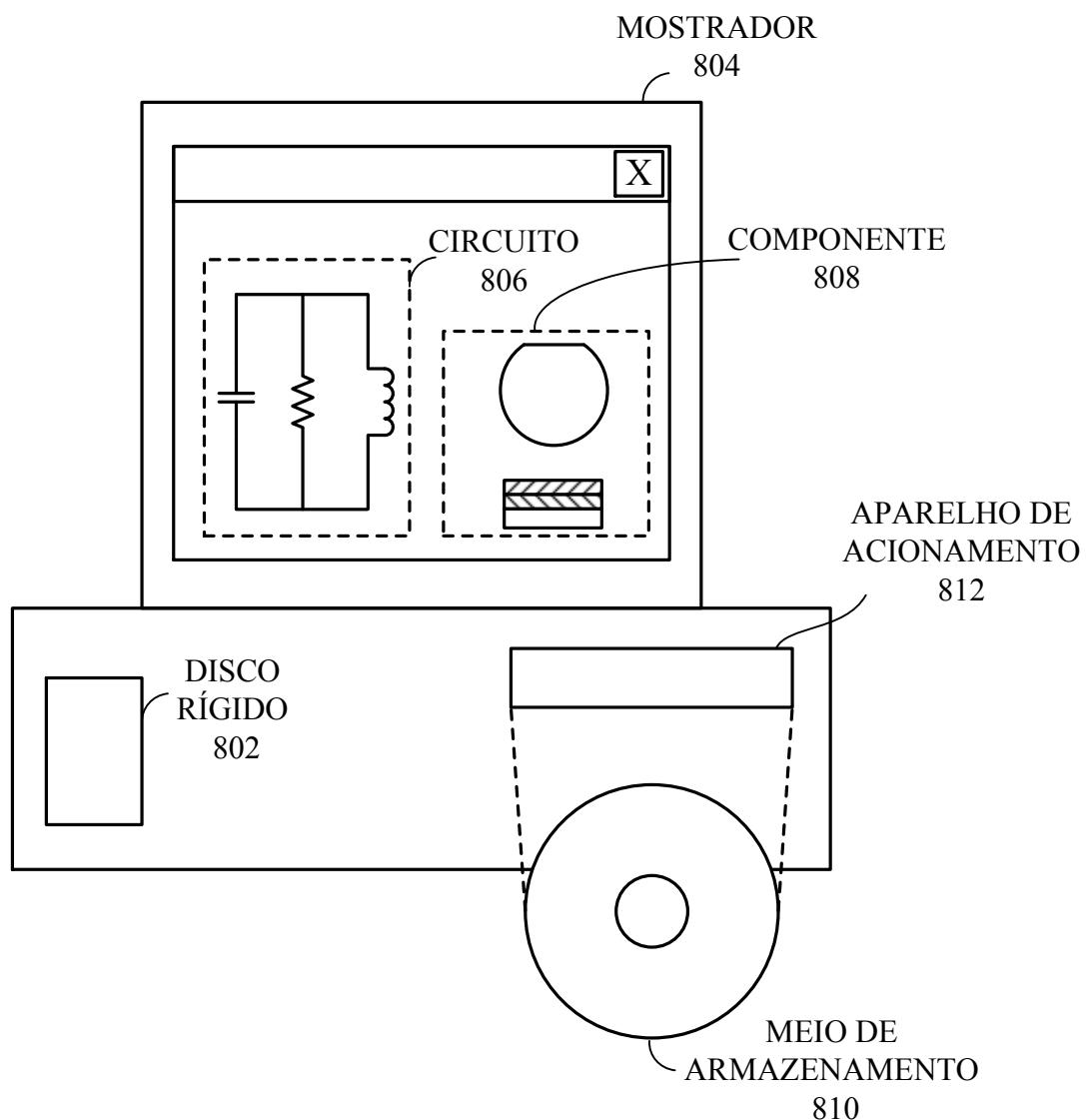

[0018] A Figura 8 é um diagrama de blocos que ilustra uma estação de trabalho de projeto usada para modelo de circuito, leiaute, e modelo lógico de um componente semicondutor de acordo com uma configuração.

#### DESCRIÇÃO DETALHADA

[0019] A descrição detalhada apresentada em seguida, em conexão com os desenhos anexos, é concebida como uma descrição de várias configurações e não se destina a representar as únicas configurações em que os conceitos aqui descritos podem ser praticados. A descrição detalhada inclui detalhes específicos para a finalidade de fornecer uma compreensão completa dos vários conceitos. Será evidente para os peritos na arte, no entanto, que esses conceitos podem ser praticados sem estes detalhes específicos. Em alguns casos, estruturas e componentes bem conhecidos são mostrados em forma de diagrama de bloco de modo a evitar obscurecer os conceitos tais. Tal como aqui descrito, o uso do termo "e/ou" destina-se a representar um "OU inclusivo", e o uso do termo "ou" destina-se a representar um "OU exclusivo".

[0020] Algumas implementações descritas referem-se a estruturas de pacote de nível de lâmina, tal como a tecnologia de interposição. Um meio de interposição geralmente serve como uma camada intermédia que pode ser utilizada para interligação elétrica direta entre um componente ou substrato e um segundo componente ou substrato com o meio de interposição posicionado no meio. Por exemplo, uma placa intermediária pode ter uma configuração de elemento de um lado que pode ser alinhada

com os elementos correspondentes em um primeiro componente (por exemplo, uma pastilha), e uma configuração de elemento diferente em um segundo lado que corresponde a elementos sobre um segundo componente (por exemplo, um substrato de embalagem, placa de sistema, etc.). Meios de interposição são amplamente utilizados para a integração de múltiplos chips de um único pacote. Além disso, os substratos de interposição podem ser compostos de vidro e de quartzo, orgânico, ou outro material semelhante e normalmente contêm algumas camadas de interligação.

[0021] A fabricação de estruturas de pacote de nível lâmina, tal como meios de interposição, pode incluir a formação de uma camada de redistribuição (RDL). A camada de redistribuição pode permitir a expansão de um padrão de ligação das pads de ligação sobre a superfície ativa de um dispositivo ativo (por exemplo, uma pastilha ou chip) com um padrão de ligação redistribuído que é mais apropriado para a ligação a um substrato (por exemplo, placa de sistema, o pacote substrato, placa de circuito impresso, etc.). Técnicas de fabricação convencionais incluem unir o dispositivo ativo antes da formação de uma camada de redistribuição de acordo com um primeiro processo de chip anexar. O processo de chip primeiro anexar, no entanto, assume que há defeitos estão associados com a camada de redistribuição. Infelizmente, os defeitos na camada de redistribuição podem levar à perda do dispositivo ativo. Além disso, a pressão sobre o dispositivo ativa durante a formação da camada de redistribuição pode tornar o dispositivo ativo com defeito.

[0022] Vários aspectos da revelação fornecem técnicas para a fabricação de uma estrutura de pacote de saída em leque de alta densidade (HDF). O fluxo do processo para a fabricação de semicondutores da estrutura

do pacote HDO pode incluir processos extremidade inicial de linha (FEOL) processos de meio de linha (MOL), e processos de extremidade final de linha (BEOL). Será entendido que o termo "camada" inclui película e não é para ser interpretado como indicando uma espessura vertical ou horizontal, a menos que indicado de outra forma. Tal como aqui descrito, o termo "substrato" pode referir-se a um substrato de uma lâmina em cubos ou pode referir-se ao substrato de uma lâmina que não é cortado. Da mesma forma, os termos chip e pastilha podem ser utilizados de forma permutável a menos que tal permutabilidade imponha credulidade.

[0023] Como aqui descrito, as camadas de interligação de meio de linha podem referir-se as interconexões condutoras para ligar uma primeira camada condutora (por exemplo, um metal um (M1)) da extremidade final de linha para a camada de difusão de óxido (OD) de um circuito integrado e também para ligar M1 aos dispositivos ativos do circuito integrado. As camadas de interligação de meio de linha para conectar M1 à camada de OD de um circuito integrado podem ser referidas como "MD1" e "MD2." A camada de interligação de meio de linha para conectar M1 às portas de um circuito integrado pode ser referida como "MP". Uma via zero de meio de linha (V0) pode conectar M1 às camadas de interligação de meio de linha.

[0024] Uma estrutura de pacote HDO, de acordo com aspectos da presente revelação, inclui pastilha ativa múltipla ou uma única estrutura de chip. A estrutura de pacote HDO pode ser fabricada de acordo com um de processo de última anexação de chip. O processo de última anexação de chip inclui acoplar uma pastilha ativa à estrutura de pacote HDO após uma camada de redistribuição ser formada. Por exemplo, a camada de redistribuição pode ser verificada

por meio de testes antes de a pastilha ativa ser ligada a fim de evitar ligação a uma camada de redistribuição com defeito.

[0025] Em um aspecto da revelação, a estrutura do pacote HDO inclui uma camada de contato que inclui uma camada de interligação condutora. A camada de interligação condutora pode incluir uma primeira superfície virada para uma pastilha ativa e uma segunda superfície voltada para a camada de redistribuição. Uma primeira interligação condutora (por exemplo, arranjo de grade de esfera (BGA)) podem acoplar a estrutura de pacote HDO para um dispositivo externo. Um revestimento condutor pode ser disposto sobre a primeira superfície da camada de interligação condutora. O revestimento condutor pode ser uma barreira ou semente forro de tântalo. O revestimento de barreira pode proporcionar proteção para a camada condutora interligam durante a formação (por exemplo, galvanização) das interligações para a pastilha ativa.

[0026] A camada de redistribuição (RDL) é acoplada à camada condutora de interligação da camada de contato. A camada de redistribuição pode ser uma camada de encaminhamento de saída em leque. A camada de redistribuição inclui camadas condutoras de encaminhamento configurado para acoplar uma primeira interligação condutora para a interligação camada condutora. Como observado, o camada de redistribuição é formada antes de fixar a pastilha ativa para evitar danificar a pastilha ativa durante a formação da camada de redistribuição. A camada de redistribuição pode ser uma camada traseira redistribuição (BRDL) que é formada numa lâmina de espessura completa. Implementar a estrutura do pacote HDO sobre a camada traseira redistribuição melhora o rendimento da pastilha ativa e reduz a deformação da estrutura do

pacote HDO.

[0027] Uma via pode ser acoplada ao revestimento de barreira para interligar a segunda interligação condutora da pastilha ativa. O material condutor pode incluir um ou mais condutores interliga. Por exemplo, o segundo material condutor pode incluir uma interligação protuberância sob condutor, um material de solda e/ou um pilar condutor. A interligação condutora protuberância sob pode ser disposta numa abertura dentro da camada condutora que expõe uma superfície do revestimento de barreira. O pilar condutor pode ser acoplado a um elemento de contato da pastilha. O material de solda ser interligação entre o condutor e protuberância sob o pilar condutor. A protuberância sob interligação condutora e o pilar condutor pode ser de cobre.

[0028] A figura 1 ilustra uma vista em perspectiva de uma lâmina de material semicondutor, num aspecto da presente revelação. Uma lâmina 100 pode ser uma lâmina de material semicondutor, ou pode ser um material de substrato com uma ou mais camadas de material semicondutor sobre uma superfície da pastilha 100. Quando a lâmina 100 é um material semicondutor, pode ser cultivada a partir de um cristal de semente com o processo de Czochralski, em que o cristal de semente é mergulhado em um banho de fundido de material semicondutor e a rodar lentamente e removida do banho. O material fundido, em seguida, cristaliza sobre o cristal semente na orientação do cristal.

[0029] A pastilha 100 pode ser um material composto, tal como o arseniato de gálio (GaAs) ou nitreto de gálio (GaN), um material ternário, tais como índio arseniato de gálio (InGaAs), materiais quaternários, ou qualquer material que pode ser um material de substrato para outros materiais semicondutores. Embora muitos dos

materiais possam ser de natureza cristalina, materiais policristalinos ou amorfos também podem ser usados para a lâmina 100.

[0030] A lâmina 100, ou camadas que são acopladas à lâmina 100, pode ser fornecida com os materiais que tornam a lâmina 100 mais condutora. Por exemplo, e não a título de limitação, uma lâmina de silício pode ter de fósforo ou de boro adicionado à lâmina 100 para permitir a carga elétrica fluir na lâmina de 100. Estes aditivos são referidos como dopantes, e proporcionam portadores de carga adicional (quer elétrons ou furos) na lâmina 100 ou porções da lâmina 100. Ao selecionar as áreas onde os portadores de carga adicionais são fornecidos, qual o tipo de portador de carga é fornecido, e a quantidade (densidade) de portadores de carga adicional na lâmina 100, diferentes tipos de dispositivos eletrônicos podem ser formados em ou sobre a lâmina 100.

[0031] A pastilha 100 tem uma orientação 102 que indica a orientação cristalina da pastilha 100. A orientação 102 pode ser uma borda plana do disco de contato 100, como mostrado na figura 1, ou pode ser um entalhe ou outros indícios para ilustrar a orientação cristalina da pastilha 100. A orientação 102 pode indicar os índices de Miller para os planos da treliça cristalina na lâmina 100.

[0032] Os índices de Miller formam um sistema de notação dos planos cristalográficos na estrutura de cristal. Os planos de treliça podem ser indicados por três inteiros  $h$ ,  $k$ , e  $l$ , que são os índices de Miller para um plano (HKL) no cristal. Cada índice indica um plano perpendicular a uma direção ( $h$ ,  $k$ ,  $i$ ) na base dos vetores de rede recíproca. Os números inteiros são geralmente escritos em termos mais baixo (por exemplo, o seu maior divisor comum deve ser 1). Miller índice 100 representa um

plano ortogonal ao sentido  $h$ ; índice 010 representa um plano ortogonal ao sentido  $k$ , e o índice de 001 representa um plano ortogonal para  $l$ . Para alguns cristais, números negativos são utilizados (escrito como uma barra sobre o número de índice) e para alguns cristais, tais como o nitreto de gálio, mais de três números pode ser empregado para descrever adequadamente os diferentes planos cristalográficos.

[0033] Quando a lâmina 100 tiver sido processada como desejado, a lâmina 100 é dividida ao longo de linhas de corte em placas 104. As linhas de corte em placas 104 indicam onde a lâmina 100 é para ser quebrada ou separada em pedaços. As linhas de corte em placas 104 podem definir o contorno dos vários circuitos integrados, que foram fabricadas na lâmina 100.

[0034] Uma vez que as linhas de corte em placas 104 são definidas, a lâmina 100 pode ser serrada ou de outra forma separado em pedaços para formar pastilha 106. Cada um da pastilha 106 pode ser um circuito integrado com muitos dispositivos ou pode ser um único dispositivo eletrônico. O tamanho físico da pastilha 106, que também pode ser referido como um chip ou um chip semicondutor depende, pelo menos em parte, na capacidade de separar a lâmina 100 em determinados tamanhos, bem como o número de dispositivos individuais que a pastilha 106 destina-se a conter.

[0035] Uma vez que a lâmina 100 foi separada em uma ou mais cunho 106, a pastilha 106 pode ser montada em embalagens para permitir o acesso aos dispositivos e/ou circuitos integrados fabricadas na pastilha 106. A embalagem pode incluir embalagem única em linha, embalagem dupla em linha, embalagem de placa-mãe, embalagem flip/chip, embalagem de ponto/protuberância de índio, ou

outros tipos de dispositivos que permitem o acesso à pastilha 106. A pastilha 106 também pode ser diretamente acessada através de pontes de fio, sondas, ou outras conexões sem montagem da pastilha 106 em uma embalagem separada.

[0036] A figura 2 ilustra uma vista em corte transversal de uma pastilha 106 de acordo com um aspecto da presente revelação. Na pastilha 106, que pode ser um substrato 200, que pode ser um material semicondutor e/ou podem atuar como um suporte mecânico para dispositivos eletrônicos. O substrato 200 pode ser um substrato semicondutor dopado, que tem tanto elétrons (designado N-canais) ou portadores de carga de furos (designado P-canais) presentes em todo o substrato 200. Dopagem subsequente do substrato 200 com íons/átomos portadores de carga podem alterar a taxa de realização capacidades do substrato 200.

[0037] No âmbito de um substrato de 200 (por exemplo, um substrato semicondutor), pode haver cavidades 202 e 204, que podem ser a origem e/ou de drenagem de um transistor de efeito de campo (FET), ou cavidades 202 e/ou 204 podem ser estruturas de aleta de uma aleta FET estruturada (FinFET). Cavidades 202 e/ou 204 também podem ser outros dispositivos (por exemplo, uma resistência, um condensador, um diodo, ou outros dispositivos eletrônicos), dependendo da estrutura e outras características das cavidades 202 e/ou 204 e a estrutura circundante do substrato 200.

[0038] O substrato semicondutor também pode ter uma cavidade 206 e uma cavidade 208. A cavidade 208 pode ser completamente dentro da cavidade 206, e, em alguns casos, podem formar um transistor de junção bipolar (BJT). A cavidade 206 também pode ser usada como uma cavidade de isolamento para isolar a cavidade 208 de campos magnéticos

e/ou elétricos no interior da pastilha 106.

[0039] Camadas (por exemplo, 210 a 214) podem ser adicionadas à pastilha 106. A camada 210 pode ser, por exemplo, um óxido ou camada isolante que pode isolar as cavidades (por exemplo, 202-208) a partir de cada um dos outros ou a partir de outros dispositivos na pastilha 106. Em tais casos, a camada 210 pode ser dióxido de silício, um polímero, um dielétrico, ou outra camada eletricamente isoladora. A camada 210 também pode ser uma camada de interligação, caso em que pode compreender um material condutor, tal como cobre, de tungstênio, de alumínio, de uma liga metálica, ou outros materiais condutores ou metálicos.

[0040] A camada 212 também pode ser uma camada dielétrica ou condutora, em função das características desejadas do dispositivo e/ou os materiais das camadas (por exemplo, 210 e 214). A camada 214 pode ser uma camada de encapsulação, o que pode proteger as camadas (por exemplo, 210 e 212), bem como as cavidades 202-208 e o substrato 200, a partir de forças externas. Por exemplo, e não como forma de limitação, a camada 214 pode ser uma camada que protege a pastilha 106 de danos mecânicos, ou a camada 214 pode ser uma camada de material que protege a pastilha 106 de danos eletromagnética ou radiação.

[0041] Os dispositivos eletrônicos concebidos na pastilha 106 podem compreender muitas características ou componentes estruturais. Por exemplo, a pastilha 106 pode ser exposta a qualquer número de métodos para conferir dopantes no substrato 200, as cavidades 202-208, e, se desejado, as camadas (por exemplo, 210-214). Por exemplo, e não como forma de limitação, a pastilha 106 pode ser exposta a implantação iônica, deposição de átomos dopantes que são empurrados para uma estrutura cristalina através de

um processo de difusão, a deposição de vapor químico, o crescimento epitaxial, ou outros métodos. Por meio de crescimento seletivo, seleção do material, e a remoção de porções das camadas (por exemplo, 210-214), e por meio de remoção seletiva, seleção do material, e a concentração dopante do substrato 200 e as cavidades 202-208, muitas estruturas diferentes e dispositivos eletrônicos podem ser formadas dentro do âmbito da presente revelação.

[0042] Além disso, o substrato 200, as cavidades 202-208, e as camadas (por exemplo, 210-214) podem ser seletivamente removidos ou adicionados através de vários processos. Gravura química, planarização mecânico-química (CMP), gravação com plasma, mascaramento fotorresistente, processos damascenos, e outros métodos podem criar as estruturas e dispositivos da presente revelação.

[0043] A Figura 3 ilustra uma estrutura de pacote de saída em leque de alta densidade (HDO) 300 de acordo com um aspecto da presente revelação. O HDO estrutura de pacote 300 pode acoplar uma primeira interligação condutora 350 (por exemplo, volta-lado) a uma pastilha ativa 302 através de uma segunda interligação condutora 310 (por exemplo, frente-lado). Neste arranjo, a segunda interligação condutora 310 tem uma forma de coluna e inclui uma primeira porção condutora 304 (por exemplo, uma pista condutora ou elemento de contato), uma segunda porção condutora 306 (por exemplo, um material de solda) e uma terceira porção condutora 308 (por exemplo, um pilar condutor da pastilha ativa 302). Numa outra configuração, a segunda interligação condutora pode ser fabricada usando uma protuberância condutora (por exemplo, um material de solda). A estrutura de pacote HDO 300 também inclui uma camada de contato 320 que tem uma camada de interligação

condutora 330 (330a, 330b, 330c) formado entre uma ou mais camadas dielétricas (por exemplo, nitreto). A estrutura de pacote HDO 300 também inclui uma camada de redistribuição 340 incluindo camadas condutoras de encaminhamento (por exemplo, 342, 344, 346) acoplado ao primeiro condutor 350 de interligação por meio de, por exemplo, uma subcamada de preenchimento de interligação 348.

[0044] As camadas condutoras de encaminhamento (por exemplo, 342, 344, 346) da camada de redistribuição 340 em combinação com a camada de interligação condutora 330 (por exemplo, 330a, 330b, 330c) da camada de contato 320 facilitar a comunicação entre a pastilha ativa 302 e a primeira interligação condutora 350 de (por exemplo, um arranjo de grade de esfera (BGA)). Por exemplo, a camada condutora 330 de interligação é formado utilizando uma primeira extremidade final de linha (BEOL) camada de interligação condutora (por exemplo, um metal (M1)). A camada de interligação condutora 330 pode ser rodeada por camadas dielétricas da camada de contato 320 e acoplada ao segundo de interligação condutor 310 através de uma primeira via 322 (por exemplo, uma via zero (V0) de meio de linha (MOL)).

[0045] Nesta disposição, a camada de interligação condutora 330 (por exemplo, 330b) é acoplada à camada de redistribuição 340 através de uma segunda via 324 (por exemplo, uma primeira via (VI) BEOL ou um traço condutor) e acoplado à pastilha ativa 302 através da primeira via 322. a primeira via 322 pode ser formado por um processo damasceno, um aditivo e processo de corrosão, um laser através de encher e preencher processo ou outro processo semelhante para a via formação. A segunda via 324 pode ser uma camada condutora de encaminhamento da camada de redistribuição 340. As camadas condutoras de

encaminhamento (por exemplo, 342, 344, 346) podem ser formadas dentro de um material dielétrico de polímero da camada de redistribuição 340. A camada de interligação condutora 330 e as camadas condutoras de encaminhamento (por exemplo, 342, 344, 346) podem ser compostas por cobre ou outro material condutor apropriado.

[0046] Em um aspecto da revelação, as porções (por exemplo, 330a, 330b, 330c) da camada de interligação condutora 330 são parcialmente rodeadas por um revestimento de barreira 332 (por exemplo, 332a, 332b, 332c). Por exemplo, o revestimento de barreira 332 pode ser disposto em paredes laterais e uma primeira superfície da camada de interligação condutora 330 que está virada para a pastilha ativa 302. O revestimento de barreira 332, no entanto, não é em uma segunda superfície da camada condutora 330 de interligação que enfrenta a camada de redistribuição 340 e está voltada para fora da pastilha ativa 302. A barreira de revestimento 332 pode ser fornecida pela fundição durante o processo de fabricação da camada condutora de interligação 330. Embora o revestimento de barreira 332 possa ser formado durante a fabricação da estrutura de pacote HDFO 300, o forro 332 de barreira pode ser formada antes da fabricação da estrutura de pacote HDFO 300. A barreira de revestimento 332 pode ser composta por um material de barreira tal como tântalo ou outro material de barreira adequado.

[0047] A camada de redistribuição 340 inclui uma primeira camada condutora de encaminhamento 342 acoplada à segunda via 324. Neste arranjo, uma porção (por exemplo, 332d) do revestimento de barreira 332 está disposta sobre as paredes laterais da segunda via 324 e uma superfície de a primeira camada condutora 342 de encaminhamento de frente para a pastilha ativa 302. A

primeira camada condutora de encaminhamento 326 é formada utilizando, por exemplo, uma segunda camada de interligação BEOL (por exemplo, de metal dois (M2)). Uma segunda camada condutora de encaminhamento 346 é acoplada à primeira camada condutora 326 de encaminhamento através de uma terceira via 344 (por exemplo, uma segunda via BEOL (V2)). A segunda camada de encaminhamento condutora 346 é formada usando, por exemplo, um terço BEOL condutora camada de interligação (por exemplo, de metal três (M3)). A segunda camada de encaminhamento condutora 346 é também acoplada ao primeiro condutor 350 de interligação por meio de, por exemplo, uma subcamada de preenchimento de interligação 348. A primeira interligação condutora 350 pode acoplar a um sistema de placa, um substrato de embalagem ou outro substrato de suporte adequado (não mostrado). A primeira interligação condutora de 350 pode ser configurada de acordo com uma estrutura de interligação arranjo de grade de esfera (BGA).

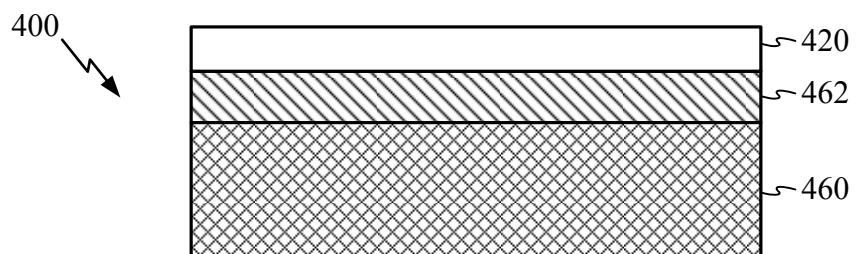

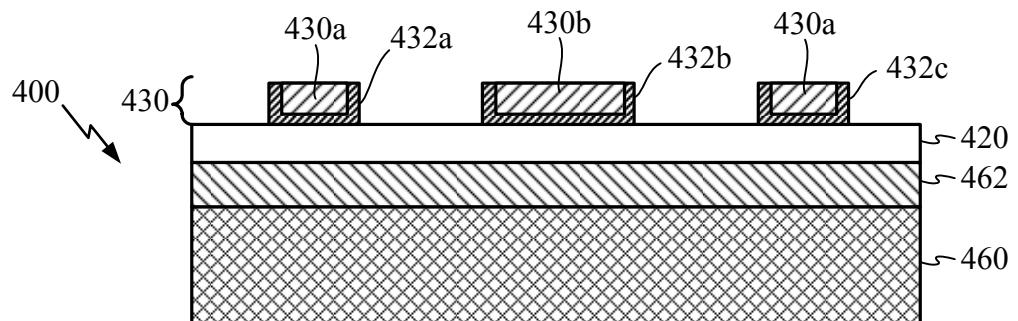

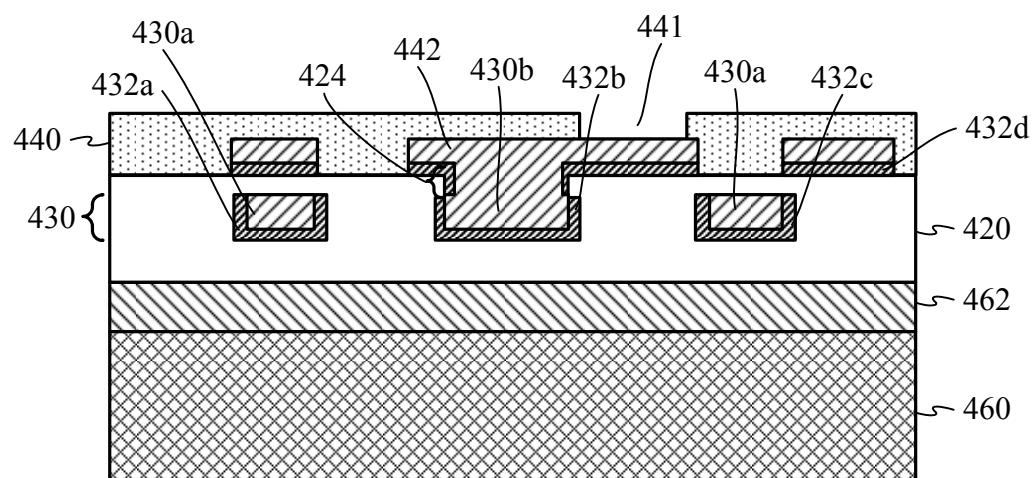

[0048] As Figuras 4A-4M ilustram uma estrutura de pacote HDO 400 em várias etapas de fabricação de acordo com aspectos da presente revelação. Por exemplo, as Figuras 4A-4L ilustram uma abordagem de fabrico sequencial da estrutura de pacote HDO 400 mostrada na figura 4M.

[0049] Começando com a figura 4A, um substrato de suporte (por exemplo, uma lâmina de material semicondutor) 460 é fornecido. O substrato de suporte 460 pode ser, por exemplo, um substrato à base de silício, um substrato à base de vidro ou outros materiais, tais como aqueles implementados com substratos em massa para lâminas de material semicondutor. Uma camada isolante 462 pode ser depositada sobre uma superfície ativa do substrato de suporte 460. A camada isolante 462 pode ser um óxido ou outro material isolador adequado. Uma primeira camada

dielétrica de uma camada de contato 420 pode ser depositada sobre a camada de isolamento 462. A camada de contato 420 pode ser uma camada de passivação, incluindo um óxido, um nitreto ou outro material semelhante isolante e pode isolar sinais, bem como proteger os vários circuitos e os elementos condutores.

[0050] Na figura 4B, uma camada de interligação condutora 430 para o encaminhamento de sinais entre uma camada de redistribuição 440 e uma pastilha ativa 402 é formada por deposição de um material condutor (por exemplo, cobre) em uma primeira camada dielétrica da camada de contato 420. A camada de interligação condutora 430 pode incluir porções condutoras 430a, 430b e 420c. As porções condutivas 430a, 430b e 420c podem ser formadas usando uma primeira camada de interligação BEOL (por exemplo, M1). Neste arranjo, as porções condutoras 430a, 430b e 430c são parcialmente rodeadas por um revestimento de barreira 432 (por exemplo, 432a, 432b, 432c). O revestimento de barreira 432 está disposto sobre as paredes laterais e uma primeira superfície das porções condutoras 430a, 430b e 430c, que está virado para o substrato de suporte 460. O revestimento de barreira 432, no entanto, não está disposta sobre uma segunda superfície das porções condutoras 430a, 430b e 430c que fica voltada para fora a partir do substrato de suporte 460. O revestimento de barreira 432 (por exemplo, tântalo) é fornecido pela fundição durante o processo de fabricação da camada condutora 430 de interligação.

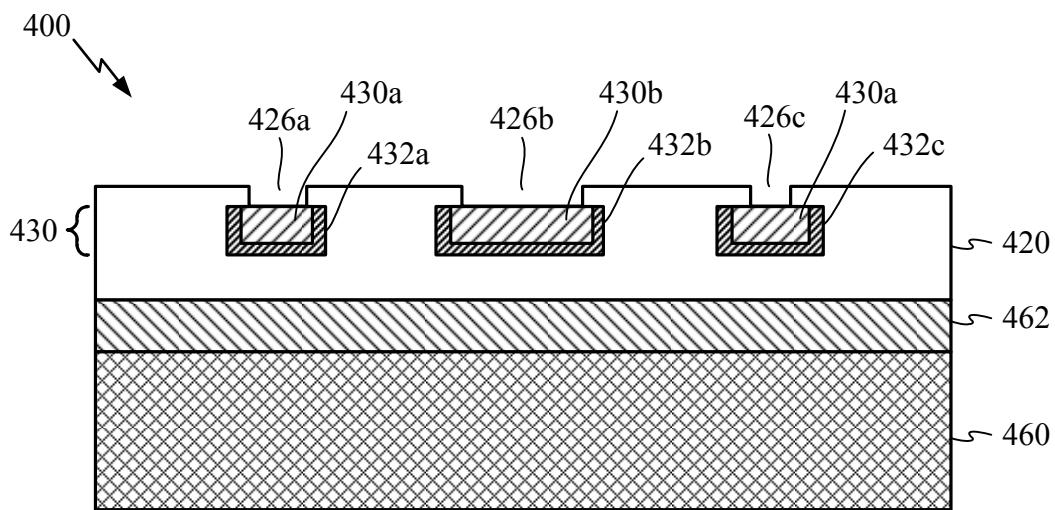

[0051] Na figura 4C, camadas dielétricas adicionais da camada de contato 420 são depositadas. As camadas dielétricas da camada de contato 420 podem ser compostas por uma camada de nitreto de (por exemplo, nitreto de silício (SiN)). Uma ou mais aberturas 426a, 426b, 426c no interior do material dielétrico da camada de

contato 420 são formadas para expor a segunda superfície das porções condutoras 430a, 430b e 430c, que não é coberta pelo forro de barreira 432. Por exemplo, a porção exposta das porções condutoras 430a, 430b e 430c pode definir uma área de contato para acoplamento a camadas condutoras de encaminhamento de uma camada de redistribuição.

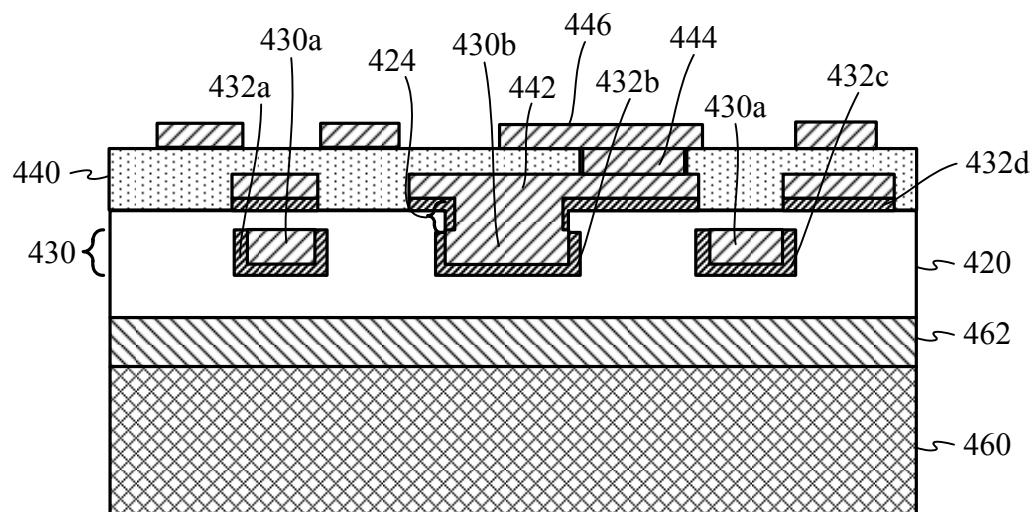

[0052] Nas figuras 4D-4I, uma primeira camada condutora 442 de encaminhamento de uma camada de redistribuição (por exemplo, 440 ilustrados na figura 4L e 4M) é formada sobre a camada de contato 420. A camada de redistribuição pode ser uma camada traseira redistribuição (BRDL) que é formada numa lâmina de espessura completa (por exemplo, o substrato de suporte 460). De acordo com um aspecto da revelação, a camada de redistribuição é formada antes da ligação de um ou mais ativos de pastilha para a estrutura de pacote HFO 400. A camada de redistribuição pode ser formada sobre uma camada dielétrica da camada de contato 420. A formação da camada de redistribuição inclui a formação de condutor encaminhamento camadas e interligando as camadas condutoras de encaminhamento através de vias ou outras interligações (por exemplo, elementos condutores, traços condutores, etc.)

[0053] Na Figura 4D, uma primeira camada condutora de encaminhamento 442 é formada sobre a camada de contato 420. A primeira camada condutora de encaminhamento 442 pode ser formada utilizando a segunda interligação BEOL (por exemplo, M2). Formando a primeira camada condutora de encaminhamento 442 inclui a formação de um contato com a camada condutora de interligação 430. Por exemplo, uma segunda via 424 podem ser formadas por deposição de um material condutor em uma das aberturas e 426B sobre a segunda superfície de uma das porções condutoras 430b. A segunda via 424 pode ser formado usando o primeiro BEOL via

(VI). A segunda via 424 é formado por deposição de um material condutor na abertura 450b no interior da camada de contato 420, em vez de utilizar um processo para a formação de um complexo através de silício através de. A primeira camada de encaminhamento condutora 442 é formada sobre a segunda via 424 e no revestimento de barreira 432d na superfície da camada de contato 420.

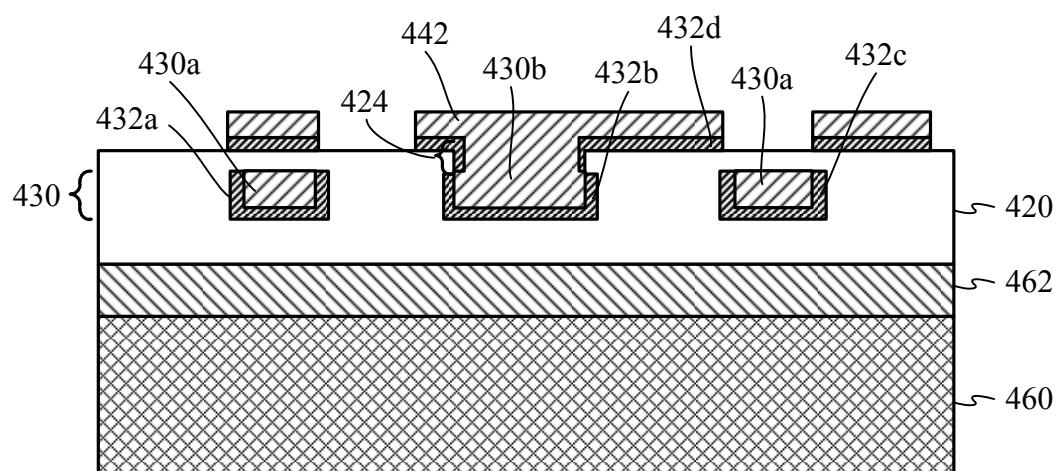

[0054] Na figura 4E, uma primeira camada de material (por exemplo, um material dielétrico de polímero) de uma camada de redistribuição 440 é depositada sobre a camada de contato 420 e em cada uma das partes da primeira camada condutora de encaminhamento 442. Por exemplo, uma primeira camada dielétrica de polímero é depositada sobre as partes da primeira camada condutora 442 de encaminhamento.

[0055] Na figura 4F, uma abertura é formada no interior da primeira camada de material da camada de redistribuição 440 para expor uma superfície da primeira camada de condutor de encaminhamento 442. Neste exemplo, a primeira camada de material da camada de redistribuição 440 inclui uma abertura 441 que expõe uma área de contato da primeira camada de condutor de encaminhamento 442. a área de contato da primeira camada condutora 442 de encaminhamento cara para o substrato de suporte 460.

[0056] Na Figura 4G, uma segunda camada condutora 446 de encaminhamento da camada de redistribuição 440 é formada sobre a primeira camada de material da camada de redistribuição 440. A segunda camada condutora de encaminhamento 446 pode ser formada utilizando a segunda interligação BEOL (por exemplo, M2) que inclui porções condutoras. Formando a segunda camada condutora de encaminhamento 446 inclui a formação de redistribuição de partes condutoras na primeira camada de material da camada

de redistribuição 440. Por exemplo, uma área de contato da segunda camada de encaminhamento condutora 446 está acoplada a uma zona de contato da primeira camada condutora 442 de encaminhamento através uma terceira via 444. A terceira via 444 é formada na abertura 441 no interior da primeira camada de material da camada de redistribuição 440. A terceira via 444 pode ser formado como o segundo BEOL via (por exemplo, V2).

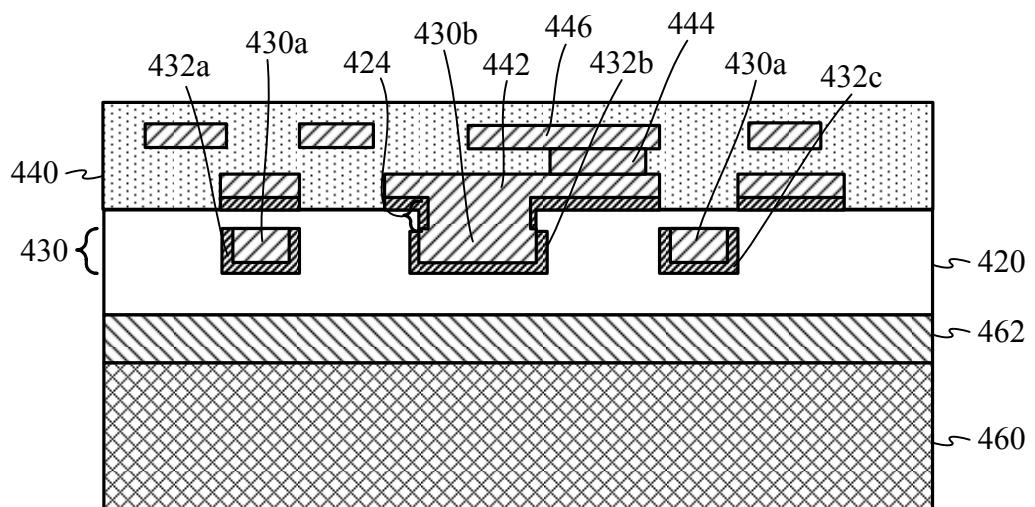

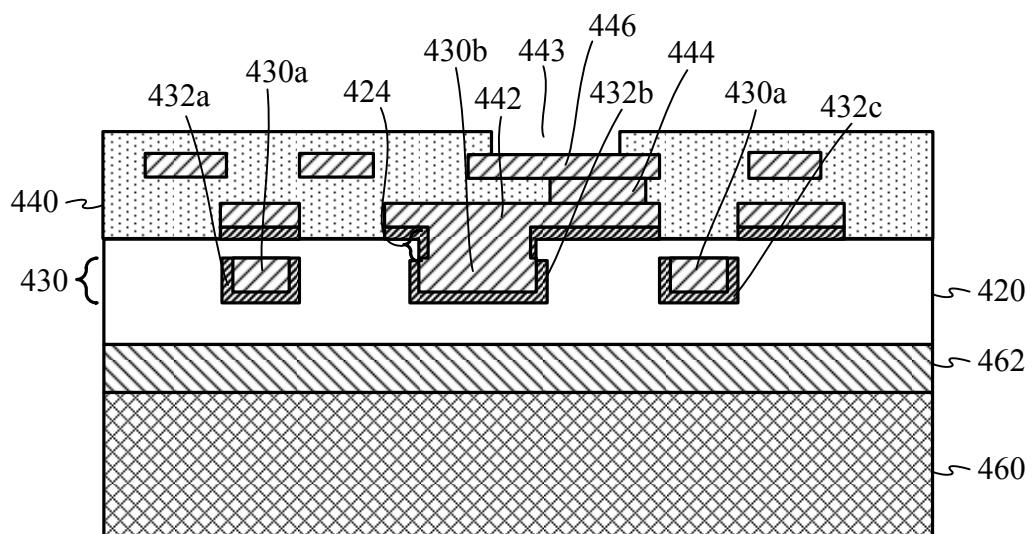

[0057] Na figura 4H, uma segunda camada de material da camada de redistribuição 440 é depositada sobre a primeira camada de material da camada de redistribuição 440. A segunda camada de material da camada de redistribuição 440 é depositada sobre cada uma das porções da segunda camada condutora de encaminhamento 446. Por exemplo, uma segunda camada de material dielétrico de polímero é depositada sobre cada parte condutora da segunda camada condutora 446 de encaminhamento e em que a primeira camada de material dielétrico de polímero da camada de redistribuição 440.

[0058] Na figura 41, uma abertura 443 é formada no interior da segunda camada de material da camada de redistribuição 440 para expor uma superfície da segunda camada condutora de encaminhamento 446. Neste exemplo, a abertura 443 expõe uma área de contato da segunda camada de encaminhamento 446. A área de contato exposta da segunda camada condutora de encaminhamento 446 pode ser preparada para ligar a dispositivos externos. Num aspecto da revelação, a área de contato da segunda camada condutora de encaminhamento 446 pode ser configurada de acordo com uma estrutura de interligação arranjo de grade de esfera (BGA). Por exemplo, a área de contato da segunda camada condutora de encaminhamento 446 pode ser configurada para receber uma camada de interligação sob enchimento para ligar o arranjo

de grade de esfera (BGA) estrutura de interligação para um dispositivo externo.

[0059] Na Figura 4J, um material condutor pode ser depositado na abertura 443 para permitir a ligação da estrutura do pacote HDO 400 para os dispositivos externos. Neste arranjo, uma sob camada de preenchimento de interligação 448 (por exemplo, uma protuberância sob metalização (UBM camada), uma camada de sementes, etc.) é depositado na abertura 443 e na 470b da segunda camada condutora de encaminhamento 446. A área de contato sob encher camada de interligação 448 pode ser configurada para receber uma primeira interligação condutora (por exemplo, 450 da figura 4M) para ligação a um dispositivo externo.

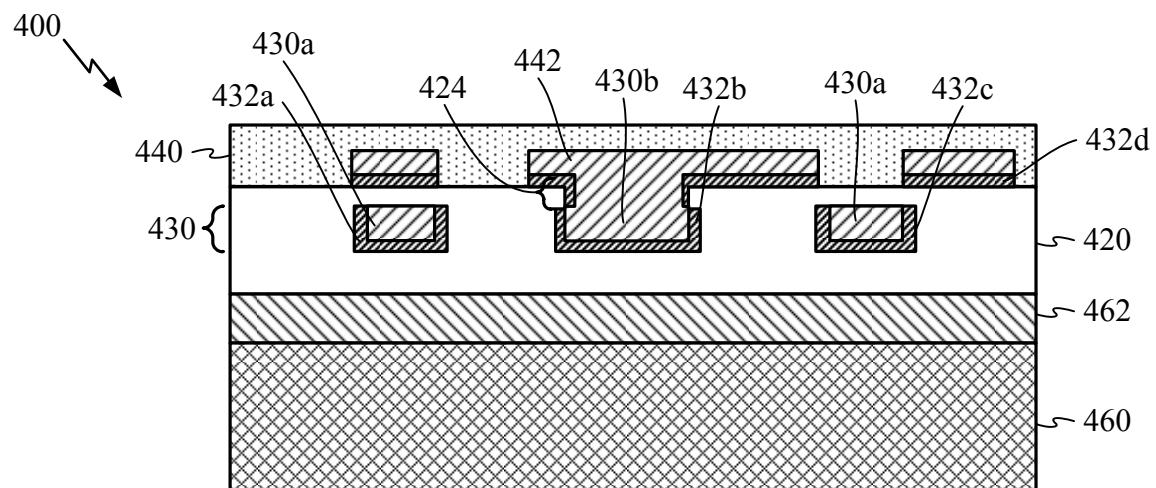

[0060] Na Figura 4K, a estrutura do pacote HDO 400 pode ser diluído para uma espessura desejada através da remoção do substrato de suporte 460. Por exemplo, o substrato de suporte 460 e as outras camadas (por exemplo, camada isolante 462 e/ou uma porção das camadas dielétricas da camada de contato 420) podem ser removidos. As camadas podem ser removidas por um processo de planarização ou de outros processos (por exemplo, moagem, polimento ou decapagem). A remoção do substrato de suporte 460 e da camada de isolamento 462 expõe uma superfície da camada de contato 420. Uma abertura 425 é formada no interior de uma camada dielétrica da camada de contato 420 para expor a barreira porção forro 432B sobre uma das porções condutoras 430b de a camada condutora de interligação 430. a abertura 445 expõe uma área de contato do revestimento de barreira porção 432B do revestimento de barreira 432 que está voltada para fora a partir da camada de redistribuição 440. Esta área exposta contato pode ser configurada para se unir com uma interligação para acoplar uma pastilha ativa para a estrutura de pacote HDO 400.

[0061] Na figura 4L, uma primeira via 422 é formado por deposição de um material condutor (por exemplo, de cobre) na abertura 425. Uma primeira porção condutora 404 (por exemplo, uma pista condutora ou elemento de contato) de um segundo interligação condutora (por exemplo, segunda interligação condutora 410 da figura 4M) é formada sobre a primeira via 422 e sobre a camada de contato 420. A primeira via 422 e a primeira parte condutora 404 podem ser formadas por um processo damasceno duplo. A primeira via 422 e a primeira porção condutora 304 podem ser uma camada de interligação sob enchimento (por exemplo, uma camada UBM). A primeira porção condutora 404 pode ser configurada para se acoplar com um pilar condutor ou de outra interligação como para acoplar uma pastilha ativa para a estrutura de pacote HDFO 400, como mostrado na figura 4M.

[0062] Na figura 4M, de uma pastilha ativa 402 é acoplado à estrutura de pacote HDFO 400 através de uma segunda interligação condutora 410 (por exemplo, frente-lado). Em um aspecto da presente revelação, a segunda de interligação condutora 410 tem uma forma de coluna e inclui uma primeira porção condutora 304 (por exemplo, uma pista condutora ou elemento de contato), uma segunda porção condutora 306 (por exemplo, um material de solda) e uma terceira porção condutora 308 (por exemplo, um pilar condutor da pastilha ativa 302). Neste arranjo, a combinação da primeira porção condutora 404, a segunda porção condutora 406 e a terceira porção condutora 408 formar uma interligação entre o pilar condutor pastilha ativa 402 e o pacote HDFO estrutura 400.

[0063] As figuras 5A-5F ilustram outra estrutura de pacote HDFO 500 em várias etapas de fabricação de acordo com aspectos da presente revelação. Similar às figuras 4A-4M, as figuras 5A-5F ilustram um processo

sequencial para a fabricação da estrutura de pacote HDFO 500.

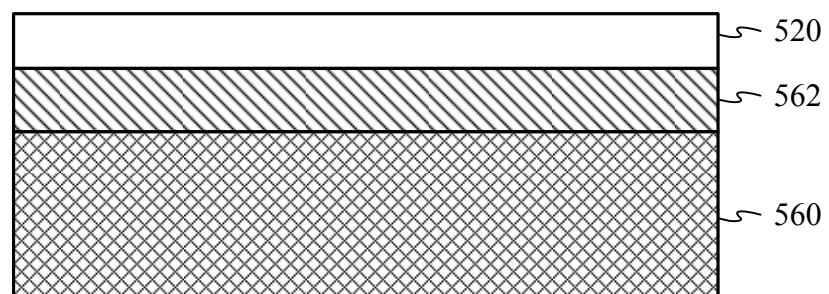

[0064] Começando com a Figura 5A, um primeiro substrato de suporte (por exemplo, uma lâmina de material semicondutor) 560 é fornecido. Uma camada isolante 562 pode ser depositada sobre uma superfície 544 do primeiro substrato de suporte 560. Uma primeira camada dielétrica de uma camada de contato 520 pode ser depositada sobre a camada de isolamento 562. A primeira camada dielétrica da camada de contato 520 pode ser uma camada de passivação incluindo um óxido, um nitreto ou outro material isolador como e pode isolar sinais, bem como proteger os vários circuitos e os elementos condutores.

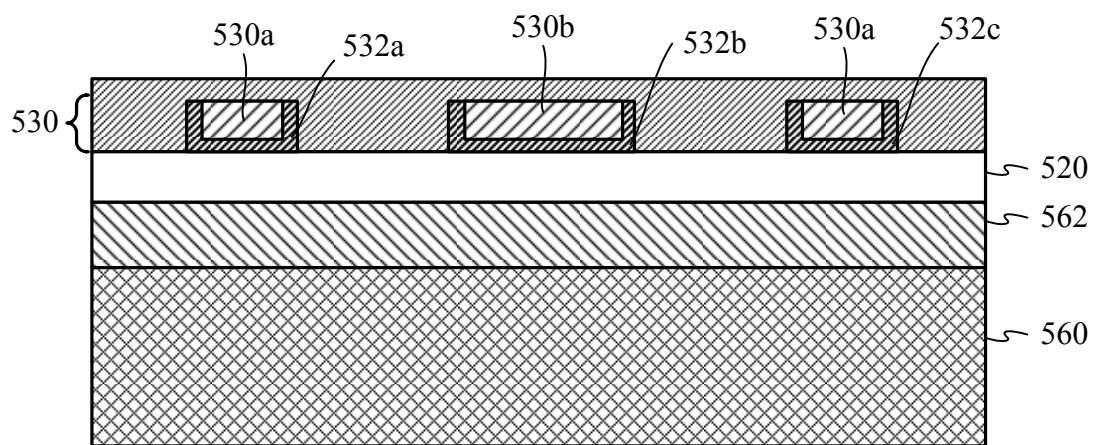

[0065] Na Figura 5B, uma camada de interligação condutora 530 para o encaminhamento de sinais entre uma camada de redistribuição e uma pastilha ativa é depositada sobre a primeira camada dielétrica da camada de contato 520. Por exemplo, a camada de interligação condutora 530 pode ser uma primeira camada de interligação BEOL (por exemplo, M1) que inclui porções condutoras. Uma segunda camada dielétrica da camada de contato 520 é depositada sobre a primeira camada dielétrica e da camada de interligação condutora 530. De modo semelhante às porções condutoras 420a, 420b e 420c, as porções condutoras 520a, 520b e 520c podem ser parcialmente rodeadas por uma barreira forro 532 (532a, 532b, 532c). O revestimento de barreira 532 (por exemplo, a partir da fundição) pode ser tântalo ou outros materiais de barreira adequados.

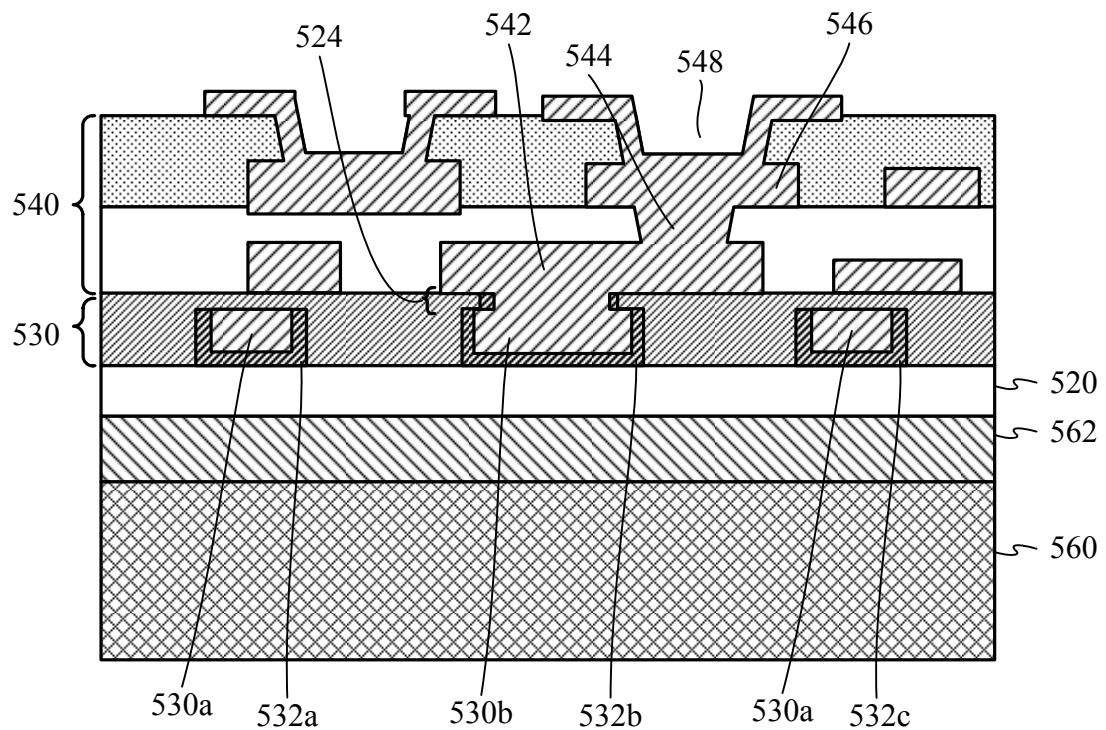

[0066] Similar à Figura 4D-4I, a figura 5C ilustra uma camada de redistribuição 540 formada sobre a camada de contato 520 e acoplado a uma porção de condutor 530b da camada de interligação condutora 530. Como se observou, a camada de redistribuição 540 é formada antes de

anexar um ou morrem mais ativo para a estrutura de pacote HDFO 500. A formação da camada de redistribuição 540 inclui a formação de camadas condutoras de encaminhamento (por exemplo, 542, 546) e a interligação das camadas condutoras de encaminhamento (por exemplo, 542, 546) por meio de vias (por exemplo, 524, 544) ou outras interligações.

[0067] Por exemplo, uma primeira camada de encaminhamento condutora 542 (por exemplo, M2) é formada sobre a camada de contato 520 e acoplado à porção de condutor 530b da camada de interligação condutora 530 utilizando uma segunda via 524 (por exemplo, VI). Uma segunda camada condutora 546 de encaminhamento (por exemplo, M3) é formada sobre uma primeira camada dielétrica de polímero e acoplada à primeira camada condutora 526 de encaminhamento utilizando uma terceira via 524 (por exemplo, V2).

[0068] A área de contato da segunda camada condutora de encaminhamento 546 pode ser acoplada a uma interligação condutora para ligar a estrutura de pacote HDFO 500 para um ou mais dispositivos externos. Num aspecto da revelação, a área de contato da segunda camada condutora de encaminhamento 546 pode ser configurada de acordo com uma estrutura de interligação arranjo de grade de esfera (BGA). Por exemplo, a área de contato da segunda camada condutora de encaminhamento 546 pode ser configurada para receber uma interligação de solda para ligar a estrutura de interligação arranjo de grade de esfera (BGA) para um ou mais dispositivos externos. Num aspecto da revelação, uma camada de enchimento de interligação sob 548, (por exemplo, uma camada traseira UBM) é depositada sobre a área de contato da segunda camada condutora de encaminhamento 546. Por exemplo, a sob camada de preenchimento de interligação 548 pode ser depositado sobre o a área de contato da

segunda camada condutora 546 de encaminhamento.

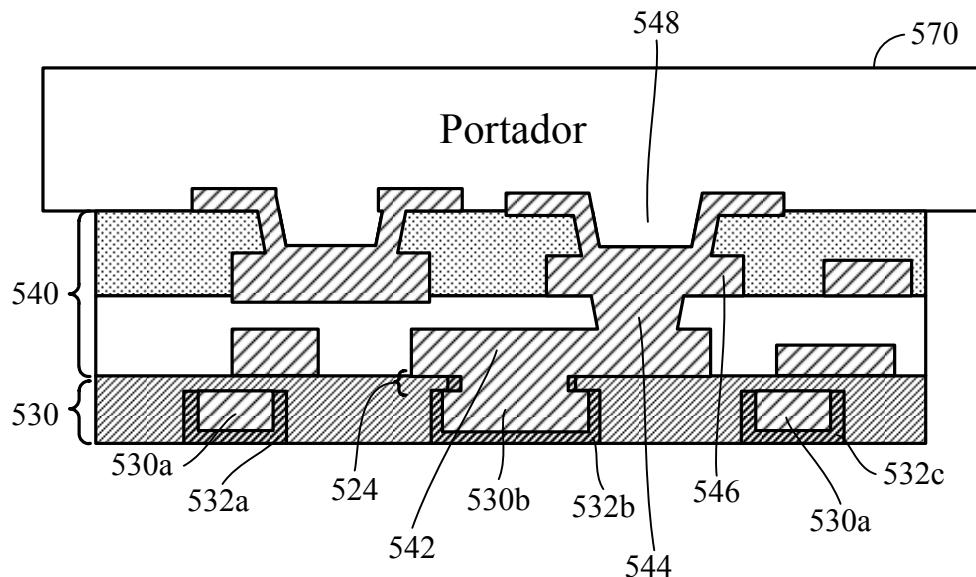

[0069] Em alguns aspectos da invenção, um segundo substrato de suporte 570 pode ser ligada à estrutura do pacote HDO 500 (como mostrado na Figura 5D) para executar os processos restantes.

[0070] Na figura 5D, as camadas da estrutura de pacote HDO 500 são removidas para trazer a estrutura de pacote HDO 500 para uma espessura desejada. As camadas da estrutura de pacote HDO 500 são removidas com o apoio do segundo substrato de suporte 570. Como se observa, o segundo substrato transportador 570 fornece suporte para a estrutura de pacote HDO 500 ao remover as camadas. O segundo substrato de suporte 570 pode ser ligado às superfícies expostas da estrutura de pacote 500 HDO opostos do substrato primeiro transportador 560 que foi removido. Por exemplo, o segundo substrato 570 transportador pode ser configurado para proporcionar uma rigidez estrutural ou uma base para a remoção do primeiro substrato de suporte 560 e as outras camadas (por exemplo, camada 562 e uma camada dielétrica da camada de contato 520 de isolamento). As camadas podem ser removidas por um processo de planarização ou outros processos como (por exemplo, esmerilhagem, polimento ou decapagem).

[0071] Em alternativa, a remoção das camadas pode incluir a remoção do primeiro substrato de suporte 560 e a camada de isolamento 562 para expor a superfície da camada de contato 520, como mostrado na Figura 5E.

[0072] Na figura 5E, uma pastilha ativa 502 é acoplada à estrutura de pacote HDO 500 por uma ou mais interligações. Neste arranjo, uma primeira via 522 (por exemplo, V0) é formado no interior da camada de contato 520. A primeira via 522 pode ser forrada com uma camada de sementes ou uma camada de enchimento de interligação sob

504. A primeira via 522 está alinhado com um segundo condutor interligação 510 para o acoplamento da pastilha ativa para a estrutura de pacote HDO 500. Por exemplo, um material de solda pode ser depositado sobre a camada de interligação sob enchimento 504 para acoplar com um elemento de contato 508 para acoplar a pastilha ativa 502 para a estrutura de pacote HDO 500.

[0073] Na figura 5F, um material da pastilha 580 é acoplado a uma superfície da pastilha ativa 502, oposta à camada de redistribuição 540. Deve reconhecer-se que uma estrutura de pacote HDO, de acordo com aspectos da presente revelação, não se limita ao número de camadas mostradas nas figuras 4A-4M e 5A a 5F.

[0074] A figura 6 é um diagrama de fluxo que ilustra um modo 600 para a fabricação de uma estrutura de pacote de saída em leque de alta densidade (HDO) de acordo com um aspecto da revelação. No bloco 602, uma camada de contato é fabricada num substrato de suporte. A camada de contato inclui uma camada de interligação condutora possuindo um revestimento de barreira sobre uma primeira superfície, por exemplo, como mostrado nas figuras 3 e 4M. No bloco 604, uma camada de redistribuição (RDL) é fabricada. A RDL inclui camadas condutoras de encaminhamento configurado para acoplar uma primeira interligação condutora para a interligação camada condutora. No bloco 606, um material condutor é depositado dentro de uma abertura na camada de contato para formar uma primeira via sobre o forro de barreira, após remoção do substrato de suporte. Por exemplo, como mostrado na figura 4K e 4L, o primeiro meio 422 é formado após a remoção do substrato de suporte 460. No bloco 608, uma pastilha ativa é ligada à via utilizando um segundo interligação condutora. Nesta disposição, o forro de barreira 432 na

primeira superfície da camada de interligação condutora 430 está virado para a pastilha ativa 402, por exemplo, como mostrado na figura 4M.

[0075] Em uma configuração, uma estrutura de pacote de saída em leque de alta densidade (HDF0) inclui meios para o acoplamento de uma primeira interligação condutora para interligar uma camada condutora. Nesta configuração, uma segunda superfície da camada condutora de interligação enfrenta os meios de acoplamento e uma primeira superfície da camada condutora de interligação enfrenta uma pastilha ativa. Num aspecto da revelação, os meios de acoplamento, são as camadas de redistribuição 440/550 das figuras 4M e 5F, configuradas para executar as funções citadas por os meios de acoplamento. Noutro aspecto, os meios acima referidos pode ser um dispositivo ou qualquer camada configurado para executar as funções citadas por os meios acima referidos.

[0076] Uma estrutura de pacote HDF0, de acordo com aspectos da presente revelação, inclui pastilha ativa multipla ou uma única estrutura de chip. A estrutura de pacote HDF0 pode ser fabricada de acordo com um chip do processo de anexação. O processo de última anexação de chip inclui acoplar uma pastilha ativa para a estrutura de pacote HDF0 depois uma camada de redistribuição é formada. Por exemplo, a camada de redistribuição pode ser verificada por meio de testes antes da pastilha ativa está ligado a fim de evitar ligação a uma camada de redistribuição com defeito.

[0077] Em um aspecto da revelação, a estrutura do pacote HDF0 inclui uma camada de contato que inclui uma camada de interligação condutora. A camada de interligação condutora pode incluir uma primeira superfície virada para uma pastilha ativa e uma segunda superfície voltada para a

camada de redistribuição. Uma primeira interligação condutora (por exemplo, arranjo de grade de esfera (BGA)) podem acoplar a estrutura de pacote HDFO para um dispositivo externo. Um revestimento condutor pode ser disposto sobre a primeira superfície da camada de interligação condutora. O revestimento condutor pode ser uma barreira ou semente forro de tântalo. O revestimento de barreira pode proporcionar proteção para a camada condutora interligam durante a formação (por exemplo, galvanização) das interligações para a pastilha ativa.

[0078] A camada de redistribuição (RDL) é acoplada à camada condutora de interligação da camada de contato. A camada de redistribuição pode ser uma camada de encaminhamento de saída em leque. A camada de redistribuição inclui camadas condutoras de encaminhamento configurado para acoplar uma primeira interligação condutora para a interligação camada condutora. Como observado, o camada de redistribuição é formada antes de fixar a pastilha ativa para evitar danificar a pastilha ativa durante a formação da camada de redistribuição. A camada de redistribuição pode ser uma camada traseira redistribuição (BRDL) que é formada numa lâmina de espessura completa. Implementando a estrutura do pacote HDFO sobre a camada traseira redistribuição melhora o rendimento da pastilha ativa e reduz a deformação da estrutura do pacote HDFO.

[0079] Uma via pode ser acoplada ao revestimento de barreira para interligar a segunda interligação condutora da pastilha ativa. O material condutor pode incluir um ou mais condutores interliga. Por exemplo, o segundo material condutor pode incluir uma interligação protuberância sob condutor, um material de solda e/ou um pilar condutor. A interligação condutora

protuberância sob pode ser disposta numa abertura no interior da camada condutora que expõe uma superfície do revestimento de barreira. O pilar condutor pode ser acoplado a um elemento de contato da pastilha. O material de solda ser interligação entre o condutor e protuberância sob o pilar condutor. A protuberância sob interligação condutora e o pilar condutor podem ser de cobre.

[0080] A figura 7 é um diagrama de blocos que mostra um sistema de comunicação sem fio exemplificativo 700, em que um aspecto da revelação pode ser empregado vantajosamente. Para fins de ilustração, a Figura 7 mostra três unidades remotas 720, 730 e 750; e duas estações base 740. Será reconhecido que os sistemas de comunicação sem fio podem ter muitas mais unidades remotas e as estações de base. As unidades remotas 720, 730, e 750 incluem IC dispositivos 725a, 725c, 725b e que incluem a estrutura de pacote HDFO divulgado. Será reconhecido que outros dispositivos podem também incluir a estrutura descrita HDFO pacote, tais como as estações de base, dispositivos de comutação, e equipamento de rede. A figura 7 mostra sinais de ligação direta 780 da estação base 740 para as unidades remotas 720, 730, e 750 e 790 a partir das unidades remotas 720, 730, e 750 sinais de ligação inversa para estações base 740.

[0081] Na Figura 7, a unidade remota 720 é mostrada como um telefone móvel, a unidade remota 730 é mostrada como um computador portátil; e a unidade remota 750 é mostrada como uma unidade remota local fixa num sistema de rede local sem fio. Por exemplo, as unidades remotas 720, 730 e 750 pode ser um telefone celular, um sistema de comunicação pessoal de mão (PCS) da unidade, um dispositivo de comunicação, uma unidade de dados portátil, como um assistente pessoal digital (PDA), um GPS

dispositivo habilitado, um dispositivo de navegação, um conversor de sinais, um leitor de música, leitor de vídeo, uma unidade de entretenimento, uma unidade de dados local fixo, como um equipamento de leitura de medidores, ou outros dispositivos que armazenam ou recuperam dados ou instruções de computador, ou combinações dos mesmos. Embora a Figura 7 ilustre as unidades remotas de acordo com os aspectos da revelação, a revelação não se limita a estas unidades ilustradas, exemplares. Os aspectos da revelação podem ser apropriadamente empregados em muitos dispositivos, que incluem os dispositivos revelados.

[0082] A figura 8 é um diagrama de blocos que ilustra uma estação de trabalho de criação usada para o circuito, a disposição, e a concepção lógica de um componente semicondutor, tal como os dispositivos descritos acima. Uma estação de trabalho de design 800 inclui um disco de 802 software disco contendo o sistema operacional, arquivos de suporte e software de projeto, como Cadence ou OrCAD. A estação de trabalho de concepção 800 também inclui um visor 804 para facilitar a criação de um circuito 806 ou um componente semicondutor 808, tais como uma estrutura de pacote HFO. Um meio de armazenamento 810 é fornecido para armazenar de modo tangível o desenho do circuito 806 ou o componente semicondutor 808. O desenho do circuito 806 ou o componente semicondutor 808 podem ser armazenados no meio de armazenamento 810 num formato de arquivo tal como GDSII ou Gerber. O meio de armazenamento 810 pode ser um CD-ROM, DVD, disco rígido, memória flash, ou outro dispositivo apropriado. Além disso, a estação de trabalho de projeto 800 inclui um aparelho de acionamento 812 para aceitar a entrada de ou gravação de saída para o meio de armazenamento 810.

[0083] Os dados gravados no meio de

armazenamento 810 podem especificar configurações de circuito lógico, dados de padrão para máscaras de fotolitografia, ou dados padrão de máscara para ferramentas de gravação de série, tais como a litografia por feixe de elétrons. Os dados podem ainda incluir dados de verificação de lógica, tais como diagramas de temporização ou circuitos líquidos associados com simulações lógicas. Fornecer dados no meio de armazenamento 810 facilita a concepção do circuito 806 ou do componente semicondutor 808, diminuindo o número de processos para a concepção de pastilhas semicondutoras.

[0084] Para uma implementação de software e/ou de firmware, as metodologias podem ser implementadas com módulos (por exemplo, procedimentos, funções, e assim por diante) que desempenham as funções aqui descritas. Um meio legível por máquina, de modo tangível que contém as instruções podem ser utilizadas na aplicação das metodologias aqui descritas. Por exemplo, os códigos de software podem ser armazenados em uma memória e executado por uma unidade do processador. Memória pode ser implementada dentro da unidade de processador ou externo à unidade do processador. Tal como aqui utilizado, o termo "memória" refere-se a tipos de longo prazo, a curto prazo, volátil, não-volátil, ou outra memória e não é para ser limitada a um tipo particular de memória ou número de memórias, ou tipo de suporte sobre a qual memória está armazenada.

[0085] Se implementado em firmware e/ou software, as funções podem ser armazenadas como uma ou mais instruções ou código num meio legível por computador. Exemplos incluem meios legíveis por computador codificados com uma estrutura de dados e meios legíveis por computador codificados com um programa de computador. Meios legíveis

por computador incluem físicos suportes informáticos. Um meio de armazenamento pode ser um meio disponível que pode ser acedido por um computador. A título de exemplo, e não como limitação, tais meios legíveis por computador podem incluir RAM, ROM, EEPROM, CD-ROM ou outro armazenamento em disco óptico, armazenamento em disco magnético ou outros dispositivos de armazenamento magnético, ou qualquer outro meio que possa ser utilizado para armazenar o desejar código de programa na forma de instruções ou estruturas de dados e que pode ser acessado por um computador; disco e do disco, tal como é aqui utilizado, inclui disco compacto (CD), disco laser, disco tico, disco versátil digital (DVD) e disco Blu-ray, onde discos geralmente reproduzir dados magneticamente, enquanto que os discos reproduzir dados opticamente com lasers. Combinações dos anteriores também devem ser incluídas no âmbito da mídia legível por computador.

[0086] Em adição à armazenagem em meio legível por computador, as instruções e/ou os dados podem ser fornecidos como sinais no meio de transmissão incluída num aparelho de comunicação. Por exemplo, um aparelho de comunicação pode incluir um emissor-receptor com os sinais indicativos de instruções e dados. As instruções e dados são configurados para fazer com que um ou mais processadores para executar as funções descritas nas reivindicações.

[0087] Embora a presente descrição e as suas vantagens tenham sido descritas em detalhe, deve ser entendido que várias mudanças, substituições e alterações podem ser aqui feitas sem afastamento da tecnologia da revelação tal como definida pelas reivindicações anexas. Por exemplo, termos relacionais, tais como "em cima" e "inferior" são usados em relação a um substrato ou

dispositivo eletrônico. Claro que, se o dispositivo eletrônico ou substrato é invertido, acima torna-se abaixo, e vice-versa. Além disso, se orientada para o lado, acima e abaixo pode referir-se para os lados de um substrato ou dispositivo eletrônico. Além disso, o âmbito do presente pedido de patente não se destina a ser limitado às configurações particulares de: processo, máquina, fabricação, composição de matéria, meios, métodos e etapas; descritos no relatório descritivo. Como um perito na arte apreciará de imediato a partir da descrição, os processos, máquinas, fabricação, composições da matéria, meios, métodos, ou etapas, atualmente existentes ou mais tarde a ser desenvolvida que realizam substancialmente a mesma função ou atingir substancialmente a mesma resultar como as configurações correspondentes aqui descritas podem ser utilizadas de acordo com a presente revelação. Por conseguinte, as reivindicações anexas destinam-se a incluir no seu âmbito tais processos, máquinas, fabricação, composições da matéria, meios, métodos, ou etapas.

[0088] Aqueles versados na arte considerariam ainda que os vários blocos, módulos, circuitos e etapas de algoritmo ilustrativos descritos lógicos em conexão com a descrição aqui podem ser implementados como hardware eletrônico, software de computador, ou combinações de ambos. Para ilustrar claramente esta permutabilidade de hardware e software, vários componentes ilustrativos, blocos, módulos, circuitos, e etapas foram descritos acima, geralmente em termos da sua funcionalidade. Se tal funcionalidade é implementada como hardware ou software depende da aplicação e design limitações específicas impostas ao sistema global. Os especialistas na técnica podem implementar a funcionalidade descrita de maneiras diferentes para cada aplicação específica, mas tais

decisões de execução não devem ser interpretadas como causando um afastamento do âmbito da presente revelação.

[0089] Os vários blocos lógicos, módulos, e circuitos ilustrativos descritos em conexão com a descrição aqui podem ser implementados ou executados com um processador de uso geral, um processador de sinal digital (DSP), uma aplicação específica de circuitos integrados (ASIC), um arranjo de porta programável no campo (FPGA) ou outro dispositivo lógico programável, porta discreta ou lógica de transistor, componentes discretos de hardware, ou qualquer combinação dos mesmos concebidos para executar as funções aqui descritas. Um processador de uso geral pode ser um microprocessador, mas em alternativa, o processador pode ser qualquer processador convencional, controlador, microcontrolador, ou máquina de estados convencional. Um processador também pode ser implementado como uma combinação de dispositivos de computação, por exemplo, uma combinação de um DSP e um microprocessador, múltiplos microprocessadores, um ou mais microprocessadores em conjunto com um núcleo DSP, ou qualquer outro tipo de configuração.

[0090] As etapas de um processo ou algoritmo descrito em conexão com a revelação podem ser incorporadas diretamente em hardware, num mulo de software executado por um processador, ou numa combinação dos dois. Um módulo de software pode residir na memória RAM, memória flash, ROM, EPROM, EEPROM, registros, disco rígido, um disco amovível, um CD-ROM, ou qualquer outra forma de meio de armazenamento conhecido na técnica. Um meio de armazenamento exemplificativo é acoplado ao processador de modo que o processador pode ler informação de, e escrever informação para, o meio de armazenamento. Em alternativa, o meio de armazenamento pode ser parte integrante do processador. O

processador e o meio de armazenamento podem residir em um ASIC. O ASIC pode residir num terminal de utilizador. Em alternativa, o processador e o meio de armazenamento podem residir como componentes discretos num terminal de utilizador.

[0091] Em um ou mais desenhos exemplares, as funções descritas podem ser implementadas em hardware, software, firmware, ou qualquer combinação dos mesmos. Se implementadas em software, as funções podem ser armazenadas ou transmitidas como uma ou mais instruções ou código num meio legível por computador. Mídia legível por computador inclui meios de armazenamento de computador e meios de comunicação, incluindo qualquer meio que facilite a transferência de um programa de computador a partir de um lugar para outro. A mídia de armazenamento pode ser qualquer meio disponível que pode ser acessado por um propósito geral ou computador de propósito especial. A título de exemplo, e não como limitação, tais meios legíveis por computador podem incluir RAM, ROM, EEPROM, CD-ROM ou outro armazenamento em disco óptico, armazenamento em disco magnético ou outros dispositivos de armazenamento magnético, ou qualquer outro meio que possa ser utilizado para transportar ou loja especificado código de programa significa na forma de instruções ou estruturas de dados e que pode ser acessado por um computador de uso comum ou de uso especial, ou um processador de propósito geral ou de propósito especial. Além disso, qualquer conexão é denominada corretamente um meio legível por computador. Por exemplo, se o software é transmitido de um site, servidor ou outra fonte remota utilizando um cabo coaxial, cabo de fibra óptica, par trançado, linha de assinante digital (DSL) ou tecnologias sem fio tais como infravermelhos, rádio e microondas, em seguida, o cabo coaxial, cabo de

fibra óptica, o par torcido, DSL, ou tecnologias sem fio, tais como infravermelho, rádio e microondas estão incluídos na definição de forma. Disco e disco, como aqui utilizado, incluem disco compacto (CD), disco laser, disco óptico, disco versátil digital (DVD) e Blu-ray onde os discos geralmente reproduzem dados magneticamente, enquanto que os discos reproduzem dados opticamente com lasers. Combinações dos anteriores também devem ser incluídas no âmbito da mídia legível por computador.

[0092] A descrição anterior da revelação é fornecida para permitir àqueles versados na arte fazer ou utilizar a revelação. Várias modificações à revelação serão prontamente aparentes para os versados na arte, e os princípios genéricos aqui definidos poderão ser aplicados a outras variações sem nos afastarmos do espírito ou âmbito da revelação. Assim, a descrição não se destina a ser limitada aos exemplos e desenhos aqui descritos, mas deve estar de acordo com o mais vasto âmbito consistente com os princípios e características inovadoras aqui apresentadas.

## REIVINDICAÇÕES

1. Estrutura de pacote de saída em leque, **caracterizada pelo** fato de que compreende:

uma camada de contato (320, 420, 520) incluindo uma camada de interligação condutora (330, 430, 530), a camada de interligação condutora tendo uma primeira superfície voltada para uma pastilha ativa (302, 402, 502), uma segunda superfície voltada para uma camada de redistribuição (340, 440, 540), e pelo menos uma parede lateral;

um revestimento de barreira (332, 432, 532), a camada de interligação condutora incluindo o revestimento de barreira apenas na parede lateral e na primeira superfície da camada de interligação condutora;

a camada de redistribuição compreendendo uma pluralidade de camadas condutoras de encaminhamento configuradas para acoplar uma primeira interligação condutora (350, 450) à camada de interligação condutora; e

uma primeira via (322, 422, 522) acoplada ao revestimento de barreira, a primeira via configurada para acoplar o revestimento de barreira à pastilha ativa através de uma segunda interligação condutora (310, 410, 510).

2. Estrutura, de acordo com a reivindicação 1, **caracterizada pelo** fato de que a primeira interligação condutora é um arranjo de grade de esfera.

3. Estrutura, de acordo com a reivindicação 1, **caracterizada pelo** fato de que o revestimento de barreira compreende tântalo.

4. Estrutura, de acordo com a reivindicação 1, **caracterizada pelo** fato de que a primeira via compreende uma camada condutora sob protuberância no revestimento de barreira e um material condutor na camada condutora sob protuberância e acoplada à segunda interligação condutora.

5. Estrutura, de acordo com a reivindicação 1, **caracterizada pelo** fato de que a camada de interligação condutora compreende uma primeira camada de interligação condutora (M1) de extremidade inicial de linha, BEOL.

6. Estrutura, de acordo com a reivindicação 1, **caracterizada pelo** fato de que a segunda interligação condutora compreende um pilar condutor ou uma protuberância condutora.

7. Estrutura, de acordo com a reivindicação 1, **caracterizada pelo** fato de que a segunda interligação condutora é acoplada a um elemento de contato da pastilha ativa.

8. Estrutura, de acordo com a reivindicação 1, **caracterizada pelo** fato de que a camada de interligação condutora é acoplada a uma dentre a pluralidade de camadas condutoras de encaminhamento da camada de redistribuição através de uma segunda via ou um traço condutor na camada condutora de encaminhamento.

9. Estrutura, de acordo com a reivindicação 8, **caracterizada pelo** fato de que a primeira via compreende uma via zero de meio de linha e a segunda via compreende uma primeira via BEOL.

10. Estrutura, de acordo com a reivindicação 1, **caracterizada pelo** fato de que é incorporada em pelo menos um dentre um reproduutor de música, um reproduutor de vídeo, uma unidade de entretenimento, um dispositivo de navegação, um dispositivo de comunicação, um assistente digital pessoal, PDA, uma unidade de dados de localização fixa, e um computador.

11. Método para uma estrutura de pacote de saída em leque de alta densidade, **caracterizado pelo** fato de que compreende:

fabricar (602) uma camada de contato (320, 420,

520) em um substrato portador (460, 560), a camada de contato incluindo uma camada de interligação condutora (330, 430, 530), a camada de interligação condutora tendo um revestimento de barreira (332, 432, 532) apenas em uma parede lateral e em uma primeira superfície da camada de interligação condutora;

fabricar (604) uma camada de redistribuição (340, 440, 540) compreendendo uma pluralidade de camadas condutoras de encaminhamento, a pluralidade de camadas condutoras de encaminhamento sendo configurada para acoplar uma primeira interligação condutora (350, 450) à camada de interligação condutora;

depositar (606), após remover o substrato portador, um material condutor dentro de uma abertura na camada de contato para formar uma primeira via (322, 422, 522), disposta no revestimento de barreira; e então

fixar (608) uma pastilha ativa (302, 402, 502) a primeira via utilizando uma segunda interligação condutora (310, 410, 510), na qual o revestimento de barreira na primeira superfície da camada de interligação condutora está voltado para a pastilha ativa.

12. Método, de acordo com a reivindicação 11 **caracterizado pelo** fato de que o depósito do material condutor comprehende adicionalmente:

depositar uma camada condutora sob protuberância sobre o revestimento de barreira; e

depositar o material condutor sobre a camada condutora sob protuberância e acoplar à segunda interligação condutora.

13. Método, de acordo com a reivindicação 11, **caracterizado pelo** fato de que comprehende adicionalmente depositar tântalo sobre a primeira superfície da camada de interligação condutora que está voltada para a pastilha

ativa como o revestimento de barreira.

14. Método, de acordo com a reivindicação 11 **caracterizado pelo** fato de que fabricar a camada de contato compreende adicionalmente:

depositar uma camada isolante sobre o substrato portador;

depositar uma camada dielétrica sobre a camada isolante; e

fabricar porções condutoras da camada de interligação condutora utilizando uma primeira camada de interligação condutora de extremidade final de linha.

15. Método, de acordo com a reivindicação 11, **caracterizado pelo** fato de que compreende adicionalmente incorporar a estrutura de pacote de saída em leque de alta densidade em pelo menos um dentre um reproduutor de música, um reproduutor de vídeo, uma unidade de entretenimento, um dispositivo de navegação, um dispositivo de comunicação, um assistente pessoal digital, uma unidade de dados de localização física, e um computador.

***FIG. 1***

***FIG. 2***

**FIG. 3****FIG. 4A****FIG. 4B**

**FIG. 4C**

**FIG. 4D**

**FIG. 4E**

**FIG. 4F**

**FIG. 4G**

**FIG. 4H****FIG. 4I****FIG. 4J**

**FIG. 4K****FIG. 4L**

**FIG. 4M****FIG. 5A**

**FIG. 5B****FIG. 5C**

**FIG. 5D****FIG. 5E**

**FIG. 5F**

**FIG. 6**

**FIG. 7**

ESTAÇÃO DE TRABALHO

DE PROJETO

800

**FIG. 8**