## (12) NACH DEM VERTRAG ÜBER DIE INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES PATENTWESENS (PCT) VERÖFFENTLICHTE INTERNATIONALE ANMELDUNG

(19) Weltorganisation für geistiges Eigentum

Internationales Büro

(43) Internationales Veröffentlichungsdatum

7. Juni 2012 (07.06.2012)

(10) Internationale Veröffentlichungsnummer

WO 2012/072212 A2

(51) Internationale Patentklassifikation:

H01L 23/538 (2006.01)

(81) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare nationale Schutzrechtsart): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) Internationales Aktenzeichen: PCT/EP2011/005912

(22) Internationales Anmeldedatum:

24. November 2011 (24.11.2011)

(25) Einreichungssprache: Deutsch

(26) Veröffentlichungssprache: Deutsch

(30) Angaben zur Priorität:

10 2010 060 855.6

29. November 2010 (29.11.2010) DE

(71) Anmelder (für alle Bestimmungsstaaten mit Ausnahme von US): SCHWEIZER ELECTRONIC AG [DE/DE]; Einsteinstr. 10, 78713 Schramberg (DE).

(72) Erfinder; und

(75) Erfinder/Anmelder (nur für US): GOTTWALD, Thomas [DE/DE]; Hochwiesenstr. 27, 78655 Dunningen-Seedorf (DE). RÖSSLER, Christian [DE/DE]; Im Park 4, 78112 St. Georgen (DE).

(74) Anwalt: HÖSSLE, Markus; Hössle Patentanwälte Partnerschaft, Postfach 10 23 38, 70019 Stuttgart (DE).

(84) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare regionale Schutzrechtsart): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), eurasisches (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), europäisches (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

[Fortsetzung auf der nächsten Seite]

(54) Title: ELECTRONIC DEVICE, METHOD FOR PRODUCING THE LATTER, AND PRINTED CIRCUIT BOARD COMPRISING ELECTRONIC DEVICE

(54) Bezeichnung : ELEKTRONISCHES BAUTEIL, VERFAHREN ZU DESSEN HERSTELLUNG UND LEITERPLATTE MIT ELEKTRONISCHEM BAUTEIL

(57) Abstract: The present invention encompasses an electronic device (50) comprising an electrically conductive core layer (10) with a first layer (16) composed of electrically conductive material, said first layer being applied on both sides, and with at least one electronic component (20) arranged in a cutout (18) of the first layer (16), wherein the first layer (16) is covered in each case with an electrically insulating, thermally conductive layer (34, 36) and a further layer (22, 26) composed of electrically conductive material is provided in each case on the thermally conductive layer (34, 36), said further layer being coated in each case with a covering layer (38) composed of electrically conductive material, and furthermore having plated-through holes (24) composed of the material of the covering layer (38), which extend through the electrically insulating, thermally conductive layer (36) covering the electronic component (20) and the further layer (22) composed of electrically and thermally conductive material for the purpose of making contact with the electronic component (20).

(57) Zusammenfassung:

[Fortsetzung auf der nächsten Seite]

**Veröffentlicht:**

- *ohne internationalen Recherchenbericht und erneut zu veröffentlichen nach Erhalt des Berichts (Regel 48 Absatz 2 Buchstabe g)*

---

Die vorliegende Erfindung umfasst ein elektronisches Bauteil (50) mit einer elektrisch leitenden Kernschicht (10) mit einer beidseitig aufgebrachten ersten Schicht (16) aus elektrisch leitendem Material und mit mindestens einem in einer Ausnehmung (18) der ersten Schicht (16) angeordneten elektronischen Bauelement (20), wobei die erste Schicht (16) jeweils mit einer elektrisch isolierenden, thermisch leitfähigen Schicht (34, 36) bedeckt ist und auf der thermisch leitfähigen Schicht (34, 36) jeweils eine weitere Schicht (22, 26) aus elektrisch leitendem Material vorgesehen ist, die jeweils mit einer Deckschicht (38) aus elektrisch leitendem Material überzogen sind, und mit des weiteren Durchkontaktierungen (24) aus dem Material der Deckschicht (38), die sich durch die das elektronische Bauelement (20) bedeckende elektrisch isolierende, thermisch leitfähige Schicht (36) und die weitere Schicht (22) aus elektrisch und thermisch leitendem Material zum Ankontakteieren des elektronischen Bauelements (20) erstrecken.

**Elektronisches Bauteil, Verfahren zu dessen Herstellung und

Leiterplatte mit elektronischem Bauteil**

Die vorliegende Erfindung betrifft ein elektronisches Bauteil sowie ein Verfahren zu dessen Herstellung.

Aus der DE 10 2009 013 818 A1 ist ein Verfahren zur Herstellung einer elektronischen Vorrichtung bekannt, bei dem nach dem Bereitstellen eines Trägers mit einer ersten leitenden Schicht über dieser ersten leitenden Schicht eine erste isolierende Schicht aufgebracht wird und mindestens eine Durchgangsverbindung von einer ersten Seite der ersten isolierenden Schicht zu einer zweiten Seite der ersten isolierenden Schicht erzeugt wird. Mindestens zwei Halbleiterchips werden an dem Träger angebracht und eine zweite isolierende Schicht wird über dem Träger aufgebracht. Dann wird die zweite isolierende Schicht geöffnet, bis der Träger freigelegt ist und eine Metallschicht wird über der geöffneten zweiten isolierenden Schicht abgeschieden, woraufhin die mindestens zwei Halbleiterchips getrennt werden.

Demgegenüber wird erfindungsgemäß ein elektronisches Bauteil mit den Merkmalen der Ansprüche 1 und 2, ein Verfahren zu deren Herstellung mit den Merkmalen der Ansprüche 6 und 7 sowie eine Leiterplatte mit erfindungsgemäßen Bauteilen mit den Merkmalen des Anspruchs 14 und ein Verfahren zum Integrieren eines elektronischen Bauteils in eine Leiterplatte mit den Merkmalen des Anspruchs 18 vorgeschlagen.

Das erfindungsgemäße elektronische Bauteil stellt eine kostengünstige Alternative zu Ausführungen aus Keramik dar. Gegenüber Ausführungsformen aus Keramik ist das elektronische Bauteil außerdem mit einer deutlich geringeren Bruchgefahr behaftet. Da die sonst üblichen langen Bonddrähte aus Aluminium durch kurze Vias aus Kupfer ersetzt sind, ist eine deutliche Verringerung des Einschaltwiderstands die Folge. Darüber hinaus ist mit der erfindungsgemäßen Ausgestaltung eine Reduzierung der Chipgröße möglich, da die verwendete galvanische Ankontaktierung weniger Fläche benötigt als die sonst üblichen Bonddrähte. Aufgrund des symmetrischen Schichtaufbaus verfügt das elektronische Bauteil über eine erhöhte Planarität. Die Differenz der thermischen Ausdehnungskoeffizienten zwischen den Chips und den Kontaktierungen ist verringert, woraus eine Steigerung der Zuverlässigkeit resultiert. Ein weiterer Vorteil besteht darin, dass die elektrische Isolierung, z.B. zu einem Motorrengehäuse, bereits durch das Dielektrikum in dem Bauteilmodul integriert ist. Das erzeugte Bauteil kann direkt in eine Leiterplatte integriert werden, was eine kostengünstige Komplettlösung darstellt.

Weitere Vorteile und Ausgestaltungen der Erfindung ergeben sich aus der Beschreibung und der beiliegenden Zeichnung.

Es versteht sich, dass die voranstehend genannten und die nachstehend noch zu erläuternden Merkmale nicht nur in der jeweils angegebenen Kombination, sondern auch in anderen Kombinationen oder in Alleinstellung verwendbar sind, ohne den Rahmen der vorliegenden Erfindung zu verlassen.

Die Erfindung ist zur Veranschaulichung anhand von Ausführungsbeispielen in der Zeichnung schematisch und nicht maßstabsgetreu dargestellt und wird im folgenden unter Bezugnahme auf die Zeichnung ausführlich beschrieben.

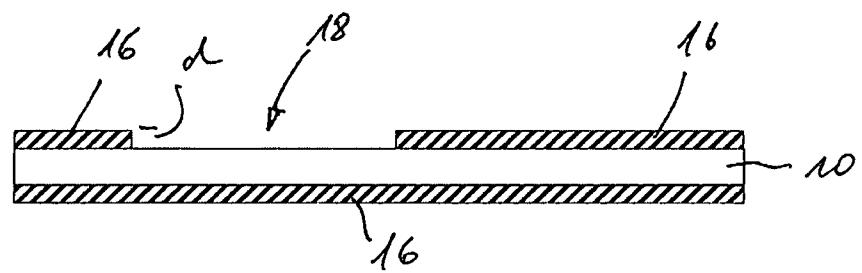

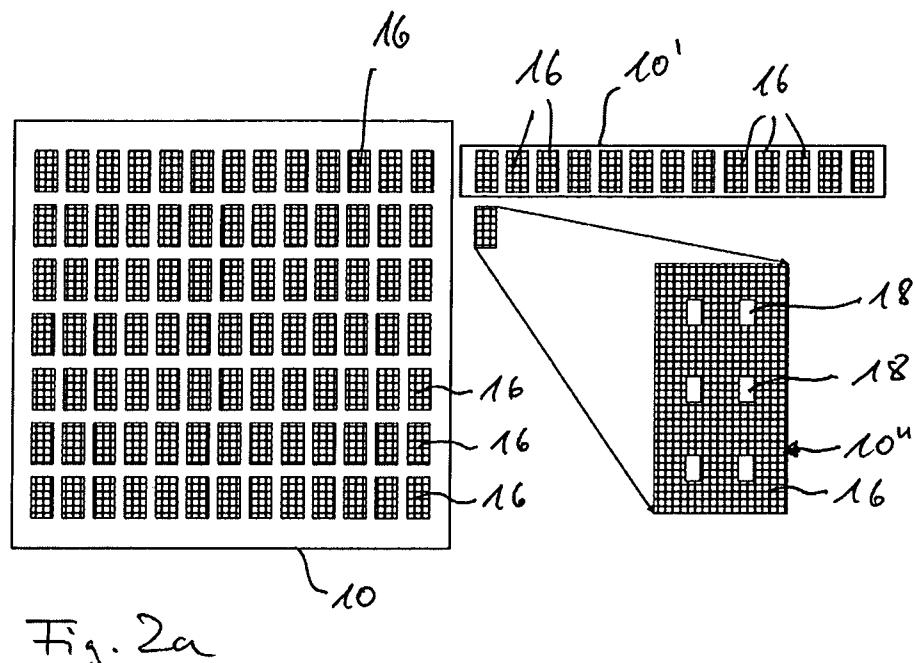

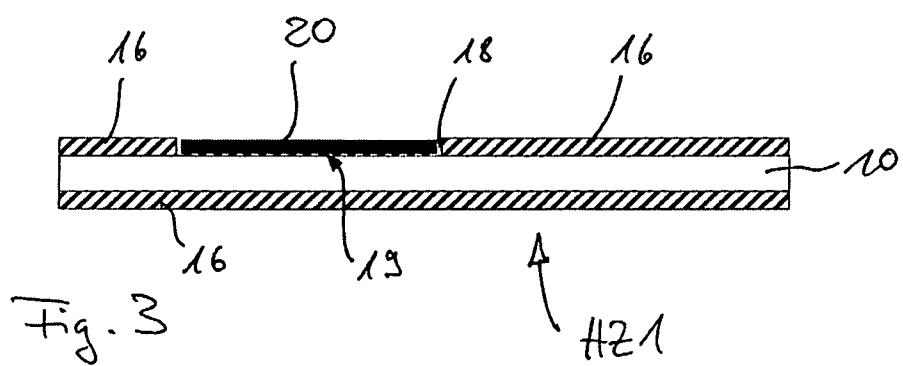

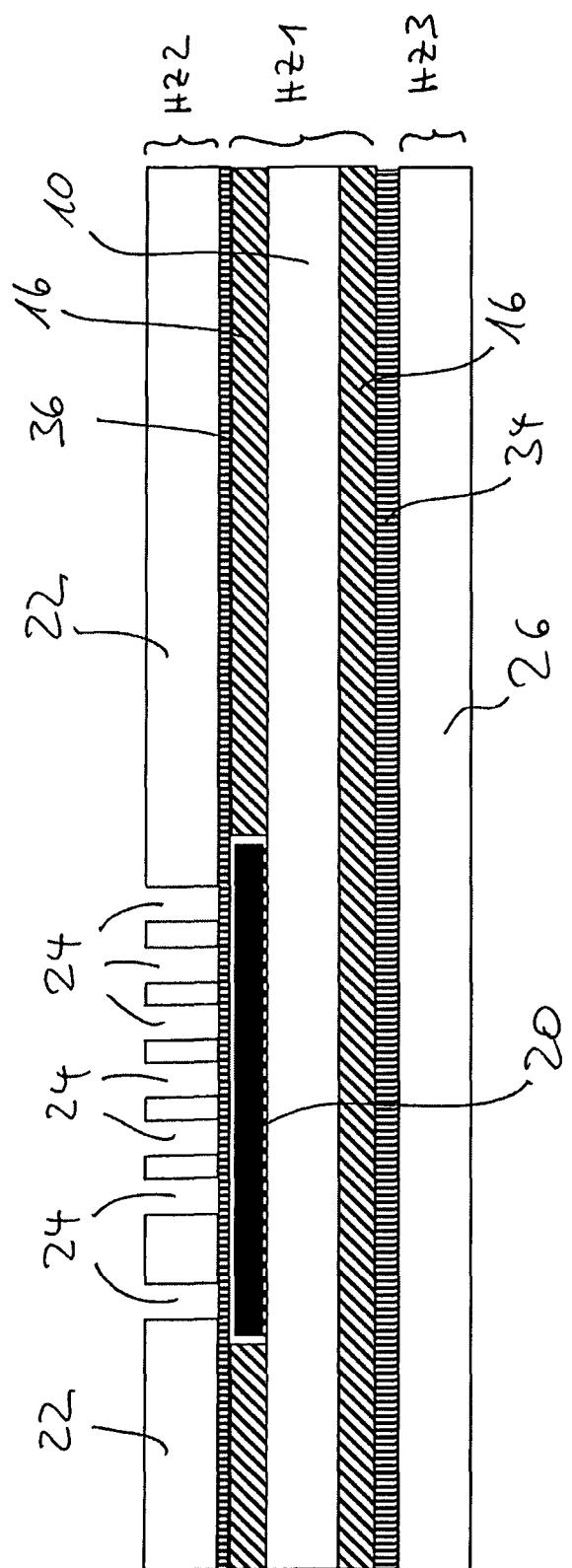

Figuren 1 bis 3 veranschaulichen das erfindungsgemäße Erzeugen eines ersten Halberzeugnisses bei der Herstellung eines elektronischen Bauteils.

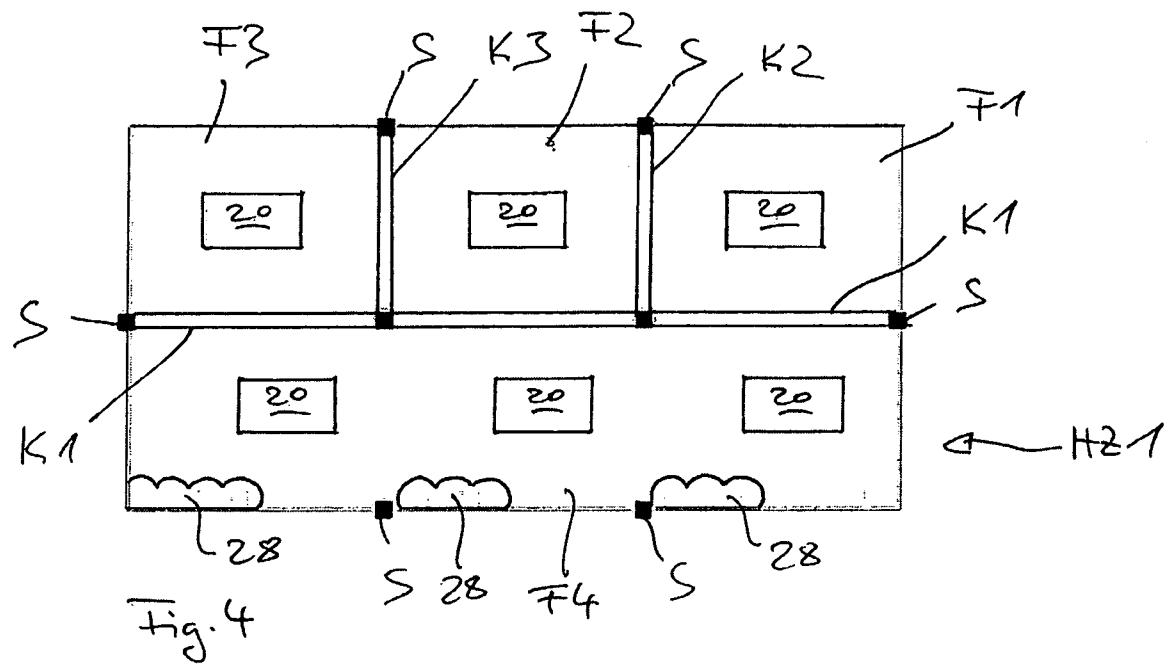

Figur 4 zeigt eine Draufsicht auf ein Layout einer Ausführungsform des ersten Halberzeugnisses.

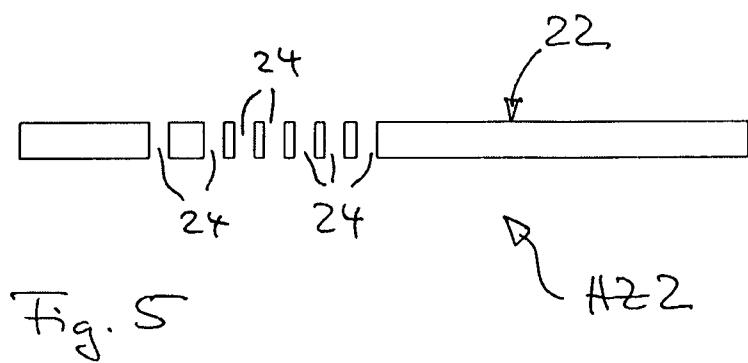

Figur 5 veranschaulicht das erfindungsgemäße Erzeugen eines zweiten Halberzeugnisses bei der Herstellung eines elektronischen Bauteils.

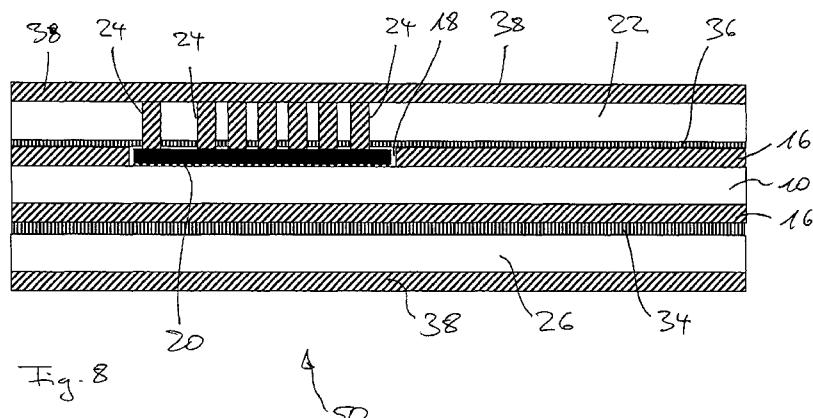

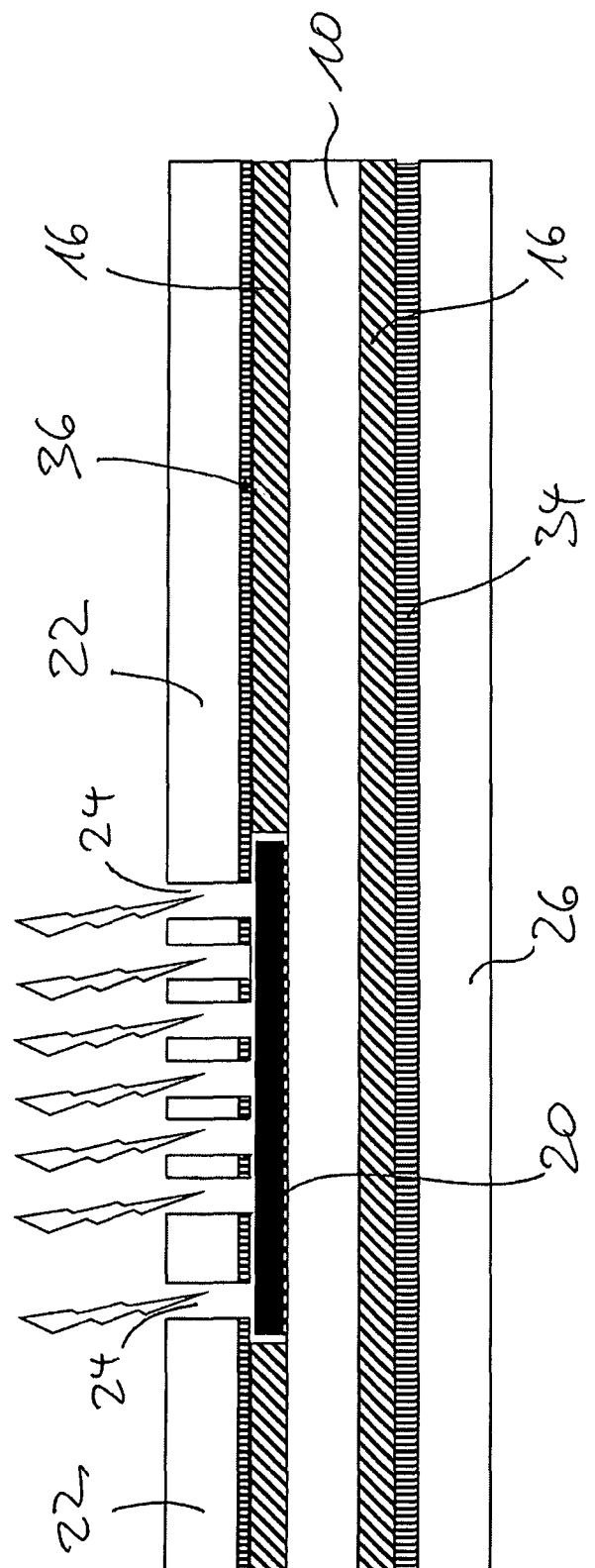

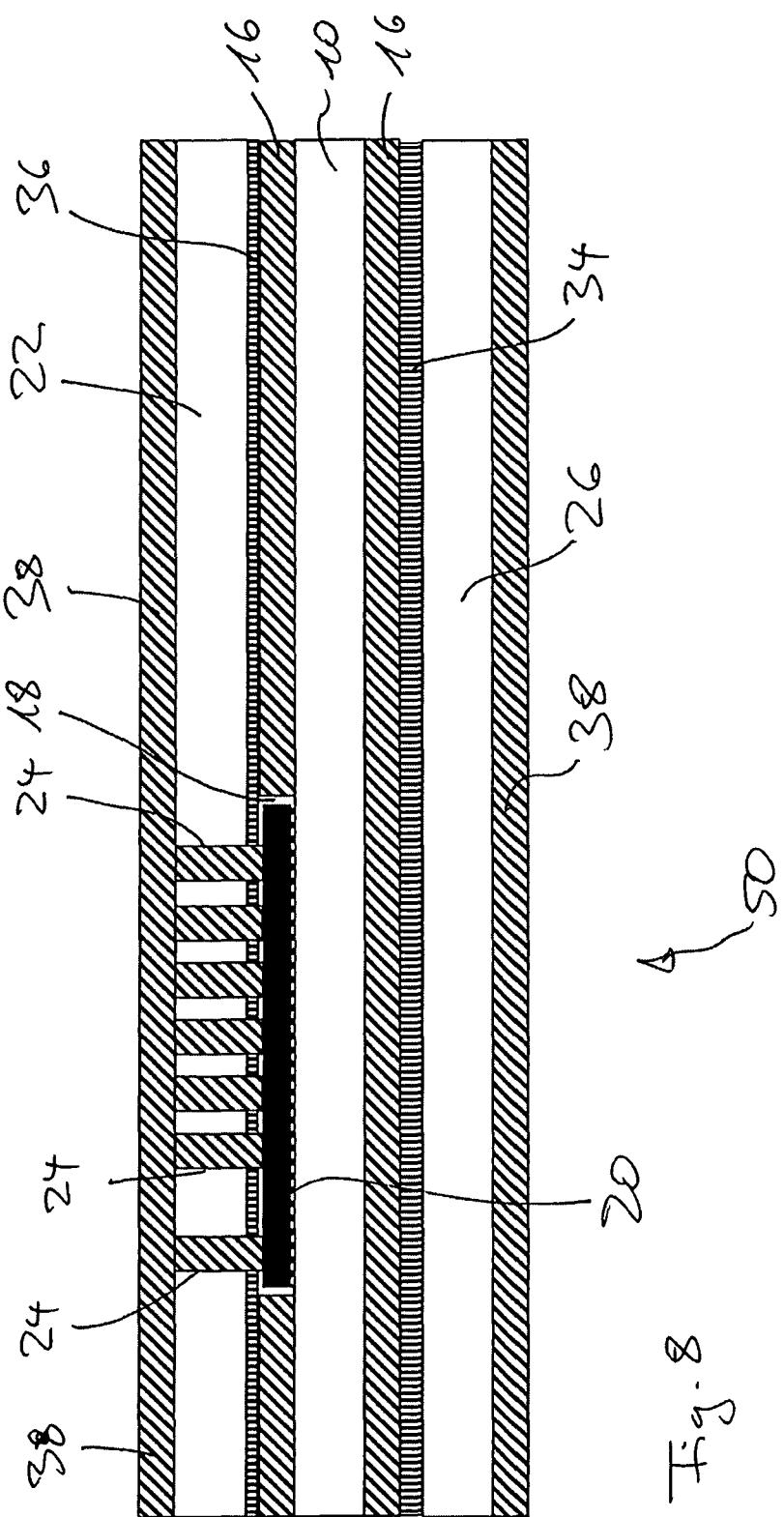

Figur 6 bis 8 veranschaulichen das Verlegen, Laminieren und weitere Verarbeiten der drei Halberzeugnisse zum Herstellen eines elektronischen Bauteils.

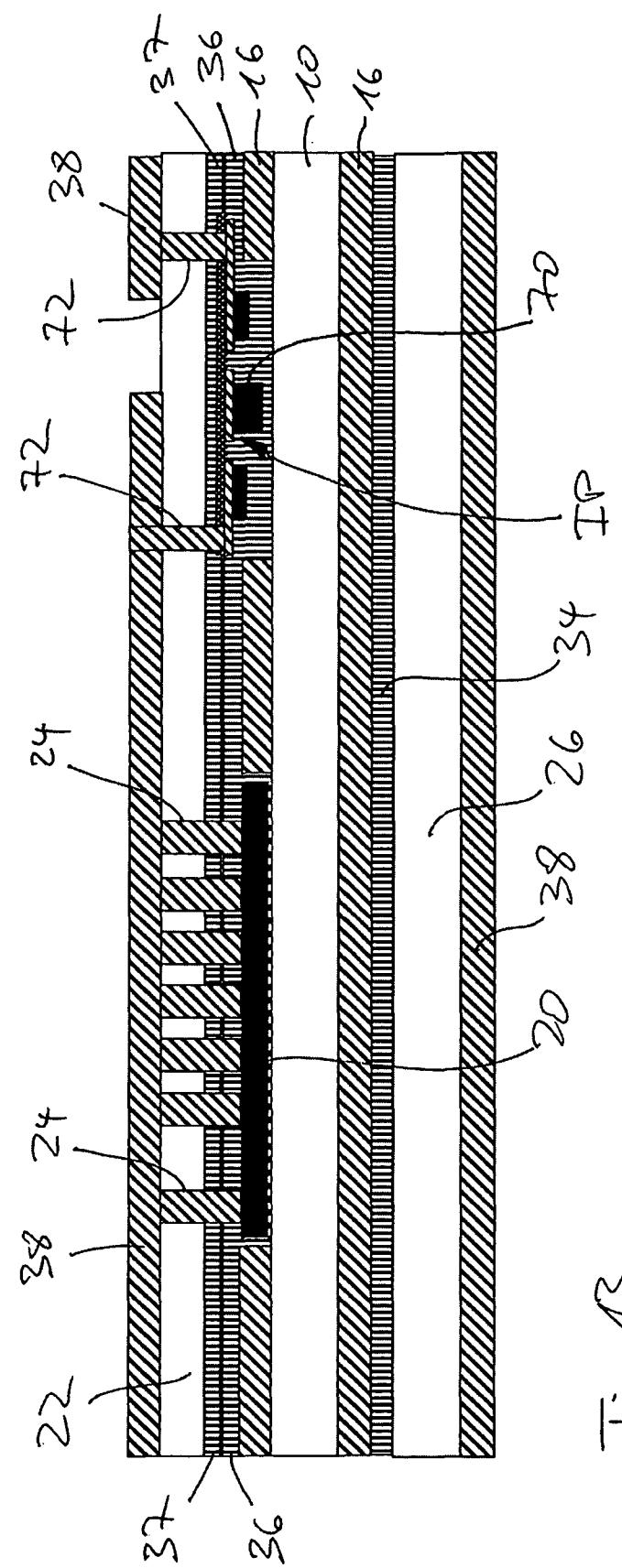

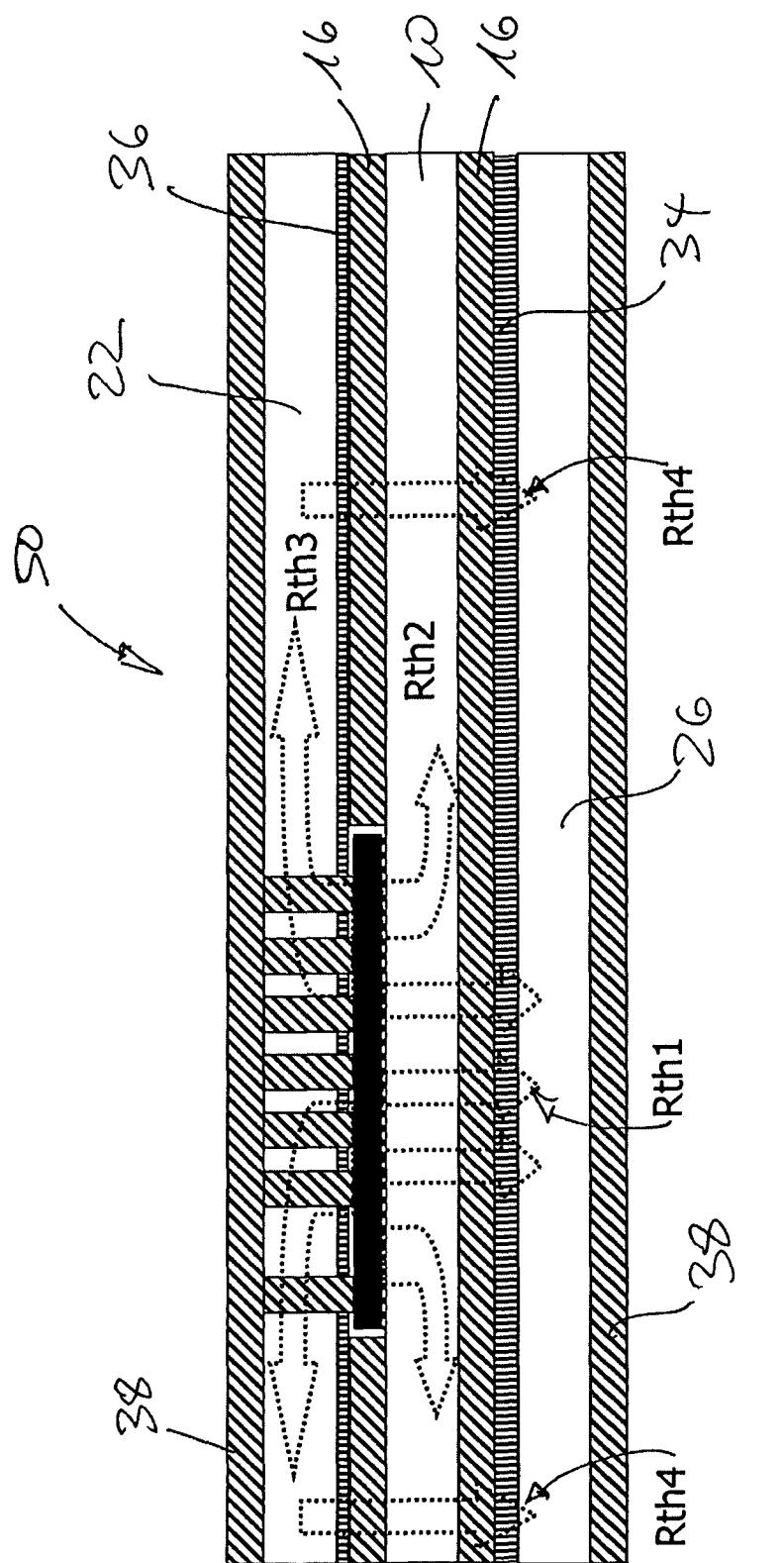

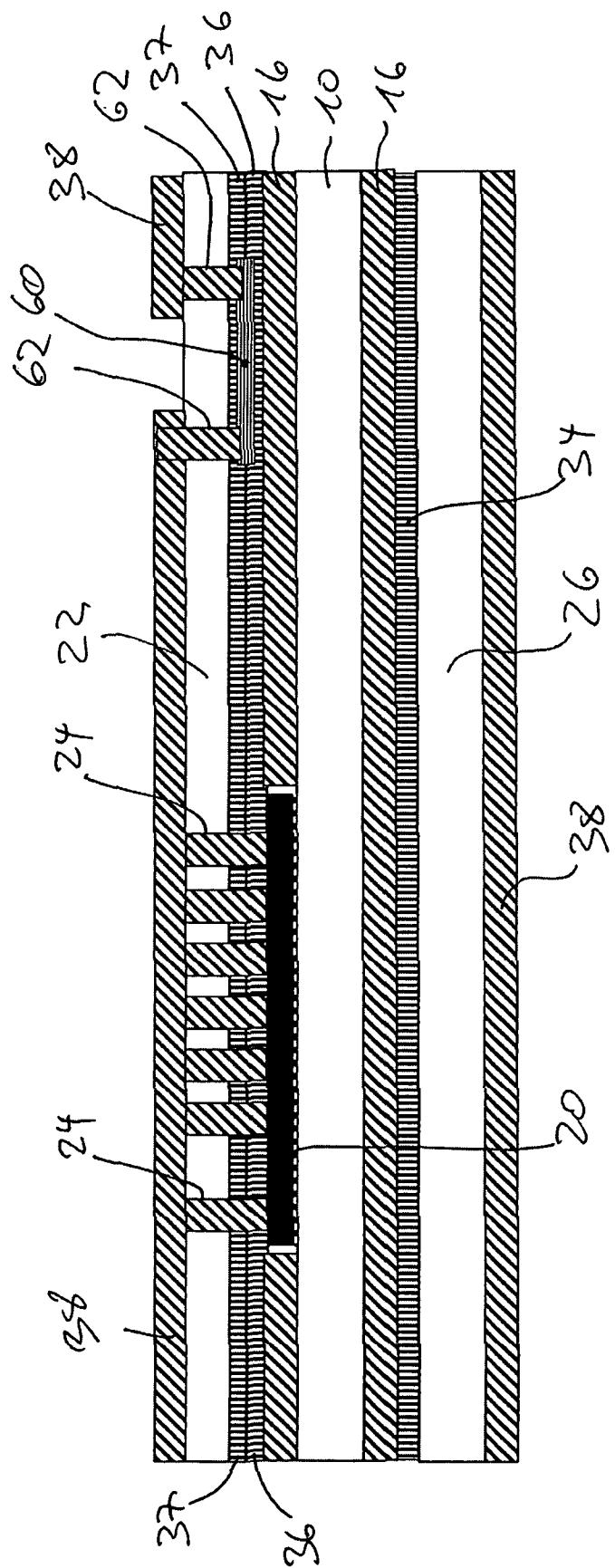

Figur 9 zeigt eine Ausführungsform eines fertigen erfindungsgemäßen elektronischen Bauteils.

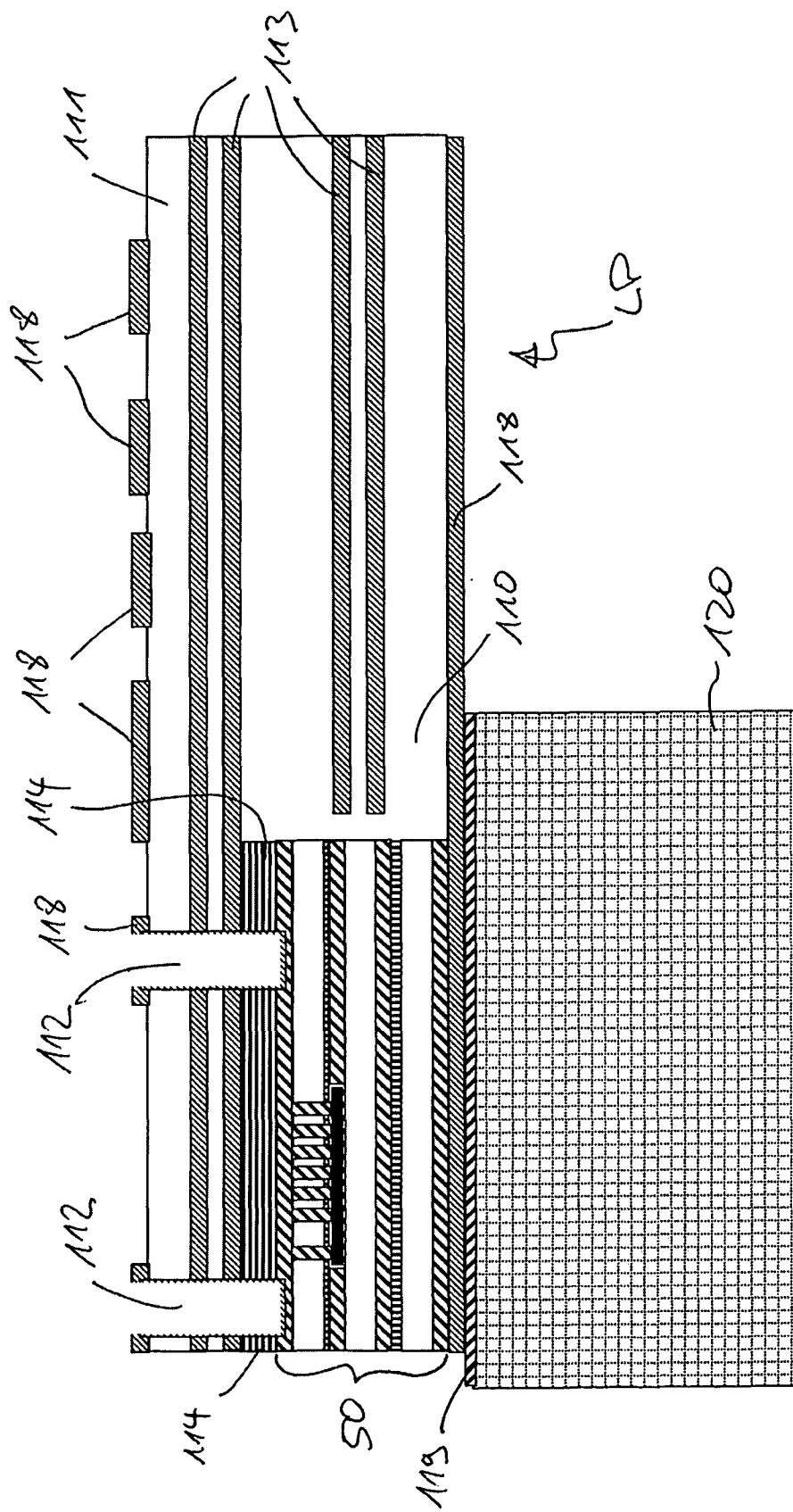

Figur 10 zeigt eine Leiterplatte mit integriertem Bauteil gemäß der Erfindung im Querschnitt.

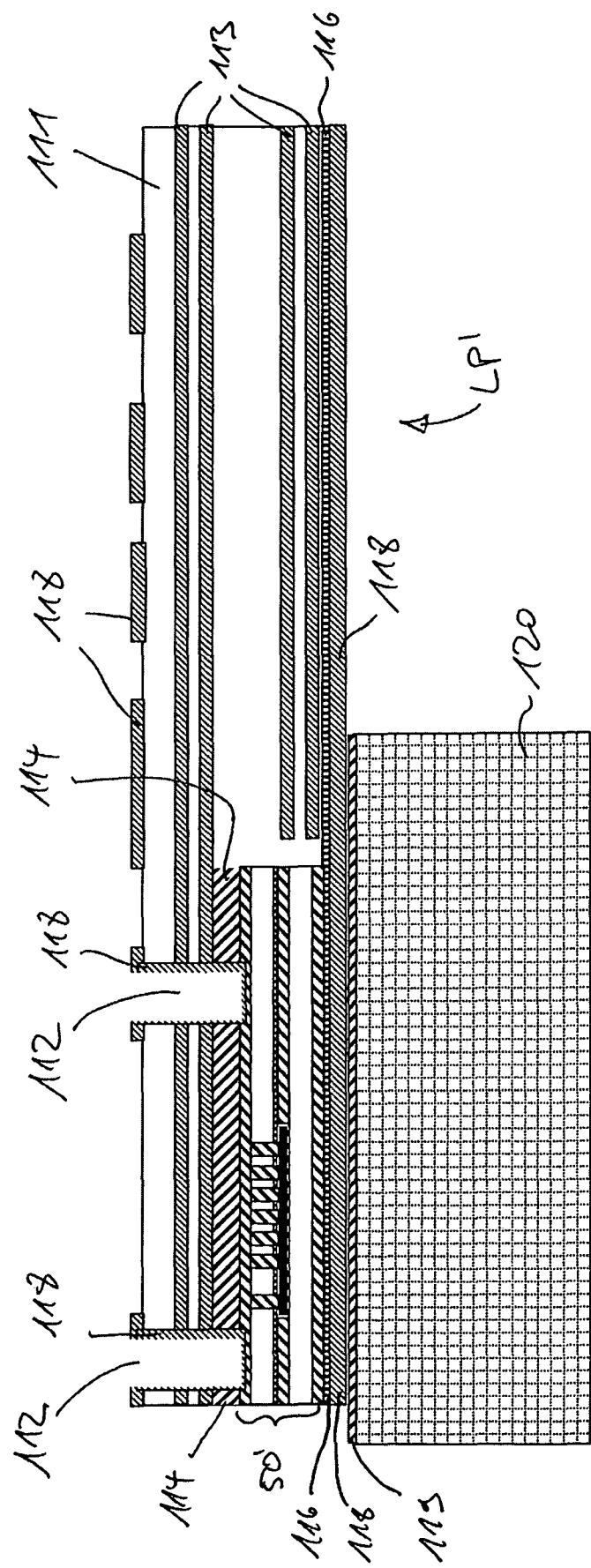

Figur 11 zeigt eine weitere Ausführungsform einer Leiterplatte mit integriertem Bauteil gemäß der Erfindung im Querschnitt.

Figur 12 zeigt ein Bauteil gemäß der Erfindung in seitlicher Schnittdarstellung mit integriertem Bauelement.

Figur 13 zeigt ein Bauteil gemäß der Erfindung in seitlicher Schnittdarstellung mit integriertem Interposer mit Bauelement.

Gemäß dem erfindungsgemäßen Verfahren wird ein Substrat 10 aus elektrisch leitendem Material mit einer Oberseite 12

und einer Unterseite 14 bereitgestellt (Figur 1). Bei dem Substrat kann es sich bspw. um ein Blech aus Kupfer handeln, grundsätzlich sind aber auch andere leitfähige Materialien möglich, die dem Fachmann bekannt sind. Kupfer verbindet drei günstige Eigenschaften, nämlich gute elektrische Leitfähigkeit, gute thermische Leitfähigkeit und es ist - verglichen mit anderen Materialien, die vergleichbare Leitfähigkeitseigenschaften aufweisen - zu vernünftigen Preisen erhältlich. Die Dimensionen des Substrats 10 können vom Fachmann im Einzelfall und unter Berücksichtigung der spezifischen Anforderungen gewählt werden. Eine typische Abmessung könnte bspw. 600 mm x 600 mm auf 0,2 bis 1 mm Dicke sein.

Optional kann ein kostengünstigeres Metall gewählt werden, das andere Ätzeigenschaften aufweist als das abgeschiedene Metall, mit der Folge, dass dann ein selektives Ätzen nur des Trägers möglich ist. So kann bspw. Aluminium als Trägermaterial verwendet werden, das zuvor verkupfert wurde. Damit sind Einsparungen bei den Kosten und beim Gewicht möglich.

In einem nächsten Schritt wird auf das Substrat 10 eine erste Schicht 16 aus elektrisch leitendem Material aufgebracht. Die erste Schicht 16 wird auf der Oberseite 12 und/oder der Unterseite 14 des Substrats 10 aufgebracht. Das Aufbringen erfolgt bspw. durch Abscheiden (Aufplattieren, galvanisches/elektrochemisches Abscheiden) oder durch andere geeignete technische Maßnahmen (wie bspw. Aufsputtern, Vakuumabscheidung usw.), die dem Fachmann bekannt sind.

Das Aufbringen der ersten Schicht 16 auf dem Substrat 10 erfolgt erfindungsgemäß derart, dass mindestens eine Ausnehmung 18 erzeugt wird. Die Abmessungen (Grundrissfläche

und Tiefe) der Ausnehmung 18 sind derart gewählt, dass die Ausnehmung 18 ein gewünschtes elektronisches Bauelement 20 (vgl. Figur 3) aufnehmen kann, das in einem nächsten Schritt in die Ausnehmung 18 auf dem Substrat 10 aufliegend eingesetzt wird. Bei dem elektronischen Bauelement 20 handelt es sich bspw. um einen Leistungs-Halbleiterchip oder ein anderes vergleichbares Bauelement. Die Tiefe d der Ausnehmung 18 wird z.B. so gewählt, dass die Höhe des einzusetzenden Bauelements 20 zuzüglich einer vorzusehenden Verbindungsschicht 19 zwischen Substrat 10 und einer Unterseite des Bauelements 20 etwas geringer ist, als die Tiefe d der Ausnehmung. Oder mit anderen Worten: die Plattierung (Schicht 22) ist etwas dicker als das einzusetzende Bauelement plus Verbindungsschicht. Bei der Verbindungsschicht 19 kann es sich bspw. um eine Lötschicht, eine organische Schicht oder einen geeigneten Kleber handeln. Wahlweise kann die Oberfläche des Substrats 10 im Bereich der Ausnehmung 18 mit einem geeigneten Edelmetall (wie Ag, Au, Sn o. dgl.) zur Ausbildung einer Kontaktierungsfläche für das Bauelement versehen sein. Durch geeignete Kombination von Beschichtungsmaterial für das elektronische Bauelement (bzw. den Chip) 20 und Beschichtung der Oberfläche des Substrats 10 können Verbindungen erzeugt werden, die nach dem Löten einen höheren Schmelzpunkt aufweisen als vor dem Löten. Dies wird bspw. durch die Kombination Gold (Au) auf dem Bauelement und Zinn (Sn) auf dem Substrat erreicht. Sn schmilzt bei 232 °C und es kommt zum Lötprozess. Dabei bilden sich intermetallische Phasen AuSn aus, deren Schmelzpunkt höher liegt als 232 °C. Dies verhindert ein späteres Wiederaufschmelzen bei einer Weiterverarbeitung.

Das elektronische Bauelement ist von seinen Oberflächen so beschaffen, dass die Unterseite an die vorgesehene Verbindungstechnik angepasst ausgeführt ist, bspw. mit einer lötfähigen Oberfläche, wenn gelötet werden soll. Die Ober-

seite des Bauelements ist dabei so ausgebildet, dass es für eine spätere galvanische Ankontaktierung geeignet ist, z.B. durch Verkupferung der Kontaktflächen.

Das beschriebene erfindungsgemäße Vorgehen des Ausbildens einer Ausnehmung zum Aufnehmen des Chips oder anderen Bauelements hat den Vorteil, dass das Bauelement in einem späteren Verfahrensschritt des Verpressens/Laminierens vor der Einwirkung mechanischen Drucks geschützt ist, indem die Höhe der Plattierung (und somit die Tiefe  $d$  der Ausnehmung) etwas größer gewählt wird, als die Dicke des Bauelements plus Verbindungsschicht. Dadurch wird gewährleistet, dass die Oberfläche des Bauelements zumindest so viel unterhalb der Oberfläche der Schicht 22 zu liegen kommt, dass beim Verpressen kein schädlicher Druck auf das Bauelement ausgeübt wird. Das Herstellen der Ausnehmung durch Aufbringen einer leitenden Schicht um die Ausnehmung herum hat den Vorteil, dass die Ausnehmung rechte Winkel und senkrechte Flächen aufweist (was durch Ätzen nicht und nur sehr aufwendig erzielt werden kann), so dass die Ausnehmung sehr passgenau auf die Größe des einzusetzenden Bauelements ausgebildet werden kann.

Zum Ausgleich von Bestückungstoleranzen ggf. vorgesehene Freisparungen um das Bauelement 20 können nach dessen Bestückung und Verlötung mit einem geeigneten Material vergossen werden, bspw. mit einer handelsüblichen Vergussmasse.

Nach dem bereits beschriebenen Einsetzen des Bauelements 20 in die dafür vorgesehene Ausnehmung 18 ist das erste Halberzeugnis HZ1 erzeugt.

In Ausgestaltung (vgl. Figur 4) kann das erste Halberzeugnis mit durch Kanäle K1, K2, K3 definierten Feldern F1, F2,

F3, F4 versehen werden. Dabei handelt es sich um Felder F1, F2, F3, F4, die nach Fertigstellung elektrisch voneinander isoliert sein sollen. Hierzu werden in die erste Schicht 16 und das Substrat 10 Kanäle K1, K2, K3 eingebracht, bspw. durch Ätzen, die zu diesem Zeitpunkt (noch) Stege S aufweisen, die sich quer durch die Kanäle K1, K2, K3 und diese mechanisch überbrückend erstrecken und eine Stabilitätsfunktion haben (Haltestege). Nach dem (nachfolgend noch zu beschreibenden) Laminierungsvorgang werden diese Haltestege mittels geeigneter Prozesse entfernt, bspw. durch Bohren, Fräsen, Stanzen u.dgl. Dadurch werden potential-getrennte Bereiche in dem elektronischen Bauteil erzeugt. Die in der Darstellung der Figur 4 im unteren Bereich des ersten Halberzeugnisses HZ1 erkennbaren halbkreis- bzw. teilkreisförmigen Freisparungen 28 dienen zur Potentialtrennung für Durchgangsbohrungen im fertigen Bauteil. Die wie voranstehend beschrieben erzeugten Felder F1, F2, F3, F4 dienen erfundungsgemäß zur Bereitstellung von Flächen zur Wärmespreizung für die elektronischen Bauelemente 20. Die Größe jedes Feldes F1, F2, F3, F4 wird derart gewählt, dass jedem der bestückten Bauelementen eine im wesentlichen gleich große Wärmespreizungsfläche zugeordnet ist.

Die beschriebenen Kanäle können vor dem eigentlichen Laminierprozess verfüllt werden, um die vor dem Verpressen in den Schichtaufbau einzubringende Harzmenge (vgl. Figur 6) zu reduzieren. Dies kann bspw. erforderlich sein, wenn einerseits sehr dünne Isolationsabstände zwischen den drei Halberzeugnissen HZ1, HZ2 und HZ3 gewünscht sind, andererseits aber lange und breite Kanäle zu verfüllen sind. Dies kann bspw. mittels Druckprozess oder Roller-Coater erfolgen. Das Harz muss nicht unbedingt speziell thermisch leitfähig sein.

Die voranstehend beschriebenen Felder dienen im Rahmen eines Aspektes der vorliegenden Erfindung dazu, den auf den Feldern anzuordnenden Bauelementen jeweils gleiche Bauteilflächen zur „symmetrischen“ Wärmespreizung zuzuordnen. „Symmetrisch“ in diesem Zusammenhang bedeutet, dass die von den Bauelementen im Betrieb entwickelte Wärme aufgrund der zugeordneten gleich großen Flächen gleichmäßig abgeleitet wird, wie dies auch nachfolgend unter Bezug auf die Darstellung der Figur 9 noch erläutert wird.

In Ausgestaltung der Erfindung kann das Substrat 10 nach dem in Figur 2 veranschaulichten Verfahrensschritt vereinzelt werden, wie dies in Figur 2a veranschaulicht ist.

Figur 2a zeigt links eine Draufsicht auf ein Substrat 10 mit einer Vielzahl (im dargestellten Ausführungsbeispiel: 91) von Bauteilkarten, die zu bestücken sind. Wie in der Darstellung der Figur 2a rechts zu erkennen ist, kann eine Vereinzelung zu Zwecken der Bestückung (mit elektronischen Bauelementen 20 wie beschrieben) als Streifen 10' oder als Einzelkarten 10'' erfolgen. Im Ausführungsbeispiel verfügt die vergrößert dargestellte Einzelkarte 10' über sechs Ausnehmungen 18. Nach dem Bestücken der Ausnehmungen mit den einzusetzenden Bauelementen werden die Streifen bzw. Einzelkarten zur Weiterverarbeitung wieder zusammengesetzt, was bspw. durch Einsetzen der Streifen bzw. Einzelkarten in ein geeignetes Tray (nicht dargestellt) erfolgt.

Zur Erzeugung eines zweiten erfindungsgemäßen Halberzeugnisses HZ2 wird nun ein erstes Plattenelement 22 aus elektrisch leitendem Material bereitgestellt (vgl. Figur 5). Bei dem ersten Plattenelement handelt es sich um ein plattenförmiges Element, bspw. um ein Blech aus geeignetem elektrisch leitendem Material. Bei diesem Material kann es sich - aus den bereits voranstehend dargelegten Erwägungen

- um Kupfer handeln. Die Abmessungen des ersten Plattenelements orientieren sich im Hinblick auf die nachstehend noch beschriebene Weiterverarbeitung an den Maßen des Substrats 10, also im beschriebenen Ausführungsbeispiel ca. 600 mm x 600 mm. Die Dicke kann wiederum ca. 0,2 mm betragen; sie kann vom Fachmann jedoch auch dicker oder dünner gewählt werden, je nach den Erfordernissen des Einzelfalls.

Das Plattenelement wird nach dem Bereitstellen an einer oder mehreren Stellen mit durchgehenden Löchern 24 für spätere Durchkontaktierungen versehen. Die Durchkontaktierungslöcher 24 können durch Bohren, Stanzen, Ätzen, Laserbearbeitung oder andere dem Fachmann geläufige Verfahren erstellt werden.

Danach ist das zweite Halberzeugnis HZ2 gemäß der Erfindung fertig.

Anschließend wird ein zweites Plattenelement 26 aus elektrisch leitendem Material als drittes Halberzeugnis HZ3 bereitgestellt (nicht separat dargestellt).

In dem ersten Halberzeugnis HZ1 und dem dritten Halberzeugnis HZ3 können dem Fachmann an und für sich bekannte Ausrichtungselemente vorgesehen sein, die der Ausrichtung der beiden Halberzeugnisse zueinander beim Bilden des Schichtaufbaus dienen.

Die Oberflächen aller oder einzelner der drei Halberzeugnisse HZ1, HZ2, HZ3 können vor dem nun folgenden Verlegen der Schichten zum Erzielen einer verbesserten Haftung der später verwendeten Laminierharzen durch geeignete Maßnahmen aufgerauht und/oder mit haftungsverbessernden Schichten (Haftvermittler) überzogen werden. Im Falle des ersten Halberzeugnisses kann ein geeigneter Haftvermittler gleich-

zeitig sowohl auf der Oberfläche des Halberzeugnisses als auch auf der Oberfläche des elektronischen Bauelements aufgetragen werden.

In Figur 6 ist die Ausrichtung der bislang erzeugten drei Halberzeugnisse HZ1, HZ2, HZ3 veranschaulicht.

Auf das dritte Halberzeugnis HZ3 wird das erste Halberzeugnis HZ1 aufgesetzt, wobei die Seite des ersten Halberzeugnisses HZ1 mit aufgesetztem Bauelement 20 nach oben und somit weg von dem dritten Halberzeugnis HZ3 weist. Zwischen die beiden Halberzeugnisse wird vor dem Aufsetzen als Zwischenlage eine erste Prepreg-Schicht 34 eingebracht. Diese erste Prepreg-Schicht 34 kann derart ausgestaltet sein, dass sie sich nicht in die gegenseitigen Eingriffstellen eventuell vorhandener Ausrichtungselemente erstreckt.

Auf die erste Schicht 16 auf der Oberseite 12 des ersten Halberzeugnisses HZ1 wird, nach Auflegen einer zweiten Prepreg-Schicht 36, das zweite Halberzeugnis HZ2 aufgesetzt, derart dass die durchgehenden Löcher 24 des zweiten Halberzeugnisses HZ2 in gewünschter Ausrichtung über dem elektronischen Bauelement 20 zu liegen kommen, um später als Durchkontaktierungen zu dem Bauelement 20 dienen zu können.

Optional kann das Prepreg im Bereich der späteren Durchkontaktierungen (durchgehende Löcher 24) vorgebohrt sein. Dadurch ist das Glasgewebe im Bereich der Vorbohrungen entfernt, wodurch das nachfolgende Laserbohren erleichtert wird, wenn das Prepreg auf die Durchkontaktierungslöcher 24 ausgerichtet aufgelegt wird, da der Laser nach dem Laminieren lediglich die Harzfüllung abtragen muss.

Bei der Auswahl der Prepreg-Schichten sollte auf eine gute thermische Leitfähigkeit des Materials geachtet werden. Bspw. kann hochthermisch leitfähiges Material verwendet werden. Es können Prepregs mit Harzen, die Füllstoffe mit hoher Leitfähigkeit enthalten, wie bspw. Al<sub>2</sub>O<sub>3</sub> oder TiN, verwendet werden. Die Dicke der Prepreg-Schicht wird abhängig von der erforderlichen thermischen Leitfähigkeit und anderen Parametern, wie bspw. die Durchschlagfestigkeit, gewählt.

Die so entstandene Sandwichstruktur (Schichtaufbaustruktur) der Figur 6 wird dann unter dem Fachmann bekannten Prozessparametern verpresst bzw. laminiert.

In einem folgenden Verfahrensschritt werden die durch das Laminieren mit Prepreg-Harz gefüllten Durchkontaktierungslöcher 24 freigelegt (einschließlich eventuell vorhandener Glasfasern). Dies kann durch dem Fachmann bekannte geeignete Maßnahmen, wie bspw. durch Lasern, wie dies in Figur 7 durch die stilisierten Laserblitze angedeutet ist, erfolgen.

Nach dem Entfernen des Dielektrikums aus den durchgehenden Löchern 24 wird auf der Dielektrikumswandung in den Löchern 24 aufgrund der Prepreg-Schicht 36 direkt oberhalb der Oberfläche des elektronischen Bauelements 20 in an sich bekannter Art und Weise eine dünne elektrisch leitende Schicht erzeugt. Diese Schicht kann bspw. durch chemisches Abscheiden von bspw. Kupfer erzeugt werden.

Auf der obersten Schicht 22 der entstandenen Laminatzwischenstruktur wird dann eine Deckschicht 38 aus elektrisch leitendem Material aufgebracht. Bei dem elektrisch leitenden Material kann es sich bspw. wiederum um Kupfer handeln, das durch Galvanisieren derart aufgebracht wird,

dass die Durchkontaktierungslöcher 24 vollständig gefüllt oder zumindest angefüllt werden, um eine gute Ankontaktierung des darunter liegenden elektronischen Bauelements 20 zu gewährleisten. Die Deckschicht kann auch - wie in dem Ausführungsbeispiel der Figur 8 dargestellt - auf der Unterseite (unterste Schicht 26) der entstandenen Laminat-Zwischenstruktur aufgebracht werden.

Figur 9 zeigt eine Querschnittsdarstellung eines erfindungsgemäßen elektronischen Bauteils 50, das aus einem Kupfer- bzw. Metallkern aus dem vormaligen Substrat 10 und den darauf aufgebrachten galvanischen Kupfer- bzw. Metallschichten 16, darauf (oben und unten) angeordneten thermisch leitfähigen Dielektrikumschichten 34, 36 und wiederum auf diesen (oben und unten) ausgebildeten weiteren Kupfer- bzw. Metallschichten 22, 26, 38 mit einem eingebetteten und über Metall-/Kupfer-Vias 24 ankontaktierten Bauelement bzw. Chip 20 besteht.

Dieser erfindungsgemäße Aufbau eines elektronischen Bauteils gewährleistet eine stabile und thermisch hoch leistungsfähige Anordnung, die im Vergleich zu ähnlich leistungsfähigen Keramiksubstraten deutlich kostengünstiger herstellbar und kleiner dimensionierbar ist und eine höhere Bruchfestigkeit aufweist. Durch die galvanische Ankontaktierung ist eine kleinere Chipdimensionierung ermöglicht, da keine Rücksicht auf Dickdrähte zum Anboden genommen werden muss.

In Figur 9 sind die sogenannten Entwärmungspfade des Bauteils 50 anhand punktierter Pfeile, verbunden mit unterschiedlichen thermischen Widerständen  $R_{th1}$  bis  $R_{th4}$ , ange deutet. Wie aus dieser Darstellung ersichtlich ist, verfügt das erfindungsgemäß aufgebaute Bauteil 50 über eine hohe Zahl derartiger Entwärmungspfade, die dafür sorgen, dass in

dem elektronischen Bauelement erzeugte Wärme gezielt abgeleitet wird. Dies wird u.a. durch die Verwendung von zwei Kupferebenen zur elektrischen und thermischen Verbindung erzielt. Dadurch wird die Verwendung von Bauelementen höherer Leistung bei gleicher Fläche (höhere Leistungsdichte) und/oder ein Flächengewinn bei der Gestaltung (Design) der Leiterbahnstrukturen ermöglicht, ohne die Gefahr einer Überhitzung. Der Effekt wird zur Wärmespreizung verwendet, d.h. der thermische Widerstand sinkt bei Erhöhung der Querschnittsfläche proportional.

Im Zusammenhang mit der vorliegenden Erfindung verwendete Materialien zeichnen sich vorteilhafterweise durch besonders gute Wärmeleitkoeffizienten aus. Übliche Prepreg-Harz-Materialien weisen eine thermische Leitfähigkeit von ca. 0,2 bis 0,3 W/mK auf. Möglich sind jedoch auch Materialien mit einer Wärmeleitfähigkeit von 0,8 bis 2,0 W/mK.

Vorteilhafterweise sind die Flächen der Felder F1, F2, F3 sowie ein Drittel der Fläche des Feldes F4 gleich groß (vgl. auch Figur 4), damit jedem Bauelement die gleiche Fläche zur Wärmespreizung zur Verfügung steht. Dabei ist berücksichtigt, dass Felder, auf denen mehrere Bauelemente/Chips zur Anordnung kommen, gegenüber Flächen mit nur einem Bauelement eine entsprechend um die Anzahl der Bauelemente vielfache Fläche aufweisen müssen, damit die erfindungsgemäße Wärme-Gleichableitung gewährleistet ist. Dadurch wird vermieden, dass sich ein Chip aufgrund unterschiedlicher Geometrien stärker aufheizt als die anderen Chips (sogenannter Hot-Spot-Effekt) und die Leistung des Gesamtsystems dann zum Abkühlen des einzelnen heißen Chips gedrosselt werden muss.

Das erfindungsgemäß hergestellte elektronische Bauteil 50 kann in eine Leiterplatte integriert werden, wie dies anhand Figur 10 veranschaulicht ist.

Dazu wird das elektronische Bauteil 50 in eine dafür vorgesehene Aussparung der Leiterplatte eingesetzt und mit dieser gemeinsam derart verpresst, dass nach dem Verpressen die Oberfläche der Leiterplatte bündig mit der Oberfläche des Bauteils abschließt. In der Darstellung der Figur 10 stellen weiße Schichten der Leiterplatte LP Dielektrikumschichten 110, 111 und schraffierte Schichten leitende Schichten 113 dar. Zwei eingezeichnete Sacklöcher 112 dienen zur Ankontaktierung zwischen Bauteil 50 und Leiterplatte LP. Direkt oberhalb des Bauteils 50 befindet sich eine (horizontal schraffierte) Schicht 114 mit geringer thermischer Leitfähigkeit. Zwischen dem Kühlkörper 120 und einer unteren (Kupfer-)Außenlage 118 der Leiterplatte LP kann eine TIM-Schicht 119 zur Ausbildung eines thermisch lückenlosen Spalts vorgesehen sein (TIM: thermal interface material).

Beim Einbau in eine Leiterplatte LP kann auch alternativ auf die Schichtenfolge 34, 26, 38 des dritten Halberzeugnisses HZ3 verzichtet werden. Eine derartige Variante ist beispielhaft in Figur 11 dargestellt. Hier ist ein elektronisches Bauteil 50' ohne das dritte Halberzeugnis HZ3 direkt in eine Leiterplatte LP' integriert. Die Leiterplatte LP' weist einen grundsätzlich gleichen Aufbau wie in der Figur 10 auf, wobei zusätzlich an der Unterseite der Leiterplatte ein thermisch leitfähiges Prepreg 116, das sich über die Fläche der Leiterplatte und des integrierten Bauteils 50' erstreckt. Als gemeinsame Außenlage der Leiterplatte und des Bauteils 50' wird anschließend noch eine Kupferschicht 118 aufgebracht (die beim galvanischen Aufbringen einer Deckschicht zur Ausbildung der Durchkontakte-

tierung der Sacklöcher 112 auf der Oberseite der Leiterplatte mit entsteht). Bei der Integration des Bauteils 50' mit der Leiterplatte LP' erfolgt ein gemeinsames Verpressen mit diesem thermisch leitfähigen Außenlagendielektrikum. Unterhalb des Bauteils 50' schließt sich an der Unterseite der Außenlage 116 wiederum die Kupferlage 118, eine TIM-Schicht 119 und ein Kühlkörper 120 an.

Alternativ kann die Leiterplatte auch so ausgestaltet sein, dass sie sich unterhalb des Bauteils erstreckt und die Kühlflächenfunktion erfüllt (nicht dargestellt), die in den beiden in den Figuren 11 und 12 dargestellten Ausführungsformen von dem Kühlkörper 120 übernommen wird.

Der Bereich der Leiterplatte oberhalb des Bauteils kann - wie bereits angedeutet - so ausgestaltet sein, dass ein schlechter Wärmefluss nach oben resultiert. Dadurch wird die Aufheizung eventuell temperaturempfindlicher Bauelemente auf der Leiterplatte vermieden bzw. zumindest reduziert. Zu diesem Zwecke kann bspw. alternativ oder zusätzlich zu der bereits in den Figuren 11 und 12 dargestellten Schicht 114 mit geringer thermischer Leitfähigkeit innerhalb dieser Schicht 114 mindestens ein Hohlraum (nicht dargestellt) oberhalb des Bauteils und direkt an dieses anschließend vorgesehen sein. Die elektrische als auch die mechanische Anbindung des Bauteils an die Leiterplatte erfolgt dann über die seitlichen Ränder und verbliebene Bereiche der Oberfläche.

In Ausgestaltung der Erfindung können zwischen dem ersten Halberzeugnis HZ1 und dem zweiten Halberzeugnis HZ2 zwei Prepreg-Schichten 36, 37 eingebracht werden, zwischen denen sich wiederum ein Bauelement befindet. Bei diesem Bauelement kann es sich bspw. um ein Bauelement 60 zur Strommessung bzw. Stromsensierung (sogenannter Shunt) handeln (in

der dargestellten Ausführungsform ein Folien-Bauelement; vgl. Figur 12). Dessen Ankontaktierung erfolgt - wie bereits in anderem Zusammenhang voranstehend beschrieben - bspw. über ausplattierte Laserlöcher 62.

In weiterer Ausgestaltung kann - ähnlich wie im Zusammenhang mit Figur 12 beschrieben - zwischen die beiden Prepregschichten 36, 37 zwischen dem ersten Halberzeugnis HZ1 und dem zweiten Halberzeugnis HZ2 mindestens ein passives, diskretes Bauelement 70, bspw. mittels eines sogenannten Interposers IP, eingebracht werden, wie dies in Figur 13 veranschaulicht ist. Abhängig von dessen Bauhöhe kann ggf. ein Hohlraum bzw. eine Kavität 17 in dem ersten Halberzeugnis HZ1 zur Aufnahme des Interposers IP vorgesehen sein. Die Ankontaktierung erfolgt wiederum über ausplattierte Laserlöcher 72 o.dgl.

Aspekte der Erfindung sind in der nachfolgenden Liste nummerierter Aspekte zusammengefasst:

1. Elektronisches Bauteil (50) mit einer elektrisch leitenden Kernschicht (10) mit einer beidseitig aufgebrachten ersten Schicht (16) aus elektrisch leitendem Material und mit mindestens einem in einer Ausnehmung (18) der ersten Schicht (16) angeordneten elektronischen Bauelement (20), wobei die erste Schicht (16) jeweils mit einer elektrisch isolierenden, thermisch leitfähigen Schicht (34, 36) bedeckt ist und auf der thermisch leitfähigen Schicht (34, 36) jeweils eine weitere Schicht (22, 26) aus elektrisch leitendem Material vorgesehen ist, die jeweils mit einer Deckschicht (38) aus elektrisch leitendem Material überzogen sind, und mit des weiteren Durchkontakteierungen (24) aus dem Material der Deckschicht (38), die sich durch die das elektronische Bauelement (20) bedeckende elektrisch isolierende, thermisch leitfähige Schicht (36) und die wei-

tere Schicht (22) aus elektrisch und thermisch leitendem Material zum Ankontaktieren des elektronischen Bauelements (20) erstrecken.

2. Elektronisches Bauteil (50) nach Aspekt 1, bei dem die Kernschicht (10) aus Kupfer oder aus verkupfertem Aluminium besteht.

3. Elektronisches Bauteil (50) nach Aspekt 1 oder 2, bei dem die erste Schicht (16) galvanisch abgeschiedenes Kupfer ist.

4. Elektronisches Bauteil (50) nach einem der Aspekte 1 bis 3, bei dem eine Tiefe (d) der Ausnehmung (18) etwas größer ist als eine Höhe des elektronischen Bauelements (20) zuzüglich einer Verbindungsschicht (19).

5. Elektronisches Bauteil (50) nach einem der Aspekte 1 bis 4, bei dem bei mehr als einem elektronischen Bauelement (20) jedem Bauelement (20) derart eine Fläche zur Wärmespreizung zugeordnet ist, dass die Wärmespreizungsfläche für jedes montierte Bauelement (20) im wesentlichen gleich ist.

6. Elektronisches Bauteil (50') mit einer elektrisch leitenden Kernschicht (10) mit einer beidseitig aufgebrachten ersten Schicht (16) aus elektrisch leitendem Material und mit mindestens einem in einer Ausnehmung (18) der ersten Schicht (16) angeordneten elektronischen Bauelement (20), wobei die erste Schicht (16) oberhalb des elektronischen Bauelements (20) mit einer elektrisch isolierenden, thermisch leitfähigen Schicht (36) bedeckt ist und auf der thermisch leitfähigen Schicht (36) eine weitere Schicht (22) aus elektrisch leitendem Material vorgesehen ist, die wiederum mit einer Deckschicht (38) aus elektrisch leiten-

dem Material überzogen ist, und mit des weiteren Durchkontakteierungen (24) aus dem Material der Deckschicht (38), die sich durch die das elektronische Bauelement (20) bedeckende elektrisch isolierende, thermisch leitfähige Schicht (36) und die weitere Schicht (22) aus elektrisch und thermisch leitendem Material zum Ankontaktieren des elektronischen Bauelements (20) erstrecken.

Das elektronische Bauteil gemäß Aspekt 6 ist als Zwischenprodukt vorgesehen, bspw. zur Integration in eine Leiterplatte, wie nachstehend und in der Beschreibung unter Bezugnahme auf das Ausführungsbeispiel der Figur 11 beschrieben.

7. Elektronisches Bauteil (50') nach Aspekt 6, bei dem die Kernschicht (10) aus Kupfer oder aus verkupfertem Aluminium besteht.

8. Elektronisches Bauteil (50') nach Aspekt 6 oder 7, bei dem die erste Schicht (16) galvanisch abgeschiedenes Kupfer ist.

9. Elektronisches Bauteil (50') nach einem der Aspekte 6 bis 8, bei dem eine Tiefe (d) der Ausnehmung (18) etwas größer ist als eine Höhe des elektronischen Bauelements (20) zuzüglich einer Verbindungsschicht (19).

10. Elektronisches Bauteil (50') nach einem der Aspekte 6 bis 9, bei dem bei mehr als einem elektronischen Bauelement (20) jedem Bauelement (20) derart eine Fläche zur Wärmespreizung zugeordnet ist, dass die Wärmespreizungsfläche für jedes montierte Bauelement (20) im wesentlichen gleich ist.

11. Verfahren zum Herstellen eines elektronischen Bauteils (50) mit den folgenden Schritten:

- Erzeugen eines ersten Halberzeugnisses (HZ1) durch

- Bereitstellen eines Substrats (10) aus elektrisch leitendem Material mit einer Oberseite (12) und einer Unterseite (14),

- Aufbringen einer ersten Schicht (16) aus leitendem Material auf die Oberseite (12) und/oder die Unterseite (14) des Substrats (10), wobei in der ersten Schicht (16) mindestens eine Ausnehmung (18) zur Aufnahme eines elektronischen Bauelements vorgesehen wird,

- Einsetzen mindestens eines Bauelements (20) in die mindestens eine Ausnehmung (18),

- Erzeugen eines zweiten Halberzeugnisses (HZ2) durch

- Bereitstellen eines ersten Plattenelements (22) aus elektrisch leitendem Material,

- Erzeugen von durchgehenden Löchern (24) für spätere Durchkontaktierungen in dem ersten Plattenelement (22),

- Erzeugen eines dritten Halberzeugnisses (HZ3) durch

- Bereitstellen eines zweiten Plattenelements (26) aus elektrisch leitendem Material,

- Verlegen der drei Halberzeugnisse (HZ1, HZ2, HZ3) in einer Schichtstruktur durch Auflegen des ersten Halberzeugnisses (HZ1) auf das dritte Halberzeugnis (HZ3) und Auflegen des zweiten Halberzeugnisses (HZ2) auf das erste Halberzeugnis (HZ1) mit jeweils dazwischen vorgesehener Prepreg-Schicht (34, 36),

- Laminieren der Struktur,

- Freilegen der nach dem Laminieren mit Harz gefüllten Löcher (24) des ersten Plattenelements (22),

- zumindest teilweises Füllen der Löcher (24) mit leitfähigem Material (38) zur Durchkontaktierung.

12. Verfahren nach Aspekt 11, bei dem das Substrat (10) aus Kupfer oder verkupfertem Aluminium besteht.

13. Verfahren nach Aspekt 11 oder 12, bei dem das Aufbringen der ersten Schicht (16) durch galvanisches Abscheiden erfolgt.

14. Verfahren nach einem der Aspekte 11 bis 13, bei dem die Ausnehmung (18) derart durch selektives Aufbringen der ersten Schicht (16) gebildet wird, dass eine Tiefe (d) der Ausnehmung (18) etwas größer ist als die Höhe des einzusetzenden elektronischen Bauelements (20) zuzüglich einer Verbindungsschicht (19).

15. Verfahren nach einem der Aspekte 11 bis 14, bei dem nach dem Bestücken mit dem mindestens einen elektronischen Bauelement (20) Freisparungen in der Ausnehmung (18) um das Bauelement (20) vor dem Verpressen aufgefüllt werden.

16. Verfahren nach einem der Aspekte 11 bis 15, bei dem in die erste Schicht (16) und das Substrat (10) Kanäle (K1, K2, K3) eingebracht werden, wobei die Kanäle Haltestege (S) aufweisen, die nach dem Schritt des Laminierens entfernt werden.

17. Verfahren zum Herstellen eines elektronischen Bauteils (50') mit den folgenden Schritten:

- Erzeugen eines ersten Halberzeugnisses (HZ1) durch

- Bereitstellen eines Substrats (10) aus elektrisch leitendem Material mit einer Oberseite (12) und einer Unterseite (14),

- Aufbringen/Abscheiden einer ersten Schicht (16) aus leitendem Material auf die Oberseite (12) und/oder die Unterseite (14) des Substrats (10), wobei in der ersten Schicht (16) mindestens eine

Ausnehmung (18) zur Aufnahme eines elektronischen Bauelements vorgesehen wird,

- Einsetzen eines Bauelements (20) in die mindestens eine Ausnehmung (18),

- Erzeugen eines zweiten Halberzeugnisses (HZ2) durch

- Bereitstellen eines ersten Plattenelements (22) aus elektrisch leitendem Material,

- Erzeugen von durchgehenden Löchern (24) für spätere Durchkontaktierungen in dem ersten Plattenelement (22),

- Verlegen der zwei Halberzeugnisse (HZ1, HZ2) in einer Schichtstruktur durch Auflegen des zweiten Halberzeugnisses (HZ2) auf das erste Halberzeugnis (HZ1) mit einer dazwischen vorgesehenen Prepreg-Schicht (36),

- Laminieren der Struktur,

- Freilegen der nach dem Laminieren mit Harz gefüllten Löcher (24) des ersten Plattenelements (22),

- zumindest teilweises Füllen der Löcher (24) mit leitfähigem Material (38) zur Durchkontaktierung.

18. Verfahren nach Aspekt 17, bei dem das Substrat (10) aus Kupfer oder verkupfertem Aluminium besteht.

19. Verfahren nach Aspekt 17 oder 18, bei dem das Aufbringen der ersten Schicht (16) durch galvanisches Abscheiden erfolgt.

20. Verfahren nach einem der Aspekte 17 bis 19, bei dem die Ausnehmung (18) derart durch selektives Aufbringen der ersten Schicht (16) gebildet wird, dass eine Tiefe (d) der Ausnehmung (18) etwas größer ist als die Höhe des einzusetzenden elektronischen Bauelements (20) zuzüglich einer Verbindungsschicht (19).

21. Verfahren nach einem der Aspekte 17 bis 20, bei dem nach dem Bestücken mit dem mindestens einen elektronischen Bauelement (20) Freisparungen in der Ausnehmung (18) um das Bauelement (20) vor dem Verpressen aufgefüllt werden.

22. Verfahren nach einem der Aspekte 17 bis 21, bei dem in die erste Schicht (16) und das Substrat (10) Kanäle (K1, K2, K3) eingebracht werden, wobei die Kanäle Haltestege (S) aufweisen, die nach dem Schritt des Laminierens entfernt werden.

23. Leiterplatte (LP) mit einem elektronischen Bauteil (50) nach einem der Aspekte 1 bis 5.

24. Leiterplatte (LP) nach Aspekt 23, bei der eine Oberfläche der Leiterplatte (LP) bündig mit dem elektronischen Bauteil (50) abschließt.

25. Leiterplatte (LP) nach Aspekt 24, bei der sich ein Kühlkörper (120) an den bündigen Abschluss von Leiterplatte (LP) und elektronischem Bauteil (50) anschließt.

26. Leiterplatte (LP) nach einem der Aspekte 23 bis 25, bei der zwischen dem elektronischen Bauteil (50) und darüber liegenden Leiterbahnen (113) der Leiterplatte (LP) eine Schicht (114) mit geringer thermischer Leitfähigkeit vorgesehen ist.

27. Leiterplatte (LP') mit einem elektronischen Bauteil (50') nach einem der Aspekte 6 bis 10.

28. Leiterplatte (LP') nach Aspekt 27, bei der ein isolierender Teil (110) der Leiterplatte (LP') bündig mit dem elektronischen Bauteil (50') abschließt.

29. Leiterplatte (LP') nach Aspekt 28, bei der sich ein Kühlkörper (120) an den bündigen Abschluss von Leiterplatte (LP') und elektronischem Bauteil (50') anschließt.

30. Leiterplatte nach einem der Aspekte 27 bis 29, bei der zwischen dem elektronischen Bauteil (50') und darüber liegenden Leiterbahnen (113) der Leiterplatte (LP') eine Schicht (114) mit geringer thermischer Leitfähigkeit vorgesehen ist.

31. Verfahren nach einem der Aspekte 11 bis 22, bei dem in dem Schritt des Verlegens zwischen dem ersten Halberzeugnis (HZ1) und dem zweiten Halberzeugnis (HZ2) zwei Prepreg-Schichten (36, 37) eingebracht werden, wobei zwischen den beiden Prepreg-Schichten (36, 37) ein weiteres Bauelement (60) und/oder ein Interposer (IP) angeordnet wird, das bzw. der nach dem Schritt des Verpressens mittels ausplattierten Löchern (62, 72) ankontaktiert wird.

32. Verfahren nach Aspekt 31, bei dem die Löcher (62, 72) zum Ankontaktieren des weiteren Bauelements (60) und/oder des Interposers (IP) mittels Laserbohren und anschließendem Ausplattieren erzeugt werden.

33. Verfahren nach Aspekt 31 oder 32, bei dem bei dem Schritt des Erzeugens des zweiten Halberzeugnisses (HZ2) durchgehende Löcher zum Ankontaktieren des weiteren Bauelements (60) und/oder des Interposers (IP) vorgesehen werden.

34. Verfahren nach einem der Aspekte 31 bis 33, bei dem zur Aufnahme des weiteren Bauelements (60) und/oder des Interposers (IP) eine Kavität (17) vorgesehen wird.

35. Elektronisches Bauteil (50, 50') nach einem der Aspekte 1 bis 10, das zwischen zwei elektrisch isolierenden

Schichten (36, 37) ein weiteres Bauelement (60) und/oder einen Interposer (IP) aufweist.

36. Verfahren zum Integrieren eines elektronischen Bauteils (50, 50') in eine Leiterplatte, mit den Schritten des

- Bereitstellens eines elektronischen Bauteils (50, 50') nach einem der Aspekte 1 bis 10 oder nach Aspekt 35,

- Bereitstellens einer Leiterplatte mit einer zur Aufnahme des elektronischen Bauteils (50, 50') vorgesehenen Aussparung,

- Einbringens einer Schicht (114) geringer thermischer Leitfähigkeit in die Aussparung,

- Einsetzens des elektronischen Bauteils (50, 50') in die Aussparung der Leiterplatte auf die Schicht (114) geringer thermischer Leitfähigkeit,

- Verpressens der derart entstandenen Schichtstruktur,

- Aufbringen einer gemeinsame Außenlage bildenden elektrisch leitenden Schicht (118), die auch zur Ankontaktierung zwischen dem elektronischen Bauteil (50, 50') und der Leiterplatte (LP, LP') dient.

37. Verfahren nach Aspekt 36, bei dem auf die gemeinsame Außenlage bildende Schicht (118) im Bereich des elektronischen Bauteils (50, 50') ein Kühlkörper (120) aufgebracht wird.

38. Verfahren nach Aspekt 37, bei dem zwischen der elektrisch leitenden Schicht (118) und dem Kühlkörper (120) eine TIM-Schicht (119) zur Ausbildung eines thermisch lückenlosen Spalts eingebracht ist.

39. Verfahren nach einem der Aspekte 36 bis 38, bei dem zwischen der Leiterplatte mit eingesetztem elektronischen Bauteil einerseits und der gemeinsamen Außenlage (118) an-

dererseits eine thermisch leitfähiges Dielektrikum (116) eingebracht wird.

**Patentansprüche**

1. Elektronisches Bauteil (50) mit einer elektrisch leitenden Kernschicht (10) mit einer beidseitig aufgebrachten ersten Schicht (16) aus elektrisch leitendem Material und mit mindestens einem in einer Ausnehmung (18) der ersten Schicht (16) angeordneten elektronischen Bauelement (20), wobei die erste Schicht (16) jeweils mit einer elektrisch isolierenden, thermisch leitfähigen Schicht (34, 36) bedeckt ist und auf der thermisch leitfähigen Schicht (34, 36) jeweils eine weitere Schicht (22, 26) aus elektrisch leitendem Material vorgesehen ist, die jeweils mit einer Deckschicht (38) aus elektrisch leitendem Material überzogen sind, und mit des weiteren Durchkontaktierungen (24) aus dem Material der Deckschicht (38), die sich durch die das elektronische Bauelement (20) bedeckende elektrisch isolierende, thermisch leitfähige Schicht (36) und die weitere Schicht (22) aus elektrisch und thermisch leitendem Material zum Ankontaktieren des elektronischen Bauelements (20) erstrecken.

2. Elektronisches Bauteil (50') mit einer elektrisch leitenden Kernschicht (10) mit einer beidseitig aufgebrachten ersten Schicht (16) aus elektrisch leitendem Material und mit mindestens einem in einer Ausnehmung (18) der ersten Schicht (16) angeordneten elektronischen Bauelement (20), wobei die erste Schicht (16) oberhalb des elektronischen Bauelements (20) mit einer elektrisch isolierenden, thermisch leitfähigen Schicht (36) bedeckt ist und auf der thermisch leitfähigen Schicht (36) eine weitere Schicht

(22) aus elektrisch leitendem Material vorgesehen ist, die wiederum mit einer Deckschicht (38) aus elektrisch leitendem Material überzogen ist, und mit des weiteren Durchkontaktierungen (24) aus dem Material der Deckschicht (38), die sich durch die das elektronische Bauelement (20) bedeckende elektrisch isolierende, thermisch leitfähige Schicht (36) und die weitere Schicht (22) aus elektrisch und thermisch leitendem Material zum Ankontaktieren des elektronischen Bauelements (20) erstrecken.

3. Elektronisches Bauteil (50; 50') nach Anspruch 1 oder 2, bei dem eine Tiefe (d) der Ausnehmung (18) etwas größer ist als eine Höhe des elektronischen Bauelements (20) zuzüglich einer Verbindungsschicht (19).

4. Elektronisches Bauteil (50; 50') nach einem der Ansprüche 1 bis 3, bei dem bei mehr als einem elektronischen Bauelement (20) jedem Bauelement (20) derart eine Fläche zur Wärmespreizung zugeordnet ist, dass die Wärmespreizungsfläche für jedes montierte Bauelement (20) im wesentlichen gleich ist.

5. Elektronisches Bauteil (50; 50') nach einem der Ansprüche 1 bis 4, das zwischen zwei elektrisch isolierenden Schichten (36, 37) ein weiteres Bauelement (60) und/oder einen Interposer (IP) aufweist.

6. Verfahren zum Herstellen eines elektronischen Bauteils (50) mit den folgenden Schritten:

- Erzeugen eines ersten Halberzeugnisses (HZ1) durch

- Bereitstellen eines Substrats (10) aus elektrisch leitendem Material mit einer Oberseite (12) und einer Unterseite (14),

- Aufbringen einer ersten Schicht (16) aus leitendem Material auf die Oberseite (12) und/oder die Un-

terseite (14) des Substrats (10), wobei in der ersten Schicht (16) mindestens eine Ausnehmung (18) zur Aufnahme eines elektronischen Bauelements vorgesehen wird,

- Einsetzen mindestens eines Bauelements (20) in die mindestens eine Ausnehmung (18),

- Erzeugen eines zweiten Halberzeugnisses (HZ2) durch

- Bereitstellen eines ersten Plattenelements (22) aus elektrisch leitendem Material,

- Erzeugen von durchgehenden Löchern (24) für spätere Durchkontaktierungen in dem ersten Plattenelement (22),

- Erzeugen eines dritten Halberzeugnisses (HZ3) durch

- Bereitstellen eines zweiten Plattenelements (26) aus elektrisch leitendem Material,

- Verlegen der drei Halberzeugnisse (HZ1, HZ2, HZ3) in einer Schichtstruktur durch Auflegen des ersten Halberzeugnisses (HZ1) auf das dritte Halberzeugnis (HZ3) und Auflegen des zweiten Halberzeugnisses (HZ2) auf das erste Halberzeugnis (HZ1) mit jeweils dazwischen vorgesehener Prepreg-Schicht (34, 36),

- Laminieren der Struktur,

- Freilegen der nach dem Laminieren mit Harz gefüllten Löcher (24) des ersten Plattenelements (22),

- zumindest teilweises Füllen der Löcher (24) mit leitfähigem Material (38) zur Durchkontaktierung.

7. Verfahren zum Herstellen eines elektronischen Bauteils (50') mit den folgenden Schritten:

- Erzeugen eines ersten Halberzeugnisses (HZ1) durch

- Bereitstellen eines Substrats (10) aus elektrisch leitendem Material mit einer Oberseite (12) und einer Unterseite (14),

- Aufbringen/Abscheiden einer ersten Schicht (16) aus leitendem Material auf die Oberseite (12)

und/oder die Unterseite (14) des Substrats (10), wobei in der ersten Schicht (16) mindestens eine Ausnehmung (18) zur Aufnahme eines elektronischen Bauelements vorgesehen wird,

- Einsetzen eines Bauelements (20) in die mindestens eine Ausnehmung (18),

- Erzeugen eines zweiten Halberzeugnisses (HZ2) durch

- Bereitstellen eines ersten Plattenelements (22) aus elektrisch leitendem Material,

- Erzeugen von durchgehenden Löchern (24) für spätere Durchkontaktierungen in dem ersten Plattenelement (22),

- Verlegen der zwei Halberzeugnisse (HZ1, HZ2) in einer Schichtstruktur durch Auflegen des zweiten Halberzeugnisses (HZ2) auf das erste Halberzeugnis (HZ1) mit einer dazwischen vorgesehenen Prepreg-Schicht (36),

- Laminieren der Struktur,

- Freilegen der nach dem Laminieren mit Harz gefüllten Löcher (24) des ersten Plattenelements (22),

- zumindest teilweises Füllen der Löcher (24) mit leitfähigem Material (38) zur Durchkontaktierung.

8. Verfahren nach Anspruch 6 oder 7, bei dem die Ausnehmung (18) derart durch selektives Aufbringen der ersten Schicht (16) gebildet wird, dass eine Tiefe (d) der Ausnehmung (18) etwas größer ist als die Höhe des einzusetzenden elektronischen Bauelements (20) zuzüglich einer Verbindungsschicht (19).

9. Verfahren nach einem der Ansprüche 6 bis 8, bei dem nach dem Bestücken mit dem mindestens einen elektronischen Bauelement (20) Freisparungen in der Ausnehmung (18) um das Bauelement (20) vor dem Verpressen aufgefüllt werden.

10. Verfahren nach einem der Ansprüche 6 bis 9, bei dem in die erste Schicht (16) und das Substrat (10) Kanäle (K1, K2, K3) eingebracht werden, wobei die Kanäle Haltestege (S) aufweisen, die nach dem Schritt des Laminierens entfernt werden.

11. Verfahren nach einem der Ansprüche 6 bis 10, bei dem in dem Schritt des Verlegens zwischen dem ersten Halberzeugnis (HZ1) und dem zweiten Halberzeugnis (HZ2) zwei Prepreg-Schichten (36, 37) eingebracht werden, wobei zwischen den beiden Prepreg-Schichten (36, 37) ein weiteres Bauelement (60) und/oder ein Interposer (IP) angeordnet wird, das bzw. der nach dem Schritt des Verpressens mittels ausplattierten Löchern (62, 72) ankontaktiert wird.

12. Verfahren nach Anspruch 11, bei dem die Löcher (62, 72) zum Ankontaktieren des weiteren Bauelements (60) und/oder des Interposers (IP) mittels Laserbohren und anschließendem Ausplattieren erzeugt werden.

13. Verfahren nach Anspruch 11 oder 12, bei dem bei dem Schritt des Erzeugens des zweiten Halberzeugnisses (HZ2) durchgehende Löcher zum Ankontaktieren des weiteren Bauelements (60) und/oder des Interposers (IP) vorgesehen werden.

14. Leiterplatte (LP; LP') mit einem elektronischen Bauteil (50; 50') nach einem der Ansprüche 1 bis 5.

15. Leiterplatte (LP; LP') nach Anspruch 14, bei der eine Oberfläche der Leiterplatte (LP; LP') bündig mit dem elektronischen Bauteil (50; 50') abschließt.

16. Leiterplatte (LP; LP') nach Anspruch 15, bei der sich ein Kühlkörper (120) an den bündigen Abschluss von Leiter-

platte (LP; LP') und elektronischem Bauteil (50; 50') anschließt.

17. Leiterplatte (LP; LP') nach einem der Ansprüche 14 bis 16, bei der zwischen dem elektronischen Bauteil (50; 50') und darüber liegenden Leiterbahnen (113) der Leiterplatte (LP; LP') eine Schicht (114) mit geringer thermischer Leitfähigkeit vorgesehen ist.

18. Verfahren zum Integrieren eines elektronischen Bauteils (50, 50') in eine Leiterplatte, mit den Schritten des

- Bereitstellens eines elektronischen Bauteils (50, 50') nach einem der Ansprüche 1 bis 6,

- Bereitstellens einer Leiterplatte mit einer zur Aufnahme des elektronischen Bauteils (50; 50') vorgesehenen Aussparung,

- Einbringens einer Schicht (114) geringer thermischer Leitfähigkeit in die Aussparung,

- Einsetzens des elektronischen Bauteils (50; 50') in die Aussparung der Leiterplatte auf die Schicht (114) geringer thermischer Leitfähigkeit,

- Verpressens der derart entstandenen Schichtstruktur,

- Aufbringens einer gemeinsame Außenlage bildenden elektrisch leitenden Schicht (118), die auch zur Ankontaktierung zwischen dem elektronischen Bauteil (50; 50') und der Leiterplatte (LP; LP') dient.

19. Verfahren nach Anspruch 18, bei dem auf die gemeinsame Außenlage bildende Schicht (118) im Bereich des elektronischen Bauteils (50; 50') ein Kühlkörper (120) aufgebracht wird.

20. Verfahren nach Anspruch 19, bei dem zwischen der elektrisch leitenden Schicht (118) und dem Kühlkörper (120)

eine TIM-Schicht (119) zur Ausbildung eines thermisch lückenlosen Spalts eingebracht ist.

21. Verfahren nach einem der Ansprüche 18 bis 20, bei dem zwischen der Leiterplatte mit eingesetztem elektronischen Bauteil einerseits und der gemeinsamen Außenlage (118) andererseits ein thermisch leitfähiges Dielektrikum (116) eingebracht wird.

22. Elektronisches Bauteil (50; 50'), hergestellt nach einem Verfahren nach einem der Ansprüche 6 bis 13.

23. Elektronisches Bauteil (50; 50') nach Anspruch 22, bei dem bei mehr als einem elektronischen Bauelement (20) jedem Bauelement (20) derart eine Fläche zur Wärmespreizung zugeordnet ist, dass die Wärmespreizungsfläche für jedes montierte Bauelement (20) im wesentlichen gleich ist.

24. Leiterplatte (LP; LP') mit einem elektronischen Bauteil (50; 50') nach Anspruch 22 oder 23.

25. Leiterplatte (LP; LP') nach Anspruch 24, bei der eine Oberfläche der Leiterplatte (LP; LP') bündig mit dem elektronischen Bauteil (50; 50') abschließt.

26. Leiterplatte (LP; LP') nach Anspruch 25, bei der sich ein Kühlkörper (120) an den bündigen Abschluss von Leiterplatte (LP; LP') und elektronischem Bauteil (50; 50') anschließt.

27. Leiterplatte (LP; LP') nach einem der Ansprüche 24 bis 26, bei der zwischen dem elektronischen Bauteil (50; 50') und darüber liegenden Leiterbahnen (113) der Leiterplatte (LP; LP') eine Schicht (114) mit geringer thermischer Leitfähigkeit vorgesehen ist.

Fig. 1

Fig. 2

Fig. 2a

Fig. 3

Fig. 6

Fig. 7

Fig. 3

Fig. 10

Fig. 11

Fig. 12