(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년01월19일

(11) 등록번호 10-1698228

(24) 등록일자 2017년01월13일

(51) 국제특허분류(Int. Cl.)

C30B 29/02 (2006.01) C01B 31/04 (2006.01)

C30B 31/02 (2006.01) C30B 31/04 (2006.01)

C30B 31/22 (2006.01) H01B 1/04 (2006.01)

B82Y 30/00 (2017.01) B82Y 40/00 (2017.01)

(21) 출원번호 10-2012-7005794

(22) 출원일자(국제) 2010년07월22일

심사청구일자 2015년07월08일

(85) 번역문제출일자 2012년03월05일

(65) 공개번호 10-2012-0080168

(43) 공개일자 2012년07월16일

(86) 국제출원번호 PCT/US2010/002058

(87) 국제공개번호 WO 2011/016837

국제공개일자 2011년02월10일

(30) 우선권주장

12/461,343 2009년08월07일 미국(US)

(56) 선행기술조사문헌

JP2006278586 A

(73) 특허권자

가디언 인더스트리즈 코퍼레이션.

미국 48326 미시건, 오번 힐스, 하몬로드 2300 월

드헤드워터즈

(72) 발명자

베르사미, 비야엔 에스.

미국 48103 미시건 앤 아르보르 이글 로드 756

(74) 대리인

특허법인 무한

전체 청구항 수 : 총 11 항

심사관 : 이영화

(54) 발명의 명칭 그래핀의 대면적 증착 및 도핑과 이를 포함하는 제품

### (57) 요약

본 발명의 어떤 구체예는 투명 전도성 코팅으로 그래핀을 사용하는 것에 관한 것이다. 어떤 구체예에서는, 그래핀 박막은 촉매 박막 상에서  $C_2H_2$ ,  $CH_4$ 등과 같은 탄화 수소 가스로부터 대면적 이형-에피택셜 성장한 것이다. 어떤 구체예에서의 그래핀 박막은 도핑되거나 도핑되지 않을 수 있다. 어떤 구체예에서는, 형성된 그래핀 박막이 캐리어 기판으로부터 박리되고 중간 또는 최종 제품의 수용 기판으로 이전될 수 있다. 성장하여 박리 및 이전된 그래핀은 낮은 면적(예를 들어, 도핑 시  $150 \Omega/\square$  미만)과 높은 투광도(예를 들어, 적어도 가시광선 및 적외선 영역에서의)를 가질 수 있다.

대 표 도 - 도12

## 명세서

### 청구범위

#### 청구항 1

삭제

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

삭제

#### 청구항 5

단일-배향된 대면적 결정입자 결정 구조를 갖는 촉매 박막 상에 중간 그래핀 박막을 이형-에피택셜하게 (hetero-epitaxially) 성장시키는 단계; 및

상기 중간 그래핀 박막을 n-형 또는 p-형 도편트로 도핑하는 단계;

를 포함하고,

상기 도핑된 그래핀 박막은  $150 \Omega/\square$  보다 작은 면저항 값을 갖는 것이고,

상기 중간 그래핀 박막의 도핑 단계는,

목표 수용 기판의 제작에 사용되는 용융 공정의 결과로, 고상 도편트를 내부에 포함하는 상기 목표 수용 기판을 제공하는 단계; 및

상기 목표 수용 기판의 상기 고상 도편트를 열화산에 의하여 상기 중간 그래핀 박막으로 이전시키는 단계;

를 포함하는 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

#### 청구항 6

제5항에 있어서, 상기 목표 수용 기판은 1-10 원자량% 도편트 물질을 포함하는 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

#### 청구항 7

단일-배향된 대면적 결정입자 결정 구조를 갖는 촉매 박막 상에 중간 그래핀 박막을 이형-에피택셜하게 (hetero-epitaxially) 성장시키는 단계; 및

상기 중간 그래핀 박막을 n-형 또는 p-형 도편트로 도핑하는 단계;

를 포함하고,

상기 도핑된 그래핀 박막은  $150 \Omega/\square$  보다 작은 면저항 값을 갖는 것이고,

상기 중간 그래핀 박막의 도핑 단계는,

이온 범의 조사에 의하여 고상 도편트를 내부에 포함하는 목표 수용 기판을 제공하는 단계; 및

상기 목표 수용 기판의 상기 고상 도편트를 열화산에 의하여 상기 중간 그래핀 박막으로 이전시키는 단계;

를 포함하는 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

#### 청구항 8

제7항에 있어서, 상기 이온 빔 조사는 10-1000 eV 전력 수준에서 수행되는 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

#### 청구항 9

단일-배향된 대면적 결정입자 결정 구조를 갖는 촉매 박막 상에 중간 그래핀 박막을 이형-에피택셜하게 (hetero-epitaxially) 성장시키는 단계; 및

상기 중간 그래핀 박막을 n-형 또는 p-형 도편트로 도핑하는 단계;

를 포함하고,

상기 도핑된 그래핀 박막은  $150 \Omega/\square$  보다 작은 면저항 값을 갖는 것이고,

상기 중간 그래핀 박막의 도핑 단계는,

목표 수용 기판 상에 배치되고, 고상 도편트를 내부에 포함하는 적어도 하나의 박막 코팅을 갖는 상기 목표 수용 기판을 제공하는 단계; 및

상기 목표 수용 기판 상에 형성된 상기 적어도 하나의 박막의 상기 고상 도편트를 열화산에 의하여 상기 중간 그래핀 박막으로 이전시키는 단계;

를 포함하는 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

#### 청구항 10

단일-배향된 대면적 결정입자 결정 구조를 갖는 촉매 박막 상에 중간 그래핀 박막을 이형-에피택셜하게 (hetero-epitaxially) 성장시키는 단계; 및

상기 중간 그래핀 박막을 n-형 또는 p-형 도편트로 도핑하는 단계;

를 포함하고,

상기 도핑된 그래핀 박막은  $150 \Omega/\square$  보다 작은 면저항 값을 갖는 것이고,

상기 중간 그래핀 박막의 도핑 단계는,

상기 촉매 박막에 고상 도편트를 미리 심어놓는 (pre-implanting) 단계; 및

상기 촉매 박막의 상기 고상 도편트를 열화산에 의하여 상기 중간 그래핀 박막으로 이전시키는 단계;

를 포함하는 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

#### 청구항 11

제10항에 있어서, 상기 열화산은, 상기 중간 그래핀 박막의 증착 과정에서 발생하는 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

#### 청구항 12

제10항에 있어서, 상기 촉매 박막은 그 총량에 (in its bulk) 1-5 원자량% 고상 도편트 원자를 포함하는 것을

특징으로 하는 도핑된 그래핀 박막의 제조방법.

### 청구항 13

제12항에 있어서, 상기 촉매 박막은 니켈을 포함하는 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

### 청구항 14

제5항, 제7항, 제9항 및 제10항 중 어느 한 항에 있어서, 상기 도핑된 그래핀 박막은 질소, 봉소, 인, 불소, 리튬, 칼륨 및 황 중 하나 이상으로 도핑된 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

### 청구항 15

제5항, 제7항, 제9항 및 제10항 중 어느 한 항에 있어서, 상기 도핑된 그래핀 박막은 10-20 Ω/□의 면적항 값을 갖는 것을 특징으로 하는 도핑된 그래핀 박막의 제조방법.

### 청구항 16

삭제

### 청구항 17

삭제

### 청구항 18

삭제

### 청구항 19

삭제

### 청구항 20

삭제

## 발명의 설명

### 기술 분야

[0001] 본 발명의 일 구체예는 그래핀을 포함하는 박막에 관한 것이다. 더욱 구체적으로, 본 발명의 일 구체예는 그래핀을 투명 전도성 코팅 (TCC)으로 사용하는 것에 관한 것이다. 일 구체예에서, 그래핀 박막은, 예를 들어 촉매 박막 등의 대면적 상에 탄화수소 가스 (예를 들어,  $C_2H_2$ ,  $CH_4$  등)로부터 이형-에피택셜하게 성장한 것이다. 어떤 구체예의 그래핀 박막은 도핑된 것일 수도 있고 도핑되지 않은 것일 수도 있다. 어떤 구체예에서, 그래핀 박막은 형성된 후에 캐리어 기판으로부터 박리되어 예를 들어, 중간 또는 최종 제품에 포함되는 수용 기판으로 이전될 수 있다.

## 배경 기술

[0002] 인듐주석산화물 (ITO) 및 불소 도핑된 주석산화물 (FTO 또는  $SnO_2:F$ ) 코팅은 광전자 장치의 원도우 전극으로 널리 사용된다. 이러한 투명 전도성 산화물 (Transparent Conductive Oxides, TCOs)은 다양한 적용에 있어서 매우 유용하다. 그러나 불행히도, ITO 및 FTO의 사용은 많은 문제점이 대두되고 있다. 예를 들어, 지구 상의 인듐 성분의 고갈, 산 또는 염기 환경에서의 TCOs의 불안정성, 이온 전도성 층으로부터 이온 확산에 대한 민감성, 적외선 영역 근방 (예를 들어, 고에너지 스펙트럼)에서의 제한적인 투명성, FTO 구조 결함에 의한 FTO 장치의 높

은 누설전류 등의 문제이다. ITO의 비탄력성 및 높은 증착 온도 또한 그 적용의 한계이다. 게다가, Sn02:F의 거친 표면은 아크 문제를 야기할 수 있다.

[0003] 그러므로, 안정성, 고투명성, 월등한 전도성을 갖는 부드럽고 폐탄 형성 가능한 전극 물질에 대한 해당 분야의 요구가 있다.

[0004] 안정성, 고투명성, 월등한 전도성을 갖는 새로운 전극 물질에 대한 연구가 계속되고 있다. 이러한 연구의 일면은 상용 TCOs의 가능한 대체물을 찾는 것이다.

## 발명의 내용

### 해결하려는 과제

[0005] 상용 TCOs의 가능한 대체물을 찾는 관점에서, 본 발명의 발명자들은 사용 가능한 탄소, 특히 그래핀을 기초로 하는 투명 전도성 코팅 (TCC)을 개발하게 되었다.

### 과제의 해결 수단

[0006] 본 발명의 도핑된 그래핀 박막의 제조방법은, 실질적으로 단일-기원 대입자 결정 구조를 갖는 촉매 박막 상에 중간 그래핀 박막을 이형-에피택셜하게 (hetero-epitaxially) 성장시키는 단계; 및 상기 중간 그래핀 박막을 n-형 또는 p-형 도편트로 도핑하는 단계;를 포함하고, 상기 도핑된 그래핀 박막은  $150 \Omega/\square$  보다 작은 면저항 값을 갖는 것을 특징으로 한다.

[0007] 상기 중간 그래핀 박막의 도핑 단계는, 상기 도편트로 사용되는 물질을 포함하는 도핑 가스에 상기 중간 그래핀 박막을 노출시키는 단계; 상기 중간 그래핀 박막과 상기 도핑 가스를 함유하는 챔버 내에 플라즈마를 여기하는 단계; 및 상기 도핑 가스 내의 물질을 이용하여 상기 중간 그래핀 박막 내의 상기 도편트에 이온 범을 조사하는 단계;를 포함할 수 있다.

[0008] 상기 이온 범 전력은 10-200 eV일 수 있고, 20-40 eV일 수 있다.

[0009] 상기 중간 그래핀 박막의 도핑 단계는, 목표 수용 기판의 제작에 사용되는 용융 공정의 결과로, 고상 도편트를 내부에 포함하는 상기 목표 수용 기판을 제공하는 단계; 및 상기 목표 수용 기판의 상기 고상 도편트를 열화산에 의하여 상기 중간 그래핀 박막으로 이전시키는 단계;를 포함할 수 있다.

[0010] 상기 목표 수용 기판은 1-10 원자량% 도편트 물질을 포함할 수 있다.

[0011] 상기 중간 그래핀 박막의 도핑 단계는, 이온 범의 조사에 의하여 고상 도편트를 내부에 포함하는 목표 수용 기판을 제공하는 단계; 및 상기 목표 수용 기판의 상기 고상 도편트를 열화산에 의하여 상기 중간 그래핀 박막으로 이전시키는 단계;를 포함할 수 있다.

[0012] 상기 이온 범 조사는 10-1000 eV 전력 수준에서 수행될 수 있다.

[0013] 상기 중간 그래핀 박막의 도핑 단계는, 목표 수용 기판 상에 배치되고, 고상 도편트를 내부에 포함하는 적어도 하나의 박막 코팅을 갖는 상기 목표 수용 기판을 제공하는 단계; 및 상기 목표 수용 기판 상에 형성된 상기 적어도 하나의 박막의 상기 고상 도편트를 열화산에 의하여 상기 중간 그래핀 박막으로 이전시키는 단계;를 포함할 수 있다.

[0014] 상기 중간 그래핀 박막의 도핑 단계는, 상기 촉매 박막에 고상 도편트를 미리 심어놓는 (pre-implanting) 단계; 및 상기 촉매 박막의 상기 고상 도편트를 열화산에 의하여 상기 중간 그래핀 박막으로 이전시키는 단계;를 포함할 수 있다.

[0015] 상기 열화산은, 상기 중간 그래핀 박막의 증착 과정에서 발생하는 것일 수 있다.

[0016] 상기 촉매 박막은 그 총량에 (in its bulk) 1-5 원자량% 고상 도편트 원자를 포함할 수 있다.

[0017] 상기 촉매 박막은 니켈을 포함할 수 있다.

[0018] 상기 도핑된 그래핀 박막은 질소, 붕소, 인, 불소, 리튬, 칼륨 및 황 중 하나 이상으로 도핑된 것일 수 있다.

- [0019] 상기 도핑된 그래핀 박막은 10-20  $\Omega/\square$ 의 면저항 값을 갖는 것일 수 있다.

- [0020] 본 발명의 도핑된 그래핀 박막은, 실질적으로 단일-기원 대입자 결정 구조를 갖는 금속 측면 박막 상에 직접 또는 간접적으로 이형-에피택셜하게 성장한 것으로서, 1-10 원자층 두께를 갖고, 150  $\Omega/\square$  보다 작은 면저항 값을 갖는 것이다.

- [0021] 상기 도핑된 그래핀 박막은 n-형 도편트를 포함할 수 있고, p-형 도편트를 포함할 수 있다.

- [0022] 상기 도핑된 그래핀 박막은, 질소, 붕소, 인, 불소, 리튬, 칼륨 및 황 중 하나 이상으로 도핑된 것일 수 있다.

- [0023] 상기 도핑된 그래핀 박막은 10-20  $\Omega/\square$ 의 면저항 값을 갖는 것일 수 있다.

### 발명의 효과

- [0024] 본 발명에 따르면, 상용 TCOs를 대체할 수 있는 탄소 물질, 특히 그래핀을 기반으로 하는 투명 전도성 코팅 (TCC)을 얻을 수 있다.

### 도면의 간단한 설명

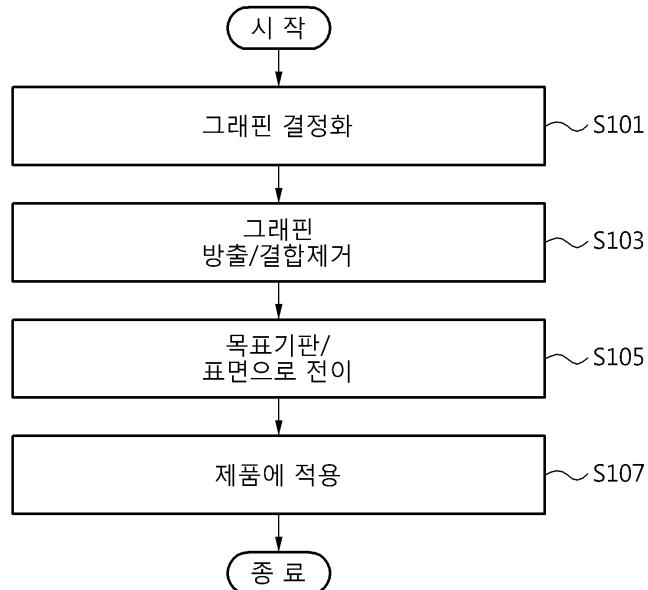

- [0025] 도 1은 일 구체예의 과정을 대략적으로 도시한 고급 흐름도이다.

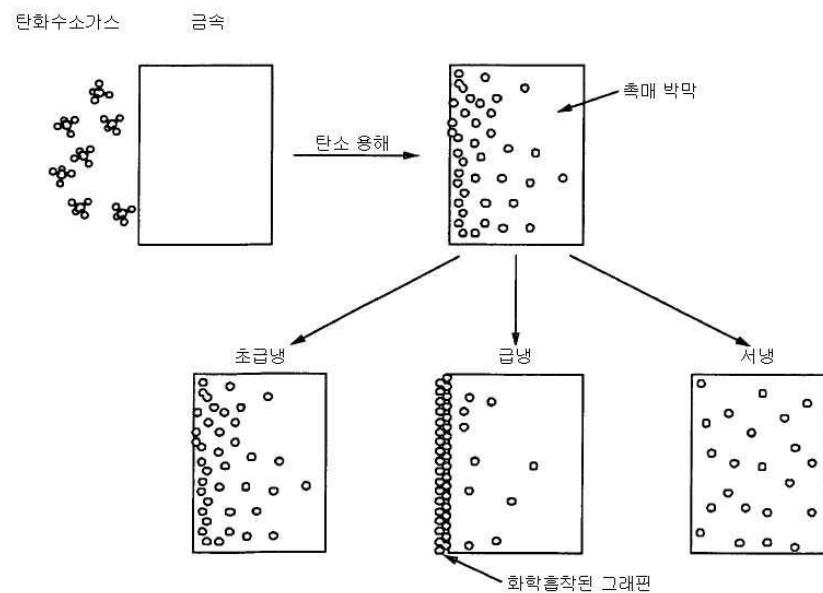

- 도 2는 몇 구체예에 따른 탄화수소 가스의 도입, 탄소의 용해 및 몇 가지 담금질의 가능한 결과를 나타내는 구체예들의 측면 성장 기법의 개략 예시도이다.

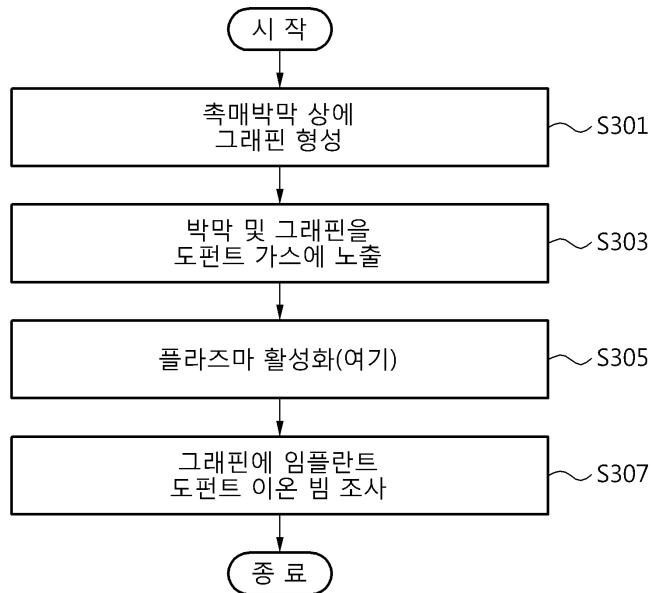

- 도 3은 일 구체예에 따른 실시예 1의 그래핀 도핑 방법을 나타낸 흐름도이다.

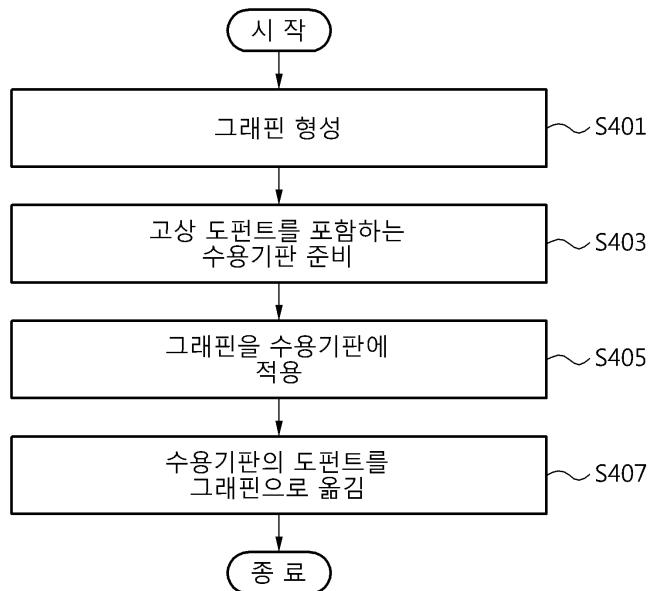

- 도 4는 일 구체예에 따른 실시예 2의 따른 그래핀 도핑 방법을 나타낸 흐름도이다.

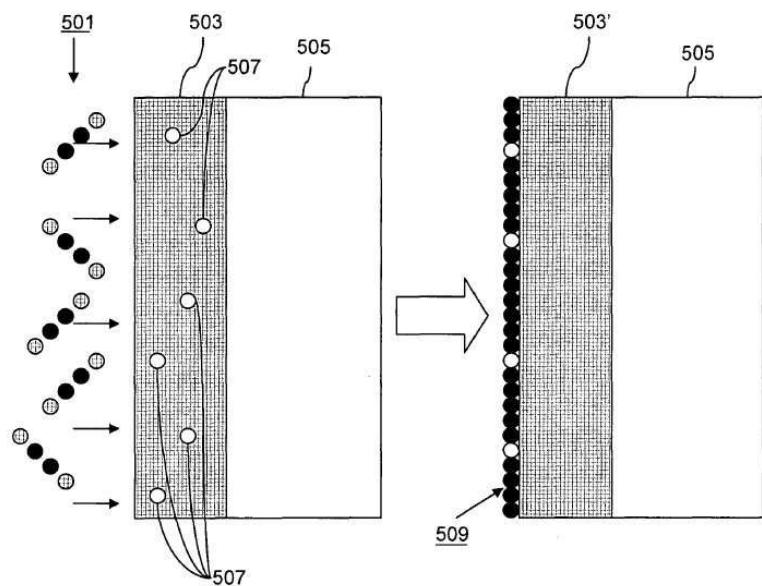

- 도 5는 일 구체예에 따른 실시예 3의 그래핀 도핑 방법의 개략 예시도이다.

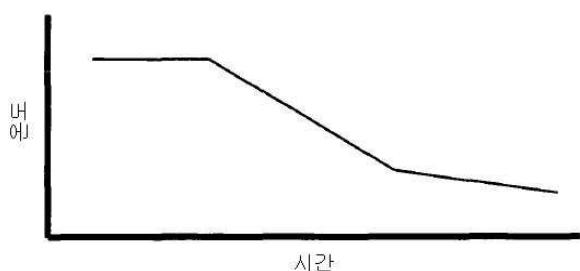

- 도 6은 일 구체예에 따른 그래핀 도핑의 시간에 따른 온도를 나타낸 그래프이다.

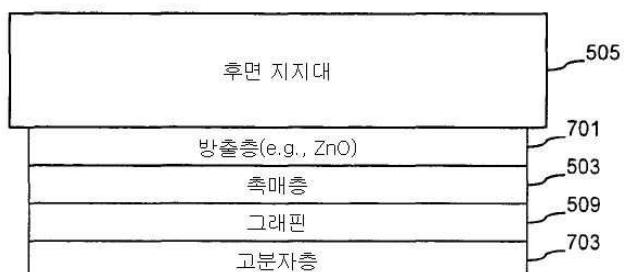

- 도 7은 일 구체예에 따른 그래핀 방출 (release) 또는 결합 제거 (debonding)에 유용한 적층예를 나타낸 것이다.

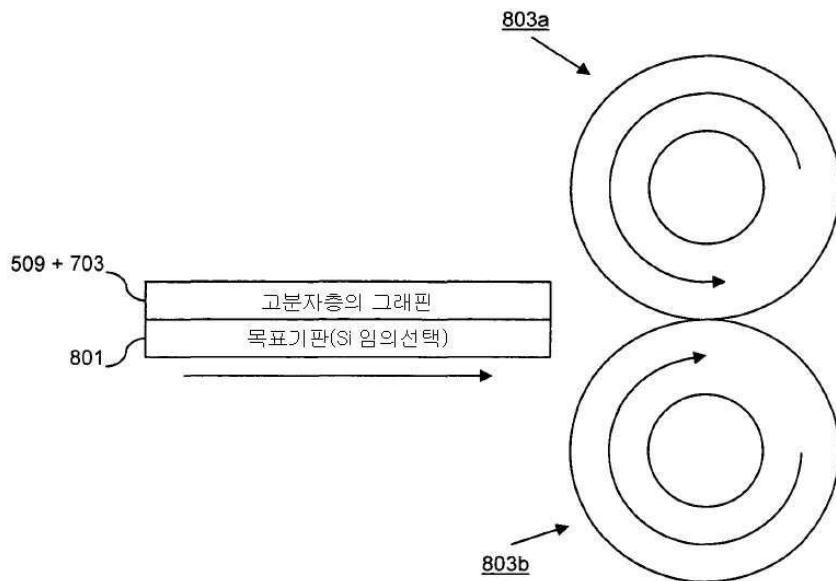

- 도 8은 일 구체예에 따른 목표 (target) 유리 기판 상에 그래핀을 배치하는데 사용 가능한 적층 장치의 개략도이다.

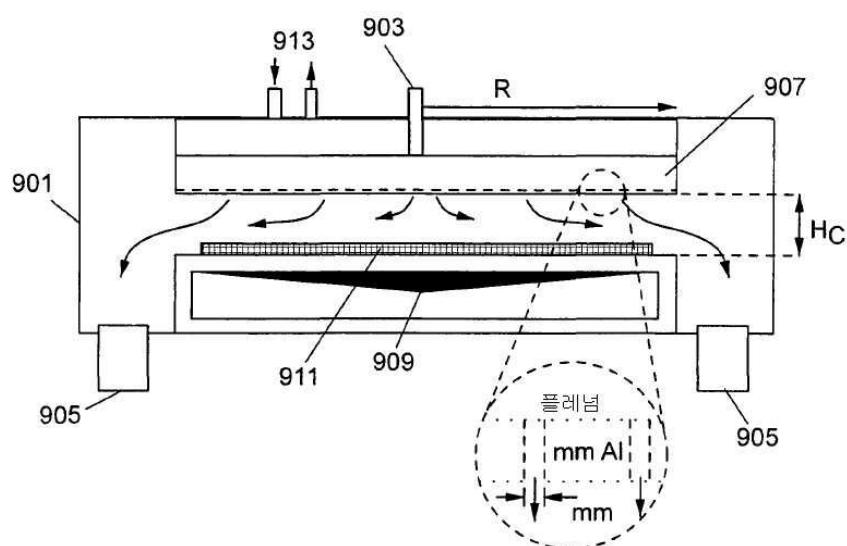

- 도 9는 일 구체예에 따른 고전자급 (HEG) 그래핀 증착에 적합한 반응기의 단면 개략도이다.

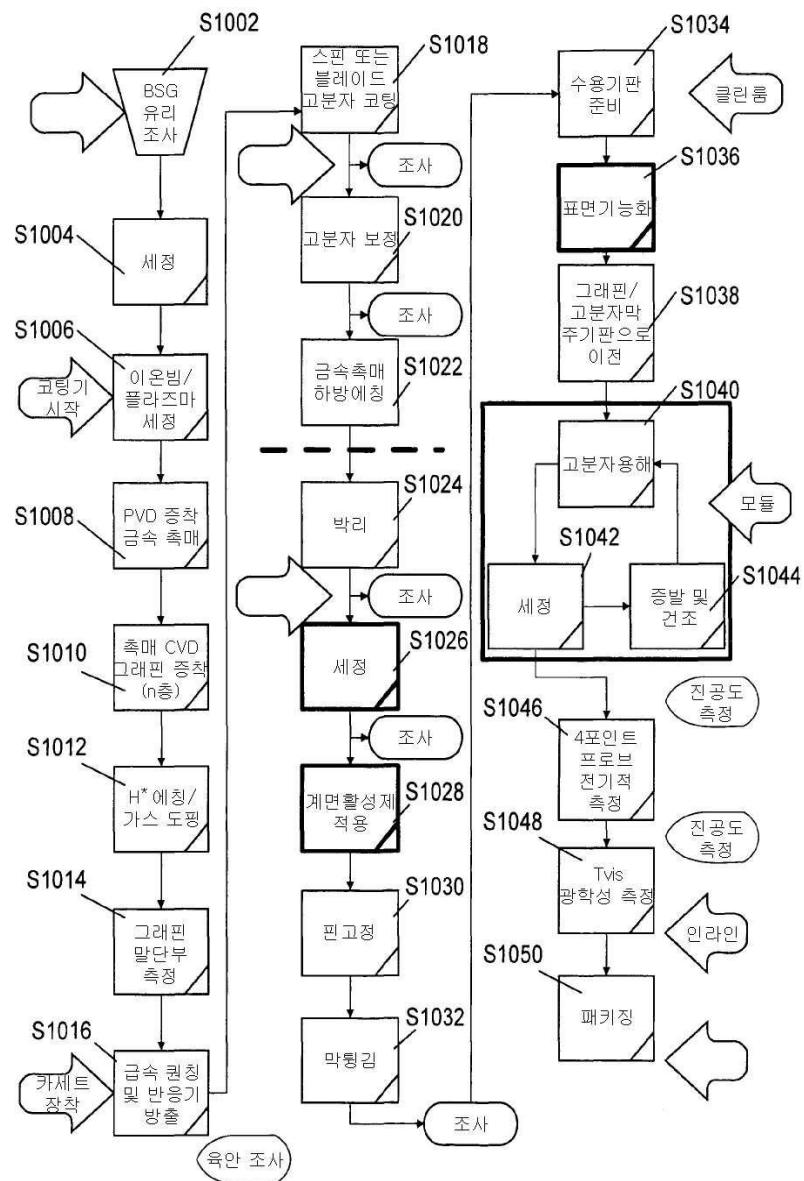

- 도 10은 일 구체예에 따른 측면 CVD 성장, 박리 및 전이 과정의 예를 나타내는 흐름도이다.

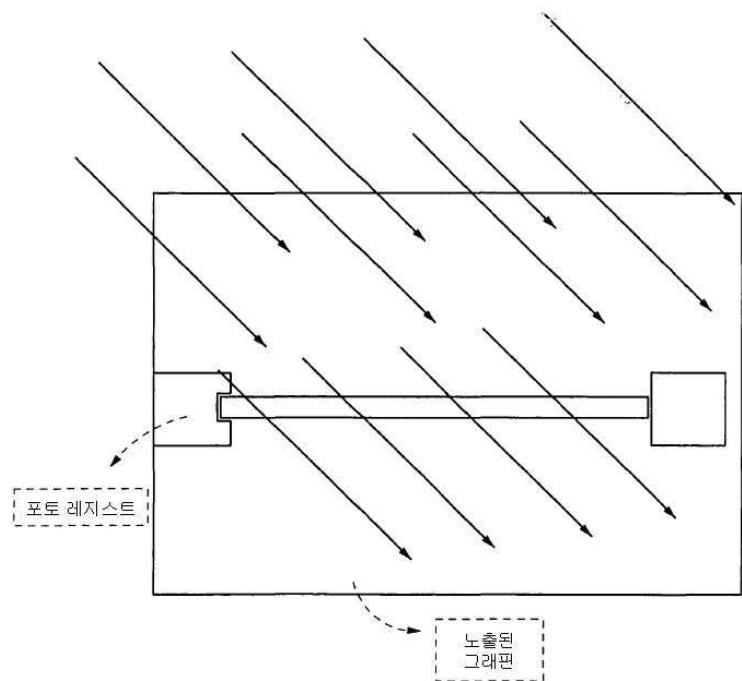

- 도 11은 일 구체예에 따라 제조된 그래핀 예의 이미지이다.

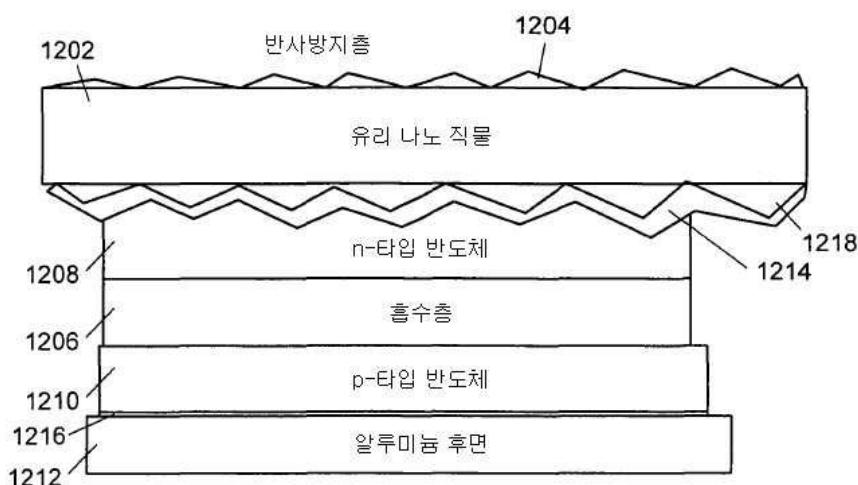

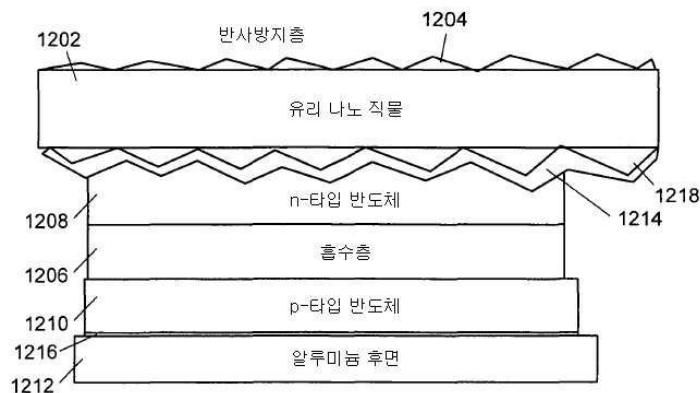

- 도 12는 일 구체예에 따른 그래핀 기반 층을 포함하는 태양 광전지 장치의 단면 개략도이다.

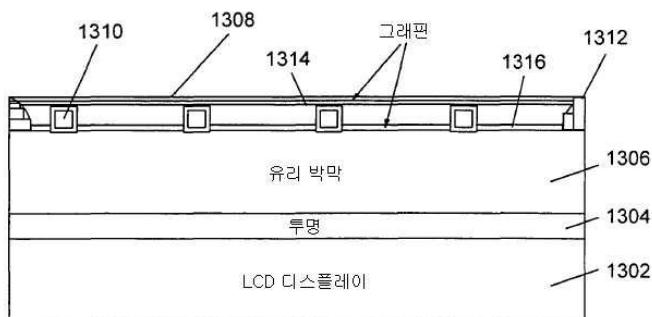

- 도 13은 일 구체예에 따른 그래핀 기반 층을 포함하는 터치 스크린의 단면 개략도이다.

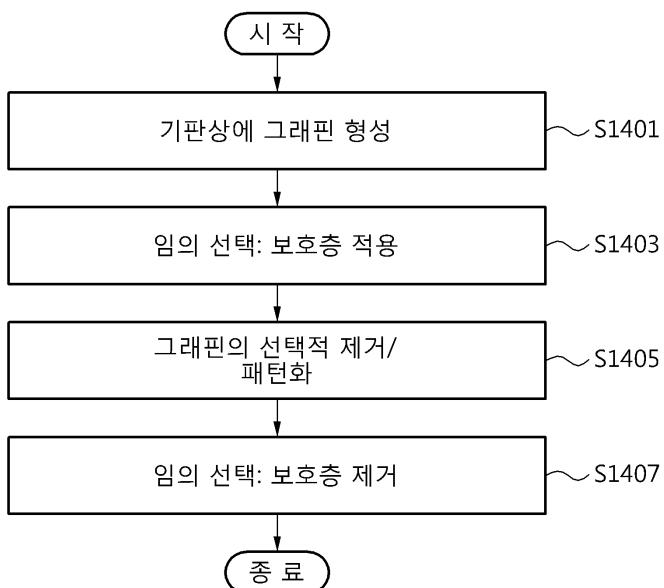

- 도 14는 일 구체예에 따른 전도성 데이터/버스라인의 제조 방법의 흐름도이다.

- 도 15는 일 구체예에 따른 전도성 데이터/버스라인의 제조방법의 개략도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0026] 일반적으로 그래핀이라 함은, 하나 또는 그 이상의 원자층 흑연, 즉, 단일 그래핀층 또는 SGL이 n 개의 층 (n은 약 10까지 될 수 있다)으로 확장된 것을 가르킨다. 최근의 그래핀의 발견과 맨체스터 대학에서의 흑연 결정의 쪼개에 의한 떼어냄은 전자 공학 분야의 트랜드가 회로 소자를 나노 단위로 줄여가는 시점에 이루어졌다. 이러한 관점에서, 그래핀은, 기준 전자 물질에서는 일어나지 않는 기대 이상의 탁월한 광전자 특성을 갖는 새로운 지평을 이끌어 내었다. 이 특성은 질량이 0이고 상대론적 입자와 같이 행동하는 그래핀 내의 캐리어를 충전하는 선분산 관계 ( $E$  vs.  $k$ )로부터 나타났다. 탄소 원자의 주위를 움직이는 전이 입자와 같은 상대론적 행동은, 그래

핀의 별집 격자의 주기적인 포텐셜이, 낮은 에너지 ( $E < 1.2 \text{ eV}$ )에서  $v_F \approx c/300 = 10^6 \text{ ms}^{-1}$ 의 빛의 효과적인 속도에 관한 (2+1) 차원 디렉 방정식으로 정확하게 묘사되는 새로운 유사 입자를 생성하는 그들의 상관관계에 기인한다. 그러므로, 그래핀 연구에서 (광자를 다루는) 양자 전자 역학 (QED)의 잘 정립된 기법에 연구 노력이 기울여질만하다 - 더 유리한 면으로서 그러한 효과는 그래핀에서 300배 증가된다. 예를 들어, 일반적인 커플링 상수  $a$ 는 진공에서  $1/137$ 인데 반하여, 그래핀에서는 거의 2이다 (참고: K.S. Novoselov, "Electrical Field Effect in Atomically Thin Carbon Films," *Science*, vol. 306, pp. 666-69 (2004)).

[0027] 단지 (최소) 단원자 두께임에도 불구하고, 그래핀은 화학적으로 열적으로 안정해서 (그래핀이  $300^\circ\text{C}$ 에서 표면이 산화될 수 있음에도 불구하고), 그러한 연유로 주변 환경에 견딜 수 있는 그래핀 기반 디바이스에 효과적으로 적용할 수 있다. 고성능 그래핀 시트는 벌크 흑연으로부터 미세 기계적으로 떼어냄으로 처음 만들어졌다. 동일한 기법이 현재  $100 \mu\text{m}^2$  크기의 고성능 그래핀 미소 결정을 제공하는데 정밀 조정된다. 이 정도 크기는 마이크로 전자공학에 적용하기에 충분하다. 결론적으로, 주로 대학에서 발달된 대부분의 기술은 스케일-업 보다는 미시적인 샘플과 장치 준비 및 특성에 집중되어 있다.

[0028] 대부분의 현재의 연구 방향과는 달리, 가능한 TCC로서의 무한한 가능성을 인식하기 위해서는, 기판 (예를 들어, 유리 또는 플라스틱 기판) 상에 고성능 물질을 대면적으로 증착하는 것은 필수적이다. 현재까지, 최대면적의 그래핀 제조 공정은 습식 화합물을 이용한 벌크 흑연의 박리에 의존하고, 고정렬 열분해 흑연 (HOPG)과 화학적 박리로부터 시작한다. 알려진 대로, 고정렬 열분해 흑연은,  $c$  축으로 1도 미만으로 펼쳐진 각을 갖는 열분해 흑연의 고정렬 형태이고, 일반적으로  $3000^\circ\text{K}$ 에서의 압박 열처리 (stress annealing)로 얻어진다. 고정렬 열분해 흑연은 부서지기 쉽고 박리성을 갖지만, 통상 반사성과 전기적 전도성을 갖는 점에서 순수 금속과 유사하게 행동한다. 이런 식으로, 제조된 그래핀은 필터링된 후 표면에 접착된다. 그러나 이러한 박리 공정은 단점이 있다. 예를 들어, 박리된 그래핀은 접히거나 구겨지고, 작은 조각으로 존재하고 콜라주 (collage) / 스티치 (stitch) 공정에 의존하여, 그래핀층 수 등에 대한 본질적인 제어가 불가능하다. 이렇게 제조된 물질은 종종 삽입물에 오염되고, 불량한 전기적 물성을 갖게 된다.

[0029] 탄소의 상태도에 대한 면밀한 분석은 공정 윈도우 조건 (process window conditions)이 흑연 및 다이아몬드의 제조뿐만 아니라, 예를 들어, 탄소나노튜브 (CNT)와 같은 동소체 형태의 제조에도 적합하다는 것을 보여준다. 나노 튜브의 촉매 증착은 작용기의 다양성에 의하여  $1000^\circ\text{C}$  정도의 온도의 가스 상 (phase)로부터 이루어진다.

[0030] 전통적인 연구 분야 및 전통적인 기법과는 반대로, 본 발명의 일 구체예는, 결정형 그래핀을 ( $n$ 이 약 15 정도로 큰) 단결정형 그래핀으로 이형-에피택셜하게 성장시키고, 이것을 ( $n$ 이 3보다 작은) 고전자급 (high electronic grade, HEG) 그래핀으로 전환하는 확장 가능 기법에 관한 것이다. 일 구체예는 또한 가시광선 및 적외선 영역 모두에서 투명하고, 전도성을 갖는 초박막 그래핀 필름을, 예를 들어, 고상 태양 전지와 같은 다양한 적용기기의 유비쿼터스한 금속 산화물 윈도우 전극을 대체하는 HEG 그래핀의 사용에 관한 것이다. 일 구체예의 성장 기법은, 유리 친화적인 (glass-friendly) 충분히 낮은 온도에서 발생하는, 촉매에 의해 유도되는 이형-에피택셜 CVD 공정에 기초한다. 예를 들어, 역학 원리만큼이나 열역학적 원리에 의해서도, 약  $700^\circ\text{C}$ 보다 낮은 온도에서 시드 (seed) 촉매 층 상에 가스 상으로부터 HEG 그래핀 필름이 결정화될 수 있다.

[0031] 본 발명의 일 구체예는 그래핀 도핑 박막의 제조방법과 관련이 있다. 중간 그래핀 박막은 실질적으로 단일-기원 대입자 결정 구조를 갖는 촉매 박막 상에 이형-에피택셜하게 성장한다. 그래핀 도핑 박막 제조 과정 중에, 중간 그래핀 박막은  $n$ -형 또는  $p$ -형 도편트로 도핑된다. 도핑 그래핀 박막은  $150 \Omega/\square$  보다 작은 면저항 값을 갖는다.

[0032] 어떤 구체예에서는, 중간 그래핀 박막의 도핑 단계는, 중간 그래핀 박막을 도편트로 사용되는 물질을 포함하는 도핑 가스에 노출시키는 단계, 중간 그래핀 박막과 도핑 가스를 함유하는 챔버 내에 플라즈마를 여기하는 단계 및 도핑 가스 중의 물질을 이용하여 중간 그래핀 박막의 도편트에 저에너지 이온빔을 조사하는 단계를 포함한다. 상기 이온빔 전력은 10-200 eV일 수 있고, 20-40 eV일 수 있다.

[0033] 어떤 구체예에서는, 중간 그래핀 박막의 도핑 단계는, 목표 수용 기판의 제작에 사용되는 용융 공정의 결과, 고상 도편트를 그 내부에 포함하는 목표 수용 기판을 제공하는 단계 및 목표 수용 기판의 고상 도편트를 열화산에 의하여 중간 그래핀 박막으로 이전시키는 단계를 포함한다. 상기 목표 수용 기판은 1-10 원자량% 도편트 물질을 포함할 수 있다.

[0034] 어떤 구체예에서는, 중간 그래핀 박막의 도핑 단계는, 이온빔의 조사에 의하여 고상 도편트를 그 내부에 포함

하는 목표 수용 기판을 제공하는 단계 및 목표 수용 기판의 고상 도편트를 열화산에 의하여 중간 그래핀 박막으로 이전시키는 단계를 포함한다. 상기 이온 범 조사는 10-1000 eV 전력 수준에서 수행될 수 있다.

[0035] 어떤 구체예에서는, 중간 그래핀 박막의 도핑 단계는, 목표 수용 기판 상에 배치된, 고상 도편트를 그 내부에 포함하는 적어도 하나의 박막 코팅을 갖는 목표 수용 기판을 제공하는 단계 및 목표 수용 기판의 고상 도편트를 열화산에 의하여 중간 그래핀 박막으로 이전시키는 단계를 포함한다.

[0036] 어떤 구체예에서는, 중간 그래핀 박막의 도핑 단계는, 열화산에 의하여 중간 그래핀 박막으로 이전되도록, 촉매 박막에 고상 도편트를 미리 심어놓는 (pre-implanting) 단계를 포함한다. 예를 들어, 열화산은 중간 그래핀 박막을 증착하는 동안 발생할 수 있다. 상기 촉매 박막은 그 총량에 (in its bulk) 1-5 원자량% 고상 도편트 원자를 포함할 수 있고, 상기 촉매 박막은 니켈을 포함할 수 있다. 상기 도핑된 그래핀 박막은 질소, 봉소, 인, 불소, 리튬, 칼륨 및 황 중 하나 이상으로 도핑된 것일 수 있다. 상기 도핑된 그래핀 박막은 10-20 Ω/□의 면저항 값을 갖는 것일 수 있다.

[0037] 본 발명의 어떤 구체예는 실질적으로 단일-기원 대입자 결정 구조를 갖는 금속 촉매 박막 상에 직접 또는 간접적으로, 이형-에피택셜하게 성장한 도핑된 그래핀 박막에 관한 것이다. 그래핀 박막은 1-10 원자층 두께이다. 도핑된 그래핀 박막은 150 Ω/□ 보다 작은 면저항 값을 갖는다.

[0038] 어떤 구체예에서는, (2 층 이상의) 도핑된 그래핀 박막은, 질소, 봉소, 인, 불소, 리튬 및 황 중 하나 이상으로 도핑된 것일 수 있다. 어떤 구체예에서는, 도핑된 그래핀 박막은 10-20 Ω/□의 면저항 값을 가질 수 있다. 어떤 구체예의 도핑된 그래핀 박막은 n-형 또는 p-형 도편트를 포함한다.

[0039] 여기에서 기술된 특징, 양상, 장점과 예시적인 실시예는 추가적인 실시예를 실현하기 위해 결합될 수 있다.

[0040] 여러 가지 특징과 장점은 더 좋을 수 있고 도면과 관련한 예시적 묘사 구현은 다음 상세한 설명을 참고로 더 완전히 이해될 수 있다.

[0041] 본 발명의 일 구체예는, (n이 약 15정도로 큰) 단결정형 흑연을 이형-에피택셜하게 성장시키고, 이것을 (n이 3 보다 작은) 고전자급 (high electronic grade, HEG) 그래핀으로 전환하는 확장 가능 기법에 관한 것이다. 일 구체예는 또한 가시광선 및 적외선 영역 모두에서 투명하고, 전도성을 갖는 초박막 그래핀 필름을, 예를 들어, 고상 태양 전지와 같은 다양한 적용기기의 유비쿼터스한 금속 산화물 원도우 전극을 대체하는 HEG 그래핀의 사용에 관한 것이다. 일 구체예의 성장 기법은, 유리 친화적인 (glass-friendly) 충분히 낮은 온도에서 발생하는, 촉매에 의해 유도되는 이형-에피택셜 CVD 공정에 기초한다. 예를 들어, 역학 원리만큼이나 열역학적 원리에 의해서도, 약 600 °C 보다 낮은 온도에서 시드 (seed) 촉매 층 상에 가스 상으로부터 HEG 그래핀 필름이 결정화될 수 있다.

[0042] 도 1은 일 구체예의 과정을 대략적으로 도시한 고급 흐름도이다. 도 1에서 나타난 바와 같이, 구체예들의 전반적인 기법은 기본적인 4단계의 하나로 분류될 수 있다; 적절한 후면 지지판 (back support) 상의 그래핀의 결정화 (단계 S101), 후면 지지판으로부터 그래핀의 방출 (release) 또는 결합 제거 (debonding) (단계 S103), 목표 기판 (target substrate) 또는 표면으로 그래핀의 전이 (단계 S105), 및 목표 기판 또는 표면의 제품으로의 결합 (단계 S107). 아래 더 상세하게 설명된 것처럼, S107 단계에서 언급된 제품은 중간 제품 또는 최종 생산품일 수 있다.

#### [0043] 실시예: 그래핀 결정화 기술

[0044] 일 구체예로서 그래핀 결정화 기술은, 탄화수소 가스의 "크랙킹 (cracking)"과 탄소 원자를 대면적 (예를 들어 약 1 미터 또는 그 이상)에 걸쳐서 익숙한 벌집 구조로 재조립하고 표면 촉매 경로로 이끄는 것 (leveraging)을 포함하는 것으로 생각할 수 있다. 일 구체예로서 그래핀 결정화 기술은 고온 및 상압에서 수행된다. 구체적인 공정의 상세는 이하에 상세히 기술될 것이다.

[0045] 일 구체예로서의 촉매성장법은 이형-에피택셜한 영역 상에서의 흑연 성장에 사용되는 기술과 얼마간 관련이 있다. 그래핀 결정화를 위한 촉매는 적절한 후면 지지대 상에 배치된다. 후면 지지대는, 예를 들어, 세라믹 또는 유리 제품, 지르코늄 포함 물질, 알루미늄 질화물, 실리콘 웨이퍼 등과 같은 고온 (예를 들어, 약 1000 °C 이상)을 견딜 수 있는 물질일 수 있다. 박막은 직접 또는 간접적으로 상기 후면 지지대에 배치되어, 그 표면은 상기 결정화 과정 전에 실질적으로 오염되지 않게 된다. 본 발명의 발명자는 촉매 층이 단일-기원 결정 구조를 가질 때 그래핀 결정화가 촉진되는 것을 발견하였다. 이러한 관점에서, 작은 입자들은, 그 모자이크 구조가 즉

시 그래핀 층으로 전이되기 때문에, 더 불리하다. 어떤 경우에는, 촉매 층이 적어도 상당한 부분에서 단일-기원 결정 구조를 갖는 경우에는 결정 구조의 특정 기원은 대체로 의미 없다. 실제로, 촉매에서 상대적인 입자 경계의 부재 또는 극소 존재는, 같거나 적게 그래핀 성장의 기원이 되고, 고전자급 (HEG) 그래핀이 된다.

[0046] 촉매 층 자체는, 예를 들어, 스퍼터링, 연소증착법 (combustion vapor deposition, CVD), 불꽃 열분해법 등 적절한 기법으로 후면 지지대에 배치될 수 있다. 촉매 층 자체는 적절한 금속 또는 금속 함유 물질을 포함한다. 예를 들어, 촉매 층은, 니켈, 코발트, 철, 페말로이 (premalloy, 예를 들어 니켈-철 합금, 통상 철 약 20 원자량%, 니켈 약 80 원자량%), 니켈-크롬 합금, 구리 및 이들의 조합을 포함한다. 물론, 어떤 구체예에서는 다른 금속이 사용될 수도 있다. 본 발명의 발명자는 니켈을 포함하는 촉매 층이 특히 그래핀 결정화에 유리하고 니켈-크롬 합금이 더욱 유리한 것을 발견하였다. 더 나아가, 본 발명의 발명자는 대결정 형성을 증진시키는데 최적화된 니켈-크롬 층 (종종 니크롬(nichrome) 또는 NiCr층이라 불림) 중 크롬의 양을 발견하였다. 특히, NiCr층 중 크롬이 3-15 원자량%, 바람직하게는 5-12 원자량%, 더욱 바람직하게는 7-10 원자량%인 것이 유리하다. 금속 박막 중 바나듐이 있는 경우, 대결정 성장을 증진시키는데 유리하다. 촉매 층은 상대적으로 얇거나 두꺼울 수 있다. 예를 들어, 박막 두께는 50-1000 nm, 바람직하게는 75-750 nm, 더욱 바람직하게는 100-500 nm일 수 있다. '대결정화 성장 (large crystal growth)'은 어떤 예의 경우에는 주축을 따라 수십 마이크로미터 또는 때로는 그보다 더 긴 결정을 포함할 수도 있다.

[0047] 촉매 박막이 후면 지지대에 배치된 후, 탄화수소 가스 (예를 들어,  $C_2H_2$  가스,  $CH_4$  가스 등)가 챔버에 제공되고, 챔버 내에서 촉매 박막 상에 배치된다. 탄화수소 가스는 5-150 mTorr, 바람직하게는 10-100 mTorr 압력 범위로 제공된다. 일반적으로, 압력이 높을수록, 그래핀 성장 속도가 빨라진다. 후면 지지대 및/또는 챔버 전체는, 탄화 수소 가스를 용해하거나 크랙 개방 (crack open)하도록 가열된다. 예를 들어, 후면 지지대는 600-1200 °C, 바람직하게는 700-1000 °C, 더욱 바람직하게는 800-900 °C 온도 범위까지 가열된다. 가열은 예를 들어, 단파 적외선 가열기와 같은 장치를 통하여 이루어진다. 가열은 아르곤, 질소, 질소와 수소 혼합 가스 또는 적절한 분위기 하에서 이루어진다. 다시 말하면, 탄화수소 가스의 가열은 일 구체예에서는 다른 기체를 포함하는 분위기에서 이루어질 수 있다. 어떤 구체예에서는, 순수 탄화수소 가스 (예를 들어,  $C_2H_2$ )를 사용하는 것이 바람직할 수 있고, 반면에, 다른 불활성 가스를 포함하는 탄화수소 혼합 가스 (예를 들어, Ar 포함  $CH_4$  혼합 가스)를 사용하는 것이 바람직할 수도 있다.

[0048] 그래핀은 이러한 환경 또는 다른 적절한 환경에서 성장한다. 성장을 멈추고 (촉매 내에 파묻힌 것과 달리) 촉매 표면 상의 그래핀 성장을 유지하기 위해서, 어떤 구체예는 담금질 공정을 포함할 수 있다. 담금질 과정은 예를 들어, 아르곤, 질소, 이들의 조합과 같은 불활성 기체를 이용하여 수행될 수 있다. 촉매 층 표면에서의 그래핀 성장을 촉진하기 위해서, 담금질은 매우 빠르게 수행될 수 있다. 특별히, 너무 빠른 담금질 또는 너무 느린 담금질의 경우, 촉매 층 상의 그래핀 성장이 매우 적거나 거의 없을 수 있다. 일반적으로, 후면 지지대 및/또는 기판을 몇 분 내에 900 °C로부터 700 °C 또는 그 이하로 냉각시키는 담금질이 화학 흡착 등을 통해서 양호한 그래핀 성장을 일으키는 것이 확인되었다. 이러한 관점에서, 도 2는, 몇 구체예에 따른, 탄화수소 가스의 도입, 탄소의 용해 및 몇 가지 담금질의 가능한 결과를 나타내는 구체예들의 촉매 성장 기법의 개략 예시도이다.

[0049] 그래핀 성장 공정은  $t = n \times SLG$  ( $n$ 은 불연속 단계 수이다)라는 엄격한 필름 두께 관계식을 따른다. 그래핀의 생성의 빠른 확인 및 필름 면 상의  $n$  값의 확인은 대체로 필름의 질과 균일성을 단번에 측정하는 것과 유사하다. 그래핀 시트가 원자간 힘 주사 전자 현미경 (atomic force and scanning electron microscopy)으로 관찰되더라도, 이러한 기법은 장시간과 그래핀의 오염을 초래한다. 그러므로, 일 구체예에서는 강제 촉매 표면에서 그래핀의 시인성을 증진시키는 위상차 기법을 사용한다. 이것은 금속 촉매 필름 상의 증착 표면 상의  $n$  변수값의 사상(寫像)의 관점에서 이루어진다. 이 기법은 그래핀의 대조가 그 위의 스핀 코팅 물질에 의하여 실질적으로 증진되는 것에 의존한다. 예를 들어, 널리 사용되는 UV 경화 레지스트 (예를 들어 PMMA)는 스핀 코팅, 스크린 프린팅, 그라비어 코팅 또는 다른 방법에 의하여, 시인성 필름을 연속적으로 만들기에 충분한 두께 (예를 들어 1 마이크로미터 두께)로 그래핀/금속/후면 지지대 상에 배치될 수 있다. 아래에 더욱 상세히 설명되겠지만, 고분자 레지스트를 포함하는 것은 그래핀의 최종 표면으로의 전이 이전의 박리 공정을 도울 수 있다. 즉, 그래핀의 완성 시점에 대한 표시를 제공함에 더하여, 아래에 상세히 설명되듯이, 금속 층이 방출 (release)되거나 후면 지지대로부터 결합 제거 (debonding)될 때, 고분자 레지스트는 고탄성 그래핀의 지지대를 제공할 수 있다.

[0050] 층이 너무 두껍게 (의도적 또는 비의도적으로) 성장한 경우에는, 그 층을, 예를 들어, ( $H^*$ ) 수소 원자를 이용하여 에칭하여 내릴 수 있다. 이러한 기법은 다양한 경우에 유용할 수 있다. 예를 들어, 성장이 너무 빨리, 예상

치 못하게, 평탄하지 않게 발생한 경우 등에,  $H^*$ 는 이러한 문제를 바로잡는데 사용될 수 있다. 다른 예로서, 충분한 그래핀을 성장시키기 위해서, 흑연이 형성될 수 있고, 그래핀 (graphane)이 증착될 수 있고, 그 그래핀 (graphane)은  $H^*$ 를 이용하여 바람직한 n-급 고전자급 그래핀으로 선택적으로 에칭 (etched back) 될 수 있다. 또 다른 예로서,  $H^*$ 는 전도성 영역과 비전도성 영역을 만들기 위해서 그래핀을 에칭 (etching away)하는데 사용될 수 있다. 이것은, 예를 들어, 적당한 마스크를 제공하고, 에칭을 실시한 후, 마스크를 제거하여 이루어질 수 있다.

[0051] 그래핀에 대한 이론적인 연구는 캐리어의 이동도가  $200,000 \text{ cm}^2/(\text{V} \cdot \text{s})$ 보다 클 수 있음을 알려준다. 그래핀의 이형-에피택셜 성장을 다루는 가스 상에 대한 실험적 측정 값은 저항도가  $3 \times 10^{-6} \Omega\text{-cm}$ 만큼 낮고, 이는 은 박막의 저항도보다 우수한 것이다. 이러한 그래핀 층의 면 저항은 약  $150 \Omega/\square$ 이다. 변할 수 있는 한 가지 요소는, 가장 낮은 저항도 및 면저항을 제공할 수 있는 그래핀 층의 수이고, 바람직한 그래핀의 두께는 적용 기기에 따라 달라진다. 대체로, 대부분의 기기에 적용 가능한 그래핀은 n이 1-15, 바람직하게는 n=1-10, 더욱 바람직하게는 n=1-5인 그래핀일 수 있다. n=1인 그래핀 층은 약 2.3-2.6% 전송 강하를 일으키는 것으로 확인되었다. 이러한 전송 강하는 자외선 영역으로부터 가시광선 영역을 지나 적외선 영역에까지 실질적으로 전 영역을 걸쳐 대체로 선형적으로 나타난다. 더욱이, 전송 손실은 n의 각 연속적인 (successive) 증가에 따라 실질적으로 선형으로 나타난다.

#### 도핑 기법 예

[0053] 어떤 적용 예의 경우에는  $150 \Omega/\square$ 의 면저항이 적절할 수 있더라도, 면 저항의 추가적인 감소는 다른 적용 예에서는 바람직할 수 있다. 예를 들어,  $10-20 \Omega/\square$  면저항이 어떤 적용 예에서는 바람직할 수 있다. 본 발명의 발명자는 그래핀의 도핑을 통하여 면저항을 더 낮추었다.

[0054] 이러한 관점에서, 단원자 층 두께인 경우, 그래핀은 마이크로미터 이하 수준의 탄도 전이 (ballistic transport)를 나타내고, 게이트 전압뿐만 아니라 분자 흡착질, 또는  $n = 2$  인 경우의 삽입물에 의하여 이동도의 손실 없이 과하게 도핑될 수 있다. 본 발명의 발명자는 도너(doner)/액셉터(acceptor)의 구별과 별개로, 그래핀 내에서 상자성 및 비상자성으로 명명되는 일반적으로 두 가지 종류의 도편트가 존재함을 알았다. 통상의 반도체와는 달리, 후자 타입의 불순물은 일반적으로 약한 도편트로 작용하는데 반하여, 상자성 불순물은 강한 도핑을 초래한다: 선형적인 소멸때문에, 스핀 편극 없이 불순물 상태를 국한시킨 그래핀의 디랙 (Dirac) 점 근처에서의 전자홀 (electron-hole) 대칭적 상태 밀도 (density of state, DOS)는, 가상 차이(gap)의 중심에 고정된다. 그러므로, 그래핀에서의 오염 상태는 일반적 반도체에 있는 그들 편을 구분하고 원자가 (valence) 및 전도대 (conduction bands)의 DOS는 매우 다르고 불순물 수준은 일반적으로 그 차이의 중간값에서 멀다. 페르미 (Fermi) 레벨로부터 면 수십 볼트의 정의가 명확한 도너 (또는 억셉터)의 존재를 요하는 강한 도핑 효과를 제외하지 않더라도, 불순물이 국부적인 자성을 갖는다면, 그 에너지 레벨은 Hund 교환에 의하여 대칭적으로 1 eV 단위로 더 많이 또는 더 적게 쪼개지고, 그래핀 내에 존재하는 것과 같은 Dirac 유사 스펙트라를 수반하는 이차원 시스템의 전자 구조에 강한 도핑 불순물 효과에 바람직한 상황을 제공한다. 이러한 추리는, 그래핀을 도핑하고 그 전도성을  $10^3 \text{ S/cm}$ 에서  $10^5 \text{ S/cm}$ 으로, 때로는  $10^6 \text{ S/cm}$ 까지 증진시키기 위해서 상자성 단분자와 반자성 2분자체 시스템 모두를 형성하는 분자를 선택하는 기준으로 이용된다.

[0055] 구체 예에 적용하여 사용하기 적절한 도편트의 예는 질소, 봉소, 인, 불소 화합물, 리튬, 칼륨, 암모늄 등이다. 황산화물과 같은 황 기반 도편트도 어떤 구체 예에 사용될 수 있다. 예를 들어, 유리 기판의 황화물의 존재는 유리로부터 스며나와서 그래핀 기반 층을 도핑하게 될 수 있다. 아래에 몇 가지 그래핀 도핑 기법을 더욱 상세히 나타낸다.

[0056] 도 3은 일 구체 예에 따른 실시 예 1의 그래핀 도핑 방법을 나타낸 흐름도이다. 도 3의 기법은 기본적으로 그래핀에 도핑 물질을 심는 이온 빔과 관계가 있다. 이 기법에서는, 상술한대로 그래핀이 금속 촉매 상에서 성장한다 (단계 S301). 그래핀이 그 위에 형성된 촉매는 도편트로 사용되는 물질을 포함하는 가스 (종종 도편트 가스로 칭해짐)에 노출된다 (단계 S303). 그 다음에 그래핀이 그 위에 형성된 촉매와 도편트 가스를 포함하는 챔버 내에 플라즈마가 여기된다 (단계 S305). 그 다음에 이온 빔이 그래핀에 도편트를 심기 위해서 사용된다 (단계 S307). 이와 같은 종류의 도핑에 적합한 이온 빔 기법들은 예를 들어, 미국등록특허6,602,371호, 6,808,606호 및 Re.38,358호와 미국공개특허2008/0199702호에 개시되어 있다. 이온 빔 전력은 약 10-200 eV, 바람직하게는

20-50 eV, 더욱 바람직하게는 20-40 eV일 수 있다.

[0057] 도 4는 일 구체예에 따른 실시예 2의 따른 그래핀 도핑 방법을 나타낸 흐름도이다. 도 4의 기법은 기본적으로 고상 도편트를 목표 기판에 미리 임플란트하고 (pre-implanting), 그 다음에 그래핀이 수용 기판 (receiving substrate)에 적용되는 시점에 고상 도편트를 그래핀으로 옮겨지게 한다. 이 기법에서는 그래핀은 상술된 대로 금속 촉매 상에서 성장한다 (단계 S401). 수용 기판은 고상 도편트를 그 안에 포함할 수 있도록 미리 조립된다 (step S403). 예를 들어, 고상 도편트는 유리 내에서 포뮬레이션에 녹음으로서 포함될 수 있다. 도편트는 용융 유리 내에 약 1-10 원자%, 바람직하게는 1-5 원자%, 더욱 바람직하게는 2-3 원자%로 포함될 수 있다. 그래핀은 아래에 상세히 설명할 예들 중 하나를 사용하여 수용 기판에 적용될 수 있다 (step S405). 그 다음에, 수용 기판 내의 고상 도편트는 그래핀으로 이전된다. 그래핀의 증착에 사용되는 열은 도편트가 형성되는 그래핀 층으로 이전하도록 한다. 마찬가지로, 추가적인 도핑 필름이 유리 상에 포함될 수 있고, 그 위의 도편트는 열확산에 의하여 이전되고  $n \geq 2$ 인 도핑 그래핀 층을 형성한다.

[0058] 이온 빔은 일 구체예에서 유리에 직접적으로 도편트를 심는데 사용될 수 있다. 이온 빔 전력은 약 10-1000 eV, 바람직하게는 20-500 eV, 더욱 바람직하게는 20-100 eV일 수 있다. 중간층이 도핑되고 그래핀에 불순물이 제공될 때는, 이온 빔 전력은 약 10-200 eV, 바람직하게는 20-50 eV, 더욱 바람직하게는 20-40 eV일 수 있다.

[0059] 도 5는 일 구체예에 따른 실시예 3의 그래핀 도핑 방법의 개략 예시도이다. 도 5의 예시적 기법은 고상 도편트 (507)을 금속 촉매 층 (503)에 미리 임플란트하고 (pre-implanting), 그 다음에 그래핀이 형성됨에 따라 고상 도편트 (507)를 촉매 층 (503)을 통해서 이전시킴으로써, 촉매 층 (503)의 표면에 도핑된 그래핀 (509)을 제조하는 것에 관한 것이다. 더욱 구체적으로, 이 예시적 기법에서, 촉매 층 (503)은 후면 지지대 (505) 상에 배치된다. 촉매 층 (503)은 그 안에 고상 도편트 (507)를 포함한다. 다시 말하면, 촉매는 그 벌크 내에 고상 도편트 원자를 갖는다 (예를 들어, 약 1-10 원자량%, 바람직하게는 약 1-5 원자량%, 더욱 바람직하게는 약 1-3 원자량%). 탄화 수소 가스 (501)는 고온에서 가까이 형성된 촉매 층 (503)으로 제공된다. 촉매 층 (503) 내의 고상 도편트 (507)는, 그래핀의 결정화가 이루어질 때, 고온에 의해 그 표면 외부 쪽으로 이동하게 된다. 도편트가 표면에 도달하는 비율은 촉매의 두께와 온도의 함수이다. 결정화가 끝나고 즉시, 도핑된 그래핀 (509)는 촉매 층 (503) 표면에 형성된다. 도핑된 그래핀 (509)의 형성 이후에, 이제는 촉매 층 (503)은 내부에 고상 도편트를 거의 또는 전혀 갖지 않게 된다. 이러한 기법의 한 가지 장점은, 퀸칭률 공정 (quenching rate process)에서 사용되는 반응 라디칼 뿐만 아니라 금속 표면 온도, 부분 압력 및 증착 가스 종의 체류 시간을 신중하게 변화 시킴으로써 초박막 성장을 제어할 수 있는 잠재력과 관련이 있다.

[0060] 이러한 예들의 도핑 기법은 단독으로 사용될 수도 있고, 다른 기법들과 조합되어 사용될 수도 있다. 또한, 어떤 구체예는, 특정 기법을 1회 사용하거나, 반복적으로 사용하거나, 하나 이상의 기법을 조합적으로 사용함에 따라서, 단일 도편트 물질을 포함할 수도 있고, 복수의 도편트 물질을 포함할 수도 있다. 예를 들어, p-타입 및 n-타입 도편트들이 구체예에서 사용 가능하다.

[0061] 도 6은 일 구체예에 따른 그래핀 도핑의 시간에 따른 온도를 나타낸 그래프이다. 위에서 언급된대로, 냉각은 예를 들어 비활성 가스를 이용하여 수행될 수도 있다. 일반적으로, 역시 위에서 언급된대로, 일 구체예에서 고온은 약 900 °C일 수 있고, 저온은 약 700 °C일 수 있고, 냉각은 몇 분 동안 이루어질 수 있다. 도 6에 나타난 바와 같이, 동일한 가열/냉각 곡선 (profile)은 그래핀이 도핑되는지에 무관하게 사용될 수 있다.

#### 0062] 그래핀 방출 (release) / 결합 제거 (debonding) 및 이전 기법예

[0063] 그래핀이 이형-에피택셜 성장을 하면, 예를 들어, 중간 또는 최종 결과물로 병합되는 기판상으로 위치하기 전에, 금속 촉매 및/또는 후면 지지대로부터 방출 또는 결합 제거될 수 있다. 일 구체예에 따라 성장 기판부터 에피택셜 필름을 리프팅 (lifting)하기 위해서 다양한 과정이 결합될 수 있다. 도 7은 일 구체예에 따른 그래핀 방출 또는 결합 제거에 유용한 적층예를 나타낸 것이다. 도 7에 따르면, 일 구체예에서, 추가적인 방출 층 (701)이 후면 지지대 (505) 및 촉매 층 (503) 사이에 제공될 수 있다. 방출 층 (701)은 예를 들어, 산화 아연 (ZnO 또는 적합한 화학양론)이거나 이를 포함할 수 있다. 그래핀 (509)/금속 촉매 층 (503)/방출 층 (701) 적층이 형성된 기판 (505)은, 스핀 코팅, 메니스커스 (meniscus) 흐름을 통한 제조 등으로 (몇 마이크론 두께의) 두꺼운 고분자 과도코팅 (overcoat) 층 (703)이 형성될 수 있고, 이는 고쳐질 수 있다. 상기 암시된 대로, 이 고분자 층 (703)은, 박리 (lift-off) 및/또는 결합 제거, 초유연 그래핀 박막의 연속 유지 과정에서, 그래핀의 기본 골격 또는 지지대로 작용할 수 있고, 그래핀 필름의 움츠러짐, 주름짐 등의 가능성을 감소시킨다.

- [0064] 상기 암시된 바와 같이, PMMA는 위상차에 의하여 그래핀을 보이게 하고 박리 과정 전 및/또는 박리 과정 동안 지지대로 작용하는 고분자로 사용될 수 있다. 하지만, 그래핀의 물성과 매칭될 수 있는 물리적 및 화학적 물성을 갖는 넓은 범위의 고분자는, 어떤 구체예에서는 방출 전이상 (transfer phase) 뿐만 아니라, 지지대 상 동안 사용될 수 있다. 박리 작업은, 흑연으로부터 화학적으로 박리될 수 있는 그래핀 필름 실험을 통하여, 주된 에피택셜 성장 가지 (main epitaxial growth branch)와 동시에 진행될 수 있다.

- [0065] 층 방출은, 고분자층이 배치되어 있는 모(母)기판으로부터 그래핀/금속을 화학적으로 결합 제거하는 것을 포함 할 수 있다. 예를 들어, 산화 아연 방출 층의 경우, 식초 (vinegar) 세정은 그래핀의 방출을 유발할 수 있다. 본 발명의 발명자가 금속 층과 함께 이탈되는 것을 발견하였기 때문에, 산화 아연 방출 층의 사용은 이점이 있다. 이는, 층과 입자들로 내부적으로 연결되어 형성된 산화 아연 방출 층에 의하여 야기되는 짜임(texturing)의 결과이다. 이것은 후에 층을 제거할 필요를 감소 (때로는 소멸)시킨다.

- [0066] 어떤 박리/결합 제거 및 이전 기법은 기본적으로 원 기판을 재사용 가능한 에피택셜 성장 시판으로 간주한다. 이와 같이, 에피택셜하게 성장한 (최상층의 고분자와 함께) 그래핀으로부터 금속 층을 깎아내거나 용해 시켜 내기 위한 선택적 에칭이 해당 구체예에서 요구될 수 있다. 그러므로, 어떤 구체예에서는 방출 층이 사용되는지와 무관하게 층이 에칭 제거될 수 있다. 예를 들어, 적절한 에칭 물질 (etchant)은 염산, 인산 등의 산을 포함할 수 있다.

- [0067] 최종 수용 유리 기판은 그래핀 층을 수용하기 위하여 준비될 수 있다. 예를 들어, 일 예로 랭뮤어-브로젯 산으로부터 얻는 랭뮤어-브로젯 필름 (Langmuir Blodgett film)이 유리 기판에 적용될 수 있다. 최종 수용 기판은 대신 또는 부가적으로, 예를 들어, 후자가 그래핀을 수용하도록 하는 실리콘 기반 고분자 등의 부드러운 그래피노필릭 (graphenophilic) 층으로 코팅될 수 있다. 이는 전자적 결합을 확실하게 하는 데 도움이 되어, 이전 과정에서 그래핀의 이전을 우선적으로 이뤄낸다. 목표 기판은, 기판의 표면 에너지를 증가시켜 그래핀을 더 수용 가능하도록 만들도록, 부가적 또는 대체적 (alternatively)으로 UV 복사에 노출될 수 있다.

- [0068] 일 구체예에서 그래핀은 브랜켓 스템핑 (blanket stamping) 및/또는 압연 (rolling)을 통하여 적용될 수 있다. 이러한 공정은 그래핀을 미리 성장시키고 금속 캐리어 상에 화학흡착하도록 하여 접촉 압력에 의하여 수용 유리 상에 이전되도록 한다. 도 8은 일 구체예에 따른 목표 (target) 유리 기판 상에 그래핀을 배치하는데 사용 가능한 적층 장치의 개략도이다. 이러한 관점에서, 도 8은, 압력을 가하고 그래핀 (509)와 고분자 층 (703)이 목표 기판 (801)으로 합착되도록 하는 상하 롤러 (803a 및 803b)을 보여준다. 상기 언급된 대로, 목표 기판 (801)은, 합착을 형성하여 배치된 실리콘 함유 또는 다른 그래피노필릭 층을 갖는다. 고분자 층 (703)은 최외각층으로 적용되고, 그래핀 층 (509)은 목표 기판 (801)에 근접 (또는 직접 그 위에)할 수 있다. 어떤 구체예에서는, 하나 또는 그 이상의 층이 그래핀의 적용 전에 기판 상에 제공될 수 있다.

- [0069] 그래핀이 목표 기판에 배치되면, 고분자 층은 제거된다. 일 구체예에서 고분자는 적절한 용매로 용해될 수 있다. PMMA같은 감광성 물질이 사용되는 경우, UV 광 노출을 통하여 제거될 수 있다. 물론 다른 제거 기법이 적용될 수도 있다.

- [0070] 상술된 에칭 물질 (etchant)를 사용하는 등의 일 구체예에서 그래핀이 목표 기판에 적용된 후에 층은 에칭 제거 (etching off)될 수 있다. 에칭 물질의 선택은 그래핀 밑의 층의 존재 또는 부재에 따라 결정될 수 있다.

- [0071] 어떤 구체예는 그래핀 층 아래의 금속 층을 박막을 더 직접적으로 전기화학적으로 양극 처리 (anodize)한다. 그러한 구체예에서는, 아래의 금속이 원 기판에 여전히 결합하고 있지만 투명 산화물로 양극 처리되기 때문에, 그래핀 자체는 음극 (cathode)으로 작용할 수 있다. 그러한 구체예는, 하나의 단계에서 기본적으로 박리 제거 (lift-off) 및 이전 공정을 수행함으로써 고분자 과도 코팅의 사용으로 우회 사용되기도 한다. 하지만, 전기화학적인 수단에 의한 양극 처리는 그래핀의 전기적 성질에 영향을 미칠 수 있어 보정이 필요하다. 어떤 구체예에서는, 그래핀 아래의 층은 이를 투명하게 만드는 다른 방법으로 산화처리될 수 있다. 예를 들어, 전도성 산화물이 그래핀 기반 층을 기판, 반도체 또는 다른 층에 결합 (link)하는데 사용될 수 있다. 이러한 관점에서, 코발트, 코발트-크롬 합금, 니켈-크롬-코발트 및/또는 이와 같은 것들이 산화될 수 있다. 어떤 구체예에서는 이것은 그래핀의 박리 제거, 이전, 조작 및 그래핀의 사전 처리의 필요를 줄일 수 있다.

- [0072] 그래핀은 접착제 또는 테이프 같은 물질을 사용하여 들려질 수 있다. 접착제는 목표 기판에 위치될 수 있다. 그래핀은 압력의 적용에 이어서 테이프 쪽보다 더 강하게 기판에 접착하도록 하여 목표 기판으로 이전될 수 있다.

## [0073] 반응기 설계 예

일반적인 샤워헤드형 반응기는, 반응성 가스를 일률적으로 두 번째 평행 평면 가열된 표면 위로 더 또는 덜 제조하는 관통형 또는 다공성 평면 표면을 갖는다. 그러한 배열은 설명된 이형-에피택셜 기법을 사용하여 그래핀 성장에 사용될 수 있다. 샤워헤드형 반응기는 대형 사각 초연성 (ultra-smooth) 유리 또는 세라믹 기판 공정에 유리하다. 기본적인 샤워헤드형 반응기의 개념도 및 플레넘 디자인 (plenum design)의 부분 확대도가 도 9이다. 다시 말하면, 도 9는 일 구체예에 따른 고전자급 (HEG) 그래핀 증착에 적합한 반응기의 단면 개략도이다. 반응기는 도입 및 배출구 (inlets and outlets)를 갖는 몸체 부분 (901)을 포함한다. 더 구체적으로, 가스 도입부 (903)는 최상부 및 반응기의 몸체 부분 (901)의 수평 중심 부근에 제공된다. 가스 도입부 (903)은 가스를 하나 이상의 출처로부터 받아들이고, 예를 들어, 탄화수소 가스, 이형-에피택셜 성장 동안 주변을 형성하는 데 사용되는 가스, 담금질 가스 등을 포함하는 다양한 가스가 제공될 수 있다. 가스의 흐름 및 유동은, 샤워헤드 (907)의 확대도를 참고하여 아래에 상세히 설명된다. 복수의 배출부 (905)가 반응기의 몸체 부분 (901)의 바닥에 제공된다. 도 9에서, 일 구체예에서, 2개의 배출부 (905)는 반응기의 몸체 부분 (901)의 주변부에 가까이 제공된다. 즉, 배출 가스가 가스 도입부 (903)에 의하여 제공되어, 일반적으로 실질적으로 몸체 부분 (901) 전체를 통하여 흐른다. 어떤 구체예에서는 더 많거나 적은 배출부 (905)가 제공된다 (예를 들어, 더 많은 배출부 (905)가, 반응기의 몸체 부분 (901)의 대략적인 수평 중심 부근, 반응기의 몸체 부분 (901)의 상부 또는 옆면 등에 제공된다).

후면 지지대 (909)는 세정될 수 있고, 어떤 구체예에서는 로드-로크 매커니즘 (load-lock mechanism)에 의하여 반응기로 도입되기 전 (예를 들어, 물리적 증기 증착 또는 PVD, 스퍼터링, CVD, 불꽃 열분해 등을 통하여) 그 위에 배치된 촉매 박막을 가질 수 있다. 후면 지지대 기판 (909)의 표면은 (RTA 히터, 단파 IR 히터, 또는 기판 및/또는 그 위의 층을 필수적으로 챔버 전체의 가열 없이 유도 가열이 가능한 다른 적합한 히터를 사용하여) 제어 가능한 온도 수준 및 균일성까지 빠르게 가열될 수 있고, 상기 온도 및 균일성은 (i) 금속 필름이 결정화되고 활성화되도록 하고 (ii) 그 표면 상에 가스 상 전구체로부터 실질적으로 균일한 그래핀의 우선적인 증착 및 제어 가능한 두께를 제공한다. 히터는 촉매율 (catalyst ratio)의 증착 속도/(온도\*두께) 파라미터를 계산하기 위해서 제어 가능할 수 있다. 후면 지지대 (909)는 R 방향으로 반응기를 통하여 이동하거나 샤워헤드 (907) 아래에 고정되어 있을 수 있다. 샤워헤드 (907)는 하나 이상의 냉각제 도입/배출부 (913)에 의한 냉각류 (cooling fluid) 또는 냉각 가스를 사용하여 냉각될 수 있다. 대략적으로, 도 9 확대도에 나타난 바와 같이, 플레넘 디자인 (plenum design)은 샤워헤드 (907)의 바닥에 몇 밀리미터 정도의 폭을 갖는 복수의 간극을 포함한다.

천장 틈 ( $H_c$ )의 변화 또는 샤워헤드 (907)의 바닥 표면과 후면 지지대 기판 (909)가 움직이는 상층 표면 사이의 높이는 몇 가지 효과를 갖는다. 예를 들어, 챔버 부피와 표면-부피 비는 수정될 수 있고, 이는 가스 체류 시간, 소모 시간, 방사 속도 (radial velocities)에 영향을 미친다. 체류 시간의 변화는 가스 상 반응에 큰 영향을 미친다. 도 9에 나타난 바와 같은 냉각된 표면의 아래 뜨거운 표면이 있는 샤워헤드의 배치는, 수백 Torr와 같은 고압에서 작동되는 경우 베나드 (Benard) 자연 대류의 잠재력을 갖고, 그러한 경향은 Rayleigh 수 (자유 대류 또는 자연 대류로 알려진 부력 유도 흐름; 흐름, 열이동 임계 값을 초과하는 경우에 대류를 주로 형성하는 것과 관계된 무차원 수)를 통한 높이에 영향을 강하게 받는다. 따라서, 천장 틈 ( $H_c$ )는, 기판 전극의 조정 가능한 마운트를 제공함에 의한 간단한 하드웨어적 변화일 수 있고, 그래핀의 에피택셜한 성장에 영향을 미친다.

도 9의 구체예가 필수적으로 반응기 내에 플라즈마를 작동하는 것은 아니다. 이는 수정 (crystalline) 필름 성장 매커니즘이 (일반적으로 촉매 표면에서만 일어나는) 표면 수착 (收着)에 의한 이형-적층성장 (epitaxy)에 의하기 때문이다. 플라즈마 상으로부터의 성장은 대부분 비결정형 필름을 형성하고, 거대 입자나 필름의 질을 악화시키는 분말을 형성하고, 1 내지 10 층 필름에 해로운 필 훌을 만드는 것으로 알려져 있다. 대신, 어떤 구체예는 흑연 (예를 들어 단결정 흑연)의 형성, 이를 그래핀 (graphane)으로 애칭하는 것 (예를 들어, n 값의) 및 그래핀 (graphane)을 그래핀(graphene) (예를 들어, 고전자급 그래핀)으로 바꾸는 것과 관계가 있다. 물론, 원위치 말단 기법은 피드-백 파라미터로 수행될 수도 있다.

어떤 구체예에서는 이온 빔 원(原)이 라인 내에 위치할 수도 있고, 상술한 기법 예들에 따라 도핑을 수행하기 위해서 도 9와 같이 반응기 외부에 있을 수도 있다. 그러나, 어떤 구체예에서는 이온 빔 원이 반응기의 몸체 부분 내에 있을 수도 있다.

도 10은 일 구체예에 따른 촉매 CVD 성장, 박리 및 전이 과정의 예를 나타내는 흐름도이다. 도 10의 공정 예는 후면 지지대 유리가, 일반적인 유리 조사 방법 (단계 S1002) 및 세정 (단계 S1004)을 사용하여 조사되면서 시작된다. 이후에 후면 지지대 유리는 이온 빔 세정 또는 플라즈마 표백 (ashing) 등을 사용하여 세정된다 (단계

S1006). 금속 촉매와 같은 촉매는, PVD를 사용하여 후면 지지대 상에 배치된다 (단계 S1008). 단계 S1006의 세정 공정은 그래핀 코팅기/반응기 내에서 수행될 수도 있다. 다시 말하면, 그 위에 형성된 금속 촉매 박막이 있거나 없는 후면 지지대 유리는 단계 S1006 이전에 그래핀 코팅기/반응기 내에 장착될 수 있고, 이는 금속 촉매 층이 그래핀 코팅기/반응기 내에서 중착되는지 또는 그전에 중착되는지에 따라 결정된다. 그 다음에 n-층 그래핀의 촉매 중착이 이루어질 수 있다 (단계 S1010). 어떤 구체예에서는 그래핀이 수소 원자 ( $H^*$ ) 조사에 의하여 에칭되고, 적용 기기에 따라 그래핀이 도핑될 수도 있다 (단계 S1012). 충분한 그래핀이 중착되었는지,  $H^*$  에칭이 충분한지에 의하여 그래핀 형성의 종료가 결정된다 (단계 S1014). 그래핀 형성을 중단하기 위해서 금속 담금질 공정이 사용되고, 그래핀이 형성된 후면 지지대 유리는 반응기/코팅기를 나온다 (단계 S1016). 이 지점에서 육안 조사가 수행될 수도 있다.

[0080] 그래핀 형성에 이어, 그래핀의 이전에 유용한 고분자가, 스펜 코팅, 블레이드 코팅 등의 기법으로 그래핀 상에 배치된다 (단계 S1018). 불가결한 색변경이 일어났는지 여부를 확인하는 조사가 이루어질 수도 있다. 만약 색변경이 일어났다면, 고분자가 열, UV 방사 등으로 보정하고 (단계 S1020) 다시 방사할 수 있다. 금속 촉매는 하방 에칭 (under-etching)될 수도 있고, 박리 (단계 S1024)를 위한 그래핀을 준비하기 위해서 방출될 수도 있다 (단계 S1022).

[0081] 박리가 이루어지면, 고분자와 그래핀을 확인한 후, 남아있는 에칭 물질 및/또는 고분자를 제거하기 위해서 세정 할 수도 있다 (단계 S1026). 이 시점에서 추가적인 확인 공정이 수행될 수도 있다. 계면활성제가 적용될 수도 있고 (단계 S1028), 고분자에 편이 최소화되고 (단계 S1030), 막 (membrane)이 이러한 편들에 의하여 튀게 된다 (단계 S1032). 박리 공정은 완성되고, 그래핀이 수용 기판으로 이전될 준비가 된다.

[0082] 수용 기판이 클린룸에 준비된다 (단계 S1034). 수용 기판의 표면은, 표면 에너지를 올리고 그래피노필릭 (graphenophilic) 코팅 등을 적용하기 위해서 UV광에 노출하여 기능화될 수 있다 (단계 S1036). 그래핀/고분자 막 (membrane)은 주(主) 기판으로 이전될 수 있다 (단계 S1038).

[0083] 이전이 완료된 직후, 그래핀이 형성된 수용 기판 및 이에 붙어있는 고분자는 고분자를 제거하기 위해서 모듈로 제공된다 (단계 S1040). 이는 UV광, 열, 화학물질 등에 노출되어 수행될 수 있다. 그 다음에 그래핀이 형성된 기판 및 적어도 부분적으로 용해된 고분자가 과량의 물 또는 다른 증기 물질로 세정되고 (단계 S1042) 건조될 수 있다 (단계 S1044). 필요에 따라 고분자 제거 공정은 반복될 수 있다.

[0084] 고분자 제거 공정에 이어서, 기준 4 포인트프로브를 사용하여 기판 상의 그래핀의 면적항이 측정될 수 있다 (단계 S1046). Tvis 등의 광투과도 역시 측정될 수 있다 (단계 S1048). 중간 또는 최종 제품이 기준 품질을 만족하면, 포장될 수 있다 (단계 S1050).

[0085] 이런 기법을 사용하여 샘플 필름을 준비하였다. 샘플 필름들은 15500 S/cm의 높은 전도도와 500-3000 nm 파장 범위에서 80% 이상의 투명도는 나타내었다. 더욱이 화학적 및 열적 안정성이 뛰어났다. 도 11은 일 구체예에 따라 제조된 그래핀 예의 이미지이다. 도 11의 이미지는 이형-에피택설 성장 그래핀의 퍼멀로이 (permalloy) 박막으로부터의 박리를 강조한다.

#### [0086] 그래핀 포함 기기예

[0087] 상술된 바와 같이, 그래핀 기반 층은 다양한 기기 및/또는 전자장치에 널리 사용될 수 있다. 그러한 기기 및 전자장치에 있어서, ITO 및/또한 다른 전도성 층은 그래핀 기반 층으로 대체될 수 있다. 그래핀을 포함하는 기기의 제조는 전형적으로 금속 접촉의 제조와 관련이 있고, ITO같은 반도체, a-Si 및 CdTe와 같은 태양 전지 반도체를 퇴화시킬 것이다.

[0088] 0 밴드 갭 및 브륄앵 (Brillouin) 영역의 K 지점에서의 밀도 소멸 상태 (vanishing density of states)에도 불구하고, 독립 그래핀은 금속성 거동을 나타낸다. 그러나, 금속성, 반도체성 또는 절연 기판 상의 흡착은 그 전기적 성질을 바꿀 수 있다. 이를 보완하기 위해서, 기기 및/또는 전자장치에 있어서, 추가적으로 또는 대신하여, 인접 반도체 층을 따라 그래핀 기반 층이 도핑될 수 있다. 즉, 어떤 구체예에서는 그래핀 기반 층이 n-타입 반도체 층에 인접한다면, 그래핀 기반 층은 n-타입 도편트로 도핑될 수 있다. 또한, 어떤 구체예에서, 그래핀 기반 층이 p-타입 반도체 층에 인접한다면, 그래핀 기반 층은 p-타입 도편트로 도핑될 수 있다. 물론, 원뿔형 꼭지점 때문에 그래핀 내 페르미 레벨 (Fermi level)의 증가는 밀도법함수이론(density functional theory, DFT)을 사용하여 모델링될 수 있다. 밴드 갭 계산은 금속/그래핀 계면이, 일명 화학증착과 물리적 흡착

두 가지 큰 류로 분류된 수 있음을 보여준다. 후자의 경우, 증가 (또는 하락)는 전자 (또는 정공)이 금속에 의하여 그래핀에 재공되었다는 것을 의미한다. 그러므로, 기기에 따라 그래핀에 접하도록 사용되는 금속 또는 TCO를 예상할 수 있게 해준다.

[0089] 하나 이상의 그래핀 기반 층을 사용하는 첫 번째 전자장치의 예는 태양 광전지 장치이다. 이 예들은 전(前)면 전극과 후면 전극을 포함한다. 그래핀 기반 층은 단순히 전형적으로 사용되는 ITO를 대체할 수 있다. 예를 들어, 광전지 장치는 미국등록특허 6,784,361호, 6,288,325호, 6,613,603호 및 6,123,824호와 미국공개특허 2008/0169021호, 2009/0032098호, 2008/0308147호 및 2009/0020157호와 출원번호 12/285,374호, 12/285,890호 및 12/457,006호에 개시되어 있다.

[0090] 대신 또는 추가적으로, 도핑된 그래핀 기반 층은 인접하는 반도체 층에 맞추어 포함될 수 있다. 도 12는 일 구체예에 따른 그래핀 기반 층을 포함하는 태양 광전지 장치의 단면 개략도이다. 도 12의 예에서, 유리 기판 (1202)이 제공된다. 제한이 아닌 일 예로서, 유리 기판 (1202)은 미국 특허 출원번호 11/049,292호 및/또는 11/122,218호에 개시된 유리 기판일 수 있다. 유리 기판은 태양 전지의 효율을 향상시키기 위해 나노 직물일 수도 있다. 투광도 향상을 위하여 반사방지 코팅 (1204)이 유리 기판 (1202)의 외부 표면에 제공될 수 있다. 반사방지 코팅 (1204)은, 산화 실리콘 반사 방지 코팅과 같은 단일 층 반사 방지 (single-layer anti-reflective (SLAR)) 코팅일 수도 있고, 다중 층 반사 방지 (multi-layer anti-reflective (MLAR)) 코팅일 수도 있다. 반사방지 코팅은 적절한 기법을 사용하여 제공될 수 있다.

[0091] 도 12의 예에서 나타난 것과 같이, 후면 전극 장치의 경우, 하나 이상의 흡수 층 (1206)이 유리 기판 (1202)의 반사 방지 코팅 (1204) 반대 면에 제공될 수도 있다. 흡수 층 (1206)은 제 1 반도체와 제2 반도체 사이에 끼어 있을 수 있다. 도 12의 예에서는, 흡수 층 (1206)은 유리 기판 (1202)에 가까운 n-타입 반도체 층 (1208)과 유리 기판 (1202)에서 면 p-타입 반도체 (1210) 사이에 끼어 있다. 알루미늄 또는 다른 적당한 물질인 후면 (1212)이 제공될 수 있다. 반도체 (1208)와 유리 기판 (1202) 사이 및/또는 반도체 (1210)와 후면 (1212) 사이에 ITO 또는 다른 전도성 물질을 제공하는 대신, 제1 및 제2 그래핀 기반 층 (1214 및 1216)이 제공될 수 있다. 그래핀 기반 층 (1214 및 1216)은 각각 인접 반도체 층 (1208 및 1210)에 맞추기 위해 도핑될 수 있다. 도 12의 예에서, 그래핀 기반 층 (1214)는 n-타입 도핀트로 도핑될 수 있고, 다른 그래핀 기반 층 (1216)은 p-타입 그래핀 기반 층으로 도핑될 수 있다.

[0092] 그래핀을 직접 직조하는 것이 어렵기 때문에, 추가 층 (1218)이 유리 기판 (1202)와 제1 그래핀 기반 층 (1214) 사이에 제공될 수 있다. 하지만, 그래핀이 매우 유연하기 때문에, 일반적으로 그래핀은 그것이 놓여지는 표면을 따라 형성된다. 따라서, 추가 층 (1218)을 형성하고 이전하거나 순응적인 그래핀 기반 층 (1214)에 반사시킬 수 있다. 이러한 관점에서, 추가 직조 층 (1218)은 아연 도핑 산화 주석을 포함할 수 있다 (ZTO). 어떤 구체예에서는 하나 혹은 두 개 모두의 반도체 (1208 및 1210)은 고분자 전도성 물질로 대체될 수 있다.

[0093] 그래핀은 본질적으로 적외선 부근 및 중간 영역에서 투명하기 때문에, 대부분의 투과성 장파장 방사는 통과하고, 단일 및 텐덤 연결형 태양 전지 모두의 i 층으로 캐리어를 제공한다. 이것은, 몇 % 정도의 효율 증가와 함께 그래핀 기반 층에서는 후면 직조가 불필요한 것을 나타낸다.

[0094] 스크린 프린팅, 증발법 및 소결 기법과 고온 CdCl<sub>2</sub> 처리는 CdS/CdTe 태양전지 이형접합에 현재 사용되고 있다. 이러한 전지는 0.8보다 큰 필 팩터 (fill factors)를 갖는다. 하지만, 연속 저항 (series resistance, Rs)은 인위 결과를 제한하는 효율이다. Rs에서, 그 꼭대기에서의 CdTe와 흑연 기반 접촉으로 결합된 CdS 층과 개별 소자의 면 저항으로부터 분배된 부분이 있다. 양호한 이형 접합 특성을 보존하지만, 하나 이상의 그래핀 기반 층의 사용은 Rs에 대한 양쪽의 기여를 감소시키는데 도움을 준다. 양쪽 전면 및 후면 접속 배치를 위한 태양 구조에 그래핀을 포함시킴으로써, 실질적 효율 상승이 달성될 수 있다.

[0095] 어떤 구체예는 직렬형 태양전지에 관한 것인데 반하여 어떤 구체예는 단일 접합 태양 전지에 관한 것일 수도 있다. 어떤 구체예는 CdS, CdTe, CIS/ CIGS, a-Si, 및/또는 다른 타입 태양전지일 수 있다.

[0096] 하나 이상의 그래핀 기반 층을 구체화할 수 있는 또 다른 예시적인 실시예는 터치 패널 디스플레이이다. 예를 들어, 터치 패널 디스플레이의 ITO 또는 다른 도전층을 포함하는 전기 용량 또는 저항성 접촉 패널 디스플레이일 수 있다. 예를 들어, 미국등록특허 7,436,393호, 7,372,510호, 7,215,331호, 6,204,897호, 6,177,918호 및 5,650,597호와 미국특허 출원번호 12/292,406호를 참고할 수 있다. ITO 및/또는 다른 전도성 층은 터치 패널에서 그래핀 기반 층으로 대체될 수 있다. 도 13은 일 구체예에 따른 그래핀 기반 층을 포함하는 터치 스크린의 단면 개략도이다. 도 13은 기본적인 디스플레이 (1302)를 포함하며, 그것은 일 구체예에서 LCD, 플라스마 또는

기타 평판 디스플레이일 수 있다. 광학적으로 투명한 접착제 (1304)는 얇은 유리 시트 (1306)에 디스플레이 (1302)를 연결한다. 변형 가능한 PET 포일 (1308)은 도 13의 실시예에서 최상단층으로서 제공된다. 다수의 기둥 모양 스페이서 (1310)과 가장자리 밀봉 (1312)에 의하여 PET 포일 (1308)이 얇은 기판 유리 (1306)의 상부 표면으로부터 이격된다. 제1 및 제2 그래핀 기반 층 (1314 및 1316)은 각각 디스플레이 (1302)에 더 가까운 PET 포일 (1308) 및 PET 포일 (1308)을 마주보는 표면상의 얇은 유리 기판 (1306)에 제공될 수 있다. 하나 또는 양쪽 그래핀 기반 층 (1314 및 1316)은, 이온 빔 및/또는 레이저 에칭에 의해 패턴화될 수 있다. PET 포일 위의 그래핀 기반 층은 그 성장 위치로부터 PET 포일 자체를 사용하는 중간 제품으로 이동될 수 있다. 다시 말하면, PET 포일은 그래핀 박리 및/또는 이동 시에 감광제 (photoresist) 또는 다른 물질 대신에 사용될 수 있다.

[0097] 그래핀 기반 층의 약 500  $\Omega/\square$  보다 낮은 면 저항은 도 13에 나타난 것과 유사한 구체예에서 허용되고, 약 300  $\Omega/\square$  보다 낮은 면 저항은 그래핀 기반 층에 유리하다.

[0098] 전형적으로 디스플레이 (1302)에서 발견되는 ITO는 하나 이상의 그래핀 기반 층으로 대체될 수 있다. 예를 들어, 디스플레이 (1302)가 LCD 디스플레이인 경우, 그래핀 기반 층은 컬러 필터 기판 위의 공통 전극 (common electrode)으로 제공될 수 있고, 소위 TFT 기판 위의 패턴화된 전극으로서 제공될 수 있다. 물론, 도핑되거나 도핑되지 않은 그래핀 기반 층은 개별적 TFT의 디자인과 제작과 관련하여 사용될 수도 있다. 유사한 배열은 플라스마 및/또는 다른 평면 패널 디스플레이와 관련하여 제공될 수도 있다.

[0099] 그래핀 기반 층은 전도성 데이터/버스 라인, 버스 바, 안테나 및/또는 기타 등을 생성하기 위해서도 사용될 수 있다. 그러한 구조는 유리 기판, 실리콘 웨이퍼 기타 등등 위에 형성되거나 적용될 수 있다. 도 14는 일 구체예에 따른 전도성 데이터/버스라인의 제조 방법의 흐름도이다. 단계 S1401에서, 그래핀 기반 층은 적절한 기판 상에 형성된다. 임의선택적 단계, 단계 S1403에서, 보호층은 그래핀 기반 층 위에 제공될 수 있다. 단계 S1405에서, 그래핀 기반 층은 선택적으로 제거 또는 패턴화 된다. 이 제거 또는 패턴화는 레이저 에칭에 의하여 수행될 수 있다. 그러한 경우에, 레이저의 해상도 (resolution)가 충분히 미세한 경우에는 보호층의 필요는 감소할 수 있다. 선택적 또는 추가적으로 에칭은 이온 빔/플라즈마 노출 처리에 의하여 수행될 수 있다. 또한, 상술한 바와 같이, H<sup>+</sup>가 고온 필라멘트와 관련하여 사용될 수 있다. 에칭을 위해 이온 빔/플라즈마 처리가 사용될 때, 보호층은 바람직할 수도 있다. 예를 들어, 감광성 재료는 관심 그래핀 영역을 보호하기 위해 사용될 수 있다. 감광선 재료는 단계 S1403에서 스픬 코팅 등으로 적용될 수 있다. 그러한 경우에, 또 다른 임의선택적 단계 S1407에서, 임의선택적 보호층은 제거된다. 예를 들어, UV 방사에 대한 노출은 적절한 감광제에 있어 사용될 수 있다. 개시되지 않은 하나 이상의 단계에서, 전도성 그래핀 기반 패턴은 (예를 들면, 상기에 기술된 그것들과 같은) 적절한 기법을 사용하여, 그것은 그 위에 이미 형성되지 않은 경우에는 중간 또는 최종 제품에 이전될 수 있다.

[0100] 어떤 구체예에서는 그래핀 기반 층이 에칭 또는 제거되지만, 어떤 구체예에서는 단지 그래핀 기반 층의 전도도를 변화시킬 수 있다. 그러한 경우에, 그래핀의 일부 또는 전부는 제거되지 않을 수 있다. 그러나, 전도도가 적절히 변경되기 때문에, 단지 적절하게 패턴화된 영역은 전도성이 있을 수도 있다.

[0101] 도 15는 일 구체예에 따른 전도성 데이터/버스라인의 제조방법의 개략도이다. 도 15에 나타난 바와 같이, 그래핀의 전도도는 이온 빔에 노출에 따라서 선택적으로 변화한다. 그래핀 기반 층의 나머지 부분이 이온 빔/플라즈마에 노출되어 남아 있는 것에 반하여, 감광제는, 그래핀 기반 층의 원하는 부분을 보호하도록 적절한 패턴으로 적용된다.

[0102] 아래의 표 1은 증착 및 에칭 후의 다양한 예의 운동도 데이터이다.

표 1

| 예칭 샘플 | 경로 | 두께 (Å) | Rho ( $\Omega \text{cm}$ ) | 전도도 ( $1/\Omega \text{cm}$ ) | 운동도 $\mu$ ( $\text{cm}^2/\text{Vs}$ ) |

|-------|----|--------|----------------------------|------------------------------|---------------------------------------|

| A     | 25 | 8      | 1.03E-04                   | 970000                       | 120000                                |

| B     | 20 | 6      | 5.24E-03                   | 1010000                      | 143000                                |

| C     | 10 | 6      | 5.94E-02                   | 1600000                      | 150000                                |

| D     | 5  | 6      | 1.48E-02                   | 1500000                      | 160000                                |

[0104] 이 방법 및/또는 다른 방법으로 그래핀을 패턴화하는 것이 여러 가지 이유에서 유리하다. 예를 들어, 층은 주로 투명할 것이다. 그러므로, 패턴이 보이지 않는 "이음새 없는" 안테나를 제공할 수 있다. 비슷한 결과가 (즉,

서리 제거, 안테나 사용, 동력 요소 등을 위해) 차량 유리, 평면 패널 (즉, LCD, 플라스마, 및/또는 등) 표시 장치, 채광창, 냉동기/냉각기, 도어/윈도우 등의 내부에 적용할 수 있는 버스 바와 관련하여 제공될 수 있다. 이것은 또한 유용하게 그러한 제품에서 발견되는 검은 프릿 (frit)의 필요를 감소시킬 수도 있다. 게다가 그래핀 기반 충은 일렉트로크로믹 (electrochromic) 장치 내의 ITO를 대체할 수도 있다.

- [0105] 상기와 같이 어떤 기기/장치 예가 설명되었지만 그래핀 기반 전도성 충을, ITO, 산화 아연 등의 다른 투명 전도성 코팅 (TCCs)에 대체적 또는 추가적으로 사용하는 것은 가능하다.

- [0106] 여기에서 사용된 "상", "-에 의하여 지지되는"과 같은 용어는 2 가지의 구성 요소가 명확하게 표현되지 않는 한, 직접적으로 접착된 것으로 해석되어서는 안된다. 다시 말하면, 제2 충 "상"의 제1 충 또는 제2 충"에 의하여 지지되는" 제1충은 그들 사이에 단일 또는 복수의 충이 있는 것을 포함하는 것이다.

- [0107] 상술된 발명이 현재 실용적이고 및 적절한 실시예로 여겨질 수 있으나, 본 발명이 상기 기술된 실시예에 제한되지 않는 것이고 첨부된 청구항의 사상과 범위 내에 포함된 다양한 변형과 유사한 장치 배열을 포함하는 것이다.

### 부호의 설명

|                     |                 |

|---------------------|-----------------|

| 501 탄화 수소 가스        | 503 금속 촉매 충     |

| 505 후면 지지대          | 507 고상 도편트      |

| 509 도핑된 그래핀         |                 |

| 701 방출 충            | 703 고분자 충       |

| 801 목표 기판           | 803 상하 롤러       |

| 901 반응기 몸체 부분       | 903 가스 도입부      |

| 905 배출부             | 907 샤크헤드        |

| 909 후면 지지대 기판       | 913 냉각제 도입/배출부  |

| 1202 유리 기판          | 1204 반사방지 충     |

| 1206 흡수 충           | 1208 n-타입 반도체 충 |

| 1210 p-타입 반도체 충     | 1212 후면         |

| 1214, 1216 그래핀 기반 충 | 1218 추가 충       |

| 1302 디스플레이          | 1304 투명 접착제     |

| 1306 얇은 유리 시트       | 1308 PET 포일     |

| 1310 기둥 스페이서        | 1312 밀봉         |

| 1314, 1316 그래핀 기반 충 |                 |

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

## 도면12

## 도면13

## 도면14

도면15