(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3679592号

(P3679592)

(45) 発行日 平成17年8月3日(2005.8.3)

(24) 登録日 平成17年5月20日(2005.5.20)

(51) Int.C1.<sup>7</sup>

F 1

H04N 5/907

H04N 5/907

B

H04N 5/92

H04N 5/92

H

請求項の数 10 (全 8 頁)

(21) 出願番号

特願平10-8682

(22) 出願日

平成10年1月20日(1998.1.20)

(65) 公開番号

特開平11-205732

(43) 公開日

平成11年7月30日(1999.7.30)

審査請求日

平成14年10月25日(2002.10.25)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090538

弁理士 西山 恵三

(74) 代理人 100096965

弁理士 内尾 裕一

(72) 発明者 栄木 裕二

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 加藤 恵一

最終頁に続く

(54) 【発明の名称】信号処理装置及び撮像装置

(57) 【特許請求の範囲】

## 【請求項 1】

第1のタイミング信号を発生する第1の発生手段と、

前記第1のタイミング信号を用いて入力画像信号の画素数を削減する処理手段と

前記処理手段からの画像信号を記憶するバッファメモリと、

前記第1のタイミング信号とは非同期な第2のタイミング信号を発生する第2の発生手段と、

画像信号を記憶するメモリ手段と、

前記メモリ手段より読み出された画像信号を前記第2のタイミング信号に応じて表示手段に出力する出力手段と、

前記第2のタイミング信号に応じて前記メモリ手段に記憶された画像信号をバースト状に読み出し、データバスを介して前記出力手段に転送すると共に、前記第1のタイミング信号に応じて前記バッファメモリに記憶された画像信号を読み出し、前記データバスを介して前記メモリ手段に対してバースト転送して書き込むメモリ制御手段とを備える信号処理装置。

## 【請求項 2】

前記メモリ制御手段は前記データバスを時分割に用いて前記バッファメモリから前記メモリ手段に対する前記画像信号の転送処理と、前記メモリ手段から前記出力手段に対する前記画像信号の転送処理とを実行することを特徴とする請求項1記載の信号処理装置。

## 【請求項 3】

前記第1のタイミング信号は前記表示手段の駆動タイミングと同期していることを特徴とする請求項1記載の信号処理装置。

【請求項4】

前記処理手段は前記表示手段における表示画素数に従って前記入力画像信号の画素数を縮小することを特徴とする請求項1記載の信号処理装置。

【請求項5】

第1のタイミング信号を用いて画像信号を発生する撮像手段と、

前記撮像手段により得られた画像信号を記録媒体に記録する記録手段と、

前記第1のタイミング信号を用いて前記撮像手段により得られた画像信号の画素数を削減する処理手段と、

10

前記処理手段からの画像信号を記憶するバッファメモリと、

画像信号を記憶するメモリ手段と、

前記メモリ手段より読み出された画像信号を表示手段に出力する出力手段と、

前記第1のタイミング信号とは非同期の第2のタイミング信号に応じて前記メモリ手段に記憶された画像信号をバースト状に読み出し、データバスを介して前記出力手段に転送すると共に、前記第1のタイミング信号に応じて前記バッファメモリに記憶された画像信号を読み出し、前記データバスを介して前記メモリ手段に対してバースト転送して書き込むメモリ制御手段とを備える撮像装置。

【請求項6】

前記メモリ制御手段は前記データバスを時分割に用いて前記バッファメモリから前記メモリ手段に対する前記画像信号の転送処理と、前記メモリ手段から前記出力手段に対する前記画像信号の転送処理とを実行することを特徴とする請求項5記載の信号処理装置。

20

【請求項7】

前記第2のタイミング信号は前記表示手段の駆動タイミングと同期していることを特徴とする請求項5記載の撮像装置。

【請求項8】

前記処理手段は前記表示手段における表示画素数に従って前記入力画像信号の画素数を削減することを特徴とする請求項5記載の撮像装置。

【請求項9】

前記撮像手段により得られた画像信号の情報量を圧縮すると共に符号化する圧縮手段を備え、前記記録手段は前記圧縮手段により圧縮された画像信号を前記記録媒体に記録することを特徴とする請求項5記載の撮像装置。

30

【請求項10】

前記記録媒体より画像信号を再生する再生手段を備え、前記処理手段は前記第1のタイミング信号に従って前記再生手段により再生された画像信号の画素数を削減することを特徴とする請求項5記載の撮像装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、信号処理装置及び撮像装置に関し、特に、入力時と非同期なタイミングで信号を出力する処理に関する。

40

【0002】

【従来の技術】

近年、パソコンの普及に伴い、パソコンに対する画像入力手段として、画像をデジタル信号としてメモリに記録するいわゆるデジタルカメラが注目されている。

【0003】

この種のデジタルカメラでは、一般に、撮像素子としてのCCDから得られた画像信号をデジタル信号に変換し、その情報量を圧縮してメモリに記録している。そして、このとき、記録された画像信号を再生して外部のTVモニタに出力する機能や、現在撮像されている画像を内蔵モニタで確認できる機能を持つものもある。

50

**【0004】**

また、近年では、高画質化も急速に進んでおり、そのために、非常に画素数の多いC C Dが用いられるようになってきた。

**【0005】****【発明が解決しようとする課題】**

さて、前述のように、高画質化のためにC C Dの画素数を増やすと、C C Dから画像信号を読み出すのに非常に時間がかかる。これを避けるためには、C C Dの駆動クロックを高速にすればよいが、クロックを高速にするほどC C DやA / D変換器等の回路素子が高価になってしまう。

**【0006】**

また、C C Dからの読み出しに時間がかかると、これを外部のモニタやE V Fに表示する場合、表示される画像のフレームレートが低くなってしまう。

**【0007】**

そのため、従来では、外部モニタやE V Fに画像を表示する際、C C Dからの画像信号の画素を間引いて表示画像のフレームレートを上げると共に、回路規模の縮小化及び設計の簡略化のため、C C Dからの画像信号のフレームレートと表示用の画像信号のフレームレートとの間に簡単な整数比をもたせ、撮像系と表示用画像信号の出力系とを同一のタイミング信号を用いて同期して駆動している。

**【0008】**

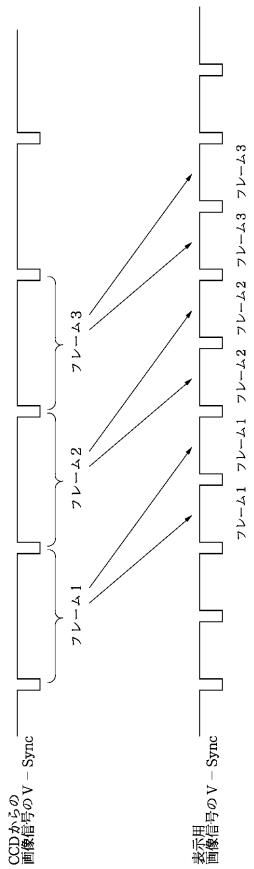

図4はこのように撮像系と表示用画像信号の出力系とを同期して駆動する際の一例を示すタイミングチャートである。図4の例では、C C Dからの画像信号のフレームレートと表示用の画像信号のフレームレートとの比が1対2となっている。

20

**【0009】**

しかしながら、回路をこのように設計した場合、使用するC C Dの画素数が変わる度に撮像系で扱う画像信号の同期タイミングと外部出力系で扱う画像信号の同期タイミングとが変化するため、C C Dの画素数が変化するたびに回路の設計をやり直さなければならない。

**【0010】**

これを回避するため、撮像系と外部出力系とを非同期に駆動する構成も考えられるが、この場合には、撮像系と外部出力系との間のタイミングが変化した場合を考慮した、非常に大容量のバッファが必要になってしまう。

30

**【0011】**

本発明は前述の如き問題を解決することを目的とする。

**【0012】**

本発明の他の目的は、簡単な構成で、且つ、回路規模を大型化することなく、入力時とは非同期なタイミングで信号を出力可能とする処にある。

**【0013】****【課題を解決するための手段】**

前述の如き問題を解決し、前記目的を達成するため、本発明は、第1のタイミング信号を発生する第1の発生手段と、前記第1のタイミング信号を用いて入力画像信号の画素数を削減する処理手段と、前記処理手段からの画像信号を記憶するバッファメモリと、前記第1のタイミング信号とは非同期な第2のタイミング信号を発生する第2の発生手段と、画像信号を記憶するメモリ手段と、前記メモリ手段より読み出された画像信号を前記第2のタイミング信号に応じて表示手段に出力する出力手段と、前記第2のタイミング信号に応じて前記メモリ手段に記憶された画像信号をバースト状に読み出し、データバスを介して前記出力手段に転送すると共に、前記第1のタイミング信号に応じて前記バッファメモリに記憶された画像信号を読み出し、前記データバスを介して前記メモリ手段に対してバースト転送して書き込むメモリ制御手段とを備えて構成されている。

40

**【0014】****【発明の実施の形態】**

50

以下、本発明の実施の形態について、図面を用いて詳細に説明する。

【0015】

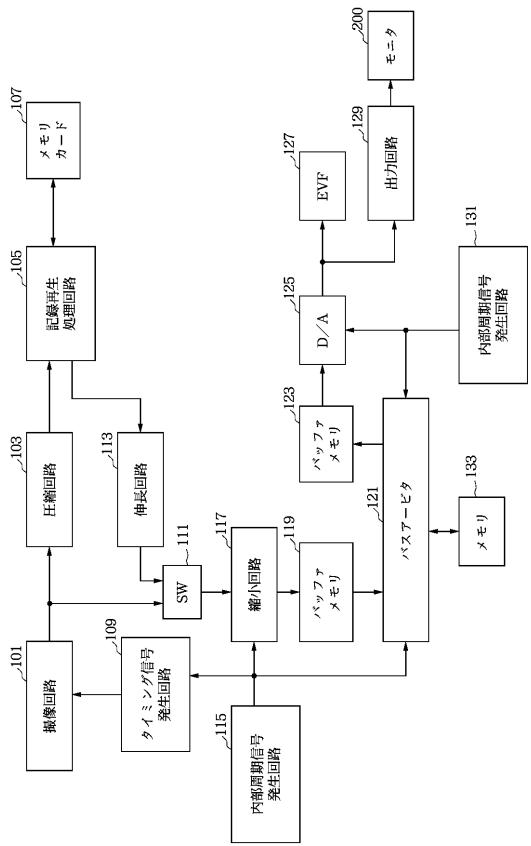

図1は本発明が適用されるデジタルカメラの構成を示すブロック図である。

【0016】

図1の装置では、撮像された画像信号を圧縮してメモリカードに記録すると共に、撮像されている画像を内蔵モニタあるいは外部モニタにて確認可能となっている。また、メモリカードに記録された画像信号を読み出してその情報量を伸長し、やはり内蔵モニタあるいは外部モニタにて確認可能となっている。

【0017】

まず、記録時の処理について説明する。

10

【0018】

図1において、撮像回路101は周知のCCD、CDS回路、アンプ、A/D変換器等を有し、被写体像を1サンプル複数ビットのデジタル信号に変換して圧縮回路103及びスイッチ111に出力する。ここで、内部同期信号発生回路115は後述の如く内部水平同期信号及び内部垂直同期信号を発生し、タイミング信号発生回路109及び縮小回路117に出力する。タイミング信号発生回路109は内部同期信号発生回路115からの各同期信号を用いて撮像回路101を駆動するためのタイミング信号を発生し、撮像回路101に出力する。従って、撮像回路101の各要素は内部同期信号発生回路115からの信号に同期して駆動することになる。

【0019】

20

圧縮回路103では、周知のDCT、可変長符号化等を用いてその情報量を圧縮すると共に符号化し、記録再生処理回路105に出力する。記録再生処理回路105は、圧縮・符号化された画像信号に対してID信号等を付加すると共に記録に適した形態に変換し、メモリカード107に書き込む。

【0020】

次に、再生時の動作について説明する。

【0021】

記録再生処理回路105はメモリカード107に前述の如く記録された1画面分の画像信号を読み出し、伸長回路113に出力する。伸長回路113はメモリカード107から読み出された画像信号に対して記録時とは逆の処理を施して復号すると共にその情報量を伸長し、スイッチ111に出力する。

30

【0022】

スイッチ111は、再生時においては伸長回路113からの出力を選択し、縮小回路117に出力する。縮小回路117は内部同期信号発生回路115からの同期信号に従って以下の通り伸長回路113からの画像信号の画素を間引くことにより、EVF127もしくは外部の一般的なTVモニタのサイズである、水平方向640×垂直方向480画素にそのサイズを縮小する。

【0023】

いま、撮像回路101により得られた画像信号、即ち、メモリカード107より読み出された画像信号のサイズが、1画面あたり水平方向1280×垂直方向960画素であった場合、縮小回路117により1画面のうちの75%の画像信号が間引かれることになる。

40

【0024】

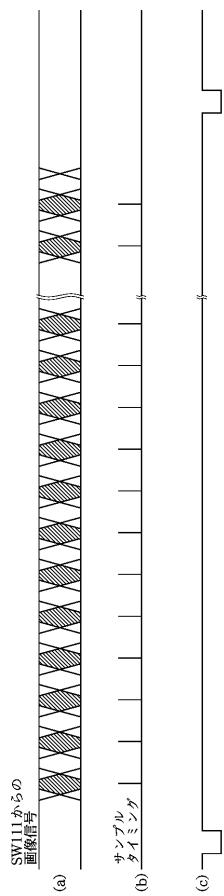

ここで、縮小回路117の動作を図2を用いて説明する。

【0025】

図2は縮小回路117の動作を説明するためのタイミングチャートであり、(a)はスイッチ111から入力される画像信号列を示している。そして、縮小回路117は、(c)に示した内部同期信号発生回路115からの水平同期信号に基づいて(b)に示したサンプルタイミングを示すクロックを発生し、このクロックに従って入力画像信号をサンプリングする。即ち、(a)において斜線で示した部分が縮小回路117にてサンプリングされ、バッファメモリ119に出力される画像信号である。

50

## 【0026】

前述の通り、本形態では入力画像信号の水平方向の1280画素を640画素にするため、ここでは、水平方向に1/2に間引いている。また、垂直方向の960画素（ライン）を480画素にするため、ここでは垂直方向に1/2に間引いている。従って、縮小回路117は、1水平期間おきに画像信号をサンプリングしてバッファメモリ119に出力する。

## 【0027】

バッファメモリ119に記憶された画像信号はバスアービタ121により読み出されてメモリ113に書き込まれる。バスアービタ121は内部にデータバスを有し、内部同期信号発生回路115からの同期信号に従って、縮小回路117により縮小され、バッファメモリ119に記憶された画像信号をバースト状に集中させ、メモリ133に転送する。 10

## 【0028】

また、バスアービタ121は、内部同期信号発生回路115からの同期信号とは非同期なタイミングで発生される外部同期信号発生回路131からの同期信号に従ってメモリ133に記憶された画像信号をバースト状に集中してバッファメモリ123に転送する。

## 【0029】

バッファメモリ123に集中して書き込まれた画像信号は時間軸伸長されてD/A変換器125に出力され、ここで、内部同期信号発生回路131からの同期信号に従ってアナログ信号に変換され、EVF127及び出力回路129に出力される。EVF127はD/A変換器125からの画像信号に従い、前述の如き $640 \times 480$ 画素のサイズの画像を表示する。また、出力回路129は、D/A変換器125からの画像信号に対して同期信号を付加すると共にそのレベルを増幅し、外部モニタ200における処理に適した形態に変換してモニタ200に出力する。 20

## 【0030】

ここで、バスアービタ121によるバッファメモリ119からメモリ133に対する画像信号の転送処理、及び、メモリ133からバッファメモリ123に対する画像信号の転送処理について説明する。

## 【0031】

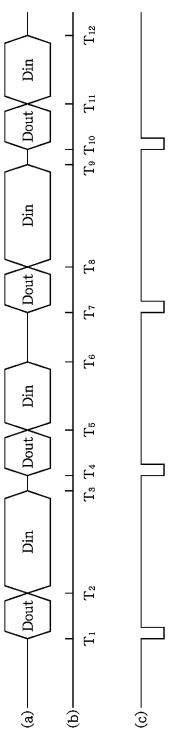

図3はバスアービタ121の転送動作を説明するためのタイミングチャートである。

## 【0032】

図3において、(a)はバスアービタ121内のデータバスを流れるデータを示し、(c)は外部同期信号発生回路131からの水平同期信号を示している。 30

## 【0033】

前述の通り、本形態では、縮小回路117により画像信号のサイズを75%程縮小しているので、その分データバスを使用しない時間のゆとりが生まれる。

## 【0034】

そこで、本形態では、バスアービタ121により、外部同期信号発生回路131からの同期信号に同期してバッファメモリ123に画像信号を転送する一方、外部同期信号発生回路131からの同期信号とは非同期に発生される内部同期信号発生回路115からの同期信号に同期して信号を出力するバッファメモリ119からの画像信号をバースト状に集中させ、メモリ133からバッファメモリ123へ転送する時間のあまり時間にメモリ133に転送するように制御する。 40

## 【0035】

即ち、図3において、外部同期信号発生回路131からの水平同期信号に応じて、T1～T2, T4～T5, T7～T8, 及びT10～T11の期間でメモリ133からバッファメモリ123に対して4ライン分のデータDoutを転送する。

## 【0036】

そして、これ以外の期間でバッファ119から出力された画像信号をメモリ133に転送する。

## 【0037】

即ち、図3においては、T2～T3の期間でバッファメモリ119からの画像信号を転送した後、転送しきれなかつた分を更に、次の水平同期期間におけるT5～T6の期間で転送する。このT2～T3及び、T5～T6の期間でバッファメモリ119に記憶されていた1水平ライン分の画像信号がメモリ133に転送される。従つて、バッファメモリ119は間引いた後の1水平ライン分の画像信号を記憶可能な容量を備えていればよい。また、同様にバッファメモリ123も1水平ライン分の容量を備えていればよい。

#### 【0038】

また、本形態では、前述の如くバッファメモリ119からメモリ133に対する画像信号の転送時と、メモリ133からバッファメモリ123に対する画像信号の転送時とでデータバスを時分割に用いることができる、メモリ133は安価なシングルポートメモリでよい。

10

#### 【0039】

また、撮像回路101により得られた画像信号に応じた画像をEVF127または外部モニタ200に表示する場合は、スイッチ111により撮像回路101からの画像信号を縮小回路117に転送する以外は、メモリカード107の再生時の動作と同じである。

#### 【0040】

なお、記録時においては、撮像回路101からの画像信号に係る画像が動画像としてEVF127に表示され、ユーザはEVF127に表示された画像をモニタしつつ、不図示の操作部にて記録の指示を行う。そして、記録紙時に応じたタイミングで1画面分の画像信号が前述の如くメモリカード107に記録される。

20

#### 【0041】

以上説明したように、本形態では、撮像された画像信号あるいは、メモリカードより再生された画素数の多い（詳細な）画像を撮像系あるいは記録再生系とは非同期なタイミングでモニタする際、その画素数を縮小し、バースト状に集中してメモリに転送することにより、撮像系で扱う画像信号の画素数が変化した場合であっても大幅な設計変更を行うことなく画像のモニタが可能になる。

#### 【0042】

なお、前述の実施形態では、撮像系あるいは記録再生系で扱う画像信号の画素数を水平・垂直方向にそれぞれ1/2に間引く場合について説明したが、もちろんこれ以外の画素数にすることも可能であり、同様の効果を有する。

30

#### 【0043】

また、本形態では、デジタルカメラに対して本発明を適用した場合について説明したが、入力信号と非同期に外部に信号を出力する装置であればどのようなものにも本発明を適用可能である。

#### 【0044】

#### 【発明の効果】

以上説明したように、本発明によれば、入力画像信号と非同期なタイミングで外部に画像信号を出力し、これをモニタする場合、入力及び出力画像信号の画素数が変化しても回路の設計を大幅に変更する必要がない。

#### 【0045】

40

また、バッファメモリの容量も少なくてすむ。

#### 【図面の簡単な説明】

【図1】本発明が適用されるデジタルカメラの構成例を示す図である。

【図2】図1装置の動作を説明するためのタイミングチャートである。

【図3】図1の装置の動作を説明するためのタイミングチャートである。

【図4】撮像系で扱う画像信号と表示用の画像信号のフレームレートを示す図である。

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(56)参考文献 実開昭59-037634 (JP, U)

特開平10-013732 (JP, A)

特開平9-93470 (JP, A)

特開平7-312714 (JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H04N 5/225, 5/76-5/956