(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4031904号

(P4031904)

(45) 発行日 平成20年1月9日(2008.1.9)

(24) 登録日 平成19年10月26日(2007.10.26)

(51) Int.C1.

F 1

G 11 C 11/22 (2006.01)

G 11 C 11/22 501 G

請求項の数 9 (全 13 頁)

(21) 出願番号 特願2000-333160 (P2000-333160)

(22) 出願日 平成12年10月31日 (2000.10.31)

(65) 公開番号 特開2002-133857 (P2002-133857A)

(43) 公開日 平成14年5月10日 (2002.5.10)

審査請求日 平成15年12月18日 (2003.12.18)

前置審査

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 山本 彰

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 川嶋 将一郎

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 加藤 俊哉

最終頁に続く

(54) 【発明の名称】データ読み出し回路とデータ読み出し方法及びデータ記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

プレート電圧が供給されるプレート線と接地電位に設定されたビット線との間に接続されたメモリセルに記憶されたデータを読み出すデータ読み出し回路であって、

供給された電荷を蓄積する電荷蓄積手段と、

前記データに応じて前記メモリセルに蓄積された電荷を前記電荷蓄積手段へ転送する電荷転送手段と、

前記電荷蓄積手段に蓄積された電荷により生ずる電圧を增幅して、前記メモリセルに記憶されていたデータを読み出す増幅手段とを備え、

前記電荷転送手段は、前記プレート電圧が変動した場合においても前記ビット線の電位が接地電位から変動しないように前記電荷を転送することを特徴とするデータ読み出し回路。

## 【請求項 2】

プレート線とビット線との間にメモリセルに記憶されたデータを読み出すデータ読み出し方法であって、

前記データに応じて前記メモリセルに蓄積された電荷を電荷蓄積手段へ転送する転送ステップと、

前記電荷蓄積手段に蓄積された電荷により生ずる電圧を增幅して、前記メモリセルに記憶されていたデータを読み出す増幅ステップとを有し、

前記転送ステップは、前記プレート電圧が変動した場合においても前記ビット線の電位

10

20

が接地電位から変動しないように前記電荷を転送することを特徴とするデータ読み出し方法。

**【請求項 3】**

プレート線とビット線との間に接続されたメモリセルとを含むデータ記憶装置であって、供給された電荷を蓄積する電荷蓄積手段と、

記憶されるデータに応じて前記メモリセルに蓄積され、前記データの読み出し時に前記ビット線へ出力された電荷を前記電荷蓄積手段へ転送する電荷転送手段と、

前記電荷蓄積手段に蓄積された電荷により生ずる電圧を増幅して、前記メモリセルに記憶されていたデータを読み出す増幅手段とを備え、

前記電荷転送手段は、前記プレート電圧が変動した場合においても前記ビット線の電位が接地電位から変動しないように前記電荷を転送することを特徴とするデータ記憶装置。 10

**【請求項 4】**

前記メモリセルは、

前記ビット線と前記プレート線との間に接続された強誘電体コンデンサとを含む請求項 3に記載のデータ記憶装置。

**【請求項 5】**

前記電荷転送手段は、前記電荷蓄積手段へ負の電圧を充電することにより前記電荷を転送する請求項 3に記載のデータ記憶装置。

**【請求項 6】**

前記電荷蓄積手段に転送された前記電荷により生ずる電圧をレベルシフトして前記増幅手段へ供給する電圧シフト手段をさらに備えた請求項 3に記載のデータ記憶装置。 20

**【請求項 7】**

前記ビット線の電位の変動を検知するビット線電位検知手段を有することを特徴とする請求項 3に記載のデータ記憶装置。

**【請求項 8】**

前記電荷転送手段は、非導通状態と導通状態の中間状態に設定されており、

前記ビット線電位検知手段は、ビット線電位の変動の検知がなされた際、前記電荷転送手段を導通状態となるように調整することを特徴とする請求項 7記載のデータ記憶装置。 20

**【請求項 9】**

前記電荷転送手段は、P チャネルMOS トランジスタを含むことを特徴とする請求項 8記載のデータ記憶装置。 30

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、データ読み出し回路とデータ読み出し方法及びデータ記憶装置に関するものである。

**【0002】**

**【従来の技術】**

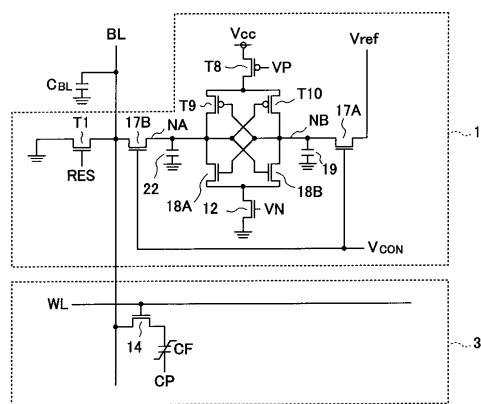

図 1 は、従来の強誘電体メモリの構成を示す回路図である。図 1 に示されるように、従来の強誘電体メモリはワード線WL 及びビット線BL と、強誘電体コンデンサCF と、NチャネルMOS トランジスタ12, 14, 17A, 17B, 18A, 18B, T1 と、PチャネルMOS トランジスタT8 ~ T10 と、キャパシタ19, 22 と、ノードNA, NB とを備える。なお、ビット線BL はビット線容量CBL を有する。 40

**【0003】**

ここで、NチャネルMOS トランジスタ14 はゲートがワード線WL に接続され、ソース/ドレインの一端がビット線BL に接続され、他端が強誘電体コンデンサCF に接続される。そして、強誘電体コンデンサCF の一端にはプレート線CP が接続される。

**【0004】**

また、NチャネルMOS トランジスタ17A, 17B のゲートには電圧V<sub>C0N</sub> が供給され、NチャネルMOS トランジスタ17A のソース/ドレインには参照電圧V<sub>ref</sub> が供 50

給される。また、NチャネルMOSトランジスタ12のゲートには電圧VNが供給され、NチャネルMOSトランジスタT1のゲートには電圧RESが供給される。一方、PチャネルMOSトランジスタT8のゲートには電圧VPが供給される。

#### 【0005】

ここで、上記強誘電体メモリにおいては、図1に示されるように、一つの強誘電体メモリセルは一個のNチャネルMOSトランジスタ14と一個の強誘電体コンデンサCFにより構成される。そして、この強誘電体コンデンサCFは、逆向きの分極状態をとることによって、1または0のデジタル情報を不揮発的に保持する。

#### 【0006】

次に、上記強誘電体メモリセルへデータを書きこむ場合の動作を説明する。まず、強誘電体メモリセルへ「1」の情報を書き込む場合はビット線BLを接地電位とし、「0」の情報を書き込む場合はビット線BLを電源電位Vccとする。そしてこのとき、ワード線WLを活性化してNチャネルMOSトランジスタ14を導通状態とともに、プレート線CPを接地電位とした後に一旦電源電位Vccとして再び接地電位に戻す。強誘電体コンデンサCFは、このように電圧が印加されることによって所定の分極状態に遷移し、「1」または「0」の情報を保持することになる。なお、データの書き込みが終了した場合には、ビット線BLの電位は、接地電位に戻される。

#### 【0007】

次に、上記強誘電体メモリセルからデータを読み出す場合の動作を説明する。この場合には、まずビット線BLの電位を接地電位とする。そしてワード線WLを活性化することによりNチャネルMOSトランジスタ14を導通状態とともに、プレート線CPを接地電位から電源電位Vccまで移行させることにより、強誘電体コンデンサCFに分極している電荷をビット線BLに移動する。ここで、ビット線BLの電位は、強誘電体コンデンサCFの分極状態に応じて大きく又は小さく上昇する。

#### 【0008】

そして、例えばラッチ型センスアンプ回路は、上記ビット線BLの電位とリファレンス電位とを比較する。ここで、センスアンプ回路は初期状態において電源がオフとされ、二つの入力端子に電圧が入力された時点において電源が投入される。これにより、他方より高い電位を有する入力端子は電源電位Vccまで上昇し、他方より低い電位を有する入力端子は接地電位まで下降する。従って、上記のようなセンスアンプ回路により、強誘電体コンデンサCFに保持されたデータを読み出すことが可能となる。

#### 【0009】

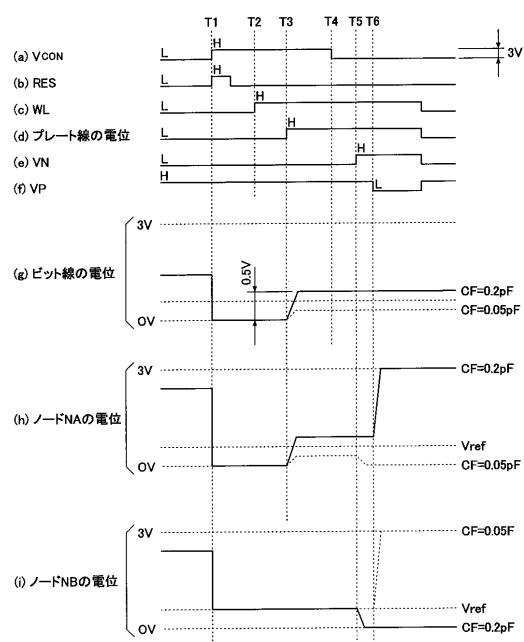

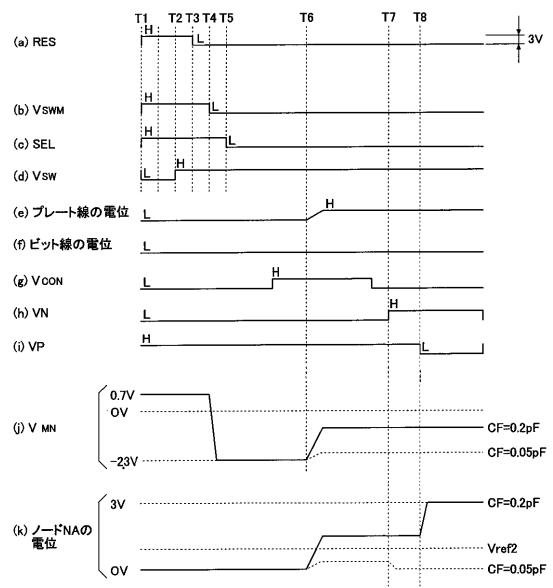

図2は、図1に示された従来の強誘電体メモリのデータ読み出し動作を示すタイミングチャートである。まず図2(a)及び図2(b)に示されるように、電圧V<sub>CO\_N</sub>及び電圧RESは共に時刻T1において、0V(ロウレベル)から3V(ハイレベル)へ活性化される。これにより、図2(g)に示されるように、ビット線BLの電位は0Vに初期化される。なお、図2(a)に示されるように、電圧V<sub>CO\_N</sub>は時刻T4までハイレベルとされる。

#### 【0010】

次に、図2(c)に示されるように、時刻T2においてワード線WLが活性化され、NチャネルMOSトランジスタ14がオンする。そして、図2(d)に示されるように、時刻T3においてプレート線CPの電位が0Vから電源電位(3V)まで引き上げられる。このとき、図2(g)に示されるように、強誘電体コンデンサCFの分極電荷量に応じてビット線BLの電位が上昇する。

#### 【0011】

ここで、例えば強誘電体コンデンサCFの換算容量値が0.2pFの場合は実線、0.05pFの場合は破線によりそれぞれ示される。従って、分極電荷量が大きいほどビット線BLの電位は上昇し、強誘電体コンデンサCFの換算容量値が0.2pFの場合は0.5Vまで上昇することが分かるが、このことについては後述する。

#### 【0012】

10

20

30

40

50

次に、図2(e)に示されるように、時刻T5においてセンスアンプを構成するNチャネルMOSトランジスタ12のゲートに供給される電圧VNがハイレベルとされる。このとき、図2(h)及び図2(i)に示されるように、ノードNAの電位(ビット線BLの電位)がノードNBの電位(参照電圧Vref)よりも低い場合には、破線で示されるようにノードNAの電位は0Vとなり、ノードNBの電位は参照電圧Vrefとなる。一方、ノードNAの電位がノードNBの電位よりも高い場合には、実線で示されるようにノードNAの電位は変化せず、ノードNBの電位は0Vとなる。

#### 【0013】

次に、図2(f)に示されるように、時刻T6においてセンスアンプを構成するPチャネルMOSトランジスタ18のゲートに供給される電圧VPがロウレベルとされる。このとき、図2(h)及び図2(i)に示されるように、ノードNAの電位がノードNBの電位よりも低い場合には、破線で示されるようにノードNAの電位は0Vとなり、ノードNBの電位は3Vとなる。一方、ノードNAの電位がノードNBの電位よりも高い場合には、実線で示されるようにノードNAの電位は3Vとなり、ノードNBの電位は0Vとなる。

10

#### 【0014】

上記のように、ノードNA及びノードNBの一方の電位が0Vとされ他方の電位が3Vとされた後に、ノードNAの電位がビット線BLを介して伝達されることによって、強誘電体メモリセルに保持されていた情報が読み出されることになる。

#### 【0015】

以上のように、図1に示された従来の強誘電体メモリにおける情報読み出し過程では、強誘電体の分極状態に応じてビット線の電位が上昇する。このとき、強誘電体の分極電荷量と該電極間に印加される電圧から算出される容量値を約0.2pF、ビット線の寄生容量を1pF、電源電圧を3Vとそれぞれ仮定すると、プレート線を0Vから3Vまで上昇させたときのビット線の電圧は図2(g)に示されるように、約3V × 0.2pF / (0.2pF + 1pF)により算出される0.5Vだけ上昇することになる。従って、該強誘電体に印加される電圧は(3V - 0.5V)により算出され2.5Vとなる。

20

#### 【0016】

ところで、該強誘電体に印加される読み出し電圧を低電圧化する技術が材料の改良も含め盛んに研究されているが、読み出し電圧が小さいと十分に分極電荷を読み出すことが出来ないため、正確な情報読み出しに支障をきたして読み出しマージンの減少をもたらすという問題がある。

30

#### 【0017】

一方、携帯電話やモバイル機器の低電力化のため電源電圧も低下させることが強く求められている。ここで、仮にビット線容量を大きくすればビット線の電圧上昇は減少するが、このことは読み出し信号が小さくなることを意味するため、強誘電体メモリにおけるラッチ型センスアンプ回路においては、入力オフセット電圧の誤差により誤動作する可能性が高くなる。

#### 【0018】

従って、該ラッチ型センスアンプ回路は、実際的にはビット線の電圧上昇が0.5V程度となるよう容量比が設計される必要があるが、電源電圧が2V又は1Vの場合には該電圧上昇を担保するのが難しいという問題がある。

40

#### 【0019】

##### 【発明が解決しようとする課題】

本発明は、上述の問題を解消するためになされたもので、信頼性が高く消費電力が低減されたデータ記憶装置と、該装置において採用されるデータ読み出し回路及びデータ読み出し方法を提供することを目的とする。

#### 【0020】

##### 【課題を解決するための手段】

本発明は、プレート電圧が供給されるプレート線と接地電位に設定されたビット線との間に接続されたメモリセルに記憶されたデータを読み出すデータ読み出し回路であって、

50

供給された電荷を蓄積する電荷蓄積手段と、データに応じてメモリセルに蓄積された電荷を電荷蓄積手段へ転送する電荷転送手段と、電荷蓄積手段に蓄積された電荷により生ずる電圧を増幅して、メモリセルに記憶されていたデータを読み出す増幅手段とを備え、電荷転送手段はプレート電圧が変動した場合においてもビット線の電位が接地電位から変動しないように電荷を転送することを特徴とする。

【0021】

また、本発明は、プレート線とビット線との間にメモリセルに記憶されたデータを読み出すデータ読み出し方法であって、データに応じて前記メモリセルに蓄積された電荷を電荷蓄積手段へ転送する転送ステップと、電荷蓄積手段に蓄積された電荷により生ずる電圧を増幅して、メモリセルに記憶されていたデータを読み出す増幅ステップとを有し、転送ステップはプレート電圧が変動した場合においてもビット線の電位が接地電位から変動しないように電荷を転送することを特徴とする。

10

【0024】

また、本発明のメモリセルは、ビット線とプレート線との間に接続された強誘電体コンデンサとを含むことを特徴とする。さらに、電荷転送手段は、電荷蓄積手段へ負の電圧を充電することにより電荷を転送する。また、電荷蓄積手段に転送された前記電荷により生ずる電圧をレベルシフトして前記増幅手段へ供給する電圧シフト手段をさらに備えたことを特徴とする。

【0025】

また、本発明は、ビット線の電位の変動を検知するビット線電位検知手段を有することを特徴とする。電荷転送手段は非導通状態と導通状態の中間状態に設定されており、ビット線電位検知手段はビット線電位の変動の検知がなされた際、電荷転送手段を導通状態となるように調整することを特徴とする。電荷転送手段は、PチャネルMOSトランジスタを含むことを特徴とする。

20

【0026】

【発明の実施の形態】

以下において、本発明の実施の形態を図面を参照して詳しく説明する。なお、図中同一符号は同一又は相当部分を示す。

【0027】

本発明の実施の形態に係る強誘電体メモリでは、ビット線の電圧が接地電位から上昇しないようにして、強誘電体メモリを構成する強誘電体コンデンサに印加する最大電圧を電源電圧と同じ3Vとする。ここで、ビット線の電位を接地電位のままとして、該強誘電体からビット線へ流出した電荷量を測定する。

30

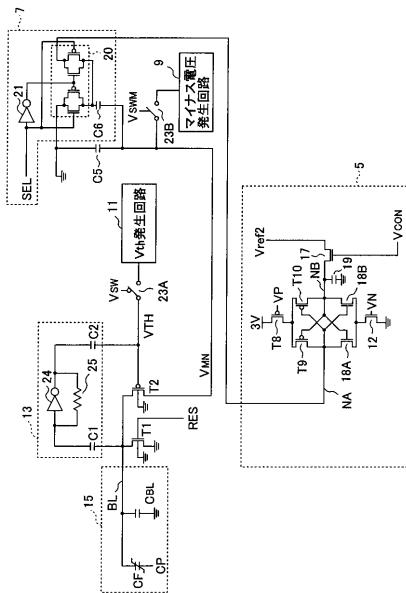

【0028】

以下において、本実施の形態に係る強誘電体メモリを詳しく説明する。図3は、本発明の実施の形態に係る強誘電体メモリの構成を示す回路図である。図3に示されるように、本実施の形態に係る強誘電体メモリはセンスアンプ回路5と、電圧シフト回路7と、マイナス電圧発生回路9と、Vth発生回路11と、フィードバック回路13と、メモリセル領域15と、NチャネルMOSトランジスタT1と、PチャネルMOSトランジスタT2と、キャパシタC5と、スイッチ23A, 23Bとを備える。

40

【0029】

そして、センスアンプ回路5は、NチャネルMOSトランジスタ12, 17, 18A, 18BとPチャネルMOSトランジスタT8~T10と、キャパシタ19と、ノードNA, NBとを含む。また、電圧シフト回路7はゲート回路20と、反転回路21及びキャパシタC6を含む。また、フィードバック回路13は、キャパシタC1, C2と反転回路24及び抵抗素子25を含み、メモリセル領域15はビット線BLとビット線容量CBL、及び強誘電体コンデンサCFとプレート線CPとを含む。

【0030】

また、メモリセル領域15には、ビット線BLと強誘電体コンデンサCF、プレート線CP、及びビット線容量CBLが含まれる。なお、ビット線容量CBLは、回路図上において

50

て等価回路として表したビット線 B L の寄生容量を意味するものである。

【0031】

ここで、電圧シフト回路 7 に含まれたキャパシタ C 6 はキャパシタ C 5 と並列接続され、電圧シフト回路 7 の出力ノードはセンスアンプ回路 5 のノード N A に接続される。また、マイナス電圧発生回路 9 はマイナスの電圧  $V_{M_N}$  を生成し、スイッチ 23B を介してビット線 B L へ供給する。

【0032】

さらに、V th 発生回路 11 はしきい値電圧 V TH を生成し、スイッチ 23A を介して P チャネルMOSトランジスタ T 2 のゲートへ供給する。また、フィードバック回路 13 は、ビット線 B L と P チャネルMOSトランジスタ T 2 のゲートとの間に接続される。 10

【0033】

なお、スイッチ 23A は供給される電圧  $V_{SW}$  に応じて制御され、スイッチ 23B は供給される電圧  $V_{SWM}$  に応じて制御される。また、センスアンプ回路 5 に含まれたNチャネルMOSトランジスタ 17 のゲートには電圧  $V_{CON}$  が供給され、ソース / ドレインには参照電圧  $V_{REF2}$  が供給される。

【0034】

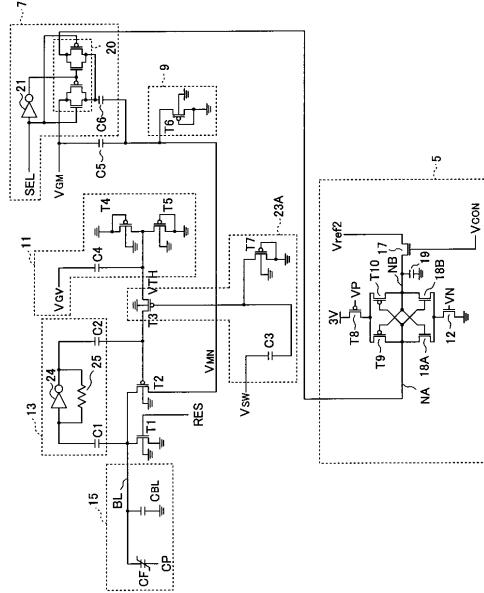

図 4 は、図 3 に示された本実施の形態に係る強誘電体メモリをより具体的に示す具体例である。ここで、図 4 に示されるように、マイナス電圧発生回路 9 はダイオード接続された P チャネルMOSトランジスタ T 6 により構成され、V th 発生回路 11 はキャパシタ C 4 と、それぞれダイオード接続された P チャネルMOSトランジスタ T 4, T 5 とにより構成される。ここで、キャパシタ C 4 を構成する一方の電極には電圧  $V_{GV}$  が供給される。 20

【0035】

また、スイッチ 23A はキャパシタ C 3 と P チャネルMOSトランジスタ T 3 、及びダイオード接続された P チャネルMOSトランジスタ T 7 とにより構成され、キャパシタ C 3 を構成する一方の電極には電圧  $V_{SW}$  が供給される。

【0036】

なお、図 4 に示されるように、キャパシタ C 5 を構成する一方の電極とゲート回路 20 へは接地電圧の代わりに電圧  $V_{GM}$  を供給してもよい。

【0037】

上記のように、本実施の形態に係る強誘電体メモリにおいては、使用する負電圧は P チャネルMOSトランジスタとキャパシタにより生成する構成をとっており、負電源を必要としない。また、P チャネルMOSトランジスタのNウェルバックゲート電位は一般的には電源電圧レベルとされるが、低耐圧のトランジスタでも使用できるよう負電圧が使用される P チャネルMOSトランジスタにおいては、Nウェルバックゲート電位が 0 V とされる。 30

【0038】

以下において、図 3 に示された本実施の形態に係る強誘電体メモリの動作を、図 5 に示されたタイミングチャートを参照しつつ説明する。

【0039】

まず、図 5 (a) に示されるように、NチャネルMOSトランジスタ T 1 のゲートに供給される信号 RES が時刻 T 1 においてハイレベルに活性化されると、図 5 (f) に示されたビット線 B L の電位は接地電位に初期化される。一方このとき、図 5 (d) に示されるように、時刻 T 1 から時刻 T 2 までの間ににおいて電圧  $V_{SW}$  がロウレベルとされることによりスイッチ 23A がオンされ、P チャネルMOSトランジスタ T 2 のゲートにしきい値電圧 V TH が印加される。 40

【0040】

ここで、図 4 に示されたV th 発生回路 11 において、P チャネルMOSトランジスタ T 5 はダイオード接続されているので、+0.7V のクランプ回路として働くと共に、キャパシタ C 4 へ充電させる意義を持つ。従って、電圧  $V_{GV}$  を 3V とするとキャパシタ C 4 に 50

は約2.3Vだけ充電される。一方、PチャネルMOSトランジスタT4もダイオード接続され約0.7Vの電圧降下を生じさせるため、-0.7Vのクランプ回路として働くと共に、電圧VTHを-0.7Vより下げないようにする意義を持つ。従って、電圧VGVを0Vとすると電圧VTHは約-0.7Vとなる。

#### 【0041】

このとき、電圧VTHはPチャネルMOSトランジスタT2のしきい値電圧とほぼ等しいため、PチャネルMOSトランジスタT2は非導通状態（オフ状態）と導通状態（オン状態）の中間状態となる。これより、少しでもゲート電圧が下降すればオン状態となり、ゲート電圧が上昇すればオフ状態となる。そして、PチャネルMOSトランジスタT2のゲート電圧を設定した後の時刻T2において、PチャネルMOSトランジスタT3がオフされる。

#### 【0042】

また、PチャネルMOSトランジスタT3のゲートには電圧Vswに応じた電圧が供給される。ここで、PチャネルMOSトランジスタT7はダイオード接続になっているため、約0.7Vの電圧降下を生じ+0.7Vのクランプ回路として働く。従って、電圧Vswを3Vとすると、PチャネルMOSトランジスタT3のゲートには+0.7Vが供給されるためオフ状態になるとと共に、キャパシタC3には2.3Vが充電される。次に電圧Vswを0Vにすると、PチャネルMOSトランジスタT3のゲートには-2.3Vが供給されるためオン状態になる。

#### 【0043】

そして、図5(a)に示されるように、時刻T3において信号RESがロウレベルに不活性化され、NチャネルMOSトランジスタT1がオフされる。次に、図5(b)に示されるように、時刻T4において電圧VswMがロウレベルとされ、スイッチ23Bがオンされる。これにより、マイナス電圧発生回路9において発生された負の電圧はスイッチ23Bを導通し、図5(j)に示されるように、電圧Vmnは例えば約-2.3Vとなる。なお、上記電圧Vmnの値は-3Vや-1.5V等となるように設計してもよい。

#### 【0044】

ここで、図4に示される具体例においては、PチャネルMOSトランジスタT6とキャパシタC5, C6及び電圧Vgmを制御することにより電圧Vmnが負の電圧とされる。すなわち、まず最初に信号SELがハイレベルとされることによりキャパシタC5, C6が並列接続される。次に、PチャネルMOSトランジスタT6はダイオード接続されているため、約0.7Vの電圧降下を生じ+0.7Vのクランプ回路として働く。従って、電圧Vgmが3VとされることによりキャパシタC5, C6には約2.3V充電され、次に電圧Vgmを0Vとすることにより電圧Vmnが-2.3Vとされる。

#### 【0045】

また、図3に示された電圧シフト回路7は、電圧Vmnを約2.3Vだけ正方向へシフトした電圧を出力する回路とされる。すなわち、電圧Vmnは負電圧とされるが、負電圧を使用する回路は一般に設計面や消費電力の面において問題を生じるため、該電圧Vmnを正電圧の領域までシフトさせることにより、次段に接続されるラッチ型のセンスアンプ回路5を正電圧の範囲で使用するようにするものである。

#### 【0046】

ここで、図5(c)に示されるように、時刻T1から時刻T5までの間において信号SELがハイレベルとされ、キャパシタC6の一方の電極は接地される。そして、時刻T5以降において信号SELのレベルがロウレベルとされると、上記電極がセンスアンプ回路5のノードNAに接続される。これにより、ノードNAの電位は電圧Vmnに対し約2.3Vだけ高い電圧となる。

#### 【0047】

次に、図5(c)に示されるように、時刻T6においてプレート線CPの電位が接地電位から電源電圧電位Vccへ遷移されると、強誘電体コンデンサCFからビット線BLへ電荷が放出され、ビット線BLの電位が上昇する。このとき、ビット線BLの電位が接地電

10

20

30

40

50

位より上昇すると、フィードバック回路13によりPチャネルMOSトランジスタT2のゲート電圧が下げられる。これより、PチャネルMOSトランジスタT2がオンし、ソース・ドレン間に電流が流れるため、ビット線BLの該電荷は負の電圧 $V_{MN}$ を有する部分へ流れ込む。

【0048】

従って、図5(j)に示されるように電圧 $V_{MN}$ は時刻T6において上昇すると共に、図5(f)に示されるようにビット線BLの電位はロウレベルに保たれる。ここで、ビット線BLの電圧が変化しないということは、換言すれば、ビット線BLが低インピーダンス状態であることを意味する。

【0049】

なお、上記のようにビット線BLに読み出された電荷を、PチャネルMOSトランジスタT2を介して負の電圧 $V_{MN}$ を有する部分へ転送する回路は、電荷転送回路と呼ぶことができる。

【0050】

また、上記における電圧 $V_{MN}$ はキャパシタC5の両電極間に印加される電圧でもあり、結果的には強誘電体コンデンサCFに蓄積された電荷は、全てキャパシタC5に転送されビット線BLの電位上昇が回避される。これより、キャパシタC5の電圧は強誘電体コンデンサCFの分極電荷量に応じて変化することになる。

【0051】

ここで、キャパシタC5の上記電圧は、キャパシタC6を介してセンスアンプ回路5のノードNAに接続されているため、図5(j)及び図5(k)に示されるように時刻T6においては、ノードNAの電位は電圧 $V_{MN}$ と同じ大きさだけ上昇することとなる。また、センスアンプ回路5に供給する参照電圧 $V_{ref2}$ を適当に選ぶことにより、強誘電体コンデンサCFの分極状態を検出することが可能である。

【0052】

すなわち、図5(g)に示されるように、NチャネルMOSトランジスタ17のゲートに供給する電圧 $V_{coN}$ を、時刻T6近傍の所定期間ハイレベルに活性化することによりNチャネルMOSトランジスタ17をオンし、ノードNBへ参照電圧 $V_{ref2}$ を供給する。

【0053】

そして、図5(h)及び図5(i)に示されるように、時刻T7においてNチャネルMOSトランジスタ12のゲートに供給する電圧VNをハイレベルに活性化させ、時刻T8においてPチャネルMOSトランジスタT8のゲートに供給する電圧VPをロウレベルに活性化させる。これにより、ノードNAの電位がノードNBの電位(参照電圧 $V_{ref2}$ )より高い場合には、図5(k)の実線に示されるように、ノードNAの電位は電源電圧レベル(3V)まで上昇し、ノードNAの電位がノードNBの電位(参照電圧 $V_{ref2}$ )より低い場合には、図5(k)の破線に示されるように、ノードNAの電位は接地電圧レベル(0V)まで下降する。

【0054】

以上より、本実施の形態に係る強誘電体メモリにおいては、時刻T8以後におけるノードNAの電位を調べることにより、ビット線BLの電位を接地電位より上昇させることなく、強誘電体コンデンサCFの分極状態(強誘電体メモリセルに記憶されたデータ)を読み取ることができる。

【0055】

また、上記本発明の実施の形態に係る強誘電体メモリは、負の電圧をキャパシタC5の一方の電極へ供給し、データの読み出しに際してビット線BLに生じた電荷をキャパシタC5へ流れるようにすることによって、ビット線BLの電圧上昇を防ぐと共に、キャパシタC5の電圧値を調べることにより強誘電体コンデンサCFの分極状態を検出するものであるといえる。

【0056】

10

20

30

40

50

従って、本発明の実施の形態に係る強誘電体メモリによれば、強誘電体コンデンサ C F が保持する電荷を確実に読み出すことにより、データの読み出し精度を向上させて強誘電体メモリの信頼性を高めると共に、ビット線 B L の電圧上昇を回避して強誘電体コンデンサ C F に対する印加電圧を従来より効率的に高められることとし、強誘電体メモリの消費電力を低減することができる。

【 0 0 5 7 】

なお、本発明の実施の形態に係る強誘電体メモリによれば、データの読み出しにおいてビット線 B L の電位が一定とされるため、ビット線 B L 同士におけるノイズの影響も低減することができる。

【 0 0 5 8 】

また、従来はメモリセルから電荷が読み出されるとビット線の電位が上昇する。そして、ビット線の電位が上昇することによって、プレート線とビット線の間にあるメモリセルに印加される電圧は小さくなるため、読み出せる電荷量は少なくなってしまう。そのため、ビット線容量を増加させてビット線の電圧上昇を防ぐこともできるが、この場合には読み出せる信号の電圧が小さくなり問題である。

【 0 0 5 9 】

従って、セルに印加される電圧を大きくしつつ読み出し信号も大きくするために、ビット線容量とセル容量の比率を最適化する必要があり、設計の障害となる。本発明においては、ビット線電位を変化させない読み出し方法を実現することにより、ビット線容量やセル容量を自由に設定することができるため、プロセスにあわせて自由に設定できる。

(付記 1 ) プレート線とビット線との間に接続されたメモリセルを有するデータ記憶装置であって、前記プレート線へ電圧を印加しても前記ビット線の電位が変動しないよう、前記ビット線の電位を所定の電位に保持する電位保持手段を備えたことを特徴とするデータ記憶装置。

(付記 2 ) メモリセルに記憶されたデータを読み出すデータ読み出し回路であって、供給された電荷を蓄積する電荷蓄積手段と、前記データに応じて前記メモリセルに蓄積された電荷を前記電荷蓄積手段へ転送する電荷転送手段と、前記電荷蓄積手段に蓄積された電荷により生ずる電圧を増幅して、前記メモリセルに記憶されていたデータを読み出す増幅手段とを備えたことを特徴とするデータ読み出し回路。

(付記 3 ) ビット線と、前記ビット線に接続されたメモリセルとを含むデータ記憶装置であって、供給された電荷を蓄積する電荷蓄積手段と、記憶されるデータに応じて前記メモリセルに蓄積され、前記データの読み出し時に前記ビット線へ出力された電荷を前記電荷蓄積手段へ転送する電荷転送手段と、前記電荷蓄積手段に蓄積された電荷により生ずる電圧を増幅して、前記メモリセルに記憶されていたデータを読み出す増幅手段とを備えたことを特徴とするデータ記憶装置。

(付記 4 ) 前記メモリセルは、プレート電圧が供給されるプレート線と、前記ビット線と前記プレート線との間に接続された強誘電体コンデンサとを含む付記 3 に記載のデータ記憶装置。

(付記 5 ) 前記電荷転送手段は、前記プレート電圧が変動した場合においても前記ビット線の電位が変動しないよう前記電荷を転送する付記 4 に記載のデータ記憶装置。

(付記 6 ) 前記電荷転送手段は、前記電荷蓄積手段へ負の電圧を充電することにより前記電荷を転送する付記 3 に記載のデータ記憶装置。

(付記 7 ) 前記電荷蓄積手段に転送された前記電荷により生ずる電圧をレベルシフトして前記増幅手段へ供給する電圧シフト手段をさらに備えた付記 3 に記載のデータ記憶装置。

(付記 8 ) 前記電荷転送手段では、負の電圧を導通するスイッチング素子として P 型トランジスタが使用される付記 3 に記載のデータ記憶装置。

(付記 9 ) メモリセルに記憶されたデータを読み出すデータ読み出し方法であって、前記データに応じて前記メモリセルに蓄積された電荷を電荷蓄積手段へ転送する転送ステップと、前記電荷蓄積手段に蓄積された電荷により生ずる電圧を増幅して、前記メモリセルに記憶されていたデータを読み出す増幅ステップとを有することを特徴とするデータ読み出

10

20

30

40

50

し方法。

(付記 10) 前記メモリセルは、プレート電圧が供給されるプレート線と、前記ビット線と前記プレート線との間に接続された強誘電体コンデンサとを含む付記 9 に記載のデータ読み出し方法。

(付記 11) 前記転送ステップでは、前記プレート電圧が変動した場合においても前記ビット線の電位が変動しないよう前記電荷を転送する付記 10 に記載のデータ読み出し方法。

【発明の効果】

上述の如く、本発明に係るデータ読み出し回路とデータ読み出し方法、及びデータ記憶装置によれば、メモリセルに蓄積された電荷を確実に読み出すことができるため、信頼性の高い読み出し動作を実現することができる。

【0060】

ここで、上記メモリセルに供給されるプレート電圧が変動する場合においてもビット線の電位が変動しないよう電荷を転送すれば、強誘電体コンデンサに効率的に電圧を印加することができるため、消費電力を低減することができる。

【図面の簡単な説明】

【図 1】従来の強誘電体メモリの構成を示す回路図である。

【図 2】図 1 に示された強誘電体メモリのデータ読み出し動作を示すタイミングチャートである。

【図 3】本発明の実施の形態に係る強誘電体メモリの構成を示す回路図である。

【図 4】図 3 に示された強誘電体メモリの具体例を示す回路図である。

【図 5】図 4 に示された強誘電体メモリの動作を示すタイミングチャートである。

【符号の説明】

1, 5 センスアンプ回路

3, 15 メモリセル領域

7 電圧シフト回路

9 マイナス電圧発生回路

11 Vth 発生回路

13 フィードバック回路

12, 14, 17, 17A, 17B, 18A, 18B, T1 N チャネルMOSトランジスタ

19, 22, C1 ~ C6 キャパシタ

20 ゲート回路

21, 24 反転回路

23A, 23B スイッチ

25 抵抗素子

B L ビット線

C P プレート線

CBL ビット線容量

C F 強誘電体コンデンサ

T2 ~ T10 P チャネルMOSトランジスタ

NA, NB ノード

10

20

30

40

【図1】

従来の強誘電体メモリの構成を示す回路図

【図2】

図1に示された強誘電体メモリのデータ読み出し動作を示すタイミングチャート

【図3】

本発明の実施の形態に係る強誘電体メモリの構成を示す回路図

【図4】

図3に示された強誘電体メモリの具体例を示す回路図

【図5】

図4に示された強誘電体メモリの動作を示す

タイミングチャート

---

フロントページの続き

(56)参考文献 特開平10-214488(JP,A)

特開平09-185890(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/22