(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6881973号

(P6881973)

(45) 発行日 令和3年6月2日(2021.6.2)

(24) 登録日 令和3年5月10日(2021.5.10)

(51) Int.Cl.

F 1

|              |           |              |         |

|--------------|-----------|--------------|---------|

| G 06 F 12/02 | (2006.01) | G 06 F 12/02 | 5 7 0 M |

| B 41 J 29/38 | (2006.01) | B 41 J 29/38 | 4 0 1   |

| G 06 F 13/14 | (2006.01) | G 06 F 13/14 | 3 2 0 B |

請求項の数 15 (全 18 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2016-254088 (P2016-254088)  |

| (22) 出願日  | 平成28年12月27日 (2016.12.27)      |

| (65) 公開番号 | 特開2018-106547 (P2018-106547A) |

| (43) 公開日  | 平成30年7月5日 (2018.7.5)          |

| 審査請求日     | 令和1年12月18日 (2019.12.18)       |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 110003281<br>特許業務法人大塚国際特許事務所               |

| (72) 発明者  | 久我 剛<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内    |

審査官 佐賀野 秀一

最終頁に続く

(54) 【発明の名称】情報処理装置、及び情報処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のICチップを直列接続して、前記複数のICチップによりデータを処理する情報処理装置であって、

前記複数のICチップの少なくとも1つの対象ICチップは、

プログラムに基づきICチップの制御を行うプログラム実行手段と、

前記プログラム実行手段が第1のアドレス幅でアドレッシング可能な第1のメモリ空間と、

前記第1のアドレス幅よりも大きい第2のアドレス幅でアドレッシング可能であり、前記対象ICチップとは異なる他のICチップにアクセスするための領域を含み、かつ、前記プログラム実行手段が直接アクセスすることができない第2のメモリ空間と、

前記第2のメモリ空間からアクセスすることができるICチップとの間の通信を行う通信手段と、

前記第1のメモリ空間と前記第2のメモリ空間の間でのアドレス変換を行うアドレス変換手段とを有し、

前記第1のメモリ空間からのアクセスが行われる場合、前記アドレス変換手段が前記アクセスのアドレス値を前記第2のメモリ空間へのアドレス値に変換することにより、前記第2のメモリ空間に含まれる前記他のICチップにアクセスするための領域へのアクセスが行われ、

前記第2のメモリ空間からのアクセスが行われる場合、前記アドレス変換手段が前記ア

10

20

クセスのアドレス値を前記第1のメモリ空間へのアドレス値に変換することにより、前記対象I Cチップの前記第1のメモリ空間へのアクセスが行われる、

ことを特徴とする情報処理装置。

【請求項2】

前記第2のメモリ空間の一部が前記第1のメモリ空間にマッピングされることを特徴とする請求項1に記載の情報処理装置。

【請求項3】

前記プログラム実行手段が前記アドレス変換手段にアクセスすることに基づいて、前記アドレス変換手段は前記第1のアドレス幅のアドレス値を前記第2のアドレス幅のアドレス値に変換することを特徴とする請求項1又は2に記載の情報処理装置。 10

【請求項4】

前記対象I Cチップとは異なるI Cチップが前記対象I Cチップを指し示すアドレス値を用いてアクセスしている場合、前記対象I Cチップ内の前記第1のメモリ空間にアクセスするようにアドレス値が変換されることを特徴とする請求項1乃至3のいずれか1項に記載の情報処理装置。

【請求項5】

前記アドレス変換手段は、前記対象I Cチップを指し示すアドレス値の上位のnビットを取り除き前記第1のメモリ空間のアドレス値に変換することを特徴とする請求項4に記載の情報処理装置。 20

【請求項6】

前記第2のメモリ空間のアドレス値の内、上位のnビットがI Cチップを特定し、残りのビットが前記第1のメモリ空間へアクセスするために使用されることを特徴とする請求項1乃至5のいずれか1項に記載の情報処理装置。

【請求項7】

前記対象I Cチップの前記第2のメモリ空間には、前記対象I Cチップの前記第1のメモリ空間と、前記対象I Cチップに接続された第1のI Cチップおよび第2のI Cチップの少なくとも1つの第1のメモリ空間がマッピングされることを特徴とする請求項1乃至6のいずれか1項に記載の情報処理装置。

【請求項8】

前記第1のI Cチップから前記第2のI Cチップにアクセスする場合、前記第1のI Cチップから前記第2のI Cチップにアクセスは前記対象I Cチップを通過することで実行されることを特徴とする請求項7に記載の情報処理装置。 30

【請求項9】

前記複数のI Cチップの少なくとも1つのI Cチップは、

前記第2のメモリ空間でデータ転送可能なDMA Cを備え、

前記DMA Cは他のI Cチップをインターフェクトに接続し、

前記他のI Cチップへのデータ転送に前記DMA Cを用いることを特徴とする請求項1乃至8のいずれか1項に記載の情報処理装置。

【請求項10】

前記情報処理装置は、インクジェット記録装置であり、

前記複数のI Cチップのうちの1つのI Cチップは、前記インクジェット記録装置の全体制御と前記インクジェット記録装置が接続されるホストとの通信のために割当てられ、

前記複数のI Cチップの残りのI Cチップは、記録ヘッドを制御して記録を行うためのデータの画像処理のために割当てられることを特徴とする請求項1乃至9のいずれか1項に記載の情報処理装置。 40

【請求項11】

前記残りのI Cチップは、前記記録ヘッドが吐出するインクの色に対応した色成分データを画像処理するために割当てられることを特徴とする請求項10に記載の情報処理装置。

【請求項12】

50

前記複数の I C チップは、 P C I - E x p r e s s により接続され、

前記複数の I C チップの間のデータ転送は、前記 P C I - E x p r e s s により D M A

C を介した転送と、前記 P C I - E x p r e s s により C P U を介した転送とのうちの少

なくともいずれかを含むことを特徴とする請求項 1 乃至 1 1 のいずれか 1 項に記載の情報

処理装置。

**【請求項 1 3】**

前記第 2 のメモリ空間は、前記他の I C チップの C P U が前記第 1 のアドレス幅でアド

レッシング可能な第 3 のメモリ空間にマッピングされた領域を含むことを特徴とする請求

項 1 乃至 1 2 のいずれか 1 項に記載の情報処理装置。

**【請求項 1 4】**

前記他の I C チップとして、第 1 の I C チップと第 2 の I C チップがあり、

前記第 2 のメモリ空間は、前記第 1 の I C チップの C P U が前記第 1 のアドレス幅でア

ドレッシング可能な第 3 のメモリ空間にマッピングされた領域と、前記第 2 の I C チップ

の C P U が前記第 1 のアドレス幅でアドレッシング可能な第 4 のメモリ空間にマッピング

された領域を含むことを特徴とする請求項 1 乃至 1 2 のいずれか 1 項に記載の情報処理裝

置。

**【請求項 1 5】**

複数の I C チップを直列接続して、前記複数の I C チップによりデータを処理する情報

処理装置における情報処理方法であって、

前記複数の I C チップの少なくとも 1 つの対象 I C チップは、

プログラムに基づき I C チップの制御を行うプログラム実行手段と、

前記プログラム実行手段が第 1 のアドレス幅でアドレッシング可能な第 1 のメモリ空

間と、

前記第 1 のアドレス幅よりも大きい第 2 のアドレス幅でアドレッシング可能であり、

前記対象 I C チップとは異なる他の I C チップにアクセスするための領域を含み、かつ、

前記プログラム実行手段が直接アクセスすることができない第 2 のメモリ空間と、

前記第 2 のメモリ空間からアクセスすることができる I C チップとの間の通信を行う

通信手段と、

前記第 1 のメモリ空間と前記第 2 のメモリ空間の間でのアドレス変換を行うアドレス

変換手段を備え、

前記情報処理方法は、

前記アドレス変換手段が、前記第 1 のメモリ空間と前記第 2 のメモリ空間の間でのア

ドレッシングを行なうアドレス変換工程、を有し、

前記第 1 のメモリ空間からのアクセスが行われる場合、前記アドレス変換工程では、前

記アクセスのアドレス値を前記第 2 のメモリ空間へのアドレス値に変換することにより、

前記第 2 のメモリ空間に含まれる前記他の I C チップにアクセスするための領域へのア

クセスが行われ、

前記第 2 のメモリ空間からのアクセスが行われる場合、前記アドレス変換工程では、前

記アクセスのアドレス値を前記第 1 のメモリ空間へのアドレス値に変換することにより、

前記対象 I C チップの前記第 1 のメモリ空間へのアクセスが行われる、

ことを特徴とする情報処理方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は情報処理装置、及び情報処理方法に関し、特に、複数の I C チップを備え、1

つの I C チップからアドレス変換回路を経由して他の I C チップにデータを転送する情報

処理装置、及び情報処理方法に関する。

**【背景技術】**

**【0 0 0 2】**

従来より、ある I C チップのメモリ空間の一部の領域を他の I C チップのメモリ空間に

10

20

30

40

50

割り当てて、アクセスするシステムにおいて、アドレス変換を行う構成が知られている（特許文献1、2参照）。特許文献1は、隣接ICチップの所望のメモリアドレスにアクセスするための技術を開示している。また、特許文献2は、3つのICチップが直列に連結された構成において、一端のチップから中央のチップを跨いで他端のチップにアクセスするための技術を開示している。

#### 【0003】

他のICチップから限られた特定のメモリ空間の範囲にのみアクセスする場合は、上記特許文献に開示するような技術を用いて十分に満足すべき結果が得られていた。

#### 【先行技術文献】

##### 【特許文献】

10

##### 【0004】

【特許文献1】特開2001-337909号公報

【特許文献2】特開2013-088879号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0005】

しかしながら、情報処理装置が画像データを処理する画像処理装置として用いられる場合、あるICチップのメモリから他のチップのメモリに対して大量のデータを転送する必要がある。この場合、他のICチップへのアクセスするためのメモリ空間が不足してしまうことがある。さらに、特許文献2のように、複数のICチップを直列に連結した構成を用いる場合、隣接するICチップとそのICチップを介して接続している別のICチップにアクセスするメモリ空間が使用される。このため、1つのICチップ当たりに割り当たられるメモリ空間がさらに制限されることになる。その結果、メモリ空間が不足して満足のゆくデータ処理性能が得られないことがある。

20

##### 【0006】

メモリ空間の不足に対応するためには、例えば、ICチップに32ビットCPUを内蔵していれば、そのCPUを単純に64ビットCPUに実装するようにすれば良い。しかしながら、64ビットCPUを実装することはコストが上昇するという問題がある。

##### 【0007】

本発明は上記従来例に鑑みてなされたもので、複数のICチップを備えた構成において1つのICチップから他のICチップのメモリ空間全域にアクセス可能な情報処理装置、及びその情報処理方法を提供することを目的としている。

30

#### 【課題を解決するための手段】

##### 【0008】

上記目的を達成するために本発明の情報処理装置は次のような構成を有する。

##### 【0009】

即ち、複数のICチップを直列接続して、前記複数のICチップによりデータを処理する情報処理装置であって、前記複数のICチップの少なくとも1つの対象ICチップは、プログラムに基づきICチップの制御を行うプログラム実行手段と、前記プログラム実行手段が第1のアドレス幅でアドレッシング可能な第1のメモリ空間と、前記第1のアドレス幅よりも大きい第2のアドレス幅でアドレッシング可能であり、前記対象ICチップとは異なる他のICチップにアクセスするための領域を含み、かつ、前記プログラム実行手段が直接アクセスすることができない第2のメモリ空間と、前記第2のメモリ空間からアクセスすることができるICチップとの間の通信を行う通信手段と、前記第1のメモリ空間と前記第2のメモリ空間の間でのアドレス変換を行うアドレス変換手段とを有し、前記第1のメモリ空間からのアクセスが行われる場合、前記アドレス変換手段が前記アクセスのアドレス値を前記第2のメモリ空間へのアドレス値に変換することにより、前記第2のメモリ空間に含まれる前記他のICチップにアクセスするための領域へのアクセスが行われ、前記第2のメモリ空間からのアクセスが行われる場合、前記アドレス変換手段が前記アクセスのアドレス値を前記第1のメモリ空間へのアドレス値に変換することにより、前

40

50

記対象 I C チップの前記第 1 のメモリ空間へのアクセスが行われることを特徴とする。

【発明の効果】

【0010】

従って本発明によれば、複数の I C チップを用いてデータを処理する際に、少ないアドレス幅でアドレッシング可能な安価な C P U を用いても、各 I C チップから他の I C チップのメモリ空間全域にアクセスすることができるという効果がある。

【図面の簡単な説明】

【0011】

【図 1】本発明の代表的な実施例であるインクジェット記録装置の構成を示すブロック図である。 10

【図 2】図 1 で示した記録装置の I C チップで用いるメモリ空間のマッピング例を示す図である。

【図 3】アドレス変換部 116 のメモリ空間のマッピング例を示す図である。

【図 4】アドレス変換部 126 のメモリ空間のマッピング例を示す図である。

【図 5】4 つの I C チップの初期動作を示すフローチャートである。

【図 6】D M A を用いた 2 つの I C チップ間のデータ転送の例を示す図である。

【図 7】C P U を用いた 2 つの I C チップ間のデータ転送の例を示す図である。

【発明を実施するための形態】

【0012】

以下添付図面を参照して本発明の好適な実施例について、さらに具体的かつ詳細に説明する。なお、以下の説明では、図面全体を通して、同じ構成要素に対して同じ参照番号を付して言及する。そのため、一度説明した構成要素に対しては同じ参照番号を用いて言及し、その説明を繰り返すことはしない。 20

【0013】

なお、この明細書において、「記録」（「プリント」という場合もある）とは、文字、図形等有意の情報を形成する場合のみならず、有意無意を問わない。さらに入人が視覚で知覚し得るように顕在化したものであるか否かも問わず、広く記録媒体上に画像、模様、パターン等を形成する、または媒体の加工を行う場合も表すものとする。

【0014】

また、「記録媒体」とは、一般的な記録装置で用いられる紙のみならず、広く、布、プラスチック・フィルム、金属板、ガラス、セラミックス、木材、皮革等、インクを受容可能なものも表すものとする。 30

【0015】

さらに、「インク」（「液体」と言う場合もある）とは、上記「記録（プリント）」の定義と同様広く解釈されるべきものである。従って、記録媒体上に付与されることによって、画像、模様、パターン等の形成または記録媒体の加工、或いはインクの処理（例えば記録媒体に付与されるインク中の色剤の凝固または不溶化）に供され得る液体を表すものとする。

【0016】

またさらに、「記録素子」とは特にことわらない限りインク吐出口乃至これに連通する液路及びインク吐出に利用されるエネルギーを発生する素子を総括して言うものとする。 40

【0017】

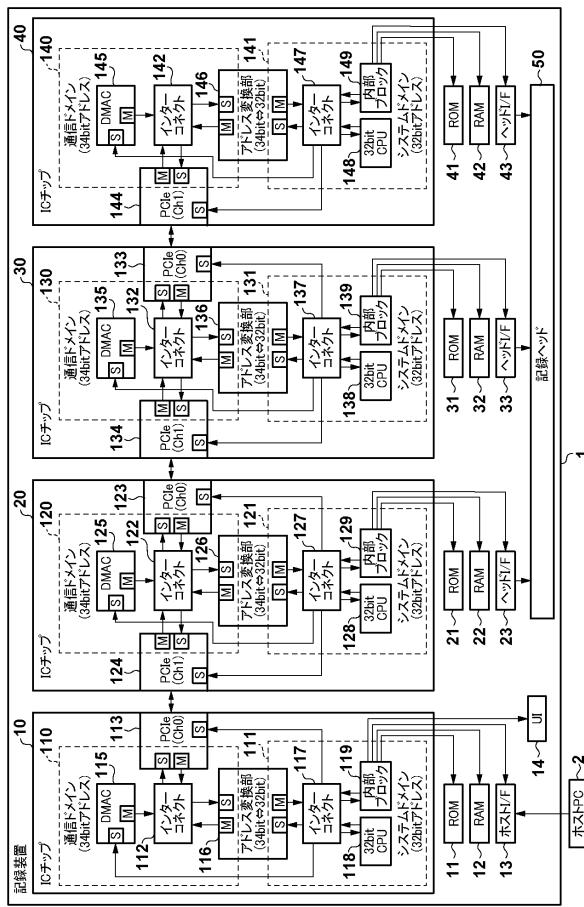

図 1 は本発明の代表的な実施例であるインクジェット記録装置の構成を示すブロック図である。

【0018】

インクジェット記録装置（以下、記録装置）は、記録媒体を搬送する搬送機構、記録ヘッドを搭載するキャリッジ、そのキャリッジを往復移動させる走査機構、記録ヘッドの吸引回復や予備吐出を行う回復機構などを備える。しかしながら、これらは公知の技術なので、その説明は省略する。また、インク液滴を吐出する記録ヘッドそのものの構成や、その記録ヘッドに実装する素子基板も公知の技術を用いるので、その説明は省略する。 50

**【0019】**

従って、図1は、画像データを生成して記録装置1に送信するホストPC2とのインターフェース処理を行うICチップ10が図示されている。また、画像データに対して画像処理を実行して記録ヘッド50に転送する処理を行うICチップ20～40の構成が図示されている。このため、図1に示す構成は画像処理装置としての役割を果たす。

**【0020】**

次に、上記のような4つのICチップを実装した記録装置1の内部構成を説明する。

**【0021】**

ICチップ10は、ROM11とRAM12とホストインターフェース(I/F)13とUI(ユーザインターフェース)14と接続している。また、ICチップ20は、ROM21とRAM22とヘッドインターフェース(I/F)23と接続している。ICチップ30は同様に、ROM31とRAM32とヘッドインターフェース(I/F)33と接続している。ICチップ40も同様に、ROM41とRAM42とヘッドインターフェース(I/F)43と接続している。10

**【0022】**

ホストI/F13は、ホストPC2との通信を行うインターフェースであり、UI14はスイッチやLCDやLEDランプを備えた操作パネルで構成され、ユーザから記録装置に対する指示を受付、ユーザに対して情報を報知する。

**【0023】**

記録媒体にインクを吐出して画像を記録する記録ヘッド50は、3つのヘッドI/F23、33、43を介して、3つのICチップ20、30、40にそれぞれ接続される。ICチップ10とICチップ20との間、ICチップ20とICチップ30との間、ICチップ30とICチップ40との間はそれぞれPCI-Express(以下、PCIe)により接続される。20

**【0024】**

ICチップ10は、ROM11に格納された制御プログラムを読み出し、RAM12を作業領域として用いて実行し、ホストPC2とのインターフェース処理に加えて、記録装置全体の制御やUIの制御や各種駆動機構の制御等を行う。また、RAM12には、PC2から転送された画像データを一時的に記憶するために画像メモリが設けられる。

**【0025】**

図1から分かるように、ICチップ20、30、40は、夫々に専用のヘッドI/Fを介して記録ヘッド50に接続される。ICチップ20、30、40は、記録ヘッドが扱う複数の色のインクに対応して生成される各色成分の画像データを処理するように割当てられる。例えば、記録ヘッド50が12色のインクを吐出する構成である場合、ホストPC2から転送された画像データは12色の色成分データに分解される。例えば、12色のインクとは、以下の通りである。即ち、

マットブラック(MBK)と、フォトブラック(PBK)と、シアン(C)と、

マゼンタ(M)と、イエロ(Y)と、フォトシアン(PC)と、

フォトマゼンタ(PM)と、グレー(GY)と、フォトグレー(PGY)と、

レッド(R)と、ブルー(B)と、クロマオブティマイザー(CO)とである。40

**【0026】**

これら12の色成分データの画像処理が、4つの色成分データずつICチップ20、30、40に割当てられる。なお、以上のような色成分データの割当ては一例に過ぎず、記録ヘッドの仕様やICチップの性能により異なる割当てが可能であることは言うまでもない。例えば、記録ヘッドが6色のインク(ブラック、マットブラック、シアン、マゼンタ、イエロ、レッド)に対応している仕様であれば、各ICチップに2つの色成分データを割当てられても良い。また、ICチップ20を各色成分に共通の画像処理を割当て、ICチップ30、40にそれぞれ、6つの色成分データずつの画像処理を割当てるよう構成しても良い。

**【0027】**

50

以下、4つのI Cチップの内部構成について説明するが、この実施例では32ビットアーキテクチャのCPUを実装した、同じ構成の4つのI Cチップを直列接続して用いるものとする。図1に示されているように、4つのI Cチップ10、20、30、40はそれぞれ、34ビットアドレッシング可能な通信ドメイン110、120、130、140と、32ビットアドレッシング可能なシステムドメイン111、121、131、141を備える。なお、この実施例では、通信ドメインのアドレス幅はシステムドメインのアドレス幅よりも2ビット大きくなっている。このアドレス幅のサイズについては後述する。なお、この実施例では、通信ドメインのアドレス幅はシステムドメインのアドレス幅よりも大きく、その差は2ビットであるが、それに限らず、その差がnビット(nは自然数)でも良い。なお、アドレスサイズの観点で言い換えると、通信ドメインのアドレスサイズはシステムドメインのアドレスサイズより大きく、その差はnビットに対して $2^n$ 倍のサイズとなる(nは自然数)。そして、4つのI Cチップにはそれぞれ、これら2つのドメインの間を接続するためのアドレス変換部116、126、136、146を備える。

#### 【0028】

I Cチップ10は、通信ドメイン110にインターフェース112とDMA115とを備え、システムドメイン111にインターフェース117と32ビットCPU(以下、CPU)118とI Cチップ外の機器を接続する内部ブロック119を備える。内部ブロック119は、ROMコントローラ、RAMコントローラ、及び、他の機器とのインターフェースコントローラとしての役割を果たす。また、I Cチップ10は、I Cチップ20との通信を行うPCIeインターフェース113を備える。

#### 【0029】

通信ドメイン110はPCIeインターフェース113やDMA115を用いて他のチップとの通信を行うためのドメインである。システムドメイン111はCPU118の直接の制御によりI Cチップ内の制御を行うためのドメインである。アドレス変換部116は通信ドメイン110とシステムドメイン111との間でのアドレス空間のアドレス変換を行う。具体的なアドレス変換方法は後述する。

#### 【0030】

なお、図1に記載された記号「M」は「Master」を表し、記号「S」は「Slave」を表している。「Master」は内部バスの主導権を取り、「Slave」に対してライト/リードアクセスを行う。

#### 【0031】

I Cチップ20は、通信ドメイン120にインターフェース122とDMA125とを備え、システムドメイン121にインターフェース127とCPU128とI Cチップ外の機器を接続する内部ブロック129を備える。内部ブロック129は、ROMコントローラ、RAMコントローラ、及び、他の機器とのインターフェースコントローラとしての役割を果たす。また、I Cチップ20は、I Cチップ10との通信を行うPCIeインターフェース113とI Cチップ30との通信を行うPCIeインターフェース123とを備える。

#### 【0032】

同様にI Cチップ30は、通信ドメイン130にインターフェース132とDMA135とを備え、システムドメイン131にインターフェース137とCPU138とI Cチップ外の機器を接続する内部ブロック139を備える。内部ブロック139は、ROMコントローラ、RAMコントローラ、及び、他の機器とのインターフェースコントローラとしての役割を果たす。また、I Cチップ30は、I Cチップ20との通信を行うPCIeインターフェース134とI Cチップ40との通信を行うPCIeインターフェース133とを備える。

#### 【0033】

最後のI Cチップ40は、通信ドメイン140にインターフェース142とDMA145とを備え、システムドメイン141にインターフェース147とCPU148とI Cチップ外の機器を接続する内部ブロック149を備える。内部ブロック149は、ROM

10

20

30

40

50

コントローラ、RAMコントローラ、及び、他の機器とのインターフェースコントローラとしての役割を果たす。また、ICチップ40は、ICチップ30との通信を行うPCIeインターフェース144を備える。

#### 【0034】

PCIeインターフェース113、123、133をPCIe(Ch0)と呼び、PCIeインターフェース124、134、144をPCIe(Ch1)と呼んで区別する。

#### 【0035】

以上のような構成の記録装置において、ICチップ10がホストI/F13を介してホストPC2から転送された印刷ジョブを受信すると、ICチップ10は印刷モード等に従って画像処理を実行する。その後、画像処理が施された画像データがICチップ10からICチップ20、ICチップ30、ICチップ40に転送される。10

#### 【0036】

ICチップ間で転送される画像データは、印刷モードによってRGBデータである場合やCMYKデータである場合もある。また、ICチップ20、30、40の間でも、コマンド通信や画像処理後のデータを他の処理に用いる場合はデータ転送を実行することがあり得る。ICチップ20、30、40で処理されたデータは記録ヘッド50に転送され、記録ヘッド50は記録媒体へインクを吐出して画像を記録する。

#### 【0037】

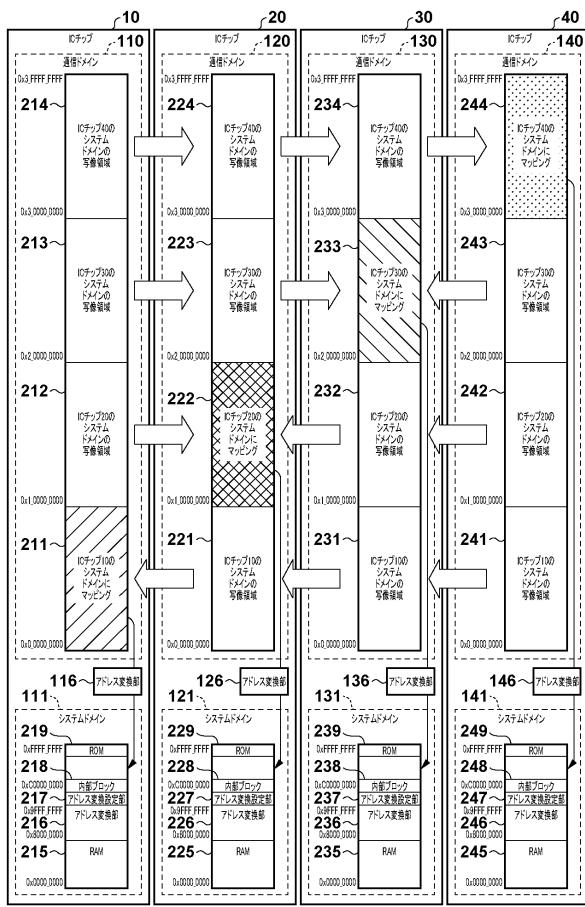

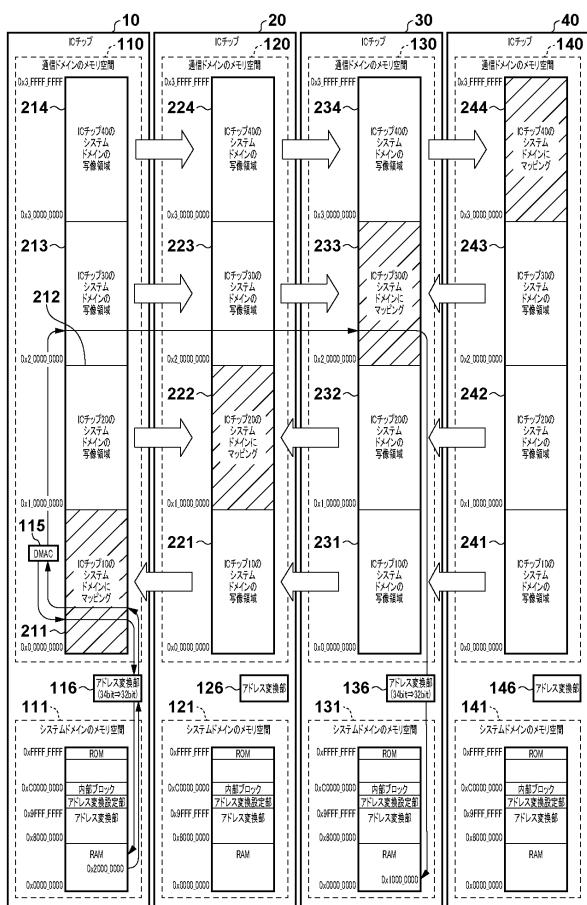

図2は図1で示した記録装置のICチップで用いるメモリ空間のマッピング例を示す図である。図2では各ドメインをメモリ空間の視点で図示している。20

#### 【0038】

まず、ICチップ10のメモリ空間について説明する。

#### 【0039】

システムドメイン111はCPU118から直接制御できるメモリ空間である。CPU118は32ビットCPUであるため0x0000\_0000から0xFFFF\_FFFFまでのアドレス(4GB空間)にアクセスできる。一方、通信ドメイン110は34ビット空間であり、この空間にあるマスタ(図1におけるDMAC115)は0x0\_0000\_0000から0x3\_FFFF\_FFFFまでのアドレス(16GB空間)にアクセスできる。30

#### 【0040】

ICチップ20、ICチップ30、ICチップ40が用いるメモリ空間についても同様である。

#### 【0041】

ここで、通信ドメイン110、120、130、140のメモリ空間のマッピングを説明する。なお、通信方法の詳細については後述する。

#### 【0042】

アドレス空間211、221、231、241はそれぞれ、0x0\_0000\_0000から0x0\_FFFF\_FFFFのメモリ空間(4GB空間)であって、アドレス空間211はICチップ10のシステムドメイン111にマッピングされている。アドレス空間221、231、241はアドレス空間211の写像領域であって、通信マスタとなるDMAC及びCPUがアドレス空間221、231、241にアクセスすると、そのアクセスはPCIeを介してアドレス空間211に転送される。40

#### 【0043】

アドレス空間212、222、232、242はそれぞれ、0x1\_0000\_0000から0x1\_FFFF\_FFFFのメモリ空間(4GB空間)であって、アドレス空間222はICチップ20のシステムドメイン121にマッピングされている。アドレス空間212、232、242はアドレス空間222の写像領域であって、通信のマスタとなるDMAC及びCPUがアドレス空間212、232、242にアクセスすると、そのアクセスはPCIeを介してアドレス空間222に転送される。

#### 【0044】

10

20

30

40

50

アドレス空間 213、223、233、243はそれぞれ、 $0 \times 2_0000_000$ から $0 \times 2_FFFF_FFFF$ のメモリ空間(4GB空間)であって、アドレス空間233はI Cチップ30のシステムドメイン131にマッピングされている。アドレス空間213、223、243はアドレス空間233の写像領域であって、通信のマスタとなるD M A C及びC P Uがアドレス空間213、223、243にアクセスすると、そのアクセスはP C I eを介してアドレス空間233に転送される。

#### 【0045】

アドレス空間214、224、234、244はそれぞれ、 $0 \times 3_0000_000$ から $0 \times 3_FFFF_FFFF$ のメモリ空間(4GB空間)であって、アドレス空間244はI Cチップ40のシステムドメイン141にマッピングされている。アドレス空間214、224、234はアドレス空間244の写像領域であって、通信のマスタとなるD M A C及びC P Uがアドレス空間214、224、234にアクセスすると、そのアクセスはP C I eを介してアドレス空間244に転送される。10

#### 【0046】

次に、4つのアドレス変換部が実行するアドレス変換について説明する。

#### 【0047】

- ・アドレス変換部116

通信ドメイン110からシステムドメイン111へのアクセスのアドレス変換は、以下のように実行する。

#### 【0048】

通信ドメイン110のメモリ空間のうち、 $0 \times 0_0000_0000$ から $0 \times 0_FFFF_FFFF$ のメモリ空間(4GB空間)がシステムドメイン111にマッピングされている。この場合、アドレス変換部116は、通信ドメイン110から受信した転送のアドレス上位2ビット(アクセス先となるI Cチップ10を特定する情報)が“ $0 \times 0$ ”であったならば、このアドレス上位2ビットを取り除きシステムドメイン111へ転送する。なお、“ $0 \times 0$ ”を指定してI Cチップ20～40からI Cチップ10へ送信されるデータの一例としてインクの不吐に関する情報が挙げられる。例えば、I Cチップ40があるノズルがインクを吐出できないことを認識した場合、不吐に関する情報にアドレス(上位2ビットに“ $0 \times 0$ ”)を設定して転送する。アドレス変換部116は、この不吐に関する情報に設定された上位2ビットの“ $0 \times 0$ ”を取り除いて、システムドメインに転送する。その結果、I Cチップ10は、不吐のノズルにより記録できなかった分を補完するためのデータをI Cチップ40に対して送信することができる。2030

#### 【0049】

- ・アドレス変換部126

通信ドメイン120からシステムドメイン121へのアクセスのアドレス変換は、以下のように実行する。

#### 【0050】

通信ドメイン120のメモリ空間のうち、 $0 \times 1_0000_0000$ から $0 \times 1_FFFF_FFFF$ のメモリ空間(4GB空間)がシステムドメイン121にマッピングされている。この場合、アドレス変換部126は、通信ドメイン120から受信した転送のアドレス上位2ビット(アクセス先となるI Cチップ20を特定する情報)が“ $0 \times 1$ ”であったならば、このアドレス上位2ビットを取り除きシステムドメイン121へ転送する。40

#### 【0051】

- ・アドレス変換部136

通信ドメイン130からシステムドメイン131へのアクセスのアドレス変換は、以下のように実行する。

#### 【0052】

通信ドメイン130のメモリ空間のうち、 $0 \times 2_0000_0000$ から $0 \times 2_FFFF_FFFF$ のメモリ空間(4GB空間)がシステムドメイン131にマッピングさ50

れている。この場合、アドレス変換部 136 は、通信ドメイン 130 から受信した転送のアドレス上位 2 ビット（アクセス先となる I C チップ 30 を特定する情報）が“0 × 2”であったならば、このアドレス上位 2 ビットを取り除きシステムドメイン 131 へ転送する。

#### 【0053】

- ・アドレス変換部 146

通信ドメイン 140 からシステムドメイン 141 へのアクセスのアドレス変換は、以下のように実行する。

#### 【0054】

通信ドメイン 140 のメモリ空間のうち、 $0 \times 3\_0\ 0\ 0\ 0\_0\ 0\ 0\ 0$  から  $0 \times 3\_F\ F\ F\_F\ F\ F\ F$  のメモリ空間（4 GB 空間）がシステムドメイン 141 にマッピングされている。10 この場合、アドレス変換部 146 は、通信ドメイン 140 から受信した転送のアドレス上位 2 ビット（アクセス先となる I C チップ 40 を特定する情報）が“0 × 3”であったならば、このアドレス上位 2 ビットを取り除きシステムドメイン 141 へ転送する。

#### 【0055】

なお、上述されている通り、I C チップ 10 から I C チップ 20 ~ 40 に対しては色成分データが送信される。この際、例えば、I C チップ 10 が、I C チップ 20 に対して色成分データを転送する場合は、色成分データにアドレス（上位 2 ビットが“0 × 1”）を設定してデータを転送する。また、I C チップ 20 ~ 40 のいずれかにおいて画像処理が実行される場合、I C チップ 20 ~ 40 間でデータ転送が行われる。例えば、I C チップ 40 が画像処理を実行する場合、一部の処理として I C チップ 20 の処理が必要である場合、I C チップ 40 は、画像処理に関わるデータにアドレス（上位 2 ビットが“0 × 1”）を設定してデータを転送する。20

#### 【0056】

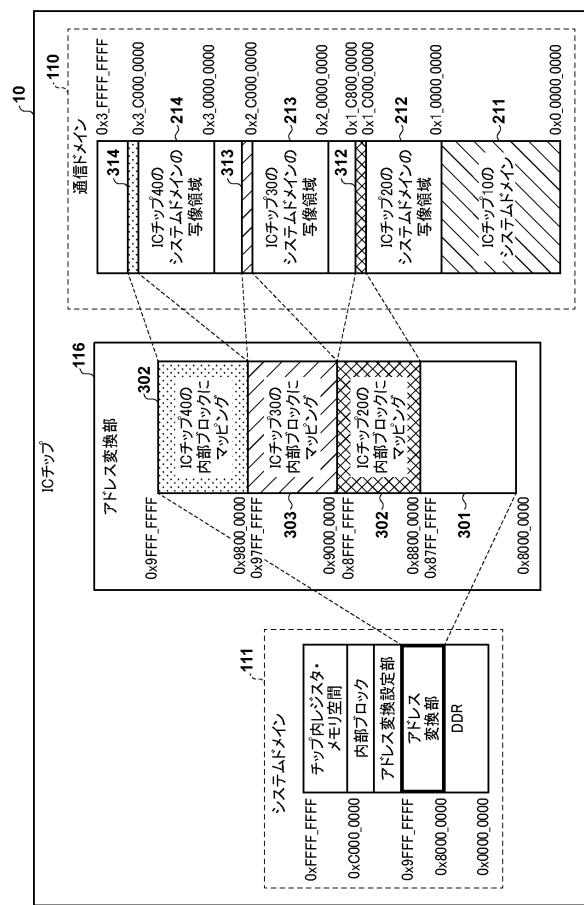

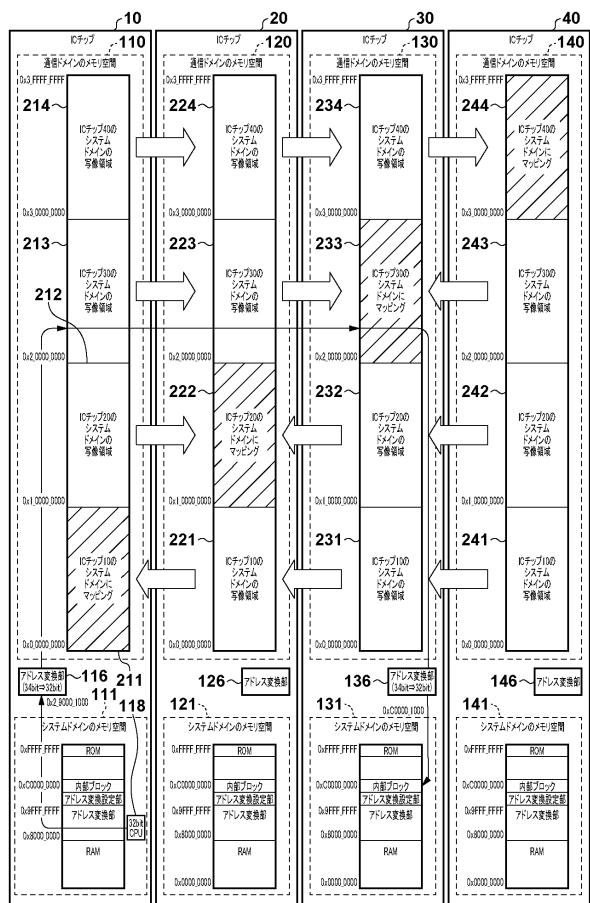

図 3 はアドレス変換部 116 のメモリ空間のマッピング例を示す図である。

#### 【0057】

ここで、図 3 を参照して、アドレス変換部 116 が実行するシステムドメイン 111 から通信ドメイン 110 へのアクセスのアドレス変換について説明する。

#### 【0058】

システムドメイン 111 に示されるように、アドレス変換部 116 はメモリ空間のうち  $0 \times 8\ 0\ 0\ 0\_0\ 0\ 0\ 0$  から  $0 \times 9\ F\ F\ F\_F\ F\ F\ F$  (512 MB 空間) を確保する。アドレス変換部 116 では、領域 302 ( $0 \times 8\ 8\ 0\ 0\_0\ 0\ 0\ 0$  から  $0 \times 8\ F\ F\ F\_F\ F\ F$ ) を I C チップ 20 の内部ブロックにマッピングする。この場合、変換元のベースアドレス  $0 \times 8\ 8\ 0\ 0\_0\ 0\ 0\ 0$  を変換先のベースアドレス  $0 \times 1\_C\ 0\ 0\ 0\_0\ 0\ 0\ 0$  に変換してデータを通信ドメイン 110 へ転送する。従って、CPU 118 は、領域 302 へアクセスすることでアドレス空間 212 へアクセスすることができ、図 2 で説明したメモリ空間を介して I C チップ 20 のメモリ空間にアクセスすることができる。30

#### 【0059】

また、領域 303 ( $0 \times 9\ 0\ 0\ 0\_0\ 0\ 0\ 0$  から  $0 \times 9\ 7\ F\ F\_F\ F\ F\ F$ ) を I C チップ 30 の内部ブロックにマッピングする。この場合、変換元のベースアドレス  $0 \times 9\ 0\ 0\_0\ 0\ 0\ 0$  を変換先のベースアドレス  $0 \times 2\_C\ 0\ 0\ 0\_0\ 0\ 0\ 0$  に変換してデータを通信ドメイン 110 へ転送する。従って、CPU 118 は領域 303 へアクセスすることでアドレス空間 213 へアクセスすることができ、図 2 で説明したメモリ空間を介して I C チップ 30 のメモリ空間にアクセスすることができる。40

#### 【0060】

同様に、領域 304 ( $0 \times 9\ 8\ 0\ 0\_0\ 0\ 0\ 0$  から  $0 \times 9\ F\ F\ F\_F\ F\ F\ F$ ) を I C チップ 40 の内部ブロックにマッピングする。この場合、変換元のベースアドレス  $0 \times 9\ 8\ 0\ 0\_0\ 0\ 0\ 0$  を変換先のベースアドレス  $0 \times 3\_C\ 0\ 0\ 0\_0\ 0\ 0\ 0$  に変換してデータを通信ドメイン 110 へ転送する。従って、CPU 118 は領域 304 へアクセスするこ50

とでアドレス空間 214へアクセスすることができ、図2で説明したメモリ空間を介して I Cチップ40のメモリ空間にアクセスすることができる。

#### 【0061】

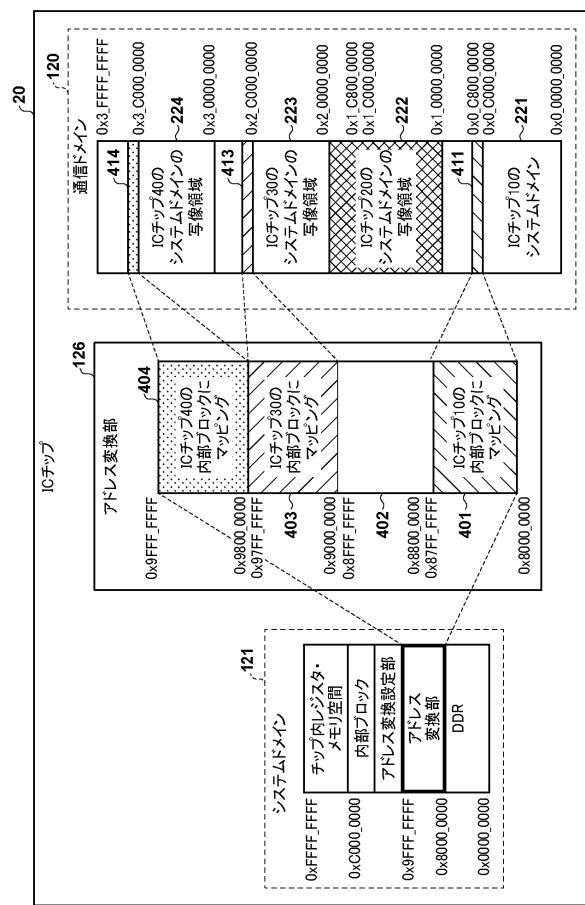

図4はアドレス変換部126のメモリ空間のマッピング例を示す図である。

#### 【0062】

ここで、図4を参照して、アドレス変換部126が実行するシステムドメイン121から通信ドメイン120へのアクセスのアドレス変換の機能について説明する。

#### 【0063】

システムドメイン121に示されるように、アドレス変換部126はメモリ空間のうち 0x8000\_0000から0x9FFF\_FFFF(512MB空間)を確保する。アドレス変換部126では、領域401(0x8000\_0000から0x87FF\_FFF)をI Cチップ10の内部ブロックにマッピングする。この場合、変換元のベースアドレス0x8000\_0000を変換先のベースアドレス0x0\_C000\_0000に変換してデータを通信ドメイン120へ転送する。CPU128は領域401へアクセスすることでアドレス空間221へアクセスすることができ、図2で説明したメモリ空間を介してI Cチップ10のメモリ空間にアクセスすることができる。10

#### 【0064】

また、領域403(0x9000\_0000から0x97FF\_FFFF)をI Cチップ30の内部ブロックにマッピングする。この場合、変換元のベースアドレス0x9000\_0000を変換先のベースアドレス0x2\_C000\_0000に変換してデータを通信ドメイン110へ転送する。従って、CPU128は領域403へアクセスすることでアドレス空間223へアクセスすることができ、図2で説明したメモリ空間を介してI Cチップ30のメモリ空間にアクセスすることができる。20

#### 【0065】

同様に、領域404(0x9800\_0000から0x9FFF\_FFFF)をI Cチップ40の内部ブロックにマッピングする。この場合、変換元のベースアドレス0x9800\_0000を変換先のベースアドレス0x3\_C000\_0000に変換してデータを通信ドメイン110へ転送する。従って、CPU128は領域404へアクセスすることでアドレス空間224へアクセスすることができ、図2で説明したメモリ空間を介してI Cチップ40のメモリ空間にアクセスすることができる。30

#### 【0066】

アドレス変換部136、アドレス変換部146についても同様の機能を備える。

#### 【0067】

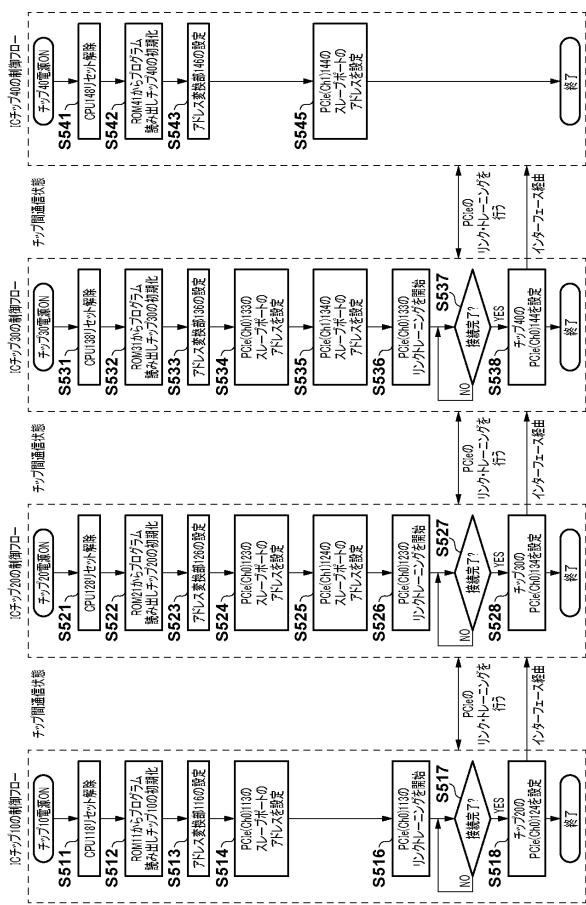

図5は4つのI Cチップの初期動作を示すフローチャートである。

#### 【0068】

- ・ I Cチップ10の制御フロー

電源が投入されると、ステップS511では、CPU118のリセットを解除する。次に、ステップS512では、CPU118はROM11から制御プログラムを読み出し、I Cチップ10を初期化する。さらに、ステップS513では、アドレス変換部116の初期設定を行う。ここでは、図3を参照して説明したアドレス変換が可能なように設定を行う。40

#### 【0069】

ステップS514では、CPU118は、PCIe(Ch0)113のスレーブポートのアドレス設定を行う。ここでは、図2を参照して説明したアドレス空間212、213、214へのアクセスがあった場合、CPU118は、そのアクセスをI Cチップ20に転送する設定を行う。上述したように図3にて説明したアドレス変換が可能なようにS513の初期設定が行われているため、アドレス空間212、213、214へのアクセスがあった場合、CPU118は、そのアクセスをI Cチップ20に転送できる。さらにステップS516では、CPU118は、PCIe(Ch0)113のリンク・トレーニングを開始し、ステップS517では、リンク・トレーニングの完了を待ち合わせる。そし50

て、リンク・トレーニングが完了し、PCIe(Ch0)113の接続完了が確認されたなら、ステップS518において、CPU118は、ICチップ20のPCIe(Ch1)124を設定する。

#### 【0070】

- ・ICチップ20の制御フロー

電源が投入されると、ステップS521では、CPU128のリセットを解除する。次に、ステップS522では、CPU128はROM21から制御プログラムを読み出し、ICチップ20を初期化する。さらに、ステップS523では、アドレス変換部126の初期設定を行う。ここでは、図4を参照して説明したアドレス変換が可能なように設定を行う。

10

#### 【0071】

ステップS524では、CPU128は、PCIe(Ch0)123のスレーブポートのアドレス設定を行う。ここでは、図2を参照して説明したアドレス空間223、224へのアクセスがあった場合、CPU128は、そのアクセスをICチップ30に転送する設定を行う。さらにステップS525では、CPU128は、PCIe(Ch1)124のスレーブポートのアドレス設定を行う。ここでは、図2を参照して説明したアドレス空間221へのアクセスがあった場合、CPU128は、そのアクセスをICチップ10に転送する設定を行う。ステップS526では、CPU128は、PCIe(Ch0)123のリンク・トレーニングを開始し、ステップS527では、リンク・トレーニングの完了を待ち合わせる。そして、リンク・トレーニングが完了し、接続完了が確認されたなら、ステップS528において、CPU128は、ICチップ30のPCIe(Ch1)134を設定する。

20

#### 【0072】

- ・ICチップ30の制御フロー

電源が投入されると、ステップS531では、CPU138のリセットを解除する。次に、ステップS532では、CPU138はROM31から制御プログラムを読み出し、ICチップ30の初期化を行う。さらに、ステップS533では、アドレス変換部136の設定を行う。ここでは、図4を参照して説明したアドレス変換と同様なことが可能なように設定を行う。

30

#### 【0073】

ステップS534では、CPU138は、PCIe(Ch0)133のスレーブポートのアドレス設定を行う。ここでは、図2を参照して説明したアドレス空間234へのアクセスがあった場合、そのアクセスをICチップ40に転送する設定を行う。さらにステップS535では、CPU138は、PCIe(Ch1)134のスレーブポートのアドレス設定を行う。ここでは、図2を参照して説明したアドレス空間231、232へのアクセスがあった場合、CPU138は、そのアクセスをICチップ20に転送する設定を行う。ステップS536では、CPU138は、PCIe(Ch0)133のリンク・トレーニングを開始し、ステップS537では、リンク・トレーニングの完了を待ち合わせる。そして、リンク・トレーニングが完了し、接続完了が確認されたなら、ステップS538において、CPU138は、ICチップ40のPCIe(Ch1)144を設定する。

40

#### 【0074】

- ・ICチップ40の制御フロー

電源が投入されると、ステップS541では、CPU148のリセットを解除する。次に、ステップS542では、CPU148はROM41から制御プログラムを読み出し、ICチップ40の初期化を行う。さらに、ステップS543では、アドレス変換部146の設定を行う。ここでは、図4を参照して説明したアドレス変換と同様なことが可能なように設定を行う。

#### 【0075】

ステップS545では、CPU148は、PCIe(Ch1)144のスレーブポートのアドレス設定を行う。ここでは、図2を参照して説明したようにアドレス空間241、

50

242、243へのアクセスがあった場合、そのアクセスをICチップ30に転送する設定を行う。

#### 【0076】

以上の処理を実行し、4つのICチップを通信可能となれば、図2に示したメモリマップで他のICチップへのデータ転送が可能になる。

#### 【0077】

次に、4つのICチップが通信可能となった状態でのDMAを用いたデータ転送について説明する。

#### 【0078】

図6はDMAを用いた2つのICチップ間のデータ転送の例を示す図である。

10

#### 【0079】

図6におけるメモリマップは図2と同様であり、図6には、ICチップ10に接続したRAM12の0x2000\_0000から、ICチップ30に接続したRAM32の0x1000\_0000にDMA転送を行う例が図示されている。

#### 【0080】

ICチップ10のCPU118がDMAC115に転送元アドレスと転送先アドレスとデータ長を設定することでDMA転送を実行する。この例では、ICチップ10のシステムドメイン111にマッピングされた領域のうちRAMのアドレス0x0\_2000\_000を転送元アドレスとする。また、ICチップ30のシステムドメイン131にマッピングされた領域のうちRAMに該当するアドレス0x2\_1000\_0000を転送先アドレスとする。その他、所定の転送長等の指定をしてDMA転送を実行する。

20

#### 【0081】

DMA転送の実行が開始すると、DMAC115は転送元アドレスにリード・トランザクションを発行する。アドレス変換部116はリード・トランザクションを受信すると、アドレスの上位2ビットを取り除きシステムドメイン111にリード・トランザクションを発行する。アドレス変換部116は所定のアドレスからリードデータを読み出すと、DMAC115にリードデータを返す。

#### 【0082】

DMAC115は読み出したデータを転送先アドレスにライト・トランザクションを発行する。通信ドメイン110のアドレス空間213にライト・トランザクションを発行すると、PCIeを介してICチップ30の通信ドメイン130のアドレス空間233にデータが転送される。アドレス空間233に転送されたデータはアドレス変換部136に転送される。アドレス変換部136ではアドレス上位2ビットを取り除いてシステムドメイン131にそのデータを転送し、所定の場所に書き込まれる。

30

#### 【0083】

上記の例では1つのICチップ(ICチップ10)から他のICチップ(ICチップ30)にデータを転送する方法を示したが、同様に逆方向に他のICチップから自ICチップにデータを転送することもDMAの転送元、転送先の設定により可能である。

#### 【0084】

さらに、4つのICチップが通信可能となった状態でのCPUを用いたデータ転送について説明する。

40

#### 【0085】

図7はCPUを用いた2つのICチップ間のデータ転送の例を示す図である。

#### 【0086】

図7において、メモリマップは図2と図3とに示したものと同様であり、図7には、ICチップ10のCPU118からICチップ30の内部ブロック139にライト転送を行う例が図示されている。転送先アドレスは0xC000\_1000とする。

#### 【0087】

ICチップ10のCPU118は、図3で説明したICチップ30の内部ブロック139にマッピングされた領域303にライト・トランザクションを発行する。転送アドレス

50

は $0 \times C000\_0000$ をベースアドレスとして $0 \times 9000\_0000$ からのオフセットを指定する。この例の場合、 $0 \times C000\_1000$ にアクセスしようとしているので、 $0 \times 9000\_1000$ にアクセスする。

#### 【0088】

アドレス変換部116はライト・トランザクションを受信すると、 $0 \times 9000\_1000$ を $0 \times 2\_C000\_1000$ に変換して通信ドメイン110にライト・トランザクションを発行する。通信ドメイン110のアドレス空間213にライト・トランザクションを発行すると、PCIeを介してICチップ30の通信ドメイン130のアドレス空間233に転送される。アドレス空間233に転送されたデータはアドレス変換部136に転送される。アドレス変換部136ではアドレス上位2ビットを取り除いてシステムドメイン131に転送し、内部ブロックの $0 \times C000\_1000$ にライトされる。10

#### 【0089】

上記の例では1つのICチップ(ICチップ10)から他のICチップ(ICチップ30)にライト・トランザクションを発行する例を示したが、同様に逆方向のリード・トランザクションも可能である。

#### 【0090】

以上説明した実施例に従えば、システムを構成する複数のICチップは互いのメモリ空間の全領域にアクセスすることができる。このため、大容量のメモリを用いる際にも高機能で高コストの64ビットCPUを使用せずに、安価な32ビットCPUを使用することが可能なので、装置全体のコストを抑えることができる。20

#### 【0091】

更に以上説明した実施例では、アドレス変換部がシステムドメインと通信ドメインの間に設けられているため、あるICチップから他のICチップへのアクセスにおいて、中間のICチップを通過するアクセスがそのアドレス変換部を通過しない。言い換えると、中間のICチップのアドレス変換部はデータ転送においてバイパスされる。仮にICチップを通過するアクセス途中にアドレス変換部が存在していると、各ICチップのシステムドメインの都合で設定を変えることができない。しかし、この構成であれば各ICチップのシステムドメインの都合でアドレス変換部の設定を変更可能であるので、柔軟にシステムを構築することができるという利点がある。

#### 【0092】

また以上説明した実施例では、4つのICチップのメモリ空間全体にアクセス可能なように、使用する32ビットCPUに対応してシステムドメインのアドレス幅が32ビットであるのに対し、通信ドメインのアドレス幅を34ビットとした。これによって、通信ドメインのアドレス空間では2ビットを4つのICチップを識別可能な情報として用いることができ、その結果、各ICチップが他のICチップのシステムドメインのメモリ空間に対してアクセス可能となる。

#### 【0093】

なお、以上説明した実施例では、ICチップの数を“4”、システムドメインのアドレス幅を32ビット、通信ドメインのアドレス幅を34ビットとしたが、本発明はこれによって限定されるものではない。システムドメインと通信ドメインのアドレス幅の差が、 $2^n$ ビットであり、nが自然数である条件を満たすなら、ICチップの数は“4”である必要はない。例えば、32ビットCPUを使用する場合でも、n=3であれば、通信ドメインのアドレス幅を35ビット、ICチップの数を“8”としたり、n=4であれば、通信ドメインのアドレス幅を36ビット、ICチップの数を“16”とすることもできる。40

#### 【0094】

8つのICチップを用いる場合、例えば、1つのICチップを記録装置の全体制御とホストPCとの通信に割当て、別の1つのICチップを色共通の画像処理のために割当て、残りの6つを各色成分データの画像処理専用のチップとして割当てることができる。ここで、インク色の数が12なら各ICチップに2つの色成分データの処理を割当て、インク色の数が6なら各ICチップに1つの色成分データの処理を割当てることができる。50

**【0095】**

さらに、例えば、通信ドメインのアドレス幅を標準的な64ビットとしてもよい。またさらに、アドレス幅ビットをそれより小さくしつつも、I Cチップの一部、例えば、メモリ空間の半分だけでもマッピング可能にしても良い。その場合、他のI Cチップのメモリ空間全体にアクセスできなくとも、アクセス可能なメモリ空間の範囲を広げができる。

**【0096】**

またさらに、以上説明した実施例では、全てのI Cチップが通信ドメインとシステムドメインを備えるとしたが、本発明はこれによって限定されるものではない。例えば、I Cチップを直列接続して構成するシステムである場合に、両端を除く、データを中継するI Cチップのみが上記の構成をとるようしても良い。例えば3つのI CチップA、B、Cが直列接続されたシステムを想定する。このシステムにおいて、左端のI CチップAが64ビットCPUで、右端のI CチップCが32ビット幅のアドレス空間しか持たないチップであったとする。しかしながら、この状況であっても、I CチップAとCの間にあるI CチップCが本実施形態の構成を備えており、かつ、I CチップAのメモリ空間内に4GB×2の空間を確保すれば、I CチップAはI CチップB - Cの全てのメモリ空間をマッピングできる。つまり、複数のI Cチップの内、少なくとも1つがこの実施例で説明した構成であれば良い。

**【0097】**

またさらに、以上説明した実施例では記録装置を例として挙げたが、本発明を適用可能な装置は記録装置に限定されるものではない。例えば、パソコン等の情報処理装置やサーバ装置などデータ転送が必要な機器に、上記のような通信制御を行う構成が用いられているなら、本発明は適用可能である。

**【符号の説明】****【0098】**

- 1 記録装置(画像処理装置)、2 ホストPC、

10、20、30、40 I Cチップ、11、21、31、41 ROM、

12、22、32、42 RAM

10

20

【 図 1 】

【図2】

【図3】

【 四 4 】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開2014-016749(JP,A)

特開2008-003867(JP,A)

特開2013-088879(JP,A)

特開2008-067242(JP,A)

米国特許出願公開第2016/0350241(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F      12 / 00 -    12 / 06

G 06 F      13 / 14

G 06 F      13 / 16 -    13 / 18

B 41 J      29 / 38