(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2000-7007127   | (65) 공개번호   | 10-2001-0033614 |

| (22) 출원일자   | 2000년06월24일       | (43) 공개일자   | 2001년04월25일     |

| 번역문 제출일자    | 2000년06월24일       |             |                 |

| (86) 국제출원번호 | PCT/JP1998/005770 | (87) 국제공개번호 | WO 1999/34445   |

| 국제출원일자      | 1998년12월21일       | 국제공개일자      | 1999년07월08일     |

(81) 지정국 국내특허 : 중국, 대한민국, 미국, 싱가포르,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드, 사이프러스,

(30) 우성권주장 1997-359271 1997년 12월 26일 일본(JP)

(73) 특히권자 가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 6고

(72) 발명자 미즈노, 히로유끼

일본 185-8601 도쿄도 고꾸분지시 히가시고이가꾸보 1-280 가부시키가이

야히타치 세이사쿠 쇼중앙연구소내

이시바시고이찌로

일본185-8601도쿄도고꾸분지시히가시고이가꾸보1-280가부시키가이

샤히타치세이사쿠쇼중앙연구소내

시무라, 다까노리

일본 185-8601 도쿄도 고꾸분지 시히가시 고이가꾸보 1-280 가부시키 가이

샤히타치 세이사 쿠쇼 중앙 연구소 내

핫또리, 도시히로

일본 187-8588 도쿄도 고다이라시 죠우스 이촌 쪽 5-20-1 가부시키가이샤

히타치 세이사쿠 쿠션 밤도체 사업 분부내

(74) 대리인 장수길

구영창

심사관 : 정병홍

#### (54) 반도체 집적 회로 장치

요약

고속성, 저전력성, 신뢰성을 양립한 마이크로 프로세서 등의 반도체 집적 회로 장치를 실현하도록, 반도체 기판 상에 구성된 트랜지스터를 구비하는 주회로(LOG)와, 기판에 인가되는 전압을 제어하는 기판 바이어스 제어 회로(VBC)를 구비하고, 주회로는 기판에 인가되는 전압을 제어하는 스위치 트랜지스터(MN1, MP1)를 구비하고, 기판 바이어스 제어 회로로 부터 출력된 제어 신호가 스위치 트랜지스터의 게이트에 입력되고 있으며 또한 제어 신호는 기판 바이어스 제어 회로로 되돌아가도록 구성되어 있다.

## 내포도

도 1

## 색인어

기판 바이어스, 제어 신호, 기판 제어, 기판 전위, 검지 신호

## 명세서

### 기술분야

본 발명은 반도체 집적 회로 장치에 관한 것으로, 특히 고속성과 저전력성을 겸비한 반도체 집적 회로 장치에 관한 것이다.

본건 출원은 미국에서는 1997년 11월 21일 출원한 PCT/JP97/04253호의 일부 계속 출원이며, 그 내용은 인용에 의해 본건 출원에 합체된다.

### 배경기술

현재, 마이크로 프로세서 등의 반도체 집적 회로 장치의 실현에는 CMOS에 의한 집적 회로가 널리 이용되고 있다. CMOS 회로의 소비 전력에는 스위칭 시의 충방전에 의한 다이내믹한 소비 전력과 서브 임계 누설 전류에 의한 스태틱한 소비 전력에 의한 것이 있다. 이 중 다이내믹 소비 전력은 전원 전압 VDD의 2승에 비례하여 큰 전력을 소비하기 때문에, 저소비 전력화를 위해서는 전원 전압을 내리는 것이 효과적이고, 최근 많은 마이크로 프로세서의 전원 전압은 저하되고 있다.

한편, 현재의 저전력인 마이크로 프로세서는 파워 매니지먼트 기구를 구비하고, 프로세서에 복수의 동작 모드를 설치하고, 그에 따라서 대기 시에 실행 유닛으로의 클럭의 공급을 정지하고 있는 것이 있다.

이 클럭 공급의 정지에 의해, 불필요한 실행 유닛에서의 다이내믹한 소비 전력을 가능한 한 삭감할 수 있다. 그러나, 서브 임계 누설 전류에 의한 스태틱한 소비 전력은 삭감할 수 없고 그대로 잔존한다.

CMOS 회로의 동작 속도는 전원 전압의 저하와 함께 늦어지기 때문에, 동작 속도의 열화를 막기 위해서는 전원 전압의 저하에 연동하여 MOS 트랜지스터의 임계 전압을 내릴 필요가 있다. 그러나, 임계 전압을 내리면 서브 임계 누설 전류가 극단적으로 증가하기 때문에, 전원 전압의 저하가 진행함에 따라서, 종래는 그만큼 크지 않았던 서브 임계 누설 전류에 의한 스태틱한 소비 전력의 증가가 현저해지고 있다. 이 때문에, 고속성과 저전력성의 두점을 양립한 마이크로 프로세서 등의 반도체 집적 회로 장치를 실현하는 것이 문제가 되고 있다.

상기 문제를 해결하는 방법으로서, 예를 들면 특개평 6-54396호에 공개되어 있듯이 기판 바이어스를 가변 설정함으로써, MOS 트랜지스터의 임계 전압을 제어하는 방법이 있다.

CMOS 회로의 고속 동작이 요구되는 활성화 상태에서는 기판 바이어스를 PMOS(P 채널 MOS 트랜지스터)에 대해서는 전원 전위로, NMOS(N 채널 MOS 트랜지스터)에 대해서는 접지 전위로 설정한다. 한편, CMOS 회로가 고속으로 동작할 필요가 없는 대기 상태에서는 기판 바이어스를 PMOS에 대해서는 전원 전압보다도 높은 전위를, NMOS에 대해서는 낮은 전위를 인가한다(이 동작을 이하, 「기판을 당긴다」로 표현한다).

대기 시에 기판을 당김으로써, CMOS 회로를 구성하고 있는 MOS 트랜지스터의 임계치를 높게 할 수 있고, 서브 임계 누설 전류에 의한 스태틱한 소비 전력을 삭감할 수 있다.

## 발명의 상세한 설명

고속성과 저전력성의 두 점을 양립한 마이크로 프로세서 등의 반도체 집적 회로 장치를 실현하기 위해서는 CMOS 회로에 대하여 상기한 바와 같은 기판 바이어스 제어를 행하고, 활성화 시에는 MOS 트랜지스터의 임계치 전압을 낮게 하여 고속성을 유지하고, 대기 시에는 MOS 트랜지스터의 임계치를 높게 하여 서브 임계 누설 전류를 저감할 필요가 있다.

그러나, 발명자 등의 검토한 바에 의하면, 실제 회로 장치에서 기판 바이어스 제어를 하기 위해서는 이하와 같은 과제가 남게 된다.

- (1) 기판 바이어스 제어 회로의 테스트 용이성을 확보한다.

- (2) 기판 바이어스 제어를 함으로써 CMOS 회로의 오동작을 방지한다.

- (3) 기판 바이어스 제어를 하는 것에 의해, 회로 면적 증가를 최소한으로 저지한다.

- (4) 기판 바이어스의 전환 시에서의 반도체 집적 회로 장치의 오동작을 방지한다.

상기 과제를 해결하기 위해서 본 발명에서 제시한 수단의 주된 것은 이하와 같이 된다.

기판 바이어스 제어 회로 내의 마이너스 전압 발생 회로의 출력을 패드에 출력하는 것으로 하여, 회로의 테스트를 용이하게 하였다. 즉, 마이너스 전압 발생 회로는 그 출력 신호인 전압의 레벨이 설정한 전압으로 되어 있는지의 여부를 확인할 필요가 있고, 이 때문에 그 출력이 그대로 나와 있는 단자를 설치하는 것이 편리하다.

또한, 활성화 상태 시에 기판 바이어스를 구동하는 기판 구동 MOS 트랜지스터를 기판 바이어스 제어해야 할 주회로 내에 복수 배치하고, 기판 임피던스를 내린다. 이 경우, 활성화 상태 시에는 주회로 내의 회로가 동작하기 때문에, 임피던스를 낮게 하여 기판 전위를 고정하고, 트랜지스터 임계치의 변동을 억제할 필요가 있기 때문이다.

이 때, 대기 시에 비하여 활성화 상태 시의 구동력은 커지며, 예를 들면 5배, 이상적으로는 10배 이상의 구동력이 바람직하다.

또한, 기판 바이어스 전환 시의 회로의 안정성을 확보하기 위해서, 기판 구동 MOS 트랜지스터의 게이트 전압을 제어하는 게이트 제어 신호는 기판 구동 MOS 트랜지스터의 게이트에 접속된 후에 기판 바이어스 제어 회로로 복귀되고, 복귀된 신호의 전위에 의해서 기판 바이어스 제어 회로가 주회로의 기판 바이어스가 안정되었음을 검출할 수 있도록 게이트 제어 신호를 배선한다.

반도체 집적 회로 장치는 파워 온 리셋 회로를 구비하고 있고, 파워 온 리셋 회로는 주회로의 전원이 투입되는 것을 검출하고, 파워 온 리셋 회로에 의해서 주회로의 전원이 투입되어 일정 시간 동안은 기판 구동 MOS 트랜지스터가 기판 바이어스를 얇게 구동하는 활성화 상태로 한다.

또한, 기판 바이어스 제어 회로는 대기 상태로부터 활성화 상태로 천이하는 과정에서의 게이트 제어 신호의 출력 임피던스를 활성화 상태로 완전히 천이한 후에서의 임피던스보다도 크게 제어한다.

또한, 반도체 집적 회로 장치는 마이너스 전압 발생 회로를 구비하고 있으며, 기판 바이어스 제어 회로는 대기 상태에서의 마이너스 전압 발생 회로의 출력 임피던스를 활성화 상태에서의 마이너스 전압 발생 회로의 출력 임피던스보다도 작게 제어한다.

또한, 주회로는 복수의 셀로 이루어지고 있으며 복수의 셀의 전원 네트는 제1 배선층에 의해서 급전되고 있으며 또한 이들 제1 배선층과 직행하는 제2 배선층을 이용한 전원 네트가 있으며, 제1 배선층에 의한 전원 네트와 제2 배선층에 의한 전원 네트의 교점에 스위치 셀을 배치하여 제1 배선층에 의한 전원 네트와, 제2 배선층에 의한 전원 네트의 접속은 그 스위치 셀 내에서 행해지고 있으며 또한 상기 기판 구동 MOS 트랜지스터를 스위치 셀 내에 배치한다.

또한, 상기 셀을 구성하는 MOS 트랜지스터의 기판 바이어스 공급선이 제1 배선층에 의한 전원 네트와 평행하게 제1 배선층에 의해서 행해지며, 제2 배선층에 의한 전원 네트에도 평행하게 제2 배선층에 의해서도 행해지고, 전원 네트와 마찬가

지로, 상기 스위치 셀 내에서 제1 배선층에 의한 기판 바이어스 공급선과, 제2 배선층에 의한 기판 바이어스 공급선이 접속되며, 상기 기판 구동 MOS 트랜지스터의 게이트 전압을 제어하는 게이트 제어 신호가, 제2 배선층에 의한 전원 네트와 평행한 상기 스위치 셀 상공의 제2 배선층에 따라 공급되며, 상기 스위치 셀 내에서 기판 구동 MOS 트랜지스터의 게이트 단자에 접속한다.

보다 구체적으로 설명하면, 본 발명은 적어도 하나의 트랜지스터로 구성된 주회로와, 트랜지스터의 기판에 인가되는 전압을 제어하는 기판 바이어스 제어 회로와, 기판 바이어스 제어 회로를 제어함으로써 주회로에 흐르는 서브 임계 누설 전류가 많은 활성화 상태와, 서브 임계 누설 전류가 작은 대기 상태의 적어도 두 상태로 전환하는 대기 제어 회로를 구비하고, 기판 바이어스 제어 회로에 마이너스 전압 발생 회로를 내장함과 함께, 상기 마이너스 전압 발생 회로에서 발생한 마이너스 전압을 장치 외부로 출력하는 단자를 갖는다.

이 때 반도체 집적 회로 장치는, 출력 패드를 갖는 반도체 칩과, 반도체 칩을 내장하여 외부 펈을 갖는 패키지를 가지며, 단자로서 출력 패드의 하나를 이용하고 또한 그 단자는 외부 펈과는 접속되어 있지 않다.

다른 예에서는, 적어도 하나의 MOS 트랜지스터로 구성된 주회로와, MOS 트랜지스터의 기판에 인가되는 전압을 제어하는 기판 바이어스 제어 회로와, 기판 바이어스 제어 회로를 제어함으로써, 주회로에 흐르는 서브 임계 누설 전류가 많은 활성화 상태와, 서브 임계 누설 전류가 작은 대기 상태가 적어도 두 상태로 전환하는 대기 제어 회로를 가지며, 활성화 상태에는 기판 바이어스를 얇게 제어하고, 대기 상태에서는 기판 바이어스를 짚게 제어하고, 활성화 상태에서 기판 바이어스를 얇게 구동하는 구동력이 스텐바이 상태에서 기판 바이어스를 짚게 구동하는 구동력보다도 10배 이상 큰 것을 특징으로 한다.

이 때, 기판 바이어스를 짚게 제어하고 있을 때는 기판을 당기고 있는 트랜지스터로 구성되는 주회로를 동작시키지 않은 것이 바람직하다. 기판을 당기고 있을 때는 기판의 임피던스가 높으므로, MOS 트랜지스터가 동작함으로써 기판 전위가 변화하기 쉽다. 이 때문에, MOS 트랜지스터가 오동작할 가능성이 있기 때문이다.

디바이스 구조로서는 활성화 상태에서 기판 바이어스를 얇게 구동하기 위한 기판 구동 MOS 트랜지스터는 거리  $20\mu m$  이상 떨어져서 적어도 두 개 이상 있으며, 기판 구동 MOS 트랜지스터의 게이트 전위는 기판 바이어스 제어 회로에 의해 제어되고 있다.

기판 구동 MOS 트랜지스터의 게이트 전압을 제어하는 게이트 제어 신호는 기판 구동 MOS 트랜지스터의 게이트에 접속된 후에 기판 바이어스 제어 회로로 복귀되며, 복귀된 신호의 전위에 의해서 기판 바이어스 제어 회로가 상기 주회로의 기판 바이어스가 안정된 것을 검출할 수 있다.

기판 구동 MOS 트랜지스터의 임계치 전압은 주회로를 구성하고 있는 MOS 트랜지스터의 임계치보다도 큰 것이 바람직하다. 또한, 외부와의 인터페이스를 하는 I/O 회로를 구비할 때, 그 I/O 회로를 구성하고 있는 적어도 하나의 MOS 트랜지스터의 산화막 두께는 주회로를 구성하고 있는 MOS 트랜지스터의 산화막 두께보다도 두꺼운 것이 바람직하다. 이와 같이, 주로 높은 전압이 인가되는 부분의 내압을 높게 하는 것이 바람직하다.

또한, 주회로의 전원이 투입되는 것을 검출하는 파워 온 리세트 회로를 구비하고, 주회로의 전원이 투입되어 일정한 시간 동안은 기판 구동 MOS 트랜지스터가 기판 바이어스를 얇게 구동하는 활성화 상태로 제어한다.

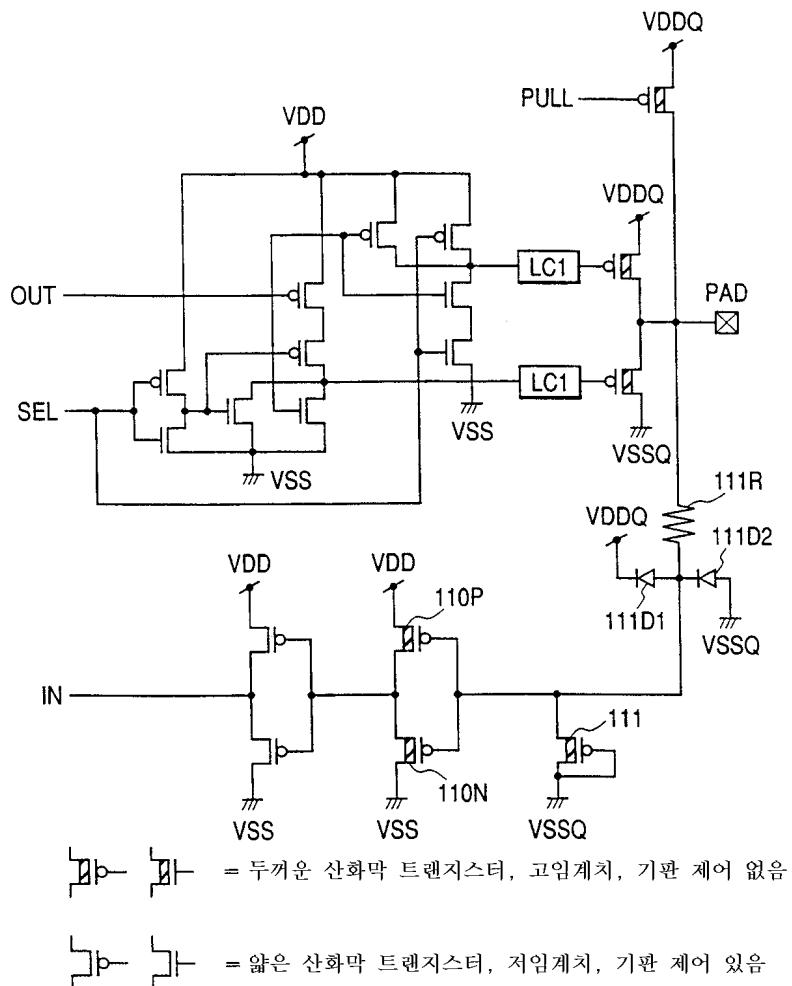

본 발명을 적용한 시스템의 다른 형태에서는, 반도체 집적 회로 장치는 제1(VDDQ)과 제2(VDD) 전원 전압을 가지고, 제1 전원 전압은 제2 전원 전압보다도 절대치가 크며, 제2 전원 전압은 2V 이하이며, 제2 전원 전압(VDD)은 상기 주회로(LOG)에 공급되며, 제1 전원 전압(VDDQ)은 기판 바이어스 제어 회로(VBC)와 대기 제어 회로(VBCC)에 공급되며, 제1 전원 전압은 제2 전원 전압보다도 먼저 투입되며, 기판 바이어스 제어 회로는 제2 전원 전압이 투입되어 일정 시간 동안은 주회로를 활성화 상태로 제어하는 것을 특징으로 한다.

또한, 대기 상태로부터 활성화 상태로 천이하는 과정에서의 기판 구동 MOS 트랜지스터의 게이트 제어 신호의 출력 임피던스를 활성화 상태로 완전히 천이한 후에서의 임피던스보다도 크게 제어함으로써, 대기 상태로부터 활성화 상태로 천이하는 천이 속도를 조정하고, 천이 과정에서의 돌입 전류를 작게 제어할 수 있다.

또한, 대기 상태로부터 활성화 상태로 천이하는 과정에서의 기판 구동 MOS 트랜지스터의 게이트 제어 신호의 출력 임피던스를 활성화 상태로 완전히 천이한 후에서의 임피던스보다도 크게 제어함으로써, 대기 상태로부터 활성화 상태로 천이하는 천이 속도를 조정하고, 천이 과정에서의 돌입 전류를 작게 제어하고 또한 활성화 상태로 완전히 천이한 것은 상술한 복귀된 신호에 의해서 검출할 수 있다.

게이트 제어 신호의 진폭은 상기 기판 구동 트랜지스터의 게이트 내압보다도 크게 할 수 있다.

또한, 반도체 집적 회로 장치는 마이너스 전압 발생 회로를 구비하고, 기판 바이어스 제어 회로는 대기 상태에서의 마이너스 전압 발생 회로의 출력 임피던스를 활성화 상태에서의 마이너스 전압 발생 회로의 출력 임피던스보다도 작게 제어할 수 있다.

또한, 청구항 13에 기재된 반도체 집적 회로 장치에 있어서, 마이너스 전압 발생 회로는 제1 차지 펌프 회로와 제2 차지 펌프 회로를 가지며, 기판 바이어스 제어 회로는 대기 상태에서는 제1 차지 펌프 회로를 이용하여 마이너스 전압을 발생시키고, 활성화 상태에서는 제2 차지 펌프 회로를 이용하여 마이너스 전압을 발생시키며, 제1 차지 펌프 회로의 펌핑 콘덴서의 용량은 제2 차지 펌프 회로의 펌핑 콘덴서의 용량보다도 작은 것을 특징으로 한다.

제1과 제2 전원 전압을 가지고, 상기 마이너스 전압 발생 회로는 제3 전원 전압을 발생하고, 제1 전원 전압은 제2 전원 전압보다도 크며, 제2 전원 전압은 2V 이하이며, 주회로에는 제2 전원 전압이 공급되어 있으며, 기판 바이어스 제어 회로와 상기 대기 제어 회로에는 적어도 제1 전원 전압이 공급되어 있으며, 대기 상태에서 기판 바이어스 제어 회로는 PMOS 트랜지스터의 상기 기판 바이어스를 제2 전원 전압 전위로 제어하고, NMOS 트랜지스터의 상기 기판 바이어스를 제3 전원 전압 전위로 제어하고, (제3 전원 전압)=(제1 전원 전압)-(제2 전원 전압)으로 해도 좋다.

또한, 마이너스 전압 발생 회로는 적어도 하나의 차지 펌프 회로와, 비교기와, 제2 전원 전압의 반 정도의 전위를 발생하는 제1 기준 전압 회로와, 제1 전원 전압과 제3 전원 전압의 중간 전위를 발생하는 제2 기준 전압 회로를 구비하고, 비교기는 제1 기준 전압 회로의 출력 전압과, 제2 기준 전압 발생 회로의 출력 전압을 비교하여, 차지 펌프 중 적어도 하나를 제어하여 제3 전원 전압을 안정화할 수 있다.

제1 및 제2 기준 전압 발생 회로는 각각 기판 단자가 소스 단자에 접속되며 또한, 게이트 단자가 드레인 단자에 접속된 동일 도전형의 MOS 트랜지스터가 직렬로 접속된 직렬 회로로 이루어지고 있으며 복수의 MOS 트랜지스터가 포화 영역에서 동작하도록 선택되어 있을 수 있다. 또한, 장치는 슈미트 특성을 갖도록 구성할 수 있다.

주회로는 복수의 셀로 이루어지고 있으며 상기 복수의 셀의 전원 네트는 제1 배선층에 의해서 급전되고 있으며, 또한 이들 제1 배선층의 상공에는 이들에 직행하는 제2 배선층을 이용한 전원 네트가 있고, 제1 배선층에 의한 전원 네트와 제2 배선층에 의한 전원 네트의 교점에 스위치 셀을 배치하여, 제1 배선층에 의한 전원 네트와, 제2 배선층에 의한 전원 네트의 접속은 그 스위치 셀 내에서 행해지고 있으며 또한 기판 구동 MOS 트랜지스터가 상기 스위치 셀 내로 배치되어 있는 것을 특징으로 한다.

스위치 셀에는 또한 디커플링 콘덴서가 전원과 접지 간에 배치되는 것으로 해도 좋다.

또한, 제2 배선층에 의한 전원 네트의 상공에는 또한 제2 배선층에 의한 전원 네트와 평행한 제4 배선층에 의한 전원 네트가 있고, 제2 배선층에 의한 전원 네트와 제4 배선층에 의한 전원 네트의 접속은 스위치 셀 외에서 행해지는 것으로 해도 좋다.

또한, 제5 배선층에 의한 전원 네트가 있고 제4 배선층에 의한 전원 네트와, 제5 배선층에 의한 전원 네트와의 접속은 스위치 셀 내에서 행해지며, 제4 배선층에 의한 전원 네트와 제5 배선층에 의한 전원 네트로 이루어지는 전원 메쉬는 제1 배선층에 의한 전원 네트와 제2 배선층에 의한 전원 네트로 이루어지는 전원 메쉬보다도 거칠고 제4 배선층의 두께와 제5 배선층의 두께는 제1 배선층의 두께와 제2 배선층의 두께 중 어느 하나보다도 두꺼운 것으로 해도 좋다.

셀을 구성하는 MOS 트랜지스터의 기판 바이어스 공급선이 제1 배선층에 의한 전원 네트와 평행하게 제1 배선층에 의해서 행해지며, 제2 배선층에 의한 전원 네트에도 평행하게 제2 배선층에 의해서도 행해지며, 전원 네트와 마찬가지로, 스위치 셀 내에서 제1 배선층에 의한 기판 바이어스 공급선과, 제2 배선층에 의한 기판 바이어스 공급선이 접속되어 있는 것으로 해도 좋다.

기판 구동 MOS 트랜지스터의 게이트 전압을 제어하는 게이트 제어 신호가 제2 배선층에 의한 상기 전원 네트와 평행한 스위치 셀 상공의 제2 배선층에 의해서 공급되며, 스위치 셀 내에서, 기판 구동 MOS 트랜지스터의 게이트 단자에 접속되어 있는 것으로 해도 좋다.

스위치 셀 상공의 제2 배선층에 의해서 배선되어 있는 기판 바이어스 공급선과 게이트 제어 신호가 스위치 셀 상공의 제2 배선층에 의해서 배선되어 있는 전원 네트 간에 배치되어 있는 것으로 해도 좋다.

반도체 집적 회로 장치에는 데이터 패스 회로가 구비되고 있으며, 데이터 패스 회로의 데이터 플로우 방향과 복수 셀의 제1 배선층에 의한 전원 네트가 평행한 것으로 해도 좋다.

기판 바이어스가 반도체 집적 회로 장치의 선별 시에는 적어도 하나의 MOS 트랜지스터의 임계치가 커지도록 설정할 수 있다.

또한, 다른 형태에서는 제1 펌핑 콘덴서와, 제2 펌핑 콘덴서와, 제1과 제2 두 개의 P 채널 트랜지스터와, 제1과 제2 두 개의 N 채널 트랜지스터와, 발진 회로로 이루어지는 차지 펌프 회로에서 발진 회로의 출력이 'H'일 때, 제1 펌핑 콘덴서와 제1 P 채널 트랜지스터와 제1 N 채널 트랜지스터를 이용하여 상기 제1 펌핑 콘덴서의 전하를 펌핑하고, 발진 회로의 출력이 'L'일 때, 제2 펌핑 콘덴서와 제2 P 채널 트랜지스터와 제2 N 채널 트랜지스터를 이용하여 상기 제2 펌핑 콘덴서의 전하를 펌핑하는 것을 특징으로 한다.

다른 형태에서는, 반도체 기판 상에 구성된 트랜지스터를 포함하는 주회로(LOG)와, 기판에 인가되는 전압을 제어하는 기판 바이어스 제어 회로(VBC)를 가지며, 주회로는 기판에 인가되는 전압을 제어하는 스위치 트랜지스터(MN1, MP1)를 가지고, 기판 바이어스 제어 회로로부터 출력된 제어 신호가 스위치 트랜지스터의 게이트에 입력되고 있으며 또한 제어 신호는 기판 바이어스 제어 회로로 복귀하도록 구성되어 있다.

또한, 스위치 트랜지스터는 구형의 스위치 셀에 배치되며 트랜지스터는 구형의 표준셀에 배치되고, 스위치 셀 하나와 표준 셀 복수가 일렬로 나란히 배치하는 것이 레이아웃 상 적합하다.

또한, 주회로의 트랜지스터(MN2, MP2)를 구동하는 구동 전원(VSS, VDD)의 배선과, 기판 바이어스 제어 회로로부터 공급되는 기판 바이어스 전원(vbp, vbn)의 배선이 스위치 셀과 복수의 표준 셀을 셀이 배열하는 방향으로 종단시키는 것이 적합하다.

트랜지스터의 내성이라는 점에서는 스위치 트랜지스터의 임계치가 트랜지스터의 임계치보다 큰 것이 바람직하다.

스위치 트랜지스터(MN1, MP1)는 주회로의 트랜지스터(MN2, MP2)를 구동하는 구동 전원(VSS, VDD)과, 상기 기판 바이어스 제어 회로로부터 공급되는 기판 바이어스 전원(vbp, vbn) 간에 삽입되는 것이 레이아웃 상에서는 적합하다.

또한, 트랜지스터의 소스 또는 드레인이 상기 구동 전원(VSS, VDD)에 접속되며, 트랜지스터의 기판 전위가 기판 바이어스 전원에 접속될 수 있다.

기판 바이어스 제어 회로는, 제어 신호(vbp, vbn)를 출력한 후, 주회로를 거쳐서 되돌아온 상기 제어 신호(vbpr, vbnr)가 소정 전압이 된 것을 검지하고, 검지 신호(vbbenbr)를 형성함으로써 주회로의 동작의 안정화를 도모할 수 있다.

### 도면의 간단한 설명

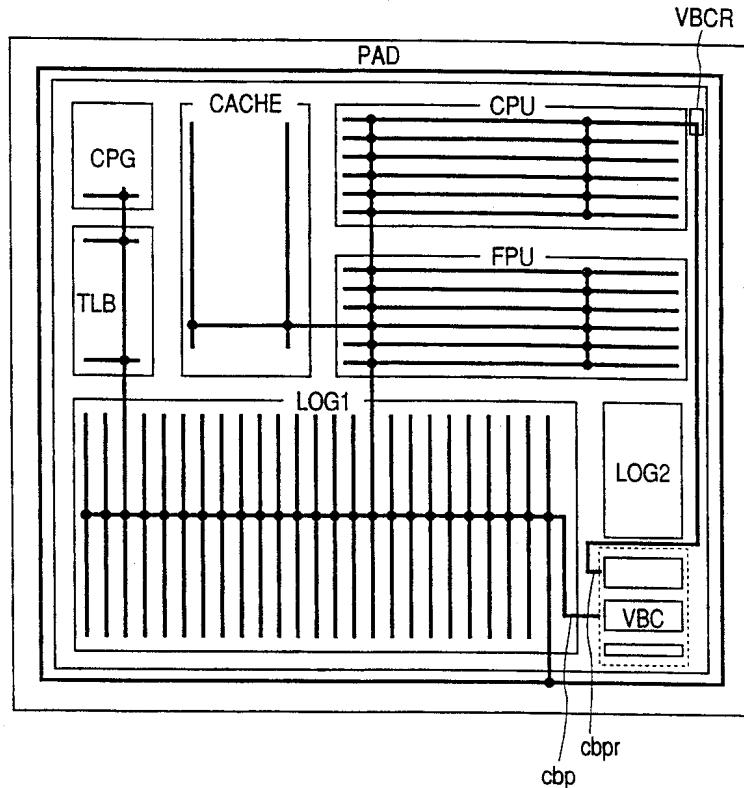

도 1은 본 발명의 반도체 집적 회로 장치의 블록도.

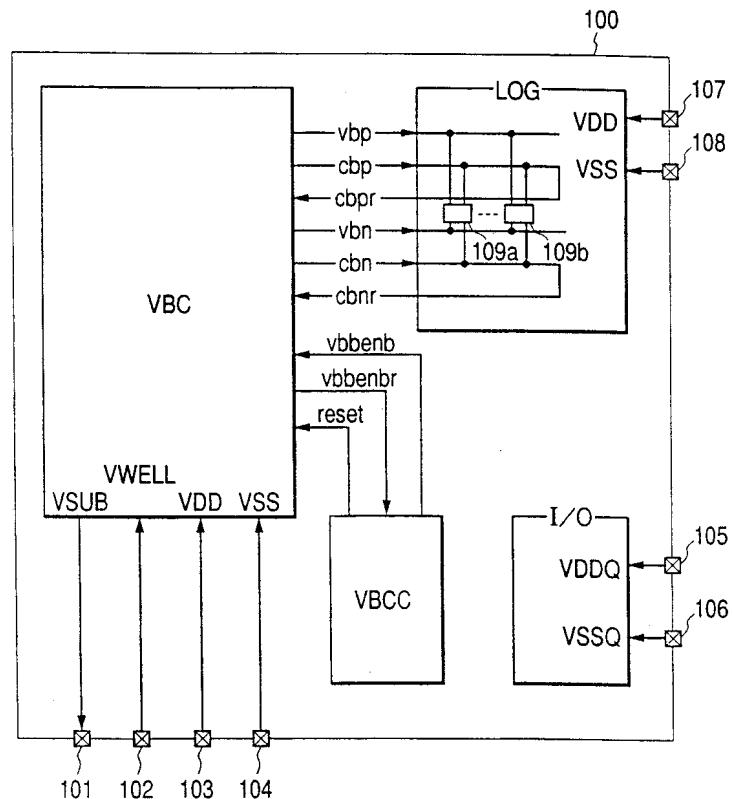

도 2는 주회로의 내용을 보다 자세히 나타낸 회로도.

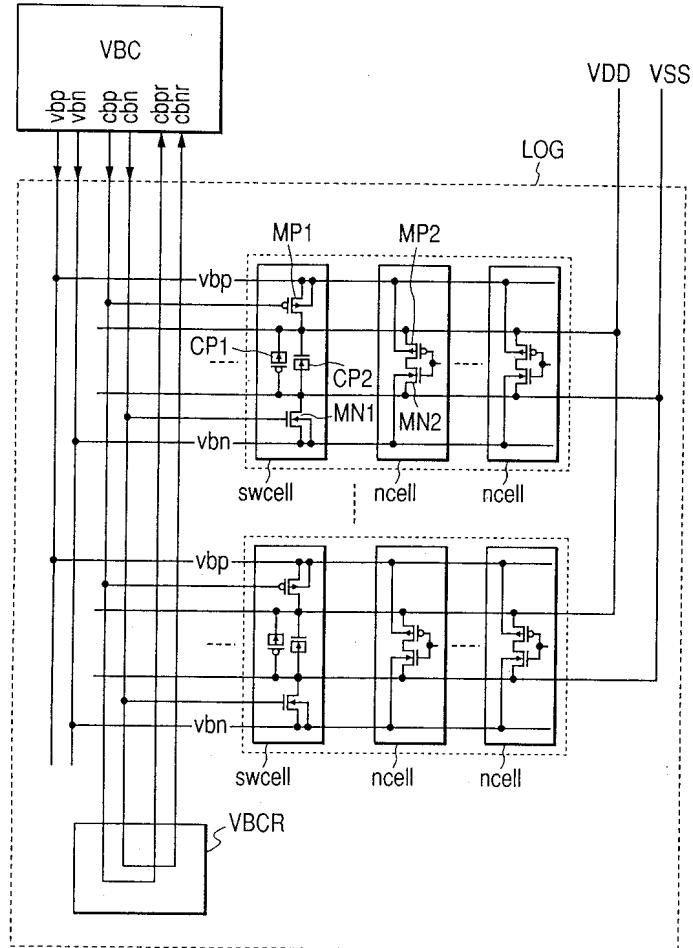

도 3은 I/O 회로의 회로도.

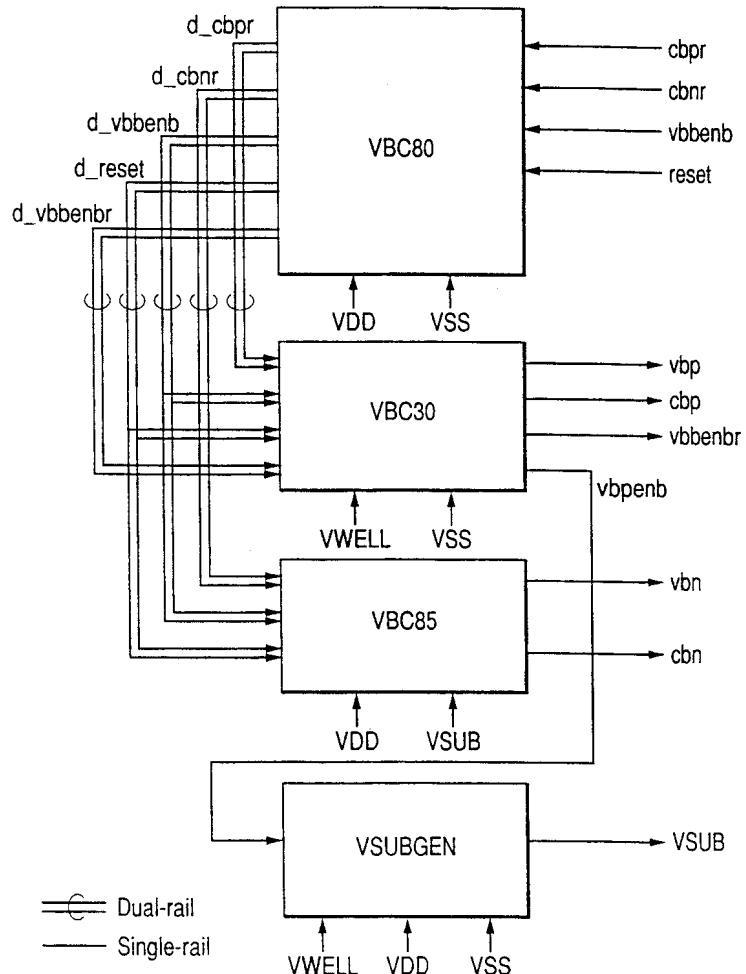

도 4는 기판 바이어스 제어 회로의 각 회로 블록도.

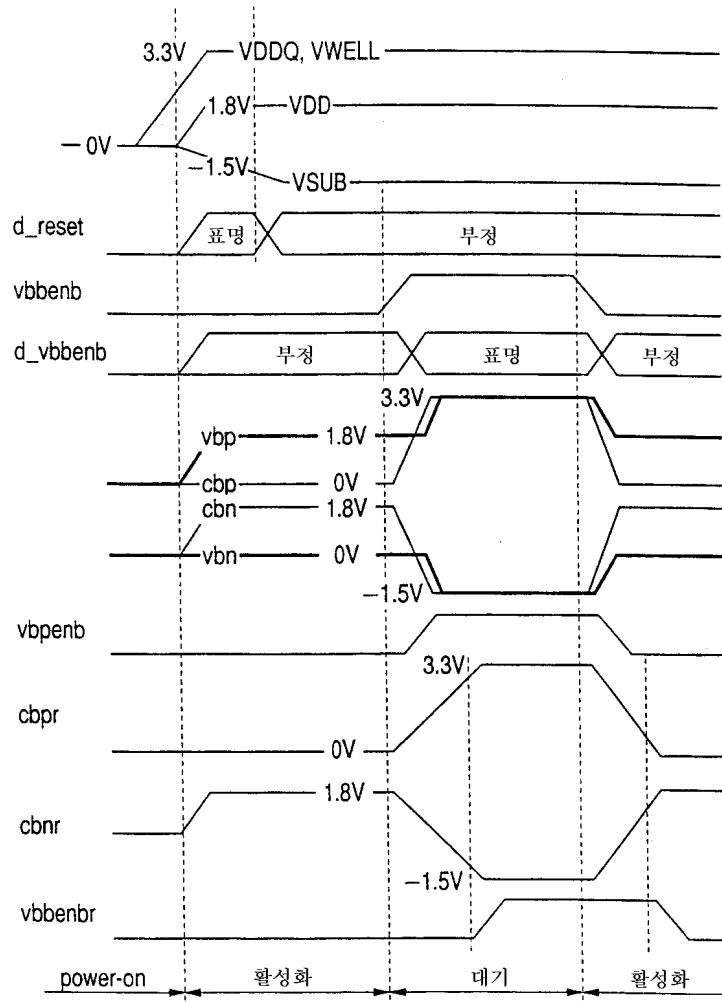

도 5는 기판 바이어스 제어 회로의 동작 과정을 나타내는 도면.

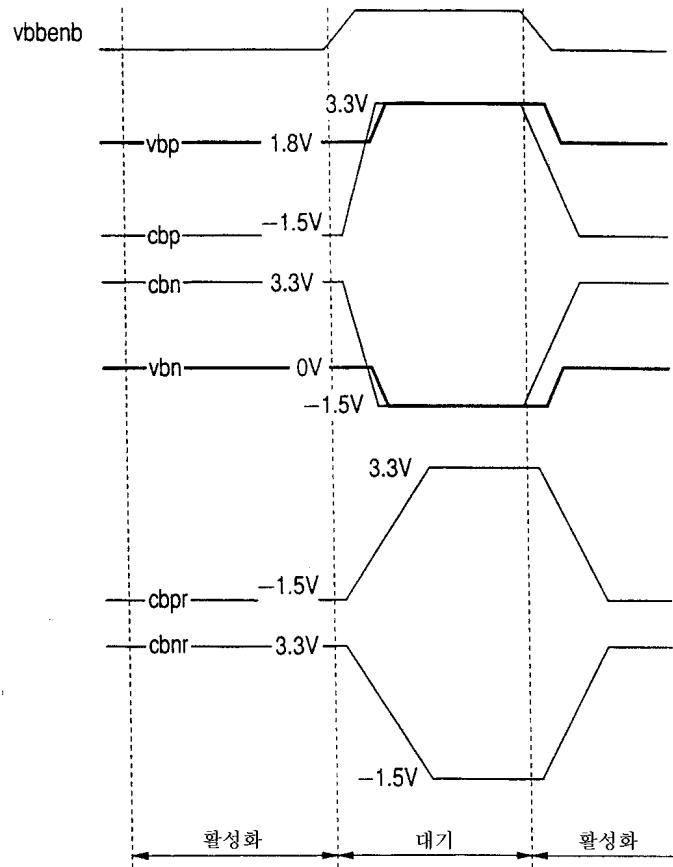

도 6은 기판 바이어스 제어 회로의 동작 과정의 도 5와는 다른 실시예를 나타내는 과정도.

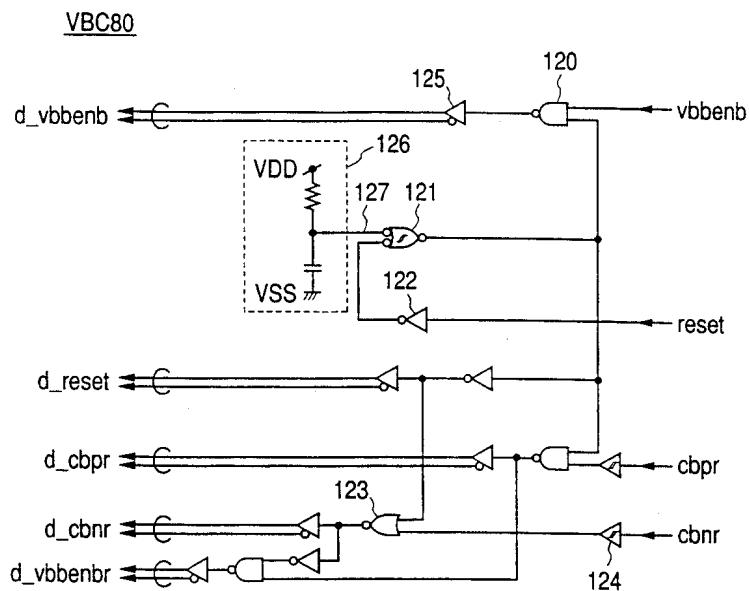

도 7은 VBC80의 회로도.

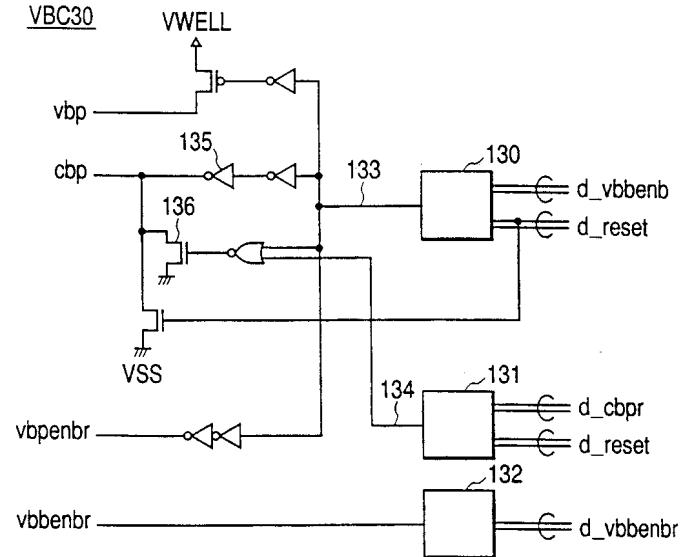

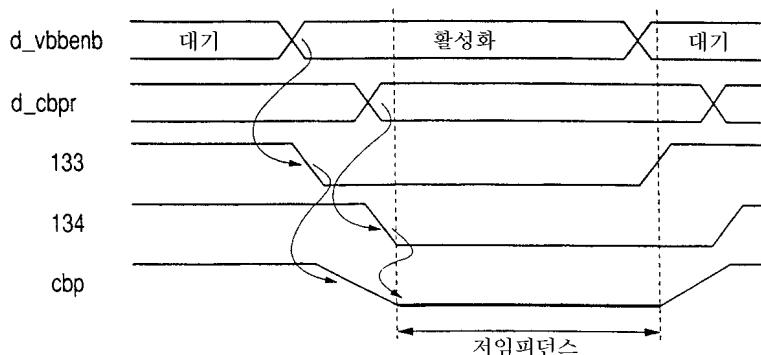

도 8은 VBC30의 회로도.

도 9는 VBC30의 동작 과정도.

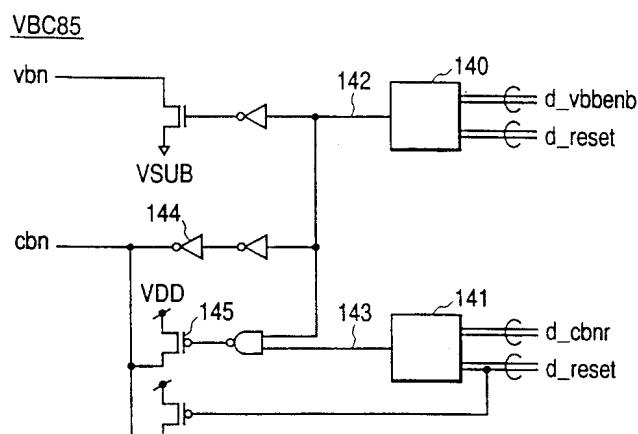

도 10은 VBC85의 회로도.

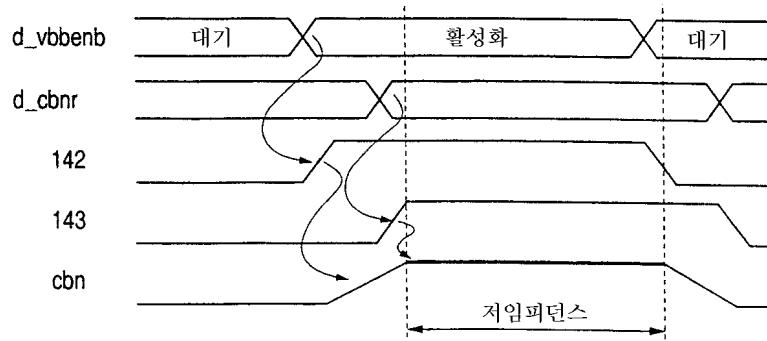

도 11은 VBC85의 동작 과정도.

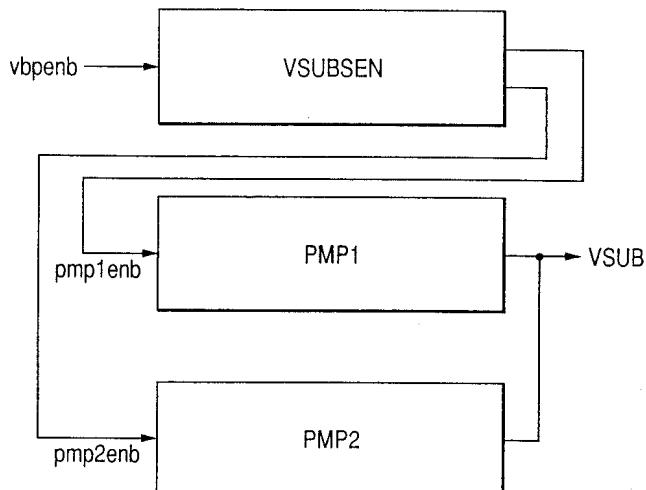

도 12는 VSUBGEN의 각 회로 블록도.

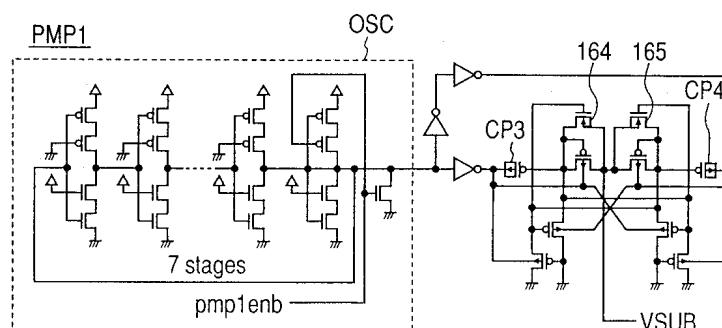

도 13은 차지 펌프의 회로도.

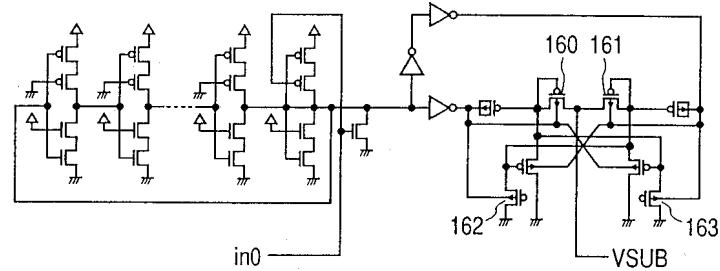

도 14는 차지 펌프의 회로도.

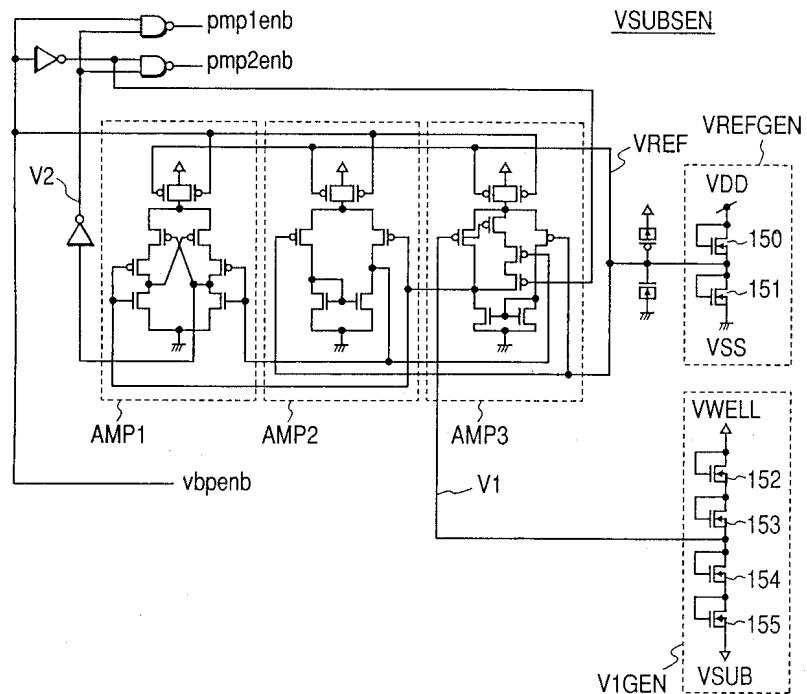

도 15는 VSUBSEN의 회로도.

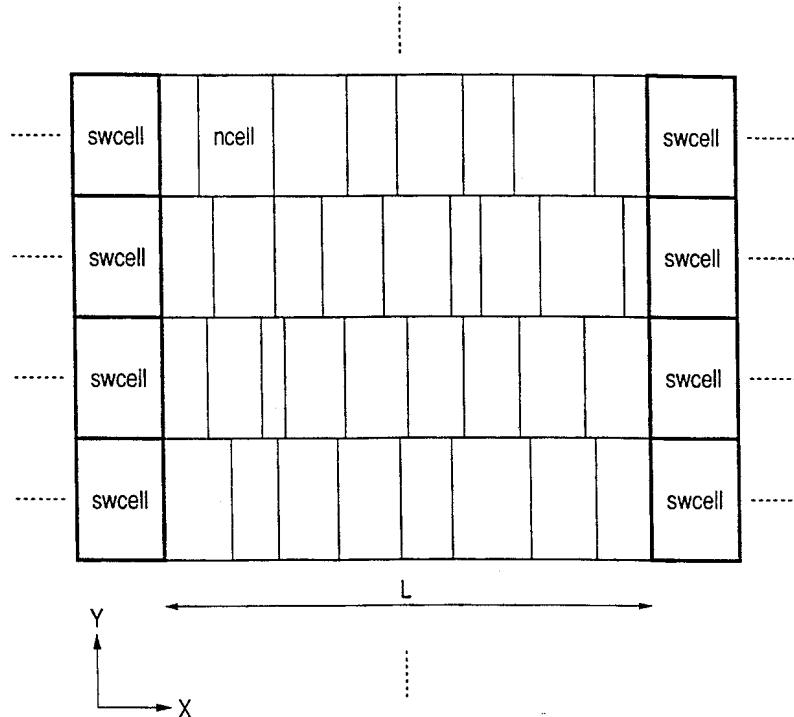

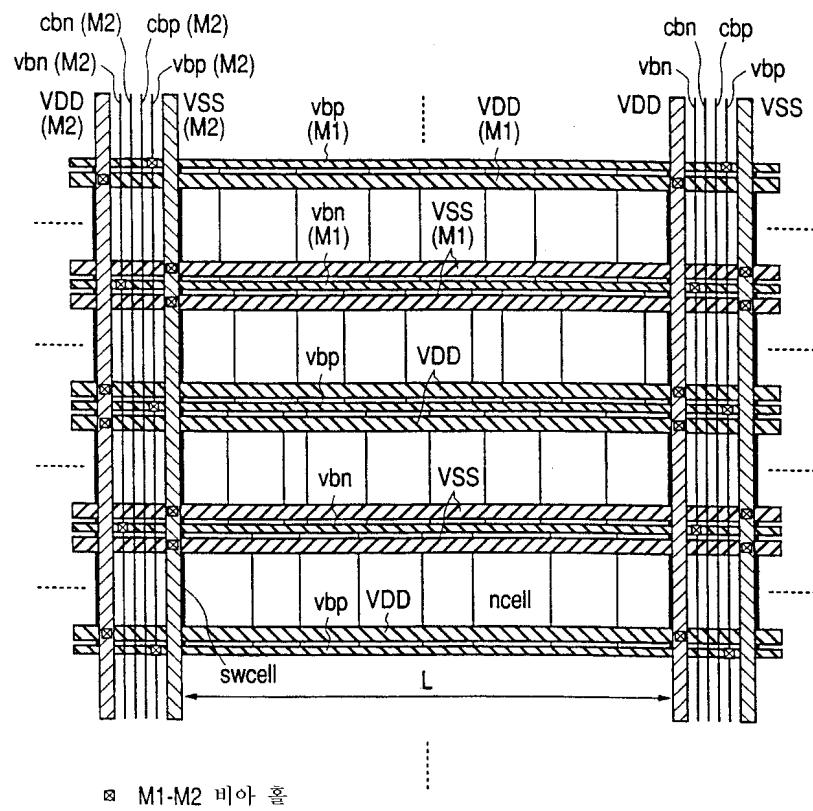

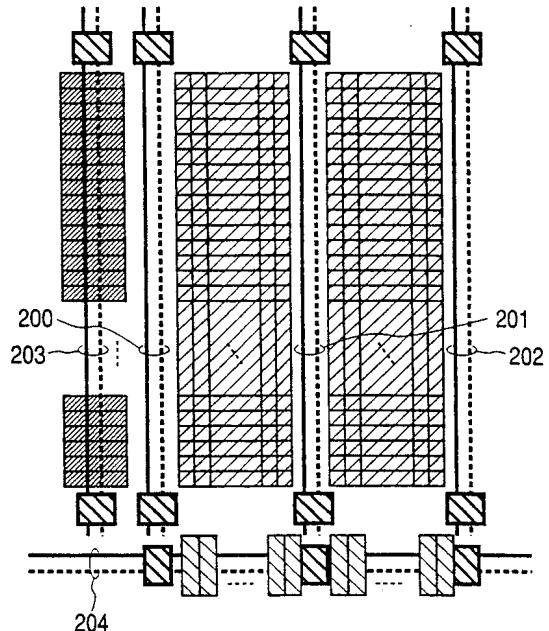

도 16은 본 발명의 스위치 셀의 배치도.

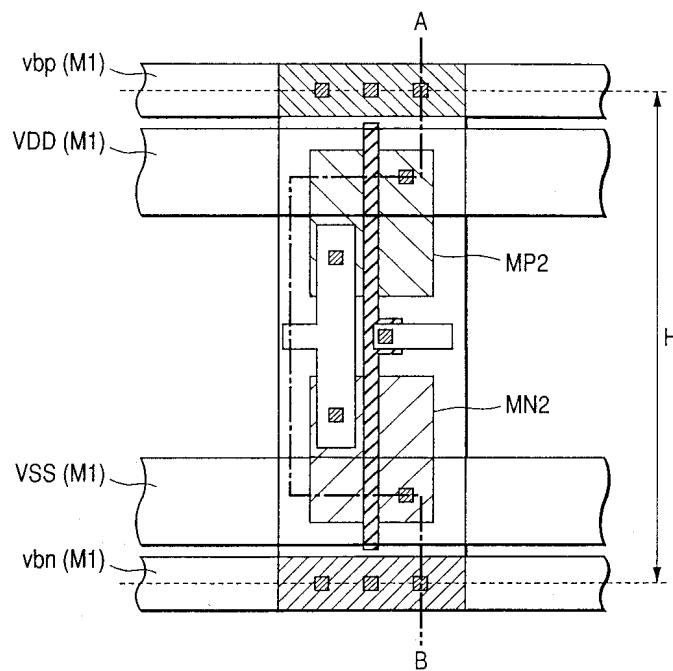

도 17은 표준 셀의 레이아웃도.

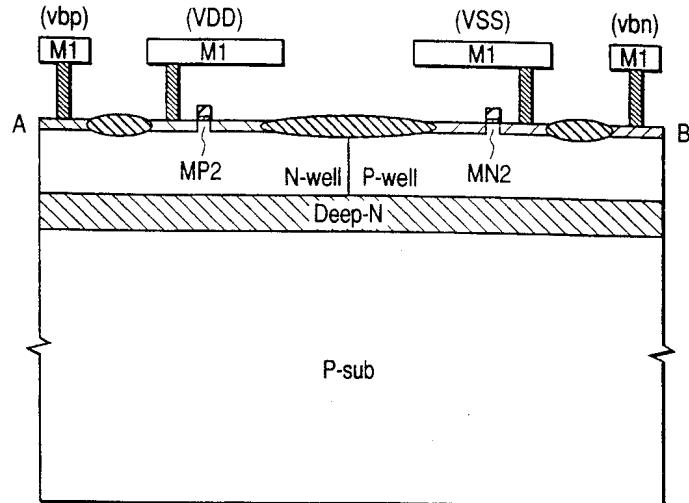

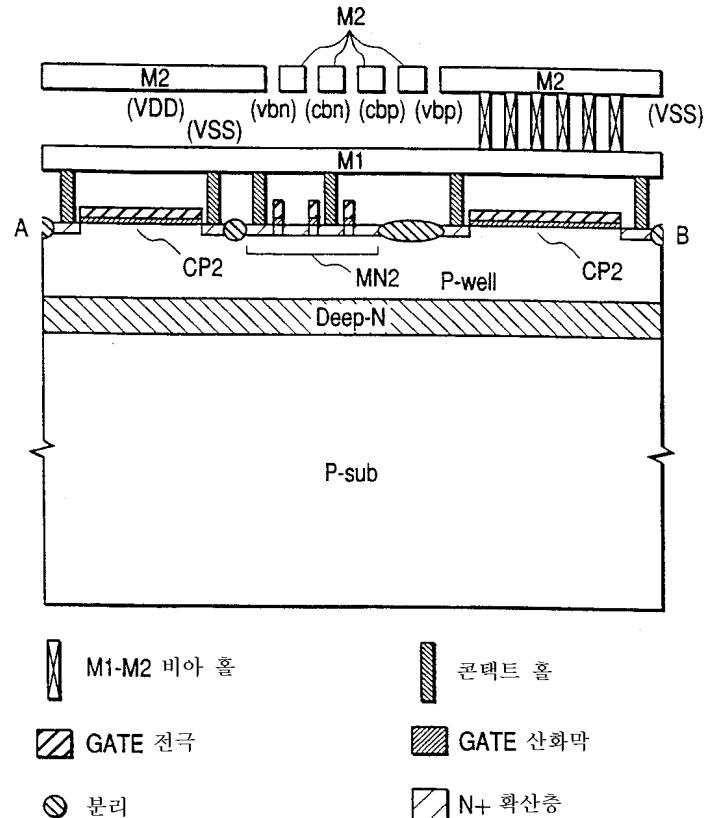

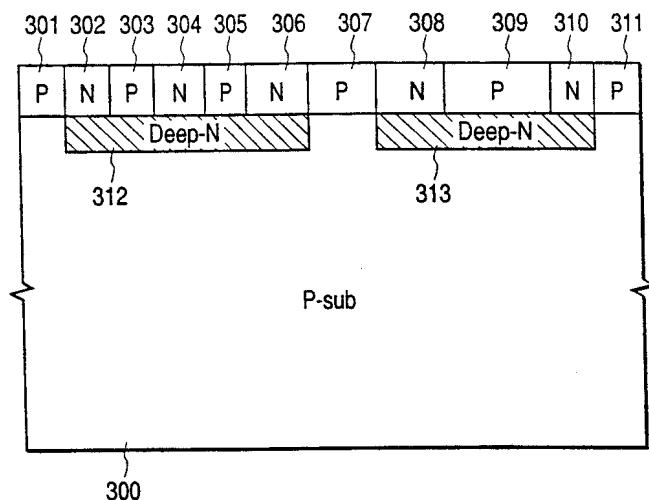

도 18은 도 17의 단면도.

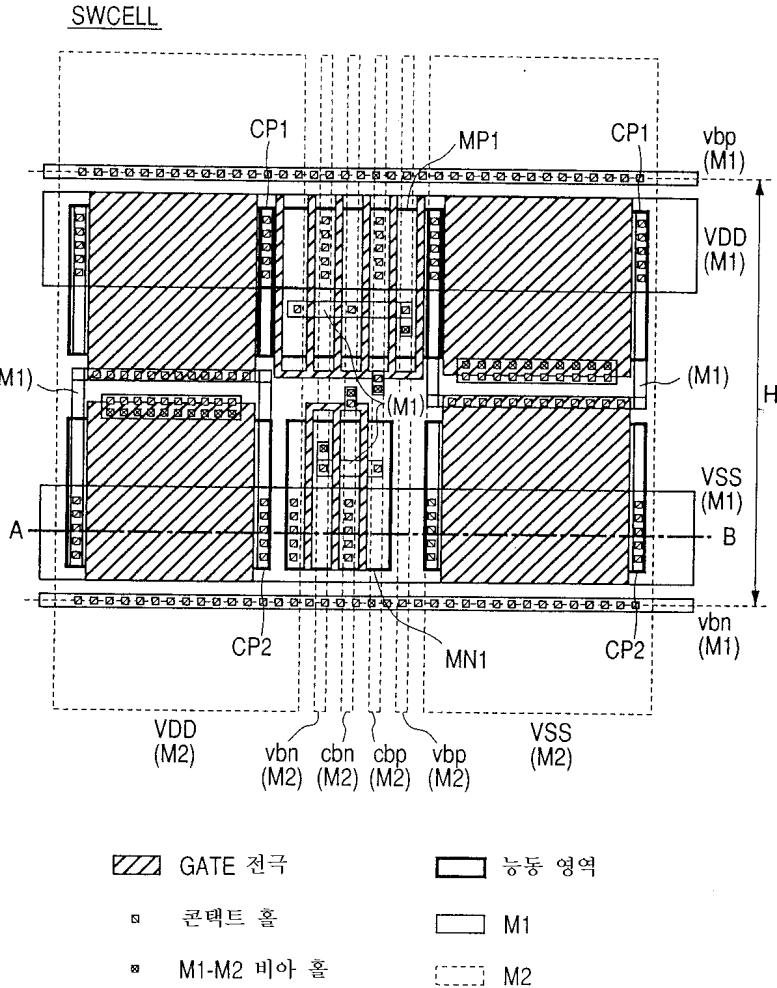

도 19는 스위치 셀의 레이아웃도.

도 20은 도 19의 단면도.

도 21은 전원 배선 및 vbp, vbn, cbp, cbn의 배선도.

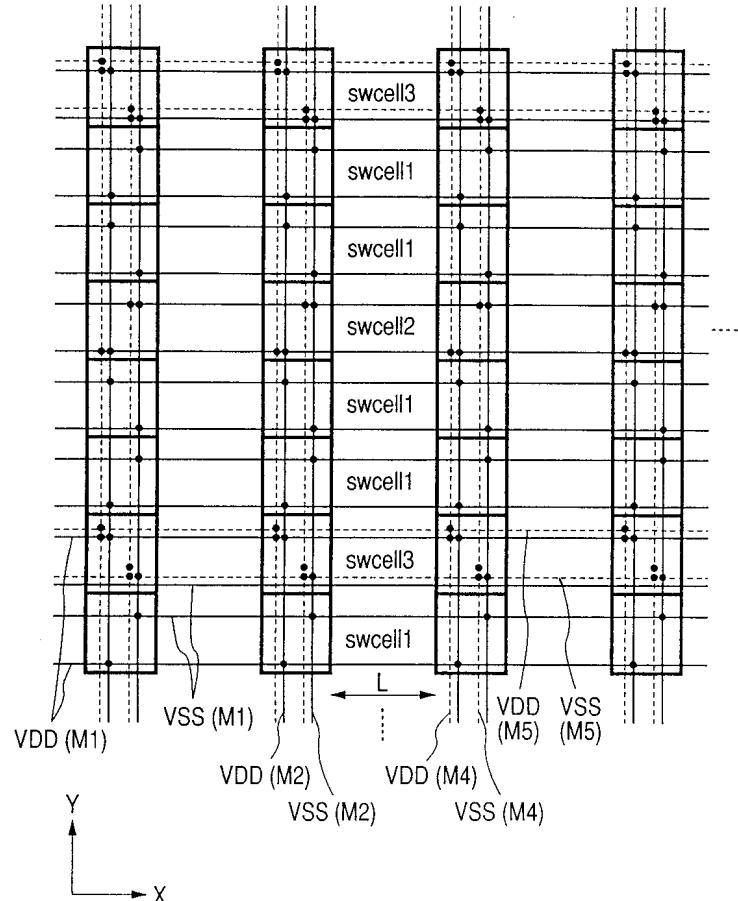

도 22는 전원 보강선의 배선도.

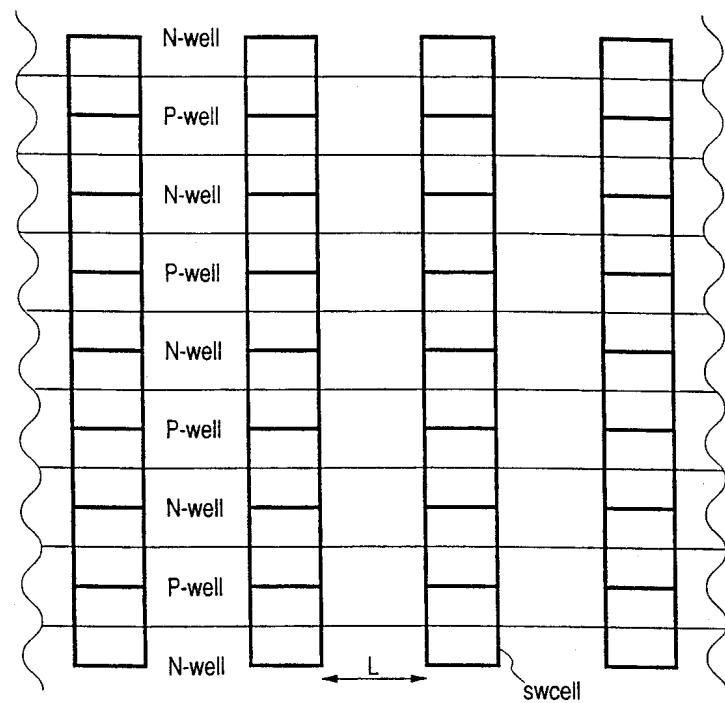

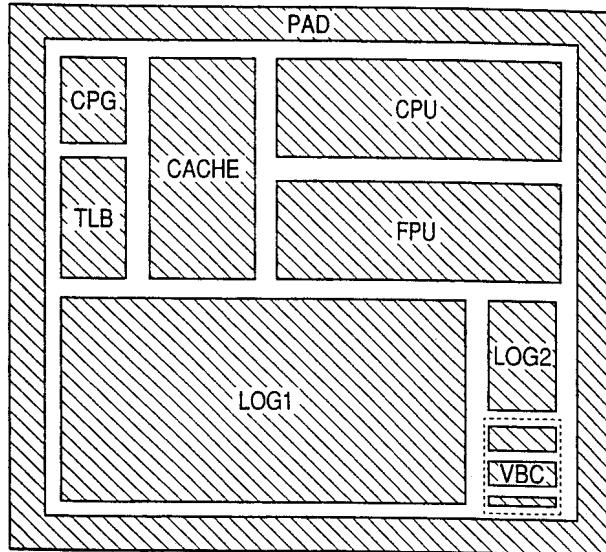

도 23은 웰의 구성도.

도 24는 메모리 회로에서의 스위치 셀의 배치도.

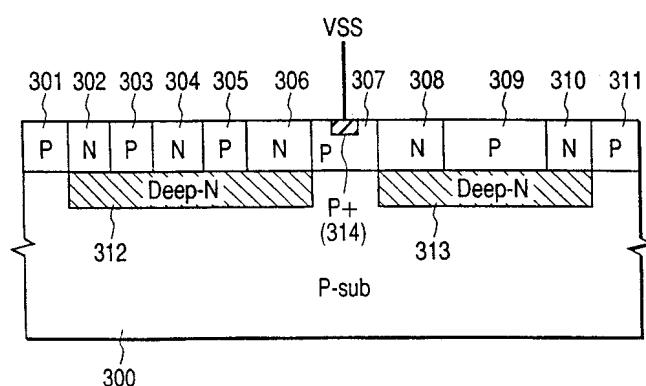

도 25는 웰의 단면도.

도 26은 Deep-N 웰의 레이아웃도.

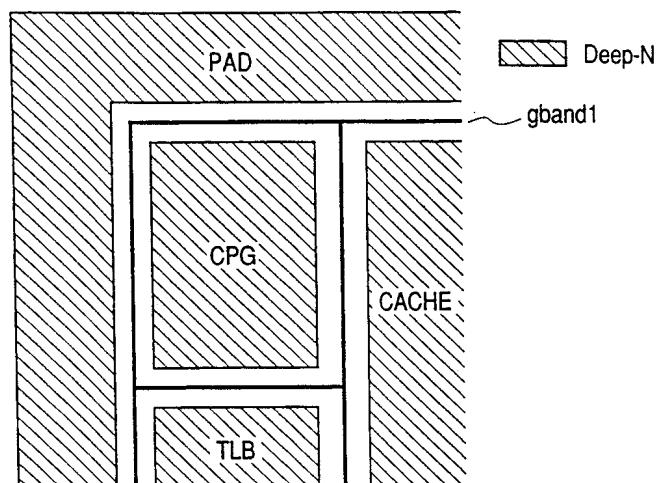

도 27는 Deep-N 웰과 가드 대역의 레이아웃도.

도 28은 도 27의 단면도.

도 29는 cbpr, cbnr, 및 VBCR의 배치도.

### 실시예

도 1에 본 발명의 기판 바이어스 제어 회로를 이용한 반도체 집적 회로 장치(100)의 개념도를 나타낸다. VBC는 기판 바이어스 제어 회로이다. LOG는 기판 바이어스 제어되는 주회로이고, 논리 회로나 메모리회로로 구성되어 있다. VBCC는 기

관 바이어스 제어 회로의 제어를 행하는 대기 제어 회로를 나타내고 있다. I/O는 반도체 집적 회로 장치(100)의 외부와의 인터페이스를 행하는 I/O 회로이다. 여기서는 회로 블록 간의 배선으로 기판 제어에 특히 필요없는 것은 생략하고 있다. 또한, 참조 번호 109a, 109b는 기판 구동 회로를 나타내고 있다.

전원은 3종류 있으며 각각 VDDQ, VDD, VWELL로 나타내고 있다. VSS, VSSQ는 각각, VDD, VDDQ에 대한 접지 전위를 나타내고 있다. VDDQ, VSSQ는 I/O 회로용 전원으로, VDD, VSS는 주회로용 전원, VWELL은 기판 바이어스 제어 회로 VBC용 전원이다.

도 1에 도시한 바와 같이, 기판 바이어스 제어 회로 VBC에는 VDD, VSS도 공급되어 있다. 또한, 기판 바이어스 제어 회로 VBC는 내부에 마이너스 전압 발생 회로를 내장하고 있으며, VDD나 VDDQ와는 역극성의 마이너스 전압 VSUB를 발생하고 있다. 여기서는 이하, VDDQ=VWELL=3.3V, VDD=1.8V, VSUB=-1.5V로 하고 전원 전압으로서 2 종류를 가정한다.

참조 번호 101, 102, 103, 104는 반도체 집적 회로 장치(100)의 패드를 나타내고 있고, 참조 번호 102는 3.3V의 VWELL 전원, 참조 번호 103은 1.8V의 VDD 전원, 참조 번호 104는 0V의 VSS(접지)가 금전된다. 참조 번호 101은 VSUB 패드이지만 기판 바이어스 제어 회로 VBC의 내부에서 발생한 마이너스 전압을 출력하기 위한 패드로서 사용되고 있다. 반도체 집적 회로 장치(100)의 웨이퍼 테스트 시에 패드(101)의 전압을 모니터함으로써 기판 바이어스 제어 회로 VBC 내의 마이너스 전압 발생 회로의 불량을 검출할 수 있다. 통상, 참조 번호 102 내지 104까지의 패드는 반도체 집적 회로 장치(100)의 외부 편에 본딩 접속되지만, 참조 번호 101은 외부 편에는 본딩 접속되지 않은 것으로 한다. 이와 같이 하면, 이 테스트 방법에 의해 외부 편수를 절약할 수 있다.

vbbenb는 기판 바이어스 제어 개시 신호, vbbenbr은 기판 바이어스 제어 중 신호이다. 한편, reset은 리세트 신호에서 반도체 집적 회로 장치(100)의 리세트 신호로 접속된다. vbp는 PMOS 기판 바이어스선, vbn은 NMOS 기판 바이어스선, cbp는 PMOS 기판 제어선, cbn은 NMOS 기판 제어선, cbpr은 PMOS 기판 제어 리턴선, cbnr은 NMOS 기판 제어 리턴선이다. 기판 제어 리턴선 cbpr 및 cbnr은 cbp 및 cbn 신호의 주회로 내를 통과한 후의 복귀 신호이며, 네트는 동일 네트가 된다. 즉, cbp 및 cbn의 드라이브 전압은 소정 지연 후, cbpr 및 cbnr로 각각 나타내게 된다.(후술하는 도 2 참조). 기판 구동 회로(109a, 109b) 각각에는 cbp, vbp, cbn, vbn이 접속되어 있다.

도 2에 상기 vbp로부터 cbnr까지의 6개의 기판 바이어스 제어선의 주회로 LOG 내의 접속 방법을 나타낸다. VBCr은 리턴 셀로 내부에서 PMOS 기판 제어선 cbp와 PMOS 기판 제어 리턴선 cbpr을 접속하고, NMOS 기판 제어선 cbn과 NMOS 기판 제어 리턴선 cbnr을 접속하고 있다.

ncell은 표준 셀을 나타내고 있다. 여기서는 모든 ncell은 간단하게 하기 위해서 PMOS MP2, NMOS MN2로 구성된 CMOS 인버터로 나타내고 있다. 물론, 각각 독립적으로 NAND 게이트나 래치 등의 보다 복잡한 셀이어도 된다. 도 2와 같이 ncell을 구성하고 있는 MOS 트랜지스터의 기판 전위는 PMOS에 대해서는 vbp에, NMOS에 대해서는 vbn에 접속하고 있다.

swcell은 스위치 셀로서, PMOS MP1과, NMOS MN1로 구성된 기판 구동 회로(도 1의 참조 번호 109a, 109b에 상당한다)와, 디커플링 콘텐서 CP1, CP2로 구성되어 있다. MP1의 게이트는 cbp에 드레인은 VBP에 소스는 VDD에 접속되어 있다. 따라서, cbp가 VDD-Vthp(Vthp는 MP1의 임계치 전압의 절대치)보다도 낮은 전압일 때, MP1은 온하고 vbp는 VDD 전위(1.8V)로 구동되게 된다.

한편, MN1의 게이트는 cbn에 접속되고, 드레인은 VBN에, 소스는 VSS(0V)에 접속되어 있다. 따라서, cbn이 Vthn(Vthn은 MN1의 임계치 전압의 절대치)보다도 높은 전압일 때, MN1은 온하고 vbn은 VSS 전위(0V)로 구동되게 된다.

일반적으로, 하나 이상의 많은 수의 ncell이 배치된다. 또한, swcell에 대해서도 하나 이상의 많은 swcell이 배치된다. ncell의 수를 늘림으로써 복잡한 회로를 주회로 LOG 상에 접속할 수 있다. 또한, swcell의 수를 늘림으로써, MP1 및 MN1을 온했을 때 의해 저임피던스에 의해 vbp, vbn을 각각 VDD, VSS로 구동할 수 있다.

또한, 스위치 셀 swcell 내에 디커플링 콘텐서를 내장한 것과는 독립적으로, 스페이스 셀에도 디커플링 콘텐서를 내장시킬 수 있다. 스페이스 셀이란 예를 들면 표준셀 ncell을 열거하여 배치했을 때, 배선 영역 확보를 위해서 생긴 스페이스에 삽입되는 셀이다. 스페이스 셀에도 디커플링 콘텐서를 내장시킴으로써 칩 전체의 디커플링 콘텐서의 용량이 증가하고, 전원 노이즈를 더 저감할 수 있다. 본래, 스페이스 셀은 배선층만의 빈 스페이스이기 때문에, 여기에 콘텐서를 넣음으로써 면적이 증가할 우려는 없다.

swcell 내의 MP1과 MN1은 ncell 내의 MOS 트랜지스터보다도 고임계치로 할 필요가 있다. 이것은, ncell 내의 MOS 트랜지스터의 기판 전위(각각 vbp 혹은 vbn에 접속되어 있다)는 그 소스 전위와는 독립되어 있지만, swcell 내의 MP1과 MN1의 기판 전위는 항상 드레인 전위와 동일하며, 기판 바이어스 효과를 기대할 수 없고 서브 임계 누설 전류가 흐르기 때문이다.

예를 들면 NMOS 트랜지스터 MN1, MN2에 대하여  $v_{bp}=3.3V$ ,  $v_{bn}=-1.5V$ ,  $VDD=1.8V$ ,  $VSS=0V$ 라고 가정하면, ncell 내의 MN2의 소스 전위 S, 드레인 전위 D, 기판 전위 B는, 각각  $S=0.0V$ ,  $D=1.8V$ ,  $B=-1.5V$ 가 되며, 기판 바이어스 효과에 의해 MN2의 임계치 전압이 상승하고, 서브 임계 누설 전류가 작아진다. 그런데, swcell 내의 MN1의 소스 전위 S, 드레인 전위 D, 기판 전위 B는 각각  $S=0.0V$ ,  $D=-1.5V$ ,  $B=-1.5V$ 가 되어, 기판 바이어스 효과에 의한 임계치 전압의 변화가 나타나지 않는다. 따라서, MN1에는 큰 서브 임계 누설 전류가 VSS와 vbn 간에서 흐르게 된다.

swcell 내의 MP1과 MN1의 임계치 전압을 ncell 내의 MOS 트랜지스터보다도 높게 하는 방법에는 주입량을 바꾸거나 게이트 길이(L) 사이즈를 바꾸거나 게이트 산화막 두께를 바꾸거나 함으로써 실현할 수 있다. 이 방법은 특히 한정하지 않지만, 여기서는 L 사이즈와 게이트 산화막 두께를 바꿈으로써 실현하는 것으로 한다. 이 방법에 의해, 마이크로 컴퓨터의 외부와의 입출력 부분의 회로(이하, I/O 회로라고 적는다)에 사용되는 고내압 MOS 트랜지스터를 전용할 수 있다.

도 3에 I/O 회로의 실시예를 나타낸다. 여기서는 1비트분만을 나타내고 있다. 입출력 회로는 침 내부와 외부의 신호를 입출력 단자 PAD를 통하여 행한다. SEL이 'L'일 때 PAD는 입력 단자가 되며, SEL이 'H'일 때는 출력 단자가 된다. LC1은 레벨 변환 회로이며, VDD의 진폭 신호를 진폭이 큰 VDDQ의 진폭 신호로 변환한다. 따라서, 레벨 변환 셀 LC1과 입출력 단자 PAD 간의 트랜지스터는 VDDQ에서 구동되는 두께 산화막 트랜지스터로 구성된다. 여기서는, PULL이 풀업할 필요가 있을 때 'L'로 하여 PMOS의 풀업 트랜지스터로 풀업한다. 이 PMOS도 두께 산화막 트랜지스터로 구성한다.

입력측에 대해서는 외부로부터 입력되는 VDDQ의 진폭을 갖는 신호를 참조 번호 110P 및 110N으로 구성되는 인버터로 VDD의 진폭으로 변환한다. 따라서, 이 두개의 트랜지스터는 레벨 변환 전의 신호를 취급하므로 두께 산화막 트랜지스터로 구성한다. 저항(111R), 다이오드(111D1, 111D2), 트랜지스터(111)는 입력 보호 회로이다. 또, 다이오드(111D1, 111D2)는 MOS 트랜지스터로 구성하여도 좋다. 이 입력 보호 회로 중 트랜지스터는 두께 산화막 트랜지스터로 구성한다.

이상으로 나타낸 두께 산화막 트랜지스터는 그만큼 고속인 스위칭 속도를 요구하지 않은 것과, 취급하는 전압이 VDD에 비교하여 높기 때문에, 임계치 전압을 높게 설정할 수 있다. ncell로 사용되는 트랜지스터보다도 높게 할 수 있다. 이에 따라 이들의 두께 산화막 트랜지스터의 오프 시의 서브 임계 누설 전류를 작게 억제할 수 있다. 이 두께 산화막 트랜지스터를 도 2의 스위치 셀 swcell을 구성하는 MP1 및 MN1로 사용할 수 있다. 이와 같이 하면, 새롭게 MP1, MN1용에 프로세스를 복잡화할 필요가 없어진다.

도 4에서 기판 바이어스 제어 회로 VBC의 내부 구성을 나타낸다. 4개의 회로 블록으로 이루어지며, VBC80은 전원으로서 VDD와 VSS가 공급되고, VBC30에 대해서는 VWELL과 VSS가, VBC85에 대해서는 VDD와 VSUB가, VSUBGEN에는 VWELL, VDD, VSS가 각각 공급되고 있다.

따라서, VBC30, VBC85, VSUBGEN의 내부 회로에 관한 전원 전압은 기껏해야 3.3V이다. 이와 같이  $VDDQ=VWELL$ 로 함으로써, I/O 회로에 공급되어 있는 전원도 VDDQ와 VSSQ에서 3.3V이기 때문에, I/O 회로에 사용하고 있는 디바이스와 기판 바이어스 제어 회로에 사용하는 디바이스를 공통화할 수 있다.

한편, VBC80의 전원은 1.8V이다. 따라서, VBC80으로부터 VBC30, VBC85로의 신호선은 이중 레일 신호(정 논리 신호와 부 논리 신호를 사용하는 한쌍으로 사용하는 밸런스 신호)를 이용하고 VBC30, VBC85 내부에서 레벨 변환(1.8V 진폭 신호를 3.3V 진폭 신호로 변환)하고 있다.

VBC80은 기판 바이어스 제어 회로 VBC의 외부로부터의 입력 신호 cbpr, cbnr, vbbn, reset와 VBC30, VBC85 간의 인터페이스 회로 블록, VBC30은 PMOS의 기판 바이어스를 제어하는 회로 블록, VBC85는 NMOS의 기판 바이어스를 제어하는 회로 블록, VSUBGEN은 마이너스 전압 발생 회로 블록이다.

도 5에 동작 과정 예를 나타낸다. 전원 I/O 회로용 전원 VDDQ, 기판 바이어스 제어 회로 VBC용 전원 VWELL이 투입된 후에 주회로용 전원 VDD가 투입된다. 이에 의해서, 마이너스 전압 발생 회로 블록 VSUBGEN이 기동하여, 마이너스 전압 VSUB가 생성된다. 한편, 전원 VDD가 투입되면 일정 시간 동안 d\_reset 신호가 표명(assert)된다. 이 신호가 표명되면, 기판 바이어스 제어 회로는 주회로의 기판 바이어스를 당기지 않은(이하, 기판 혹은 기판 바이어스를 당긴다는 것은

PMOS에 대해서는 그 기판 바이어스를 VDD 전위로, NMOS에 대해서는 그 기판 바이어스를 VSS 전위로 하는 것으로 한다. 또한, 기판 혹은 기판 바이어스를 당긴다는 것은 PMOS에 대해서는 그 기판 바이어스를 VDD 전위보다 높은 전위로, NMOS에 대해서는 그 기판 바이어스를 VSS 전위보다 낮은 전위로 하는 것으로 한다) 상태 즉 활성화 상태로 최우선으로 천이한다.

이 상태에서는, PMOS 기판 바이어스선 vbp=1.8V, NMOS 기판 바이어스선 vbn=0V, PMOS 기판 제어선 cbp=0V, NMOS 기판 제어선 cbn=1.8V가 된다. 기판 제어 리턴선 cbpr, cbnr은 cbp, cbn 신호의 복귀 신호이므로 cbpr=cbp=0V, cbnr=cbn=1.8V가 된다.

전원 VDD가 투입되어 일정 시간 후, d\_reset 신호가 부정되면, vbbenb 신호에 의해서 기판 바이어스가 제어된다. vbbenb가 3.3V일 때에는 기판이 당겨진 대기 상태로 천이하고, 0V일 때에는 기판이 당겨지지 않는 활성화 상태로 천이한다.

즉, vbbenb가 0V에서 3.3V로 천이하면, vbp=cbp=3.3V, vbn=cbn=-1.5V로 천이한다. 그 후, cbpr=cbp=3.3V, cbnr=cbn=-1.5V로 천이한다. vbbenb는 cbpr=3.3V, cbnr=0V에서 3.3V가 된다. 따라서, vbbenb가 0V에서 3.3V로 천이하고 있는 시간이 경과한 후에(cbp 혹은 cbn의 복귀 신호 cbpr, cbnr이 복귀) 3.3V가 된다.

vbbenb가 3.3V에서 0V로 천이하면, vbp=1.8V, cbp=0V, vbn=0V, cbn=1.8V로 천이한다. 그 후 어느 시간이 경과한 후에, cbpr=cbp=0V, cbnr=cbn=1.8V, vbbenb = 0V로 천이한다. 이와 같이, vbbenb는 vbbenb의 복귀 신호로서 가능한다. 또한, 도 2에서 설명한 바와 같이 기판 전위는 cbp, cbn 전위에 의해서 결정되기 때문에, cbp, cbn 전위로부터 얻어지는 vbbenb를 모니터함으로써 기판의 전위 상태를 검출한 것과 동가일 수 있다.

도 6은 동작 과정의 다른 예이다. 도 5와 다른 부분만 나타내고 있다. 도 6과 같이 cbp, cbn을 제어한 경우에는 제어 회로가 약간 복잡해지지만, 활성화 시에 도 2의 MP1, MN2의 소스 단자와 게이트 단자에 관한 전압을 크게 취할 수 있고, 보다 저임피던스에 vbp, vbn을 구동할 수 있다. 이 경우, 게이트 제어 신호에 상당하는 cbp, cbn의 진폭은 기판 구동 트랜지스터 MP1, MN1의 게이트 내압보다도 커진다. 그러나, 도 6로부터 알 수 있는 바와 같이, cbp, cbn을 천천히 변화시킴으로써 MP1, MN1의 게이트 단자·드레인 단자 및 게이트 단자·소스 단자 간의 전압은 기껏 3.3V가 되며 게이트 내압 이하로 빙아들일 수 있다.

이하에 각각의 회로 블록의 상세 회로도 예를 나타낸다. 이하의 각 회로 블록의 예는 간단하게 하기 위해서 도 4의 과정을 실현하는 회로 예를 나타낸 것으로 한다.

도 7은 VBC80의 회로도이다. 참조 번호 120은 2 입력 NAND, 참조 번호 121은 슈미트 특성을 갖는 2 입력 AND, 참조 번호 122는 인버터, 참조 번호 123은 NOR, 참조 번호 124는 슈미트 특성을 갖는 버퍼, 참조 번호 125는 차동 출력을 갖는 버퍼를 나타내고 있다. 참조 번호 126은 파워 온 리세트 회로로, 그 출력(127)은 전원 VDD가 투입되고나서 서서히 0V에서 1.8V로 충전된다. 따라서, 참조 번호 121의 출력은 일정 시간 0V를 출력하고, 일정 시간 후 1.8V를 출력하게 된다. 이 출력에 의해서 도 5에서 도시한 바와 같이 전원 VDD 투입 시에 d\_reset 신호가 일정 시간 표명된다. 도 7에서는 파워 온 리세트 회로(126)는 저항과 캐패시터에 의한 간단한 것을 사용하고 있지만, 다른 회로 방식이라도 좋다. 요는 전원 VDD가 안정화하기까지를 검출할 수 있는 것이면 된다. d\_vbbenb, d\_cbpr, d\_cbnr은 각각 vbbenb, cbpr, cbnr을 이중 레일화한 신호이지만, 파워 온 리세트 기간은 기판 제어 상태가 활성화 상태가 되도록 하고 있다. d\_vbbenb는 도 5의 vbbenb를 만들기 위한 이중 레일 신호로, cbpr, cbnr에서 만들고 있다.

도 8은 VBC30의 회로도이다. 참조 번호 130은 레벨 변환 회로이고, d\_vbbenb와 d\_reset의 VDD에서 VSS까지의 1.8V 진폭의 이중 레일 신호로부터 VWELL에서 VSS까지의 3.3V 진폭의 신호(133)를 만들고 있다. 참조 번호 133이 'L'이 되는 것은 활성화 상태 혹은 파워 온 리세트 기간일 때이다.

참조 번호 131도 레벨 변환 회로이며, d\_cbpr과 d\_reset의 VDD에서 VSS까지의 1.8V 진폭의 이중 레일 신호로부터, VWELL에서 VSS까지의 3.3V 진폭의 신호(134)를 만들고 있다. 참조 번호 134가 0V가 되는 것은 cbpr이 0V 혹은 파워 온 리세트 기간일 때이다. 참조 번호 133이 0V가 됨으로서, vbp는 하이 임피던스 상태가 되며, cbp는 0V가 되며, cbpenbr은 0V가 된다. cbp가 0V가 되면 주회로 내의 전 swcell 내의 MP1이 온하고, vbp는 1.8V로 구동된다.

참조 번호 132도 레벨 변환 회로이고, 도 7에서 설명한 VBC80으로부터의 d\_vbbenb 신호를 3.3V 진폭의 vbbenb 신호로서 출력하고 있다.

도 9는 cbp의 천이한 모습을 나타낸 것이지만, cbp의 출력 임피던스는 2단계로 변화한다. cbp는 참조 번호 133 신호에 의해서 제어되는 인버터(135)로 구동되지만, 참조 번호 133이 0V에서 또한 참조 번호 134가 0V일 때에는 NMOS(136)가 온하여 NMOS에 의해서도 구동된다. 여기서는 인버터(135) 내의 NMOS의 게이트 폭보다도 NMOS(136)의 게이트 폭을 충분히 크게 해둔다. 활성화 상태로 천이하고, 참조 번호 133이 0V가 되면 인버터(135)에 의해서 cbp는 0V로 구동된다. 그러나, cbp는 주회로 전체에 배선되고 있고, 그 부하 용량은 크게 되어 있다. 여기에서 cbp는 천천히 0V로 구동되게 된다. 그 천이를 cbp의 복귀 신호 cbpr의 천이에 의해서 검출하고, d\_cbpr 신호가 변화한다. 이에 따라 참조 번호 134가 0V가 되면 NMOS(136)가 온한다. 이것에 의해서 cbp는 저임피던스로 0V로 구동된다. 이와 같이 하여 활성화 상태에서는 cbp는 저임피던스로 구동되고, 주회로의 동작에 의한 노이즈의 영향을 저감할 수 있다. 또한, cbp가 0V로 구동되면, 주회로 내의 전 swcell 내의 MP1이 온하지만, cbp의 0V로의 구동을 도 8b와 같이 천천히 구동함으로써 전 swcell 내의 MP1의 동시 스위칭 노이즈를 저감할 수 있다.

도 10은 VBC85의 회로도이다. 참조 번호 140은 레벨 변환 회로이고, d\_vbbenb와 d\_reset의 VDD에서 VSS까지의 1.8V 진폭의 이중 레일 신호로부터, VDD에서 VSUB까지의 3.3V 진폭의 신호(142)를 만들고 있다. 참조 번호 142가 1.8V가 되는 것은 활성화 상태 혹은 파워 온 리셋 기간일 때이다.

참조 번호 141도 레벨 변환 회로이고, d\_cbnr과 d\_reset의 VDD에서 VSS까지의 1.8V 진폭의 이중 레일 신호로부터, VDD에서 VSUB까지의 3.3V 진폭의 신호(143)를 만들고 있다. 참조 번호 143이 1.8V가 되는 것은 cbnr이 1.8V 혹은 파워 온 리셋 기간일 때이다. 참조 번호 142가 1.8V가 됨으로서, vbn은 고임피던스 상태가 되고 cbn은 1.8V가 된다. cbn이 1.8V가 되면 주회로 내의 전 swcell 내의 MN1이 온하고 vbn은 0V로 구동된다.

도 11은 cbn의 천이의 모습을 나타낸 것이지만, cbn의 출력 임피던스는 cbp와 마찬가지로 2 단계로 변화한다. cbn은 참조 번호 143 신호에 의해서 제어되는 인버터(144)로 구동되지만, 참조 번호 142가 1.8V이고 또한 참조 번호 143이 1.8V일 때는 PMOS(145)가 온하여 PMOS(145)에 의해서도 구동된다. 여기서는 인버터(144) 내의 PMOS의 게이트 폭보다도 PMOS(145)의 게이트 폭을 충분히 크게 해둔다. 활성화 상태로 천이하고, 참조 번호 142가 1.8V가 되면 인버터(144)에 의해서 cbn은 0V로 구동된다. 그러나, cbn은 주회로 전체에 배선되어 있으며, 그 부하 용량은 크게 되어 있다. 여기에서 cbn은 천천히 0V로 구동되게 된다. 그 천이를 cbn의 복귀 신호 cbnr의 천이에 의해서 검출하고, d\_cbnr 신호가 변화한다. 이에 따라, 참조 번호 143이 1.8V가 되면 PMOS(145)가 온다. 이것에 의해서 cbn은 저임피던스로 1.8V로 구동된다. 이와 같이 하여 활성화 상태에서는 cbn은 cbp와 마찬가지로 저임피던스로 구동되며, 주회로의 동작에 의한 노이즈의 영향을 저감할 수 있다. 또한, cbn이 1.8V로 구동되면, 주회로 내의 전 swcell 내의 MN1이 온하지만, cbn의 1.8V로의 구동을 도 11과 같이 천천히 구동함으로써 전 swcell 내의 MN1의 동시 스위칭 노이즈가 저감할 수 있다.

이상의 설명에서 밝힌 바와 같이, 본 발명의 기판 바이어스 제어 방식에서는 기판의 구동 임피던스는 기판을 당기지 않은 활성화 상태(전 swcell에 의한 기판 구동)쪽이 기판을 당기는 대기 상태(VBC에 의한 기판 구동)보다도 작아지고 있다. 따라서, 상술한 바와 같이 전원 투입 시에 기판은 당기지 않은 활성화 상태로 천이함으로써, 기판 전위가 불안정하기 때문에 생기는 전원 투입 시의 전원 간 관통 전류 증가 문제나 래치업 문제를 회피할 수 있다. 또한, 활성화 시에는 주회로가 동작하여 기판 노이즈가 많이 발생하지만, 기판의 구동 임피던스를 낮게 함으로써 기판 노이즈를 저감할 수 있고 주회로의 오동작이나 래치업 등을 막을 수 있다.

도 12에 마이너스 전압 발생 회로 VSUBGEN의 내부 구성을 나타낸다. 3개의 회로 블록으로 이루어지며, VSUBSEN은 기판 바이어스 감지 회로, PMP1은 차지 펌프 회로(1), PMP2는 차지 펌프 회로(2)이다. 기판 바이어스 감지 회로 VSUBSEN은 VSUB 전위를 모니터하고, 계다가 vbbenb 신호에 의해서 활성화 상태와 대기 상태를 모니터하여, VSUB=VDD+VSS-VWELL을 만족하도록 제어 신호 pmp1enb, pmp2enb를 이용하여 PMP1 및 PMP2를 제어한다.

PMP1은 pmp1enb 신호가 표명되면 동작하고, PMP2는 pmp2enb가 표명되면 동작한다. PMP1과 PMP2의 차이가 펌프 능력의 차이로, PMP1 쪽이 PMP2와 비교하여 펌프 능력을 크게 하고 있다. PMP1과 PMP2 중 어느 쪽을 사용할지는 vbbenb 신호에 의해 결정되며, 활성화 상태에서는 PMP2가 사용되며, 대기 상태에서는 PMP1이 사용된다.

활성화 상태에서는 VSUB 전위는 기판 바이어스 제어 회로 VBC 내에서만 사용되므로, 그만큼 VSUB에는 전류가 흐르지 않는다. 이 때문에, 펌프 능력이 작은 PMP2가 사용된다. 대기 상태에서는 VSUB 전위는 주회로 전체에 공급되므로, VSUB에는 접합 전류 등의 전류가 흐른다. 이 때문에, 펌프 능력이 큰 PMP1이 사용된다.

도 13에 본 발명의 차지 펌프 회로(1) PMP1의 회로도를 나타낸다. OSC는 링오실레이터로, pmp1enb가 표명되었을 때만 발진하고, VSUB를 마이너스 전압에 충전한다.

도 14는 伊藤清男 저 「초LSI 메모리」, 培風館, p266에 기술되어 있는 차지 펌프 회로에 PMOS(162, 163)를 추가한 것으로, 참조 번호 160, 161의 PMOS를 이용하여 링오실레이터의 1사이클 기간 중에 2회 차지 펌프를 행하는 차지 펌프 회로이다. 본 발명에서는 또한, 도 13에 도시한 바와 같이 NMOS(164, 165)를 추가하고 있다. 이에 의해서, PMOS(160, 161)의 임계치의 영향을 없애고, 저전압 동작에서도 충분히 깊은 VSUB가 얻어진다. VWELL이 3.3V일 때, 도 14의 구성으로는 VSUB=-3.3+ vthp(vthp=PMOS(160, 161)의 임계치의 절대치)까지밖에 얻을 수 없고, 겨우 VSUB=-2.3V 정도인데 대하여, 본 발명의 방식에서는 VSUB=-3.3V 정도까지 얻을 수 있다.

차지 펌프 회로(2) PMP2의 회로도는 특히 여기서는 나타내지 않았지만, 도 13에서 콘덴서로서 사용하고 있는 PMOS CP3, CP4를 작게 하여 콘덴서의 용량을 작게 하면 된다. 물론 이 CP3 혹은 CP4에 맞춰서 그 외의 MOS의 크기를 최적화하면 된다.

도 15에 기판 바이어스 감지 회로 VSUBSEN의 회로도를 나타낸다. VREFGEN은 기준 전압 발생 회로에서, 참조 번호 150, 151에서 나타낸 NMOS의 직렬 접속에 의해  $V_{REF} = (VDD - VSS)/2$ 의 출력을 얻고 있다. V1GEN은 VSUB 전위의 감지 회로에서, 참조 번호 152 내지 155까지의 NMOS의 직렬 접속에 의해,  $V_1 = (VWELL - VSUB)/2$ 의 출력을 얻고 있다. 각각의 NMOS의 소스·드레인 간에는 약 1V 정도의 전위차만이 걸리도록 하고 또한 게이트 길이를 길게 한다. 이것에 의해서, VDD에서 VSS 혹은 VWELL에서 VSUB로의 관통 전류를 작게 억제할 수 있다. 또한, 포화 영역에서 동작하고 있으므로 변동에 대하여 둔감하게 VREF 혹은 V1이 얻어진다. 또한, 본 발명에서는 PMOS가 아닌 NMOS를 사용하고 있다. NMOS는 PMOS보다도 포화 특성이 좋으므로, 소스·드레인 간에 약 1V 정도의 전위차밖에 걸리지 않아도 각 NMOS 간의 변동에 대하여 보다 둔감히 VREF 혹은 V1이 얻어진다.

AMP1, AMP2, AMP3은 각각 차동 증폭기로, 하나의 차동 증폭기를 구성하고 있다. 이 AMP1, AMP2, AMP3으로 이루어지는 차동 증폭기에는 VREF와 V1이 입력되며,  $V_{REF} < V_1$  일 때는 pmp1enb 혹은 pmp2enb가 표명된다. 이에 따라 VSUB는 마이너스 전압 방향으로 충전된다.  $V_{REF} > V_1$  일 때는 pmp1enb 혹은 pmp2enb는 부정된다. VSUB에는 VSS 혹은 VWELL, VDD 방향으로 얼마간의 누설 전류가 있으므로, pmp1enb와 pmp2enb의 양쪽이 부정되고 있으면 VSUB는 플러스 전위 방향으로 방전된다. 이 pmp1enb 혹은 pmp2enb의 표명·부정을 반복함으로써,  $V_1 = V_{REF}$  즉  $VSUB = VDD - VSS - VWELL$ 이 유지되게 된다. 또, 상술한 바와 같이, vbpenb가 3.3V일 때(대기 상태 시)에는 pmp1enb가 표명되고, vbpenb가 0V일 때(활성화 상태 시)에는 pmp2enb가 표명된다.

또한, AMP1과 AMP2 간에는 피드백 경로가 있으며, AMP1, AMP2, AMP3으로 이루어지는 차동 증폭기는 히스테리시스 특성을 가지고 있다. 여기서 말하는 히스테리시스 특성이란 차동 증폭기의 차동점이 증폭기의 출력에 의해서 변화하는 것을 말하며, 소위 슈미트 특성을 갖는 것이다. 이에 따라,  $V_1 = V_{REF}$  부근에서 과도하게 pmp1enb 혹은 pmp2enb가 표명·부정을 반복하는 것을 방지하고 있으며 소비 전력의 증가를 막고 있다.

또한, vbpenb가 표명되었을 때와 부정되었을 때로, AMP1에서 AMP3까지의 차동 증폭기의 동작 전류를 바꾸고 있다. vbp가 표명되는 대기 시에는 VSUB에는 주회로의 vbn이 접속되기 때문에 큰 기판 용량이 접속되게 된다. 따라서, VSUB는 천천히 변화한다. AMP1 내지 AMP3은 고속으로 동작할 필요가 없으므로 동작 전류를 제한할 수 있다. 이에 따라 AMP1에서 AMP3의 소비 전력을 삭감할 수 있다. 한편, vbp가 부정되는 활성화 시에는 VSUB에는 기판 바이어스 제어 회로 VBC만이 접속되기 때문에, 비교적 작은 용량이 VSUB에 접속되게 된다. 따라서, VSUB는 재빠르게 변화하고, AMP1 내지 AMP3은 고속으로 동작할 필요가 있다. 또한, 활성화 시에는 그 정도로 소비 전력이 우려되지는 않는다. 이 때문에, AMP1 내지 AMP3의 동작 전류를 크게 하여 고속 동작시키고 있다.

이하, 기판 바이어스 급전 방법의 보다 자세한 실시예에 대하여 설명한다.

도 16에 ncell 및 swcell의 레이아웃 예를 나타낸다. swcell은 세로 방향(Y 방향)으로 연속하여 배치한다. 또한, swcell과 ncell의 셀 높이는 동일 높이로 통일하고, swcell과 swcell의 가로 방향(X 방향)의 간격 L은 어느 값이내로 가변으로 한다. 물론 일정 간격으로 해도 좋지만 어느 정도 가변으로 하는 쪽이 보다 레이아웃의 자유도가 증가한다. 어느쪽으로 해도 간격 L은 이하의 항목을 고려하여 결정하면 좋다.

(1) 전원선의 임피던스

(2) 전원 배선의 마이그레이션

(3) ncell의 동작함으로써 vbp나 vbn에 생기는 기판 노이즈

도 17에 ncell의 레이아웃 예를 나타낸다. 도 2의 경우와 마찬가지로 인버터를 예로 들고 있다. vbp, vbn, VDD, VSS는 4개의 평행한 제1층 메탈 배선(이하 M1이라고 적는다)에 의해서 급전되고 있다. vbp, vbn은 각각 표면 고농도층에 의해서도 급전되어 있다. H는 셀 높이로, 세로 방향의 기본 반복 단위를 나타내고 있다. 이 높이를 기준으로 세로 방향으로 경면 대칭으로 배치된다. 이것에 의해서 vbp 및 vbn이 상하의 인접하는 ncell과 공유할 수 있으며 면적을 삭감할 수 있다.

도 18에 도 17의 A-B 라인에서의 단면도를 나타낸다. N-well은 MP2를 형성하기 위한 N형 웰, P-well은 MN2를 형성하기 위한 P형 웰이다. Deep-N은 N-well1, P-well1보다도 깊은 곳에 있는 N형 웰이며 소위 3중 웰 구조로 되어 있다.

도 19에 swcell의 레이아웃 예를 나타낸다. 셀의 높이는 ncell과 마찬가지로 H에서 M1에 의한 vbp, vbn, VDD, VSS의 급전선은 ncell과 동일 위치에 있다. 도 16에 도시한 바와 같이, swcell는 세로 방향으로 연속하여, 가로 방향에는 어느 간격이나의 간격으로 배열하고 있다. 이러한 배치로 하는 것으로 이 swcell의 장소에 전원 강화선을 배치할 수 있다. 도 19에서 세로 방향으로 평행하게 배선되어 있는 제2층 메탈 배선(이하, M2라고 적는다)이 이 전원 강화선 2개이다. 이 2개의 전원 강화선 간에 vbp, vbn 강화선 2개와, cbp, cbn 2개가 평행하게 배치되어 있다. 양단의 전원 강화선 VDD, VSS에 의해서, 비교적 임피던스가 높은 4개의 기판 바이어스 제어선을 외래 노이즈로부터 지킬 수 있다.

MP1은 6개의 트랜지스터로 분리되어 형성되며, 그 게이트는 cbp에 드레인은 vbp에, 소스는 VDD에 각각 접속되어 있다. 또한, MN1은 3개의 트랜지스터로 분리되어 형성되며, 그 게이트는 cbn에 접속되고, 드레인은 vbn에, 소스는 VSS에 각각 접속되어 있다. 디커플링 콘덴서 CP1, CP2는 각각 2개의 트랜지스터로 분리되며, MP1 및 MN1의 양단에 형성되어 있으며 MOS 게이트 용량을 이용하여 용량이 만들어지고 있다.

디커플링 콘덴서 CP1 및 CP2의 크기와 MP1 및 MN1의 크기의 비는 특히 한정하지 않는다. 극단적인 예에서는 디커플링 콘덴서 CP1 및 CP2 중 어느 한쪽은 양 쪽을 없애도 좋다. 디커플링 콘덴서를 크게 하면, 전원 노이즈를 저감할 수 있다. 한편, MP1 및 MN1을 크게 하면 마이크로 컴퓨터가 통상 상태일 때, 기판 바이어스를 보다 저임피던스로 전원과 접속할 수 있고 노이즈에 대하여 강해져서 래치업도 발생하기 어려워진다.

M1의 VDD선과 M2의 VDD선 간의 VIA 홀 및, M1의 VSS선과 M2의 VSS 선 간의 비아홀은 간단화를 위해 생략하고 있지만, 각각의 배선의 교점에 비아홀을 설치하면 된다.

도 20에 도 19의 A-B 라인에서의 단면도를 나타낸다. 도 18과 마찬가지로, P-well은 MN1을 형성하기 위한 P형 웰이며, Deep-N은 P-well보다도 깊은 곳에 있는 N형 웰이며 소위 3중 웰 구조로 되어 있다. 여기서는 도 19에서 생략한 M1의 VSS 선과 M2의 VSS선 간의 VIA 홀도 도시하고 있다. 도 2의 설명 부분에서 기술한 바와 같이 MN2에는 두께 산화막 트랜지스터를 이용하여, 임계치를 높게 하고 있다.

도 21에 전원 배선 VDD, VSS 및 기판 바이어스 제어선 vbp, vbn, cbp, cbn의 배선 방법의 보다 구체적인 예를 나타낸다. 도 21은 도 16에 상기 배선을 추가한 것이다. 가로 방향에는 M1에서 배선된 VDD, VSS, vbp, vbn이 평행하게 배선되어 있다. 도 17에서 설명한 바와 같이 vbp는 상하 두개의 셀에 의해서 공유되어, 그 상하에 VDD가 평행하게 배선되어 있다. 또한, vbn도 상하 두개의 셀에 의해서 공유되며, 그 상하에 VSS가 평행하게 배선되어 있다. 물론, VDD, VSS는 vbp, vbn 보다도 굵게 하는 쪽이 좋다.

도 19에서 설명한 바와 같이, 세로 방향으로는 M2로 배선된 VDD, VSS, vbp, vbn, cbp, cbn이 swcell 상을 배선되고 있고, M1과 M2의 교점에서 각각 VDD, VSS, vbp, vbn이 메쉬 형상으로 접속되어 있다.

도 22는 전원 VDD, VSS의 보강의 모습을 나타낸 것이다. 도 21의 기본 반복 단위로 또한 제4 메탈 배선층(이하 M4라고 적는다), 제5 메탈 배선층(이하, M5라고 적는다)으로 형성된 전원선 VDD, VSS가 메쉬 형상으로 배선되어 있다.

세로 방향으로 배선되어 있는 M2의 VDD, VSS의 상공에 M4에서 배선된 VDD, VSS를 배선하고 있지만, 이 양자를 접속하기 위해서는 제3 메탈 배선층(이하, M3라고 적는다)이 필요하다. 이 접속을 모든 swcell 상에서 행하면 M3이 세로 방향으로 배선되게 되며 M3의 가로 방향의 패스가 없어지게 된다는 문제가 있다.

도 22에서는 M2와 M4의 전원선의 접속을 swcell2 혹은 swcell3으로 나타낸 3개마다의 swcell 상에서만 행하고 있다. 이와 같이 함으로써, M3의 가로 방향의 배선 패스를 확보할 수 있다.

M5의 전원선은 swcell3으로 나타낸 6개마다의 swcell 상에서만 행하고 있고, swcell3 상의 M4의 전원선과의 교점에서 접속하고 있다.

상기한 바와 같이 M1, M2가 미세한 피치의 전원 메쉬로, M4, M5가 거친 피치의 전원 메쉬로 보강함으로써, 전원선 VDD, VSS의 임피던스를 내릴 수 있다.

또, 도 22에서는 M4의 세로 방향의 전원선은 전 swcell 상에서 배선하고 있지만, 가로 방향에 2개마다 혹은 3개마다와 같이 거칠게 배선하여도 좋다. 전원선의 임피던스는 커지지만, M4의 세로 방향의 패스를 확보할 수 있다.

도 23에 도 22에 도시한 swcell의 배치와 웰의 관계를 나타낸다. P형 웰 P-well과 N형 웰이 교대로 띠형상으로 대치되어 있고, ncell 두개에서 하나의 웰을 공유하도록 배치되어 있다.

도 24에 메모리 회로의 swcell과 전원선의 레이아웃 예를 나타낸다. 여기서는 워드선 및 비트선은 도시하지 않았지만, 가로 방향으로 워드선이 세로 방향으로 비트선이 배치되어 있다. 메모리 매트의 전원선은 메모리 셀 내는 가로 방향으로 통해 있지만, 이들을 메모리 매트의 양단의 전원선(200, 201, 202)으로 보강하고 있다. 참조 번호 203은 각 워드 드라이버 및 워드 디코더로 전원을 공급하는 전원선을, 참조 번호 204는 각 감지 증폭기로 전원을 공급하는 전원선을 나타내고 있다. swcell은 이상의 200 내지 204까지의 전원선에 도 24와 같이 배치되어 있다.

통상, 복수의 워드 드라이버 및 워드 디코더 내, 동시에 동작하는 것은 하나 혹은 두개 정도이다. 따라서, 기판 노이즈의 량도 그 만큼 많이는 되어 있지 않기 때문에 도면과 같이 참조 번호 203의 양단에 두개의 swcell을 배치한 만큼 되어 있다.

또한 반대로 감지 증폭기는 동시에 다수의 감지 증폭기가 동작한다. 그러나, 감지 증폭기 내부의 전위는 'L'로부터 'H'로 천이하는 노드의 수와 'H'로부터 'L'로 천이하는 노드 1의 수가 거의 동일 수만큼 있다. 그 때문에, 동시에 많은 감지 증폭기가 동작하여도 기판 노이즈는 그만큼 커지지 않는다. 여기서는 도면과 같이 전원선(204)의 양단 이외에도 swcell을 배치하고 기판 노이즈를 저감하고 있다.

그 외, swcell의 배치 방법은 여러가지 생각되지만, 동일 웰 상의 디바이스가 동시에 동작하는 비율이 많을수록 그 웰 상에는 많은 swcell을 배치하면 좋다. 또한, 하나의 웰 내에 있는 확산층에서 그 확산층의 전위 변화를 |NH-NL|/NA(NH=전원에 접속되어 있는 확산층을 제외하는 확산층의 면적, NH=전위가 'H'로부터 'L'로 변화하는 확산층의 면적, NL=전위가 'L'로부터 'H'로 변화하는 확산층의 면적)에 의해서 평가하고, 그것을 기준으로 swcell의 수, swcell의 간격 L 및 swcell 내의 MOS 트랜지스터의 크기를 결정하면 좋다. 요는 되도록이면 |NH-NL|/NA의 값이 작아지도록 하면 좋다.

예를 들면, 데이터 패스와 같은 규칙적인 데이터 플로우가 있는 회로의 경우, 데이터 패스의 데이터 플로우 방향이 도 22에서 X 방향이 되도록 하면 좋다. 동시에 동작하는 셀이 복수의 웰로 분산되기 때문에 상기 |NH-NL|/NA가 작아진다.

도 25는 본 발명의 반도체 집적 회로 장치(100)의 단면도를 나타내고 있다. 도 18에서 도시한 바와 같이, 참조 번호 302, 304, 306, 308, 310으로 나타낸 N은 N-well과 동일하고 PMOS 트랜지스터를 형성하기 위한 N형 웰, 참조 번호 301, 303, 305, 307, 309, 311으로 나타낸 P는 P-well과 같고, NMOS 트랜지스터를 형성하기 위한 P형 웰이다. 참조 번호 312 및 313으로 나타낸 Deep-N은 N, P보다도 깊은 곳에 있는 N형 웰이며 소위 3중 웰 구조로 되어 있다.

Deep-N(312, 313)은 참조 번호 310의 p 기판 및 참조 번호 307의 P 웰에 의해서 전기적으로 분리되어 있다. 따라서, 참조 번호 302, 304, 306, 308, 310 상에 형성된 MOS 트랜지스터 A의 기판 전위와, 참조 번호 301, 303, 305, 307, 309, 311 상에 형성된 MOS 트랜지스터 B의 기판 전위와는 독립된 전위를 제공할 수 있다. 또한, MOS 트랜지스터 A에서 발생한 노이즈 등이 MOS 트랜지스터 B에 영향을 받는 것을 저감할 수 있다.

도 26은 본 발명의 반도체 집적 회로 장치의 Deep-N의 구조를 나타낸 것이다. CPG는 클럭 제어부에서 PLL(위상 로크 루프) 등의 아날로그 회로를 포함하고 있다. TLB는 어드레스 변환부, CACHE는 캐시 메모리, CPU는 중앙 연산 처리 장치, FPU는 부동 소수점 연산기, LOG1은 랜덤 로직 1, LOG2는 랜덤 로직 2, PAD는 I/O부를 나타내고 있다. 이와 같이 각 회로 블록을 다른 Deep-N 상에 형성하고 있다.

도 25에서 설명한 바와 같이 각 회로 블록에서 발생한 노이즈가 다른 블록에 영향을 주는 것을 저감할 수 있다. 예를 들면 PAD는 외부 핀을 내부의 신호 진폭보다도 큰 진폭으로 구동하기 때문에 큰 노이즈를 발생한다. 이 노이즈를 CPG 등의 아날로그 회로에 영향을 주는 것을 막을 수 있다.

또한, 기판 전위를 각각 독립하여 인가할 수 있기 때문에, 예를 들면 LOG2에는 vbp, vbn, cbp, cbn에 의한 기판 제어를 행하지 않은 회로를 배치할 수 있다. 즉, 전원과 기판 전위를 접속한(VDD=vbp, VSS=vbn) 회로를 배치할 수 있다.

도 27은 Deep-N과 Deep-N 간에 배치한 가드 대역을 나타낸 것이다. 도 27과 같이 Deep-N과 Deep-N 간에 가드 대역 gband1을 배치한다.

도 28에 단면도를 나타낸다. Deep-N 간에 있는 P 웰(307)을  $P^+$  확산층(314)을 통하여 VSS 전위에 접지한다. Deep-N 간의 노이즈의 전파를 더 작게 할 수 있다. 예를 들면, P-well(305) 상의 MOS에서 발생한 기판 노이즈는, Deep-N(312)의 임피던스가 그만큼 낮지 않기 때문에, 용량 결합으로 Deep-N(312)에 노이즈가 되어 전파한다. 이 노이즈는 마찬가지로 용량 결합에 의해 p 기판(300)에 전파하고자 하지만, p 기판은 가드 대역에서 저임피던스에 의해 접지 전위로 고정되어 있다. 따라서, p 기판에 나타나는 노이즈는 작아진다. 이와 같이 하여, 참조 번호 302, 304, 306, 308, 310 상에 형성된 MOS 트랜지스터로부터의 노이즈의, 참조 번호 301, 303, 305, 307, 309, 311 상에 형성된 MOS 트랜지스터로의 전파가 감소된다.

도 29는 cbp, cbpr의 반도체 접적 회로 상에서의 레이아웃 이미지와, 도 2의 리턴 셀 VBCR의 위치를 나타낸 것이다. cbn, cbnr에 대해서는 마찬가지로 할 수 있는 것으로 여기에서는 생략하였다. 도 21에서 도시한 바와 같이 vbp 및 vbn은 swcell을 배열함으로써 메쉬 형상으로 배선되거나 cbp, cbn은 메쉬 형상으로는 배선되지 않고, 스트라이프형으로 배선된다. 도 29에서는 swcell을 배치됨으로서 배선되는 스트라이프형의 배선을 분로하도록 접속하고 있는 모습을 나타내고 있다. 또한, 리턴 셀은 입력되는 cbp, cbn을 cbpr, cbnr로서 기판 바이어스 제어 회로 VBC로 복귀하기 위한 셀에서, 복귀하는 태이밍을 각 swcell 내에서 cbp의 전파 시간이 가장 느린 swcell의 cbp 도달 태이밍보다도 느린 태이밍으로 cbpr을 복귀할 수 있도록 배치한다. 예를 들면 기판 바이어스 제어 회로 VBC에서 가장 먼 장소로 배치하면 좋다.

이상의 실시예에서는 기판 바이어스에 인가하는 전위는 활성화 시에는 1.8 V, 0.0V, 대기 시에는 3.3V, -1.5V이지만 특히 이에 한정되는 것은 아니다. 활성화 시에 적당한 전위를 기판 바이어스에 인가하여, MOS 트랜지스터의 임계치 변동을 조절할 수 있도록 하여도 좋다.

또한, 주회로를 복수의 회로 블록으로 나누어서, 각각의 회로 블록에 VBC30, VBC85 등의 제어 회로를 개별로 설치하고, 독립하여 활성화 상태와 대기 상태를 설치하여도 좋다. 각각의 회로 블록마다 제어하면 동작하지 않은 회로 블록을 대기 상태로 할 수 있으며, 보다 세밀하게 소비 전력을 제어할 수 있어 저전력화할 수 있다. 또한, 회로 블록에 의해서는, 대기 상태에서도 기판 바이어스를 당기지 않아도 되는 경우도 있다. 그것은 예를 들면 그 회로 블록이나 고임계치인 MOS 트랜지스터로 구성되며 서브 임계 누설 전류를 무시할 수 있는 경우이다.

또한, 이상의 실시예에서는 MOS 트랜지스터의 임계치는 회로의 동작 모드가 활성화 시에 저임계치로 대기 시에는 고임계치로 했지만, I·E·E·E, 스펙트럼, 제66페이지 내지 제71페이지, 1996년(1996 IEEE SPECTRUM, pp66 ~ 71)에 기재되어 있는 것과 같이 IDDQ 테스트 시에 고임계치가 되도록 기판 바이어스를 설정하여 사용하여도 좋다.

이 때, IDDQ 테스트시에 기판에 인가하는 기판 전위가 대기 시에 인가하는 기판 전위보다도 크게 되어 있는 것이 적합하다. 즉, PMOSFET에 대해서는 대기 시보다 높은 전위, NMOSFET에 대해서는 보다 낮은 전위를 인가한다. 이와 같이 하면, IDDQ 테스트 시에 흐르는 서브 임계 누설 전류를 보다 저감할 수 있으므로 고장 발견의 정밀도가 향상된다.

이러한 동작을 가능하게 하기 위해서는, IDDQ 테스트 시에 VWELL 전위를 예를 들면, 3.3V에서 4.0V로 올리고, VSUB 전위를 -1.5V에서 -2.2V로 내린다. 회로적으로는, VWELL 전위를 VDDQ 전위와 다른 전위로 하여도 관통 전류가 흐르도록 할 필요가 있다. 이 때문에, 예를 들면, 기판 바이어스 제어 회로 VBC로의 신호는 모두 VBC80으로 레벨 다운하고나서 VWELL 전위 혹은 VSUB 전위로 변환하여 사용한다. 이와 같이 전압적인 버퍼를 설치함으로써 실현할 수 있다.

이상의 실시예에서는, 기판 구조는 3중 웰 구조를 가정했지만 그 구조는 특히 한정하지 않는다. 소위 트윈터브 구조의 2중 웰 구조라도 좋고, SOI(Silicon on insulator) 구조라도 좋다.

또한, 도 17, 도 19, 도 21에 도시한 바와 같이, 본 발명에서는 셀 내의 기판 바이어스 급전은 M1에 의해서 행하였지만, 이 구조는 특히 한정하지 않는다. 예를 들면 1997 심포지움·온·VLSI·서킷·다이제스트·오브·테크니컬·페이퍼즈, 제95페이지 내지 제96페이지, 1997년(1997 Symposium on VLSI circuits Digest of Technical Papers, pp. 95-96)에 기재되어 있듯이 확산층 혹은 실리사이드화한 확산층에 의해서 급전하여도 좋다.

본 출원의 도면 중의 부호의 설명을 이하에 통합하여 적는다.

VBC는 기판 바이어스 제어 회로, LOG는 주회로, VBCC는 대기 제어 회로, I/O는 I/O 회로, vbbenb는 기판 바이어스 제어 개시 신호, vbbenbr은 기판 바이어스 제어 중 신호, vbp는 PMOS 기판 바이어스선, vbn은 NMOS 기판 바이어스선, cbp는 PMOS 기판 제어선, cbn은 NMOS 기판 제어선, cbpr은 PMOS 기판 제어리턴선, cbnr은 NMOS 기판 제어 리턴선, AMP1, AMP2는 차동 증폭기, AMP3은 슈미트 입력 차동 증폭기, VBCR은 리턴 셀, swcell은 스위치 셀, ncell은 표준 셀, P-sub는 P 기판, PLL은 위상·로크·루프, CPG는 클럭 제어부, TLB는 어드레스 변환부, CACHE는 캐시 메모리, CPU는 중앙 처리 장치, FPU는 부동 소수점 연산기, PAD는 I/O 부이다.

### 산업상 이용 가능성

이상 설명한 바와 같이, 본 발명에 따르면, 이하의 과제를 만족하는 고속성과 저전력성의 두점을 양립한 마이크로 프로세서 등의 반도체 집적 회로 장치를 실현할 수 있다.

- (1) 기판 바이어스 제어 회로의 테스트가 용이하다.

- (2) 기판 바이어스를 제어함으로써 CMOS 회로의 오동작을 방지할 수 있다.

- (3) 기판 바이어스를 제어함으로써 면적 증가를 최소한으로 그칠 수 있다.

- (4) 기판 바이어스의 전환 시에서의 반도체 집적 회로 장치의 오동작을 방지할 수 있다.

### (57) 청구의 범위

#### 청구항 1.

반도체 집적 회로 장치에 있어서,

복수의 영역을 포함하는 주회로와,

상기 복수의 영역의 각각에 포함되는 제1 MOS 트랜지스터에 공급되는 기판 바이어스 전압을 제어하는 기판 바이어스 제어 회로와,

상기 기판 바이어스 제어 회로를 제어하여, 상기 주회로의 상태를 제1 상태 또는 제2 상태로 제어하는 대기(standby) 제어 회로와,

상기 기판 바이어스 제어 회로에 의해 제어되고, 상기 제1 상태에서 상기 기판 바이어스 전압을 구동하는 복수의 구동 트랜지스터를 구비하고,

상기 복수의 구동 트랜지스터의 각각의 소스·드레인 경로는, 복수의 상기 영역에 포함되는 제1 MOS 트랜지스터의 소스·웰 간에 설치되어 있고,

상기 기판 바이어스 제어 회로는, 상기 제2 상태에서의 제1 MOS 트랜지스터의 임계치 전압의 절대치가 상기 제1 상태에서의 제1 MOS 트랜지스터의 임계치 전압의 절대치보다도 높게 되도록 상기 기판 바이어스를 제어하고,

상기 기판 바이어스 전압은, 상기 제1 상태에서는 상기 복수의 구동 트랜지스터의 소스·드레인 경로를 통해 공급되고, 상기 제2 상태에서는 상기 기판 바이어스 제어 회로로부터 공급되는 반도체 집적 회로 장치.

#### 청구항 2.

제1항에 있어서,

상기 복수의 구동 트랜지스터의 게이트는 기판 제어선에 접속되고,

상기 기판 바이어스 제어 회로는, 상기 복수의 구동 트랜지스터의 게이트를 구동하는 기판 제어 신호를 상기 기판 제어선에 출력하는 반도체 집적 회로 장치.

### 청구항 3.

제2항에 있어서,

상기 기판 바이어스 제어 회로는, 상기 제2 상태로부터 상기 제1 상태로 천이하는 과정에서의 상기 기판 제어 신호의 출력 임피던스를 상기 제1 상태로 천이한 후에서의 임피던스보다도 크게 되도록 제어하는 반도체 집적 회로 장치.

### 청구항 4.

제2항 또는 제3항에 있어서,

상기 기판 바이어스 제어 회로는, 상기 기판 제어선을 통해 상기 기판 바이어스 제어 회로로 복귀되는 상기 기판 제어 신호의 복귀 신호를 수신하고,

상기 복귀 신호의 전위에 기초하여, 상기 제1 MOS 트랜지스터의 웰의 전위 상태를 검출하는 반도체 집적 회로 장치.

### 청구항 5.

제2항 내지 제4항 중 어느 한 항에 있어서,

상기 기판 제어 신호의 진폭은 상기 구동 트랜지스터의 게이트 내압보다도 큰 반도체 집적 회로 장치.

### 청구항 6.

제1항 내지 제5항 중 어느 한 항에 있어서,

마이너스 전압 발생 회로를 구비하고,

상기 기판 바이어스 제어 회로는, 상기 제2 상태에서의 상기 마이너스 전압 발생 회로의 출력 임피던스를, 상기 제1 상태에서의 상기 마이너스 전압 발생 회로의 출력 임피던스보다도 작게 되도록 제어하는 반도체 집적 회로 장치.

### 청구항 7.

제6항에 있어서,

상기 마이너스 전압 발생 회로는, 제1 차지 펌프 회로와 제2 차지 펌프 회로를 구비하고,

상기 기판 바이어스 제어 회로는, 상기 제2 상태에서는 상기 제1 차지 펌프 회로를 이용하여 마이너스 전압을 발생시키고, 상기 제1 상태에서는 상기 제2 차지 펌프 회로를 이용하여 마이너스 전압을 발생시키며,

상기 제1 차지 펌프 회로의 펌핑 콘덴서의 용량은, 상기 제2 차지 펌프 회로의 펌핑 콘덴서의 용량보다도 작은 반도체 집적 회로 장치.

#### 청구항 8.

제1항 내지 제7항 중 어느 한 항에 있어서,

상기 구동 트랜지스터의 임계치 전압의 절대치는 상기 제1 MOS 트랜지스터의 임계치 전압의 절대치보다도 큰 반도체 집적 회로 장치.

#### 청구항 9.

제1항 내지 제8항 중 어느 한 항에 있어서,

상기 반도체 집적 회로 장치의 외부와 인터페이스를 하는 I/O 회로를 구비하고,

상기 I/O 회로를 구성하는 적어도 하나의 제2 MOS 트랜지스터의 게이터 절연막 두께는, 상기 제1 MOS 트랜지스터의 게이트 절연막 두께보다도 두꺼운 반도체 집적 회로 장치.

#### 청구항 10.

삭제

#### 청구항 11.

삭제

#### 청구항 12.

삭제

#### 청구항 13.

삭제

#### 청구항 14.

삭제

#### 청구항 15.

삭제

#### 청구항 16.

삭제

#### 청구항 17.

삭제

#### 청구항 18.

삭제

#### 청구항 19.

삭제

청구항 20.

삭제

청구항 21.

삭제

청구항 22.

삭제

청구항 23.

삭제

청구항 24.

삭제

청구항 25.

삭제

청구항 26.

삭제

청구항 27.

삭제

청구항 28.

삭제

청구항 29.

삭제

청구항 30.

삭제

청구항 31.

삭제

청구항 32.

삭제

청구항 33.

삭제

청구항 34.

삭제

청구항 35.

삭제

청구항 36.

삭제

청구항 37.

삭제

청구항 38.

삭제

청구항 39.

삭제

청구항 40.

삭제

청구항 41.

삭제

청구항 42.

삭제

청구항 43.

삭제

청구항 44.

삭제

청구항 45.

삭제

청구항 46.

삭제

청구항 47.

삭제

청구항 48.

삭제

청구항 49.

삭제

청구항 50.

삭제

청구항 51.

삭제

도면

도면1

## 도면2

## 도면3

## 도면4

VBC

## 도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

VSUBGEN

도면13

도면14

도면15

도면16

도면17

- |  |         |  |                           |

|--|---------|--|---------------------------|

|  | GATE 전극 |  | NMOS의 능동 영역               |

|  | M1      |  | PMOS의 능동 영역               |

|  | 콘택트 홀   |  | PMOS의 기판 금전을 위한 표면 고농도 N층 |

|  |         |  | NMOS의 기판 금전을 위한 표면 고농도 P층 |

도면18

- |            |                           |

|------------|---------------------------|

| GATE 산화막   | NMOS의 능동 영역 (N+)          |

| GATE 전극    | PMOS의 능동 영역 (P+)          |

| 분리         | PMOS의 기판 급전을 위한 표면 고농도 N층 |

| M1-M2 비아 홀 | NMOS의 기판 급전을 위한 표면 고농도 P층 |

## 도면19

도면20

도면21

도면22

도면23

도면24

|  |             |  |     |

|--|-------------|--|-----|

|  | swcell      |  | VDD |

|  | 메모리 셀       |  | VSS |

|  | 감지 증폭기      |  |     |

|  | 워드 디코더·드라이버 |  |     |

도면25

도면26

■ Deep-N

도면27

도면28

도면29