(19) RÉPUBLIQUE FRANÇAISE

—

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

—

COURBEVOIE

(11) **Nº de publication :**

(à n'utiliser que pour les

commandes de reproduction)

**3 030 877**

(21) **Nº d'enregistrement national :**

**15 63137**

(51) Int Cl<sup>8</sup> : **H 01 L 21/318 (2016.01)**

(12)

## BREVET D'INVENTION

**B1**

(54) **FABRICATION DE COUCHES DE NITRURE DE GROUPE IIIA SUR STRUCTURES DE SEMI-CONDUCTEUR SUR ISOLANT.**

(22) **Date de dépôt :** 22.12.15.

(30) **Priorité :** 22.12.14 US 62095282.

(60) **Références à d'autres documents nationaux apparentés :**

**Demande(s) d'extension :**

(71) **Demandeur(s) :** *SUNEDISON SEMICONDUCTOR LIMITED — SG.*

(43) **Date de mise à la disposition du public de la demande :** 24.06.16 Bulletin 16/25.

(45) **Date de la mise à disposition du public du brevet d'invention :** 08.11.19 Bulletin 19/45.

(56) **Liste des documents cités dans le rapport de recherche :**

*Se reporter à la fin du présent fascicule*

(72) **Inventeur(s) :** WANG GANG et SEACRIST MICHAEL R.

(73) **Titulaire(s) :** GlobalWafers Co., Ltd Société dite "limited" de droit taiwanais.

(74) **Mandataire(s) :** LAVOIX.

## FABRICATION DE COUCHES DE NITRURE DE GROUPE IIIA SUR STRUCTURES DE SEMI-CONDUCTEUR SUR ISOLANT

### RENOVI À DEMANDE CONNEXE

[0001] La présente demande revendique la priorité de la demande de brevet provisoire U.S. n° 62/095 282 déposée le 22 décembre 2014.

### 5 DOMAINE DE L'INVENTION

[0002] La présente invention concerne de manière générale le domaine de la fabrication des tranches de semi-conducteur. De manière plus spécifique, la présente invention concerne un procédé de formation d'une couche de nitrure de groupe IIIA sur la couche de dispositif d'une structure de semi-conducteur sur isolant (par exemple, silicium sur isolant).

### ARRIÈRE-PLAN DE L'INVENTION

[0003] Les tranches semi-conductrices sont généralement préparées à partir d'un lingot monocristallin (par exemple, lingot de silicium) qui est taillé et meulé pour présenter un ou plusieurs méplats ou encoches à des fins d'orientation de la tranche dans les procédures ultérieures. Le lingot est ensuite découpé en tranches individuelles. Alors que nous ferons référence ici à des tranches semi-conductrices construites à partir de silicium, d'autres matériaux peuvent être utilisés, tels que du carbure de silicium, du saphir et du nitrure d'aluminium.

[0004] Les tranches semi-conductrices (par exemple, tranches de silicium) peuvent être utilisées dans la préparation de structures de couches composites. Une structure de couches composites (par exemple, une structure de semi-conducteur sur isolant, et de manière plus spécifique, une structure de silicium sur isolant (SOI)) comprend généralement une tranche ou couche de base, une couche de dispositif et un film isolant (à savoir, diélectrique) (d'ordinaire, une couche d'oxyde) entre la couche de base et la couche de dispositif. De manière générale, la couche de dispositif fait entre 0,01 et 20 micromètres d'épaisseur, par exemple, entre 0,05 et 20 micromètres d'épaisseur. En général, les structures de couches composites, telles que du silicium sur isolant (SOI), du silicium sur saphir (SOS) et du silicium sur quartz, sont produites en plaçant deux tranches en contact étroit, puis en procédant à un traitement thermique pour renforcer la liaison.

[0005] Après recuit thermique, la structure liée subit un traitement complémentaire pour éliminer une partie substantielle de la tranche donneuse pour obtenir le transfert de couche. Par exemple, des techniques d'affinage de tranche, par exemple, par gravure ou meulage, peuvent être utilisées, souvent désignées par SOI à gravure en retrait (à savoir, 5 BESOI), où une tranche de silicium est liée à une tranche de base et puis éliminée lentement par gravure jusqu'à que seule une couche mince de silicium subsiste sur la tranche de base. Voir, par exemple, le brevet U.S. n° 5 189 500. Ce procédé prend du temps et est coûteux, gaspille l'un des substrats et ne présente généralement pas d'uniformité d'épaisseur appropriée, pour des couches plus minces que quelques microns.

10 [0006] Un autre procédé commun d'obtention de transfert de couche utilise un implant d'hydrogène suivi par une séparation de couche induite thermiquement. Des particules (par exemple, des atomes d'hydrogène ou une combinaison d'atomes d'hydrogène et d'hélium) sont implantées à une profondeur spécifiée en dessous de la surface avant de la tranche donneuse. Les particules implantées forment un plan de clivage dans la tranche 15 donneuse à la profondeur spécifiée à laquelle elles ont été implantées. La surface de la tranche donneuse est nettoyée pour éliminer les composés organiques déposés sur la tranche pendant le processus d'implantation.

20 [0007] La surface avant de la tranche donneuse est ensuite liée à une tranche de base pour former une tranche liée par le biais d'un processus de liaison hydrophile. Avant la liaison, la tranche donneuse et/ou la tranche de base sont activées en exposant les surfaces des tranches au plasma contenant, par exemple, de l'oxygène ou de l'azote. L'exposition au plasma modifie la structure des surfaces dans un processus souvent appelé activation de 25 surface, lequel processus d'activation rend hydrophiles les surfaces de l'une ou des deux de la tranche donneuse et de la tranche de base. Les tranches sont ensuite pressées ensemble, et une liaison est formée entre elles. Cette liaison est relativement faible, et doit être renforcée avant de pouvoir effectuer un traitement complémentaire.

30 [0008] Dans certains procédés, la liaison hydrophile entre la tranche donneuse et la tranche de base (à savoir, une tranche liée) est renforcée par chauffage ou recuit de la paire de tranches liée. Dans certains procédés, la liaison de tranches peut se produire à de basses températures, telles qu'entre environ 300°C et 500°C. Dans certains procédés, la liaison de tranches peut se produire à de hautes températures, telles qu'entre environ 800°C et 1100°C.

Les températures élevées entraînent la formation de liaisons covalentes entre les surfaces attenantes de la tranche donneuse et de la tranche de base, solidifiant ainsi la liaison entre la tranche donneuse et la tranche de base. En parallèle avec le chauffage ou le recuit de la tranche liée, les particules implantées plus tôt dans la tranche donneuse affaiblissent le plan de 5 clivage.

[0009] Une partie de la tranche donneuse est ensuite séparée (à savoir, clivée) le long du plan de clivage de la tranche liée pour former la tranche SOI. Le clivage peut être effectué uniquement en plaçant la tranche liée dans un bâti où une force mécanique est appliquée perpendiculairement aux côtés opposés de la tranche liée afin d'écartier une partie 10 de la tranche donneuse de la tranche liée. Selon certains procédés, des ventouses sont utilisées pour appliquer la force mécanique. La séparation de la portion de la tranche donneuse est lancée en appliquant un coin mécanique au niveau du bord de la tranche liée au niveau du plan de clivage afin de lancer la propagation d'une fissure le long du plan de clivage. La force mécanique appliquée par les ventouses tire ensuite la partie de la tranche 15 donneuse de la tranche liée, formant ainsi une tranche SOI.

[0010] Selon d'autres procédés, la paire liée peut à la place être soumise à une température élevée sur une période de temps pour séparer la partie de la tranche donneuse de la tranche liée. L'exposition à la température élevée entraîne la création et la propagation d'une fissure le long du plan de clivage, séparant ainsi une partie de la tranche donneuse. Ce 20 procédé permet une meilleure uniformité de la couche transférée et permet de recycler la tranche donneuse, mais requiert d'ordinaire le chauffage de la paire implantée et liée à des températures approchant 500°C.

[0011] La croissance du cristal de la masse des nitrures de groupe IIIA, en particulier du GaN, constitue un défi et n'a pas été opérée avec succès dans la production en 25 volume. D'ordinaire, les nitrures de groupe IIIA, tels que le GaN, sont produits par dépôt hétéroépitaxial sur des substrats de tranche constitués de saphir, de carbure de silicium et de silicium. Le dépôt de nitrures de groupe IIIA sur des tranches semi-conductrices constitue un défi du fait du décalage du coefficient de dilatation thermique (CTE – Coefficient of Thermal Expansion) entre le GaN et au substrat, ce qui conduit à un fort bombement du substrat de la 30 tranche et à des craquelures dans la couche de nitrure de groupe IIIA déposée.

[0012] D'ordinaire, il existe plusieurs approches techniques pour répondre à la tension résiduelle dans les couches de nitre de groupe IIIA, par exemple, de GaN, déposées de manière hétéroépitaxiale sur des substrats semi-conducteurs. Dans une solution, les couches de nitre de groupe IIIA sont déposées sur des substrats semi-conducteurs épais. Par 5 exemple, des substrats de silicium ayant une épaisseur d'au moins environ 1,0 millimètre, tels que de 1,5 millimètre, ont été utilisés pour réduire le bombement de tranche causé par la couche de GaN déposée de manière hétéroépitaxiale. Cette approche ne change pas la tension, mais atténue la déformation de substrat induite par la tension en augmentant la rigidité du substrat. Bien que le bombement de tranche soit réduit, la tension résiduelle ne 10 change pas et les craquelures dans la couche de GaN peuvent rester présentes. Les craquelures sont un défaut nuisible pour la croissance des couches de GaN épaisses ( $> 5 \mu\text{m}$ ) telles qu'utilisées dans les dispositifs d'alimentation haute tension ( $> 800\text{V}$ ). La craquelure de couche et le bombement de tranche deviennent plus sévères lors de l'extension du diamètre du substrat jusqu'à 200 mm ou au-delà.

[0013] Dans une autre technique pour réduire la défectivité dans la couche de nitre de groupe IIIA déposée (par exemple, GaN), une couche tampon ayant une épaisseur comprise entre environ 2 micromètres et environ 5 micromètres peut être déposée sur le substrat de tranche avant la formation de la couche de nitre de groupe IIIA (par exemple, de GaN). La couche tampon peut comprendre du nitre d'aluminium, du nitre d'aluminium et 20 de gallium, ou une multicoche comprenant du nitre d'aluminium et du nitre d'aluminium et de gallium. La tension résiduelle dans les tampons d'AlN/AlGaN tend à déformer le substrat et à créer ainsi une non-uniformité de température à travers le substrat, ce qui conduit à une non-uniformité dans l'épaisseur de la couche ou bien sa composition. Voir Dadgar, Journal of Crystal Growth, 272 (2004) 72–75. Par ailleurs, la tension dans la couche de GaN 25 layer pose un problème en termes de performance de dispositif. Voir Zhang, J. Appl. Phys., 108, 073522 (2010).

[0014] Dans une autre approche, la structure de tampon est optimisée pour induire une tension compressive dans la couche de nitre de groupe IIIA (par exemple, GaN) de telle sorte que la contrainte de traction induite par le décalage CTE peut être partiellement 30 compensée. Un exemple de cette technique est l'utilisation d'une mince couche intermédiaire d'AlN à basse température lors de la croissance épitaxiale du GaN. Le GaN développé sur une couche AlN ou AlGaN à tension relâchée est soumis à une contrainte de compression.

Etant donné que la dislocation dans le GaN a une faible mobilité, la relaxation de contrainte dans la couche de GaN n'est pas complète. A la fin de l'épitaxie, une tension compressive est conservée dans la couche de GaN pour compenser la contrainte de traction induite par le décalage CTE. Voir, par exemple, Amano, J. Appl. Phys. 37, L1540 (1998), et Krost & 5 Dadgar, Phys. Stat. Sol. (a) 200, No. 1, 26–35 (2003). Etant donné que la couche intermédiaire d'AlN et la couche tampon d'AlGaN ne compensent que partiellement la contrainte de traction dans le GaN, l'épaisseur du GaN exempt de craquelures reste limitée à quelques micromètres.

[0015] Dans encore une autre approche, les nitrures de groupe IIIA, tels que GaN, 10 sont développés sur des substrats à motifs. Voir, par exemple, le brevet U.S. n° 8 507 737, qui divulgue la croissance du GaN sur des substrats de saphir à motifs. Voir également la publication U.S. n° 2011/004568 qui divulgue des substrats rainurés. Il a également été rapporté que le GaN peut croître sur des substrats de Si (111) à motifs. Voir Kawaguchi, phys. stat. sol. (a) 176, 553 et Sawaki, Journal of Crystal Growth 311 (2009) 2867–2874. L'objet 15 de ce procédé est de relâcher la tension au bord des îlots de GaN. Toutefois, la relaxation de contrainte est seulement efficace dans les couches de GaN ayant une dimension latérale de quelques centaines de micromètres.

[0016] En outre encore, le GaN a été développé sur des substrats compatibles. La croissance du GaN sur des substrats de SOI présente une qualité cristalline améliorée telle 20 qu'indiquée par Cao, J. Appl. Phys., 83, 3829, 1998. Toutefois, il n'existe aucune étude détaillée sur l'avantage de l'utilisation de substrats de couverture en SOI en termes de craquelure et de relaxation de contrainte. Cette approche peut réduire la défectivité du GaN, mais n'augmente pas nécessairement l'épaisseur du GaN exempt de craquelures.

[0017] Pour finir, l'utilisation d'une couche de CTE côté arrière pour équilibrer le 25 bombement a été divulguée dans la publication U.S. n° 2012/0132921. La publication U.S. n° 2012/0132921 divulgue un procédé pour équilibrer la contrainte de traction dans le GaN en utilisant une couche de CTE sur le côté arrière du substrat. Le défi de ce procédé est que la réaction du film de CTE au changement de température doit suivre celle du GaN.

## RÉSUMÉ DE L'INVENTION

[0018] Un procédé est fourni pour déposer des couches de nitrure de groupe IIIA sur 30 des substrats de semi-conducteur sur isolant (SOI). Dans certains modes de réalisation, les

couches de nitre de groupe IIIA (par exemple, des couches de nitre de gallium (GaN)) sont formées par dépôt hétéroépitaxial sur des substrats de semi-conducteur sur isolant. Avant le dépôt des couches de nitre de groupe IIIA, les substrats de semi-conducteur sur isolant sont soumis à un processus qui produit un motif d'îlots mesa dans la couche de dispositif du substrat de SOI. Dans certains modes de réalisation, le motif d'îlots mesa comprend des îlots semi-flottants, flottants ou des combinaisons à la fois d'îlots flottants et semi-flottants supportés par des colonnes de support formées dans la couche diélectrique des substrats de SOI. Les couches de nitre de groupe IIIA peuvent être formées sur les îlots mesa formés dans les couches de dispositif. Ce procédé est conçu pour répondre au décalage des coefficients de dilatation thermique (CTE) entre un nitre de groupe IIIA, par exemple, GaN, et le substrat ainsi que pour fournir des gabarits épitaxiaux de nitre de groupe IIIA qui sont prêts à être transférés à un substrat porteur dissemblable à faible coût.

[0019] En bref, la présente invention concerne un procédé de formation d'une structure multicouche. Le procédé comprend : la formation d'un motif comprenant une pluralité d'îlots mesa sur une structure de semi-conducteur sur isolant, la structure de semi-conducteur sur isolant comprenant une tranche de base semi-conductrice monocristalline, une couche diélectrique en contact interfacial avec la tranche de base semi-conductrice monocristalline, et une couche de dispositif semi-conductrice monocristalline en contact interfacial avec la couche diélectrique, et en outre dans lequel le motif comprenant la pluralité d'îlots mesa est formé dans la couche de dispositif semi-conductrice monocristalline ; et la formation d'une couche de nitre de groupe IIIA sur la pluralité d'îlots mesa.

[0020] La présente invention concerne en outre une structure multicouche comprenant : une tranche de base semi-conductrice monocristalline comprenant deux surfaces principales généralement parallèles, dont une est une surface avant de la tranche de base semi-conductrice monocristalline et dont l'autre est une surface arrière de la tranche de base semi-conductrice monocristalline, un rebord circonférentiel joignant les surfaces avant et arrière de la tranche de base semi-conductrice monocristalline, une région volumique entre les surfaces avant et arrière, et un plan central de la tranche de base semi-conductrice monocristalline entre les surfaces avant et arrière de la tranche de base semi-conductrice monocristalline ; une couche diélectrique en contact interfacial avec une surface principale de la tranche de base semi-conductrice monocristalline ; une couche de dispositif semi-conductrice monocristalline en contact interfacial avec la couche diélectrique, la couche de

dispositif semi-conductrice monocristalline comprenant un motif comprenant une pluralité d'îlots mésa ; et une couche de nitrure de groupe IIIA sur les îlots mésa.

[0021] La présente invention concerne en outre une structure multicouche comprenant : un substrat porteur ; une couche de liaison interfaciale ; et une couche de nitrure de groupe IIIA, la couche de nitrure de groupe IIIA ayant une épaisseur comprise entre environ 500 nanomètres et environ 1000 micromètres.

[0022] D'autres objets et caractéristiques de la présente invention seront en partie évidents et en partie soulignés ci-après.

#### BRÈVE DESCRIPTION DES DESSINS

[0023] Les figures 1A à 1D illustrent un mode de réalisation du processus de la présente invention.

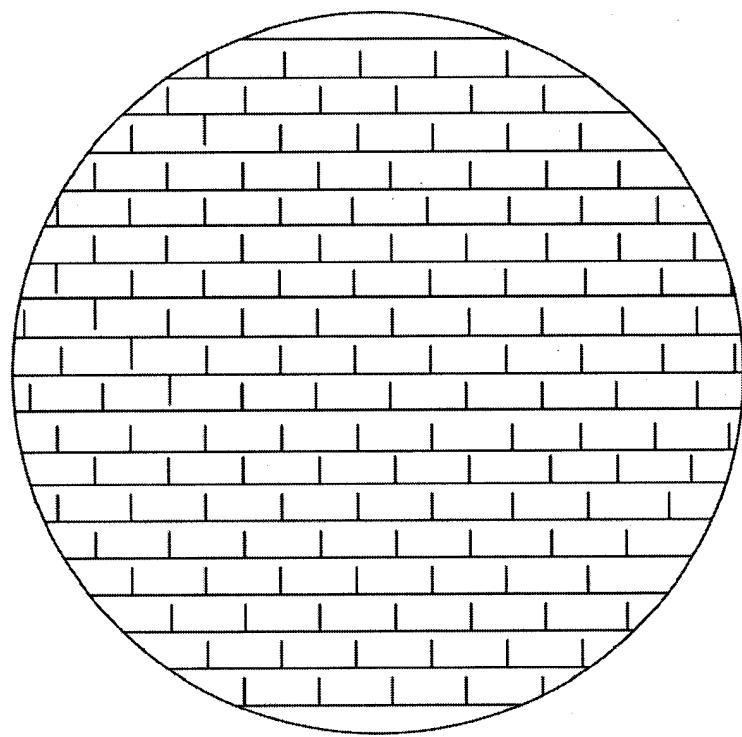

[0024] La figure 2A illustre un motif d'îlots mésa semi-flottants sur un substrat de SOI selon un mode de réalisation de la présente invention.

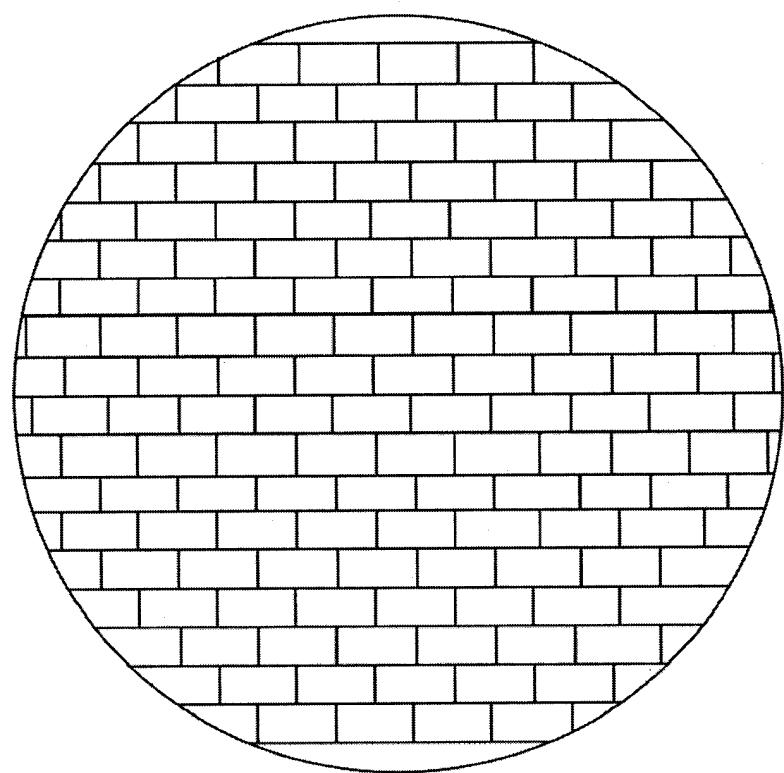

[0025] La figure 2B illustre un motif d'îlots mésa flottants sur un substrat de SOI selon un mode de réalisation de la présente invention.

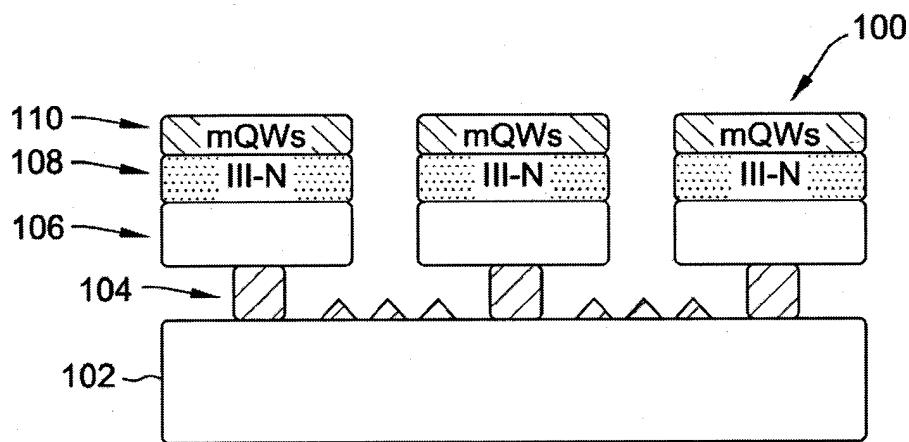

[0026] La figure 3A illustre une structure multicouche selon un mode de réalisation de la présente invention. Dans un mode de réalisation, la structure multicouche illustrée sur la figure 3A comprend un dispositif de diode électroluminescente (DEL) formé directement sur un nitrure de groupe IIIA sur des îlots mésa.

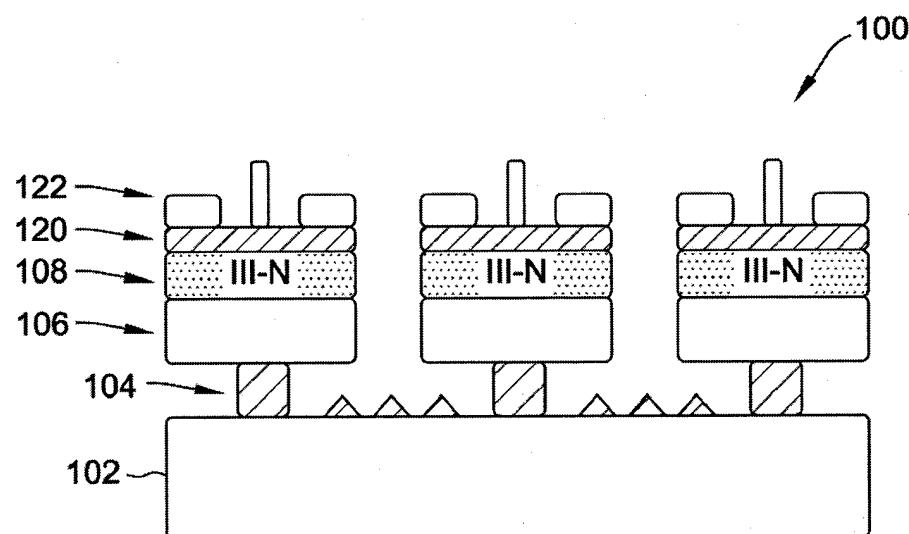

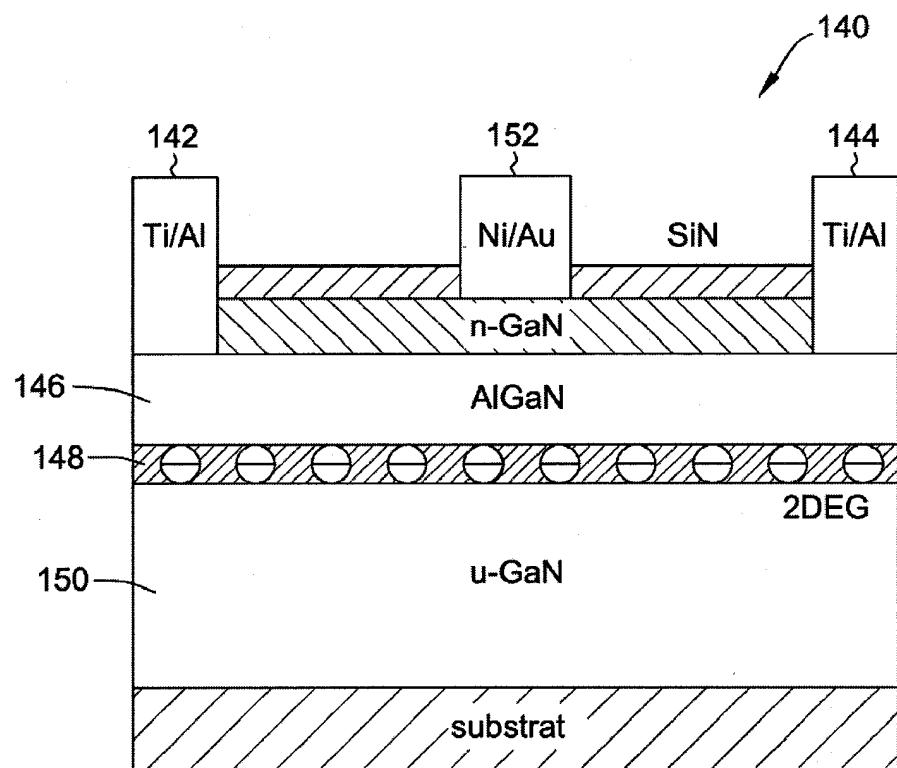

[0027] La figure 3B illustre une structure multicouche selon un mode de réalisation de la présente invention. Dans un mode de réalisation, la structure multicouche illustrée sur la figure 3B comprend un dispositif d'alimentation à transistor à haute mobilité d'électrons (HEMT - High-Electron-Mobility Transistor) formé directement sur un nitrure de groupe IIIA sur des îlots mésa.

[0028] La figure 4 est une illustration d'un dispositif d'alimentation à transistor à haute mobilité d'électrons (HEMT) latéral qui peut être construit sur une couche de nitrure de groupe IIIA sur des îlots mésa.

[0029] Les figures 5A à 5D illustrent un mode de réalisation du processus de la présente invention.

#### DESCRIPTION DÉTAILLÉE DE MODE(S) DE RÉALISATION DE L'INVENTION

[0030] Selon la présente invention, un procédé est fourni pour former une couche de nitrate de groupe IIIA, telle qu'une couche comprenant du GaN, sur un substrat. Dans certains modes de réalisation, la couche de nitrate de groupe IIIA (par exemple, une couche de GaN) est déposée sur un substrat semi-conducteur sur isolant à motifs mésa (SOI, par exemple, silicium sur isolant). Dans certains modes de réalisation, la couche de nitrate de groupe IIIA peut être déposée par dépôt hétéroépitaxial sur des substrats semi-conducteur sur isolant à motifs mésa (SOI, par exemple, silicium sur isolant). Plus particulièrement, une structure de semi-conducteur sur isolant est préparée pour comprendre un motif comprenant une pluralité d'îlots mésa. Le motif comprenant la pluralité d'îlots mésa est formé dans la couche de dispositif semi-conductrice monocristalline (par exemple, une couche de dispositif de silicium monocristallin) du substrat SOI. Dans le contexte de la présente divulgation, la référence à une « couche de dispositif » est faite à la couche de matériau semi-conducteur (d'ordinaire, de silicium monocristallin) sur un substrat de SOI qui résulte d'un processus de transfert de couche classique utilisé pour former une structure de SOI. En d'autres termes, une structure de SOI comprend une tranche de base, une couche diélectrique (d'ordinaire, une couche d'oxyde enterrée, ou BOX), et une couche de dispositif, et elle est formée par un transfert de couche classique au moyen d'une tranche de base et d'une tranche donneuse. La couche de dispositif est dérivée d'une tranche donneuse semi-conductrice monocristalline. Une « couche de dispositif » dans le contexte de la présente divulgation ne désigne pas nécessairement le matériau semi-conducteur dans lequel un dispositif peut être formé. Au contraire, dans le contexte de la présente divulgation, des dispositifs sont généralement formés dans les couches de nitrate de groupe IIIA formées par le procédé de la présente invention. La couche de nitrate de groupe IIIA peut être formée sur les îlots mésa formés dans la couche de dispositif semi-conductrice monocristalline d'un substrat de SOI.

[0031] Dans certains modes de réalisation, une couche tampon peut être formée sur la pluralité d'îlots mésa formés dans la couche de dispositif semi-conductrice monocristalline. La couche de nitrate de groupe IIIA peut être formée sur la couche de tampon formée sur les îlots mésa. Dans le contexte de la présente invention, un îlot mésa formé dans la couche de dispositif semi-conductrice monocristalline (par exemple, une couche de dispositif de silicium

monocristallin) comprend une surface plane pour dépôt d'un nitrule de groupe IIIA. De manière essentiellement perpendiculaire à la surface de dépôt, se trouvent des parois latérales qui définissent les contours des îlots mésa. Les îlots mésa sont supportés par la couche diélectrique de la structure semi-conducteur sur isolant.

5 [0032] Dans certains modes de réalisation, la couche diélectrique est modifiée en retirant une partie de celle-ci, laissant des colonnes de support en dessous des îlots mésa. Dans certains modes de réalisation, par conséquent, le motif d'îlots mésa semi-conducteurs monocristallins flottants et semi-flottants ou leurs combinaisons est supporté par les colonnes de support dérivées de la couche diélectrique. Dans le contexte de la présente invention, un

10 motif d'îlots semi-flottants comprend l'interconnexion ou la formation de pont entre les îlots. Voir, par exemple, la figure 2A. L'interconnexion des îlots avec un matériau semi-conducteur dérivé de la couche de dispositif aide à surmonter par l'affaissement de couche induit par la gravité. Dans certains modes de réalisation, par exemple, la figure 2B, les îlots mésa sont flottants en ce que les îlots ne présentent pas de pont d'interconnexion entre les

15 îlots. Dans encore d'autres modes de réalisation, le motif des îlots mésa peut comprendre à la fois des îlots flottants et semi-flottants, à savoir, dans certains segments de la tranche, les îlots mésa peuvent être connectés par un matériau semi-conducteur, alors que dans d'autres segments de la tranche, les îlots mésa ne sont pas connectés. Le procédé de la présente invention est censé répondre au décalage des coefficients de dilatation thermique (CTE) entre

20 le GaN et le substrat de SOI.

25 [0033] Dans certains modes de réalisation, les dispositifs peuvent être fabriqués directement dans la couche de nitrule de groupe IIIA formée sur le motif d'îlots mésa. Dans certains modes de réalisation, la couche de nitrule de groupe IIIA sur le motif comprenant une pluralité d'îlots mésa peut être transférée sur un substrat porteur dissemblable, et la couche de nitrule de groupe IIIA peut subir en outre une croissance avant la fabrication de dispositifs dans la couche de nitrule de groupe IIIA. Dans certains modes de réalisation, les gabarits de GaN développés sur la structure de SOI sont faciles à transférer vers un substrat porteur dissemblable. Le procédé permet le transfert d'une couche de nitrule de groupe IIIA vers un substrat porteur dissemblable à faible coût. Dans certains modes de réalisation, après transfert

30 de la couche de nitrule de groupe IIIA vers le substrat porteur dissemblable, elle peut être épaisse. Dans certains modes de réalisation, la technique d'épaisseur comprend le dépôt épitaxial. Les dispositifs peuvent être fabriqués dans la couche de nitrule de groupe

IIIA épaisse. Dans certains modes de réalisation, le procédé de la présente invention permet la fabrication de dispositifs qui peuvent actuellement être fabriqués uniquement sur une masse de GaN tel que du GaN vertical sur un dispositif d'alimentation haute tension en GaN, du GaN sur des DEL de GaN et des diodes laser.

5

### 1. Substrat de semi-conducteur sur isolant

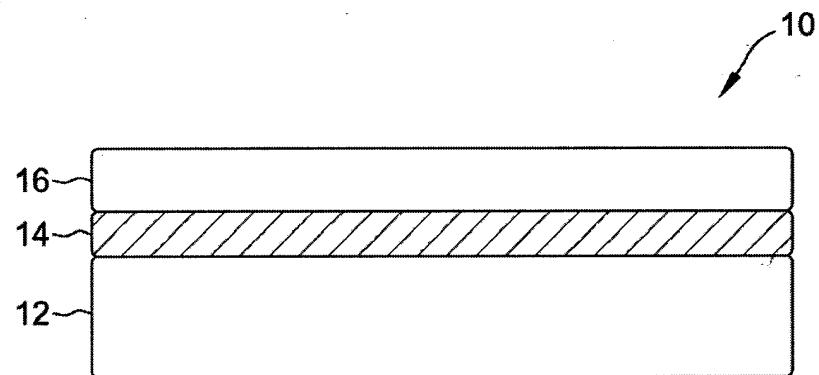

[0034] Les substrats destinés à être utilisés dans la présente invention sont des structures semi-conducteur sur isolant, par exemple, une structure silicium sur isolant. Voir la figure 1A. Une structure semi-conducteur sur isolant **10** est formée par liaison d'une tranche de base semi-conductrice **12** et d'une tranche donneuse semi-conductrice. Une couche diélectrique **14** se trouve entre la tranche de base semi-conductrice **12** et la couche de dispositif semi-conductrice **16**. Lors de la fabrication du SOI, la couche diélectrique intervenante **14** peut être formée sur la surface avant de la tranche de base semi-conductrice **12**, ou elle peut être formée sur la tranche donneuse semi-conductrice. Dans certains processus de fabrication de SOI, les couches diélectriques peuvent être formées sur les deux tranches. La couche de dispositif semi-conductrice **16** dans une structure composite semi-conducteur sur isolant **10** est dérivée de la tranche donneuse semi-conductrice. La couche de dispositif semi-conductrice **16** peut être transférée sur la tranche de base semi-conductrice **12** par des techniques d'amincissement de tranche telles que par gravure d'un substrat donneur semi-conducteur ou par clivage d'un substrat donneur semi-conducteur comprenant un plan de dommage.

[0035] En général, la tranche de base semi-conductrice monocristalline **12** et la tranche donneuse semi-conductrice monocristalline (la couche de dispositif **16** est dérivée de la tranche donneuse dans la fabrication de SOI) comprennent deux surfaces principales généralement parallèles. L'une des surfaces parallèles est une surface avant de la tranche, et l'autre surface parallèle est une surface arrière de la tranche. Les tranches comprennent un rebord circonférentiel joignant les surfaces avant et arrière, et un plan central entre les surfaces avant et arrière. Les tranches comprennent en outre un axe central imaginaire perpendiculaire au plan central et une longueur radiale qui s'étend de l'axe central au rebord circonférentiel. Par ailleurs, étant donné que les tranches, par exemple, les tranches de silicium, présentent d'ordinaire une certaine variation d'épaisseur totale (TTV), une

déformation et un renflement, le point intermédiaire entre chaque point sur la surface avant et chaque point sur la surface arrière peut ne pas se trouver précisément à l'intérieur d'un plan. En pratique, toutefois, la TTV, la déformation et le renflement sont d'ordinaire si légers que dans une proche approximation, on peut dire que les points intermédiaires se trouvent à l'intérieur d'un plan central imaginaire qui est environ équidistant entre les surfaces avant et arrière.

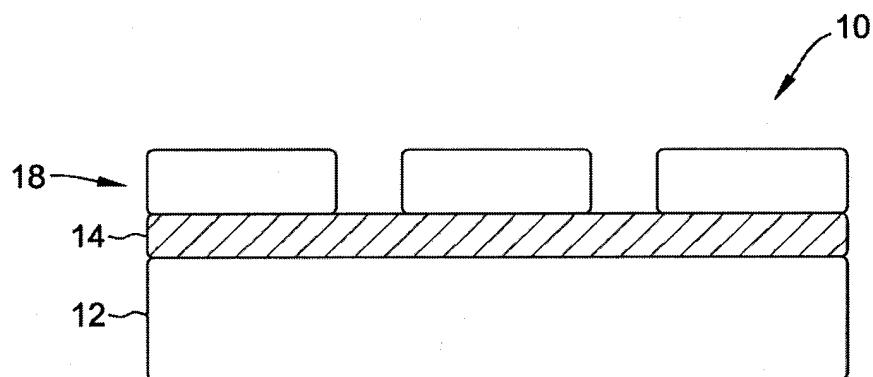

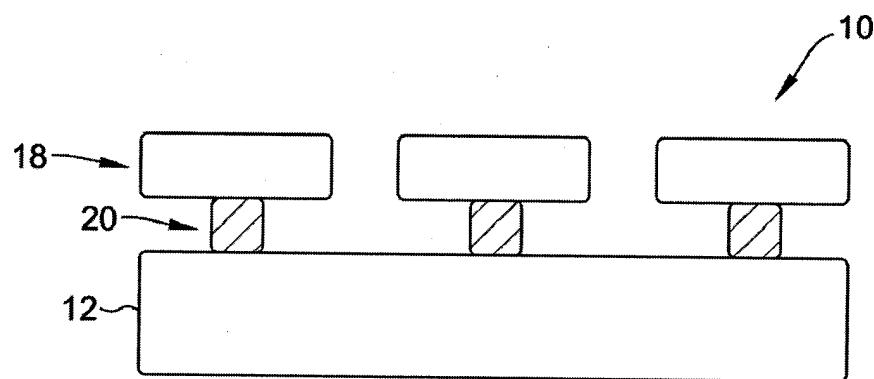

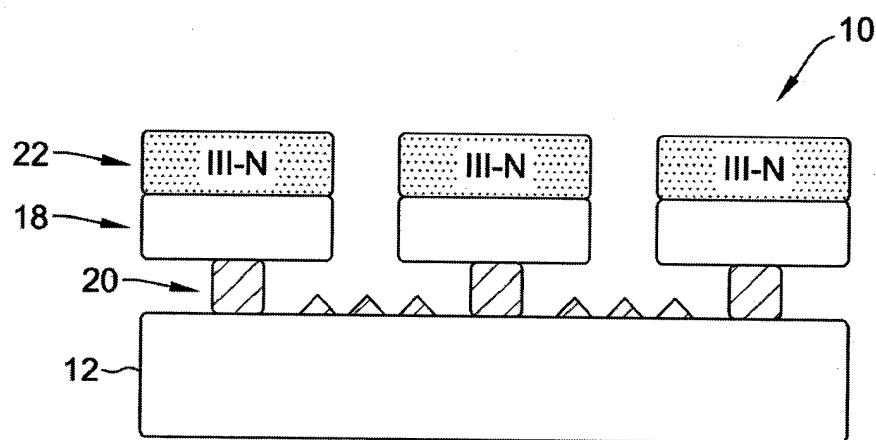

[0036] Si nous regardons à nouveau la figure 1A, la couche de dispositif semi-conductrice **16** dans une structure composite semi-conducteur sur isolant **10** est dérivée d'une tranche donneuse semi-conductrice monocristalline. La couche de dispositif semi-conducteur **16** peut être transférée sur la tranche de base semi-conductrice **12** par des techniques d'amincissement de tranche telles que par gravure d'un substrat donneur semi-conducteur et par clivage d'un substrat donneur semi-conducteur comprenant un plan de dommage. Lors de l'exécution d'étapes de liaison et d'amincissement de tranche classiques, la structure composite semi-conducteur sur isolant (par exemple, silicium sur isolant) **10** comprend la tranche de base semi-conductrice monocristalline **12**, une couche diélectrique **14** telle qu'une couche d'oxyde enterrée, et la couche de dispositif semi-conductrice monocristalline **16**. Un substrat de SOI fini est soumis à la formation de motifs mésa selon le procédé de la présente invention, avant dépôt de la couche de nitrate de groupe IIIA. De manière plus spécifique, la couche de dispositif **16** est soumise à une série d'étapes pour former ainsi un motif d'îlots mésa dans la couche de dispositif semi-conducteur. Se référer à la figure 1B sur laquelle se trouvent une structure composite de semi-conducteur sur isolant **10** (par exemple, silicium sur isolant) comprenant une tranche de base semi-conductrice monocristalline **12**, une couche diélectrique **14** telle qu'une couche d'oxyde enterrée, et un motif d'îlots mésa **18**, qui sont dérivés de la couche de dispositif semi-conducteur **16** de la figure 1A. C'est sur ce motif d'îlots mésa **18** (figures 1B et 1C) formé à partir de la couche de dispositif **16** (figure 1A) que les couches de nitrate de groupe IIIA sont formées. Dans certains modes de réalisation, le motif d'îlots mésa **18** peut comprendre des îlots semi-flottants. Se référer à la figure 2A, qui est un exemple d'illustration en vue de dessus d'îlots mésa semi-flottants. Dans le contexte de la présente invention, un motif d'îlots semi-flottants comprend l'interconnexion ou la formation de ponts entre îlots. Ceci est représenté par les îlots de liaison en matériau semi-conducteur sur la figure 2A, qui est une vue de dessus d'un motif d'îlots mésa interconnectés. Le matériau semi-conducteur de pontage, qui est dérivé de la couche de dispositif **16** de la figure 1A peut être situé sensiblement comme illustré sur la figure 2A, mais d'autres

configurations de liaison sont possibles, telles qu'une liaison substantielle au niveau ou à proximité du milieu des îlots, et en outre un îlot peut être lié à un îlot adjacent, deux îlots adjacents, trois îlots adjacents, quatre îlots adjacents ou encore plus d'îlots, en fonction de la forme des îlots. Dans certains modes de réalisation, le motif d'îlots mésa 18 peut comprendre 5 des îlots flottants. Se référer à la figure 2B, qui est une représentation en vue de dessus d'îlots mésa flottants. Comme le montre la figure 2B, les îlots mésa sont flottants en ce que les îlots ne présentent pas de pont d'interconnexion entre îlots. Dans encore d'autres modes de réalisation, le motif d'îlots mésa peut comprendre à la fois des îlots flottants et semi-flottants, 10 à savoir, dans certains segments de la tranche, les îlots mésa peuvent être reliés par un matériau semi-conducteur, alors que dans d'autres segments de la tranche, les îlots mésa ne sont pas connectés. Par ailleurs encore, la couche diélectrique peut également être gravée 15 pour révéler des colonnes de support qui supportent les îlots mésa. Se référer à la figure 1C, qui illustre la structure composite semi-conducteur sur isolant (par exemple, silicium sur isolant) 10 comprenant la tranche de base semi-conductrice monocristalline 12 et le motif d'îlots mésa 18. La structure de SOI 10 de la figure 1C comprend des structures de support 20 en dessous de chaque îlot mésa. Les structures de support 20 comprennent un matériau diélectrique (par exemple, dioxyde de silicium) puisqu'elles sont dérivées de la couche diélectrique 14 comme illustré sur les figures 1A et 1B.

[0037] La tranche de base semi-conductrice 12 et la couche de dispositif 16 peuvent 20 comprendre un matériau semi-conducteur monocristallin. Dans certains modes de réalisation, le matériau semi-conducteur peut être choisi dans le groupe constitué de silicium, carbure de silicium, saphir et nitre d'aluminium. Dans certains modes de réalisation, la couche de dispositif semi-conductrice, monocristalline, comprend un matériau semi-conducteur choisi dans le groupe constitué de silicium, carbure de silicium, saphir et nitre d'aluminium. Dans 25 certains modes de réalisation, le semi-conducteur peut comprendre du silicium ou du saphir. La tranche de base 12 et la couche de dispositif 14 peuvent comprendre le même matériau semi-conducteur, ou elles peuvent être différentes. Au vu de ceci, les structures de SOI 16 peuvent comprendre, par exemple, du silicium sur isolant, du saphir sur isolant, du nitre d'aluminium sur isolant et d'autres combinaisons. Les structures de semi-conducteur sur isolant 16 ont d'ordinaire un diamètre nominal d'au moins environ 150 mm, d'au moins environ 200 mm, d'au moins environ 300 mm ou d'au moins environ 450 mm. Les épaisseurs peuvent varier d'environ 250 micromètres à environ 1500 micromètres, telles

qu'entre environ 300 micromètres et environ 1000 micromètres, de manière appropriée dans la plage d'environ 500 micromètres à environ 1000 micromètres.

[0038] Dans des modes de réalisation particulièrement préférés, les structures de semi-conducteur sur isolant **10** sont préparées à partir de tranches de support et de tranches donneuses qui sont des tranches de silicium monocristallin qui ont été découpées à partir d'un lingot monocristallin développé selon des procédés classiques de croissance de cristal de Czochralski ou de procédés de croissance de zone flottante. Ces procédés, ainsi que des techniques de découpage, de rodage, de gravure et de polissage de silicium standards sont divulgués, par exemple, dans F. Shimura, *Semiconductor Silicon Crystal Technology*, Academic Press, 1989, et *Silicon Chemical Etching*, (J. Grabmaier ed.) Springer-Verlag, N.Y., 1982 (intégré ici à titre de référence). De préférence, les tranches sont polies et nettoyées par des procédés standards connus de l'homme du métier. Voir, par exemple, W.C. O'Mara et al., *Handbook of Semiconductor Silicon Technology*, Noyes Publications. Si souhaité, les tranches peuvent être nettoyées, par exemple, dans une solution SC1/ SC2 standard. Dans certains modes de réalisation, les tranches de silicium monocristallin de la présente invention sont des tranches de silicium monocristallin qui ont été découpées à partir d'un lingot monocristallin développé selon les procédés de croissance de cristal de Czochralski ("Cz") classiques, ayant d'ordinaire un diamètre nominal d'au moins environ 150 mm, d'au moins environ 200 mm, d'au moins environ 300 mm, ou d'au moins environ 450 mm. De préférence, à la fois la tranche de base en silicium monocristallin et la tranche donneuse en silicium monocristallin présentent des finis de surface avant polis miroir qui sont exempts de défauts de surface, tels que des entailles, des grandes particules, etc. L'épaisseur de la tranche peut varier d'environ 250 micromètres à environ 1500 micromètres, telle que d'entre environ 300 micromètres et environ 1000 micromètres, d'ordinaire dans la plage d'environ 500 micromètres à environ 1000 micromètres. Dans certains modes de réalisation spécifiques, l'épaisseur de la tanche peut être d'environ 725 micromètres.

[0039] Dans certains modes de réalisation, les tranches de semi-conducteur monocristallin, à savoir, la tranche de base et la tranche donneuse, comprennent de l'oxygène interstitiel dans des concentrations qui sont généralement obtenues par le procédé de croissance de Czochralski. Dans certains modes de réalisation, les tranches semi-conductrices comprennent de l'oxygène dans une concentration entre environ 4 PPMA et environ 18 PPMA. Dans certains modes de réalisation, les tranches semi-conductrices comprennent de

l'oxygène dans une concentration comprise entre environ 10 PPMA et environ 35 PPMA. Dans certains modes de réalisation, la tranche de base en silicium monocristallin comprend de l'oxygène dans une concentration ne dépassant pas environ 10 PPMA. L'oxygène interstitiel peut être mesuré selon SEMI MF 1188-1105.

5 [0040] La tranche de base en silicium monocristallin **12** peut avoir n'importe laquelle d'une orientation de cristal (100), (110) ou (111). L'orientation de cristal de la tranche de base **12** n'est souvent pas critique étant donné que la tranche de base **12** ne fait souvent pas partie du dispositif fini. Dans certains modes de réalisation, la tranche donneuse en silicium monocristallin a une orientation de cristal (111). En conséquence et à nouveau en 10 référence à la figure 1A, la structure semi-conducteur sur isolant **10** comprend une couche de dispositif monocristallin **14** ayant une orientation de cristal (111). L'orientation du cristal de silicium (111) est préférée afin d'obtenir une croissance épitaxiale de haute qualité de matériaux de nitrure de groupe IIIA. D'autres orientations de cristaux, telles que (100) et (110), ne sont pas autant réussies pour le dépôt épitaxial de nitrures de groupe IIIA. Par 15 exemple, l'orientation du cristal en silicium (111) est préférée puisqu'elle est conforme à l'habitude de croissance hexagonale du GaN.

20 [0041] Dans certains modes de réalisation la tranche de base semi-conductrice monocristalline **12**, telle que la tranche de base en silicium monocristalline, et/ou la couche de dispositif semi-conducteur **16**, par exemple, une couche de silicium monocristalline, possède une résistivité volumique minimale relativement élevée. Les tranches de haute résistivité sont généralement découpées de lingots monocristallins développés par le procédé de Czochralski ou un procédé de zone flottante. Les tranches de silicium développées par Cz peuvent être soumises à un recuit thermique allant d'environ 600°C à environ 1000°C afin d'annihiler les donneurs thermiques causés par l'oxygène qui sont incorporés lors de la croissance du cristal. 25 Dans certains modes de réalisation, la tranche de base semi-conductrice monocristalline possède une résistivité volumique minimale d'au moins 10 Ohm-cm, d'au moins 100 Ohm-cm, d'au moins environ 500 Ohm-cm, d'au moins environ 1000 Ohm-cm, ou encore d'au moins environ 3000 Ohm-cm, comme d'entre environ 100 Ohm-cm et environ 100 000 Ohm-cm, ou d'entre environ 500 Ohm-cm et d'environ 100 000 Ohm-cm, ou d'entre environ 1000 Ohm-cm et d'environ 100 000 Ohm-cm, ou d'entre environ 500 Ohm-cm et environ 10 000 Ohm-cm, ou d'entre environ 750 Ohm-cm et environ 10,000 Ohm-cm, d'entre environ 1000 Ohm-cm et environ 10 000 Ohm-cm, d'entre environ 2000 Ohm-cm et environ 10 000 Ohm- 30

cm, d'entre environ 3000 Ohm-cm et environ 10 000 Ohm-cm, ou d'entre environ 3000 Ohm cm et environ 5 000 Ohm-cm. Les procédés pour préparer des tranches de haute résistivité sont connus dans l'art, et de telles tranches de haute résistivité peuvent être obtenues de fournisseurs commerciaux, tels que SunEdison Semiconductor Ltd. (St. Peters, MO ; 5 anciennement MEMC Electronic Materials, Inc.).

[0042] Pour former la structure de semi-conducteur sur isolant **10**, la tranche de base semi-conductrice monocristalline **12** est liée à une tranche donneuse semi-conductrice monocristalline, par exemple, une tranche donneuse semi-conductrice monocristalline, qui est préparée selon des procédés de transfert de couche classiques. A savoir, la tranche donneuse 10 semi-conductrice monocristalline peut être soumise à des étapes de traitement standard incluant le nettoyage d'oxydation, d'implantation et post-implantation. En conséquence, une tranche donneuse semi-conductrice monocristalline d'un matériau qui est d'ordinaire utilisé dans la préparation de structures semi-conductrices multicouches, par exemple, d'une tranche donneuse en silicium monocristallin, qui a été gravée et polie et oxydée, est soumise à 15 implantation ionique pour former une couche de dommage dans le substrat donneur.

[0043] La tranche de base et la tranche donneuse sont amenées en contact étroit pour former ainsi une structure liée. Etant donné que la liaison mécanique est relativement faible, la structure liée est en outre recuite par des procédés classiques pour solidifier la liaison entre la tranche donneuse et la tranche de base. Après le recuit thermique, la liaison entre les 20 tranches est suffisamment forte pour lancer le transfert de couche via clivage de la structure liée au niveau du plan de clivage. Le clivage peut se produire selon des techniques connues dans l'art. Si nous regardons la figure 1A, le clivage élimine une partie de la tranche donneuse semi-conductrice, laissant ainsi une couche de dispositif semi-conducteur **16**, de préférence, une couche de dispositif de silicium, en contact interfacial avec une couche 25 diélectrique **14** (à savoir, une couche d'oxyde enterrée ou BOX), qui est en contact avec une tranche de base semi-conductrice monocristalline (par exemple, de silicium) **12**. L'ensemble de la structure comprend la structure composite de semi-conducteur sur isolant **10**, qui est le substrat pour le procédé de la présente invention.

[0044] Si nous regardons à nouveau la figure 1A, entre le substrat de support **12** et la 30 couche de dispositif **16**, se trouve une couche diélectrique **14**. Les matériaux de couche diélectrique **14** appropriée incluent le dioxyde de silicium, le nitre de silicium, l'oxynitre

de silicium, l'oxyde d'hafnium, l'oxyde de titane, l'oxyde de zirconium, l'oxyde de lanthane, l'oxyde de baryum et une combinaison de ceux-ci. Dans certains modes de réalisation préférés, la couche diélectrique **14** comprend une couche d'oxyde enterrée, à savoir, une BOX. L'épaisseur de la couche diélectrique peut être comprise entre environ 10 nanomètres 5 et environ 5000 nanomètres, telle qu'entre environ 10 nanomètres et environ 1000 nanomètres, telle qu'entre environ 50 nanomètres et environ 500 nanomètres.

[0045] La couche de dispositif semi-conductrice monocristalline **16**, par exemple, une couche de dispositif en silicium monocristalline, peut avoir une épaisseur comprise entre environ 1 nanomètre et environ 500 nanomètres, telle que d'entre environ 5 nanomètres et 10 environ 100 nanomètres. A nouveau, la structure de SOI **10** comprend de préférence une couche de dispositif **16** ayant une orientation de cristal Si (111) afin d'obtenir une croissance épitaxiale de haute qualité de matériaux de nitrure de groupe IIIA.

2. Formation d'îlots mésa dans la couche de dispositif d'un substrat de semi-conducteur sur isolant

[0046] Selon le procédé de la présente invention, et en faisant référence à la figure 1B, un motif comprenant une pluralité d'îlots mésa **18** est formé sur une structure de semi-conducteur sur isolant **10**. De manière plus spécifique, le motif comprenant la pluralité d'îlots mésa **18** est formé dans la couche de dispositif semi-conductrice monocristalline **16**. 20 Comparer la figure 1A et la figure 1B, qui sont des illustrations illustrant le substrat de SOI de départ (figure 1A) et un substrat de SOI comprenant un motif d'îlots mésa **18** (figure 1B), où les îlots mésa sont préparés dans la couche de dispositif semi-conducteur d'origine **16**. Le motif comprenant la pluralité d'îlots mésa **18** comprend de préférence des formes formées dans la couche de dispositif semi-conducteur **16** qui sont utiles dans la structure finale qui 25 incorpore la couche de nitrure de groupe IIIA. Dans certains modes de réalisation, les îlots mésa **18** sont formés en éliminant une partie de la couche de dispositif semi-conductrice monocristalline **16**. Dans certains modes de réalisation, les îlots mésa **18** sont formés par lithographie. La lithographie définit les motifs par photorésine. L'élimination du matériau semi-conducteur dans la couche de dispositif **16**, par exemple, du silicium entre les îlots, est 30 réalisée par gravure sélective du matériau semi-conducteur, par exemple, du silicium au moyen d'une gravure ionique réactive (RIE) ou d'une gravure humide. Dans la RIE, un gaz

Cl<sub>2</sub> grave sélectivement le semi-conducteur, par exemple, le silicium. Lors d'une gravure humide, une solution KOH aqueuse ou une solution TMAH aqueuse peut être utilisée. Une fois que la couche de dispositif **16** est ouverte, la photorésine est décapée et la tranche est soumise à une solution HF pour sous-graver la BOX de telle sorte que des îlots mésa flottant et semi-flottant **18** (figure 1C) sont obtenus. La forme des îlots n'est pas primordiale, mais des formes rectangulaires ou carrées sont préférées pour la fabrication de dispositif sur les couches de GaN. Voir la figure 2A illustrant un motif d'îlots mésa semi-flottants sur un substrat de SOI selon un mode de réalisation de la présente invention, et la figure 2B illustrant un motif d'îlots mésa flottants sur un substrat de SOI selon un mode de réalisation de la 10 présente invention.

[0047] Dans certains modes de réalisation de la formation de motifs mésa, des îlots mésa flottants, à savoir, des îlots mésa sans ponts d'interconnexion de matériau semi-conducteur, ne sont pas préférés car il est préférable de maximiser la dimension latérale des îlots. De plus, l'interconnexion ou la formation de pont entre les îlots aide à surmonter 15 l'affaissement de couche induit par gravité. Dans certains modes de réalisation préférés, la partie de la couche de dispositif semi-conductrice monocristalline **16** éliminée pour former un motif d'îlots mésa **18** dans la couche de dispositif semi-conductrice monocristalline laisse un motif dans lequel chaque îlot mésa a une forme quadrilatérale, par exemple, carrée, rectangulaire, de losange, de parallélogramme, etc., lorsqu'il est vu depuis le dessus. Voir, 20 par exemple, les figures 2A et 2B pour illustrations d'un exemple de forme d'îlot mésa approprié. Dans certains modes de réalisation, chaque côté de la forme quadrilatérale a une dimension comprise entre environ 10 micromètres et environ 10 000 micromètres. Les dimensions des îlots mésa peuvent dépendre de la taille de puce requise pour l'utilisation finale souhaitée. Par exemple, les tailles de puce de dispositif d'alimentation peuvent aller 25 d'environ 1000 micromètres à environ 10 000 micromètres. Les tailles de puce pour les dispositifs DEL peuvent aller d'environ 10 micromètres à environ 1000 micromètres, telles qu'entre environ 10 micromètres et environ 500 micromètres. De plus, dans certains modes de réalisation, les îlots mésa peuvent être séparés par un espace ayant une distance comprise entre environ 1 micromètre et environ 100 micromètres.

30 [0048] Dans certains modes de réalisation, la partie de la couche de dispositif semi-conductrice monocristalline **16** (figure 1A) retirée pour former un motif d'îlots mésa **18** (FIGS. 1B et 1C) dans la couche de dispositif semi-conductrice monocristalline laisse un

- motif dans lequel chaque îlot mésa a une forme rectangulaire, lorsqu'il est vu de dessus. Voir par exemple, les figures 2A et 2B, qui sont des vues de dessus d'une structure de SOI dans laquelle une partie de la couche donneuse est retirée pour former un motif comprenant une pluralité d'îlots mésa rectangulaires. Dans certains modes de réalisation, la partie de la 5 couche de dispositif semi-conductrice monocristalline **16** (figure 1A) éliminée pour former un motif d'îlots mésa **18** (figures 1B et 1C) dans la couche de dispositif semi-conductrice monocristalline laisse un motif dans lequel chaque îlot mésa a une forme carrée, lorsqu'il est vu de dessus. Dans certains modes de réalisation, chaque côté de la forme rectangulaire ou carré a une dimension comprise entre environ 10 micromètres et environ 10 000 micromètres.

- 10 De plus, dans certains modes de réalisation, les îlots mésa sont séparés par un espace ayant une distance comprise entre environ 1 micromètre et environ 100 micromètres.

[0049] Après élimination d'une partie de la couche de dispositif semi-conductrice monocristalline **16** pour révéler un motif d'îlots mésa **18** (par exemple, îlots rectangulaires sur la couche d'oxyde enterrée) dans la couche de dispositif comme illustré sur la figure 1B (et 15 illustré en exemple sur les figures 2A et 2B), dans certains modes de réalisation de l'invention, le substrat de SOI **10** est gravé pour éliminer une partie de la couche diélectrique **14** pour former ainsi une couche de structures de support **20** en dessous des îlots mésa **18**. Voir la figure 1C pour un exemple d'illustration non limitative de structures de support **20** 20 supportant un motif d'îlots mésa **18**. Dans certains modes de réalisation, une couche diélectrique **14**, par exemple, du dioxyde de silicium, est éliminée partiellement, de telle sorte qu'un motif d'îlots mésa de silicium monocristallins **18** semi-flottants ou flottants ou les deux est obtenu. Voir figure 1C. La couche diélectrique **14**, par exemple, la BOX, peut être gravée au moyen d'acide fluorhydrique, soit aqueux, soit en phase vapeur. Dans un mode de réalisation, la couche diélectrique **14** peut être gravée au moyen d'une solution HF (0,5-10%) 25 sur un banc humide. Dans un mode de réalisation, la couche diélectrique **14** peut être gravée au moyen de vapeur HF dans une chambre fermée. Dans certains modes de réalisation, la couche diélectrique **14** est gravée de telle sorte que les colonnes de support restantes **20** (figure 1C) ont essentiellement la même forme quadrilatérale que les îlots mésa **18** dans la couche donneuse semi-conductrice monocristalline, mais avec de plus petites dimensions. A 30 savoir, le matériau de couche diélectrique restant **20** (figure 1C), qui supporte les îlots mésa **18**, peut avoir essentiellement une forme quadrilatérale, par exemple, carrée, rectangulaire, de losange, de parallélogramme, etc., lorsqu'ils sont vus de dessus, et ayant des dimensions plus

petites, laissant ainsi des îlots mésa flottants ou semi-flottants **18** formés sur le substrat de SOI **10**.

[0050] Dans certains modes de réalisation, avant dépôt de la couche de nitre de groupe IIIA, le substrat de SOI **10** comprenant le motif d'îlots mésa **18** peut être nettoyé. Par exemple, dans certains modes de réalisation, le substrat de SOI **10** peut être cuit dans une atmosphère d'hydrogène à une température comprise entre environ 900°C et environ 1100°C. Ces conditions de cuisson peuvent être appropriées pour nettoyer l'oxyde à l'état de trace résiduelle sur la couche de dispositif de silicium comprenant les îlots mésa.

### 3. Dépôt de couche tampon sur îlots mésa

[0051] Dans certains modes de réalisation, avant dépôt de la couche de nitre de groupe IIIA, une couche tampon peut être éventuellement déposée sur le motif d'îlots mésa **18** formé dans la couche de dispositif semi-conductrice monocristalline du substrat de SOI **10**. La couche de tampon peut comprendre une couche de nitre d'aluminium formée sur le motif comprenant la pluralité d'îlots mésa **18**. Dans certains modes de réalisation, une couche de nitre d'aluminium peut être déposée par dépôt chimique en phase vapeur à partir de composés organométalliques (MOCVD - MetalOrganic Chemical Vapor Phase Deposition) ou épitaxie en phase vapeur à partir de composés organométalliques (MOVPE - MetalOrganic Vapor Phase Epitaxy), généralement à une température comprise entre 800 et 1100°C. L'épitaxie par faisceaux moléculaires est également une option pour le dépôt d'AlN. Les instruments de dépôt sont disponibles dans le commerce auprès de fabricants tels qu'Aixtron et Vecco. La couche de nitre d'aluminium peut être déposée à une épaisseur comprise entre environ 1 nanomètre et environ 500 nanomètres, telle qu'entre environ 10 nanomètres et environ 100 nanomètres. La couche tampon peut comprendre une couche de nitre d'aluminium et de gallium formée sur le motif comprenant la pluralité d'îlots mésa. En général, le nitre d'aluminium et de gallium peut être déposé par dépôt chimique en phase vapeur à partir de composés organométalliques (MOCVD) ou épitaxie en phase vapeur à partir de composés organométalliques (MOVPE), généralement à des températures comprises entre 800 et 1100°C. La couche de nitre d'aluminium et de gallium peut être déposée à une épaisseur comprise entre environ 1 nanomètre et environ 500 nanomètres, telle qu'entre environ 10 nanomètres et environ 100 nanomètres. Dans certains modes de réalisation, la couche tampon peut comprendre une couche de nitre d'aluminium et de gallium formée sur

une couche de nitrure d'aluminium avant formation de la couche de nitrure de groupe IIIA sur le motif comprenant la pluralité d'îlots mésa.

#### 4. Dépôt de couche de nitrure de groupe IIIA sur îlots mésa

[0052] Si nous regardons la figure 1D, la structure de SOI **10** comprenant la tranche de base semi-conductrice monocristalline **12**, la partie restante de la couche diélectrique **20** comprenant les structures de support, et le motif d'îlots mésa **18** semi-flottants formés à partir de la couche de dispositif semi-conductrice monocristalline supportée par la partie restante de la couche diélectrique **20** est ensuite soumise à un dépôt d'une couche de nitrure de groupe IIIA **22**. Dans le contexte de la présente invention, le groupe IIIA désigne le groupe d'éléments bore, incluant le bore, l'aluminium, le gallium et l'indium. En conséquence, les nitrures de groupe IIIA incluent le nitrure de bore, le nitrure d'aluminium, le nitrure de gallium et le nitrure d'indium. Dans des modes de réalisation préférés, le nitrure de gallium est déposé sur le motif d'îlots mésa. Le nitrure de gallium peut être déposé sur une couche tampon, qui a été préalablement déposée sur les îlots mésa. La couche de nitrure de groupe IIIA peut être déposée par dépôt chimique en phase vapeur à partir de composés organométalliques (MOCVD), épitaxie en phase vapeur à partir de composés organométalliques (MOVPE), ou épitaxie par faisceaux moléculaires (MBE). Dans certains modes de réalisation préférés, la couche de nitrure de groupe IIIA peut être déposée par dépôt chimique en phase vapeur à partir de composés organométalliques (MOCVD). Un réacteur MOCVD approprié peut être un Veeco TurboDisc ou un Aixtron G5. Les précurseurs d'aluminium adaptés au MOCVD incluent le triméthylaluminium et le triéthylaluminium. Les précurseurs de gallium adaptés au MOCVD incluent le triméthylgallium et le triéthylgallium. Les précurseurs d'indium adaptés au MOCVD incluent le triméthylindium, le triéthylindium, le di-isopropylméthylindium, et l'éthyldiméthylindium. Les précurseurs d'azote adaptés au MOCVD incluent l'ammonium, la phénylhydrazine, la diméthylhydrazine, la butylamine tertiaire et l'ammoniac. Les précurseurs de bore incluent le diborane, le chlorure de bore, la 1,3,5-tri(N-méthyl)borazine. Le rapport molaire du précurseur de groupe V (par exemple, ammoniac) sur le précurseur de groupe IIIA (par exemple, triméthylgallium) peut être compris entre 1 et 10000, de préférence, entre 100 et 1000. Un réacteur MOCVD comprend une chambre comprenant des parois de réacteur, un revêtement, un suscepteur, des unités d'injection de gaz et des unités de régulation de température. Les parties du réacteur sont constituées de matériaux résistants aux matériaux précurseurs et non réactifs à ceux-ci.

Pour empêcher une surchauffe, de l'eau de refroidissement peut s'écouler à travers les canaux à l'intérieur des parois de réacteur. Un substrat repose sur un suscepiteur qui est à une température régulée. Le suscepiteur est réalisé à partir d'un matériau résistant aux composés organométalliques utilisés, tels que SiC ou graphite. Du gaz réactif est introduit par une entrée 5 qui contrôle le rapport de réactifs précurseurs. Avant la croissance du GaN, une couche d'ensemencement d'AlN peut être déposée à une épaisseur comprise entre environ 1 nanomètre et environ 200 nanomètres, ou entre environ 5 nanomètres et environ 100 nanomètres, ou entre environ 50 nanomètres et environ 100 nanomètres. La température de croissance peut être comprise entre environ 600°C et environ 1200°C, telle qu'entre environ 10 800°C et environ 1200°C, de préférence, qu'entre environ 1000°C et environ 1150°C. Le 15 nitrure de groupe IIIA peut être formé sous pression réduite, telle qu'entre environ 10 Torr et environ 760 Torr (environ 101 kPa), de préférence, entre environ 10 Torr (environ 1,33 kPa) et environ 80 Torr (environ 10,67 kPa). Lors de la croissance du GaN, la diffusion de précurseurs issue de la phase gazeuse vers les cavités entre deux îlots mésa adjacents est 20 retardée, ce qui supprime en outre le dépôt de matériaux de nitrure. La couche de nitrure de groupe IIIA peut être déposée à une épaisseur comprise entre environ 500 nanomètres et environ 200 micromètres, telle qu'entre environ 500 nanomètres et environ 100 micromètres, ou entre environ 1 micromètre et environ 50 micromètres, ou entre environ 2 micromètres et environ 10 micromètres. La contrainte dans les couches de nitrure est libérée à la fois par des dislocations inadaptées et la déformation élastique de la couche de Si semi-flottante.

[0053] La couche de nitrure de groupe IIIA déposée selon le procédé de la présente invention peut avoir une densité de dislocations traversantes entre environ  $10^6/\text{cm}^2$  et environ  $10^9/\text{cm}^2$ , telle qu'entre environ  $10^7/\text{cm}^2$  et environ  $10^8/\text{cm}^2$ . Dans certains modes de réalisation de la présente invention, la couche de nitrure de groupe IIIA peut être déposée à 25 une épaisseur telle que la densité de dislocations traversantes est inférieure à environ  $10^6/\text{cm}^2$ , telle qu'entre environ  $10^3/\text{cm}^2$  et environ  $10^6/\text{cm}^2$ , ou entre environ  $10^3/\text{cm}^2$  et environ  $10^5/\text{cm}^2$ . Le procédé de la présente invention permet la croissance de couches de GaN épaisses sans craquelures. On sait que la densité de dislocations traversantes (TDD - Threading Dislocation Density) (Kapper, JCG, 300, 70 (2007) dépend de l'épaisseur de la 30 couche de nitrure de groupe IIIA. Selon le procédé de la présente invention, des couches de GaN épaisses peuvent être développées, conduisant à des TDD réduites. Toutefois, l'épaisseur de la couche de GaN épitaxiale issue d'une croissance de GaN classique sur des substrats de couverture est limitée par la craquelure de couche due au décalage de coefficient de dilatation

thermique (CTE - Coefficient of Thermal Expansion) entre le GaN et le substrat, qui est généralement inférieur de 5  $\mu\text{m}$  en conjugaison avec une densité de dislocations traversantes d'environ  $10^8/\text{cm}^2$ . Le procédé de la présente invention permet de surmonter les contraintes de CTE grâce à la croissance de GaN sur des îlots mésa. Par conséquent, l'épaisseur de la 5 couche de GaN peut être étendue à 10  $\mu\text{m}$  et plus, pouvant même atteindre 100 micromètres ou plus, ce qui conduit à une densité de dislocations traversantes sensiblement réduite.

[0054] Une autre technique de défauts peut être appliquée pour réduire les dislocations traversantes, telles qu'une formation de nanomotifs de SiNx in-situ. Voir Kapper, JCG, 300, 70 (2007) et le brevet U.S. n° 7 708 832 B2. La formation de nanomotifs 10 implique l'utilisation de diélectriques (tels que  $\text{Si}_3\text{N}_4$ ) pour bloquer ou terminer les dislocations traversantes sur la surface avant de croissance de la couche de GaN. Comme le diélectrique est mince ( $\sim 1\text{nm}$ ), il présente des orifices qui permettent l'accès à la couche de GaN épitaxiale sous-jacente dans la croissance épitaxiale consécutive. La croissance latérale épitaxiale au-dessus du masque diélectrique favorise la formation d'une couche continue. 15 Voir Kapper. Le masque diélectrique peut être formé dans le réacteur de MOCVD (in-situ) ou par d'autres techniques de dépôt, telles que CVD, ALD, etc. La couche de masque diélectrique peut être du  $\text{Si}_3\text{N}_4$ , du  $\text{SiO}_2$  ou un autre oxyde.

##### 5. Structures de dispositif fabriquées dans la couche de nitrure de groupe IIIA

[0055] Dans certains modes de réalisation et en référence à la figure 3A, une fois 20 terminé le dépôt de la couche de nitrure de groupe IIIA **108** sur le motif d'îlots mésa **106** formé dans la couche de dispositif semi-conductrice monocristalline (**16** sur la figure 1A), de multiples puits quantiques et une couche de contact en P-GaN **110** peuvent être développés directement pour terminer une structure de dispositif de DEL. La croissance des puits quantiques est expliquée dans la littérature. Voir par exemple, Zhang, phys. stat. sol. (a) 188, 25 No. 1, 151–154 (2001)]. Après formation de puits quantiques dans la couche de nitrure de groupe IIIA, la structure **100** comprend la tranche de base semi-conductrice monocristalline **102**, une couche de structures de support **104** dérivée de la couche diélectrique (par exemple, couche d'oxyde enterrée, et **14** sur la figure 1A), une couche comprenant le motif d'îlots mésa **106** (dérivé de la couche de dispositif **16** sur la figure 1A), la couche de nitrure de groupe IIIA **108** formée sur la couche comprenant le motif d'îlots mésa **106**, et les multiples puits 30 quantiques et la couche de contact en P-GaN **110** formés dans la couche de nitrure de groupe IIIA **108**. Dans certains modes de réalisation, les îlots mésa **106** comprenant le nitrure de

groupe IIIA **108** et les puits quantiques **110** sont transférés vers un autre substrat, tel que du verre pour terminer la fabrication et le conditionnement du dispositif de DEL.

[0056] Dans certains modes de réalisation et en référence à la figure 3B, une fois terminé le dépôt de la couche de nitre de groupe IIIA **108** sur le motif d'îlots mésa **106** formé dans la couche donneuse semi-conductrice monocristalline, un dispositif latéral de transistor à haute mobilité d'électrons (HEMT) **120**, **122** peut être développé directement sur la couche de nitre de groupe IIIA **108**. Le dispositif HEMT peut être utilisé comme un dispositif d'alimentation ou comme un dispositif radiofréquence. La puce peut ensuite être détachée et montée directement dans un boîtier. La structure mince (silicium mince avec couches hétéroépitaxiales) aiderait à minimiser les pertes de conductivité thermique. Un dispositif à transistor à haute mobilité d'électrons (HEMT) latéral **140** qui peut être fabriqué sur un nitre de groupe IIIA, par exemple, du GaN, est illustré sur la figure 4. Voir également, par exemple, Joshin, Proceedings of Asia-Pacific Microwave Conference, 2006. Dans le dispositif HEMT latéral **140** illustré sur la figure 4, les électrons se déplacent horizontalement de la source **142** vers le drain **144** le long du gaz d'électrons bidimensionnel **148** (2DEG) formé au niveau de l'interface entre la couche AlGaN **146** et la couche de GaN **150**. La tension de la grille **152** module le 2DEG **148** pour ouvrir et fermer le trajet de courant. Un champ électrique élevé est accumulé entre le drain **144** et la grille **152** et une tension de rupture est d'ordinaire limitée par ce champ électrique. La densité d'électrons du 2DEG **148** détermine la résistance à l'état passant ( $R_{on}$ ) et le courant d'attaque. Comme la densité d'électrons du 2DEG **148** ( $5-10 \times 10^{12}/\text{cm}^2$ ) est induite par effet de polarisation, la tension résiduelle du décalage du CTE peut modifier la performance du dispositif ainsi que la fiabilité du dispositif. Voir Jocob Leach et Hadis Morkoc, Proceedings of the IEEE, 1127, V98, No. 7, July 2010. La présente invention permet la réduction de la tension résiduelle issue du décalage du CTE et fournit une performance de dispositif plus stable.

[0057] Un autre avantage de la présente invention est qu'elle fournit l'option de transfert de la couche de nitre de groupe IIIA de haute qualité (par exemple, une couche de GaN déposée par dépôt épitaxial) vers un autre substrat porteur qui est mis au point pour couvrir l'application du dispositif. Par exemple, un substrat porteur isolant ou semi-isolant ou à haute résistivité, tel qu'un saphir ou AlN polycristallin, est utilisé pour les dispositifs HEMT radiofréquence (RF) construit dans des couches de GaN pour minimiser la perte de RF et la distorsion du signal. Les dispositifs HEMT RF comprennent des structures similaires aux

dispositifs d'alimentation HEMT, mais ils fonctionnent à des tensions plus basses. La structure du HEMT RF est une structure latérale comme celle du dispositif d'alimentation haute tension (600V). Etant donné que le besoin en tension est bien inférieur (<100V), la couche de GaN peut ne pas être aussi épaisse que pour un dispositif d'alimentation, mais par contre, la structure et la séquence de la couche sont d'ordinaire identiques. Ces dispositifs sont conçus sur des substrats semi-isolants pour éviter le couplage de substrat en signal haute fréquence, dans le silicium haute résistivité (> 1000ohm-cm) du cas GaN/Si(111) de Nitronex. Un substrat porteur hautement conducteur, tel que du diamant ou du Si revêtu de diamant, peut être utilisé pour les dispositifs HEMT d'alimentation pour faciliter la dissipation de chaleur.

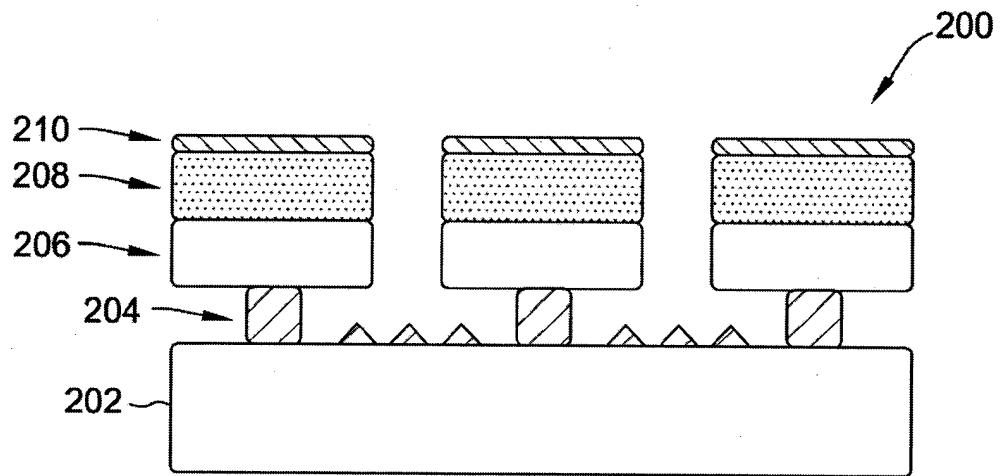

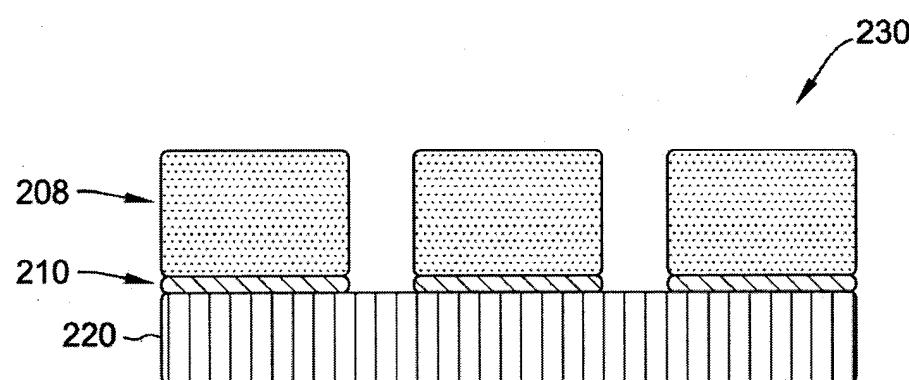

[0058] Dans certains modes de réalisation, la structure telle qu'illustrée sur la figure 1D est adaptée à une utilisation comme point de départ dans la fabrication de dispositifs d'alimentation haute tension. Dans la fabrication de dispositifs d'alimentation haute tension, les îlots mésa comprenant le matériau de nitrure de groupe IIIA (par exemple, GaN) peuvent être transférés vers un substrat porteur pour la croissance supplémentaire du matériau de nitrure de groupe IIIA et la fabrication ultérieure du dispositif. Dans certains modes de réalisation, le substrat porteur possède des propriétés de haute conductivité thermique et de faible conductivité électrique. Dans certains modes de réalisation, le substrat porteur peut comprendre un substrat semi-conducteur monocristallin à haute résistivité, tel qu'un substrat de silicium monocristallin à haute résistivité, un substrat de silicium polycristallin, un substrat de nitrure d'aluminium, un substrat de saphir, un substrat de nitrure d'aluminium polycristallin, un substrat de diamant, une tranche de silicium revêtue de diamant, et similaire. Si nous regardons maintenant les figures 5A à 5D, une structure multicouche 200 est fournie, comprenant une tranche de base semi-conductrice monocristalline 202, une couche de structures de support 204 dérivée de la couche diélectrique (par exemple, une couche d'oxyde enterrée, et 14 sur la figure 1A), une couche comprenant le motif d'îlots mésa 206 (dérivée de la couche de dispositif 16 sur la figure 1A), et la couche de nitrure de groupe IIIA 208 formée sur la couche comprenant le motif d'îlots mésa 206.

[0059] Dans certains modes de réalisation, une mince couche de liaison interfaciale 210 est déposée sur la couche de nitrure de groupe IIIA 208. Dans certains modes de réalisation, la mince couche de liaison interfaciale 210 comprend entre environ 1 nanomètre et environ 5 nanomètres d'oxyde d'aluminium ( $Al_2O_3$ ). La couche de liaison interfaciale 210 peut être

déposée par dépôt de couche atomique ou épitaxie par faisceaux moléculaires. Dans certains modes de réalisation, une couche d'oxyde d'aluminium ( $Al_2O_3$ ) est formée sur la couche de nitrate de groupe IIIA avant transfert sur le substrat porteur.

[0060] Après dépôt de la couche de liaison interfaciale **210**, la couche peut être activée pour liaison par activation par plasma d'oxygène ou d'azote. Dans certains modes de réalisation, l'outil d'activation de surface par plasma d'oxygène est un outil disponible dans le commerce, tel que ceux disponibles dans le groupe EV, tel que le système d'activation par plasma à basse température EVG®810LT. La tranche donneuse semi-conductrice monocristalline éventuellement nettoyée est chargée dans la chambre. La chambre est évacuée et remplie à nouveau avec de l' $O_2$  à une pression inférieure à la pression atmosphérique pour créer ainsi le plasma. La structure multicouche de SOI **200** est exposée à ce plasma pendant le temps souhaité, qui peut aller d'environ 1 seconde à environ 120 secondes. L'oxydation de surface par plasma d'oxygène est effectuée afin de rendre la surface avant de la couche de liaison interfaciale **210** hydrophile et apte à former la liaison à un substrat de base semi-conducteur monocristallin préparé selon le procédé décrit plus haut.

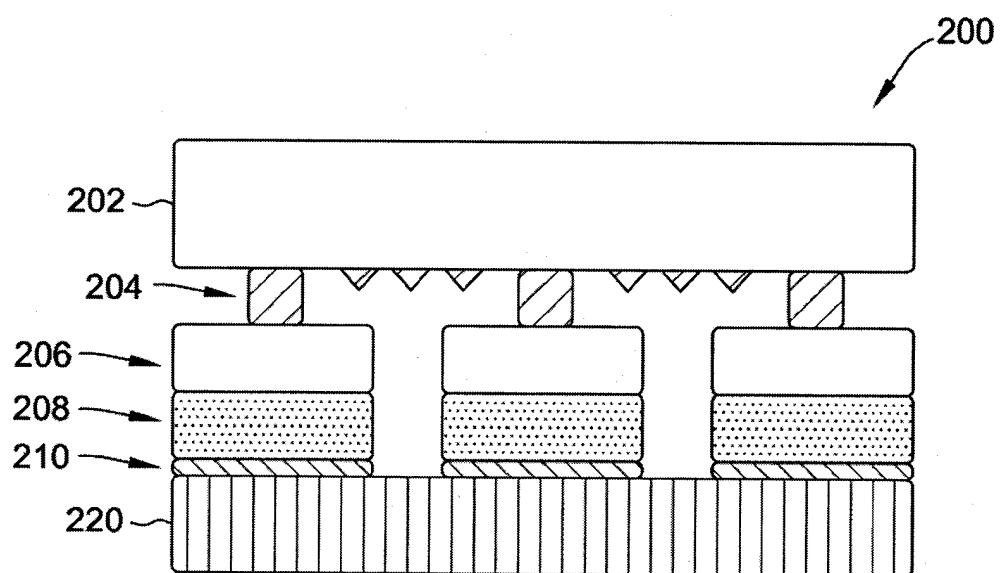

[0061] Si nous regardons maintenant la figure 5B, la structure multicouche **200** comprenant une tranche de base semi-conductrice monocristalline **202**, une couche de structure de support **204** dérivée de la couche diélectrique (par exemple, couche d'oxyde enterrée, **14** sur la figure 1A), une couche comprenant le motif d'îlots mésa **206** (dérivée de la couche de dispositif **16** sur la figure 1A), et la couche de nitrate de groupe IIIA **208** formée sur la couche comprenant le motif d'îlots mésa **206**, et la couche de liaison interfaciale activée **210** est ensuite liée à un substrat de base ou porteur **220**. Le substrat de base ou porteur **220** peut être n'importe quel substrat qui est adapté à une application spécifique. Pour les dispositifs HEMT d'alimentation, des substrats ayant une bonne conductivité thermique, tels que des substrats de diamant, sont adaptés. Pour les dispositifs d'alimentation verticaux, des substrats métalliques, tels que des substrats de cuivre, sont adaptés. Pour les dispositifs DEL, un substrat transparent, tel que du saphir ou du verre, sont adaptés. Pour les dispositifs RF HEMT, des substrats semi-isolants ou isolants sont préférés, tels que du saphir, du Si à haute résistivité, de l'AlN, etc. La liaison entre la structure multicouche **200** et le substrat porteur **220** n'a pas besoin d'être forte. Dans certains modes de réalisation, le substrat de base **220** procure uniquement un support à l'îlot mésa de GaN. Dans certains modes de réalisation, il n'existe pas de processus de suppression de liaison consécutif, tel qu'un clivage. Dans

certains modes de réalisation, la couche d'interface est optionnelle, pourvu qu'un processus de liaison assisté par activation par plasma soit utilisé.

[0062] Selon le processus de la présente invention, la couche diélectrique **204** est gravée pour éliminer la couche diélectrique et le substrat de base en silicium monocristallin **202**. Dans certains modes de réalisation, la couche diélectrique est gravée en immergeant la structure liée dans une solution de gravure comprenant 1-10 % de HF. Une fois la gravure de la couche diélectrique restante effectuée, le motif d'îlots mésa **206** et la couche de nitrure de groupe IIIA **208** sont libérés du substrat de base en silicium monocristallin **202** et sont transférés vers le substrat porteur **220**. Au niveau de l'interface de la couche de nitrure de groupe IIIA **208** et du substrat porteur **220**, la couche de liaison interfaciale **210** est partiellement gravée et affaiblit la résistance de liaison, ce qui s'adapte à toute tension thermique potentielle dans le processus d'épaisseur de nitrure de groupe IIIA consécutif.

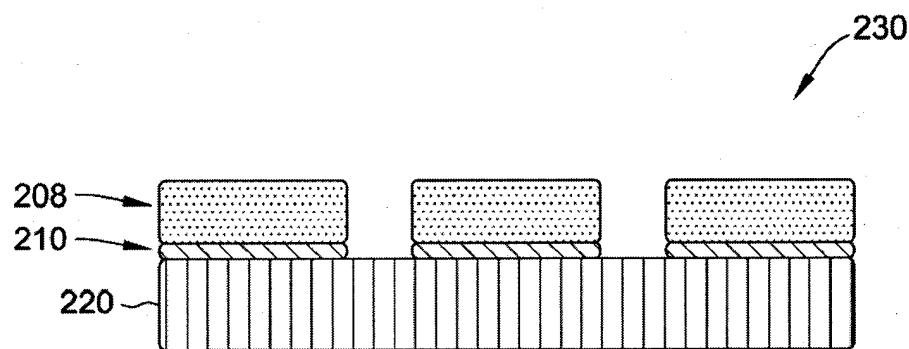

[0063] Selon le processus de la présente invention, les îlots mésa formés dans la couche donneuse semi-conductrice monocristalline **206** sont ensuite retirés pour préparer ainsi la structure **230** représentée sur la figure 5C comprenant un substrat porteur **220**, la couche de liaison interfaciale **210** et la couche de nitrure de groupe IIIA **208**. Ce processus de transfert de couche sur un substrat différent fournit des options polyvalentes pour une différente application de dispositif. Sur les îlots mésa de GaN tels que transférés, des DEL, un dispositif d'alimentation HEMT et un dispositif radiofréquence HEMT peuvent être construits. Les îlots mésa formés dans la couche donneuse semi-conductrice monocristalline **206** peuvent être éliminés par gravure soit par une chimie par voie humide, telle qu'une solution  $\text{HNO}_3/\text{HF}$  et TMAH ou par gravure par plasma. Dans certains modes de réalisation dans lesquels des couches tampons comprenant de l'AlN et/ou de l'AlGaN sont présentes, une gravure au plasma est préférée. La gravure au plasma est également adaptée pour éliminer les couches défectueuses de nitrure de groupe IIIA. Après élimination des couches supérieures défectueuses, une couche de nitrure de groupe IIIA de haute qualité **208** (par exemple, de GaN) ayant des dislocations traversantes comprises entre environ  $10^6/\text{cm}^2$  et environ  $10^9/\text{cm}^2$ , telles qu'entre environ  $10^7/\text{cm}^2$  et environ  $10^8/\text{cm}^2$ , est laissée sur le substrat porteur **220**.

[0064] Dans certains modes de réalisation et en référence à la figure 5D, la couche de nitrure de groupe IIIA de haute qualité **208** (par exemple, de GaN) peut être épaisse. Dans certains modes de réalisation, la couche de nitrure de groupe IIIA de haute qualité **208** (par

exemple, de GaN) peut être épaissie par dépôt épitaxial, par exemple, par épitaxie en phase vapeur à partir de composés organométalliques (MOVPE) ou épitaxie en phase vapeur aux hydrures (HVPE). Les réacteurs HVPE disponibles dans le commerce incluent le système Aura HVPE d'Agnitron Technology, Inc. Les précurseurs de Ga peuvent être de la poudre de 5 GaN synthétisée ou du liquide de Ga. Du gaz vapeur d'HCl est utilisé pour convertir le GaN ou le liquide de Ga en précurseur de GaCl. Du NH<sub>3</sub> est utilisé en tant que précurseur d'azote. De l'Ar est utilisé en tant que gaz porteur. La croissance du GaN survient à une température comprise entre environ 1000°C et environ 1200°C, d'ordinaire d'environ 1000°C à environ 10 1100°C. Le taux de croissance peut être aussi élevé que 100 micromètres par heure. Dans certains modes de réalisation, la couche de nitrure de groupe IIIA peut être épaissie à une épaisseur comprise entre environ 2 micromètres et environ 50 micromètres, de préférence, entre environ 5 micromètres et environ 10 micromètres. Dans certains modes de réalisation, la couche de nitrure de groupe IIIA peut être épaissie à une épaisseur comprise entre environ 15 2 micromètres et environ 2000 micromètres, telle qu'entre environ 2 micromètres et environ 1000 micromètres, ou entre environ 100 micromètres et environ 300 micromètres.

[0065] Dans certains modes de réalisation, la couche de nitrure de groupe IIIA épaissie, par exemple, la couche de GaN, peut être dopée pendant le processus de croissance. Dans certains modes de réalisation, la couche de nitrure de groupe IIIA peut être dopée avec un dopant de type N, tel que du silicium Si, du germanium Ge, du soufre S, du sélénium Se et 20 de l'étain Sn. Des précurseurs appropriés qui peuvent être incorporés dans la formule de gaz lors de la croissance de la couche afin de doper la couche avec un dopant de type N peuvent inclure SiH<sub>4</sub>, GeH<sub>4</sub>, H<sub>2</sub>S, H<sub>2</sub>Se, et (C<sub>2</sub>H<sub>5</sub>)Sn. Dans certains modes de réalisation, la couche de nitrure de groupe IIIA peut être dopée avec un dopant de type P, tel que Mg ou Zn. Des précurseurs appropriés qui peuvent être incorporés dans la formule de gaz lors de la 25 croissance de la couche afin de doper la couche avec un dopant de type N peuvent inclure le bis(cyclopentadiényle) de magnésium, le zinc diéthylique et le zinc diméthylique. Dans certains modes de réalisation, la couche épaissie de nitrure de groupe IIIA, par exemple, la couche de GaN, peut être dopée avec du silicium. Dans certains modes de réalisation, du gaz de SiH<sub>4</sub> peut être ajouté à la formule de gaz lors du processus d'épaississement de la couche 30 de nitrure de groupe IIIA afin de doper la couche avec du Si. Dans certains modes de réalisation, du gaz de SiH<sub>4</sub> peut être ajouté lors de l'épaississement de la couche de GaN afin de doper la couche de GaN avec du Si. L'inclusion de SiH<sub>4</sub> lors de l'épaississement de la couche de nitrure de groupe IIIA peut conduire au dopage de la couche avec du Si pour

préparer ainsi une couche de type n de nitre de groupe IIIA. L'inclusion de SiH<sub>4</sub> lors de l'épaisseur de la couche de GaN peut conduire au dopage de la couche avec du Si pour préparer ainsi la couche de GaN de type N. La concentration de dopant peut aller d'environ 1x10<sup>15</sup> atomes dopants/cm<sup>3</sup> à environ 5x10<sup>20</sup> atomes dopants/cm<sup>3</sup>. Dans certains modes de 5 réalisation pour préparer des couches de nitre de groupe IIIA N-, la concentration de dopant Si peut aller d'environ 1x10<sup>15</sup> atomes dopants/cm<sup>3</sup> à environ 3x10<sup>17</sup> atomes dopants/cm<sup>3</sup>, telle que d'environ 1x10<sup>16</sup> atomes dopants/cm<sup>3</sup> à environ 3x10<sup>16</sup> atomes dopants/cm<sup>3</sup>. Dans certains modes de réalisation pour préparer des couches de nitre de groupe IIIA N+, la concentration du Si dopant peut aller d'environ 1x10<sup>18</sup> atomes 10 dopants/cm<sup>3</sup> à environ 5x10<sup>20</sup> atomes dopants/cm<sup>3</sup>, telle que d'environ 1x10<sup>19</sup> atomes dopants/cm<sup>3</sup> à environ 3x10<sup>20</sup> atomes dopants/cm<sup>3</sup>. Dans certains modes de réalisation, par exemple, des modes de réalisation dans lesquels les couches de nitre de groupe IIIA sont 15 destinées à des dispositifs d'alimentation haute tension verticaux de nitre de gallium sur nitre de gallium, le niveau de dopant peut être modifié lors de la croissance de la couche de nitre de groupe IIIA épaisse. La variation du niveau de dopant permet la croissance d'une couche de nitre de groupe IIIA ayant de multiples couches ayant différentes concentrations 20 de dopant. Dans certains modes de réalisation, la couche de nitre de groupe IIIA peut tout d'abord être dopée avec un dopant N-, tel que Si, à un niveau de dopant d'environ 1x10<sup>15</sup> atomes dopants/cm<sup>3</sup> à environ 3x10<sup>17</sup> atomes dopants/cm<sup>3</sup>, tel que d'environ 1x10<sup>16</sup> atomes dopants/cm<sup>3</sup> à environ 3x10<sup>16</sup> atomes dopants/cm<sup>3</sup>, ce qui est suivi par la formation d'une couche N+ par augmentation du niveau de dopant d'environ 1x10<sup>18</sup> atomes dopants/cm<sup>3</sup> à environ 5x10<sup>20</sup> atomes dopants/cm<sup>3</sup>, tel que d'environ 1x10<sup>19</sup> atomes dopants/cm<sup>3</sup> à environ 3x10<sup>20</sup> atomes dopants/cm<sup>3</sup>.

[0066] Des structures multicouches 230 comprenant le substrat porteur 220, la 25 couche de liaison interfaciale 210, et la couche épaisse de nitre de groupe IIIA 208, comme illustrées sur la figure 5D, sont adaptées à la fabrication de dispositifs d'alimentation HEMT avec une application cible de 800-1000V. Les structures sont également adaptées aux dispositifs HEMT RF, aux DEL, aux diodes laser et aux dispositifs d'alimentation haute tension verticaux de nitre de gallium sur nitre de gallium, entre autres utilisations.

30 [0067] Dans certains modes de réalisation, les structures multicouche 230 comprenant un substrat porteur 220, la couche de liaison interfaciale 210 et la couche épaisse de nitre de groupe IIIA 208, telles qu'illustrées sur la figure 5D, peuvent également être