(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5851089号

(P5851089)

(45) 発行日 平成28年2月3日(2016.2.3)

(24) 登録日 平成27年12月11日(2015.12.11)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| HO1L 21/28   | (2006.01) |

| HO1L 21/3213 | (2006.01) |

| HO1L 21/768  | (2006.01) |

| HO1L 21/336  | (2006.01) |

| HO1L 29/78   | (2006.01) |

|      |         |      |

|------|---------|------|

| HO1L | 21/28   | E    |

| HO1L | 21/3213 | 301R |

| HO1L | 21/768  | D    |

| HO1L | 21/336  | 301G |

| HO1L | 29/78   | 321D |

請求項の数 8 (全 18 頁) 最終頁に続く

(21) 出願番号

特願2010-223671 (P2010-223671)

(22) 出願日

平成22年10月1日 (2010.10.1)

(65) 公開番号

特開2011-86933 (P2011-86933A)

(43) 公開日

平成23年4月28日 (2011.4.28)

審査請求日

平成25年9月27日 (2013.9.27)

(31) 優先権主張番号

10-2009-0099364

(32) 優先日

平成21年10月19日 (2009.10.19)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者

390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeon

gton-gu, Suwon-si, G

yeonggi-do, Republic

of Korea

(74) 代理人

100093779

弁理士 服部 雅紀

(72) 発明者

張鍾光

大韓民国仁川広域市富平区富平1洞東亞1

団地エーピーティー. 7棟904号

最終頁に続く

(54) 【発明の名称】半導体素子の形成方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板上に高誘電膜を形成する段階と、

前記高誘電膜上に金属含有膜を形成する段階と、

前記金属含有膜上に多結晶半導体を含む半導体膜を形成する段階と、

前記半導体膜を異方性エッティングする段階と、

前記半導体膜及び前記半導体膜に隣接した領域に反応性窒素及び／または酸素含有ガスを提供し、エッティングされた前記半導体膜の少なくとも側壁上に前記半導体基板に対して傾く保護膜を形成する段階と、

前記金属含有膜及び前記高誘電膜を異方性エッティングする段階と、

を含み、

前記保護膜は、前記半導体基板に近い部位の幅が前記半導体基板に遠い部位の幅より広くなるよう形成され、

異方性エッティングによって前記半導体膜から離脱した前記多結晶半導体は、前記反応性窒素及び／または前記酸素含有ガスによって窒化及び／または酸化されて保護膜形成粒子を形成し、

前記保護膜形成粒子は、エッティングされた前記半導体膜の側壁に付着して前記保護膜を形成することを特徴とする半導体素子の形成方法。

## 【請求項 2】

前記保護膜形成粒子は前記半導体膜と異なるエッティング選択比を有することを特徴とす

10

20

る請求項1に記載の半導体素子の形成方法。

**【請求項3】**

前記金属含有膜は前記保護膜及びエッティングされた前記半導体膜をエッティングマスクとして使ってエッティングされることを特徴とする請求項1に記載の半導体素子の形成方法。

**【請求項4】**

前記半導体基板は互いに異なる導電型のドーパントを含む第1領域及び第2領域を含み、前記高誘電膜、前記金属含有膜及び前記半導体膜は前記第1領域及び前記第2領域の前記半導体基板上に形成され、

前記第2領域の前記高誘電膜及び前記金属含有膜の間にゲート導電膜を形成することをさらに含むことを特徴とする請求項1に記載の半導体素子の形成方法。 10

**【請求項5】**

前記半導体膜をエッティングすることは、前記半導体膜の上部をエッティングすること及び前記半導体膜の下部をエッティングすることを含み、

前記反応性窒素及び／または前記酸素含有ガスを提供することは前記半導体膜の上部をエッティングする段階と前記半導体膜の下部をエッティングする段階との間に実行されることを特徴とする請求項1に記載の半導体素子の形成方法。

**【請求項6】**

前記半導体膜のエッティングと前記反応性窒素及び／または前記酸素含有ガスの提供を交互に複数回繰り返すことを含むことを特徴とする請求項1に記載の半導体素子の形成方法。 20

**【請求項7】**

半導体基板上に順に高誘電パターン及び金属含有パターンを積層する段階と、

前記金属含有パターン上に多結晶半導体を含むゲートパターンを形成する段階と、

前記ゲートパターンの側壁上に前記多結晶半導体の酸化物、窒化物及び／または酸窒化物から形成され前記半導体基板に近い部位の幅が前記半導体基板に遠い部位の幅より広い保護膜を形成する段階と、

を含み、

前記多結晶半導体の酸化物、窒化物及び／または酸窒化物は、異方性エッティングによって前記ゲートパターンから離脱した前記多結晶半導体が反応性窒素及び／または酸素含有ガスによって窒化及び／または酸化されたのち前記ゲートパターンの側壁に付着して前記保護膜を形成する保護膜形成粒子であることを特徴とする半導体素子の形成方法。 30

**【請求項8】**

基板上に金属含有膜を形成する段階と、

前記金属含有膜上に多結晶半導体を含む半導体膜を形成する段階と、

前記半導体膜を異方性エッティングして前記多結晶半導体が前記半導体膜から離脱される段階と、

前記半導体膜を異方性にエッティングする間に、反応性窒素及び／または酸素含有ガスを異方性エッティングされた前記半導体膜に提供する段階と、

前記金属含有膜を異方性エッティングする段階と、

を含み、

前記反応性窒素及び／または前記酸素含有ガスは、前記半導体膜から離脱する前記多結晶半導体と反応して保護膜形成粒子を形成し、

前記保護膜形成粒子は、エッティングされた前記半導体膜の少なくとも側壁上に前記基板に対して傾く保護膜を形成することを特徴とする半導体素子の形成方法。 40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体素子の形成方法に関し、詳しくは、半導体膜と金属含有膜とを含む半導体素子の形成方法に関する。

**【背景技術】**

**【0002】**

半導体素子の高集積化の傾向に伴い、前記半導体素子を構成する構成要素の小型化が要求されている。しかし、装備などの制約によって、このような構成要素をより小さく形成するのは容易ではない。例えば、狭い線幅を有するパターンを形成するためのパターニング工程においての狭い線幅を有するパターンの場合、小さいエッティング損傷にも素子の特性が維持されない虞がある。

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】特開2008-219006号公報

10

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

本発明の課題は、エッティング損傷が最小化された半導体素子の形成方法を提供することにある。

本発明の他の課題は、信頼性が向上した半導体素子の形成方法を提供することにある。

**【課題を解決するための手段】****【0005】**

上述の課題を解決するための半導体素子の形成方法及びこれらによって形成された半導体素子が提供される。

20

本発明の半導体素子の形成方法は、半導体基板上に高誘電膜を形成する段階と、前記高誘電膜上に金属含有膜を形成する段階と、前記金属含有膜上に多結晶半導体を含む半導体膜を形成する段階と、前記半導体膜を異方性エッティングする段階と、前記半導体膜及び前記半導体膜に隣接した領域に反応性窒素及び／または酸素含有ガスを提供し、エッティングされた前記半導体膜の少なくとも側壁上に前記半導体基板に対して傾く保護膜を形成する段階と、前記金属含有膜及び前記高誘電膜を異方性エッティングする段階とを含み、前記保護膜は、前記半導体基板に近い部位の幅が前記半導体基板に遠い部位の幅より広いことを特徴とする。

**【0006】**

一態様において、前記多結晶半導体の一部は前記異方性エッティングによって前記半導体膜から離脱することができる。離脱した前記多結晶半導体は前記反応性窒素及び／または前記酸素含有ガスによって窒化及び／または酸化されて保護膜形成粒子を形成することができる。

30

**【0007】**

一態様において、前記保護膜形成粒子がエッティングされた前記半導体膜の側壁に付着して保護膜を形成することができる。前記保護膜形成粒子は前記半導体膜と異なるエッティング選択比を有することができる。

一態様において、前記金属含有膜は前記保護膜及びエッティングされた前記半導体膜をエッティングマスクとして使ってエッティングされ得る。

**【0008】**

40

一態様において、前記半導体基板は互いに異なる導電型のドーパントを含む第1領域及び第2領域を含み、前記高誘電膜、前記金属含有膜及び前記半導体膜は前記第1領域及び前記第2領域の前記半導体基板上に形成される。前記第2領域の前記高誘電膜及び前記金属含有膜の間にゲート導電膜が形成される。

一態様において、前記ゲート導電膜は複数の導電性金属化合物層を含むことができる。複数の前記導電性金属化合物層の間に他の高誘電膜がさらに形成され得る。

**【0009】**

一態様において、前記半導体膜をエッティングすることは、前記半導体膜の上部をエッティングすること及び前記半導体膜の下部をエッティングすることを含むことができる。前記反応性窒素及び／または前記酸素含有ガスを提供することは前記半導体膜の上部をエッキン

50

グする段階と、前記下部半導体膜の下部をエッティングする段階との間に実行される。

一態様において、前記半導体膜のエッティングと前記反応性窒素及び／または前記酸素含有ガスの提供は交互に複数回繰り返して実行することができる。

#### 【0010】

一態様において、前記反応性窒素及び／または前記酸素含有ガスを提供することによって、前記金属含有膜のエッティング副産物が窒化及び／または酸化される。

#### 【0011】

本発明の半導体素子の形成方法は、半導体基板上に順に高誘電パターン及び金属含有パターンを積層する段階、前記金属含有パターン上の多結晶半導体を含むゲートパターンを形成する段階、及び、ゲートパターンの側壁上に多結晶半導体の酸化物、窒化物及び／または酸窒化物から形成され半導体基板に近い部位の幅が半導体基板に遠い部位の幅より広い保護膜を形成する段階を含むことができる。多結晶半導体の酸化物、窒化物及び／または酸窒化物は、異方性エッティングによってゲートパターンから離脱した多結晶半導体が反応性窒素及び／または酸素含有ガスによって窒化及び／または酸化されたのちゲートパターンの側壁に付着して保護膜を形成する保護膜形成粒子である。10

#### 【0012】

本発明の半導体素子の形成方法は、基板上に金属含有膜を形成する段階と、前記金属含有膜上に多結晶半導体を含む半導体膜を形成する段階と、前記半導体膜を異方性エッティングして前記多結晶半導体が前記半導体膜から離脱される段階と、前記半導体膜を異方性にエッティングする間に、反応性窒素及び／または酸素含有ガスを前記エッティングされた半導体膜に提供する段階と、前記金属含有膜を異方性エッティングする段階と、を含み、前記反応性窒素及び／または酸素含有ガスは、多結晶半導体と反応して保護膜形成粒子を形成することを特徴とする。20

#### 【0013】

一態様において、前記保護膜は互いに異なる厚さの上部及び下部を有することができる。

一態様において、前記半導体基板は第1領域及び第2領域を含み、前記高誘電パターン、金属含有パターン及びゲートパターンは前記第1領域及び第2領域の前記半導体基板上に配置される。前記半導体素子は前記第2領域の前記高誘電パターン及び前記金属含有パターンの間に選択的に介在されたゲート導電パターンをさらに含むことができる。30

#### 【0014】

一態様において、前記半導体基板の第1領域は第1導電型のドーパントがドーピングされた第1ウェル領域を含み、前記半導体基板の第2領域は第2導電型のドーパントがドーピングされた第2ウェル領域を含むことができる。

一態様において、前記保護膜は前記金属含有膜のエッティング副産物の窒化物、酸化物及び／または酸窒化物をさらに含むことができる。

#### 【0015】

一態様において、前記ゲートパターンの側壁は前記ゲートパターンの底と鋭角をなすことができる。

一態様において、前記ゲートパターンの側壁は前記半導体基板に対して実質的に垂直である。40

#### 【0016】

##### (発明の効果)

本発明によれば、半導体膜の異方性エッティングの途中または以後に反応性窒素及び／または酸素含有ガスが提供される。前記反応性窒素及び／または酸素含有ガスの提供によってエッティングされる半導体膜の側壁の所望しない損傷を防止することができる。これによって、エッティング損傷が最小化された半導体素子を形成することができる。また、前記エッティング損傷が最小化された半導体素子は高い信頼性を有することができる。

#### 【図面の簡単な説明】

#### 【0017】

10

20

30

40

50

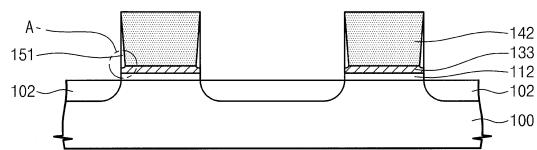

【図1A】本発明の第1実施形態による半導体素子を示す模式図である。

【図1B】図1Aに示したA領域の拡大図である。

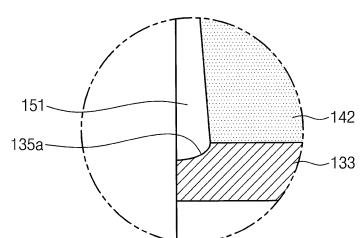

【図2A】本発明の第2実施形態の変形例による半導体素子を示す模式図である。

【図2B】図2Aに示したB領域の拡大図である。

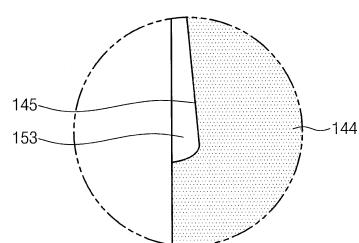

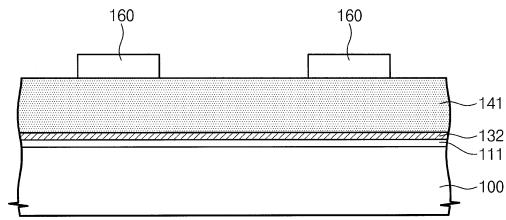

【図3A】本発明の第3実施形態による半導体素子の形成方法を説明するための断面図である。

【図3B】本発明の第3実施形態による半導体素子の形成方法を説明するための断面図である。

【図3C】本発明の第3実施形態による半導体素子の形成方法を説明するための断面図である。 10

【図4A】本発明の第4実施形態による半導体素子を示す模式図である。

【図4B】図4Aに示したA領域の拡大図である。

【図5A】本発明の第5実施形態の変形例による半導体素子を示す模式図である。

【図5B】図5Aに示したB領域の拡大図である。

【図6A】本発明の第6実施形態による半導体素子の形成方法を説明するための断面図である。

【図6B】本発明の第6実施形態による半導体素子の形成方法を説明するための断面図である。

【図6C】本発明の第6実施形態による半導体素子の形成方法を説明するための断面図である。 20

【図6D】本発明の第6実施形態による半導体素子の形成方法を説明するための断面図である。

【図7】本発明の実施形態による半導体素子の形成方法を説明するためのフローチャートである。

#### 【発明を実施するための形態】

##### 【0018】

以下、添付の図を参照して、本発明の実施形態による半導体素子及びその形成方法を説明する。説明される実施形態は本発明の思想を当業者が容易に理解するように提供されるものであり、これによって本発明が限定されない。本発明の実施形態は本発明の技術的思想及び範囲内で他の形態に変形可能である。本明細書において、「及び／または」は前後に並べた構成要素のうちの少なくとも1つを含む意味として使われた。本明細書において、一構成要素が異なる構成要素‘上に’位置するとは、一構成要素上に異なる構成要素が直接位置し、前記一構成要素上に第3の構成要素がさらに位置することができるという意味も含む。本明細書の各構成要素または部分などを第1、第2などの表現を使って指称したが、これは明確な説明のために使われた表現であり、これによって限定されない。図面に表現された構成要素の厚さ及び相対的な厚さは本発明の実施形態を明確に表現するためには誇張されている。また、本明細書の上部及び下部などの位置に係わる表現は説明を明らかにするための相対的な表現として、絶対的な構成要素間の位置を限定するものではない。同一の構成要素には同一の図面符号を使った。 30

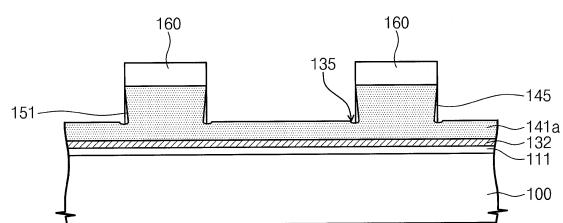

##### 【0019】

###### (第1実施形態)

図1A及び図1Bを参照して、本発明の第1実施形態による半導体素子を説明する。図1Bは、図1Aに示したA領域を拡大した図である。半導体基板100が提供される。半導体基板100は第1導電型のドーパントがドーピングされたウェル領域(図示しない)を含むことができる。半導体基板100内にソース／ドレイン領域102が配置されている。ソース／ドレイン領域102は前記第1導電型と反対の導電型である第2導電型のドーパントがドーピングされた領域であり得る。

##### 【0020】

ソース／ドレイン領域102の間の半導体基板100上にゲート絶縁パターン112、金属含有パターン133及びゲートパターン142が順に積層される。 50

ゲート絶縁パターン112は酸化シリコン(SiO<sub>2</sub>)に比較して高い誘電率を有する絶縁物質を含むことができる。すなわち、ゲート絶縁パターン112は高誘電膜であり得る。ゲート絶縁パターン112は、Hf、Zr、Al、Ti、La、Y、Gd及びTaのうちの少なくとも1つの金属を含む金属酸化物、金属シリコン酸化物または金属シリコン酸窒化物を含むことができる。例えば、ゲート絶縁パターン112はHfSiONを含むことができる。

#### 【0021】

金属含有パターン133はゲート絶縁パターン112上に配置され、ゲート絶縁パターン112の一部側壁と球面をなす側壁を有することができる。金属含有パターン133の上部面の端135Aは陥没され得る。すなわち、金属含有パターン133の端135Aの高さは金属含有パターン133の中心部の高さより低いことがある。

10

#### 【0022】

金属含有パターン133は導電性金属化合物を含むことができる。例えば、金属含有パターン133は導電性金属窒化物を含むことができる。金属含有パターン133はTi、Ta、W、Mo、Al、Hf及びZrのうちで選択された少なくとも1つの金属の窒化物を含むことができる。

#### 【0023】

ゲートパターン142はドーパントがドーピングされた半導体を含むことができる。ゲートパターン142はn型またはp型のドーパントがドーピングされた多結晶半導体を含むことができる。例えば、ゲートパターン142は多結晶シリコンを含むことができる。ゲートパターン142の最上部の幅と最下部の幅は異なることができる。例えば、ゲートパターン142の最上部の幅はゲートパターン142の最下部の幅より広いことがある。これによって、ゲートパターン142の側壁とゲートパターン142の底面は鈍角を成すことができる。

20

#### 【0024】

ゲートパターン142の側壁上に保護膜151が配置される。保護膜151は金属含有パターン133の端135A部分上に配置される。示したことと異なり、金属含有パターン133は陥没しない端を有し、前記陥没しない端上に保護膜151が配置されることもある。保護膜151はゲートパターン142の側壁上に不規則に付着した複数の保護膜形成粒子を含むことができる。前記保護膜形成粒子は互いに異なる大きさを有することができる。本実施形態において、保護膜151の下部分を構成する前記保護膜形成粒子の数は保護膜151の上部を構成する保護膜形成粒子の数より多いことがある。これによって、保護膜151は相対的に厚い下部分と相対的に薄い上部を含むことができる。前記保護膜形成粒子はゲートパターン142の側壁上に不規則に配列され得る。

30

#### 【0025】

保護膜151の厚さは不均一であり得る。例えば、保護膜151の下部分の前記保護膜形成粒子の数は保護膜151の上部の粒子の数より多いことがある。これによって、保護膜151は相対的に厚い下部分と相対的に薄い上部を含むことができる。これと異なり、保護膜151の厚さは前記保護膜形成粒子の配列によって多様に変化することができる。

40

#### 【0026】

保護膜151に含まれた保護膜形成粒子はゲートパターン142に含まれた物質の酸化物、窒化物及び/または酸窒化物を含むことができる。例えば、前記保護膜形成粒子は多結晶半導体の酸化物、多結晶半導体の窒化物及び/または多結晶半導体の酸窒化物を含むことができる。本実施形態において、前記保護膜形成粒子は表面が酸化及び/または窒化された半導体粒子を含むことができる。保護膜151によってゲートパターン142の側壁は保護される。

#### 【0027】

これに加えて、保護膜151は金属含有パターン133に含まれた物質の酸化物、窒化物及び/または酸窒化物をさらに含むことができる。例えば、保護膜151はTi、Ta、W、Mo、Al、Hf及びZrのうちで選択された少なくとも1つの酸化物、窒化物及

50

び／または酸窒化物をさらに含むことができる。

**【0028】**

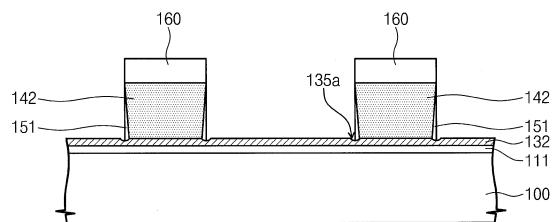

(第2実施形態)

図2A及び図2Bを参照して、本発明の第2実施形態を説明する。図2Bは、図2Aに示したB領域を拡大した図である。図1Aを参照して説明した構成要素に対する説明は省略する。

**【0029】**

ゲート絶縁パターン112上に金属含有パターン134が配置される。金属含有パターン134はゲート絶縁パターン112の側壁と球面を成す側壁を有する。金属含有パターン134は導電性金属化合物を含むことができる。例えば、金属含有パターン134はTi、Ta、W、Mo、Al、Hf及びZrのうちで選択された少なくとも1つの酸化物、窒化物及び／または酸窒化物をさらに含むことができる。

**【0030】**

金属含有パターン134上にゲートパターン144が配置される。ゲートパターン144は陥没した側壁145を有することができる。陥没した側壁145を含むゲートパターン144の側壁上に保護膜153が配置される。保護膜153はゲートパターン144の陥没した側壁145上に不規則に付着した複数の保護膜形成粒子を含むことができる。本実施形態において、前記保護膜形成粒子は互いに異なる大きさを有することができる。前記保護膜形成粒子はゲートパターン144の側壁上に不均一に配列され得る。

**【0031】**

保護膜153の厚さは不均一であり得る。例えば、保護膜153の下部分の前記保護膜形成粒子の数は保護膜153の上部の粒子の数より多いことがある。これによって、保護膜153は相対的に厚い下部分と相対的に薄い上部を含むことができる。これと異なり、保護膜153の厚さは前記保護膜形成粒子の配列によって多様に変化することができる。

**【0032】**

保護膜153に含まれた保護膜形成粒子はゲートパターン144に含まれた物質の酸化物、窒化物及び／または酸窒化物を含むことができる。例えば、前記保護膜形成粒子は多結晶半導体の酸化物、多結晶半導体の窒化物及び／または多結晶半導体の酸窒化物を含むことができる。本実施形態において、前記保護膜形成粒子は酸化及び／または窒化された半導体粒子を含むことができる。

**【0033】**

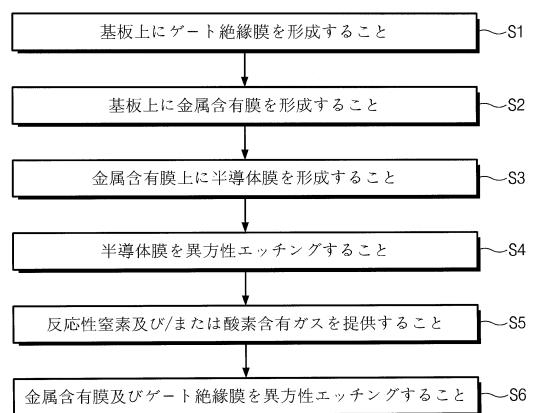

(第3実施形態)

図1A、図1B、図3A～図3C及び図7を参照して、本発明の第3実施形態による半導体素子の形成方法を説明する。図1A及び図1Bを参照して説明した内容は省略することができる。

**【0034】**

図3A及び図7を参照すれば、半導体基板100上にゲート絶縁膜111が形成される(S1)。ゲート絶縁膜111を形成する前に、半導体基板100内にドーパントをドーピングしてウェル領域を形成することができる。ゲート絶縁膜111は高誘電率を有する絶縁物質を含むことができる。例えば、ゲート絶縁膜111はHf、Zr、Al、Ti、La、Y、Gd及びTaのうちで選択された少なくとも1つの金属を含む金属酸化物、金属シリコン酸化物または金属シリコン酸窒化物を含むことができる。例えば、ゲート絶縁膜111はHfSiONを含むことができる。

**【0035】**

ゲート絶縁膜111上に金属含有膜132が形成される(S2)。金属含有膜132は導電性金属化合物を含むことができる。金属含有膜132はゲート絶縁膜111と異なるエッティング選択比を有する物質を含むことができる。金属含有膜132はTi、Ta、W、Mo、Al、Hf及びZrのうちで選択された少なくとも1つの窒化物であり得る。例えば、金属含有膜132は窒化チタン(TiN)を含むことができる。

**【0036】**

10

20

30

40

50

金属含有膜 132 上に半導体膜 141 が形成される (S3)。半導体膜 141 は多結晶シリコンを含むことができる。半導体膜 141 は化学気相蒸着法及び原子層蒸着法を含む多様な蒸着方法のうちで選択された少なくとも 1 つの方法により形成することができる。例えば、半導体膜 141 は低圧化学気相蒸着 (LPCVD) 法によって形成することができる。

半導体膜 141 上にマスクパターン 160 が形成される。マスクパターン 160 は半導体膜 141 の一部を覆うことができる。

#### 【0037】

図 3B、図 3C 及び図 7 を参照すれば、マスクパターン 160 をエッチングマスクとして使って半導体膜 141 がエッチングされる (S4)。図 3B は、一部がエッチングされた半導体膜 141A を示す工程断面図であり、図 3C は、半導体膜 141 が十分にエッチングされてゲートパターン 142 が形成された時の工程断面図である。半導体膜 141 のエッチングは半導体膜 141 に対して高いエッチング選択比を有するエッチング剤 (etchant) を使って実行することができる。

#### 【0038】

半導体膜 141 はハロゲン元素を含むエッチングガス、例えば、HBr ガスを利用してエッチングすることができる。具体的に、半導体膜 141 をエッチングすることは、数十乃至数千 (W) のソースパワー (source power) 及びバックバイアスパワー (back-bias power) で、数乃至数百 sccm の HBr ガスを提供することを含むことができる。本実施形態において、半導体膜 141 をエッチングすることは酸素 (O<sub>2</sub>) 及びヘリウム (He) ガスのうちで選択された少なくとも 1 つを提供することをさらに含むことができる。

#### 【0039】

半導体膜 141 のエッチングの時、多結晶半導体の粒子がエッチング副産物として発生することができる。図 3B を参照すれば、一部がエッチングされた半導体膜 141A の上部内に微細トレーニチ 135 が形成される。これと異なり、半導体膜 141 に対するエッチングが十分に進行された以後には図 3C に示したように、金属含有膜 132 を構成する金属含有粒子がエッチング副産物として発生することができる。この場合、金属含有膜 132 の上部内に微細トレーニチ 135A が形成される。前記エッチング副産物は前記エッチング剤と一部がエッチングされた半導体膜 141A または前記エッチング剤と金属含有膜 132 が衝突する部分、例えば、微細トレーニチ 135、135A で形成されて、一部がエッチングされた半導体膜 141A または金属含有膜 132 から取れることができる。

#### 【0040】

半導体膜 141 のエッチングが実行されている反応チャンバ内に反応性窒素及び / または酸素含有ガスが提供される (S5)。前記反応性窒素及び / または酸素含有ガスは半導体膜 141 のエッチング工程実行の途中に提供することができる。例えば、半導体膜 141 の上部をエッチングして、前記反応性窒素及び / または酸素含有ガスが提供された後、半導体膜 141 の下部をエッチングすることができる。これと異なり、半導体膜 141 のエッチングと前記反応性窒素及び / または酸素含有ガスの提供が交互に実行されることもある。前記反応性窒素及び / または酸素含有ガスは半導体膜 141 を構成する物質、例えば多結晶シリコンを窒化及び / または酸化させることができるガスを含むことができる。前記反応性窒素及び / または酸素含有ガスは例えば、O<sub>2</sub>、O<sub>3</sub> 及び N<sub>2</sub>H<sub>2</sub> のうちで選択された少なくとも 1 つを含むことができる。

#### 【0041】

前記反応性窒素及び / または酸素含有ガスによって半導体膜 141 のエッチングの時発生したエッチング副産物が窒化及び / または酸化され得る。例えば、多結晶半導体粒子及び / または前記金属含有粒子の少なくとも一部が窒化及び / または酸化され得る。前記窒化及び / または酸化された粒子は一部がエッチングされた半導体膜 141A の側壁に付着することができる。一部がエッチングされた半導体膜 141A に付着した前記窒化及び / または酸化された粒子は一部がエッチングされた半導体膜 141A の側壁を保護する保護

10

20

30

40

50

膜形成粒子であり得る。一部がエッティングされた半導体膜 141A の側壁に付着した前記保護膜形成粒子は保護膜 151 を構成することができる。

#### 【0042】

本実施形態において、前記エッティング副産物は前記エッティング剤と一部がエッティングされた半導体膜 141A が接する領域で形成され得る。例えば、前記エッティング副産物は微細トレンチ 135、135A で形成され得る。したがって、酸化及び／または窒化された前記エッティング副産物、すなわち、保護膜形成粒子の多数が微細トレンチ 135、135A に隣接したゲートパターン 142 の下部側壁に付着することができる。一方、ゲートパターン 142 の上部側壁には前記下部側壁に比較して少ない数の保護膜形成粒子が付着することができる。これによって、前記保護膜形成粒子を含む保護膜 151 は相対的に厚い下部及び相対的に薄い上部を含むことができる。これと異なり、前記反応性窒素及び／または酸素の注入時間及び／または注入時期によって保護膜 151 の厚さ及び相対的厚さは異なるように調節することができる。10

#### 【0043】

前記保護膜形成粒子は、半導体膜 141 のエッティングの時使われるエッティング剤に対して半導体膜 141 より低いエッティング率を有することができる。例えば、前記保護膜形成粒子が前記エッティング剤によってエッティングされる割合は多結晶半導体が前記エッティング剤によってエッティングされる割合より低いことがある。

#### 【0044】

異方性エッティングで、エッティング剤の一部がエッティング対象膜から衝突及び反射してエッティング対象膜を再びエッティングすることができる。例えば、一部がエッティングされた半導体膜 141A の上部面で反射したエッティング剤の一部がエッティングされた半導体膜 141A の側壁 145 と衝突することができる。これによって、一部がエッティングされた半導体膜 141A 及び半導体膜 141 のエッティングによって形成されるゲートパターン 142 の側壁 145 にネガティブプロファイルが発生することができる。20

#### 【0045】

しかし、本実施形態によって、一部がエッティングされた半導体膜 141A の側壁上にエッティングされた半導体膜 141A と異なるエッティング選択比を有する保護膜 151 が形成される場合、一部がエッティングされた半導体膜 141A の側壁の所望しないエッティングを防止することができる。すなわち、前記ネガティブプロファイルを最小化することができる。したがって、一部がエッティングされた半導体膜 141A をエッティングして形成されるゲートパターン 142 の特性が向上することができる。30

#### 【0046】

提供される前記反応性窒素及び／または酸素含有ガスの注入時間及び／または注入時期によって、保護膜 151 は多様な形態に形成可能である。例えば、図 1A に示したように、ゲートパターン 142 の側壁の全面上に保護膜 151 が形成される。これと異なり、図 2A に示したように、ゲートパターン 144 の一部側壁上に保護膜 153 が形成されることも可能である。

#### 【0047】

再び図 1A を参照すれば、マスクパターン 160、ゲートパターン 142 及び保護膜 151 をエッティングマスクとして使って、金属含有膜 132 及びゲート絶縁膜 111 がエッティングされる (S6)。ゲートパターン 142 が保護された側壁によって金属含有膜 133 及びゲート絶縁膜 111 のエッティングの時の欠陥を最小化することができる。具体的に、ゲートパターン 142 の側壁上に保護膜 151 が形成されない場合、ゲートパターン 142 の側壁、特にゲートパターン 142 の下部側壁でネガティブプロファイルが形成され得る。ネガティブプロファイルを有するゲートパターン 142 をエッティングマスクとしてエッティングされた金属含有膜 133 及びゲート絶縁膜 111 は前記ネガティブプロファイルを有するゲートパターン 142 の側壁に自己整列されるので、金属含有膜 133 の特性も劣化することができる。40

#### 【0048】

50

これと異なり、本実施形態によって、ゲートパターン142の側壁が保護される場合、ゲートパターン142の側壁が保護されると共に、ゲートパターン142をマスクとしてエッチングされる金属含有膜133及びゲート絶縁膜111の側壁も保護され得る。したがって、これによって形成される半導体素子の信頼性が向上することができる。

#### 【0049】

ゲートパターン142をイオン注入マスクとしてゲートパターン142に隣接した半導体基板100内にソース／ドレイン領域102が形成される。ソース／ドレイン領域102は前記第1導電型と反対の導電型を有する第2導電型のドーパントを半導体基板100内に注入することによって形成される。

#### 【0050】

10

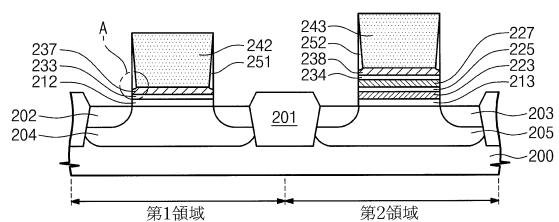

##### (第4実施形態)

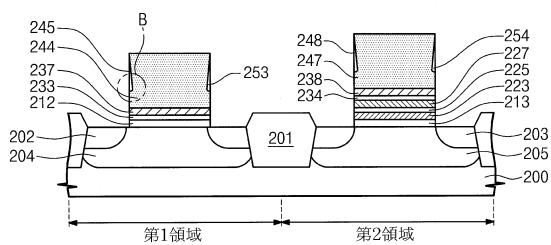

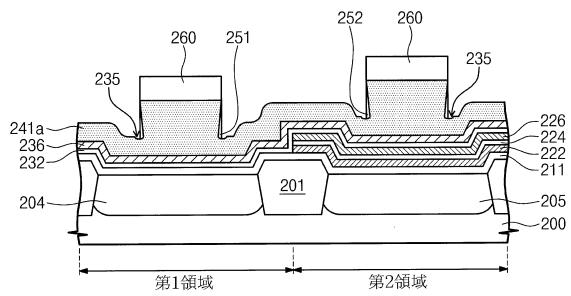

図4A及び図4Bを参照して本発明の第4実施形態による半導体素子を説明する。図4Bは、図4AのA領域を拡大した図である。第1領域及び第2領域を含む半導体基板200が提供される。前記第1領域及び前記第2領域は素子分離膜201によって分離する。前記第1領域の半導体基板200は第1導電型のドーパントがドーピングされた第1ウェル領域204を含み、前記第2領域の半導体基板200は第2導電型のドーパントがドーピングされた第2ウェル領域205を含むことができる。第1ウェル領域204内には第2導電型のドーパントがドーピングされた第1ソース／ドレイン領域202が配置され、第2ウェル領域205内には第1導電型のドーパントがドーピングされた第2ソース／ドレイン領域203が配置される。

20

#### 【0051】

第1ソース／ドレイン領域202の間の半導体基板200上に第1下部ゲート絶縁パターン212、第1上部ゲート絶縁パターン233、第1金属含有パターン237及び第1ゲートパターン242が順に積層される。

第1下部ゲート絶縁パターン212及び第1上部ゲート絶縁パターン233は高誘電物質を含むことができる。第1下部ゲート絶縁パターン212はHf、Zr、Al、Ti、La、Y、Gd及びTaのうちの少なくとも1つの金属を含む金属酸化物、金属シリコン酸化物または金属シリコン酸窒化物を含むことができる。例えば、ゲート絶縁パターン212はHfSiONを含むことができる。第1上部ゲート絶縁パターン233はランタン族金属の酸化物を含むことができる。示したことと異なり、第1下部ゲート絶縁パターン212及び第1上部ゲート絶縁パターン233のうちのいずれか1つは省略可能である。

30

#### 【0052】

第1金属含有パターン237は導電性金属化合物を含むことができる。例えば、第1金属含有パターン237はTi、Ta、W、Mo、Al、Hf及びZrのうちで選択された少なくとも1つの窒化物であり得る。例えば、第1金属含有パターン237は窒化チタン(TiN)を含むことができる。本実施形態において、第1金属含有パターン237は陥没した端235Aを有することができる。

#### 【0053】

第1ゲートパターン242は半導体基板200の平面に対して傾いた側壁を有することができる。例えば、第1ゲートパターン242は互いに異なる幅を有する上部と下部とを含み、前記下部の幅が前記上部の幅より狭いことがある。第1ゲートパターン242は多結晶半導体を含むことができる。例えば、第1ゲートパターン242は多結晶シリコンを含むことができる。

40

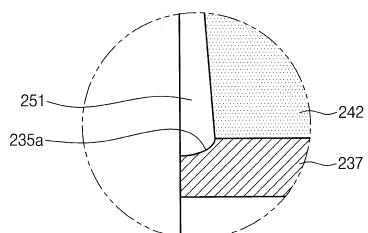

#### 【0054】

第1ゲートパターン242の側壁上に第1保護膜251が配置される。本実施形態において、第1保護膜251は第1金属含有パターン237の陥没した端235Aまで延長することができる。第1保護膜251は保護膜形成粒子を含むことができる。前記保護膜形成粒子は多結晶半導体粒子の酸化物、窒化物及び／または酸窒化物を含むことができる。本実施形態において、前記保護膜形成粒子は第1金属含有パターン237を構成する物質の酸化物、窒化物及び／または酸窒化物をさらに含むことができる。第1ゲートパターン

50

242の下部側壁に付着した前記保護膜形成粒子の数が第1ゲートパターン242の上部側壁に付着した前記保護膜形成粒子の数より多いことがある。これによって、第1保護膜251の下部は第1保護膜251の上部より厚いことがある。

#### 【0055】

第2ソース／ドレイン領域204の間の半導体基板200上に第2下部ゲート絶縁パターン213、下部ゲート導電パターン223、薄膜パターン225、上部ゲート導電パターン227、第2上部ゲート絶縁パターン234、第2金属含有パターン238及び第2ゲートパターン243が順に積層される。本実施形態において、薄膜パターン225が省略され、下部ゲート導電パターン223と上部ゲート導電パターン227が直接接することができる。10

#### 【0056】

第2下部ゲート絶縁パターン213は高誘電物質を含むことができる。第2下部ゲート絶縁パターン213はHf、Zr、Al、Ti、La、Y、Gd及びTaのうちの少なくとも1つの金属を含む金属酸化物、金属シリコン酸化物または金属シリコン酸窒化物を含むことができる。例えば、第2下部ゲート絶縁パターン213はHfSiONを含むことができる。

#### 【0057】

下部ゲート導電パターン223及び上部ゲート導電パターン227は導電性金属化合物を含むことができる。例えば、下部ゲート導電パターン223及び上部ゲート導電パターン227はTi、Ta、W、Mo、Al、Hf及びZrのうちで選択された少なくとも1つの窒化物であり得る。本実施形態において、下部及び上部ゲート導電パターン223、227は非金属不純物をさらに含むことができる。下部ゲート導電パターン223と上部ゲート導電パターン227は互いに異なる特性を有することができる。例えば、下部ゲート導電パターン223と上部ゲート導電パターン227は互いに異なる厚さを有することができる。また、下部ゲート導電パターン223と上部ゲート導電パターン227は互いに異なる含量比の元素を含むことができる。20

#### 【0058】

下部ゲート導電パターン223及び上部ゲート導電パターン227によって、下部及び上部ゲート導電パターン223、227及び第2ゲートパターン243を含むゲート構造物の仕事関数が制御され得る。例えば、前記第1領域の第1ゲートパターン242と前記第2領域の第2ゲートパターン243は同一の物質で形成され、第2ゲートパターン243と半導体基板200との間に選択的にゲート導電パターン223、227が挿入され得る。これによって、前記第2領域の前記ゲート構造物の仕事関数が選択的に制御され得る。したがって、第1領域のトランジスタと第2領域のトランジスタは互いに異なるスレッショルド電圧値を有することができる。30

#### 【0059】

下部ゲート導電パターン223と上部ゲート導電パターン227との間に薄膜パターン225が介在される。薄膜パターン225は例えば、ランタン族元素の酸化物を含むことができる。薄膜パターン225は下部ゲート導電パターン223及び上部ゲート導電パターン227に比較して薄い厚さを有することができる。例えば、下部ゲート導電パターン223及び上部ゲート導電パターン227は数十の厚さを有し、薄膜パターン225は数の厚さを有することができる。示したところと異なり、薄膜パターン225は省略可能である。40

#### 【0060】

第2上部ゲート絶縁パターン234は高誘電物質を含むことができる。第2上部ゲート絶縁パターン234はランタン族金属の酸化物を含むことができる。

#### 【0061】

第2金属含有パターン238は導電性金属化合物を含むことができる。例えば、第2金属含有パターン238はTi、Ta、W、Mo、Al、Hf及びZrのうちで選択された少なくとも1つの窒化物であり得る。例えば、第2金属含有パターン238は窒化チタン50

(TiN)を含むことができる。第2金属含有パターン238は第1金属含有パターン237と実質的に同一の物質を含むことができる。本実施形態において、第2金属含有パターン238は陥没した端235Aを有することができる。

#### 【0062】

第2ゲートパターン243は半導体基板200の平面に対して傾いた側壁を有することができる。例えば、第2ゲートパターン243は互いに異なる幅を有する上部と下部とを含み、前記下部の幅が前記上部の幅より狭いことがある。本実施形態において、第2ゲートパターン243の最上部と最下部の幅の差は第1ゲートパターン242の最上部と最下部の幅の差より小さいことがある。すなわち、2ゲートパターン243の側壁は第1ゲートパターン243の側壁より半導体基板200の平面に対してより小さく傾くことができる。10

#### 【0063】

第2ゲートパターン243の側壁上に第2保護膜252が配置される。本実施形態において、第2保護膜252は第2金属含有パターン238の陥没した端235Aまで延長することができる。第2保護膜252は保護膜形成粒子を含むことができる。例えば、前記保護膜形成粒子は多結晶半導体粒子の酸化物、窒化物及び／または酸窒化物を含むことができる。本実施形態において、前記保護膜形成粒子は第2金属含有パターン238を構成する物質の酸化物、窒化物及び／または酸窒化物をさらに含むことができる。

#### 【0064】

第2ゲートパターン243の下部側壁に付着した前記保護膜形成粒子の数が第2ゲートパターン243の上部側壁に付着した前記保護膜形成粒子の数より多いことがある。これによって、第2保護膜252の下部は第2保護膜252の上部より厚いことがある。本実施形態において、第2保護膜252と第1保護膜251の厚さは互いに異なることができる。例えば、第2保護膜252の厚さが第1保護膜251の厚さより厚いことがある。20

#### 【0065】

##### (第5実施形態)

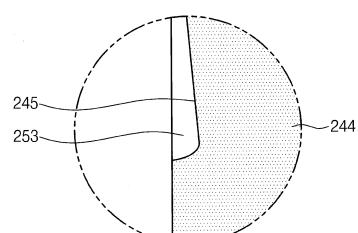

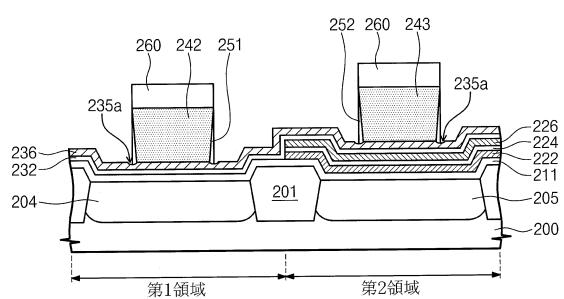

第1及び第2ゲートパターン242、243と第1及び第2保護膜251、252の形態は変形可能である。

本発明の第5実施形態を示す図5A及び図5Bを参照すれば、第1ゲートパターン244及び第2ゲートパターン247の側壁は第1及び第2陥没部245、248を含むことができる。第1及び第2陥没部245、248は前記側壁端の以外の部分、例えば、前記側壁の中間に配置され得る。第1及び第2陥没部245、248内に第1及び第2保護膜253、254が配置され得る。第1及び第2保護膜253、254は保護膜形成粒子を含むことができる。前記保護膜形成粒子は第1及び第2ゲートパターン244、247に含まれた物質のうちの少なくとも1つを含むことができる。第1及び第2保護膜253、254は上述の図4Aを参照して説明した第1及び第2保護膜251、252と実質的に同一の保護膜形成粒子を含むことができる。30

#### 【0066】

##### (第6実施形態)

図4A、図4B、図6A～図6C及び図7を参照して本発明の第6実施形態による半導体素子の形成方法を説明する。40

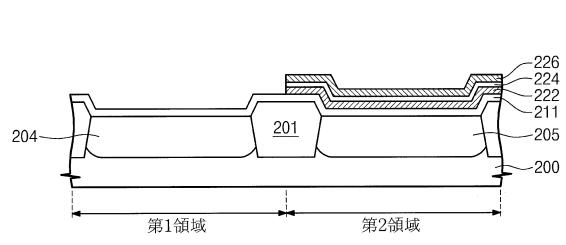

#### 【0067】

図6A及び図7を参照すれば、半導体基板200内に素子分離膜201が形成される。素子分離膜201は半導体基板200を第1領域及び第2領域に分離することができる。半導体基板200内に第1ウェル領域204及び第2ウェル領域205が形成される。第1ウェル領域204及び第2ウェル領域205は互いに異なる導電型のドーパントがドーピングされ得る。例えば、第1ウェル領域204はp型のドーパントがドーピングされ、第2ウェル領域205はn型のドーパントがドーピングされ得る。

#### 【0068】

半導体基板200上に下部ゲート絶縁膜211が形成される(S1)。下部ゲート絶縁

50

膜 2 1 1 は前記第 1 領域及び第 2 領域の半導体基板 2 0 0 の全面上に形成される。下部ゲート絶縁膜 2 1 1 は高誘電膜を有する絶縁物質を含む。例えば、下部ゲート絶縁膜 2 1 1 は HfSiON を含むことができる。下部ゲート絶縁膜 2 1 1 は原子層蒸着法及び化学気相蒸着法を含む多様な蒸着法のうちで選択された少なくとも 1 つによって形成され得る。

#### 【 0 0 6 9 】

前記第 2 領域の半導体基板 2 0 0 上に選択的に下部ゲート導電膜 2 2 2 、薄膜 2 2 4 及び上部ゲート導電膜 2 2 6 が形成される。下部ゲート導電膜 2 2 2 、薄膜 2 2 4 及び上部ゲート導電膜 2 2 6 は半導体基板 2 0 0 上に導電膜、高誘電膜及び導電膜を順に積層した後、前記第 1 領域の半導体基板 2 0 0 上の膜を選択的に除去して形成され得る。

#### 【 0 0 7 0 】

図 6 B に示すように、半導体基板 2 0 0 上に上部ゲート絶縁膜 2 3 2 が形成される。上部ゲート絶縁膜 2 3 2 は前記第 1 領域及び前記第 2 領域の半導体基板 2 0 0 及び下部ゲート絶縁膜 2 1 1 上に形成される。上部ゲート絶縁膜 2 3 2 は高誘電率を有する絶縁膜であり得る。例えば、上部ゲート絶縁膜 2 3 2 はランタン族金属のうちで選択された少なくとも 1 つの酸化物、窒化物及び / または酸窒化物を含むことができる。

#### 【 0 0 7 1 】

上部ゲート絶縁膜 2 3 2 上に金属含有膜 2 3 6 が形成される。金属含有膜 2 3 6 は前記第 1 領域及び前記第 2 領域の上部ゲート絶縁膜 2 3 2 上に形成される。金属含有膜 2 3 6 は導電性金属化合物を含むことができる。例えば、金属含有膜 2 3 6 は金属窒化物を含むことができる。

#### 【 0 0 7 2 】

金属含有膜 2 3 6 上に半導体膜 2 4 1 が形成される。半導体膜 2 4 1 は多結晶半導体を含むことができる。半導体膜 2 4 1 は上部及び下部ゲート導電膜 2 2 2 、 2 2 6 の厚さの数乃至数十倍の厚さを有することができる。

#### 【 0 0 7 3 】

半導体膜 2 4 1 上にマスクパターン 2 6 0 が形成される。マスクパターン 2 6 0 は第 1 ウェル領域 2 0 4 及び第 2 ウェル領域 2 0 5 の半導体膜 2 4 1 上に形成される。

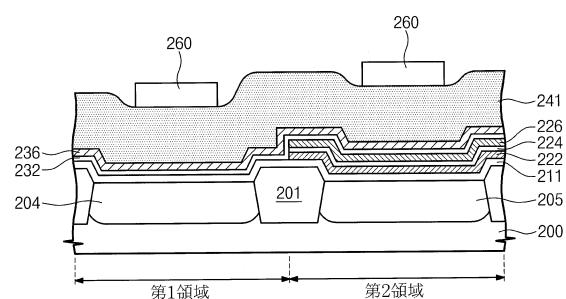

#### 【 0 0 7 4 】

図 6 C 及び図 6 D に示すように、マスクパターン 2 6 0 をエッティングマスクとして使って、半導体膜 2 4 1 が異方性エッティングされる (S 4) 。図 6 C は、一部がエッティングされた半導体膜 2 4 1 A を示し、図 6 D は、十分にエッティングされた半導体膜、すなわち、ゲートパターン 2 4 2 、 2 4 3 を示す。半導体膜 2 4 1 のエッティングはハロゲン系列のエッティング剤、例えば、 HBr を使って実行することができる。半導体膜 2 4 1 のエッティングによって半導体膜 2 4 1 を構成する物質、例えば、多結晶半導体の 粒子 が形成され得る。

#### 【 0 0 7 5 】

前記多結晶半導体 粒子 は前記一部がエッティングされた半導体膜 2 4 1 A が接する領域で形成され得る。例えば、前記多結晶半導体 粒子 は一部がエッティングされた半導体膜 2 4 1 A のエッティングされた側壁周辺の微細トレチ 2 3 5 より形成され得る。半導体膜 2 4 1 が図 6 D のように、十分にエッティングされてゲートパターン 2 4 2 、 2 4 3 が形成された場合、金属含有膜 2 3 6 の一部がエッティングされて金属含有膜 2 3 6 の上部に微細トレチ 2 3 5 A が形成されることもある。

#### 【 0 0 7 6 】

前記異方性エッティング工程の途中に反応性窒素及び / または酸素含有ガスを提供することができる。前記反応性窒素及び / または酸素含有ガスは半導体膜 2 4 1 のエッティングの時発生する多結晶半導体の 粒子 を窒化及び / または酸化させることができる。窒化及び / または酸化された前記 粒子 (以下、 保護膜形成粒子 ) は一部がエッティングされた半導体膜 2 4 1 A の表面に付着することができる。これによって、一部がエッティングされた半導体膜 2 4 1 A の側壁上に保護膜 2 5 1 、 2 5 2 が形成され得る。本実施形態において、図 6 D のように、半導体膜 2 4 1 が十分にエッティングされた場合、金属含有膜 2 3 6 に含まれ

10

20

30

40

50

た金属含有粒子がエッティング副産物として形成されて前記反応性窒素及び／または酸素含有ガスによって酸化及び／または窒化され得る。

#### 【0077】

提供される前記反応性窒素及び／または酸素含有ガスの注入時間及び／または注入時期によって、保護膜251、253は多様な形態を有することができる。例えば、図4Aに示したように、ゲートパターン242、243の側壁の全面上に保護膜251、253が形成され得る。これと異なり、図5Aに示したように、ゲートパターン244、247の一部側壁上に保護膜253、254が形成されることもある。また、保護膜251、253の厚さも前記反応性窒素及び／または酸素含有ガスの注入時間及び／または注入時期によって調節することができる。例えば、半導体膜241のエッティングが十分に行われた後、前記反応性窒素及び／または酸素含有ガスが注入される場合、保護膜251、253はゲートパターン242、243の側壁の下部上で相対的に厚い厚さを有し、ゲートパターン242、243の側壁の上部上で相対的に薄い厚さを有することができる。10

#### 【0078】

前記保護膜形成粒子は半導体膜241のエッティングの時使われるエッティング剤に対するエッティング率が半導体膜241に比較して低いことがある。これによって、前記保護膜形成粒子を含む保護膜253、254が付着した一部がエッティングされた半導体膜241A及びこれによって形成されるゲートパターン242、243の側壁の損傷は減少することができる。20

#### 【0079】

図4Aを参照すれば、マスクパターン260及びゲートパターン242、243をエッティングマスクとして使って、金属含有膜236及び上部ゲート絶縁膜232がエッティングされ得る。前記エッティングによって前記第1領域の半導体基板200上に第1上部ゲート絶縁パターン233及び第1金属含有パターン237が形成され、前記第2領域の半導体基板200上に第2上部ゲート絶縁パターン234及び第2金属含有パターン238が形成される。20

#### 【0080】

続いて、前記第2領域の上部ゲート導電膜226、薄膜224及び下部ゲート導電膜222が順にエッティングされ得る。第1及び第2ゲートパターン242、243の側壁上に第1及び第2保護膜251、252が形成されない場合、第2領域の上部ゲート導電膜226、薄膜224及び下部ゲート導電膜222のエッティングの時、第1領域の第1ゲートパターン242の特性は劣化することができる。具体的に、前記第2領域のゲート導電膜226、222がエッティングされる間前記第1領域にはエッティングされる膜が配置されないこともある。30

#### 【0081】

したがって、ゲート導電膜226、222のエッティングのために使われるエッティング剤の物理的及び／または化学的作用によって第1ゲートパターン242の側壁の損傷がより深化することができる。すなわち、第1ゲートパターン242側壁のネガティブプロファイルが深化することができる。しかし、本実施形態によって、第1ゲートパターン242の側壁上に第1保護膜251が形成される場合、前記第2領域の膜のエッティング工程の時、第1ゲートパターン242の側壁が損傷されることを防止することができる。したがって、第1ゲートパターン242は所望する垂直プロファイルを有することができる。40

#### 【0082】

図4A及び図4Bを参照すれば、ゲートパターン242、243に隣接した半導体基板200内に第1及び第2ソース／ドレイン領域202、203が形成され得る。第1及び第2ソース／ドレイン領域202、203はマスクパターン260及びゲートパターン242、243をイオン注入マスクとして使ったイオン注入工程を実行して形成され得る。マスク260は除去され得る。

#### 【符号の説明】

#### 【0083】

10

20

30

40

50

- 1 4 2 . . . ゲートパターン

- 1 3 3 . . . 金属含有パターン

- 1 1 2 . . . ゲート絶縁パターン

- 1 0 2 . . . ソース / ドレイン領域

- 1 0 0 . . . 半導体基板

- 1 5 1 . . . 保護膜

【図 1 A】

【図 2 A】

【図 1 B】

【図 2 B】

【図 3 A】

【図 3 B】

【図 3 C】

【図 4 A】

【図 4 B】

【図 5 A】

【図 5 B】

【図 6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 7】

## フロントページの続き

| (51)Int.Cl.              | F I                   |

|--------------------------|-----------------------|

| H 01 L 21/8238 (2006.01) | H 01 L 27/08 3 2 1 N  |

| H 01 L 27/092 (2006.01)  | H 01 L 21/302 1 0 5 A |

| H 01 L 21/3065 (2006.01) | H 01 L 21/88 Q        |

| H 01 L 21/3205 (2006.01) | H 01 L 29/58 G        |

| H 01 L 23/532 (2006.01)  |                       |

| H 01 L 29/423 (2006.01)  |                       |

| H 01 L 29/49 (2006.01)   |                       |

(72)発明者 文 永俊

大韓民国ソウル特別市松坡区梧琴洞大林エーピーティー . 5 棟 103 号

(72)発明者 金 徳 南

大韓民国ソウル特別市恩平区水色洞 25 - 1 番地

(72)発明者 鄭 榮鐘

大韓民国ソウル特別市永登浦区大林 2 洞 1075 - 95 番地

審査官 河合 俊英

(56)参考文献 特開平 05 - 175171 (JP, A)

特開 2007 - 235135 (JP, A)

米国特許出願公開第 2002 / 0151183 (US, A1)

特表 2008 - 514001 (JP, A)

特開 2009 - 094106 (JP, A)

米国特許出願公開第 2006 / 0148146 (US, A1)

(58)調査した分野(Int.Cl., DB名)

|        |           |

|--------|-----------|

| H 01 L | 21 / 28   |

| H 01 L | 21 / 3065 |

| H 01 L | 21 / 3205 |

| H 01 L | 21 / 3213 |

| H 01 L | 21 / 336  |

| H 01 L | 21 / 768  |

| H 01 L | 21 / 8238 |

| H 01 L | 23 / 532  |

| H 01 L | 27 / 092  |

| H 01 L | 29 / 423  |

| H 01 L | 29 / 49   |

| H 01 L | 29 / 78   |