(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4450016号

(P4450016)

(45) 発行日 平成22年4月14日(2010.4.14)

(24) 登録日 平成22年2月5日(2010.2.5)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/36

G09G 3/20 (2006.01)

G09G 3/20 621 F

G02F 1/133 (2006.01)

G09G 3/20 623 Y

G09G 3/20 623 R

G02F 1/133 570

請求項の数 3 (全 20 頁) 最終頁に続く

(21) 出願番号

特願2007-155274 (P2007-155274)

(22) 出願日

平成19年6月12日 (2007.6.12)

(65) 公開番号

特開2008-309873 (P2008-309873A)

(43) 公開日

平成20年12月25日 (2008.12.25)

審査請求日

平成21年3月27日 (2009.3.27)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100098785

弁理士 藤島 洋一郎

(74) 代理人 100109656

弁理士 三反崎 泰司

(72) 発明者 古越 靖武

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 中村 直行

最終頁に続く

(54) 【発明の名称】 液晶表示装置および液晶駆動回路

## (57) 【特許請求の範囲】

## 【請求項 1】

マトリクス状に配置され、それぞれが、TFT素子と、主容量素子としての液晶素子と、補助容量素子とを含む複数の画素と、

駆動対象の画素を線順次で選択し、選択した画素のTFT素子を所定のオン電圧により選択的にオン状態にすると共に、前記TFT素子を所定のオフ電圧により選択的にオフ状態にするための複数のゲート線と、

駆動対象の画素に対し、前記TFT素子を介して画像データを供給するための複数のソース線と、

各ゲート線の隣接ゲート線における前記オフ電圧を、前記画像データの輝度レベルに依存せずに一律に時間変化させつつ線順次動作を行うことにより、前記画素の表示駆動を行う駆動手段と

を備え、

前記液晶素子は、その一端が前記TFT素子の一端に接続され、

前記補助容量素子は、その一端が前記TFT素子の一端に接続されると共に、他端が前記隣接ゲート線に接続され、

前記駆動手段は、

現在の単位フレームの画像データとその直前の単位フレームの画像データとに基づいて、それらの画像データの輝度レベル差が所定の閾値未満の画素に対し、現在の単位フレームにおいて通常駆動による表示駆動を行うと判定する一方、前記輝度レベル差が前記閾値

以上の画素に対し、現在の単位フレームにおいてオーバードライブ駆動による表示駆動を行うと判定する判定手段と、

前記通常駆動による表示駆動を行うと判定された画素については、現在の単位フレームの画像データを、その輝度レベルが所定の分だけ下がるように補正する一方、前記オーバードライブ駆動による表示駆動を行うと判定された画素については、現在の単位フレームの画像データを、その直前の単位フレームと現在の単位フレームとの間での前記液晶素子の両端間電圧の変化が増加すると共に前記輝度レベル差が大きくなるのに応じて前記両端間電圧の変化がより大きくなるような画像データに補正する補正手段と、

前記補正手段による補正後の画像データを基に、前記表示駆動を画素ごと実施する駆動ドライバと

10

を有し、

前記補正手段は、

前記通常駆動による表示駆動を行うと判定された画素については、補正後の画像データに基づいて前記液晶素子の両端間に電圧を印加しこれが安定した後の状態における輝度レベルが、補正前の画像データに基づいて前記液晶素子の両端間に電圧を印加した直後における輝度レベルと同等となるように、現在の単位フレームの画像データを補正し、

前記オーバードライブ駆動による表示駆動を行うと判定された画素のうち、黒表示状態から白表示状態へ遷移する画素については、現在の単位フレームの画像データをそのまま補正後の画像データとして出力し、

前記オーバードライブ駆動による表示駆動を行うと判定された画素のうち、白表示状態から黒表示状態へ遷移する画素については、前記通常駆動による表示駆動の際の補正よりも輝度レベルが過剰に下がるように、現在の単位フレームの画像データを補正する

20

液晶表示装置。

### 【請求項 2】

前記ゲート線に沿った方向の各画素列ごとに 2 種類のゲート線が設けられると共に、これらの 2 種類のゲート線が、前記画素列における隣接する画素間で交互に各 TFT 素子のゲートに接続され、

前記駆動手段は、前記ゲート線に沿って隣接する画素同士および前記ソース線に沿って隣接する画素同士でそれぞれ互いに逆極性の電圧が前記液晶素子の両端間に印加されるように、前記表示駆動を行う

30

請求項 1 に記載の液晶表示装置。

### 【請求項 3】

マトリクス状に配置されそれが TFT 素子と主容量素子としての液晶素子と補助容量素子とを含む複数の画素と、駆動対象の画素を線順次で選択しこの選択した画素の TFT 素子を所定のオン電圧により選択的にオン状態にすると共に前記 TFT 素子を所定のオフ電圧により選択的にオフ状態にするための複数のゲート線と、駆動対象の画素に対し前記 TFT 素子を介して画像データを供給するための複数のソース線とを備え、前記液晶素子の一端が前記 TFT 素子の一端に接続され、前記補助容量素子の一端が前記 TFT 素子の一端に接続されると共に他端が隣接ゲート線に接続されるように構成された液晶表示装置に対して適用され、各ゲート線の隣接ゲート線における前記オフ電圧を前記画像データの輝度レベルに依存せずに一律に時間変化させつつ線順次動作を行うことにより前記画素の表示駆動を行う液晶駆動回路であって、

40

現在の単位フレームの画像データとその直前の単位フレームの画像データに基づいて、それらの画像データの輝度レベル差が所定の閾値未満の画素に対し、現在の単位フレームにおいて通常駆動による表示駆動を行うと判定する一方、前記輝度レベル差が前記閾値以上の画素に対し、現在の単位フレームにおいてオーバードライブ駆動による表示駆動を行うと判定する判定手段と、

前記通常駆動による表示駆動を行うと判定された画素については、現在の単位フレームの画像データを、その輝度レベルが所定の分だけ下がるように補正する一方、前記オーバードライブ駆動による表示駆動を行うと判定された画素については、現在の単位フレーム

50

の画像データを、その直前の単位フレームと現在の単位フレームとの間での前記液晶素子の両端間電圧の変化が増加すると共に前記輝度レベル差が大きくなるのに応じて前記両端間電圧の変化がより大きくなるような画像データに補正する補正手段と、

前記補正手段による補正後の画像データを基に、前記表示駆動を画素ごと実施する駆動ドライバと

を備え、

前記補正手段は、

前記通常駆動による表示駆動を行うと判定された画素については、補正後の画像データに基づいて前記液晶素子の両端間に電圧を印加しこれが安定した後の状態における輝度レベルが、補正前の画像データに基づいて前記液晶素子の両端間に電圧を印加した直後における輝度レベルと同等となるように、現在の単位フレームの画像データを補正し、

前記オーバードライブ駆動による表示駆動を行うと判定された画素のうち、黒表示状態から白表示状態へ遷移する画素については、現在の単位フレームの画像データをそのまま補正後の画像データとして出力し、

前記オーバードライブ駆動による表示駆動を行うと判定された画素のうち、白表示状態から黒表示状態へ遷移する画素については、前記通常駆動による表示駆動の際の補正よりも輝度レベルが過剰に下がるように、現在の単位フレームの画像データを補正する

液晶駆動回路。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、補助容量素子を含んで構成された液晶表示装置、およびそのような液晶表示装置に適用される液晶駆動回路に関する。

【背景技術】

【0002】

20

近年、液晶を用いた表示素子（液晶素子）を駆動することによって映像表示を行う液晶表示装置が広く活用されている。このような液晶表示装置では、ガラス等の基板間に封止した液晶層において、液晶分子の配列を変化させることにより光源からの光を透過、変調させて表示を行っている。

【0003】

30

また、このような液晶表示装置では、従来より、液晶素子に対する印加電圧の変化が大きい場合には、画像データに基づく電圧に対して所定のオーバードライブ電圧を付加することにより（オーバードライブ駆動）、液晶の応答速度を向上させるようになっている（例えば、特許文献1）。

【0004】

なお、これとは別の技術として、液晶表示装置の各画素に液晶素子への印加電圧を安定化させるための補助容量素子を形成すると共に、この補助容量素子の両端間の電圧を変化させることによって液晶素子の両端間の電圧をも変化させるようにしたもの（Csinga方式）が提案されている（例えば、特許文献2）。

【0005】

40

【特許文献1】特開2007-11285号公報

【特許文献2】特開平4-145490号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

ここで、従来の液晶表示装置では、駆動素子（TFT（Thin Film Transistor：薄膜トランジスタ）素子）の耐圧よりも高い電圧を液晶素子に印加することはできないことから、例えば黒表示状態から白表示状態への遷移や白表示状態から黒表示状態への遷移の際にには、上記のようなオーバードライブ電圧を付加することができず、結果として中間階調付近での遷移にのみ、オーバードライブ駆動が適用されていた。すなわち、最も電圧の変化

50

の大きい遷移の際にオーバードライブ電圧の付加ができないことから、本来最も液晶の応答速度を上げる必要のある場合にオーバードライブ駆動の適用ができず、液晶の応答速度の改善が不十分であった。

#### 【0007】

なお、電源電圧および駆動素子の耐圧自体を本来よりも高く設定するようすれば、その分だけ高い電圧を液晶素子に印加することが可能となり、液晶の応答速度も向上するが、それに伴って消費電力が増加したり発熱量が増えてしまい、駆動素子の信頼性の低下などの問題が生じてしまうことになる。

#### 【0008】

このように従来の技術では、駆動素子の耐圧を上げることなく液晶の応答速度を向上させることが困難であり、改善の余地があった。 10

#### 【0009】

本発明はかかる問題点に鑑みてなされたもので、その目的は、駆動素子の耐圧を上げることなく液晶の応答速度を向上させることができ可能な液晶表示装置および液晶駆動回路を提供することにある。

#### 【課題を解決するための手段】

#### 【0010】

本発明の液晶表示装置は、マトリクス状に配置され、それぞれが、TFT素子と、主容量素子としての液晶素子と、補助容量素子とを含む複数の画素と、駆動対象の画素を線順次で選択し、選択した画素のTFT素子を所定のオン電圧により選択的にオン状態にすると共に、TFT素子を所定のオフ電圧により選択的にオフ状態にするための複数のゲート線と、駆動対象の画素に対し、TFT素子を介して画像データを供給するための複数のソース線と、各ゲート線の隣接ゲート線におけるオフ電圧を、画像データの輝度レベルに依存せずに一律に時間変化させつつ線順次動作を行うことにより、画素の表示駆動を行う駆動手段とを備えたものである。ここで、上記液晶素子は、その一端がTFT素子の一端に接続されている。また、上記補助容量素子は、その一端がTFT素子の一端に接続されると共に、他端が隣接ゲート線に接続されている。また、上記駆動手段は、現在の単位フレームの画像データとその直前の単位フレームの画像データとに基づいて、それらの画像データの輝度レベル差が所定の閾値未満の画素に対し、現在の単位フレームにおいて通常駆動による表示駆動を行うと判定する一方、上記輝度レベル差が上記閾値以上の画素に対し、現在の単位フレームにおいてオーバードライブ駆動による表示駆動を行うと判定する判定手段と、通常駆動による表示駆動を行うと判定された画素については、現在の単位フレームの画像データを、その輝度レベルが所定の分だけ下がるように補正する一方、オーバードライブ駆動による表示駆動を行うと判定された画素については、現在の単位フレームの画像データを、その直前の単位フレームと現在の単位フレームとの間での液晶素子の両端間電圧の変化が増加すると共に上記輝度レベル差が大きくなるのに応じて両端間電圧の変化がより大きくなるような画像データに補正する補正手段と、この補正手段による補正後の画像データを基に、表示駆動を画素ごと実施する駆動ドライバとを有している。また、上記補正手段は、通常駆動による表示駆動を行うと判定された画素については、補正後の画像データに基づいて液晶素子の両端間に電圧を印加しこれが安定した後の状態における輝度レベルが、補正前の画像データに基づいて液晶素子の両端間に電圧を印加した直後における輝度レベルと同等となるように、現在の単位フレームの画像データを補正し、オーバードライブ駆動による表示駆動を行うと判定された画素のうち、黒表示状態から白表示状態へ遷移する画素については、現在の単位フレームの画像データをそのまま補正後の画像データとして出力し、オーバードライブ駆動による表示駆動を行うと判定された画素のうち、白表示状態から黒表示状態へ遷移する画素については、通常駆動による表示駆動の際の補正よりも輝度レベルが過剰に下がるように、現在の単位フレームの画像データを補正するようになっている。 30

#### 【0011】

本発明の液晶駆動回路は、マトリクス状に配置されそれがTFT素子と主容量素子 50

としての液晶素子と補助容量素子とを含む複数の画素と、駆動対象の画素を線順次で選択しこの選択した画素のTFT素子を所定のオン電圧により選択的にオン状態にすると共に TFT素子を所定のオフ電圧により選択的にオフ状態にするための複数のゲート線と、駆動対象の画素に対し TFT素子を介して画像データを供給するための複数のソース線とを備え、上記液晶素子の一端が TFT素子の一端に接続され、上記補助容量素子の一端が TFT素子の一端に接続されると共に他端が隣接ゲート線に接続されるように構成された液晶表示装置に対して適用され、各ゲート線の隣接ゲート線におけるオフ電圧を画像データの輝度レベルに依存せずに一律に時間変化させつつ線順次動作を行うことにより画素の表示駆動を行うものであって、上記判定手段と、上記補正手段と、上記駆動ドライバとを備えたものである。

10

## 【0012】

本発明の液晶表示装置および液晶駆動回路では、ゲート線により供給されるオン電圧によって駆動対象の画素内のTFT素子が選択的にオン状態となると、ソース線からこのTFT素子を介して画像データが供給され、この画像データに基づく電圧が、画素内の液晶素子および補助容量素子の両端間にそれぞれ印加される。その後、ゲート線により供給されるオフ電圧によって上記TFT素子が選択的にオフ状態となると、ソース線からの画像データの供給が停止され、液晶素子および補助容量素子の両端間の電圧が保持される。そしてその後に上記隣接ゲート線によって補助容量素子の他端に、オフ電圧の電位が、画像データの輝度レベルに依存せずに一律に時間変化しつつ供給されると、この補助容量素子および液晶素子の両端間の電圧が上記画像データに基づく電圧から変化する。

20

この際、現在の単位フレームの画像データとその直前の単位フレームの画像データとに基づいて、それらの画像データの輝度レベル差が所定の閾値未満の画素に対し、現在の単位フレームにおいて通常駆動による表示駆動を行うと判定される一方、上記輝度レベル差が上記閾値以上の画素に対し、現在の単位フレームにおいてオーバードライブ駆動による表示駆動を行うと判定される。

そして、通常駆動による表示駆動を行うと判定された画素については、現在の単位フレームの画像データが、その輝度レベルが所定の分だけ下がるように補正される。具体的には、補正後の画像データに基づいて液晶素子の両端間に電圧を印加しこれが安定した後の状態における輝度レベルが、補正前の画像データに基づいて液晶素子の両端間に電圧を印加した直後における輝度レベルと同等となるように、現在の単位フレームの画像データが補正される。このような補正後の画像データを基に表示駆動が実施されることにより、上記のように補助容量素子および液晶素子の両端間の電圧が変化した後に、これらの両端間にそれぞれ、補正前の画像データに基づく電圧値が印加されるように（オーバードライブ駆動がなされないように、つまり通常駆動がなされるように）調整可能となる。具体的には、通常駆動の際の輝度レベルが変化しないように（すなわち、表示輝度の変動を伴わないように）、調整がなされる。

30

一方、オーバードライブ駆動による表示駆動を行うと判定された画素については、現在の単位フレームの画像データが、その直前の単位フレームと現在の単位フレームとの間での液晶素子の両端間電圧の変化が増加すると共に上記輝度レベル差が大きくなるのに応じて両端間電圧の変化がより大きくなるような画像データに補正される。このような補正後の画像データを基に表示駆動が実施されることにより、上記のように補助容量素子および液晶素子の両端間の電圧が変化した後に、これらの両端間にそれぞれ、画像データに基づく電圧値よりも大きな電圧値が印加され、これにより画像データに基づく電圧変化よりも大きくなるような表示駆動、すなわちオーバードライブ駆動がなされる。

40

具体的には、オーバードライブ駆動による表示駆動を行うと判定された画素のうち、黒表示状態から白表示状態へ遷移する画素については、現在の単位フレームの画像データがそのまま補正後の画像データとして出力される。これにより、補助容量素子および液晶素子の両端間の電圧が変化した後にこれらの両端間にそれぞれ、画像データに基づく白表示状態の電圧値よりも大きな電圧値が印加される。したがって、黒表示状態から白表示への遷移の際の電圧変化よりも大きくなるような表示駆動、すなわち黒表示状態から白表

50

示状態への遷移の際のオーバードライブ駆動が可能となる。

また、オーバードライブ駆動による表示駆動を行うと判定された画素のうち、白表示状態から黒表示状態へ遷移する画素については、通常駆動による表示駆動の際の補正よりも輝度レベルが過剰に下がるように、現在の単位フレームの画像データが補正される。これにより、補助容量素子および液晶素子の両端間の電圧が変化した後にこれらの両端間にそれぞれ、画像データに基づく黒表示状態の電圧値よりも小さな電圧値が印加される。したがって、白表示状態から黒表示状態への遷移の際の電圧変化よりも大きくなるような表示駆動、すなわち白表示状態から黒表示状態への遷移の際のオーバードライブ駆動が可能となる。

#### 【発明の効果】

10

#### 【0016】

本発明の液晶表示装置または液晶駆動回路によれば、通常駆動の際に、現在の単位フレームの画像データをその輝度レベルが所定の分だけ下がるように補正して得られる画像データを基に表示駆動を行うようにしたので、このような補正により得られる画像データに基づき、補助容量素子および液晶素子の両端間の電圧が変化した後にこれらの両端間にそれぞれ、補正前の画像データに基づく電圧値が印加されるように調整することができる。また、オーバードライブ駆動の際に、直前の単位フレームと現在の単位フレームとの間での液晶素子の両端間電圧の変化を増加させるような画像データを基に表示駆動を行うようにしたので、補助容量素子および液晶素子の両端間の電圧が変化した後にこれらの両端間にそれぞれ、画像データに基づく電圧値よりも大きな電圧値を印加し、これによりオーバードライブ駆動を行うことができる。よって、駆動素子の耐圧を上げることなく、液晶の応答速度を向上させることができる。

20

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、本発明の実施の形態について、図面を参照して詳細に説明する。

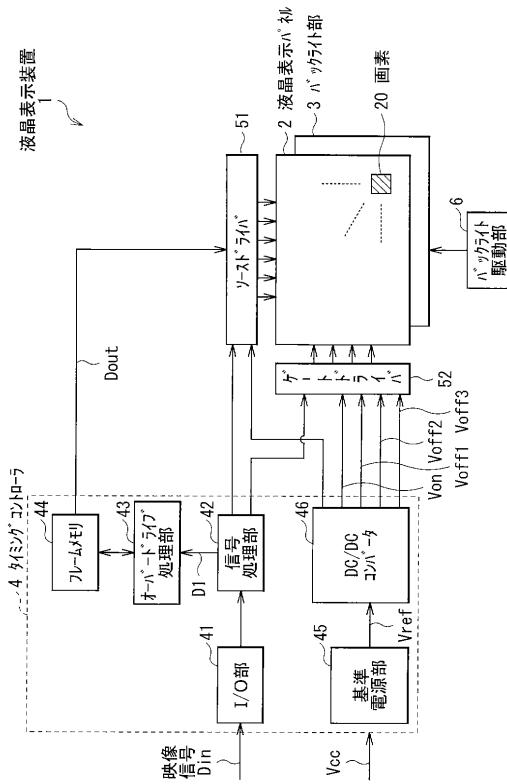

#### 【0018】

図1は、本発明の一実施の形態に係る液晶表示装置（液晶表示装置1）の全体構成を表すものである。この液晶表示装置1は、液晶表示パネル2と、バックライト部3と、タイミングコントローラ4と、ソースドライバ51およびゲートドライバ52と、バックライト駆動部6とを備えている。

30

#### 【0019】

液晶表示パネル2は、後述するソースドライバ51およびゲートドライバ52から供給される駆動信号によって入力映像信号Dinに基づく映像表示を行うものであり、マトリクス状に並んで配置された複数の画素20を含んで構成されている。また、各画素20内には、後述する画素回路ユニット（図2参照）が形成されている。なお、この画素回路ユニットの詳細構成については、後述する。

#### 【0020】

バックライト部3は、液晶表示パネル2に対して光を照射する光源であり、例えばCCL（Cold Cathode Fluorescent Lamp：冷陰極蛍光ランプ）やLED（Light Emitting Diode：発光ダイオード）などを含んで構成される。

40

#### 【0021】

タイミングコントローラ4は、I/O部41と、信号処理部42と、オーバードライブ処理部43と、フレームメモリ44と、基準電源部45と、DC/DCコンバータ46とを有している。このタイミングコントローラ4は、外部からの入力映像信号Din（輝度信号）に対して後述する所定の信号処理を施すことにより、RGB信号である映像信号Doutを生成すると共に、電源電圧Vccの供給に基づいてソースドライバ51およびゲートドライバ52において用いられる電圧を生成するものである。タイミングコントローラ4はまた、ソースドライバ51およびゲートドライバ52の駆動タイミングを制御する役割も果たしている。

#### 【0022】

50

I / O 部 4 1 は、入力映像信号 D in を入力して信号処理部 4 2 へ供給するものである。信号処理部 4 2 は、供給された入力映像信号 D in に対して所定の信号処理を施し、RGB 信号である映像信号 D 1 をオーバードライブ処理部 4 3 へ供給すると共に、ソースドライバ 5 1 およびゲートドライバ 5 2 の駆動タイミング制御信号を生成し、ソースドライバ 5 1 およびゲートドライバ 5 2 へ供給するものである。

#### 【0023】

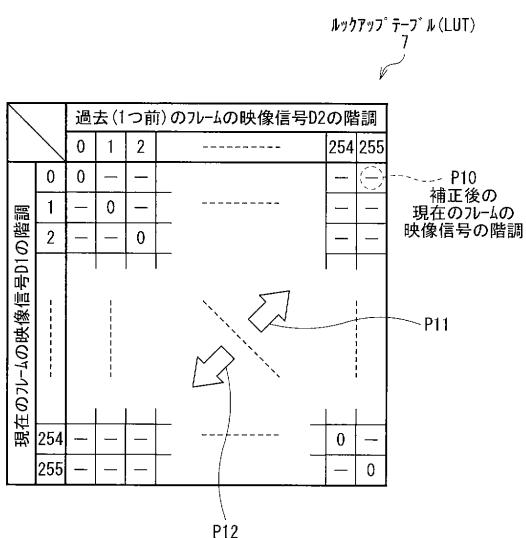

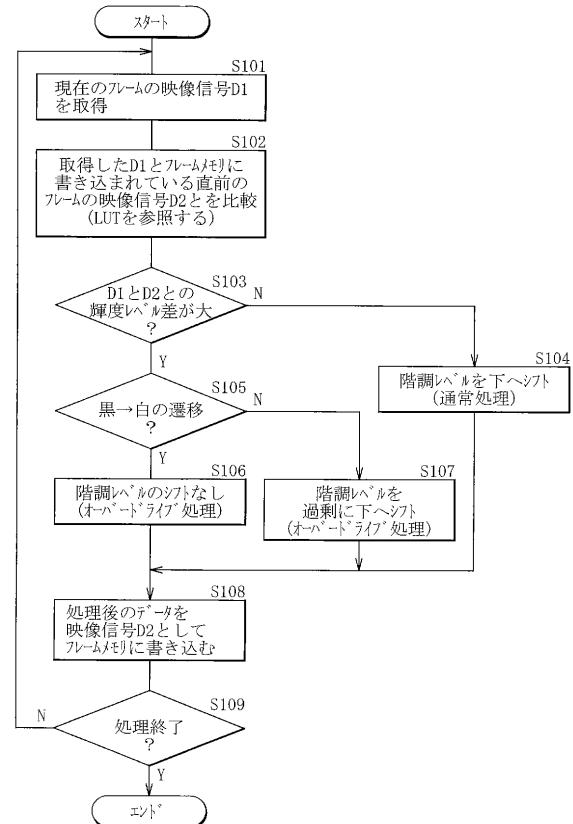

オーバードライブ処理部 4 3 は、信号処理部 4 2 から供給される現在のフレームの映像信号 D 1 と、後述するフレームメモリ 4 4 に記憶されている 1 つ前の（直前の）フレームの映像信号 D 2（図示せず）とに基づき、現在のフレームにおいて、後述する通常駆動およびオーバードライブ駆動のうちのどちらによる表示駆動を行うのかを画素 2 0 ごとに判定すると共に、この判定結果に基づき、現在のフレームの映像信号 D 1 に対して後述する補正を画素 2 0 ごとに行い、そのような補正後の映像信号 D 2 をフレームメモリ 4 4 へ書き込む（記憶させる）という処理（詳細は後述）を行うものである。なお、上記したような駆動方法の判定処理および現在のフレームの映像信号 D 1 の補正処理は、例えば図 3 に示したように、現在のフレームの映像信号 D 1 の階調（例えば、0 ~ 255 階調）および過去（1 つ前）のフレームの映像信号 D 2 の階調（例えば、0 ~ 255 階調）と、補正後の現在のフレームの映像信号の階調とを関連付けてなるルックアップテーブル 7 を用いてなされるようになっている。なお、このような駆動方法の判定処理および現在のフレームの映像信号 D 1 の補正処理の詳細については、後述する。

#### 【0024】

フレームメモリ 4 4 は、上記したように、オーバードライブ処理部 4 3 による補正後（処理後）の映像信号を、映像信号 D 2 としてフレーム単位で記憶するものである。

#### 【0025】

基準電源部 4 5 は、電源電圧 Vcc に基づいて、DC / DC コンバータ 4 6 の基準電圧である基準電圧 Vref を生成するものである。DC / DC コンバータ 4 6 は、供給される基準電圧 Vref に基づいて所定の直流電圧変換を行うことにより、ソースドライバ 5 1 の電源電圧およびゲートドライバ 5 2 において用いられる電圧（後述するゲートオン電圧 Von および複数種類のゲートオフ電圧 Voff1, Voff2, Voff3）をそれぞれ生成し、ソースドライバ 5 1 およびゲートドライバ 5 2 へ供給するものである。

#### 【0026】

ソースドライバ 5 1 は、信号処理部 4 2 から供給される駆動タイミング制御信号に従って、フレームメモリ 4 4 に記憶されている現在のフレームの映像信号 D 2 を映像信号 Dout として入力すると共に、この映像信号 Dout に基づく駆動電圧（後述するソース電圧）を液晶表示パネル 2 の各画素 2 0 へ供給するものである。

#### 【0027】

ゲートドライバ 5 2 は、信号処理部 4 2 から供給される駆動タイミング制御信号に従って、DC / DC コンバータ 4 6 からの供給電圧（ゲートオン電圧 Von およびゲートオフ電圧 Voff1, Voff2, Voff3）に基づき、液晶表示パネル 2 内の各画素 2 0 を後述するゲート線に沿って線順次駆動するものである。なお、このゲートドライバ 5 2 の詳細構成については、後述する（図 4 および図 5）。

#### 【0028】

バックライト駆動部 6 は、バックライト部 3 の点灯動作を制御するものであり、例えばインバータ回路を含んで構成されている。

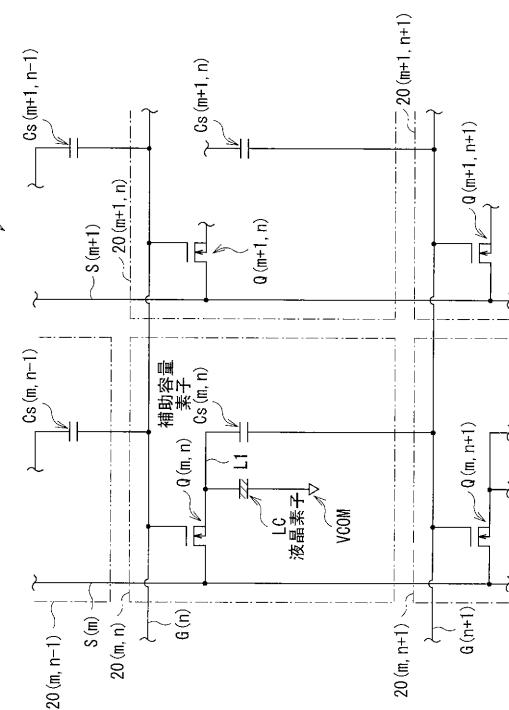

#### 【0029】

次に図 2 を参照して、各画素 2 0 に形成された画素回路ユニット（液晶表示素子）の構成について詳細に説明する。図 2 は、画素 2 0 内の画素回路ユニットの回路構成例を表したものである。なお、図中の符号 m, n はそれぞれ自然数を表しており、画素 2 0 (m, n) は、複数の画素 2 0 のうちの座標 (m, n) に位置する画素を表している。

#### 【0030】

画素 2 0 (m, n) には、主容量素子として機能する液晶素子 LC と、補助容量素子 C

10

20

30

40

50

sと、TFT素子Q(m, n)とからなる画素回路ユニットが形成されている。また、この画素20(m, n)には、駆動対象の画素回路ユニットを線順次で選択してその画素回路ユニット内のTFT素子Qを前述のゲートオン電圧V<sub>on</sub>により選択的にオン状態にすると共に、このTFT素子Qを前述の複数種類のゲートオフ電圧V<sub>off1</sub>, V<sub>off2</sub>, V<sub>off3</sub>により選択的にオフ状態にするためのゲート線G(n)と、駆動対象の画素回路ユニットに対し、その画素回路ユニット内のTFT素子Qを介して画像データ(映像信号D<sub>out</sub>)を供給するソース線S(m)とが接続されている。なお、ゲート線G(n)は、後述するようにゲート線G(n-1)に沿って延在する画素20(m, n-1)等の補助容量線としても機能するようになっている。

## 【0031】

なお、画素20(m, n)に対してソース線S(m)に沿って線順次動作方向に隣接する画素20(m, n+1)には、図示したようにTFT素子Q(m, n+1)が含まれると共に、ゲート線G(n+1)およびソース線S(m)とが接続され、画素20(m, n)に対してソース線S(m)に沿って線順次動作方向とは逆方向に隣接する画素20(m, n-1)には、図示したように補助容量素子C<sub>s</sub>(m, n-1)が含まれると共に、図示しないゲート線G(n-1)およびソース線S(m)が接続されている。また、画素20(m, n)に対してゲート線G(n)に沿って隣接する画素20(m+1, n)には、図示したようにTFT素子Q(m+1, n)および補助容量素子C<sub>s</sub>(m+1, n)が含まれると共に、ゲート線G(n)およびソース線S(m+1)が接続されている。さらに、この画素20(m+1, n)に対してソース線S(m+1)に沿って線順次動作方向に隣接する画素20(m+1, n+1)には、図示したようにTFT素子Q(m+1, n+1)が含まれると共に、ゲート線G(n+1)およびソース線S(m+1)とが接続され、画素20(m+1, n)に対してソース線S(m+1)に沿って線順次動作方向とは逆方向に隣接する画素20(m+1, n-1)(図示せず)には、図示したように補助容量素子C<sub>s</sub>(m+1, n-1)が含まれると共に、図示しないゲート線G(n-1)およびソース線S(m+1)が接続されている。

## 【0032】

液晶素子LCは、ソース線S(m)からTFT素子Q(m, n)を介して一端に供給される映像信号D<sub>out</sub>に応じて表示のための動作を行う(表示光を射出する)表示要素として機能しており、図示しない液晶層と、この液晶層を挟む一対の電極とを含んで構成されている。これら一対の電極のうちの一方(一端)側は接続線L1を介してTFT素子Q(m, n)のソースおよび補助容量素子C<sub>s</sub>の一端に接続され、他方(他端)側はコモン電極VCOMに接続されている。なお、上記液晶層は、例えばTN(Twisted Nematic)モードの液晶などにより構成される。

## 【0033】

補助容量素子C<sub>s</sub>は、液晶素子LCの蓄積電荷を安定化させるための容量素子であり、一端(一方の電極)が接続線L1を介して液晶素子LCの一端およびTFT素子Q(m, n)のソースに接続されると共に、他端(対向電極)が、ソース線S(m)に沿って線順次動作方向に隣接するゲート線である隣接ゲート線G(n+1)に接続されている。このような構成により各画素20内の画素回路ユニットは、いわゆるC<sub>s</sub> on gate方式(詳細は後述)の画素回路ユニットとして機能するようになっている。

## 【0034】

TFT素子Q(m, n)はMOS-FET(Metal Oxide Semiconductor - Field Effect Transistor)により構成されており、ゲートがゲート線G(n)に接続され、ソースが接続線L1を介して液晶素子LCの一端および補助容量素子C<sub>s</sub>の一端に接続され、ドレインがソース線S(m)に接続されている。このTFT素子Q(m, n)は、液晶素子LCの一端および補助容量素子C<sub>s</sub>の一端に対して映像信号D<sub>out</sub>を供給するためのスイッチング素子として機能している。具体的には、ゲートドライバ52からゲート線G(n)を介して供給される選択信号(ゲート信号)に応じて、ソース線S(m)と画素20(m, n)内の液晶素子LCおよび補助容量素子C<sub>s</sub>の一端同士との間を選択的に導通させる

10

20

30

40

50

(オン状態にする)ようになっている。

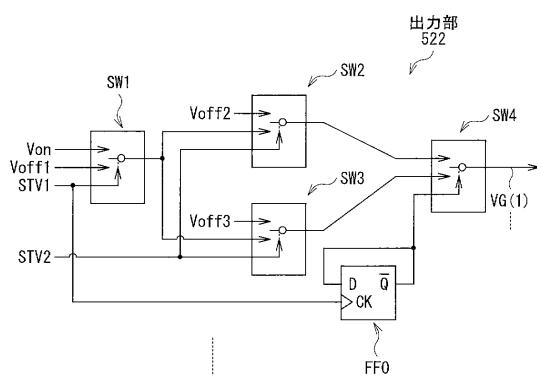

**【0035】**

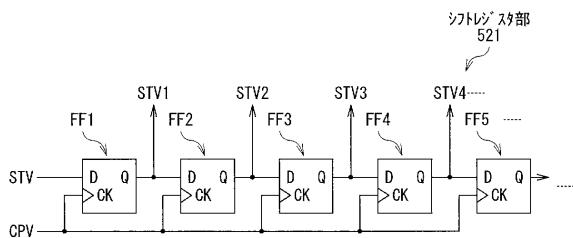

次に図4および図5を参照して、ゲートドライバ52の回路構成の詳細について説明する。このゲートドライバ52は、図4に示したシフトレジスタ部521と、図5に示した出力部522とを含んで構成されている。

**【0036】**

シフトレジスタ部521は、信号処理部42から供給される駆動タイミング制御信号であるストローブ信号STVおよびパルス信号(クロック信号)CPVに基づいて、後述するような順次異なるタイミングで「H」状態となるストローブ信号STV1, STV2, STV3, STV4, ...を生成するものであり、複数のフリップフロップ回路(例えば、図4に示したフリップフロップ回路FF1～FF5, ...)を含んで構成されている。フリップフロップ回路FF1のデータ入力端子Dにはストローブ信号STVが供給されると共に、各フリップフロップ回路FF1～FF5, ...のクロック端子CKにはパルス信号CPVが互いに並列に供給されるようになっている。また、フリップフロップ回路FF1のデータ出力端子Qからはストローブ信号STV1が出力されると共にこのストローブ信号STV1はフリップフロップ回路FF2のデータ入力端子Dに供給され、フリップフロップ回路FF2のデータ出力端子Qからはストローブ信号STV2が出力されると共にこのストローブ信号STV2はフリップフロップ回路FF3のデータ入力端子Dに供給され、フリップフロップ回路FF3のデータ出力端子Qからはストローブ信号STV3が出力されると共にこのストローブ信号STV3はフリップフロップ回路FF4のデータ入力端子Dに供給され、フリップフロップ回路FF4のデータ出力端子Qからはストローブ信号STV4が出力されると共にこのストローブ信号STV4はフリップフロップ回路FF5のデータ入力端子Dに供給されるようになっている。

10

**【0037】**

出力部522は、シフトレジスタ部521から供給されるストローブ信号STV1, STV2, STV3, STV4, ...およびDC/DCコンバータ46から供給されるゲートオン電圧Vonおよびゲートオフ電圧Voff1, Voff2, Voff3に基づいて、ゲートドライバ52の出力信号であるゲート信号(ゲート電圧VG(1), VG(2), ...)を生成するものであり、各ゲート電圧ごとに、4つのアナログスイッチ部(例えば、図5に示したように、ゲート電圧VG(1)に対するアナログスイッチ部SW1～SW4)と、1つのフリップフロップ回路(例えば、図5に示したように、ゲート電圧VG(1)に対するフリップフロップ回路FF0)とを含んで構成されている。ここで、ゲート電圧VG(1)に対するアナログスイッチSW1～SW4およびフリップフロップ回路FF0について代表して説明すると、アナログスイッチSW1は、ストローブ信号STV1の値に応じてゲートオン電圧Vonおよびゲートオフ電圧Voff1のうちの一方を選択出力するもの(具体的には、ストローブ信号STV1='H'のときにはゲートオン電圧Vonを選択出力する一方、ストローブ信号STV1='L'のときにはゲートオフ電圧Voff1を選択出力する)である。また、アナログスイッチSW2は、ストローブ信号STV2の値に応じてゲートオフ電圧Voff2およびアナログスイッチSW1からの出力電圧のうちの一方を選択出力するもの(具体的には、ストローブ信号STV2='H'のときにはゲートオフ電圧Voff2を選択出力する一方、ストローブ信号STV2='L'のときにはアナログスイッチSW1からの出力電圧を選択出力する)である。また、アナログスイッチSW3は、ストローブ信号STV2の値に応じてゲートオフ電圧Voff3およびアナログスイッチSW1からの出力電圧のうちの一方を選択出力するもの(具体的には、ストローブ信号STV2='H'のときにはゲートオフ電圧Voff3を選択出力する一方、ストローブ信号STV2='L'のときにはアナログスイッチSW1からの出力電圧を選択出力する)である。また、フリップフロップ回路FF0は、ストローブ信号STV1をクロック端子CKに入力すると共に反転データ出力端子Q-からの出力データをデータ入力端子DおよびアナログスイッチSW4の選択端子に供給しており、「H」状態と「L」状態とが交互に発生するトグル信号生成部として機能している。また、アナログスイッチSW4は、フリップフロップ回路

20

30

40

50

F F 0 から供給される上記トグル信号の値に応じてアナログスイッチ SW 2 からの出力電圧およびアナログスイッチ SW 3 からの出力電圧のうちの一方を選択し(具体的には、トグル信号=「H」のときにはアナログスイッチ SW 2 からの出力電圧を選択する一方、トグル信号=「L」のときにはアナログスイッチ SW 3 からの出力電圧を選択する)、ゲート電圧 V G (1) として出力するものである。

#### 【0038】

ここで、タイミングコントローラ 4、ソースドライバ 5 1 およびゲートドライバ 5 2 が本発明における「駆動手段」および「液晶駆動回路」の一具体例に対応し、オーバードライブ処理部 4 3 が本発明における「判定手段」および「補正手段」の一具体例に対応する。

10

#### 【0039】

次に、このような構成からなる本実施の形態の液晶表示装置 1 の動作について、詳細に説明する。

#### 【0040】

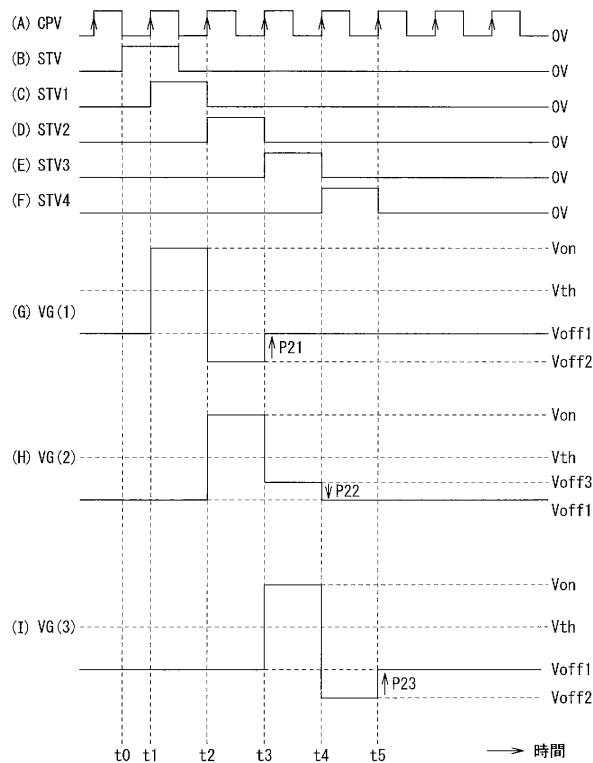

まず、図 1、図 2 および図 4 ~ 図 6 を参照して、液晶表示装置 1 の全体動作について説明する。ここで図 6 は、ゲートドライバ 5 2 の動作をタイミング波形図で表したものであり、(A) はパルス信号(クロック信号) C P V の電圧波形を、(B) ~ (F) はそれぞれストローブ信号 S T V , S T V 1 ~ S T V 4 の電圧波形を、(G) ~ (I) はそれぞれゲート信号 G (1) ~ G (3) の電圧を示すゲート電圧 V G (1) ~ V G (3) の電圧波形を、それぞれ表している。

20

#### 【0041】

この液晶表示装置 1 では、図 1 に示したように、タイミングコントローラ 4 において、外部からの入力映像信号 D in に対して所定の信号処理が施され、R G B 信号である映像信号 D out が生成されると共に、電源電圧 V c c の供給に基づいてソースドライバ 5 1 およびゲートドライバ 5 2 において用いられる電圧が生成される。

#### 【0042】

具体的には、まず、I / O 部 4 1 を介して入力した入力映像信号 D in が、信号処理部 4 2 によって所定の信号処理が施され、R G B 信号である映像信号 D 1 が生成されると共に、この信号処理部 4 2 においてソースドライバ 5 1 およびゲートドライバ 5 2 の駆動タイミング制御信号が生成され、ソースドライバ 5 1 およびゲートドライバ 5 2 へ供給される。

30

#### 【0043】

次に、オーバードライブ処理部 4 3 では、信号処理部 4 2 から供給される現在のフレームの映像信号 D 1 と、フレームメモリ 4 4 に記憶されている 1 つ前の(直前の)フレームの映像信号 D 2 とに基づき、後述する駆動方法の判定処理および現在のフレームの映像信号 D 1 の補正処理が画素 2 0 ごとになされ、これにより補正後の映像信号 D 2 がフレームメモリ 4 4 へ書き込まれる。

#### 【0044】

一方、基準電源部 4 5 により供給される基準電圧 V r e f に基づいて D C / D C コンバータ 4 6 により直流電圧変換がなされ、生成されたソースドライバ 5 1 の電源電圧がソースドライバ 5 1 へ供給されると共に、生成されたゲートオン電圧 V on および 3 つのゲートオフ電圧 V off1 , V off2 , V off3 がそれぞれ、ゲートドライバ 5 2 へ供給される。

40

#### 【0045】

ここで、ゲートドライバ 5 2 では、信号処理部 4 2 により供給される駆動タイミング制御信号(具体的には、ストローブ信号 S T V およびパルス信号(クロック信号) C P V )、ならびに D C / D C コンバータ 4 6 により供給されるゲートオン電圧 V on およびゲートオフ電圧 V off1 , V off2 , V off3 に基づき、例えば図 6 に示したようにして、各ゲート線に供給されるゲート電圧が生成される。

#### 【0046】

具体的には、まず、図 4 に示したシフトレジスタ部 5 2 1 では、信号処理部 4 2 により

50

供給されるストローブ信号 S T V ( 図 6 ( A ) ) およびパルス信号 C P V ( 図 6 ( B ) ) に基づき、図 6 ( C ) ~ ( F ) にそれぞれ示したようなタイミング波形 ( タイミング  $t_0$  ~  $t_5$  ) からなるストローブ信号 S T V 1 ~ S T V 4 等が生成される。

#### 【 0 0 4 7 】

次に、図 5 に示した出力部 5 2 2 では、シフトレジスタ部 5 2 1 から供給されるストローブ信号 S T V 1 , S T V 2 , S T V 3 , S T V 4 , ... および D C / D C コンバータ 4 6 から供給されるゲートオン電圧  $V_{on}$  およびゲートオフ電圧  $V_{off1}$  ,  $V_{off2}$  ,  $V_{off3}$  に基づいて、例えば図 6 ( G ) ~ ( I ) にそれぞれ示したようなタイミング波形 ( タイミング  $t_1$  ~  $t_5$  ) からなるゲート電圧  $V_G(1)$  ,  $V_G(2)$  ,  $V_G(3)$  , ... が生成される。すなわち、ゲートオン電圧  $V_{on}$  およびゲートオフ電圧  $V_{off1}$  ,  $V_{off2}$  ,  $V_{off3}$  の 4 値を用いた線順次のゲート電圧が生成される ( 4 値駆動のゲート電圧となる )。これにより、液晶表示パネル 2 内の各画素 2 0 がゲート線に沿って線順次により 4 値駆動される。

10

#### 【 0 0 4 8 】

一方、ソースドライバ 5 1 では、信号処理部 4 2 から供給される駆動タイミング制御信号に従って、フレームメモリ 4 4 に記憶されている現在のフレームの映像信号 D 2 を映像信号 Dout として入力すると共に、この映像信号 Dout に基づく駆動電圧 ( ソース電圧 ) が生成され、ソース線に沿って液晶表示パネル 2 の各画素 2 0 へ供給される。

#### 【 0 0 4 9 】

ここで、ゲートドライバ 5 2 およびソースドライバ 5 1 から出力される各画素 2 0 内への駆動電圧 ( ゲート電圧およびソース電圧 ) によって、各画素 2 0 に対する線順次表示駆動動作がなされる。具体的には、図 2 に示した画素 2 0 (  $m$  ,  $n$  ) 内の画素回路ユニットでは、以下のようにしていわゆるライン反転駆動動作がなされる。

20

#### 【 0 0 5 0 】

まず、ソースドライバ 5 1 からソース線 S (  $m$  ) を介して画素 2 0 (  $m$  ,  $n$  ) 用の映像信号 Dout が供給されると共に、ゲートドライバ 5 2 からゲート線 G (  $n$  ) を介して画素 2 0 (  $m$  ,  $n$  ) 用の選択信号 ( 具体的には、ゲート電圧  $V_G(n)$  におけるゲートオン電圧  $V_{on}$  ) が供給されると、ゲート線 G (  $n$  ) にパルス状の電位 ( ゲートオン電圧  $V_{on}$  の電位 ) が発生する。これにより、TFT 素子 Q (  $m$  ,  $n$  ) がオン状態となり、接続線 L 1 を介して映像信号 Dout に基づく電流が流れ、液晶素子 LC および補助容量素子 Cs の一端同士に電荷が蓄積される ( 画像データが供給される )。すなわち、映像信号 Dout に基づく電圧が、画素 2 0 (  $m$  ,  $n$  ) 内の液晶素子 LC および補助容量素子 Cs (  $m$  ,  $n$  ) の両端間にそれぞれ印加される。

30

#### 【 0 0 5 1 】

次に、ゲート線 G (  $n$  ) により供給されるゲートオフ電圧  $V_{off2}$  またはゲートオフ電圧  $V_{off3}$  ( 図 6 ( G ) , ( I ) に示したように、正極のときにはゲートオフ電圧  $V_{off2}$  、負極のときにはゲートオフ電圧  $V_{off3}$  ) によって TFT 素子 Q (  $m$  ,  $n$  ) が選択的にオフ状態となると、ソース線 S (  $m$  ) からの映像信号 Dout の供給が停止され、画素 2 0 (  $m$  ,  $n$  ) 内の液晶素子 LC および補助容量素子 Cs (  $m$  ,  $n$  ) の両端間の電圧が保持される。

#### 【 0 0 5 2 】

次に、ソース線 S (  $m$  ) に沿って線順次動作方向に隣接するゲート線である隣接ゲート線 G (  $n+1$  ) によって補助容量素子 Cs (  $m$  ,  $n$  ) の他端 ( 対向電極 ) に、例えば図 6 ( G ) ~ ( I ) 中の矢印 P 2 1 ~ P 2 3 に示したように、ゲートオフ電圧  $V_{off2}$  の電位からゲートオフ電圧  $V_{off1}$  の電位への変動や、ゲートオフ電圧  $V_{off3}$  の電位からゲートオフ電圧  $V_{off1}$  の電位への変動のように、ゲートオフ電圧の電位が時間変化しつつ供給されると、それに伴って補助容量素子 Cs (  $m$  ,  $n$  ) および液晶素子 LC の両端間の電圧も、上記した映像信号 Dout に基づく電圧から変化する ( いわゆる C<sub>s</sub> on gate 方式による作用 )。

40

#### 【 0 0 5 3 】

以上のような液晶表示パネル 2 における線順次表示駆動動作により、バックライト駆動部 6 の駆動動作によりバックライト部 3 から照射される照明光が、液晶表示パネル 2 によ

50

り画素 20 ごとに変調され、表示光として液晶表示パネル 2 から出力される。これにより、入力映像信号 D<sub>in</sub>に基づく表示光により、映像表示がなされる。

#### 【0054】

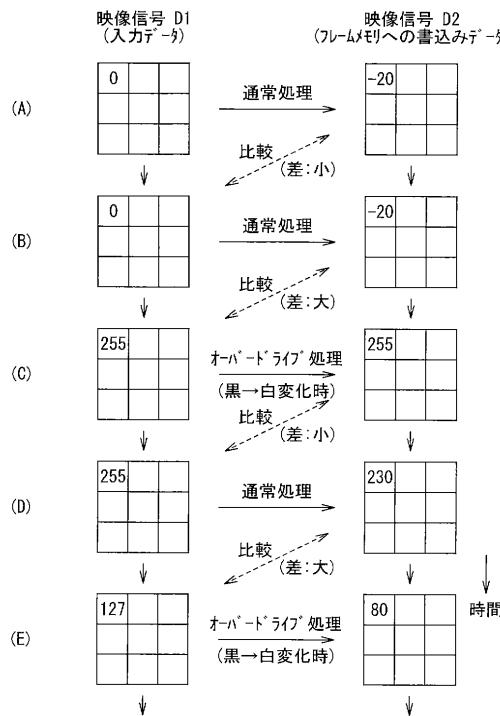

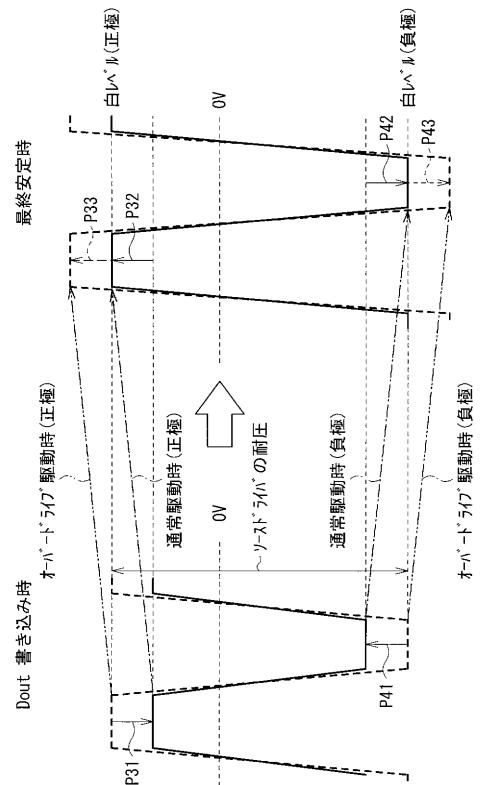

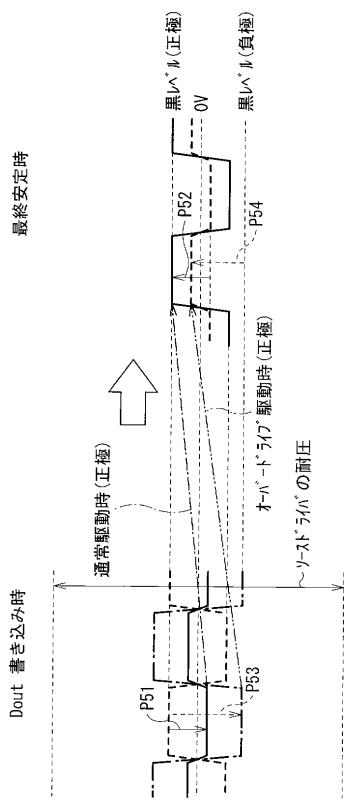

次に、図 1, 図 2, 図 4 ~ 図 6 に加えて図 3, 図 7 ~ 図 11 を参照して、本発明の特徴的部分の 1 つである、オーバードライブ処理部 43 による駆動方法の判定処理および現在のフレームの映像信号 D<sub>1</sub> の補正処理の詳細について詳細に説明する。ここで、図 7 は、このようなオーバードライブ処理部 43 による処理の一例を流れ図で表したものである。また、図 8 は、映像信号 D<sub>1</sub> (オーバードライブ処理部 43 への入力データ) および映像信号 D<sub>2</sub> (フレームメモリ 44 への書き込みデータ) のフレーム単位での時間変化とオーバードライブ処理部 43 による処理との関係をタイミング図で表したものであり、図中の 3 × 3 のマス目の左上に示した各数字は、ある画素 20 における画素データ (映像信号の輝度の階調レベル (0 ~ 255 階調)) を示している。また、図 9 は、白表示の際ににおける映像信号 D<sub>out</sub> の各画素 20 への書き込み時および最終安定時の液晶素子 LC の両端間に印加される電圧波形を、図 10 は、黒表示の際ににおける映像信号 D<sub>out</sub> の各画素 20 への書き込み時および最終安定時の液晶素子 LC の両端間に印加される電圧波形を、それぞれ表している。また、図 11 は、オーバードライブ駆動時における液晶素子 LC の両端間に印加される電圧波形をタイミング図で表したものであり、図 11 (A) は黒表示状態から白表示状態への遷移の際のオーバードライブ駆動を、図 11 (B) は白表示状態から黒表示状態への遷移の際のオーバードライブ駆動を、それぞれ表している。

#### 【0055】

まず、オーバードライブ処理部 43 は、信号処理部 42 から現在のフレームの映像信号 D<sub>1</sub> を取得すると (図 7 のステップ S<sub>101</sub>)、例えば図 3 に示したルックアップテーブル 7 を参照することにより、取得した現在のフレームの映像信号 D<sub>1</sub> と、フレームメモリ 44 に書き込まれている (記憶されている) 直前のフレームにおける補正後の映像信号 D<sub>2</sub> とを比較し (ステップ S<sub>102</sub>)、これら映像信号 D<sub>1</sub>, D<sub>2</sub> における輝度レベル差 (輝度の階調レベルの差) がオーバードライブ処理を施すべき程度に大きいか否か (ルックアップテーブル 7 により規定されている閾値よりも大きいか否か) を判断する (ステップ S<sub>103</sub>)。

#### 【0056】

具体的には、例えば図 8 に示したように、まず、図 8 (A) に示した直前の映像信号 D<sub>2</sub> と図 8 (B) に示した現在の映像信号 D<sub>1</sub> とを比較すると (ステップ S<sub>103</sub>)、映像信号 D<sub>1</sub>, D<sub>2</sub> における輝度の階調レベル差が閾値よりも小さいため (ステップ S<sub>103</sub> : N)、この画素においては通常駆動による表示駆動を行うべきであると判定し、現在のフレームの映像信号 D<sub>1</sub> における輝度の階調レベルを下にシフト (下げる) する補正である通常処理を行う (ステップ S<sub>104</sub>、図 8 (B)、図 10 中の矢印 P<sub>51</sub>)。したがって、フレームメモリ 44 には、図 8 (B) に示したように、「-20」という階調レベルのデータが、現在のフレームにおける補正後の映像信号 D<sub>2</sub> として書き込まれる (ステップ S<sub>108</sub>)。また、この際、前述した C<sub>s on gate</sub> 方式の作用により、補助容量素子 C<sub>s</sub> (m, n) および液晶素子 LC の両端間の電圧がその後この映像信号 D<sub>2</sub> (D<sub>out</sub>) に基づく電圧から変化して安定状態となったとき (最終安定時)、例えば図 10 に示したように、通常駆動 (正極) によって、補正後の映像信号 D<sub>2</sub> に基づく輝度レベルが、補正前の映像信号 D<sub>1</sub> に基づく本来の輝度レベル (例えば、図中の黒レベル (正極)) と同等のものとなっており、これにより補正の前後で輝度レベルが変化しないようになっている。

#### 【0057】

なお、その後はオーバードライブ処理部 43 による処理全体を終了するか否かが判断され (ステップ S<sub>109</sub>)、終了しないと判断した場合には (ステップ S<sub>109</sub> : N)、ステップ S<sub>101</sub> へと戻ることとなる。

#### 【0058】

次に、上記と同様のステップ S<sub>101</sub>, S<sub>102</sub> の後に、図 8 (B) に示した直前の映

10

20

30

40

50

像信号 D 2 と図 8 ( C ) に示した現在の映像信号 D 1 とを比較すると (ステップ S 103) 、映像信号 D 1 , D 2 における輝度の階調レベル差が閾値よりも大きいため (ステップ S 103 : Y) 、この画素においてはオーバードライブ駆動による表示駆動を行うべきであると判定し、次にオーバードライブ処理部 43 は、直前のフレームから現在のフレームへの遷移が黒表示状態から白表示状態への遷移か否かを判断する (ステップ S 105) 。ここでは、図 8 ( B ) , ( C ) に示したように黒表示状態から白表示状態への遷移であるため (ステップ S 105 : Y) 、オーバードライブ処理部 43 は、現在のフレームの映像信号 D 1 における輝度の階調レベルを変化させずに (輝度の階調レベルをシフトさせずに) そのまま用いるというオーバードライブ処理を行う (ステップ S 106 、図 8 ( C )) 。したがって、フレームメモリ 44 には、図 8 ( C ) に示したように、そのまま「255」 10 という階調レベルのデータが現在のフレームにおける補正後の映像信号 D 2 として書き込まれる (ステップ S 108) 。したがって、例えば図 9 に示したオーバードライブ駆動 (正極) によって、Cs on gate 方式の作用を用いたオーバードライブ駆動がなされ、これにより例えば図 11 ( A ) 中の矢印 P 61 で示したように、直前のフレームと現在のフレームとの間での液晶素子 LC の両端間の電圧変化が、現在のフレームの映像信号 D 1 (補正前の画像データ) に基づく本来の電圧変化よりも大きくなり、図中の矢印 P 62 で示したように、黒表示状態から白表示状態への遷移の際の液晶の応答速度が改善する。

#### 【0059】

次に、上記と同様のステップ S 109 , S 101 , S 102 の後に、図 8 ( C ) に示した直前の映像信号 D 2 と図 8 ( D ) に示した現在の映像信号 D 1 とを比較すると (ステップ S 103) 、映像信号 D 1 , D 2 における輝度の階調レベル差が閾値よりも小さいため (ステップ S 103 : N) 、この画素においては通常駆動による表示駆動を行うべきであると判定し、現在のフレームの映像信号 D 1 における輝度の階調レベルを下にシフト (下げる) する補正である通常処理を行う (ステップ S 104 、図 8 ( D ) 、図 9 中の矢印 P 31) 。したがって、フレームメモリ 44 には、図 8 ( D ) に示したように、「230」 20 という階調レベルのデータが、現在のフレームにおける補正後の映像信号 D 2 として書き込まれ (ステップ S 108) 、例えば図 9 に示したように通常駆動 (正極) によって、Cs on gate 方式の作用を用いた通常駆動がなされる。

#### 【0060】

次に、上記と同様のステップ S 109 , S 101 , S 102 の後に、図 8 ( D ) に示した直前の映像信号 D 2 と図 8 ( E ) に示した現在の映像信号 D 1 とを比較すると (ステップ S 103) 、映像信号 D 1 , D 2 における輝度の階調レベル差が閾値よりも大きいため (ステップ S 103 : Y) 、この画素においてはオーバードライブ駆動による表示駆動を行うべきであると判定し、次に前述したように、直前のフレームから現在のフレームへの遷移が黒表示状態から白表示状態への遷移か否かを判断する (ステップ S 105) 。ここでは、図 8 ( D ) , ( E ) に示したように白表示状態から黒表示状態への遷移であるため (ステップ S 105 : N) 、オーバードライブ処理部 43 は、現在のフレームの映像信号 D 1 における輝度の階調レベルを、通常駆動の際の補正 (図 10 中の矢印 P 51) よりも過剰に下がるようにする補正であるオーバードライブ処理を行う (ステップ S 107 、図 8 ( E ) 、図 10 中の矢印 P 53) 。したがって、フレームメモリ 44 には、図 8 ( E ) に示したように、「80」 30 という階調レベルのデータが、現在のフレームにおける補正後の映像信号 D 2 として書き込まれ (ステップ S 108) 、例えば図 10 に示したオーバードライブ駆動 (正極) によって、Cs on gate 方式の作用を用いたオーバードライブ駆動がなされ、これにより例えば図 11 ( B ) 中の矢印 P 71 で示したように、直前のフレームと現在のフレームとの間での液晶素子 LC の両端間の電圧変化が、現在のフレームの映像信号 D 1 (補正前の画像データ) に基づく本来の電圧変化よりも大きくなり、図中の矢印 P 72 で示したように、白表示状態から黒表示状態への遷移の際の液晶の応答速度が改善する。

#### 【0061】

10

20

30

40

50

なお、図9に示した白表示の際の通常駆動（負極）およびオーバードライブ駆動（負極）については、図9中の矢印P41, P42, P43に示したように、上記した白表示の際の通常駆動（正極）およびオーバードライブ駆動（正極）の場合と同様の動作となるため、説明を省略する。また、図示しない黒表示の際の通常駆動（負極）およびオーバードライブ駆動（負極）についても、上記した黒表示の際の通常駆動（正極）およびオーバードライブ駆動（正極）の場合と同様の動作となるため、説明を省略する。

#### 【0062】

このようにして本実施の形態の液晶表示装置1では、ゲート線Gにより供給されるゲートオン電圧V<sub>on</sub>によって駆動対象の画素20内のTFT素子Qが選択的にオン状態となると、ソース線SからこのTFT素子Qを介して映像信号D<sub>out</sub>が供給され、この映像信号D<sub>out</sub>に基づく電圧が、画素20内の液晶素子LCおよび補助容量素子Csの両端間にそれぞれ印加される。その後、ゲート線Gにより供給される複数種類のゲートオフ電圧V<sub>off1</sub>, V<sub>off2</sub>, V<sub>off3</sub>のうちの一のゲートオフ電圧（V<sub>off2</sub>またはV<sub>off3</sub>）によってTFT素子Qが選択的にオフ状態となると、ソース線Sからの映像信号D<sub>out</sub>の供給が停止され、液晶素子LCおよび補助容量素子Csの両端間の電圧が保持される。そしてその後にソース線Sに沿って線順次動作方向に隣接するゲート線である隣接ゲート線によって補助容量素子Csの他端（対向電極）に、複数種類のゲートオフ電圧の電位が時間変化しつつ供給されると、この補助容量素子Csおよび液晶素子LCの両端間の電圧が、映像信号D<sub>out</sub>に基づく電圧から変化する。

#### 【0063】

ここで、通常駆動の際には、現在のフレームの映像信号D1がその輝度レベルが所定の階調分だけ下がるように補正された後の映像信号D2を基に表示駆動がなされるため、このような補正後の映像信号D2に基づき、上記のように補助容量素子Csおよび液晶素子LCの両端間の電圧が変化した後に、これらの両端間にそれぞれ、補正前の映像信号D1に基づく本来の電圧値が印加されるように（オーバードライブ駆動がなされないように、つまり通常駆動がなされるように）調整可能となる。また、オーバードライブ駆動の際には、液晶素子LCの両端間の電圧変化が現在のフレームの映像信号D1に基づく本来の電圧変化よりも大きくなるような映像信号（補正後の映像信号D2）を基に表示駆動がなされるため、上記のように補助容量素子Csおよび液晶素子LCの両端間の電圧が変化した後に、これらの両端間にそれぞれ、補正前の映像信号D1に基づく本来の電圧値よりも大きな電圧値が印加され、これにより本来の電圧変化よりも大きくなるような表示駆動、すなわちオーバードライブ駆動がなされる。したがって、このような構成および作用により、本実施の形態では、駆動素子であるTFT素子Qの耐圧を上げることなく、液晶の応答速度を向上させることができるとなる。

#### 【0064】

具体的には、オーバードライブ処理部43が、現在のフレームの映像信号D1とその直前のフレームの映像信号D2とにに基づき、現在のフレームにおいて、通常駆動およびオーバードライブ駆動のうちのどちらによる表示駆動を行うのかを画素20ごとに判定すると共に、そのような判定結果に基づき、現在の単位フレームの映像信号D1を画素20ごとに補正するようにしたので、上記の効果を得ることができる。また、判定の際には、現在のフレームとその直前のフレームとの間の映像信号の輝度レベル差が所定の閾値以上の画素20に対し、オーバードライブ駆動による表示駆動を行うと判定する一方、輝度レベル差が閾値未満の画素に対し、通常駆動による表示駆動を行うと判定するようにしたので、上記の効果を得ることができる。

#### 【0065】

また、補正の際には、上記輝度レベル差が閾値以上の画素において、その輝度レベル差が大きくなるのに応じて液晶素子LCの両端間の電圧変化がより大きくなるように、現在のフレームの映像信号D1の補正を行うようにしたので、液晶の応答速度の改善の必要性に応じてオーバードライブ量の調整をすることができる。

#### 【0066】

10

20

30

40

50

また、オーバードライブ駆動の際に、黒表示状態から白表示状態へ遷移する画素においては、現在のフレームの映像信号D1をその輝度レベルを変化させずにそのまま用いて表示駆動を行うようにしたので、補助容量素子Csおよび液晶素子LCの両端間の電圧が変化した後にこれらの両端間にそれぞれ、補正前の映像信号D1に基づく白表示状態の本来の電圧値よりも大きな電圧値が印加されるため、これにより黒表示状態から白表示状態への遷移の際の本来の電圧変化よりも大きくなるような表示駆動、すなわち黒表示状態から白表示状態への遷移の際のオーバードライブ駆動を行うことが可能となる。

#### 【0067】

また、オーバードライブ駆動の際に、白表示状態から黒表示状態へ遷移する画素においては、現在のフレームの映像信号D1が通常駆動の際の補正よりも輝度レベルが過剰に下がるように補正された後の映像信号D2を基に表示駆動を行うようにしたので、補助容量素子Csおよび液晶素子LCの両端間の電圧が変化した後にこれらの両端間にそれぞれ、補正前の映像信号D1に基づく黒表示状態の本来の電圧値よりも小さな電圧値が印加されるため、これにより白表示状態から黒表示状態への遷移の際の本来の電圧変化よりも大きくなるような表示駆動、すなわち白表示状態から黒表示状態への遷移の際のオーバードライブ駆動を行うことが可能となる。

#### 【0068】

さらに、通常駆動の際ににおいて、液晶素子LCの両端間の電圧が安定状態となったときに、補正後の映像信号D2に基づく輝度レベルが補正前の映像信号D1に基づく輝度レベルと同等となっているようにしたので、補助容量素子Csおよび液晶素子LCの両端間の電圧が変化して液晶素子LCの両端間の電圧が安定状態となったときに、補正前の映像信号D1に基づく輝度レベルと同等の輝度レベルとなっているため、通常駆動の際の輝度レベルが変化しないように（すなわち、表示輝度の変動を伴わないように）調整しつつ、オーバードライブ駆動を行うことが可能となる。

#### 【0069】

以上、実施の形態を挙げて本発明を説明したが、本発明はこの実施の形態に限定されるものではなく、種々の変形が可能である。

#### 【0070】

例えば、上記実施の形態では、液晶表示パネル2内の各画素回路ユニットをいわゆるライン反転により表示駆動する場合について説明したが、例えば、いわゆるフレーム反転やドット反転により表示駆動するようにしてもよい。具体的には、ドット反転により表示駆動する場合には、例えば図12に示した液晶表示パネル2Aを備えた液晶表示装置1Aのように、上記実施の形態のゲートドライバ52に対応する2つのゲートドライバ52A, 52Bを設けると共に、この液晶表示パネル2A内の各画素21において、例えば図13に示したように、隣接する画素21間で交互に2つのゲート線Ga(ゲートドライバ52Aに接続されたもの), Gb(ゲートドライバ52Bに接続されたもの)がTFT素子Qおよび補助容量素子Csに接続されると共に、これらゲート線Ga, Gbに沿って隣接する画素21同士およびソース線Sに沿って隣接する画素21同士でそれぞれ互いに逆極性の電圧が液晶素子LCの両端間に印加されるように（ドット反転となるように）表示駆動を行うようにすればよい。

#### 【0071】

さらに、上記実施の形態では、DC/DCコンバータ46により3種類のゲートオフ電圧Voff1, Voff2, Voff3を生成すると共にこれら3種類のゲートオフ電圧Voff1, Voff2, Voff3を用いてゲートドライバ52がゲート電圧を生成する場合（4値駆動）について説明したが、ゲートオフ電圧の種類の数についてはこれには限られず、例えば4種類以上のゲートオフ電圧を用いるようにしてもよい。

#### 【図面の簡単な説明】

#### 【0072】

【図1】本発明の一実施の形態に係る液晶表示装置の全体構成を表すブロック図である。

【図2】図1に示した各画素内に形成された画素回路ユニットの詳細構成を表す回路図で

10

20

30

40

50

ある。

【図3】図1に示したオーバードライブ処理部において用いられるルックアップテーブルの一例を表す図である。

【図4】図1に示したゲートドライバに含まれるシフトレジスタ部の構成を表す回路図である。

【図5】図1に示したゲートドライバに含まれる出力部の構成を表す回路図である。

【図6】ゲートドライバの動作を説明するためのタイミング波形図である。

【図7】オーバードライブ処理部の動作を説明するための流れ図である。

【図8】オーバードライブ処理部の動作を説明するためのタイミング図である。

【図9】オーバードライブ処理部の動作を説明するためのタイミング波形図である。

【図10】オーバードライブ処理部の動作を説明するための他のタイミング波形図である。

【図11】オーバードライブ駆動時の液晶素子への印加電圧を表すタイミング波形図である。

【図12】本発明の変形例に係る画像表示装置の全体構成を表すブロック図である。

【図13】図12に示した各画素内に形成された画素回路ユニットの詳細構成を表す回路図である。

#### 【符号の説明】

#### 【0073】

1 , 1 A ... 液晶表示装置、 2 , 2 A ... 液晶表示パネル、 2 0 , 2 0 ( m , n ) , 2 0 ( m + 1 , n ) , 2 0 ( m , n - 1 ) , 2 0 ( m , n + 1 ) , 2 0 ( m + 1 , n + 1 ) , 2 1 , 2 1 ( m , n ) , 2 1 ( m + 1 , n ) , 2 1 ( m , n - 1 ) , 2 1 ( m , n + 1 ) , 2 1 ( m + 1 , n + 1 ) ... 画素、 3 ... バックライト部、 4 ... タイミングコントローラ、 4 1 ... I / O 部、 4 2 ... 信号処理部、 4 3 ... オーバードライブ処理部、 4 4 ... フレームメモリ、 4 5 ... 基準電源部、 4 6 ... D C / D C コンバータ、 5 1 ... ソースドライバ、 5 1 1 ... D / A 変換部、 5 1 2 ... 演算部、 5 1 3 ... 電源部、 5 1 4 ... 補助容量電圧生成部、 5 2 , 5 2 A , 5 2 B ... ゲートドライバ、 5 2 1 ... シフトレジスタ部、 5 2 2 ... 出力部、 6 ... バックライト駆動部、 7 ... ルックアップテーブル ( L U T ) 、 D in ... 入力映像信号、 D 1 ... 信号処理後の映像信号、 D 2 ... 補正後 ( 処理後 ) の映像信号、 D out ... ソースドライバへ供給される出力映像信号、 V c c ... 電源電圧、 V r e f ... 基準電圧、 V on ... ゲートオン電圧、 V off1 , V off2 , V off3 ... ゲートオフ電圧、 L C ... 液晶素子、 C s ... 補助容量素子、 Q 1 ... T F T 素子、 L 1 ... 接続線、 G ( n ) , G ( n + 1 ) , G a ( n ) , G a ( n + 1 ) , G b ( n ) , G b ( n + 1 ) ... ゲート線 ( 補助容量線 ) 、 S ( m ) , S ( m + 1 ) ... ソース線、 V C O M ... コモン電極、 F F 0 ~ F F 5 ... フリップフロップ回路、 S W 1 ~ S W 4 ... アナログスイッチ部、 C P V ... パルス信号 ( クロック信号 ) 、 S T V , S T V 1 ~ S T V 4 ... ストローブ信号、 V G ( 1 ) ~ V G ( 3 ) ... ゲート電圧、 t 0 ~ t 5 ... タイミング。

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図 10】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 2 F    1/133    5 5 0

G 0 9 G    3/20    6 4 1 P

(56)参考文献 特開平09-258169 (JP, A)

国際公開第2006/112110 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G    3 / 0 0    -    3 / 3 8

G 0 2 F    1 / 1 3 3