(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-243946

(P2007-243946A)

(43) 公開日 平成19年9月20日(2007.9.20)

(51) Int.C1.

HO3F 3/72

(2006.01)

F 1

HO3F 3/72

テーマコード(参考)

5J500

審査請求 未請求 請求項の数 35 O L (全 19 頁)

(21) 出願番号 特願2007-48614 (P2007-48614)

(22) 出願日 平成19年2月28日 (2007.2.28)

(31) 優先権主張番号 60/780018

(32) 優先日 平成18年3月6日 (2006.3.6)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 06115534.7

(32) 優先日 平成18年6月15日 (2006.6.15)

(33) 優先権主張国 歐州特許庁(EP)

(71) 出願人 000002369

セイコーホーリング株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100127661

弁理士 宮坂 一彦

(72) 発明者 ホセ ルイス ゴンザレス ヒメネス

スペイン国バルセロナC/ホルディ ヒロ

ナ、1-3 カンプスノルドエディフィシオ

C4 カタロニア工科大学電子工学部内

(72) 発明者 ディエゴ メテオ ベニヤ

スペイン国バルセロナC/ホルディ ヒロ

ナ、1-3 カンプスノルドエディフィシオ

C4 カタロニア工科大学電子工学部内

最終頁に続く

(54) 【発明の名称】低電力の超広帯域インパルス無線受信機のための低雑音増幅器

## (57) 【要約】

【課題】低電力で高い利得を得る低雑音増幅器を提供する。

【解決手段】本発明は、オン/オフ切り替え機能を含み、好ましくは超帯域(UWB)インパルス無線(IRD)受信機に適用される低電力低雑音増幅器(LNA)に関する。本発明では、長いオン期間の間に最良の利得を供給するため、非常に低電力で高い利得の共通ゲートの静電性クロスカップリングカスケードLNAが提案されている。本発明は、また、迅速なオン/オフ切り替えを実施する目的で、より短い受信パルス幅のための共通ソースカスコードLNAも提供している。第1及び第2増幅段が、第1段の整合ネットワークと干渉しないように、入力信号は、第1増幅段に印加され、切り替え手段は、第2増幅段に接続されている。本発明は、また、複数の低雑音増幅素子を用いて、無線周波数信号を増幅する方法に関する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

互いに接続され、共同して入力信号を増幅する第1及び第2増幅素子と、当該低雑音増幅器をオン及びオフ切り替えする切り替え手段とを備える第1回路ブランチを有し、

前記第1増幅素子は、前記入力信号を受信する入力ノードを有し、

前記切り替え手段は、前記第2増幅素子にのみ接続され、前記第2増幅素子に作用することによって、当該低雑音増幅器をオン及びオフ切り替えすること

を特徴とする低雑音増幅器。

**【請求項 2】**

前記第1増幅素子の出力端子は、前記第2増幅素子の入力端子に接続され、前記低雑音増幅器の出力ノードは、第2増幅素子に接続されていること

10

を特徴とする請求項1に記載の低雑音増幅器。

**【請求項 3】**

前記第1増幅素子は、第1共通ゲートトランジスタであり、前記第2増幅素子は、第1共通ソーストランジスタであり、前記第1共通ゲートトランジスタのドレインは、前記第1共通ソーストランジスタに接続されていること

20

を特徴とする請求項1又は請求項2に記載の低雑音増幅器。

**【請求項 4】**

前記第1共通ソーストランジスタのゲートは、前記第1共通ゲートトランジスタのドレインに、第1インピーダンスを介して接続され、前記第1インピーダンスの値は、前記第1共通ゲートトランジスタの前記ドレインにおける信号の少なくとも一部が前記第1共通ソーストランジスタの前記ゲートに入力するように選択され、前記第1共通ソーストランジスタのソースは、前記第1共通ゲートトランジスタの前記ドレインと第2インピーダンスを介して接続され、前記第2インピーダンスの値は、前記第1共通ゲートトランジスタの前記ドレインにおける信号の少なくとも一部が前記第1共通ソーストランジスタに入力するのを防ぐように選択されていること

20

を特徴とする請求項3に記載の低雑音増幅器。

**【請求項 5】**

前記第1インピーダンスは、カップリングコンデンサであり、前記第2インピーダンスは、チョークインダクタであること

30

を特徴とする請求項4に記載の低雑音増幅器。

**【請求項 6】**

バイパスコンデンサが前記第1共通ソーストランジスタの前記ソースとグラウンドとの間に接続されていること

20

を特徴とする請求項3乃至請求項5のいずれか一項に記載の低雑音増幅器。

**【請求項 7】**

第1誘導インピーダンスは、前記第1共通ゲートトランジスタのソースとグラウンドとの間に接続されていること

20

を特徴とする請求項3乃至請求項6のいずれか一項に記載の低雑音増幅器。

**【請求項 8】**

前記第1共通ソーストランジスタのドレインは、チョークインダクタを介してDC電源に接続されていること

40

を特徴とする請求項3乃至請求項7のいずれか一項に記載の低雑音増幅器。

**【請求項 9】**

前記第1回路ブランチと差動増幅器を形成する前記第1回路ブランチと対称の第2回路ブランチを備え、第2回路ブランチは、カスケード構造で接続されている第2共通ゲートトランジスタと、第2共通ソーストランジスタとを備え、前記第1及び第2共通ゲートトランジスタは、差動クロスカップリング入力スキームを備え、入力信号を当該低雑音増幅器に供給すること

20

を特徴とする請求項1乃至請求項8のいずれか一項に記載の低雑音増幅器。

10

20

30

40

50

**【請求項 10】**

前記クロスカップリング入力スキームは、直列に接続された第1及び第2コンデンサを備えること

を特徴とする請求項9に記載の低雑音増幅器。

**【請求項 11】**

前記第1コンデンサは、前記第1共通ゲートトランジスタの前記ゲートと前記第2共通ゲートトランジスタの前記ソースとの間に接続され、前記第2コンデンサは、前記第2共通ゲートトランジスタの前記ゲートと前記第1共通ゲートトランジスタの前記ソースとの間に接続され、当該低雑音増幅器の入力ノードは、前記第1及び第2共通ゲートトランジスタの前記ソースに接続されていること

10

を特徴とする請求項9又は請求項10に記載の低雑音増幅器。

**【請求項 12】**

前記第1増幅素子は、第3共通ソーストランジスタであり、前記第2増幅素子は、第3共通ゲートトランジスタであり、両トランジスタは、カスケード構造で接続されるよう、前記第3共通ゲートトランジスタのソースは、第3共通ソーストランジスタのドレインに接続されていること

を特徴とする請求項1又は請求項2に記載の低雑音増幅器。

**【請求項 13】**

当該低雑音増幅器の入力ノードは、前記第3共通ソーストランジスタのゲートに接続され、当該低雑音増幅器の出力ノードは、前記第3共通ゲートトランジスタのドレインに接続されていること

20

を特徴とする請求項12に記載の低雑音増幅器。

**【請求項 14】**

前記入力ノードは、誘導インピーダンスを介して前記第3共通ソーストランジスタに接続され、前記誘導インピーダンスの値は、入力インピーダンスに整合するよう、選択されること

を特徴とする請求項12又は請求項13に記載の低雑音増幅器。

**【請求項 15】**

前記第3共通ゲートトランジスタの前記ドレインは、チョークインダクタを介してDC電源に接続されていること

30

を特徴とする請求項12乃至請求項14のいずれか一項に記載の低雑音増幅器。

**【請求項 16】**

前記低雑音増幅器は、差動増幅器を形成するように前記第1回路ブランチと対象の第3回路ブランチを備えること

を特徴とする請求項12乃至請求項15のいずれか一項に記載の低雑音増幅器。

**【請求項 17】**

前記切り替え手段は、レジスタを介して前記第1及び第2共通ソーストランジスタの前記ゲートに接続され、前記レジスタの値は、前記第1及び第2共通ソーストランジスタの前記ゲートにおける信号の少なくとも一部が前記切り替え手段に入力するのを防ぐよう、選択されること

40

を特徴とする請求項3乃至請求項11のいずれか一項に記載の低雑音増幅器。

**【請求項 18】**

前記切り替え手段は、前記共通ソーストランジスタの前記ゲートに直接接続されていること

を特徴とする請求項12乃至請求項16のいずれか一項に記載の低雑音増幅器。

**【請求項 19】**

前記切り替え手段は、スイッチとして動作するようになされた1対の補足トランジスタを備えること

を特徴とする請求項17又は請求項18に記載の低雑音増幅器。

**【請求項 20】**

50

前記切り替え手段は、pMOSトランジスタ及びnMOSトランジスタを備え、前記pMOS及びnMOSトランジスタのドレインは、前記共通ソーストランジスタに接続され、前記pMOS及びnMOSトランジスタのゲートは、制御ノードに接続されており、前記pMOSトランジスタのソースは、DC電源に接続され、前記nMOSトランジスタのソースは、グラウンドに接続されていること

を特徴とする請求項3、請求項17のうちのいずれかに記載の低雑音増幅器。

【請求項21】

前記切り替え手段は、前記pMOSトランジスタ及び前記nMOSトランジスタを備え、前記pMOS及びnMOSトランジスタのドレインは、前記共通ゲートトランジスタのゲートに接続されており、前記ゲートは、制御ノードに接続され、前記pMOSトランジスタの前記ソースは、DC電源に接続され、前記nMOSトランジスタの前記ソースは、グラウンドに接続されていること

10

を特徴する請求項12、請求項18のうちのいずれかに記載の低雑音増幅器。

【請求項22】

前記切り替え手段は、制御ノードに印加される矩形信号によって動作可能であること

を特徴とする請求項17乃至請求項21のいずれか一項に記載の低雑音増幅器。

【請求項23】

前記トランジスタは、CMOS技術において実装されること

を特徴とする請求項3乃至請求項22のいずれか一項に記載の低雑音増幅器。

20

【請求項24】

インパルス無線超広帯域システムIR-UWBにおいて動作するよう適応されること

を特徴とする請求項1乃至請求項23のいずれか一項に記載の低雑音増幅器。

【請求項25】

およそ8GHzの中央周波数を有する帯域内で動作するよう適応されること

を特徴とする請求項1乃至請求項24のいずれか一項に記載の低雑音増幅器。

【請求項26】

およそ-3dBの帯域幅を有すること

を特徴とする請求項25に記載の低雑音増幅器。

【請求項27】

無線信号を受信するアンテナに接続され、前記アンテナによって受信される信号を増幅する請求項1乃至請求項26のいずれか一項に記載の低雑音増幅器を含む、インパルス無線受信機。

30

【請求項28】

請求項1乃至請求項26のいずれか一項に記載の低雑音増幅器の少なくとも1つを含む半導体チップを有する集積回路。

【請求項29】

請求項1乃至請求項26のいずれか一項に記載の低雑音増幅器を含む無線通信機器。

【請求項30】

互いに接続され、共同して無線周波信号を増幅する複数の増幅素子を用いて前記無線周波信号を増幅する方法において、

40

無線周波信号パルスフレームを受信する工程と、

前記受信信号を増幅素子に入力する工程と、

前記無線周波信号パルスフレームの期間と略同等の時間ウィンドウの期間にのみ、増幅器をオン切り替えする工程とを含み、

前記無線周波信号パルスフレームは、第1増幅素子に印加され、前記増幅器は、前記第1増幅素子に接続された第2増幅素子に作用することによって、オン及びオフ切り替えされること

を特徴とする方法。

【請求項31】

前記第1増幅素子からの出力信号は、入力信号として前記第2増幅素子に印加されるこ

50

と

を特徴とする請求項 3 0 に記載の方法。

【請求項 3 2】

前記第 1 増幅素子は、共通ゲートトランジスタであり、前記第 2 増幅素子は、共通ソーストランジスタであり、前記共通ゲートトランジスタの前記ドレインにおける前記信号は、前記共通ソーストランジスタの前記ゲートに印加されること

を特徴とする請求項 3 0 又は請求項 3 1 に記載の方法。

【請求項 3 3】

前記共通ソーストランジスタは、自身のゲート端子に印加されるバイアスに作用することによって、オン及びオフ切り替えされること

を特徴とした請求項 3 2 に記載の方法。

【請求項 3 4】

前記第 1 増幅素子は、共通ソーストランジスタであり、前記第 2 増幅素子は、カスケード構造で接続された共通ゲートトランジスタであること

を特徴とした請求項 3 0 又は請求項 3 1 に記載の方法。

【請求項 3 5】

前記共通ゲートトランジスタは、自身のゲート端子に印加されるバイアスに作用することによって、オン及びオフ切り替えされること

を特徴とする請求項 3 4 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、好ましくは超広帯域 (UWB) インパルス無線 (IR) 受信機に用いられる、オン / オフ切り替え機能を備えた低雑音増幅器 (LNA) に関する。

【0 0 0 2】

本発明において、超低電力及び高利得の共通ゲート増幅器が提案される。この第 1 の LNA は、長いオン期間の間に最適利得を提供するので、パルス長が充分な長さ (数ナノ秒の範囲内) になったときにこのトポロジの最大効果が得られる。

【0 0 0 3】

本発明はまた、充分に高速のオン / オフ切り替えの実行を目的として、より短い受信パルス幅用の第 2 の LNA を提供する。

【0 0 0 4】

LNA が継続的に動作する場合 (例えば、無限オン期間)、同じ電力消費量に対して、第 2 の LNA の利得は第 1 の LNA よりも低い。しかしながら、オン / オフ切り替え技術が適用された場合、第 2 のトポロジは、より短いオン期間の間により高い利得を実現し、より高速のデータレートに適することを示している。

【0 0 0 5】

本発明はまた、低雑音増幅を提供する構造を備えた複数の能動素子及び受動素子を用いて無線周波数信号を増幅させる方法にも関する。

【背景技術】

【0 0 0 6】

アメリカ合衆国連邦通信委員会 (FCC) による文書、FFC, 「First Report And Order: Revision of the part 15 of the commission's ultra-wideband transmissions system」FCC, ET Docket 98-153, 2002 年 4 月の公開後、超広帯域 (UWB) 通信技術の近距離・高速データレートの無線通信への適用に注目が高まっている。そのような UWB システムのインパルス無線 (IR) への実装は、その低複雑度、低消費電力、低コスト、高速データレート、及び他の無線システムとの共存能力に起因して、関心を引く候補となっている。

【0 0 0 7】

10

20

30

40

50

その通常の実現において、IR-UWB送信機は、タイミング回路によって一様に始動されるパルス発生器を含み、IR-USBは、一定周期の極短パルスの授受に基づいている。パルス発生器の出力は、アンテナに直接接続されている。UWBの送信電力は非常に低いため、電力増幅器は不要である。パルスのいくつかのパラメーター（例えば、BPSK変調におけるサインやPPM変調における位置）を修正することによって、データは送信される。通常のデータレートでは数ナノ秒間を有する各フレームでサブナノ秒パルスが送られるため、送信出力波形は、非常に小さいデューティサイクルを有する。

#### 【0008】

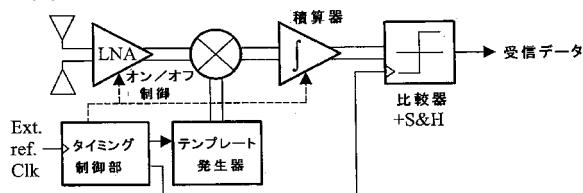

時間ホッピング（TH）技術は、複数のユーザのアクセスを可能にし、UWB信号のスペクトルにおけるピークを回避するために、一般的に用いられている。擬似ランダムコードは、異なる位置における連続するパルスのそれぞれに、そのフレームに沿って見られる。IR-UWB受信機は、いくつかの方法によって実装されるが、本発明は、近距離（BAN（Body Area Network）アプリケーションにおいては、1メートル以下）用の低電力実装に注目する。このようなIR-UWB受信機を実現可能な構造を、図2に示す。

#### 【0009】

この構造は、局地的に発生したテンプレート波形を有する受信信号の遅倍結果をまとめた後の出力データシンボルを決定するコヒーレント受信機に対応する。アンテナのインピーダンスを入力に合わせ、充分な利得を供給して受信機のチェーンの雑音を最小化するために、低雑音増幅器（LNA）が入力に必要である。LNAは自ら、受信信号に低雑音を付加しなければならない。

#### 【0010】

受信波形は極小のデューティサイクルを有するため、パルス受信時に、LNA、乗算器、又は積算器などのブロックは、継続的に作動する必要はない。これらブロックに巧妙なオン／オフ切り替えを適用することにより、電力消費の重要な節約をすることができる。さらに、（同一のチップに集積される）受信機のデジタル部分から連結した基板雑音の影響を最小化し、オン／オフ切り替え信号自身の連結による好ましくない影響を軽減するため、受信機のチェーンは、完全に差動になるよう設定される。

#### 【0011】

バーストモードで起動する他のシステムでは、パルスが到達すると期待されるときのみ、IR-UWB受信機のフロントエンドは理想的に作動することができる。LNAのオン／オフ切り替えは、大きな節電を可能にする技術として知られている。例えば、デュレーションが1ナノ秒でデータレートが100Mbpsの受信パルスを仮定すると、パルス時間のみフロントエンドブロックがオンに切り替えられた場合、理想的には90%の電力低減が実現される。実際には、LNAは、パルス到達時には完全に安定しているよう、パルス受信に先立ってしばらくオンに切り替えられていないといけないので、節約される電力はそれほど高くはない。

#### 【0012】

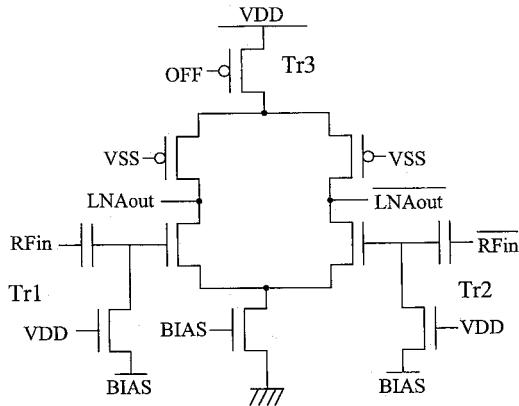

電源スイッチを有するLNAは、IEEE Journal 0-7803-8251-X/2004の「Transceivers circuits for pulse-based ultra-wideband」という題名の技術論文にて記述されている。図1は、上述の論文に記述されている、電源スイッチを有するLNAのアナログ回路を示し、パルスに基づくUWBの不連続特性の利点である、バイアス電流の切り替えによって電力消費を低減する。

#### 【0013】

図1のLNAは、デジタル電源（VDD）とグラウンド（GND）との間の電流を中断せざるよう、能動素子のゲートに作用することによって、各ブランチの能動素子のうちの1つをオフ及びオンに切り替える技術を用いている。NMOSカスコード／カスケードトランジスタのゲートは、オン状態で、VDDから直流電力が印加されるため、通常、NMOSカスコード／カスケードトランジスタを用いて上述の電流中断がなされる。オフ状態でグラウンドまでショートすることによって、増幅器の出力が効果的に落とされる。よ

り具体的には、図1のLNAにおいて、RF入力信号(RFin)を受信するトランジスタ(Tr1), (Tr2)のゲートとグラウンドとを接続することによって、回路の出力が落とされる。この切り替えスキームにおいて、オン/オフ切り替えを実行するのに用いられるトランジスタ(Tr1), (Tr2)は、入力信号バス及び入力整合回路と干渉し、結果的にLNAの利得及び線形性にマイナスに作用する。トランジスタ(Tr3)は、増幅器全体を電力供給から切斷するために用いられる。

#### 【0014】

一方、静電性のクロスカップリング(CCC)技術は、差動増幅段の動作を向上させるものとして知られている。このCCC技術の詳細は、Wei Zhou氏、Sherif Embabbi氏、Jose Pineda de Gyvez氏、及びEdgar Sanchez Sinencio氏、「Using Capacitive Cross-Coupling Technique in RF Low Noise Amplifiers and Down-Conversion Mixer Design」、the Proceeding of the European Solid-State Circuits Conference (ESSCIRC)、2000年9月10~21日、77~80頁、及びDavid J. Allstot氏、Xiaoyong Li氏、及びSuip Shekhar氏、「Design Consideration for CMOS Low-Noise Amplifier」、IEEE Radio Frequency Integrated Circuits Symposium (RFIC)、2004年、97~100頁などの論文に載っている。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0015】

本発明は、UWBシステム、好ましくは、コヒーレントIR-UWB受信機のための低雑音増幅器LNAを提供する。LNAの差動出力に加えて、その簡単な構造によって実現される低電力動作によって、LNAは、例えばスマートタグ、センサーネットワーク、またはボディーエリアネットワーク(BAN)通信アプリケーション用の、低成本、低電力、及び適度なデータレートの单一チップIR-UWB送受信機を実現する候補となる。

30

#### 【課題を解決するための手段】

#### 【0016】

本発明によれば、低雑音増幅器は、互いに接続され、共同して入力信号を増幅する、少なくとも第1及び第2増幅素子を有し、第1の増幅素子は、前記入力信号を受信する入力ノードを有し、切り替え手段は、第2増幅素子と接続され、前記第2増幅素子を残りのLNAの構成要素と共にオン及びオフ切り替えすることによって、LNA全体をオン及びオフ切り替えする。それゆえ、入力信号を受信しない増幅素子をオン及びオフ切り替えすることによってのみ、LNAはオン及びオフ切り替えされる。

#### 【0017】

第1増幅段又は素子の出力端子は、第2増幅素子の入力端子に接続され、第1増幅素子によって増幅された信号は、続いて第2増幅素子によって増幅される。増幅器の出力ノードは、第2増幅素子に接続されている。

40

#### 【0018】

本発明において、増幅されるべき入力信号は、第1増幅段に印加される一方で、第2増幅段のみオン/オフ切り替えされ、切り替え手段は、第1増幅段の入力整合回路と干渉しない。

#### 【0019】

本発明によれば、能動及び受動素子を用いて無線周波数信号を増幅する方法は、低雑音増幅を提供する構造を有する。この方法は、無線周波数信号パルスフレームの受信、受信信号の増幅素子への入力、及び前記無線周波数信号パルスフレームの期間と略同一期間で

50

ある時間ウィンドウの期間のみの増幅器のオン切り替えから成り、無線周波数信号パルスフレームは、第1増幅素子に印加され、前記第1増幅素子に接続された第2増幅素子に作用することによって、増幅器はオン及びオフ切り替えされる。

#### 【0020】

本発明の方法において、第1増幅素子からの出力信号は、入力信号として第2増幅素子に印加され、両増幅素子は、共同して前記信号を増幅させる。好ましくは、第1増幅素子は、共通ゲートトランジスタであり、第2増幅素子は、共通ソーストランジスタであり、共通ゲートトランジスタのドレインにおける信号は、共通ソーストランジスタのゲートに印加される。共通ソーストランジスタは、そのゲート端子に印加されるバイアスに作用することによって、オン及びオフ切り替えされる。

10

#### 【0021】

あるいは、第1増幅素子は、共通ソーストランジスタであり、第2増幅素子は、カスコード構造に接続された共通ゲートトランジスタである。増幅器は、共通ゲートトランジスタのゲート端子に印加されるバイアスに作用することによって、オン及びオフ切り替えされる。

#### 【0022】

低雑音増幅器が低電力で高い利得を得られるようになる。

#### 【発明を実施するための最良の形態】

#### 【0023】

本発明の特徴は、本発明の望ましい実施例を示す添付図面を参照することにより、より良好に理解される。

20

#### 【0024】

狭帯域干渉は、IR-UWBシステムにおいて最も制限のある要因であることが知られている。通常適用されるアーキテクチャー上の解決策は、受信における干渉（例えば、2.4及び5GHzのISM帯域において動作する無線システムが原因の干渉）を、できるだけ多くフィルターにかけることである。そのようなフィルターにかけることは、干渉の周波数前後のパルスのエネルギーのいくつかを失うことを意味する。

#### 【0025】

本発明の好適な実施例において、8GHzの中心周波数は、増幅器に適用され、-3dB帯域幅を1GHzに制限し、密集した2.4GHz及び5GHz帯域を回避している。上述した干渉の影響を弱めるために、本発明では、共振挙動を備えた2つのLNAが設計されている。UWBアプリケーションにおいて意外なことであるようだが、結果として得られた通過帯域は、エネルギーが8GHzに集中しているパルスを適切に受信するに充分な広さを有する。

30

#### 【0026】

LNAに一般に要求される最も重要な特徴は、低雑音、高利得、及び許容可能な線形性である。要求される電力消費は、アプリケーションによって強く左右される。通信システムが、好ましくは、エネルギー収集技術によるセンサネットワーク又はBANデバイスにおいて集約された本発明において、利得に加え、電力消費及び上述した中心周波数が、最も重要な設計制約である一方で、許容可能な雑音係数（最低係数でなく）は充分である。

40

#### 【0027】

[共通ゲート静電性クロスカップリングカスケード低雑音増幅器、CG-CCC-LNA]

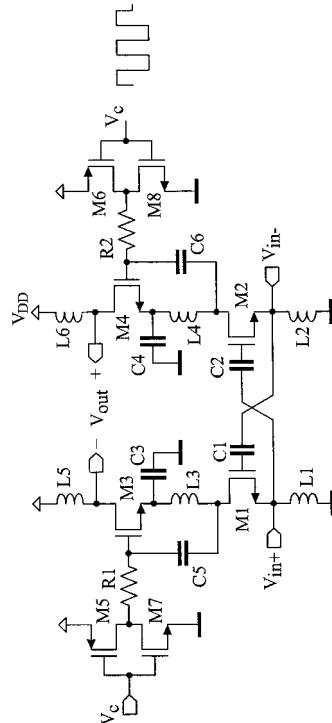

これら全ての問題を念頭におき、本発明の第1の好適な設計を図3に示す。第1LNAは、差動増幅器を実現する2つの対称な回路ブランチから成る。また、第1LNAは、それぞれ第1及び第2共通ゲートトランジスタ（M1, M2）のソースとグラウンドとの間に接続された第1インダクタ（L1）及び第2インダクタ（L2）とともに、第1トランジスタ（M1）及び第2トランジスタ（M2）（簡略化のため、自身のゲート中のバイアスレジスタは省略）から成る差動共通ゲート（CG）入力段を構成し、グラウンドへの信

50

号経路をチョークしている。

【0028】

このような CG 入力は、基本的に CG 段利得を向上させる第 1 コンデンサ (C1) 及び第 2 コンデンサ (C2) によって、静電性のクロスカップリング (CCC) 技術を可能にする。

【0029】

より具体的には、第 1 カップリングコンデンサ (C1) は、第 1 共通ゲートトランジスタ (M1) のゲートと第 2 共通ゲートトランジスタ (M2) のソースとの間に接続され、第 2 カップリングコンデンサ (C2) は、(M2) のゲートと (M1) のソースとの間に接続される。または、クロスカップリングスキームは、カップリングコンデンサを用いずに実施可能であり、トランジスタ (M1) のゲートは、トランジスタ (M2) のソースに直接接続され、トランジスタ (M2) のゲートは、トランジスタ (M1) のソースに直接接続される。

【0030】

CG 段の上部には、共通ソース (CS) 段が回路の第 1 及び第 2 差動ブランチに備えられている。この CS 段は、第 1 共通ソーストランジスタ (M3) として第 1 回路ブランチに配置される第 3 トランジスタと第 2 共通ソーストランジスタ (M4) として第 2 回路ブランチに配置される第 4 トランジスタとから成る。CS 段は、有効な電力消費節約技術として、CG 入力段の同一の DC 電流を再利用する。

【0031】

共通ゲートトランジスタ (M1, M2) のドレインは、第 1 インピーダンスを介してそれぞれ共通ソーストランジスタ (M3, M4) に接続し、共通ゲートトランジスタ (M1, M2) のドレインにおける信号を、共通ソーストランジスタ (M3, M4) のゲートへ接続させ、前記第 1 インピーダンスの値は、少なくとも一部分が選択されるようになっている。この配置において、AC 信号は、CG 段から CS 段へ印加され、両トランジスタは共同して入力信号をカスケード構造において増幅するようになっている。前記インピーダンスは、図 3 に示すように、好ましくはトランジスタ (M1, M3) の第 4 カップリングコンデンサ (C5) であり、トランジスタ (M2, M4) の第 6 カップリングコンデンサ (C6) である。

【0032】

さらに、第 2 インピーダンスは、共通ソーストランジスタ (M3, M4) のソースと共通ゲートトランジスタ (M1, M2) のドレインとの間に接続され、前記第 2 インピーダンスの値は、少なくとも一部分が選択され、共通ゲートトランジスタ (M1, M2) のドレインにおける信号の共通ソーストランジスタ (M3, M4) 内への入力を防ぐようになっている。前記第 2 インピーダンスは、好ましくは、トランジスタ (M1, M3) の第 3 チョークインダクタ (L3) とトランジスタ (M2, M4) の第 4 チョークインダクタ (L4) 内に存在する。

【0033】

バイパス第 3 及び第 4 コンデンサ (C3, C4) は、それぞれ、トランジスタ (M3, M4) のソースとグラウンドとの間に接続される。チョークインダクタ (L3, L4) 及びコンデンサ (C3, C4) は、前記 AC 信号がソースを介して CS 段内へ入力するのを防ぐ。

【0034】

切り替え手段は、インピーダンス、好ましくはレジスタ (R1, R2) を介して共通ソーストランジスタ (M3, M4) のゲートへ接続され、前記レジスタ (R1, R2) の値は、少なくとも一部分が選択され、共通ソーストランジスタ (M3, M4) のゲートにおける信号が切り替え手段に入力するのを防ぐようになっている。

【0035】

図 3 からも明らかなように、共通ソーストランジスタ (<3, M4) のドレインは、インピーダンス、好ましくは第 5 チョークインダクタ (L5) 及び第 6 チョークインダクタ

10

20

30

40

50

(L6)をそれぞれ介してDC電源に接続されている。

【0036】

入力ノード(Vin+, Vin-)は、第1及び第2共通ゲートトランジスタ(M1, M2)のソース端子にそれぞれ接続されており、出力ノード(Vout+, Vout-)は、第1及び第2共通ソーストランジスタ(M3, M4)のドレイン端子にそれぞれ接続されている。

【0037】

または、図3のLNAは、SSSスキームなしに実施可能であり、その場合、入力ノード(Vin+, Vin-)は、第1及び第2トランジスタ(M1, M2)のゲート端子に接続され、これらの端子は、共通ソーストランジスタとして配置される。

10

【0038】

また、本発明の他の好適な実施例では、図3のLNAは、もう1つの選択肢として、上述した図3の左(第1)及び右(第2)回路プランチに示されるトランジスタ(M2, M4)又はトランジスタ(M1, M3)及び付随するインピーダンスからのみ成り立つ単一の回路プランチを用いて実施可能であり、その場合、明らかにクロスカップリングスキームは利用できない。

【0039】

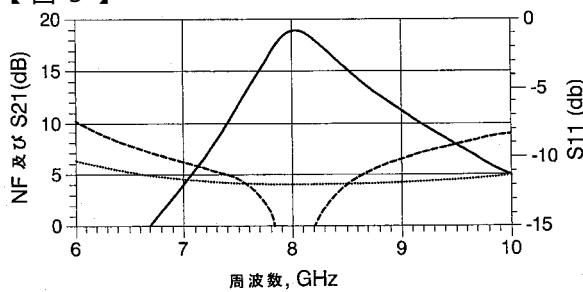

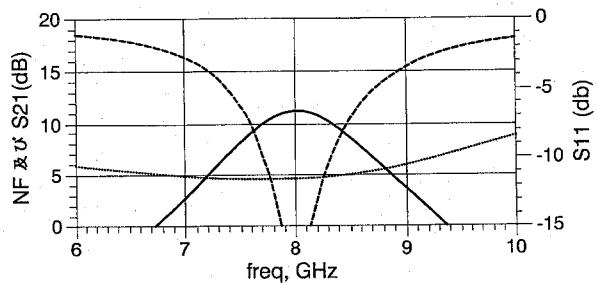

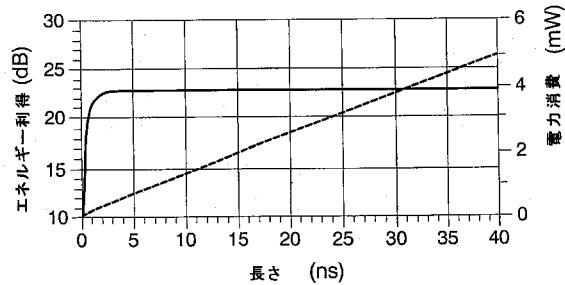

設計は、雑音や線形性ではなく、電力消費と利得を目的として最適化される。図5では、図3のLNAの電力利得(S21)が示され、-3dB帯域幅の1GHzへの制限とともに、8GHzでおよそ18dBの利得が得られることが伺える。中央周波数に対して、2.4GHzにおける減衰量は、73dBであり、5GHzにおいては、36.7dBである。LNAが自身の制限帯域幅によりパルス波形に起こす歪みは、システム全体の性能に影響を与えないことが証明されている。同図5ではまた、雑音指数が示されている。およそ4dBの値は、注目の帯域において得られる。図から明らかなように、良好な入力整合もまた実現される。最終的に、本例における継続的動作においてDC電力消費は、4.87mWである。

20

【0040】

[共通ソースカスコード低雑音増幅器、CSカスコードLNA]

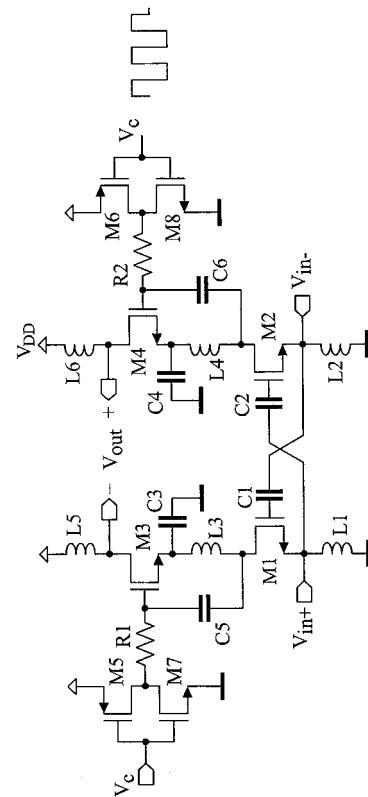

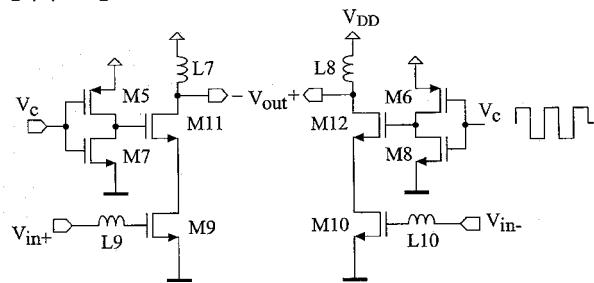

図4において、本発明における第2LNAトポロジが示されている。それは、負荷としてのチョーク第7及び第8インダクタ(L7, L8)を有する差動共通ソースカスコードLNAである。

30

【0041】

図4の回路における左のプランチにおいて、第9トランジスタは、第3共通ソーストランジスタ(M9)として配置され、第11トランジスタは、第3共通ゲートトランジスタ(M11)として配置されている。両共通ゲートトランジスタ(M9, M11)がカスコード構造において接続され、周知の方法で共同して入力信号を増幅するように、共通ゲートトランジスタ(M11)のソースは、共通ソーストランジスタ(M9)のドレインと接続されている。

【0042】

同様に、本回路における右のプランチにおいて、第10トランジスタは、第4共通ソーストランジスタ(M10)として配置され、第12トランジスタは、第4共通ゲートトランジスタ(M12)として配置されている。両共通ゲートトランジスタ(M10, M12)がカスコード構造において接続されるように、共通ゲートトランジスタ(M10)のソースは、共通ソーストランジスタ(M12)のドレインと接続されている。簡略化のため、トランジスタ(M9~M12)のバイアスレジスタは省略する。

40

【0043】

本実施例において、切り替え手段は、共通ソーストランジスタ(M11, M12)のゲート端子に直接接続されている。

【0044】

入力ポート(Vin+, Vin-)は、好ましくは共通ソーストランジスタ(M9, M

50

10) のゲートに接続されており、出力ポート ( $V_{out+}$ ,  $V_{out-}$ ) は、共通ゲートトランジスタ ( $M_{12}$ ,  $M_{11}$ ) のドレイン端子にそれぞれ接続されている。

【0045】

共通ゲートトランジスタ ( $M_{11}$ ,  $M_{12}$ ) のドレインは、それぞれチョークインダクタ ( $L_7$ ,  $L_8$ ) を介して DC 電源に接続されている。

【0046】

本発明の他の実施例では、図3のLNAは、もう1つの選択肢として、上述した図3の左(第1)及び右(第2)の左右対称な回路ブランチに示されるトランジスタ ( $M_9$ ,  $M_{11}$ ) 又はトランジスタ ( $M_{10}$ ,  $M_{12}$ ) 及び付随するインピーダンスからのみ成り立つ单一の回路ブランチを用いて実施可能である。

【0047】

本構造では、ゲートカスコードトランジスタ ( $M_{11}$ ,  $M_{12}$ ) のゲートは、信号経路に属さず(つまり、チョークレジスタが不要である)、ゲートにおいて、特別な電圧の使用が不要であるので、非常に高速でオン/オフ切り替えが可能であり、ゲートがグラウンドに接続している際は、LNAの出力を下げ、VDDに接続している際は、その出力を上げる。

【0048】

図8において、電力利得 (S21パラメータ)、雑音指数、及び反射計数 (S11パラメータ) が示されている。公正な比較を行うために、この第2LNAは、同一の継続的動作のDC電力を上述したLNA (4.87mW) よりも多く消費するよう設計されている。利得が上述したLNAより8dB低く、雑音指数はおよそ0.5dB高く、許容可能ではあるが入力整合はわずかに悪化したことが観測された。2.4GHzにおける減衰量(ピーク利得に比較して)は、42.3dBであり、5GHzにおいては、24.7dBである。つまり、同じ電力消費で、図3の第1LNAよりも性能が低い。

【0049】

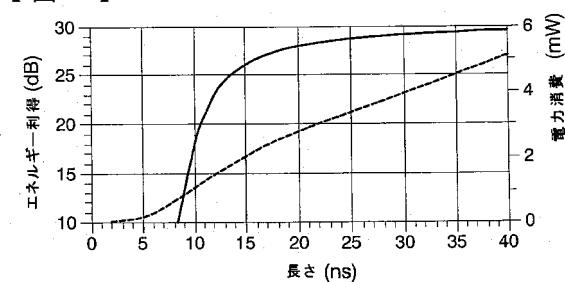

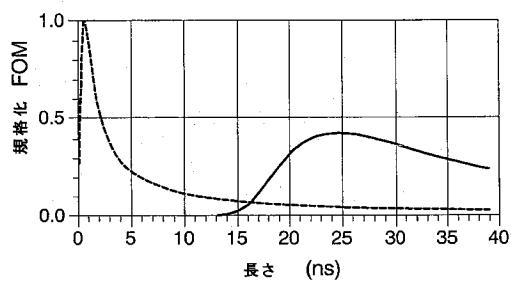

この代替トポロジの利点は、優れた性能を備え、迅速なオン/オフ切り替え技術を用いる特性である。図9は、オン/オフ技術が用いられた際の、前項において用いられたものと同一の入力信号及びオン期間においての、この第2LNAの電力消費及び利得曲線を示す。LNAがアグレッシブデューティサイクルを受ける際には、電力消費に関して同様の反応が観測されるが、利得に関してははるかに良い性能が得られた。例えば、オン期間がたった2ナノ秒であった際に、最大量の利得に対してたった1dBの利得が失われ、電力消費はたった0.4mWのみ低減される。

【0050】

アナログブロックをオフ及びオン切り替えする通常の方法は、増幅素子または増幅トランジスタである、各回路差動ブランチの能動素子うちの1つにおけるゲート上に作用することであり、VDDとGNDとの間の電流を中断させる。NMOSカスコード/カスケードトランジスタのゲートは、オン状態で、VDDから直流電力が印加されるため、通常、NMOSカスコード/カスケードトランジスタを用いて上述の電流中断がなされる。オフ状態でグラウンドまでショートすることによって、増幅器の出力が効果的に落とされる。例えば、図3に示されるLNAにおいては、トランジスタ ( $M_3$ ,  $M_4$ )、つまり入力信号を受信しないトランジスタをオフ切り替えすることによって出力が落とされる。

【0051】

本発明において、本技術を高周波増幅器に適用する際の主要問題のいくつかが考慮されている。まず第1に、中央周波数が非常に高いので、オン/オフ切り替えを行うために用いられるデバイスは、LNA利得に影響を及ぼす信号経路と干渉してはいけない。第2に、データレートが速い場合、ブロックは、エネルギー的に効果的にするために、切り替え手段に対して非常に高速で反応しなければならない。言い換えると、制御されるべきトランジスタのゲートは、低いインピーダンスノードであり、そうでなければ、切り替え手段は充分に高速ではないため、オン期間は増長されなければならず、結果として、節約される電力がより少なくなってしまう。

## 【0052】

図3のLNAにおいて、LNAトランジスタの全てのゲートは、信号を伝送する(CG段のゲートは、クロスカップリング技術において用いられ、CA段のゲートは、前のCG段の出力信号に接続されている)。これは、オン/オフ切り替えの実施を複雑化しているが、カスケードCS段の利得を制御することによって、納得いく結果が得られてきた(図3において、トランジスタM5M~7M及びM6~M9を形成するバッファ参照)。信号は、このノードを通るので、チャージレジスタ(R1, R2)は、バッファとCS段との間に接続され、LNA利得の損失を最小限にしている。これらのレジスタを最適な寸法にするため、制御信号(Vc)へのLNAの迅速な反応(R1, R2が低い値)とLNA利得の低い損失(R1, R2が高い値)との間において、トレードオフしなければならない。

10

## 【0053】

本発明の好適な実施例において、切り替え手段は、スイッチとして動作するように配置された1対の補足トランジスタから成る。具体的には、切り替え手段は、pMOS第5及び第6トランジスタ(M5, M6)及びnMOS第7及び第8トランジスタ(M7, M8)から成る。前記トランジスタのドレインは、共に接続され、前記トランジスタのゲートは、共に制御ノード(Vc)に接続されている。pMOSトランジスタ(M5, M6)のソースは、DC電源に接続され、nMOSトランジスタ(M7, M8)のソースは、グラウンドに接続されている。

20

## 【0054】

図3のLNAの場合、トランジスタ(M6, M8)のドレインは、第2トランジスタ(R2)を介してトランジスタ(M4)のゲートと接続され、トランジスタ(M5, M7)のドレインは、第1レジスタ(R1)を介してトランジスタ(M3)のゲートを介して接続されている。

## 【0055】

図4のLNAの場合、1対のトランジスタ(M6, M8)と1対のトランジスタ(M5, M7)のドレインは、トランジスタ(M12, M11)のゲートとそれぞれ直接に接続されている。

30

## 【0056】

上述の両LNAにおいて、切り替え手段は、周知の方法によって発生させられて制御ノード(Vc)に印加される矩形信号によって作動される。図3のLNAを例にとると、前記矩形信号(Vc = Vdd)の正の電圧値において、トランジスタ(M5, M6)は、電源が切られ、トランジスタ(M7, M8)は活性化され、その結果、トランジスタ(M3, M4)がオフに切り替わるよう、トランジスタ(M3, M4)のゲートは、グラウンドに接続される。前記制御矩形信号(Vc = GND)の負の電圧値において、トランジスタ(M3, M4)のゲートが電源VDDに接続されてオン切り替えされるように、トランジスタ(M5, M6)は活性化され、トランジスタ(M7, M8)は電源が切られる。

30

## 【0057】

それゆえ、切り替え手段は、図3のLNAに対して、トランジスタ(M3, M4)を活性化又はオフ切り替えするための、2つの機能を提供する。

40

## 【0058】

図4のLNAに適用される切り替え手段は、同一の方法によって動作される。

## 【0059】

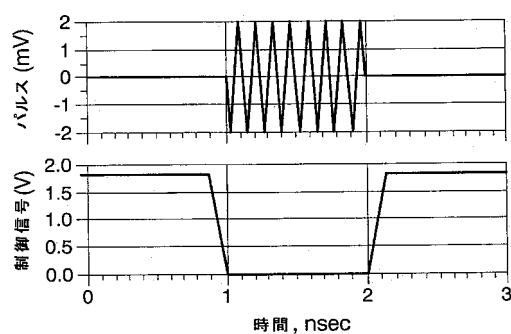

オン/オフ切り替え技術の効果は、入力信号として8GHz周波数と数サイクルの長さから成るパルスを用いたシミュレーションによって調査された。LNAは、パルス幅と同等の時間ウインドウの間(図6参照)、電源が入れられる。図7において、LNAによって消散された電力を示す。電力を計算するために考慮される積分期間は、最大限の使用されるウインドウ長であり、40ナノ秒である。同一の図において、切り替え状態におけるLNAの利得を示す。もはや利得は大きい信号規模であるため、パラメーターS21は、このような状況で、LNAオン/オフ作用により利得として利用できない。S21の代わ

50

りに、以下のように定義されるエネルギー利得 (Energy Gain) を利用することができる。

【0060】

【数1】

$$Energy\ Gain\ (dB) = 10 \log \left( \frac{\int V_{out}^2 dt}{\int V_{in}^2 dt} \right) \cdots \cdots (1)$$

10

【0061】

今回の継続的な動作における電力消費は、5.1 mW (切り替え回路の電力オーバーヘッドにより、4.87 mWよりわずかに大きいものとなっている) である。図7の電力消費曲線は、切り替え手段の適用によって得られた電力低減を明確に示している。例えば、電力消費は、0.5ナノ秒のウィンドウ長 (オン期間) の間、0.2 mWまで低減される。にもかかわらず、CSトランジスタの切り替えを制御するバッファ後に必要となるチヨークレジスタ (R1, R2) が原因で、切り替えが遅く、いくらかの利得を有するためには、オン期間はパルス幅よりはるかに長いものでなければならない。図7の利得曲線は、-3 dB以下の最大限からの利得低減を回避するために、オン期間は、15ナノ秒より長くなっていることを示し、電力消費は、期待していたものより2 mWだけ大きくならなければならず、3 mWのみだけ低減される。図4のLNAは、高データレートのための電力節約に関して、切り替え技術の効果を改善する。

20

【0062】

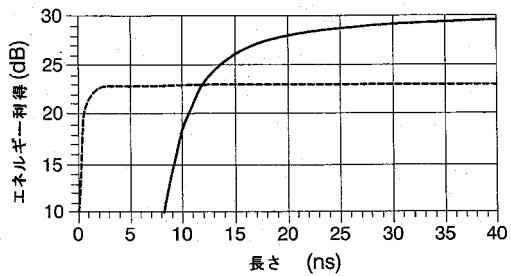

雑音指数及び適合は、両LNAにおいてあまり大差はないため、式(1)にて定義される利得及び電力消費のみ検討する。図10において、事前に得た両LNAのエネルギー利得と対応する同一の曲線は、共にグラフ化されている。CSカスコードLNAは、短いパルスの間、他方のLNAよりもはるかに良好に機能することが観測することができる (確かに、CGカスケードLNAは5ナノ秒以下のオン期間に作動しない)。しかし、パルス長がおよそ12ナノ秒以上である場合、CG-CCCCカスケードLNAは、CS-NLA似比べて、利得に関してより良好に機能し、7 dB以上まで達する。

30

【0063】

両LNAを、電力消費についても考慮して比較するために、以下の性能指数が定義される。

【0064】

【数2】

$$FOM = \frac{Energy\ Gain}{Dissipated\ Power}, \cdots \cdots (2)$$

40

【0065】

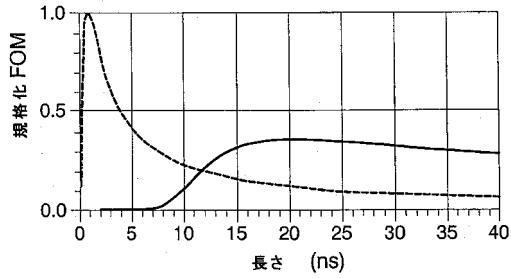

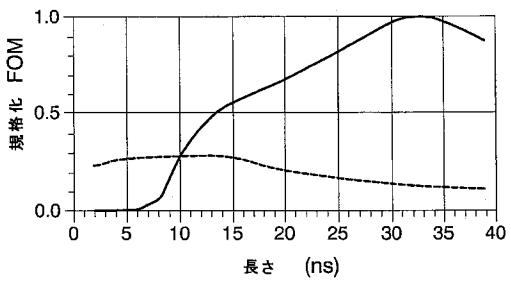

エネルギー利得 (式(1)として定義) 及び消散電力 (Dissipated Power) の両パラメータは、線形スケールとなる。図11において、この規格化されたFOMは、異なる入力パルス及びウィンドウ長に対して、グラフ化されている。この性能指数を用いて、利得から、CSカスコードLNAは短いパルス (数ナノ秒) に適し、CG-CCCCカスケードLNAは、より長いパルス (10ナノ秒以上) に適していることが導き出せる。また、CSカスコードLNAは、自身のより優れた電力消費節約によって、オン/オフ切り替え技術を通じてCG-CCCCカスケードLNAより良好に機能することを明言することができる

50

。

## 【0066】

異なるパルス幅（図面におけるパラメータ「長さ」）は、オン期間はパルス幅（図6参照）と同等であると想定し、今まで考慮されてきた。これは、パルスを検出する最良の方法が全てのパルスエネルギーを利用することだと考えると、妥当である。しかしながら、電力消費もまた考慮に入れると、興味深いトレードオフが現れる。受信パルスの任意の長さとして、検出のパルスエネルギー部分のみを利用し、より少ない利得を得る一方でより少ない電力を消費することも可能である。つまり、利得は、オン／オフ切り替え技術を用いて電力消費とトレードオフされる。

## 【0067】

固定受信パルスの長さを考慮し、受信ウィンドウの長さを変えつつも、同様のシミュレーションが行われた。図12において、750ピコ秒の短い受信パルスの場合も観測される。この場合、パルスの短さによりエネルギーを電力消費にトレードオフする可能性がないことから、図12は図11のグラフと大きな違いはない。15ナノ秒のより長い受信パルスを考慮すると、図13のグラフが得られる。CSカスコードLNAがいかに15ナノ秒以下に平坦領域を有するかが分かる（パルス長さのこの点の後、FOMは減少し、受信エネルギー増加なしに消散電力を増加させるので、LNNをパルス終了後に機能させ続けるのは明らかに無意味である）。

## 【0068】

性能指数を考慮した上で、そのような平坦領域は、つまり、利得を失う代償の代わりに、電力を節約するより短いオンウィンドウを利用することによって、LNAの性能がほとんど継続的に15ナノ秒以下となることを意味する。CG CCCカスケードLNAの正規化された性能指数を考察すると、より長いパルスの場合、そのようなLNAは、10ナノ秒以上のウィンドウ長のおかげで、より高い性能を得、ウィンドウ長は、受信ウィンドウがおよそ32ナノ秒になる（受信ウィンドウが減少し始める時）まで広がり続けるにつれ、ウィンドウ長も増加し続ける。これは、LNAの切り替えに対する反応の遅さが原因であり、切り替えへの反応を完全にするためには、15ナノ秒以上のパルス長を必要とする。

## 【0069】

両LNAの性能の比較は、その特質と共に表1に示す。比較は、多種多様な実施（0.13及び0.18μm技術、シングル及び差動出力、下限及び上限周波数帯域、継続的及びオン／オフ機能モード）のおかげで複雑なものとなつたが、その特質の全体像を示すようにした。本発明の（継続的動作の際に高い性能を持つ）CG CCCカスケードLNAと他のLNAを比較すると、非常に良好に機能することがわかる（確かに、最良の利得／電力比の性能指数をもつLNAである）。オン／オフ切り替えが適用されると、中程度及び低度のデータレートの際、つまり、長いオン期間の間に、最良の性能が得られるが、いくらかの電力が節約される。

## 【0070】

効果的に、高速のオン／オフ切り替えを利用する図4のCSカスコードLNAは、本技術を同じように利用したLNAのみと比較することができ、表1のデータはプロット曲線から直接得られたものであり、リファレンス[8]よりも34%減少するものとして、この図を0.44mW@50Mppsに対して直接推測することができるため、0.22mW@25Mppsの消費が示されているが、本実施の消費がより少ないことが確認される。

## 【0071】

10

20

30

40

## 【表1】

異なる実施の比較

| リファレンス    | 技術                | トポロジ*1                       | BW<br>(GHz) | 利得<br>(dB) | S11<br>(dB) | NF<br>(dB) | Pdiss*4<br>(mW) | Pdiss (mW)<br>ON/OFF |

|-----------|-------------------|------------------------------|-------------|------------|-------------|------------|-----------------|----------------------|

| -7        | 0.18 $\mu$ m CMOS | CS, カスコード, シングルエンド           | 2.3-9.2     | 9.3        | <-9.9       | 4.0-7.0    | 9               | ---                  |

| -8        | 0.18 $\mu$ m CMOS | CS, 差動                       | 0.1-1.0     | 18         | ---         | 5.32       | ---             | 0.671@50Mpps         |

| -9        | 0.18 $\mu$ m CMOS | CS, 並列帰還, シングルエンド            | 2.0-4.6     | 9.8        | <-9         | 2.32       | 12.6            | ---                  |

| -10       | 0.18 $\mu$ m CMOS | CS カスコード + SF, シングルエンド, 同調可能 | 6.0-10.0    | 11.6       | <-9         | 4.753      | 11.6            | ---                  |

| -11       | 0.13 $\mu$ m CMOS | CS カスコード, シングルエンド            | 3.0-10.7    | 11         | <-10        | 2.22       | 4.8             | ---                  |

| -12       | 0.18 $\mu$ m CMOS | CS カスケード, シングルエンド            | 2.6-9.2     | 10.9       | <-11.5      | 3.52       | 7.1             | ---                  |

| -13       | 0.13 $\mu$ m CMOS | CG 並列帰還 CCC, 差動              | 0.1-0.93    | 13         | <-15        | 42         | 7.2             | ---                  |

| -14       | SiGe              | CS 並列帰還, シングルエンド             | 2.0-10.0    | 13         | <-7         | 3.32       | 9.6             | ---                  |

| -15       | 0.13 $\mu$ m CMOS | CS カスコード + CS, 差動            | 2.0-5.2     | 16         | <-9         | 4.7-5.7    | 38              | ---                  |

| -16       | 0.13 $\mu$ m CMOS | CS カスコード + CS, 差動            | 2.0-4.6     | 9.5        | <-10        | 3.52       | 16.5            | ---                  |

| LNAfig 3  | 0.18 $\mu$ m CMOS | CG CCC カスケード, 差動             | 7.7-8.4     | 19         | <-13        | 4.02       | 4.87            | 0.22@25Mpps          |

| LNA fig 4 | 0.18 $\mu$ m CMOS | CS カスコード, 差動                 | 7.4-8.6     | 11         | <-6         | 4.52       | 4.87            | 2.8@25Mpps           |

\*1 CS: 共通ソース、CG: 共通ゲート、SF: ソースフォロア、CCC: 静電性クロスカップル

\*2 帯域中の最小値

\*3 平均値

\*4 Pdiss continuous

## 【0072】

図3に示す、共通ゲート静電性クロスカップリング(CG CCC)カスケード構造を有する第1LNAは、同じDC電力消費(基本的に利得に関して)に対して、図4に示す、典型的共通ソース(CS)カスコード構造を有する第2LNAより、良好な性能を備える。両LNAは、RFオプションを利用し、0.18  $\mu$ m CMOSプロセスにおいて設計された。

## 【0073】

しかしながら、オン/オフ切り替えも考慮されると、CGCCC LNAは、迅速な切り替えを保てない(つまり、高いデータレートで)一方で、CSカスコードLNAは、そのような状況ではるかに良い。その結果、第1LNAは、受信パルス幅が10ナノ秒の長さの場合、良好な性能を備える一方で、第2LNAは、パルスが数ナノ秒の長さの場合、最良の性能を備える。さらに、CSカスコードLNAは、受信パルスが長い場合、消散エネルギーに対して利得を効果的にトレードオフするために利用されることができる。

## 【0074】

継続的方法において動作されるLNAの特質を比較すると、本発明のCG CCCカスケードLNAは、非常に良好に機能し、最も高い利得/電力比を有する。オン・オフ切り替えされると、特に、適度なデータレートでではあるが、その消費量を改善することができる。

## 【0075】

本発明のCSカスコードLNAは、オン/オフ切り替えされるLNAとのみ比較して、34%良好に機能し、0.44mW@50Mppsを達成する。

## 【0076】

本発明は、また、無線信号を受信するアンテナによって受信された信号を増幅するための前述された低雑音増幅器を有する、前記アンテナに接続されたインパルス無線受信機に言及する。アンテナは、例えば、差動アンテナである。

## 【0077】

本発明は、また、半導体チップ中に、前述された低雑音増幅器を有する集積回路に言及する。

## 【0078】

本発明は、また、前述された低雑音増幅器を含む無線通信機器に言及する。

## 【0079】

10

20

30

40

50

本発明の更なる実施例は、添付の独立請求項に記述される。

【0080】

上記説明及び一連の図面から、記述された本発明の実施は、本発明の目的内で多様な方法にて組み合わせてもよいことは、当業者によって理解される。本発明は、その組み合わせのうち、いくつかの好適な実施例によって記述されているが、請求される本発明の要旨を逸脱しない範囲で、これらの実施例に変形例をなすことができることは、当業者には明白である。

【産業上の利用可能性】

【0081】

本発明は、オン／オフ切り替え機能を備えた低雑音増幅器に利用することが可能である 10

。

【図面の簡単な説明】

【0082】

【図1】オンオフ切り替え機能を含む先行技術のLNAトポロジを示す図。

【図2】インパルスラジオ受信機についてのアーキテクチャーのブロック図。

【図3】共通ゲートの静電性クロスカップリング(CG-CCC)カスケードLNAの好適な実施例を示す図。

【図4】カスコードLNAの共通ソースの好適な実施例を示す図。

【図5】図3のCG-CCCカスコードLNAの電力利得S21(左軸の実線)、雑音指數NF(左軸の点線)、及び反射係数S11(右軸の破線)を示す図。 20

【図6】入力としての正弦波パルスフレームの例を示す(上部)図であり、制御電圧Vcを示す(下部)図。

【図7】図3のCG-CCCカスコードLNAのエネルギー利得(左軸の実線)及び消散電力(右軸の破線)対ウインドウ／パルス長を示す図。

【図8】図4の共通ソース(CS)カスコードLNAの電力利得S21(左軸の実線)、NF(左軸の点線)、及び反射係数S11(右軸の破線)を示す図。

【図9】図4のCSカスコードLNAのエネルギー利得(左軸の実線)及び消散電力(右軸の破線)対ウインドウ／パルス長を示す図。

【図10】図3のCG-CCCカスコードLNA(実線)及び図4のCSカスコードLNA(破線)のエネルギー利得対ウインドウ／パルス長を示す図。 30

【図11】CG-CCCカスコードLNA(実線)及びCSカスコードNLA(破線)のメリットの正規化図を示す図。

【図12】異なる受信ウインドウ長にて750psの固定長のパルスが受信された際のCG-CCCカスコードLNA(実線)及びCSカスコードNLA(破線)のメリットの正規化図を示す図。

【図13】異なる受信ウインドウ長にて15ナノ秒の固定長のパルスが受信された際のCG-CCCカスコードLNA(実線)及びCSカスコードNLA(破線)のメリットの正規化図を示す図。

【符号の説明】

【0083】

M1...第1共通ゲートトランジスタ、M2...第2共通ゲートトランジスタ、M3...第1共通ソーストランジスタ、M4...第2共通ソーストランジスタ、M5...pMOSトランジスタ、M6...pMOSトランジスタ、M7...nMOSトランジスタ、M8...nMOSトランジスタ、M9...第3共通ソーストランジスタ、M11...第3共通ゲートトランジスタ、M12...第3共通ゲートトランジスタ、L1...誘導インピーダンス、L3...第3チョークインダクタ、L5...カップリングコンデンサ、L9...第9誘導インピーダンス、C1...第1カップリングコンデンサ、C2...第2カップリングコンデンサ、C3...バイパスコンデンサ、R1...レジスタ、R2...レジスタ、Vc...制御ノード。 40

【 図 1 】

【図2】

【 図 3 】

【 図 4 】

〔 5 〕

【 义 6 】

【 7 】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(72)発明者 エンリケ バラハス オヘダ

スペイン国バルセロナC / ホルディ ヒロナ、1 - 3 カンпусノルドエディフィシオC 4 カタロ

ニア工科大学電子工学部内

(72)発明者 カイロ モリンズ ジョセップ イグナシ

スペイン国 バルセロナ サンタ クガト デル ヴァイエス モドゥロ C 2 a プランタ ア

ルカルデ バルニルス, 64 - 68 エディフィシオ テスタ

(72)発明者 池田 勝幸

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 5J500 AA01 AA12 AA13 AA54 AC36 AC85 AH10 AH25 AH29 AH33

AK17 AK19 AK31 AK33 AM17 AS13 CA04