등록특허 10-1992158

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2019년09월30일

(11) 등록번호 10-1992158

(24) 등록일자 2019년06월18일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/20* (2006.01) *G11C 19/00* (2006.01)

- (21) 출원번호 10-2013-0048387

(22) 출원일자 2013년04월30일

심사청구일자 2018년03월16일

(65) 공개번호 10-2014-0129731

(43) 공개일자 2014년11월07일

(56) 선행기술조사문현

JP2008108374 A\*

(뒷면에 계속)

- (73) 특허권자

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

조성현

서울 마포구 망원로4길 8, 201동 604호 (망원동,

성원2차아파트)

공총식

경기 파주시 탄현면 약산골길 101, B동 202호 (수

빈빌)

장성옥

인천 부평구 길주남로113번길 12, 2동 107호 (부

개동, 동아아파트)

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 8 항

심사관 : 이수한

## (54) 발명의 명칭 게이트 쉬프트 레지스터와 이를 이용한 표시장치

## (57) 요약

본 발명에 따른 게이트 쉬프트 레지스터는 순차적으로 위상이 쉬프트되는 다수의 클럭들을 입력받아 게이트 출력신호들을 생성하는 다수의 스테이지들을 포함하고; 서로 종속적으로 접속된 상기 스테이지들 중에서 제n 스테이지는, 상기 게이트 출력신호들 중 제n 게이트 출력신호가 출력되는 출력노드; Q 노드의 전위에 따라 상기 클럭들 중 n번째 위상을 갖는 클럭의 입력단과 상기 출력노드 사이의 전류 흐름을 스위칭하는 풀업 TFT; 상기 Q 노드와 다르게 충전 및 방전되는 QB 노드의 전위에 따라 저전위 전압의 입력단과 상기 출력노드 사이의 전류 흐름을 스위칭하는 풀다운 TFT; 상기 제n 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 상기 QB 노드를 상기 저전위 레벨로 주기적으로 방전시키기 위한 BTS 보상부를 구비한다.

## 대표도 - 도5

(56) 선행기술조사문현

KR1020070045908 A\*

KR1020060079037 A

KR1020090015275 A

KR1020070002713 A

\*는 심사관에 의하여 인용된 문현

---

**명세서****청구범위****청구항 1**

삭제

**청구항 2**

삭제

**청구항 3**

삭제

**청구항 4**

순차적으로 위상이 쉬프트되는 다수의 클럭들을 입력받아 게이트 출력신호들을 생성하는 다수의 스테이지들을 포함하고;

서로 종속적으로 접속된 상기 스테이지들 중에서 제n 스테이지는,

상기 게이트 출력신호들 중 제n 게이트 출력신호가 출력되는 제1 출력노드;

제1 Q 노드의 전위에 따라 상기 클럭들 중 n번째 위상을 갖는 클럭의 입력단과 상기 제1 출력노드 사이의 전류흐름을 스위칭하는 제1 풀업 TFT;

상기 제1 Q 노드와 다르게 충전 및 방전되는 제1 QB 노드의 전위에 따라 저전위 전압의 입력단과 상기 제1 출력노드 사이의 전류흐름을 스위칭하는 제1-1 풀다운 TFT;

상기 제n 게이트 출력신호보다 위상이 앞선 제1 스타트신호에 따라 제1 고전위 전압의 입력단을 상기 제1 Q 노드에 연결시켜 상기 제1 Q 노드를 고전위 레벨로 충전시키는 제1-1 스위치 TFT;

상기 제1 Q 노드의 전위에 따라 상기 제1 QB 노드를 저전위 레벨로 방전시키는 제2-1 스위치 TFT;

상기 제n 게이트 출력신호보다 위상이 뒤진 리셋신호에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제3-1 스위치 TFT;

상기 제1 QB 노드의 전위에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제4-1 스위치 TFT; 및

상기 제n 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 상기 제1 QB 노드를 상기 저전위 레벨로 주기적으로 방전시키기 위한 제1 BTS 보상부를 구비하고,

상기 제1 BTS 보상부는,

제1 방전제어신호에 따라 스위칭되어 상기 제1 QB 노드를 상기 저전위 전압의 입력단에 연결하는 제5-1 스위치 TFT; 및

제2 방전제어신호에 따라 스위칭되어 상기 제1 QB 노드를 상기 저전위 전압의 입력단에 연결하는 제5-2 스위치 TFT를 포함하고;

상기 제1 방전제어신호는 상기 클럭들 중 n+1번째 위상을 갖는 클럭의 일부와 중첩되는 별도의 제1 보조 클럭으로 선택되고, 상기 제2 방전제어신호는 상기 n+1번째 위상을 갖는 클럭의 나머지와 중첩되는 별도의 제2 보조 클럭으로 선택되며, 상기 제1 및 제2 보조클럭 각각의 온 드티는 상기 클럭들 각각의 온 드티의 1/2로 설정되는 것을 특징으로 하는 게이트 쉬프트 레지스터.

**청구항 5**

제 4 항에 있어서,

상기 제1 BTS 보상부는,

상기 제1 방전제어신호에 따라 스위칭되어 상기 제1 출력노드를 상기 저전위 전압의 입력단에 연결하는 제6-1 스위치 TFT; 및

상기 제2 방전제어신호에 따라 스위칭되어 상기 제1 출력노드를 상기 저전위 전압의 입력단에 연결하는 제6-2 스위치 TFT를 더 포함하는 것을 특징으로 하는 게이트 쉬프트 레지스터.

#### 청구항 6

삭제

#### 청구항 7

삭제

#### 청구항 8

삭제

#### 청구항 9

순차적으로 위상이 쉬프트되는 다수의 클럭들을 입력받아 게이트 출력신호들을 생성하는 다수의 스테이지를 포함하고;

서로 종속적으로 접속된 상기 스테이지를 중에서 제n 스테이지는,

상기 게이트 출력신호들 중 제n 게이트 출력신호가 출력되는 제1 출력노드;

제1 Q 노드의 전위에 따라 상기 클럭들 중 n번째 위상을 갖는 클럭의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1 풀업 TFT;

상기 제1 Q 노드와 다르게 충전 및 방전되는 제1 QB 노드의 전위에 따라 저전위 전압의 입력단과 상기 제1 출력 노드 사이의 전류 흐름을 스위칭하는 제1-1 풀다운 TFT;

상기 제n 게이트 출력신호보다 위상이 앞선 제1 스타트신호에 따라 제1 고전위 전압의 입력단을 상기 제1 Q 노드에 연결시켜 상기 제1 Q 노드를 고전위 레벨로 충전시키는 제1-1 스위치 TFT;

상기 제1 Q 노드의 전위에 따라 상기 제1 QB 노드를 저전위 레벨로 방전시키는 제2-1 스위치 TFT;

상기 제n 게이트 출력신호보다 위상이 뒤진 리셋신호에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제3-1 스위치 TFT;

상기 제1 QB 노드의 전위에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제4-1 스위치 TFT; 및

상기 제n 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 상기 제1 QB 노드를 상기 저전위 레벨로 주기적으로 방전시키기 위한 제1 BTS 보상부를 구비하며,

상기 제n 스테이지는,

상기 제1 QB 노드와 교대로 구동되는 제2 QB 노드의 전위에 따라 상기 저전위 전압의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1-2 풀다운 TFT; 및

상기 제2 QB 노드의 전위에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제4-2 스위치 TFT를 더 구비하고;

상기 스테이지를 중에서 제n+1 스테이지는,

상기 게이트 출력신호들 중 제n+1 게이트 출력신호가 출력되는 제2 출력노드;

제2 Q 노드의 전위에 따라 상기 클럭들 중 n+1번째 위상을 갖는 클럭의 입력단과 상기 제2 출력노드 사이의 전류 흐름을 스위칭하는 제2 풀업 TFT;

상기 제1 QB 노드의 전위에 따라 상기 저전위 전압의 입력단과 상기 제2 출력노드 사이의 전류 흐름을 스위칭하

는 제2-1 풀다운 TFT;

상기 제2 QB 노드의 전위에 따라 상기 저전위 전압의 입력단과 상기 제2 출력노드 사이의 전류 흐름을 스위칭하는 제2-2 풀다운 TFT;

상기 제n+1 게이트 출력신호보다 위상이 앞서고 상기 제1 스타트신호보다 위상이 뒤진 제2 스타트신호에 따라 제1 고전위 전압의 입력단을 상기 제2 Q 노드에 연결시켜 상기 제2 Q 노드를 고전위 레벨로 충전시키는 제1-2 스위치 TFT;

상기 제2 Q 노드의 전위에 따라 상기 제2 QB 노드를 저전위 레벨로 방전시키는 제2-2 스위치 TFT;

상기 제n+1 게이트 출력신호보다 위상이 뒤진 상기 리셋신호에 따라 상기 제2 Q 노드를 상기 저전위 레벨로 방전시키는 제3-2 스위치 TFT;

상기 제1 QB 노드의 전위에 따라 상기 제2 Q 노드를 상기 저전위 레벨로 방전시키는 제4-3 스위치 TFT;

상기 제2 QB 노드의 전위에 따라 상기 제2 Q 노드를 상기 저전위 레벨로 방전시키는 제4-4 스위치 TFT; 및

상기 제n+1 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 상기 제2 QB 노드를 상기 저전위 레벨로 주기적으로 방전시키기 위한 제2 BTS 보상부를 구비하고;

상기 제n 스테이지와 상기 제n+1 스테이지는 상기 제1 QB 노드를 서로 공유함과 아울러, 상기 제2 QB 노드를 서로 공유하고;

미리 정해진 기간을 주기로 상기 제1 QB 노드와 상기 제2 QB 노드는 번갈아 휴지 구동되며, 휴지 구동되는 QB 노드는 계속해서 상기 저전위 레벨로 유지되며,

상기 제1 BTS 보상부는 방전제어신호에 따라 스위칭되어 상기 제1 QB 노드를 상기 저전위 전압의 입력단에 연결하는 제5-1 스위치 TFT를 포함하고;

상기 제2 BTS 보상부는 방전제어신호에 따라 스위칭되어 상기 제2 QB 노드를 상기 저전위 전압의 입력단에 연결하는 제5-2 스위치 TFT를 포함하며;

상기 방전제어신호는 상기 클럭들 중 n+1번째 위상을 갖는 클럭으로 선택되고;

상기 제1 BTS 보상부와 상기 제2 BTS 보상부는 상기 미리 정해진 기간을 주기로 교대로 구동되며,

상기 제1 BTS 보상부는 상기 방전제어신호에 따라 스위칭되어 상기 제1 출력노드를 상기 저전위 전압의 입력단에 연결하는 제6-1 스위치 TFT를 더 포함하고;

상기 제2 BTS 보상부는 상기 방전제어신호에 따라 스위칭되어 상기 제2 출력노드를 상기 저전위 전압의 입력단에 연결하는 제6-2 스위치 TFT를 더 포함하는 것을 특징으로 하는 게이트 쉬프트 레지스터.

## 청구항 10

순차적으로 위상이 쉬프트되는 다수의 클럭들을 입력받아 게이트 출력신호들을 생성하는 다수의 스테이지를 포함하고;

서로 종속적으로 접속된 상기 스테이지를 중에서 제n 스테이지는,

상기 게이트 출력신호들 중 제n 게이트 출력신호가 출력되는 제1 출력노드;

제1 Q 노드의 전위에 따라 상기 클럭들 중 n번째 위상을 갖는 클럭의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1 풀업 TFT;

상기 제1 Q 노드와 다르게 충전 및 방전되는 제1 QB 노드의 전위에 따라 저전위 전압의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1-1 풀다운 TFT;

상기 제n 게이트 출력신호보다 위상이 앞선 제1 스타트신호에 따라 제1 고전위 전압의 입력단을 상기 제1 Q 노드에 연결시켜 상기 제1 Q 노드를 고전위 레벨로 충전시키는 제1-1 스위치 TFT;

상기 제1 Q 노드의 전위에 따라 상기 제1 QB 노드를 저전위 레벨로 방전시키는 제2-1 스위치 TFT;

상기 제n 게이트 출력신호보다 위상이 뒤진 리셋신호에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는

제3-1 스위치 TFT;

상기 제1 QB 노드의 전위에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제4-1 스위치 TFT; 및

상기 제n 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 상기 제1 QB 노드를 상기 저전위 레벨로 주기적으로 방전시키기 위한 제1 BTS 보상부를 구비하며,

상기 제n 스테이지는,

상기 제1 QB 노드와 교대로 구동되는 제2 QB 노드의 전위에 따라 상기 저전위 전압의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1-2 풀다운 TFT; 및

상기 제2 QB 노드의 전위에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제4-2 스위치 TFT를 더 구비하고;

상기 스테이지들 중에서 제n+1 스테이지는,

상기 게이트 출력신호들 중 제n+1 게이트 출력신호가 출력되는 제2 출력노드;

제2 Q 노드의 전위에 따라 상기 클럭들 중 n+1번째 위상을 갖는 클럭의 입력단과 상기 제2 출력노드 사이의 전류 흐름을 스위칭하는 제2 풀업 TFT;

상기 제1 QB 노드의 전위에 따라 상기 저전위 전압의 입력단과 상기 제2 출력노드 사이의 전류 흐름을 스위칭하는 제2-1 풀다운 TFT;

상기 제2 QB 노드의 전위에 따라 상기 저전위 전압의 입력단과 상기 제2 출력노드 사이의 전류 흐름을 스위칭하는 제2-2 풀다운 TFT;

상기 제n+1 게이트 출력신호보다 위상이 앞서고 상기 제1 스타트신호보다 위상이 뒤진 제2 스타트신호에 따라 제1 고전위 전압의 입력단을 상기 제2 Q 노드에 연결시켜 상기 제2 Q 노드를 고전위 레벨로 충전시키는 제1-2 스위치 TFT;

상기 제2 Q 노드의 전위에 따라 상기 제2 QB 노드를 저전위 레벨로 방전시키는 제2-2 스위치 TFT;

상기 제n+1 게이트 출력신호보다 위상이 뒤진 상기 리셋신호에 따라 상기 제2 Q 노드를 상기 저전위 레벨로 방전시키는 제3-2 스위치 TFT;

상기 제1 QB 노드의 전위에 따라 상기 제2 Q 노드를 상기 저전위 레벨로 방전시키는 제4-3 스위치 TFT;

상기 제2 QB 노드의 전위에 따라 상기 제2 Q 노드를 상기 저전위 레벨로 방전시키는 제4-4 스위치 TFT; 및

상기 제n+1 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 상기 제2 QB 노드를 상기 저전위 레벨로 주기적으로 방전시키기 위한 제2 BTS 보상부를 구비하고;

상기 제n 스테이지와 상기 제n+1 스테이지는 상기 제1 QB 노드를 서로 공유함과 아울러, 상기 제2 QB 노드를 서로 공유하고;

미리 정해진 기간을 주기로 상기 제1 QB 노드와 상기 제2 QB 노드는 번갈아 휴지 구동되며, 휴지 구동되는 QB 노드는 계속해서 상기 저전위 레벨로 유지되며,

상기 제1 BTS 보상부는, 제1 방전제어신호에 따라 스위칭되어 상기 제1 QB 노드를 상기 저전위 전압의 입력단에 연결하는 제5-1 오드 스위치 TFT, 및 제2 방전제어신호에 따라 스위칭되어 상기 제1 QB 노드를 상기 저전위 전압의 입력단에 연결하는 제5-2 오드 스위치 TFT를 포함하고;

상기 제2 BTS 보상부는, 제1 방전제어신호에 따라 스위칭되어 상기 제2 QB 노드를 상기 저전위 전압의 입력단에 연결하는 제5-1 이븐 스위치 TFT, 및 제2 방전제어신호에 따라 스위칭되어 상기 제2 QB 노드를 상기 저전위 전압의 입력단에 연결하는 제5-2 이븐 스위치 TFT를 포함하며;

상기 제1 방전제어신호는 상기 클럭들 중 n+1번째 위상을 갖는 클럭의 일부와 중첩되는 별도의 제1 보조 클럭으로 선택되고, 상기 제2 방전제어신호는 상기 n+1번째 위상을 갖는 클럭의 나머지와 중첩되는 별도의 제2 보조 클럭으로 선택되며, 상기 제1 및 제2 보조클럭 각각의 온 드티는 상기 클럭들 각각의 온 드티의 1/2로 설정되는 것을 특징으로 하는 게이트 쉬프트 페지스터.

## 청구항 11

제 10 항에 있어서,

상기 제1 BTS 보상부는, 상기 제1 방전제어신호에 따라 스위칭되어 상기 제1 출력노드를 상기 저전위 전압의 입력단에 연결하는 제6-1 오드 스위치 TFT와, 상기 제2 방전제어신호에 따라 스위칭되어 상기 제1 출력노드를 상기 저전위 전압의 입력단에 연결하는 제6-2 오드 스위치 TFT를 더 포함하고;

상기 제2 BTS 보상부는, 상기 제1 방전제어신호에 따라 스위칭되어 상기 제2 출력노드를 상기 저전위 전압의 입력단에 연결하는 제6-1 이븐 스위치 TFT와, 상기 제2 방전제어신호에 따라 스위칭되어 상기 제2 출력노드를 상기 저전위 전압의 입력단에 연결하는 제6-2 이븐 스위치 TFT를 더 포함하는 것을 특징으로 하는 게이트 쉬프트 레지스터.

## 청구항 12

순차적으로 위상이 쉬프트되는 다수의 클럭들을 입력받아 게이트 출력신호들을 생성하는 다수의 스테이지들을 포함하고;

서로 종속적으로 접속된 상기 스테이지들 중에서 제n 스테이지는,

상기 게이트 출력신호들 중 제n 게이트 출력신호가 출력되는 제1 출력노드;

제1 Q 노드의 전위에 따라 상기 클럭들 중 n번째 위상을 갖는 클럭의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1 풀업 TFT;

상기 제1 Q 노드와 다르게 충전 및 방전되는 제1 QB 노드의 전위에 따라 저전위 전압의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1-1 풀다운 TFT;

상기 제n 게이트 출력신호보다 위상이 앞선 제1 스타트신호에 따라 제1 고전위 전압의 입력단을 상기 제1 Q 노드에 연결시켜 상기 제1 Q 노드를 고전위 레벨로 충전시키는 제1-1 스위치 TFT;

상기 제1 Q 노드의 전위에 따라 상기 제1 QB 노드를 저전위 레벨로 방전시키는 제2-1 스위치 TFT;

상기 제n 게이트 출력신호보다 위상이 뒤진 리셋신호에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제3-1 스위치 TFT;

상기 제1 QB 노드의 전위에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제4-1 스위치 TFT; 및

상기 제n 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 상기 제1 QB 노드를 상기 저전위 레벨로 주기적으로 방전시키기 위한 제1 BTS 보상부를 구비하며,

상기 제n 스테이지는,

상기 제1 QB 노드와 교대로 구동되는 제2 QB 노드의 전위에 따라 상기 저전위 전압의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1-2 풀다운 TFT;

상기 제2 QB 노드의 전위에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제4-2 스위치 TFT; 및

상기 제1 스타트신호에 따라 상기 제1 QB 노드를 저전위 레벨로 방전시키는 제8-1 스위치 TFT를 더 구비하고;

상기 스테이지들 중에서 제n+1 스테이지는,

상기 게이트 출력신호들 중 제n+1 게이트 출력신호가 출력되는 제2 출력노드;

제2 Q 노드의 전위에 따라 상기 클럭들 중 n+1번째 위상을 갖는 클럭의 입력단과 상기 제2 출력노드 사이의 전류 흐름을 스위칭하는 제2 풀업 TFT;

상기 제1 QB 노드의 전위에 따라 상기 저전위 전압의 입력단과 상기 제2 출력노드 사이의 전류 흐름을 스위칭하는 제2-1 풀다운 TFT;

상기 제2 QB 노드의 전위에 따라 상기 저전위 전압의 입력단과 상기 제2 출력노드 사이의 전류 흐름을 스위칭하는 제2-2 풀다운 TFT;

상기 제n+1 게이트 출력신호보다 위상이 앞서고 상기 제1 스타트신호보다 위상이 뒤진 제2 스타트신호에 따라

제1 고전위 전압의 입력단을 상기 제2 Q 노드에 연결시켜 상기 제2 Q 노드를 고전위 레벨로 충전시키는 제1-2 스위치 TFT;

상기 제2 Q 노드의 전위에 따라 상기 제2 QB 노드를 저전위 레벨로 방전시키는 제2-2 스위치 TFT;

상기 제n+1 게이트 출력신호보다 위상이 뒤진 상기 리셋신호에 따라 상기 제2 Q 노드를 상기 저전위 레벨로 방전시키는 제3-2 스위치 TFT;

상기 제1 QB 노드의 전위에 따라 상기 제2 Q 노드를 상기 저전위 레벨로 방전시키는 제4-3 스위치 TFT;

상기 제2 QB 노드의 전위에 따라 상기 제2 Q 노드를 상기 저전위 레벨로 방전시키는 제4-4 스위치 TFT;

상기 제1 스타트신호에 따라 상기 제2 QB 노드를 저전위 레벨로 방전시키는 제8-2 스위치 TFT; 및

상기 제n+1 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 상기 제2 QB 노드를 상기 저전위 레벨로 주기적으로 방전시키기 위한 제2 BTS 보상부를 구비하고;

상기 제n 스테이지와 상기 제n+1 스테이지는 상기 제1 QB 노드를 서로 공유함과 아울러, 상기 제2 QB 노드를 서로 공유하고;

미리 정해진 기간을 주기로 상기 제1 QB 노드와 상기 제2 QB 노드는 번갈아 휴지 구동되며, 휴지 구동되는 QB 노드는 계속해서 상기 저전위 레벨로 유지되며,

상기 제1 BTS 보상부는, 상기 제1 QB 노드에 고전위 레벨과 저전위 레벨을 교변하는 제1 교류 고전위 전압을 공급하는 제5-1 스위치 TFT를 포함하고;

상기 제2 BTS 보상부는, 상기 제2 QB 노드에 고전위 레벨과 저전위 레벨을 교변하는 제2 교류 고전위 전압을 공급하는 제5-2 스위치 TFT를 포함하며;

상기 제5-1 스위치 TFT의 게이트전극과 드레인전극은 상기 제1 교류 고전위 전압의 입력단에 접속되고, 상기 제5-1 스위치 TFT의 소스전극은 상기 제1 QB 노드에 접속되고;

상기 제5-2 스위치 TFT의 게이트전극과 드레인전극은 상기 제2 교류 고전위 전압의 입력단에 접속되고, 상기 제5-2 스위치 TFT의 소스전극은 상기 제2 QB 노드에 접속되며;

상기 제1 교류 고전위 전압과 상기 제2 교류 고전위 전압은 상기 미리 정해진 기간을 주기로 교대로 교류 전압으로 입력되며, 상기 제1 교류 고전위 전압과 상기 제2 교류 고전위 전압 중 어느 하나가 상기 고전위 레벨과 저전위 레벨을 교변하는 교류 전압으로 입력될 때, 나머지 하나는 상기 저전위 레벨의 직류 전압으로 입력되는 것을 특징으로 하는 게이트 쉬프트 레지스터.

### 청구항 13

표시패널; 및

청구항 4-5, 9-12 중 어느 한 항 기재의 게이트 쉬프트 레지스터를 포함하며,

상기 게이트 쉬프트 레지스터는 상기 게이트 출력신호들을 상기 표시패널에 공급하는 것을 특징으로 하는 표시 장치.

### 청구항 14

제 9 항에 있어서,

상기 제n 스테이지는 상기 제1 스타트신호에 따라 상기 제1 QB 노드를 저전위 레벨로 방전시키는 제8-1 스위치 TFT를 더 구비하고,

제n+1 스테이지는 상기 제1 스타트신호에 따라 상기 제2 QB 노드를 저전위 레벨로 방전시키는 제8-2 스위치 TFT를 더 구비하는 게이트 쉬프트 레지스터.

## 발명의 설명

## 기술 분야

[0001] 본 발명은 게이트 쉬프트 레지스터와 이를 이용한 표시장치에 관한 것이다.

## 배경기술

[0002] 현재 다양한 평판 표시장치들(Flat Panel Display, FPD)이 개발 및 시판되고 있다. 이러한 평판 표시장치의 스캔 구동회로는 일반적으로, 게이트 쉬프트 레지스터를 이용하여 스캔라인들에 스캔펄스를 순차적으로 공급하고 있다.

[0003] 스캔 구동회로의 게이트 쉬프트 레지스터는 다수의 박막트랜지스터들(Thin Film Transistor, 이하 "TFT"라 함)을 포함하는 스테이지들을 구비한다. 스테이지들은 종속적(cascade)으로 접속되어 출력을 순차적으로 발생한다.

[0004] 스테이지들 각각은 풀업 TFT(Pull-up Thin Film Transistor)를 제어하기 위한 Q 노드, 풀다운 TFT(Pull-down Thin Film Transistor)를 제어하기 위한 Q bar(QB) 노드를 포함한다. 또한, 스테이지들 각각은 전단 스테이지로부터 입력된 스타트신호, 후단 스테이지로부터 입력된 리셋신호, 및 클럭신호에 응답하여 Q 노드와 QB 노드 전압을 서로 반대로 충방전시키는 스위치 TFT들을 포함한다.

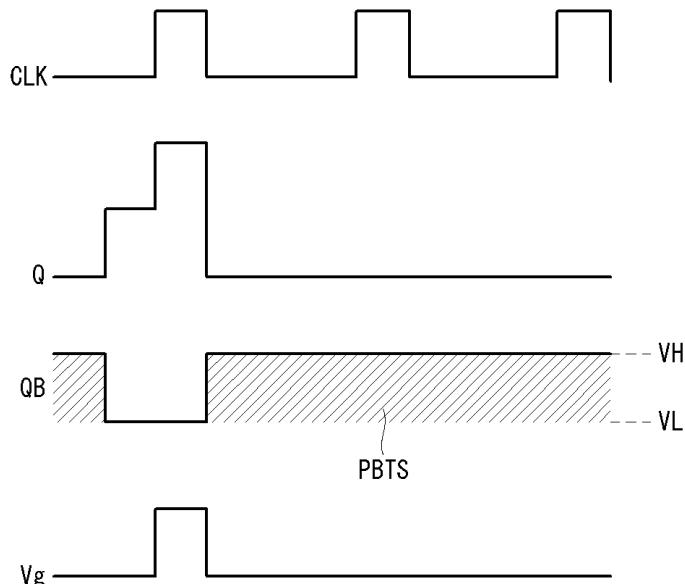

[0005] 각 스테이지는 도 1과 같은 구동 태이밍으로 동작한다. 도 1을 참조하면, 스테이지는 스타트신호에 응답하여 Q 노드를 충전한 후, 클럭신호(CLK)가 입력될 때 Q 노드의 전위를 부트 스트랩핑(bootstrapping)하여 풀업 트랜지스터를 턴 온 시킴으로써 클럭신호(CLK)를 게이트 출력신호(Vg)로 출력한다. 이어서, 스테이지는 리셋신호에 응답하여 Q 노드의 전위를 충전 레벨(예컨대, 고전위 레벨)에서 방전 레벨(예컨대, 저전위 레벨)로 낮춘 후 대략 1 프레임 기간 동안 Q 노드의 전위를 저전위 레벨로 유지한다.

[0006] QB 노드는 Q노드와 반대로 충방전된다. 즉, Q노드가 고전위 레벨을 가질 때 QB 노드는 저전위 레벨(VL)을 가지고, Q노드가 저전위 레벨로 유지될 때 QB 노드는 고전위 레벨(VH)로 유지된다. QB 노드는 한 프레임의 대부분 동안 고전위 레벨(VH)로 유지된다. 따라서, QB 노드의 전위에 따라 스위칭되는 TFT들(풀다운 TFT와 일부 스위치 TFT들)의 게이트전극에는 포지티브 바이어스 스트레스(Positive bias stress, 이하 PBTS)가 쌓인다. 이러한 PBTS는 구동시간의 경과에 비례하여 증가함으로써 해당 TFT들을 열화시킨다. TFT들의 문턱전압은 PBTS의 누적량에 비례하여 (+) 방향으로 쉬프트된다. 이와 반대로 TFT들의 문턱전압은 NBTS(Negative bias stress)의 누적량에 비례하여 (-) 방향으로 쉬프트된다. 한편, TFT는 비정질 실리콘 재질의 반도체층을 포함하는 a-Si:H TFT, 폴리 실리콘 재질의 반도체층을 포함하는 폴리 TFT가 알려져 있으며, 최근에는 수율, 공정 용이성 등의 여러 장점을 갖는 옥사이드(oxide) TFT가 많이 사용되고 있다. 옥사이드 TFT는 금속 산화물 반도체층을 포함하여 a-Si:H TFT에 비해 20~30배 빠른 전자 이동도를 나타내고 있다.

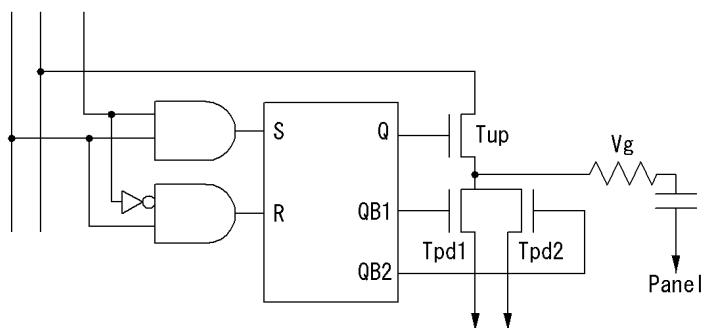

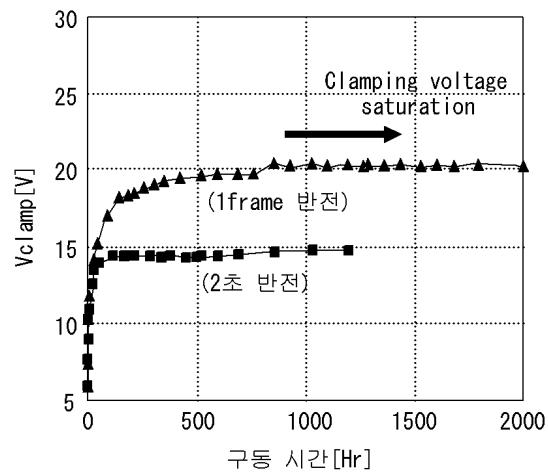

[0007] a-Si:H TFT를 이용한 스캔 구동회로에서는 도 2와 같이 2개의 QB 노드들(QB1, QB2)에 각각 접속된 2개의 풀다운 TFT들(Tpd1, Tpd2)을 교번적으로 구동시켜 TFT들의 열화를 줄이고 회로의 신뢰성을 개선하였다. 하지만, 옥사이드 TFT를 이용한 스캔 구동회로에서는 도 2와 같은 구조를 적용하여도 회로의 신뢰성이 개선되지 않는다. 왜냐하면, 휴지 구동기간 동안의 NBTS 상태에서, 옥사이드 TFT는 a-Si:H TFT에 비해 문턱전압의 (-) 쉬프트량이 매우 적어서 PBTS에 의한 문턱전압 쉬프트가 원래 상태로 회복되기 어렵기 때문이다.

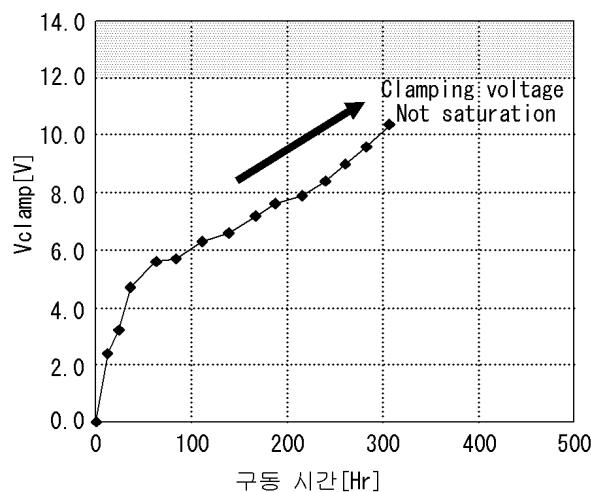

[0008] 옥사이드 TFT의 BTS(bias stress) 특성은 a-Si:H TFT보다 우수하다. 하지만, 옥사이드 TFT는 교번 구동에 의한 회복(recovery) 특성이 좋지 않기 때문에 스캔 구동회로의 신뢰성을 떨어뜨린다. a-Si:H TFT를 이용하여 도 2를 구성하면 도 3a와 같이 구동 시간이 경과하더라도 TFT들의 문턱전압이 일정치로 유지(Clamping Voltage Saturation)되는 데 반해, 옥사이드 TFT를 이용하여 도 2를 구성하면 도 3b와 같이 구동 시간의 경과에 따라 TFT들의 문턱전압이 (+) 방향으로 쉬프트(Clamping Voltage Not Saturation)된다.

## 발명의 내용

### 해결하려는 과제

[0009] 따라서, 본 발명의 목적은 QB 노드의 전위에 따라 스위칭되는 TFT들의 게이트 바이어스 스트레스를 경감하여 스캔 구동회로의 수명을 증가시킬 수 있도록 한 게이트 쉬프트 레지스터와 이를 이용한 표시장치를 제공하는 데 있다.

## 과제의 해결 수단

[0010]

본 발명의 목적을 달성하기 위하여, 본 발명의 일 실시예에 따른 게이트 쉬프트 레지스터는 순차적으로 위상이 쉬프트되는 다수의 클럭들을 입력받아 게이트 출력신호들을 생성하는 다수의 스테이지들을 포함하고; 서로 종속적으로 접속된 상기 스테이지를 중에서 제n 스테이지는, 상기 게이트 출력신호들 중 제n 게이트 출력신호가 출력되는 제1 출력노드; 제1 Q 노드의 전위에 따라 상기 클럭들 중 n번째 위상을 갖는 클럭의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1 풀업 TFT; 상기 제1 Q 노드와 다르게 충전 및 방전되는 제1 QB 노드의 전위에 따라 저전위 전압의 입력단과 상기 제1 출력노드 사이의 전류 흐름을 스위칭하는 제1-1 풀다운 TFT; 상기 제n 게이트 출력신호보다 위상이 앞선 제1 스타트신호에 따라 제1 고전위 전압의 입력단을 상기 제1 Q 노드에 연결시켜 상기 제1 Q 노드를 고전위 레벨로 충전시키는 제1-1 스위치 TFT; 상기 제1 Q 노드의 전위에 따라 상기 제1 QB 노드를 저전위 레벨로 방전시키는 제2-1 스위치 TFT; 상기 제n 게이트 출력신호보다 위상이 뒤진 리셋신호에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제3-1 스위치 TFT; 상기 제1 QB 노드의 전위에 따라 상기 제1 Q 노드를 상기 저전위 레벨로 방전시키는 제4-1 스위치 TFT; 및 상기 제n 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 상기 제1 QB 노드를 상기 저전위 레벨로 주기적으로 방전시키기 위한 제1 BTS 보상부를 구비한다.

## 발명의 효과

[0011]

본 발명에 따른 게이트 쉬프트 레지스터와 이를 이용한 표시장치는, QB 노드의 전위를 해당 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋 되기 직전까지 종래와 같이 충전 상태로만 유지시키지 않고 주기적으로 방전함으로써, QB 노드의 전위에 따라 스위칭되는 TFT들의 게이트 바이어스 스트레스를 감소시켜 스캔 구동회로의 수명을 증가시킬 수 있다.

## 도면의 간단한 설명

[0012]

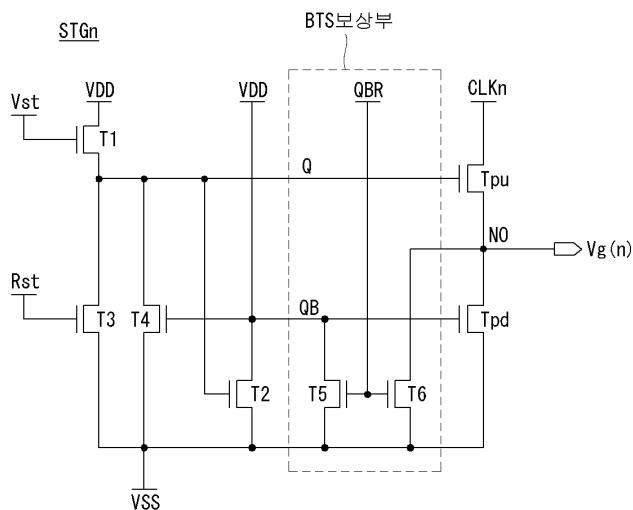

도 1은 게이트 쉬프트 레지스터를 구성하는 단위 스테이지의 일반적인 구동 타이밍도.

도 2는 종래 2개의 QB 노드들을 교변 구동하는 스테이지 구조를 개략적으로 보여주는 도면.

도 3a는 a-Si:H TFT를 이용한 스캔 구동회로의 신뢰성 특성을 보여주는 도면.

도 3b는 옥사이드 TFT를 이용한 스캔 구동회로의 신뢰성 특성을 보여주는 도면.

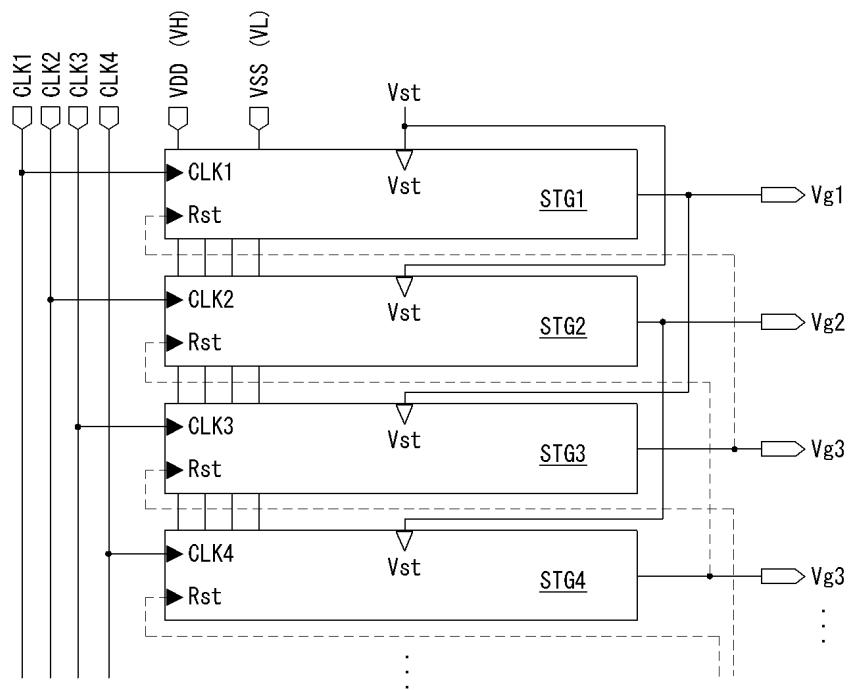

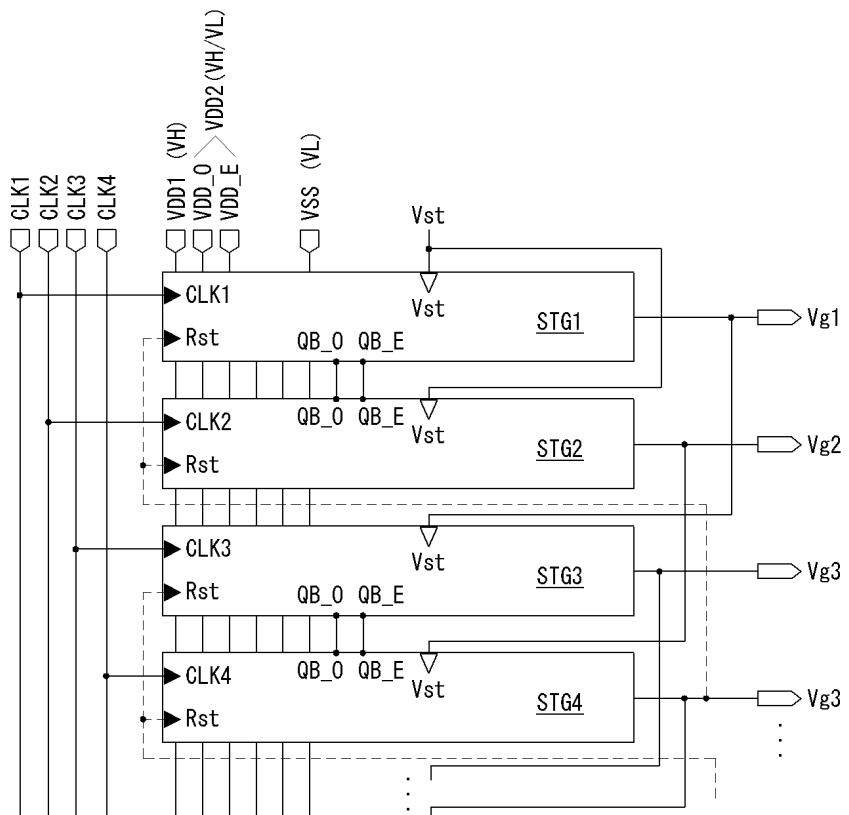

도 4는 본 발명의 일 실시예에 따른 게이트 쉬프트 레지스터 구성의 개략적인 구조를 보여주는 도면.

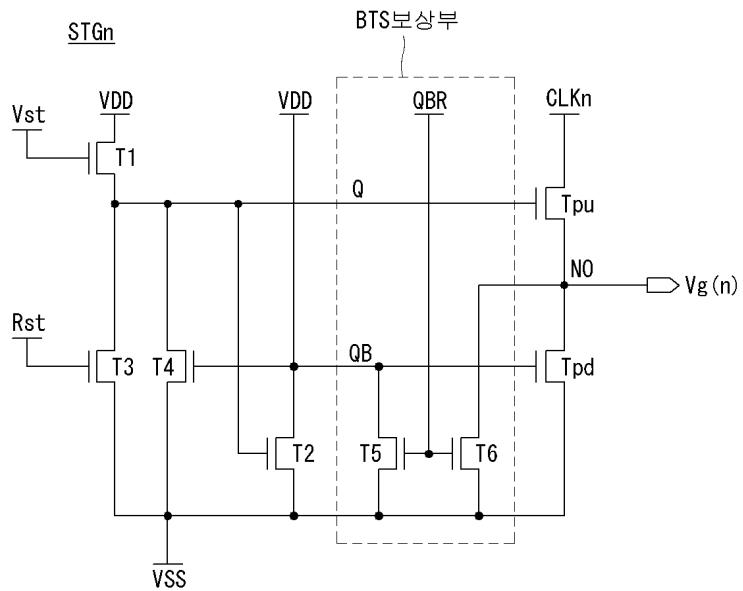

도 5는 도 4에 도시된 스테이지들 중 제n 스테이지의 일 구성을 보여주는 도면.

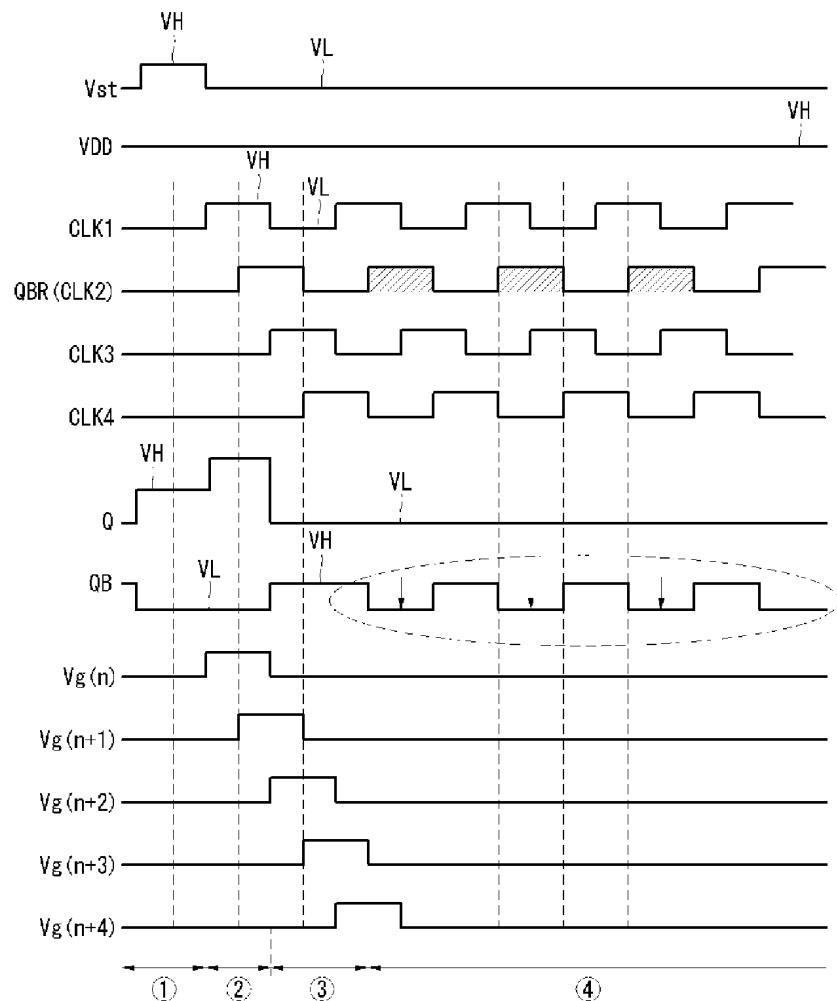

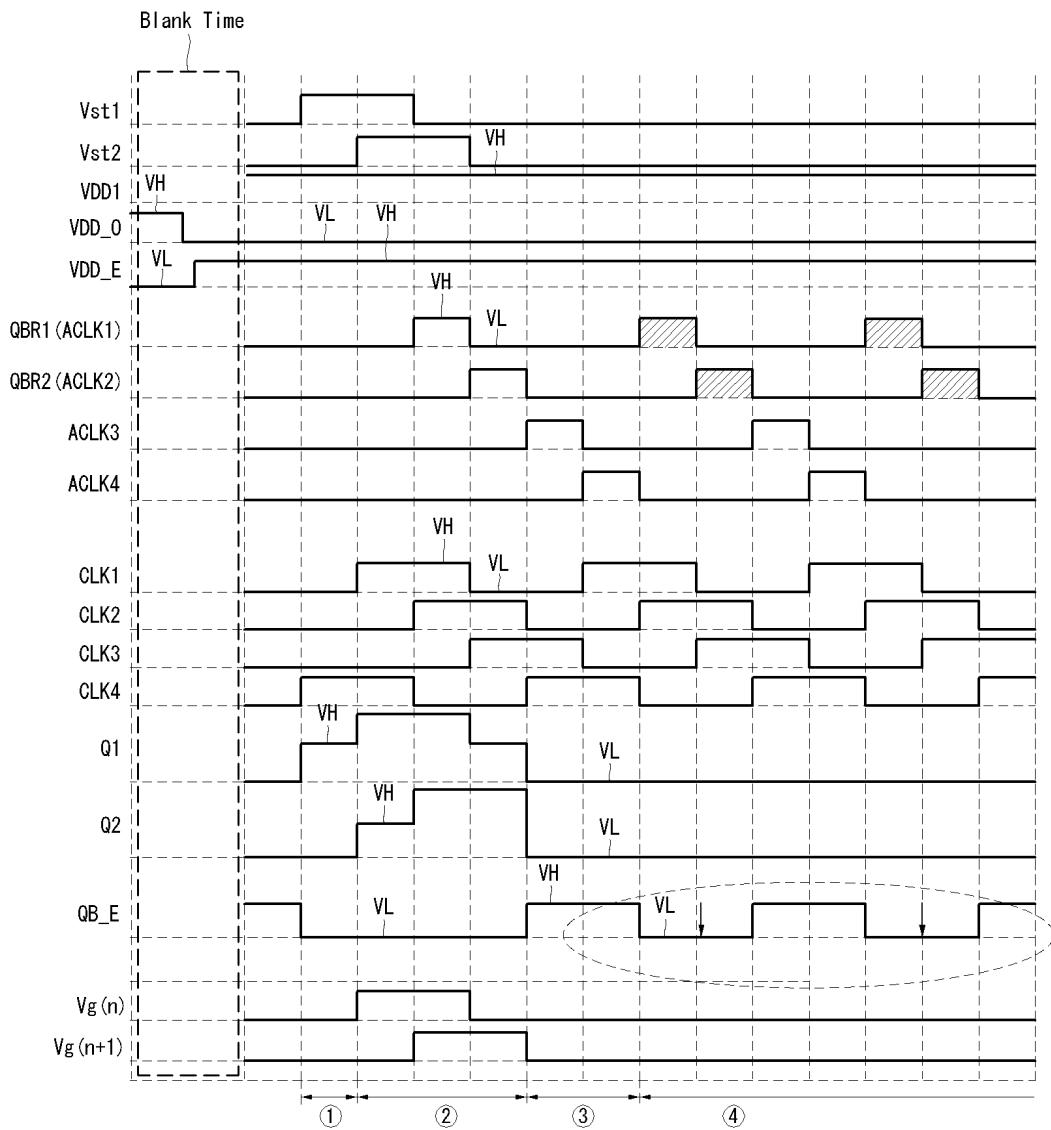

도 6은 도 5에 도시된 제n 스테이지의 동작 과정을 보여주는 도면.

도 7는 도 4에 도시된 스테이지들 중 제n 스테이지의 다른 구성을 보여주는 도면.

도 8은 도 7에 도시된 제n 스테이지의 동작 과정을 보여주는 도면.

도 9는 도 4에 도시된 스테이지들 중 제n 스테이지의 또 다른 구성을 보여주는 도면.

도 10은 도 9에 도시된 제n 스테이지의 동작 과정을 보여주는 도면.

도 11은 본 발명의 다른 실시예에 따른 게이트 쉬프트 레지스터 구성의 개략적인 구조를 보여주는 도면.

도 12는 도 11에 도시된 스테이지들 중 제n 스테이지의 일 구성을 보여주는 도면.

도 13은 도 12에 도시된 제n 스테이지의 동작 과정을 보여주는 도면.

도 14는 도 11에 도시된 스테이지들 중 제n 스테이지의 다른 구성을 보여주는 도면.

도 15는 도 14에 도시된 제n 스테이지의 동작 과정을 보여주는 도면.

도 16은 도 11에 도시된 스테이지들 중 제n 스테이지의 또 다른 구성을 보여주는 도면.

도 17은 도 16에 도시된 제n 스테이지의 동작 과정을 보여주는 도면.

도 18 및 도 19는 일부 실시예들에 대한 시뮬레이션 결과를 보여주는 과정도들.

도 20은 본 발명의 실시예에 따른 표시장치를 개략적으로 보여주는 블록도.

### 발명을 실시하기 위한 구체적인 내용

[0013]

이하 첨부된 도면을 참조하여 본 발명에 따른 바람직한 실시예들을 상세히 설명한다. 명세서 전체에 걸쳐서 동일한 참조번호들은 실질적으로 동일한 구성요소들을 의미한다. 이하의 설명에서, 본 발명과 관련된 공지 기능 혹은 구성에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우, 그 상세한 설명을 생략한다. 이하의 설명에서 사용되는 구성요소들의 명칭은 명세서 작성의 용이함을 고려하여 선택된 것으로, 실제 제품의 명칭과는 상이할 수 있다. 이하의 설명에서 "전단 스테이지들"이란, 기준이 되는 스테이지의 상부에 위치하여 기준 스테이지에서 출력되는 기준 게이트 출력신호에 의해 위상이 앞선 게이트 출력신호들을 생성하는 스테이지들을 의미한다. 그리고, "후단 스테이지들"이란, 기준이 되는 스테이지의 하부에 위치하여 기준 스테이지에서 출력되는 기준 게이트 출력신호에 의해 위상이 뒤진 게이트 출력신호들을 생성하는 스테이지들을 의미한다. 이하의 설명에서, 본 발명의 게이트 쉬프트 레지스터를 구성하는 TFT들은 옥사이드 TFT로 구현됨이 바람직하나, 본 발명의 기술적 사상은 이에 한정되지 않고 a-Si:H TFT 및 LTPS 공정의 폴리 TFT에도 당연히 적용될 수 있다.

[0014]

도 4는 본 발명의 일 실시예에 따른 게이트 쉬프트 레지스터 구성을 개략적으로 보여 준다.

[0015]

도 4를 참조하면, 본 발명의 일 실시예에 따른 게이트 쉬프트 레지스터는 종속적으로 접속된 다수의 스테이지들(STG1~STG4,...)을 구비한다.

[0016]

각 스테이지들(STG1~STG4)은 출력 채널을 구비하여 게이트 출력신호(Vg1~Vg4,...)를 생성한다. 게이트 출력신호(Vg1~Vg4,...)는 순차적으로 위상이 쉬프트된다. 각 게이트 출력신호(Vg1~Vg4,...)는 표시장치의 스캔라인들에 스캔펄스로 인가됨과 동시에, 후단 스테이지들 중 어느 하나에 스타트신호(Vst)로 입력될 수 있고 아울러, 전단 스테이지들 중 어느 하나에 리셋신호(Rst)로 입력될 수 있다.

[0017]

각 스테이지들(STG1~STG4,...)은 매 프레임마다 스타트단자에 인가되는 스타트신호(Vst)에 따라 동작이 셋(se t)된다. 셋 동작에 의해 각 스테이지들(STG1~STG4,...)의 Q 노드는 충전되고 QB 노드는 방전된다. 최상단 2개의 스테이지들(STG1, STG2)에는 외부(타이밍 콘트롤러)로부터 게이트 스타트 펄스가 스타트신호(Vst)로 인가될 수 있다. 그리고, 최상단 2개의 스테이지들(STG1, STG2)을 제외한 나머지 스테이지들(STG3, STG4,...) 각각에는 전전단 스테이지의 게이트 출력신호가 스타트신호(Vst)로 인가될 수 있다. 예를 들어, 제k(k는 자연수) 스테이지(STGk)에는 제k-2 스테이지(STGk-2)의 게이트 출력신호(Vgk-2)가 스타트신호(Vst)로 인가될 수 있다.

[0018]

각 스테이지들(STG1~STG4,...)은 매 프레임마다 리셋단자에 인가되는 리셋신호(Rst)에 따라 동작이 리셋(reset)된다. 리셋 동작에 의해 각 스테이지들(STG1~STG4,...)의 Q 노드는 방전되고 QB 노드는 충전된다. 스테이지들(STG1~STG4,...) 각각에는 후후단 스테이지의 게이트 출력신호가 리셋신호(Rst)로 인가될 수 있다. 예를 들어, 제k 스테이지(STGk)에는 제k+2 스테이지(STGk+2)의 게이트 출력신호(Vgk+2)가 리셋신호(Rst)로 인가될 수 있다.

[0019]

각 스테이지들(STG1~STG4,...)에는 소정 시간만큼 중첩되고 순차적으로 위상이 지연되는 i(i는 양의 짹수) 상 게이트 쉬프트 클럭들 중 어느 하나가 입력될 수 있다. 게이트 쉬프트 클럭들은 고속 구동시 충분한 충전시간 확보를 위해 4상 이상으로 구현됨이 바람직하다. 본 실시예를 포함한 아래의 실시예들에서 게이트 쉬프트 클럭들은 4상으로 설명되나, 본 발명의 기술적 사상은 이에 한정되지 않는다. 순차적으로 위상이 지연되는 4상 게이트 쉬프트 클럭들(CLK1~CLK4)에 동기하여 게이트 출력신호(Vg1~Vg4,...)가 순차적으로 쉬프트된다. 4상 게이트 쉬프트 클럭들(CLK1~CLK4)은 게이트 하이 전압과 게이트 로우 전압 사이에서 스윙한다.

[0020]

각 스테이지들(STG1~STG4,...)에는 고전위 레벨(VH)의 고전위 전압(VDD)과, 고전위 레벨(VH)보다 낮은 저전위 레벨(VL)의 저전위 전압(VSS)이 공급된다. 고전위 레벨(VH)은 게이트 하이 전압과 실질적으로 동일하게 설정될 수 있고, 저전위 레벨(VL)은 게이트 로우 전압과 실질적으로 동일하게 설정될 수 있다.

[0021]

특히, 각 스테이지들(STG1~STG4,...)은 도 5, 도 7, 도 9와 같은 BTS 보상부를 포함하여 QB 노드를 주기적으로 방전시킴으로써, QB 노드의 전위에 따라 스위칭되는 TFT들의 게이트 바이어스 스트레스를 감소시킨다. 각 스테

이지들(STG1~STG4,...)에서, BTS 보상부는 해당 스테이지가 리셋된 직후부터 그 다음 프레임에서 셋 되기 직전 까지 QB 노드를 주기적으로 방전시킨다. BTS 보상부는 주기적인 방전 동작을 위해 적어도 하나의 방전제어신호(도 5의 QBR, 도 7의 QBR1,QBR2)를 인가받을 수 있다. 이 방전제어신호는 도 6에서와 같이 4상 클럭들(CLK1~CLK4) 중 어느 하나로 선택될 수 있고, 도 8에서와 같이 별도의 4상 보조클럭들(ACLK1~ACLK4) 중 어느 하나로 선택될 수도 있다. 한편, BTS 보상부는 주기적인 방전 동작을 위해 도 9에서와 같이 교류 고전위 전압(AVDD)을 인가받을 수도 있다. 교류 고전위 전압(AVDD)은 고전위 레벨(VH)과 저전위 레벨(VL)로 스윙됨으로써, 소정 주기마다 저전위 레벨(VL)로 떨어진다.

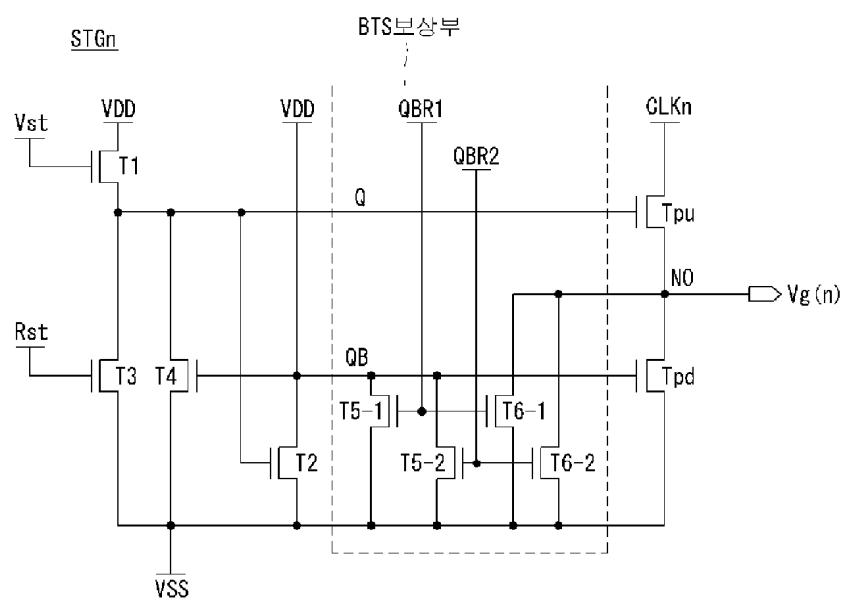

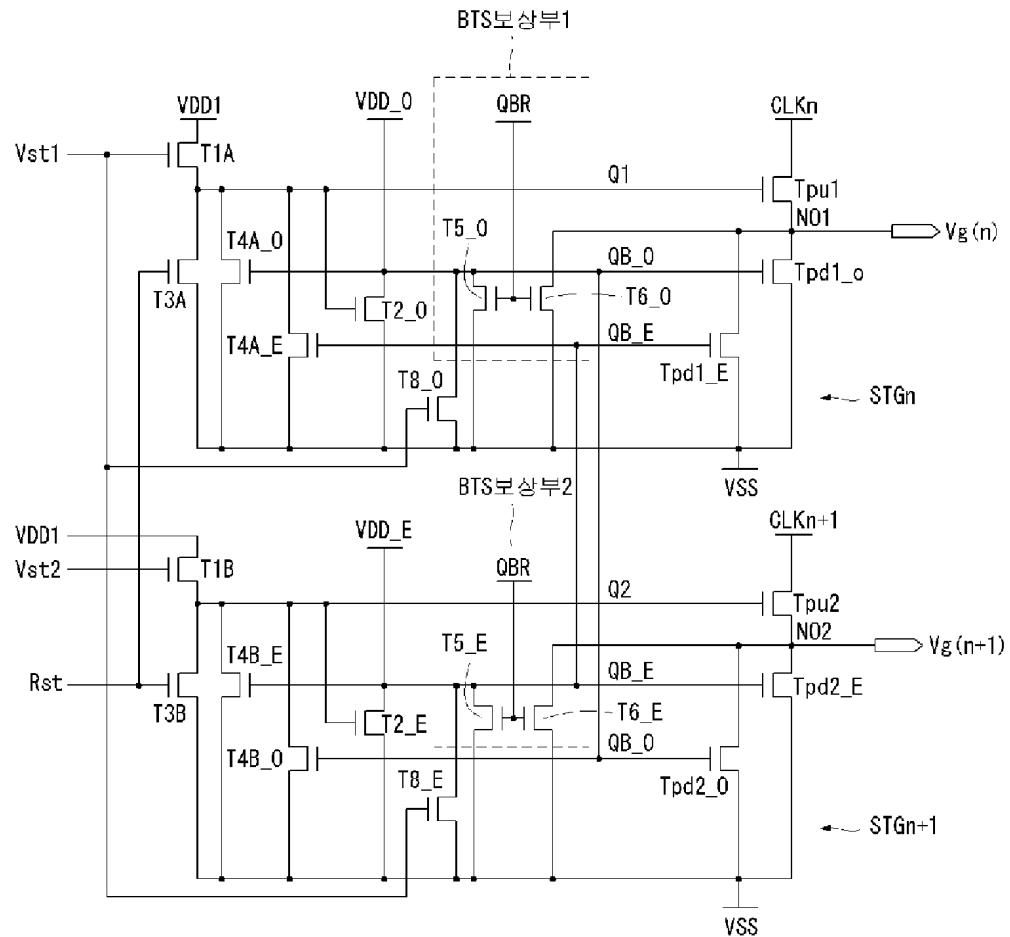

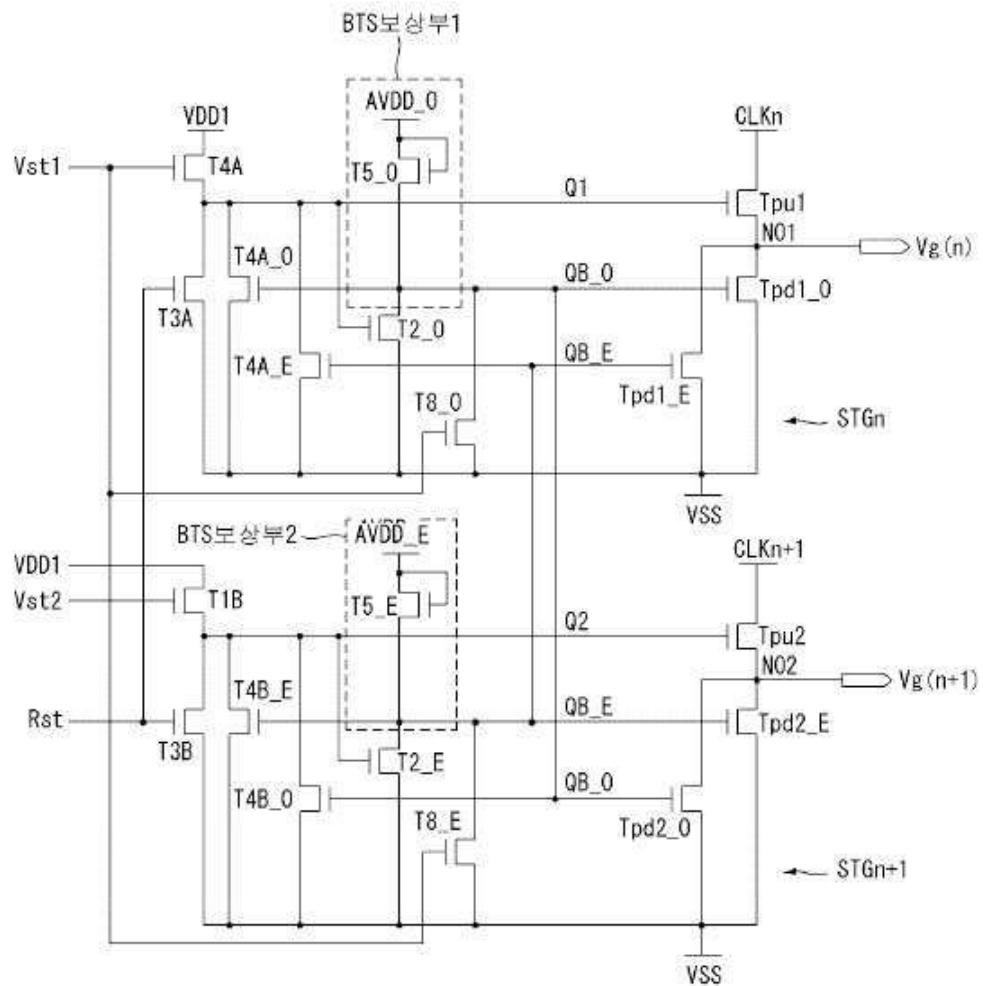

[0022] 도 5는 도 4에 도시된 스테이지들(STG1~STG4,...) 중 제n(n은 양의 정수) 스테이지(STGn)의 일 구성을 보여준다. 그리고, 도 6은 도 5에 도시된 제n 스테이지(STGn)의 동작 과형을 보여준다.

[0023] 도 5를 참조하면, 제n 스테이지(STGn)는, 제n 게이트 출력신호( $Vg(n)$ )가 출력되는 출력노드(NO), Q 노드의 전위에 따라 스위칭되는 풀업 TFT(Tpu), QB 노드의 전위에 따라 스위칭되는 풀다운 TFT(Tpd), Q 노드를 충전 및 방전시키기 위한 제1, 제3, 및 제4 스위치 TFT(T1,T3,T4), Q 노드의 전위에 따라 QB 노드를 방전시키기 위한 제2 스위치 TFT(T2), 및 방전제어신호(QBR)에 따라 QB 노드를 주기적으로 방전시켜 QB 노드의 전위에 따라 스위칭되는 TFT들(Tpd,T4)의 게이트 바이어스 스트레스를 감소시키기 위한 BTS 보상부를 구비한다.

[0024] 풀업 TFT(Tpu)는 Q 노드의 전위에 따라 n번째 위상을 갖는 클럭(CLKn)의 입력단과 출력노드(NO) 사이의 전류 흐름을 스위칭한다. Q 노드가 고전위 레벨(VH)로 충전된 상태에서 n번째 위상을 갖는 클럭(CLKn)이 입력되면, Q 노드의 전위는 고전위 레벨(VH)보다 높은 전압으로 부트 스트랩핑되어 풀업 TFT(Tpu)를 턴 온 시킨다. 풀업 TFT(Tpu)가 턴 온 되면 n번째 위상을 갖는 클럭(CLKn) 즉, 도 6의 예에서 제1 클럭(CLK1)이 출력노드(NO)에 인가된다.

[0025] 풀다운 TFT(Tpd)는 Q 노드와 다르게 충전 및 방전되는 QB 노드의 전위에 따라 저전위 전압(VSS)의 입력단과 출력노드(NO) 사이의 전류 흐름을 스위칭한다. 풀다운 TFT(Tpd)가 턴 온 되면, 저전위 전압(VSS)이 출력노드(NO)에 인가된다.

[0026] 제1, 제3, 및 제4 스위치 TFT(T1,T3,T4)는 Q 노드의 충방전에 관련된다. 제1 스위치 TFT(T1)는 제n 게이트 출력신호( $Vg(n)$ )보다 위상이 앞선 스타트신호(Vst)에 따라 고전위 전압(VDD)의 입력단을 상기 Q 노드에 연결시켜 상기 Q 노드를 고전위 레벨(VH)로 충전시킨다. 여기서, 스타트신호(Vst)는 위에서 언급했듯이 제n-2 게이트 출력신호( $Vg(n-2)$ )로 선택될 수 있다. 제3 스위치 TFT(T3)는 제n 게이트 출력신호( $Vg(n)$ )보다 위상이 뒤진 리셋 신호(Rst)에 따라 상기 Q 노드를 저전위 전압(VSS)의 입력단에 연결시켜 상기 Q 노드를 저전위 레벨(VL)로 방전시킨다. 여기서, 리셋신호(Rst)는 위에서 언급했듯이 제n+2 게이트 출력신호( $Vg(n+2)$ )로 선택될 수 있다. 제4 스위치 TFT(T4)는 QB 노드의 전위에 따라 상기 Q 노드를 저전위 전압(VSS)의 입력단에 연결시켜 상기 Q 노드를 저전위 레벨(VL)로 방전시킨다.

[0027] 제2 스위치 TFT(T2)는 상기 Q 노드의 전위에 따라 상기 QB 노드를 저전위 레벨(VL)로 방전시킨다. 제2 스위치 TFT(T2)는 상기 Q 노드가 충전될 때 상기 QB 노드를 방전시키는 역할을 한다.

[0028] BTS 보상부는 방전제어신호(QBR)에 따라 QB 노드를 주기적으로 방전시켜 QB 노드의 전위에 따라 스위칭되는 TFT들(Tpd,T4)의 게이트 바이어스 스트레스를 감소시키는 역할을 한다. 여기서, 방전제어신호(QBR)는 n+1번째 위상을 갖는 클럭(CLKn+1) 즉, 도 6의 예에서 제2 클럭(CLK2)으로 선택될 수 있다.

[0029] 이를 위해, BTS 보상부는 방전제어신호(QBR)에 응답하여 스위칭됨으로써 상기 QB 노드를 저전위 레벨(VL)로 방전시키는 제5 스위치 TFT(T5)를 포함한다. 제5 스위치 TFT(T5)의 게이트전극은 방전제어신호(QBR)의 입력 단자에, 드레인전극은 QB 노드에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제5 스위치 TFT(T5)는 방전제어신호(QBR)인 제2 클럭(CLK2)이 고전위 레벨(VH)로 입력될 때마다 턴 온 됨으로써, QB 노드를 저전위 전압(VSS)의 입력단에 연결함으로써 QB 노드를 방전시킨다.

[0030] 한편, 상기 BTS 보상부는, 방전제어신호(QBR)에 응답하여 스위칭되어 출력 노드(NO)를 저전위 레벨(VL)로 방전시키는 제6 스위치 TFT(T6)을 더 포함함으로써, 리셋된 직후부터 그 다음 프레임에서 셋되기 직전까지 제n 게이트 출력신호( $Vg(n)$ )를 안정적으로 게이트 로우 전압으로 유지시킨다. 제6 스위치 TFT(T6)의 게이트전극은 방전제어신호(QBR)의 입력 단자에, 드레인전극은 QB 노드에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제6 스위치 TFT(T6)의 스위칭 작용에 의해 제n 게이트 출력신호( $Vg(n)$ )에 포함되는 리플 성분은 효과적으로 제거될 수 있다.

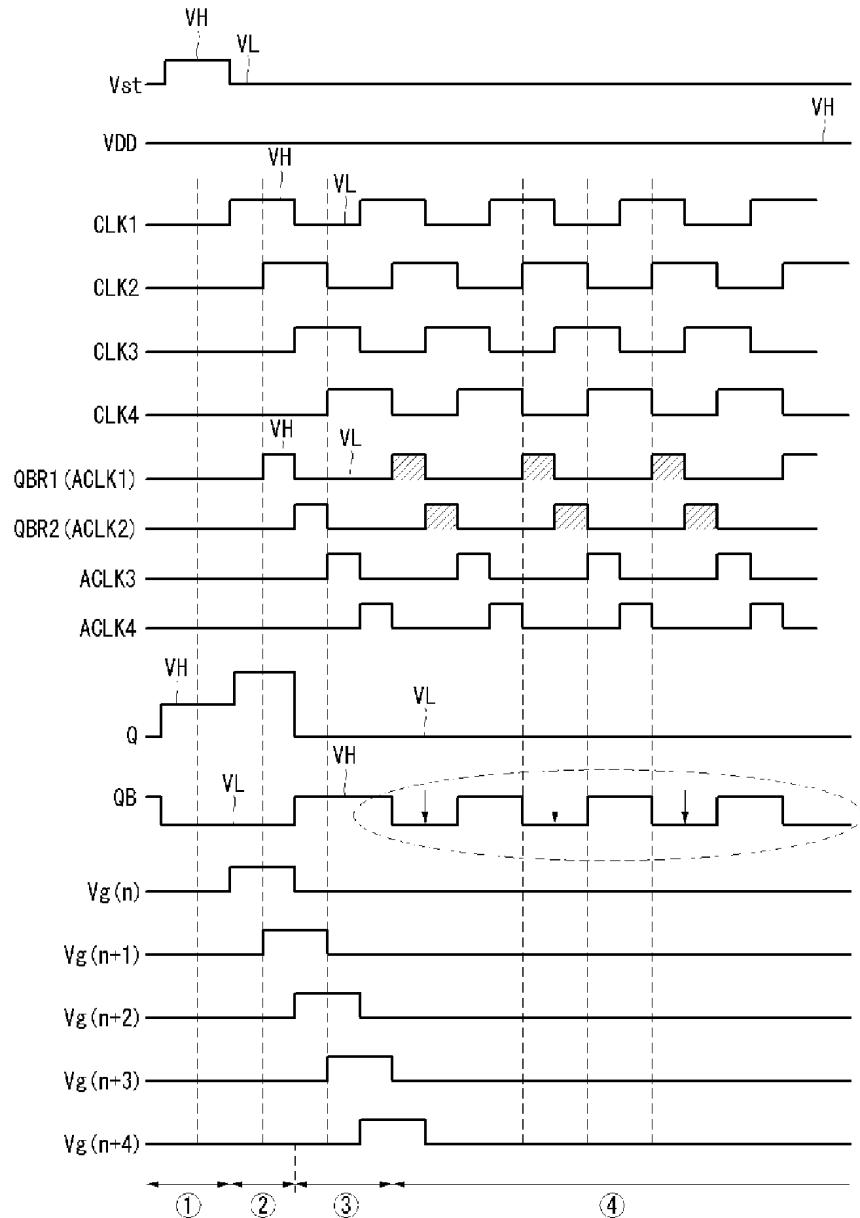

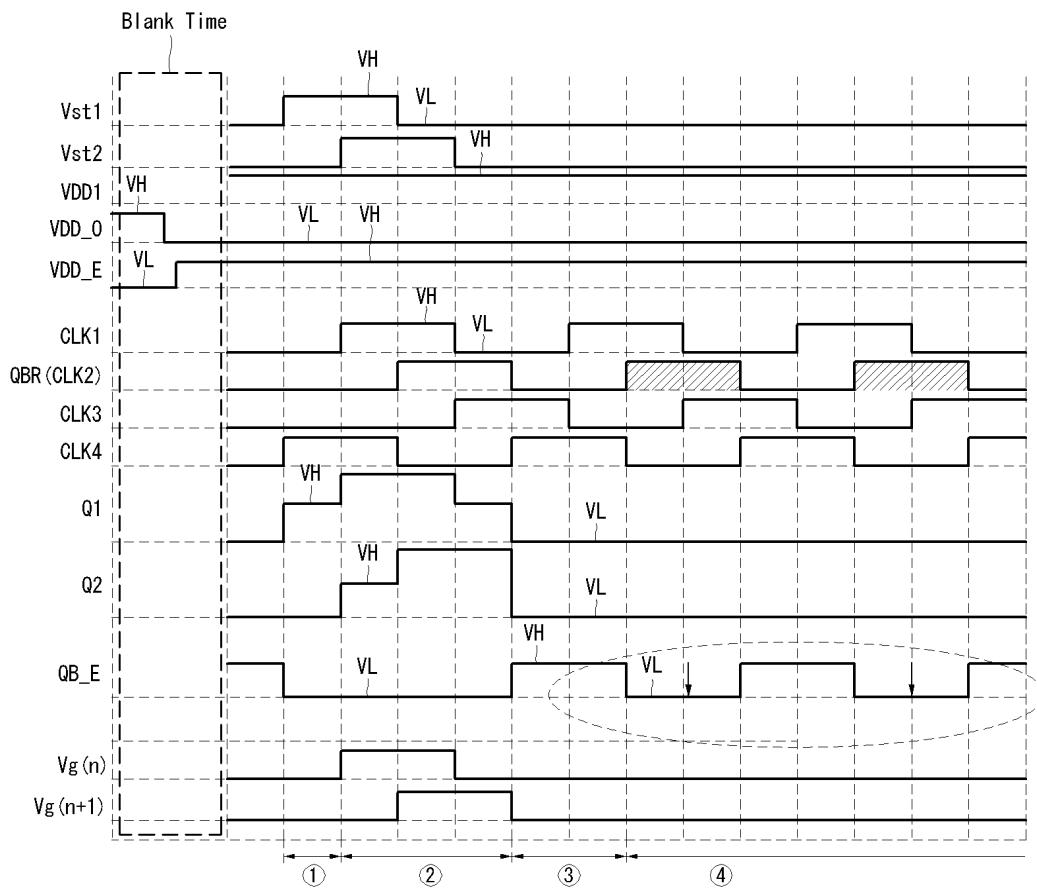

- [0031] 도 6을 참조하여 도 5에 도시된 제n 스테이지(STGn)의 동작을 살펴보면 다음과 같다.

- [0032] ① 기간에서 스타트신호(Vst)가 입력될 때, Q 노드는 제1 스위치 TFT(T1)를 통해 인가되는 고전위 전압(VDD)에 의해 고전위 레벨(VH)로 충전되고, QB 노드는 제2 스위치 TFT(T2)를 통해 인가되는 저전위 전압(VSS)에 의해 저전위 레벨(VL)로 방전된다.

- [0033] ② 기간에서 n번째 위상을 갖는 클럭(CLKn)이 풀업 TFT(Tpu)의 드레인전극에 입력되면, Q 노드와 풀업 TFT(Tpu)의 드레인전극은 기생 커플링되어 있으므로 Q 노드의 전위가 고전위 레벨(VH)보다 높은 전압으로 부트 스트랩된다. 그 결과, 풀업 TFT(Tpu)는 턴 온 된다. 풀업 TFT(Tpu)가 턴 온 되면 n번째 위상을 갖는 클럭(CLKn) 즉, 제1 클럭(CLK1)이 제n 게이트 출력신호(Vg(n))로서 출력노드(NO)에 인가된다.

- [0034] ③ 기간에서 리셋신호(Rst, 즉, 제n+2 게이트 출력신호(Vg(n+2)))가 입력될 때, Q 노드는 제3 스위치 TFT(T3)를 통해 인가되는 저전위 전압(VSS)에 의해 저전위 레벨(VL)로 방전되고, 제2 스위치 TFT(T2)는 턴 오프 되어 QB 노드의 방전 경로를 차단한다. 그 결과, QB 노드는 고전위 전압(VDD)에 의해 고전위 레벨(VH)로 충전된다.

- [0035] ④ 기간에서 방전제어신호(QBR)로 선택되는 제2 클럭(CLK2)에 의해 제5 스위치 TFT(T5)가 주기적으로 턴 온 되면, 그때마다 QB 노드는 저전위 레벨(VL)로 방전된다. 이러한 QB 노드의 주기적인 방전 동작은 그 다음 프레임에서 셋되기 직전까지 행해질 수 있다. TFT들에 인가되는 게이트 바이어스 스트레스는 인가되는 전압의 크기 및 인가 시간에 비례하여 커진다. ④ 기간은 1 프레임 중 대부분의 시간을 담당한다. ④ 기간 동안 QB 노드는 주기적으로 방전되기 때문에, QB 노드에 따라 스위칭되는 TFT들(Tpd, T4)의 게이트 바이어스 스트레스는, 종래 QB 노드의 전위가 계속해서 고전위 레벨(VH)로 유지될 때에 비해 현저히 감소된다. 게이트 바이어스 스트레스가 줄어들면 TFT들의 문턱전압 열화(즉, 문턱전압 쉬프트량)이 줄어들기 때문에, 스테이지 회로의 신뢰성 및 안정성이 높아져 결국 스캔 구동회로의 수명이 증대되는 효과가 있다.

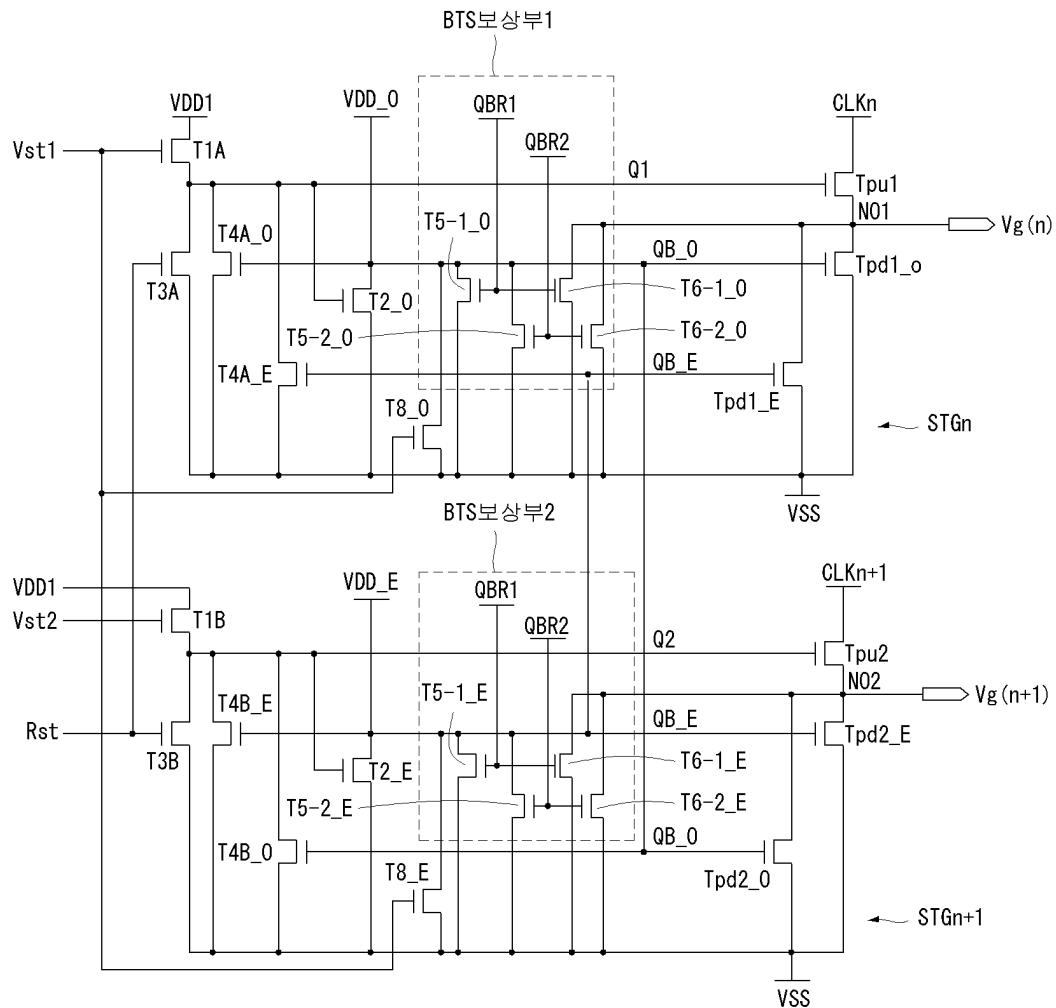

- [0036] 도 7은 도 4에 도시된 스테이지들(STG1~STG4,...) 중 제n(n은 양의 정수) 스테이지(STGn)의 다른 구성을 보여준다. 그리고, 도 8은 도 7에 도시된 제n 스테이지(STGn)의 동작 과형을 보여준다.

- [0037] 도 5와 비교하여 도 7의 제n 스테이지(STGn)는 BTS 보상부의 구성만이 다를 뿐, 나머지 구성은 실질적으로 동일하다.

- [0038] 도 7의 BTS 보상부는 제1 방전제어신호(QBR1)에 응답하여 스위칭됨으로써 상기 QB 노드를 저전위 레벨(VL)로 방전시키는 제5-1 스위치 TFT(T5-1)와, 제2 방전제어신호(QBR2)에 응답하여 스위칭됨으로써 상기 QB 노드를 저전위 레벨(VL)로 방전시키는 제5-2 스위치 TFT(T5-2)를 포함한다. 제5-1 스위치 TFT(T5-1)의 게이트전극은 제1 방전제어신호(QBR1)의 입력 단자에, 드레인전극은 QB 노드에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제5-2 스위치 TFT(T5-2)의 게이트전극은 제2 방전제어신호(QBR2)의 입력 단자에, 드레인전극은 QB 노드에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다.

- [0039] 이 BTS 보상부는 제1 및 제2 방전제어신호(QBR1, QBR2)에 따라 QB 노드를 주기적으로 방전시켜 QB 노드의 전위에 따라 스위칭되는 TFT들(Tpd, T4)의 게이트 바이어스 스트레스를 감소시키는 역할을 한다. 여기서, 제1 방전제어신호(QBR1)는 n+1번째 위상을 갖는 클럭(CLKn+1)의 일부와 중첩되는 별도의 제1 보조 클럭(즉, 도 6의 예에서 ACLK1)으로 선택되고, 제2 방전제어신호(QBR2)는 n+1번째 위상을 갖는 클럭(CLKn+1)의 나머지와 중첩되는 별도의 제2 보조 클럭(즉, 도 6의 예에서 ACLK2)으로 선택될 수 있다. 제1 및 제2 보조클럭(ACLK1, ACLK2) 각각의 온 드티는 각각 4상 클럭들(CLK1~CLK4) 각각의 온 드티의 1/2로 설정된다. 따라서, 제5-1 스위치 TFT(T5-1)와 제5-2 스위치 TFT(T5-2)는 제1 및 제2 보조클럭(ACLK1, ACLK2)이 고전위 레벨(VH)로 입력될 때마다 교대로 턴 온됨으로써, QB 노드를 저전위 전압(VSS)의 입력단에 연결함으로써 QB 노드를 방전시킨다. 제5-1 스위치 TFT(T5-1)와 제5-2 스위치 TFT(T5-2)는 1/2 온 드티로 교대로 턴 온 되기 때문에, 도 5의 비해 스위치 열화가 절반으로 줄어든다.

- [0040] 한편, 상기 도 7의 BTS 보상부는, 제1 방전제어신호(QBR1)에 응답하여 스위칭되어 출력 노드(NO)를 저전위 레벨(VL)로 방전시키는 제6-1 스위치 TFT(T6-1)와, 제2 방전제어신호(QBR2)에 응답하여 스위칭되어 출력 노드(NO)를 저전위 레벨(VL)로 방전시키는 제6-2 스위치 TFT(T6-2)를 더 포함함으로써, 리셋된 직후부터 그 다음 프레임에서 셋되기 직전까지 제n 게이트 출력신호(Vg(n))를 안정적으로 게이트 로우 전압으로 유지시킨다. 제6-1 스위치 TFT(T6-1)의 게이트전극은 제1 방전제어신호(QBR1)의 입력 단자에, 드레인전극은 QB 노드에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속되고, 제6-2 스위치 TFT(T6-2)의 게이트전극은 제2 방전제어신호(QBR2)의 입력 단자에, 드레인전극은 QB 노드에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제6-1 및 제6-2 스위치 TFT(T6-1, T6-2)의 스위칭 작용에 의해 제n 게이트 출력신호(Vg(n))에 포함되는 리플 성분은 효

과적으로 제거될 수 있다.

[0041] 도 8에 도시된 제n 스테이지(STG<sub>n</sub>)의 동작 과형은, 제1 내지 제4 클럭(CLK1~CLK4)에 의해 하프 브리지 갖는 제1 및 제2 보조 클럭(ACLK1, ACLK2)에 따라 QB 노드가 ④ 기간에서 주기적으로 방전되는 것만 제외하고, 그 외 나머지 동작은 도 6에서 설명한 것과 실질적으로 동일하다.

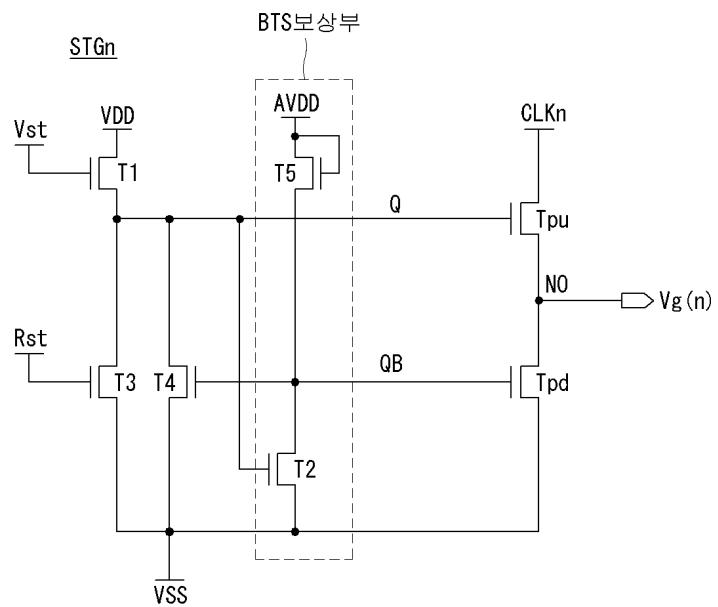

[0042] 도 9는 도 4에 도시된 스테이지들(STG1~STG4,...) 중 제n(n은 양의 정수) 스테이지(STG<sub>n</sub>)의 또 다른 구성을 보여준다. 그리고, 도 10은 도 9에 도시된 제n 스테이지(STG<sub>n</sub>)의 동작 과형을 보여준다.

[0043] 도 5와 비교하여 도 9의 제n 스테이지(STG<sub>n</sub>)는 BTS 보상부의 구성만이 다를 뿐, 나머지 구성은 실질적으로 동일하다.

[0044] 도 9의 BTS 보상부는 QB 노드에 교류 고전위 전압(AVDD)을 공급하는 제5 스위치 TFT(T5)를 포함한다. 제5 스위치 TFT(T5)는 다이오드 커넥션(diode-connection)되어 교류 고전위 전압(AVDD)의 입력단과 QB 노드에 접속된다. 다이오드 커넥션을 위해 제5 스위치 TFT(T5)의 게이트전극과 드레인전극은 교류 고전위 전압(AVDD)의 입력단에 접속되고, 제5 스위치 TFT(T5)의 소스전극은 QB 노드에 접속된다.

[0045] 리셋 된 직후부터 그 다음 프레임에서 셋되기 직전까지 도 9의 제2 스위치 TFT(T2)는 턴 오프 상태를 유지하므로, QB 노드의 전위는 교류 고전위 전압(AVDD)에 의존한다. QB 노드의 전위는 교류 고전위 전압(AVDD)이 고전위 레벨(VH)로 입력될 때 충전되고 저전위 레벨(VL)로 입력될 때 방전된다. 도 9의 BTS 보상부는 고전위 레벨(VH)과 저전위 레벨(VL)을 교변하는 교류 고전위 전압(AVDD)을 QB 노드에 인가하여 QB 노드를 주기적으로 방전시킴으로써, QB 노드의 전위에 따라 스위칭되는 TFT들(Tpd,T4)의 게이트 바이어스 스트레스를 감소시키는 역할을 한다.

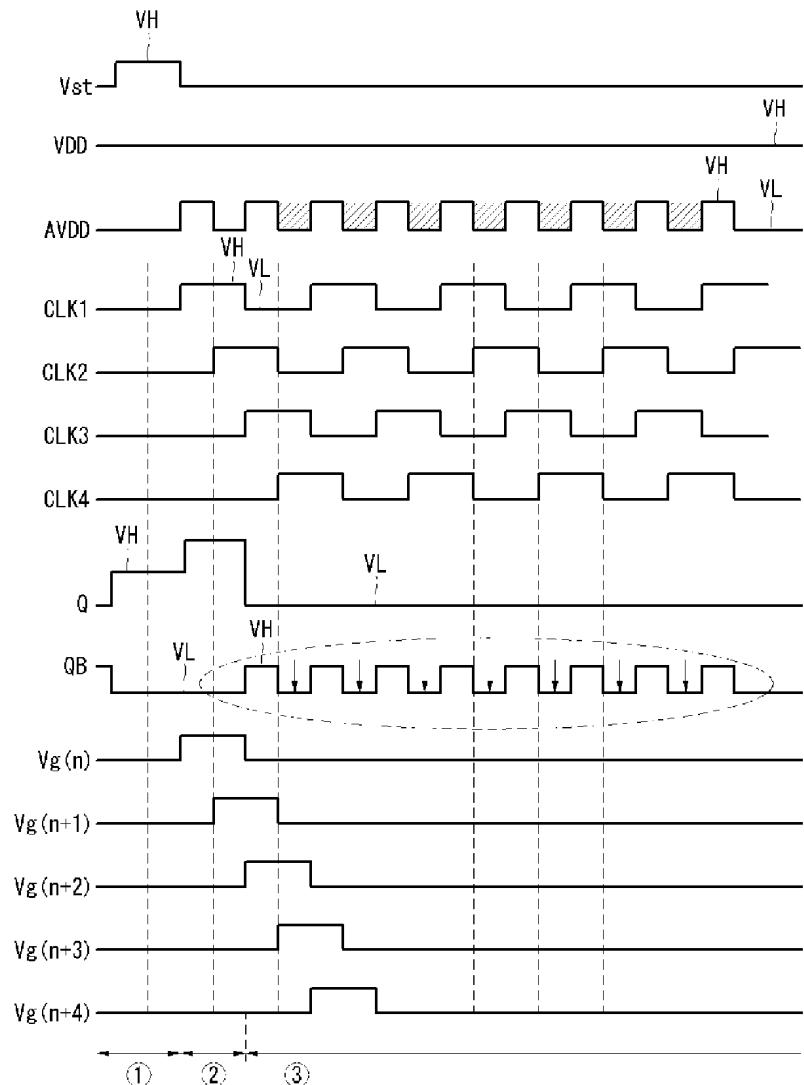

[0046] 도 10에 도시된 제n 스테이지(STG<sub>n</sub>)의 동작 과형은, 고전위 레벨(VH)과 저전위 레벨(VL)로 스윙되는 교류 고전위 전압(AVDD)에 따라 QB 노드가 ③ 기간에서 주기적으로 방전되는 것만 제외하고, 그 외 나머지 동작은 도 6에서 설명한 것과 실질적으로 동일하다.

[0047] 도 11은 본 발명의 다른 실시예에 따른 게이트 쉬프트 레지스터 구성을 개략적으로 보여 준다. 도 11은 교류 구동(각 스테이지마다 2개의 QB 노드들과 2개의 폴다운 TFT들을 구비하고, 미리 정해진 기간을 주기로 QB 노드들을 번갈아 휴지 구동) 시키기 위한 게이트 쉬프트 레지스터 구성을 나타낸 것이다. 도 11은 스테이지들에 포함된 TFT들의 개수와 전원 라인의 개수를 줄이기 위해 이웃한 2개의 스테이지들이 제1 QB 노드(QB\_O)를 서로 공유함과 동시에 제2 QB 노드(QB\_E)를 서로 공유하는 특징이 있다.

[0048] 교류 구동을 위한 구성 이외의 나머지 스테이지 구성은 도 5에서 설명한 것과 실질적으로 동일하다. 교류 구동을 위해, 각 스테이지들(STG1~STG4,...)에는 제1 고전위 전압(VDD1), 제2 고전위 전압(VDD2) 및 저전위 전압(VSS)이 공급된다.

[0049] 제1 고전위 전압(VDD1)은 일정하게 고전위 레벨(VH)로 입력된다.

[0050] 제2 고전위 전압(VDD2)은 제2-1 고전위 전압(VDD\_O)과 제2-2 고전위 전압(VDD\_E)을 포함한다. 제2-1 고전위 전압(VDD\_O)과 제2-2 고전위 전압(VDD\_E)은 대략 180도의 위상차를 갖고 미리 정해진 기간(예컨대, k 프레임 기간)을 주기로 서로 반대로 스윙된다. 예를 들어, 홀수번째 k 프레임 기간에서 제2-1 고전위 전압(VDD\_O)이 고전위 레벨(VH)로 입력되는 경우 제2-2 고전위 전압(VDD\_E)은 저전위 레벨(VL)로 입력될 수 있다. 이에 반해, 짝수번째 k 프레임 기간에서 제2-1 고전위 전압(VDD\_O)이 저전위 레벨(VL)로 입력되면 제2-2 고전위 전압(VDD\_E)은 고전위 레벨(VH)로 입력되게 된다.

[0051] 제1 고전위 전압(VDD1)은 모든 스테이지들(STG1~STG4,...)에 공통으로 입력된다. 다만, 제2-1 고전위 전압(VDD\_O)과 제2-2 고전위 전압(VDD\_E)은 QB 노드들(QB\_O, QB\_E)을 공유하는 2개의 스테이지들에 나누어 입력된다. 예를 들어, 제n 스테이지와 제n+1 스테이지가 QB 노드들(QB\_O, QB\_E)을 서로 공유한다고 가정할 때, 제n 스테이지에는 제1 고전위 전압(VDD1)과 제2-1 고전위 전압(VDD\_O)이 입력되고, 제n+1 스테이지에는 제1 고전위 전압(VDD1)과 제2-2 고전위 전압(VDD\_E)이 입력된다.

[0052] QB 노드들(QB\_O, QB\_E)을 공유하는 2개의 스테이지들은 도 12, 도 14 및 도 16과 같이 교변적으로 구동되는 2개의 BTS 보상부들을 포함하여 QB 노드들의 전위에 따라 스위칭되는 TFT들의 게이트 바이어스 스트레스를 감소시킨다.

[0053] 도 12는 도 11에 도시된 스테이지들(STG1~STG4,...) 중 QB 노드들을 공유하는 제n 스테이지(STGn)와 제n+1 스테이지(STGn+1)의 일 구성을 보여준다. 그리고, 도 13은 도 12에 도시된 제n 스테이지(STGn)와 제n+1 스테이지(STGn+1)의 동작 과정을 보여준다.

[0054] 도 12를 참조하면, 제n 스테이지(STGn)는, 제n 게이트 출력신호(Vg(n))가 출력되는 제1 출력노드(N01), 제1 Q 노드(Q1)의 전위에 따라 스위칭되는 제1 풀업 TFT(Tpu1), 제1 QB 노드(QB\_O)의 전위에 따라 스위칭되는 제1-1 풀다운 TFT(Tpd1\_O), 제2 QB 노드(QB\_E)의 전위에 따라 스위칭되는 제1-2 풀다운 TFT(Tpd1\_E), 제1 Q 노드(Q1)를 충전 및 방전시키기 위한 제1-1, 제3-1, 제4-1 및 제4-2 스위치 TFT(T1A, T3A, T4A\_O, T4A\_E), 제1 Q 노드(Q1)의 전위에 따라 제1 QB 노드(QB\_O)를 방전시키기 위한 제2-1 스위치 TFT(T2\_O), 제1 QB 노드(QB\_O)의 전위에 따라 스위칭되는 TFT들(Tpd1\_O, T4A\_O, Tpd2\_O, T4B\_O)의 게이트 바이어스 스트레스를 감소시키기 위한 제1 BTS 보상부를 구비한다. 제n 스테이지(STGn)를 구성하는 소자들의 세부 접속 구성은 전술한 실시예들에서 설명한 것과 유사하여 생략하기로 한다.

[0055] 그리고, 제n+1 스테이지(STGn+1)는, 제n+1 게이트 출력신호(Vg(n+1))가 출력되는 제2 출력노드(N02), 제2 Q 노드(Q2)의 전위에 따라 스위칭되는 제2 풀업 TFT(Tpu2), 제1 QB 노드(QB\_O)의 전위에 따라 스위칭되는 제2-1 풀다운 TFT(Tpd2\_O), 제2 QB 노드(QB\_E)의 전위에 따라 스위칭되는 제2-2 풀다운 TFT(Tpd2\_E), 제2 Q 노드(Q2)를 충전 및 방전시키기 위한 제1-2, 제3-2, 제4-3 및 제4-4 스위치 TFT(T1B, T3B, T4B\_O, T4B\_E), 제2 Q 노드(Q2)의 전위에 따라 제2 QB 노드(QB\_E)를 방전시키기 위한 제2-2 스위치 TFT(T2\_E), 제2 QB 노드(QB\_E)의 전위에 따라 스위칭되는 TFT들(Tpd1\_E, T4A\_E, Tpd2\_E, T4B\_E)의 게이트 바이어스 스트레스를 감소시키기 위한 제2 BTS 보상부를 구비한다. 제n+1 스테이지(STGn+1)를 구성하는 소자들의 세부 접속 구성은 전술한 실시예들에서 설명한 것과 유사하여 생략하기로 한다.

[0056] 한편, 제n 스테이지(STGn)는 제8-1 스위치 TFT(T8\_O)를 더 포함할 수 있고, 제n+1 스테이지(STGn+1)는 제8-2 스위치 TFT(T8\_E)를 더 포함할 수 있다. 제8-1 스위치 TFT(T8\_O)는 제1 QB 노드(QB\_O)가 정상 구동될 때, 제1 스타트신호(Vst1)에 따라 제1 QB 노드(QB\_O)를 저전위 레벨(VL)로 방전시킴으로써 도 13의 ① 구간에서 제4-1 및 제4-3 스위치 TFT(T4A\_O, T4B\_O)를 완전히 오프 시키고 제1 및 제2 Q 노드(Q1, Q2)의 안정적인 충전을 유도한다. 제8-2 스위치 TFT(T8\_E)는 제2 QB 노드(QB\_E)가 정상 구동될 때, 제1 스타트신호(Vst1)에 따라 제2 QB 노드(QB\_E)를 저전위 레벨(VL)로 방전시킴으로써 도 13의 ① 구간에서 제4-2 및 제4-4 스위치 TFT(T4A\_E, T4B\_E)를 완전히 오프 시키고 제1 및 제2 Q 노드(Q1, Q2)의 안정적인 충전을 유도한다.

[0057] 미리 정해진 기간(예컨대, k 프레임 기간)을 주기로 제1 QB 노드(QB\_O)와 제2 QB 노드(QB\_E)는 번갈아 휴지 구동되며, 휴지 구동되는 QB 노드는 계속해서 저전위 레벨(VL)로 유지된다. 따라서, 제1 QB 노드(QB\_O)와 관련되는 소자들과 제2 QB 노드(QB\_E)와 관련되는 소자들은 상기 미리 정해진 기간을 주기로 교대로 휴지 구동된다.

[0058] 제1 QB 노드(QB\_O)와 관련되는 소자들에는 제1-1 풀다운 TFT(Tpd1\_O), 제4-1 스위치 TFT(T4A\_O), 제2-1 풀다운 TFT(Tpd2\_O), 제4-3 스위치 TFT(T4B\_O), 제1 BTS 보상부, 및 제8-1 스위치 TFT(T8\_O)가 있다. 그리고, 제2 QB 노드(QB\_E)와 관련되는 소자들에는 제1-2 풀다운 TFT(Tpd1\_E), 제4-2 스위치 TFT(T4A\_E), 제2-2 풀다운 TFT(Tpd2\_E), 제4-4 스위치 TFT(T4B\_E), 제2 BTS 보상부, 및 제8-2 스위치 TFT(T8\_E)가 있다.

[0059] 제n 스테이지(STGn)의 제1 출력노드(N01)를 통해 출력되는 제n 게이트 출력신호(Vg(n))은 n번째 위상을 갖는 클럭(CLKn)에 동기되고, 제n+1 스테이지(STGn+1)의 제2 출력노드(N02)를 통해 출력되는 제n+1 게이트 출력신호(Vg(n+1))은 n+1번째 위상을 갖는 클럭(CLKn+1)에 동기된다. 제n 스테이지(STGn)의 셋 타이밍을 제어하는 제1 스타트신호(Vst1)는 제n 게이트 출력신호(Vg(n))보다 위상이 앞선다. 제n+1 스테이지(STGn+1)의 셋 타이밍을 제어하는 제2 스타트신호(Vst2)는 제n+1 게이트 출력신호(Vg(n+1))보다 위상이 앞서고 제1 스타트신호(Vst1)보다 위상이 뒤진다. 그리고, 제n 스테이지(STGn)와 제n+1 스테이지(STGn+1)를 동시에 리셋시키기 위한 리셋신호(Rst)는 제n+1 게이트 출력신호(Vg(n+1))보다 위상이 뒤진다.

[0060] 제1 BTS 보상부는 방전제어신호(QBR)에 따라 제1 QB 노드(QB\_O)를 주기적으로 방전시켜 제1 QB 노드(QB\_O)의 전위에 따라 스위칭되는 TFT들(Tpd1\_O, T4A\_O, Tpd2\_O, T4B\_O)의 게이트 바이어스 스트레스를 감소시키는 역할을 한다. 여기서, 방전제어신호(QBR)는 n+1번째 위상을 갖는 클럭(CLKn+1) 즉, 도 13의 예에서 제2 클럭(CLK2)으로 선택될 수 있다. 이를 위해, 제1 BTS 보상부는 방전제어신호(QBR)에 응답하여 스위칭됨으로써 상기 제1 QB 노드(QB\_O)를 저전위 레벨(VL)로 방전시키는 제5-1 스위치 TFT(T5\_O)를 포함한다. 제5-1 스위치 TFT(T5\_O)의 게이트전극은 방전제어신호(QBR)의 입력 단자에, 드레인전극은 제1 QB 노드(QB\_O)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제5-1 스위치 TFT(T5\_O)는 방전제어신호(QBR)인 제2 클럭(CLK2)이 고전위 레벨(VH)로 입력될 때마다 터 온 됨으로써, 제1 QB 노드(QB\_O)를 저전위 전압(VSS)의 입력단에 연결함으로써 제1

QB 노드(QB\_0)를 방전시킨다. 한편, 제1 BTS 보상부는, 방전제어신호(QBR)에 응답하여 스위칭되어 제1 출력 노드(NO1)를 저전위 레벨(VL)로 방전시키는 제6-1 스위치 TFT(T6\_0)을 더 포함함으로써, 제n 스테이지(STGn)가 리셋된 직후부터 그 다음 프레임에서 셋되기 직전까지 제n 게이트 출력신호(Vg(n))를 안정적으로 게이트 로우 전압으로 유지시킨다. 제6-1 스위치 TFT(T6\_0)의 게이트전극은 방전제어신호(QBR)의 입력 단자에, 드레인전극은 제1 QB 노드(QB\_0)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제6-1 스위치 TFT(T6\_0)의 스위칭 작용에 의해 제n 게이트 출력신호(Vg(n))에 포함되는 리플 성분은 효과적으로 제거될 수 있다.

[0061] 제2 BTS 보상부는 미리 정해진 기간(예컨대, k 프레임 기간)을 주기로 제1 BTS 보상부와 교대로 구동된다. 제2 BTS 보상부는 방전제어신호(QBR)에 따라 제2 QB 노드(QB\_E)를 주기적으로 방전시켜 제2 QB 노드(QB\_E)의 전위에 따라 스위칭되는 TFT들(Tpd1\_E, T4A\_E, Tpd2\_E, T4B\_E)의 게이트 바이어스 스트레스를 감소시키는 역할을 한다. 이를 위해, 제2 BTS 보상부는 방전제어신호(QBR)에 응답하여 스위칭됨으로써 상기 제2 QB 노드(QB\_E)를 저전위 레벨(VL)로 방전시키는 제5-2 스위치 TFT(T5\_E)를 포함한다. 제5-2 스위치 TFT(T5\_E)의 게이트전극은 방전제어신호(QBR)의 입력 단자에, 드레인전극은 제2 QB 노드(QB\_E)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제5-2 스위치 TFT(T5\_E)는 방전제어신호(QBR)인 제2 클럭(CLK2)이 고전위 레벨(VH)로 입력될 때마다 턴 온 됨으로써, 제2 QB 노드(QB\_E)를 저전위 전압(VSS)의 입력단에 연결함으로써 제2 QB 노드(QB\_E)를 방전시킨다. 한편, 제2 BTS 보상부는, 방전제어신호(QBR)에 응답하여 스위칭되어 제2 출력 노드(NO2)를 저전위 레벨(VL)로 방전시키는 제6-2 스위치 TFT(T6\_E)를 더 포함함으로써, 제n+1 스테이지(STGn+1)가 리셋된 직후부터 그 다음 프레임에서 셋되기 직전까지 제n+1 게이트 출력신호(Vg(n+1))를 안정적으로 게이트 로우 전압으로 유지시킨다. 제6-2 스위치 TFT(T6\_E)의 게이트전극은 방전제어신호(QBR)의 입력 단자에, 드레인전극은 제2 QB 노드(QB\_E)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제6-2 스위치 TFT(T6\_E)의 스위칭 작용에 의해 제n+1 게이트 출력신호(Vg(n+1))에 포함되는 리플 성분은 효과적으로 제거될 수 있다.

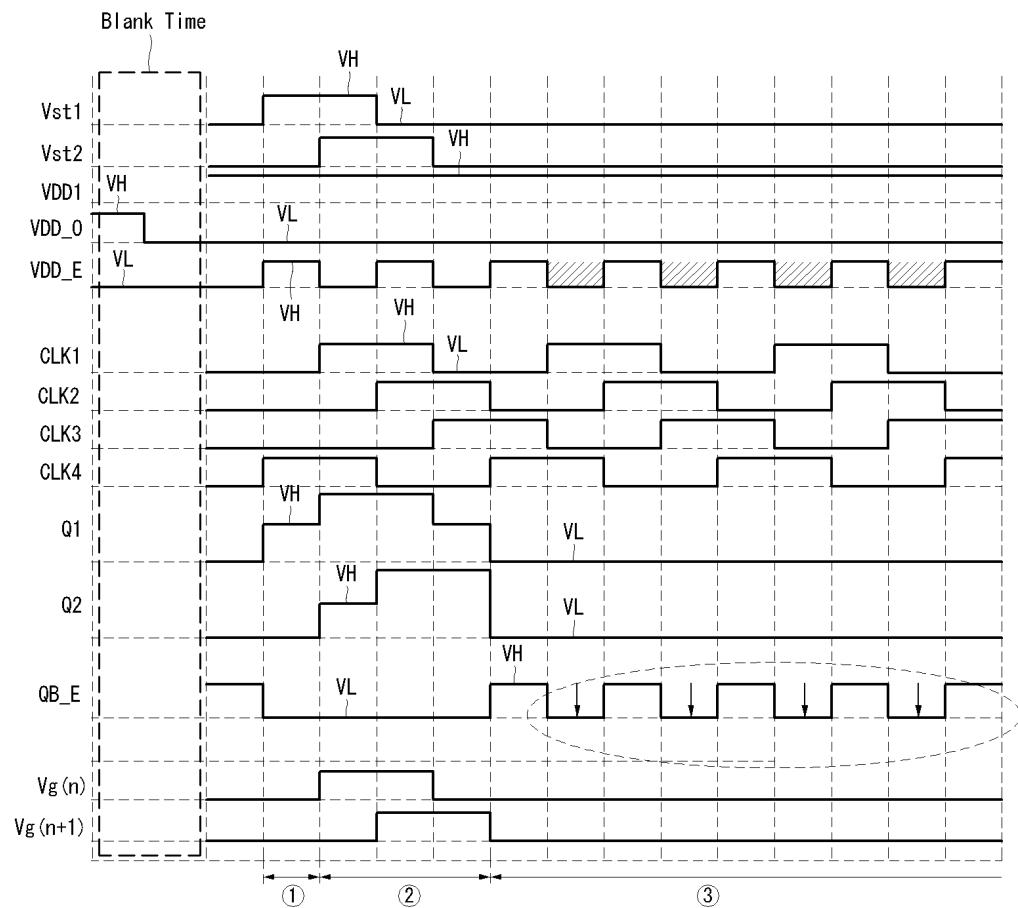

[0062] 도 13에는 도 12의 제n 및 제n+1 스테이지(STGn, STGn+1)의 동작이 도시되어 있다. 도 13은 특정 k 프레임 기간에서 제1 QB 노드(QB\_0)와 관련되는 소자들은 휴지 구동되고 제2 QB 노드(QB\_E)와 관련되는 소자들만이 정상 구동되고 있는 경우를 예로 보여준다. 도 13에서, "Blank Time"은 k 프레임 기간과 k 프레임 기간 사이의 블랭크 시간을 의미한다.

[0063] 도 13의 동작 과정은 전술한 실시예들에서 설명한 것과 유사하여 그 상세한 설명은 생략한다. 도 13의 ④ 기간에서 방전제어신호(QBR)로 선택되는 제2 클럭(CLK2)에 의해 제5-2 스위치 TFT(T5\_E)가 주기적으로 턴 온 되면, 그때마다 제2 QB 노드(QB\_E)는 저전위 레벨(VL)로 방전된다. 이러한 QB 노드의 주기적인 방전 동작은 그 다음 프레임에서 셋되기 직전까지 행해질 수 있다. ④ 기간 동안 제2 QB 노드(QB\_E)는 주기적으로 방전되기 때문에, 제2 QB 노드(QB\_E)에 따라 스위칭되는 TFT들의 게이트 바이어스 스트레스는, 종래 QB 노드의 전위가 계속해서 고전위 레벨(VH)로 유지될 때에 비해 현저히 감소된다.

[0064] 도 14는 도 11에 도시된 스테이지들(STG1~STG4, ...) 중 QB 노드들을 공유하는 제n 스테이지(STGn)와 제n+1 스테이지(STGn+1)의 다른 구성을 보여준다. 그리고, 도 15는 도 14에 도시된 제n 스테이지(STGn)와 제n+1 스테이지(STGn+1)의 동작 파형을 보여준다.

[0065] 도 14의 스테이지 구성은 도 12와 비교하여, 제1 및 제2 BTS 보상부의 구성만이 다를 뿐, 나머지 구성은 실질적으로 동일하다.

[0066] 도 14의 제1 BTS 보상부는 제1 방전제어신호(QBR1)에 응답하여 스위칭됨으로써 제1 QB 노드(QB\_0)를 저전위 레벨(VL)로 방전시키는 제5-1 오드 스위치 TFT(T5-1\_0)와, 제2 방전제어신호(QBR2)에 응답하여 스위칭됨으로써 제1 QB 노드(QB\_0)를 저전위 레벨(VL)로 방전시키는 제5-2 오드 스위치 TFT(T5-2\_0)를 포함한다. 제5-1 오드 스위치 TFT(T5-1\_0)의 게이트전극은 제1 방전제어신호(QBR1)의 입력 단자에, 드레인전극은 제1 QB 노드(QB\_0)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제5-2 오드 스위치 TFT(T5-2\_0)의 게이트전극은 제2 방전제어신호(QBR2)의 입력 단자에, 드레인전극은 제1 QB 노드(QB\_0)에, 그리고 소스전극은 저전위 전압(VS S)의 입력단에 접속된다.

[0067] 이 제1 BTS 보상부는 제1 및 제2 방전제어신호(QBR1, QBR2)에 따라 제1 QB 노드(QB\_0)를 주기적으로 방전시켜 제1 QB 노드(QB\_0)의 전위에 따라 스위칭되는 TFT들(Tpd1\_0, T4A\_0, Tpd2\_0, T4B\_0)의 게이트 바이어스 스트레스를 감소시키는 역할을 한다. 여기서, 제1 방전제어신호(QBR1)는 n+1번째 위상을 갖는 클럭(CLKn+1)의 일부와 중첩되는 별도의 제1 보조 클럭(즉, 도 15의 예에서 ACLK1)으로 선택되고, 제2 방전제어신호(QBR2)는 n+1번째 위상을 갖는 클럭(CLKn+1)의 나머지와 중첩되는 별도의 제2 보조 클럭(즉, 도 15의 예에서 ACLK2)으로 선택될 수 있다. 제1 및 제2 보조클럭(ACLK1, ACLK2)의 온 듀티는 각각 4상 클럭들(CLK1~CLK4)의 온 듀티의 1/2로

설정된다. 따라서, 제5-1 오드 스위치 TFT(T5-1\_0)와 제5-2 오드 스위치 TFT(T5-2\_0)는 제1 및 제2 보조클럭(ACLK1, ACLK2)이 고전위 레벨(VH)로 입력될 때마다 교대로 턴 온 됨으로써, 제1 QB 노드(QB\_0)를 저전위 전압(VSS)의 입력단에 연결함으로써 제1 QB 노드(QB\_0)를 방전시킨다. 제5-1 오드 스위치 TFT(T5-1\_0)와 제5-2 오드 스위치 TFT(T5-2\_0)는 1/2 온 듀티로 교대로 턴 온 되기 때문에, 도 11의 비해 스위치 열화가 절반으로 줄어든다.

[0068] 한편, 도 14의 제1 BTS 보상부는, 제1 방전제어신호(QBR1)에 응답하여 스위칭되어 제1 출력 노드(N01)를 저전위 레벨(VL)로 방전시키는 제6-1 오드 스위치 TFT(T6-1\_0)와, 제2 방전제어신호(QBR2)에 응답하여 스위칭되어 제1 출력 노드(N01)를 저전위 레벨(VL)로 방전시키는 제6-2 오드 스위치 TFT(T6-2\_0)를 더 포함함으로써, 제n 스테이지(STGn)가 리셋된 직후부터 그 다음 프레임에서 셋되기 직전까지 제n 게이트 출력신호(Vg(n))를 안정적으로 게이트 로우 전압으로 유지시킨다. 제6-1 오드 스위치 TFT(T6-1\_0)의 게이트전극은 제1 방전제어신호(QBR1)의 입력 단자에, 드레인전극은 제1 QB 노드(QB\_0)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속되고, 제6-2 오드 스위치 TFT(T6-2\_0)의 게이트전극은 제2 방전제어신호(QBR2)의 입력 단자에, 드레인전극은 제1 QB 노드(QB\_0)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제6-1 및 제6-2 오드 스위치 TFT(T6-1\_0, T6-2\_0)의 스위칭 작용에 의해 제n 게이트 출력신호(Vg(n))에 포함되는 리플 성분은 효과적으로 제거될 수 있다.

[0069] 도 14의 제2 BTS 보상부는 미리 정해진 기간(예컨대, k 프레임 기간)을 주기로 제1 BTS 보상부와 교대로 구동된다. 제2 BTS 보상부는 제1 방전제어신호(QBR1)에 응답하여 스위칭됨으로써 제2 QB 노드(QB\_E)를 저전위 레벨(VL)로 방전시키는 제5-1 이븐 스위치 TFT(T5-1\_E)와, 제2 방전제어신호(QBR2)에 응답하여 스위칭됨으로써 제2 QB 노드(QB\_E)를 저전위 레벨(VL)로 방전시키는 제5-2 이븐 스위치 TFT(T5-2\_E)를 포함한다. 제5-1 이븐 스위치 TFT(T5-1\_E)의 게이트전극은 제1 방전제어신호(QBR1)의 입력 단자에, 드레인전극은 제2 QB 노드(QB\_E)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제5-2 이븐 스위치 TFT(T5-2\_E)의 게이트전극은 제2 방전제어신호(QBR2)의 입력 단자에, 드레인전극은 제2 QB 노드(QB\_E)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다.

[0070] 이 제2 BTS 보상부는 제1 및 제2 방전제어신호(QBR1, QBR2)에 따라 제2 QB 노드(QB\_E)를 주기적으로 방전시켜 제2 QB 노드(QB\_E)의 전위에 따라 스위칭되는 TFT들(Tpd1\_E, T4A\_E, Tpd2\_E, T4B\_E)의 게이트 바이어스 스트레스를 감소시키는 역할을 한다. 제5-1 이븐 스위치 TFT(T5-1\_E)와 제5-2 이븐 스위치 TFT(T5-2\_E)는 제1 및 제2 보조클럭(ACLK1, ACLK2)이 고전위 레벨(VH)로 입력될 때마다 교대로 턴 온 됨으로써, 제2 QB 노드(QB\_E)를 저전위 전압(VSS)의 입력단에 연결함으로써 제2 QB 노드(QB\_E)를 방전시킨다. 제5-1 이븐 스위치 TFT(T5-1\_E)와 제5-2 이븐 스위치 TFT(T5-2\_E)는 1/2 온 듀티로 교대로 턴 온 되기 때문에, 도 11의 비해 스위치 열화가 절반으로 줄어든다.

[0071] 한편, 도 14의 제2 BTS 보상부는, 제1 방전제어신호(QBR1)에 응답하여 스위칭되어 제2 출력 노드(N02)를 저전위 레벨(VL)로 방전시키는 제6-1 이븐 스위치 TFT(T6-1\_E)와, 제2 방전제어신호(QBR2)에 응답하여 스위칭되어 제2 출력 노드(N02)를 저전위 레벨(VL)로 방전시키는 제6-2 이븐 스위치 TFT(T6-2\_E)를 더 포함함으로써, 제n+1 스테이지(STGn+1)가 리셋된 직후부터 그 다음 프레임에서 셋되기 직전까지 제n+1 게이트 출력신호(Vg(n+1))를 안정적으로 게이트 로우 전압으로 유지시킨다. 제6-1 이븐 스위치 TFT(T6-1\_E)의 게이트전극은 제1 방전제어신호(QBR1)의 입력 단자에, 드레인전극은 제2 QB 노드(QB\_E)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속되고, 제6-2 이븐 스위치 TFT(T6-2\_E)의 게이트전극은 제2 방전제어신호(QBR2)의 입력 단자에, 드레인전극은 제2 QB 노드(QB\_E)에, 그리고 소스전극은 저전위 전압(VSS)의 입력단에 접속된다. 제6-1 및 제6-2 이븐 스위치 TFT(T6-1\_E, T6-2\_E)의 스위칭 작용에 의해 제n+1 게이트 출력신호(Vg(n+1))에 포함되는 리플 성분은 효과적으로 제거될 수 있다.

[0072] 도 15에 도시된 스테이지들의 동작 과형은, 제1 내지 제4 클럭(CLK1~CLK4)에 비해 하프 듀티를 갖는 제1 및 제2 보조 클럭(ACLK1, ACLK2)에 따라 제2 QB 노드(QB\_E)가 ④ 기간에서 주기적으로 방전되는 것만 제외하고, 그 외 나머지 동작은 도 13에서 설명한 것과 실질적으로 동일하다.

[0073] 도 16은 도 11에 도시된 스테이지들(STG1~STG4, ...) 중 QB 노드들을 공유하는 제n 스테이지(STGn)와 제n+1 스테이지(STGn+1)의 또 다른 구성을 보여준다. 그리고, 도 17은 도 16에 도시된 제n 스테이지(STGn)와 제n+1 스테이지(STGn+1)의 동작 과형을 보여준다.

[0074] 도 16의 스테이지 구성은 도 12와 비교하여, 제1 및 제2 BTS 보상부의 구성만이 다를 뿐, 나머지 구성은 실질적으로 동일하다.

- [0075] 제1 BTS 보상부와 제2 BTS 보상부는 미리 정해진 기간(예컨대, k 프레임 기간)을 주기로 교대로 구동된다. 제1 교류 고전위 전압(AVDD\_O)과 제2 교류 고전위 전압(AVDD\_E)은 상기 미리 정해진 기간을 주기로 교대로 교류 전압으로 입력되며, 제1 교류 고전위 전압(AVDD\_O)과 제2 교류 고전위 전압(AVDD\_E) 중 어느 하나가 고전위 레벨(VH)과 저전위 레벨(VL)로 스윙되는 교류 전압으로 입력될 때, 나머지 하나는 저전위 레벨(VL)의 직류 전압으로 입력된다.

- [0076] 제1 BTS 보상부의 동작은, 제1 교류 고전위 전압(AVDD\_O)이 교류 전압으로 입력될 때 활성화되는 반면, 제1 교류 고전위 전압(AVDD\_O)이 직류 전압으로 입력될 때 비활성화된다. 마찬가지로, 제2 BTS 보상부의 동작은, 제2 교류 고전위 전압(AVDD\_E)이 교류 전압으로 입력될 때 활성화되는 반면, 제2 교류 고전위 전압(AVDD\_E)이 직류 전압으로 입력될 때 비활성화된다.

- [0077] 도 16의 제1 BTS 보상부는 제1 QB 노드(QB\_O)에 제1 교류 고전위 전압(AVDD\_O)을 공급하는 제5-1 스위치 TFT(T5\_O)를 포함한다. 제5-1 스위치 TFT(T5\_O)는 다이오드 커넥션(diode-connection)되어 제1 교류 고전위 전압(AVDD\_O)의 입력단과 제1 QB 노드(QB\_O)에 접속된다. 다이오드 커넥션을 위해 제5-1 스위치 TFT(T5\_O)의 게이트전극과 드레인전극은 제1 교류 고전위 전압(AVDD\_O)의 입력단에 접속되고, 제5-1 스위치 TFT(T5\_O)의 소스전극은 제1 QB 노드(QB\_O)에 접속된다.

- [0078] 제1 BTS 보상부가 활성화되는 기간에서, 제n 스테이지(STGn)가 리셋 된 직후부터 그 다음 프레임에서 셋되기 직전까지 도 16의 제2-1 스위치 TFT(T2\_O)는 턴 오프 상태를 유지하므로, 제1 QB 노드(QB\_O)의 전위는 교류 형태의 제1 교류 고전위 전압(AVDD\_O)에 의존한다. 제1 QB 노드(QB\_O)의 전위는 제1 교류 고전위 전압(AVDD\_O)이 고전위 레벨(VH)로 입력될 때 충전되고 저전위 레벨(VL)로 입력될 때 방전된다. 도 16의 제1 BTS 보상부는 교류 형태의 제1 교류 고전위 전압(AVDD\_O)을 제1 QB 노드(QB\_O)에 인가하여 제1 QB 노드(QB\_O)를 주기적으로 방전시킴으로써, 제1 QB 노드(QB\_O)의 전위에 따라 스위칭되는 TFT들(Tpd1\_O, T4A\_O, Tpd2\_O, T4B\_O)의 게이트 바이어스 스트레스를 감소시키는 역할을 한다.

- [0079] 도 16의 제2 BTS 보상부는 제2 QB 노드(QB\_E)에 제2 교류 고전위 전압(AVDD\_E)을 공급하는 제5-2 스위치 TFT(T5\_E)를 포함한다. 제5-2 스위치 TFT(T5\_E)는 다이오드 커넥션(diode-connection)되어 제2 교류 고전위 전압(AVDD\_E)의 입력단과 제2 QB 노드(QB\_E)에 접속된다. 다이오드 커넥션을 위해 제5-2 스위치 TFT(T5\_E)의 게이트전극과 드레인전극은 제2 교류 고전위 전압(AVDD\_E)의 입력단에 접속되고, 제5-2 스위치 TFT(T5\_E)의 소스전극은 제2 QB 노드(QB\_E)에 접속된다.

- [0080] 제2 BTS 보상부가 활성화되는 기간에서, 제n+1 스테이지(STGn+1)가 리셋 된 직후부터 그 다음 프레임에서 셋되기 직전까지 도 16의 제2-2 스위치 TFT(T2\_E)는 턴 오프 상태를 유지하므로, 제2 QB 노드(QB\_E)의 전위는 교류 형태의 제2 교류 고전위 전압(AVDD\_E)에 의존한다. 제2 QB 노드(QB\_E)의 전위는 제2 교류 고전위 전압(AVDD\_E)이 고전위 레벨(VH)로 입력될 때 충전되고 저전위 레벨(VL)로 입력될 때 방전된다. 도 16의 제2 BTS 보상부는 교류 형태의 제2 교류 고전위 전압(AVDD\_E)을 제2 QB 노드(QB\_E)에 인가하여 제2 QB 노드(QB\_E)를 주기적으로 방전시킴으로써, 제2 QB 노드(QB\_E)의 전위에 따라 스위칭되는 TFT들(Tpd1\_E, T4A\_E, Tpd2\_E, T4B\_E)의 게이트 바이어스 스트레스를 감소시키는 역할을 한다.

- [0081] 도 17은 제2 교류 고전위 전압(AVDD\_E)이 교류 형태로 입력됨에 따라서 제2 BTS 보상부가 활성화되는 동작 예를 보여주고 있다. 도 17의 스테이지들의 동작 과정은, 교류 형태의 제2 교류 고전위 전압(AVDD\_E)에 따라 제2 QB 노드(QB\_E)가 ③ 기간에서 주기적으로 방전되는 것만 제외하고, 그 외 나머지 동작은 도 13에서 설명한 것과 실질적으로 동일하다.

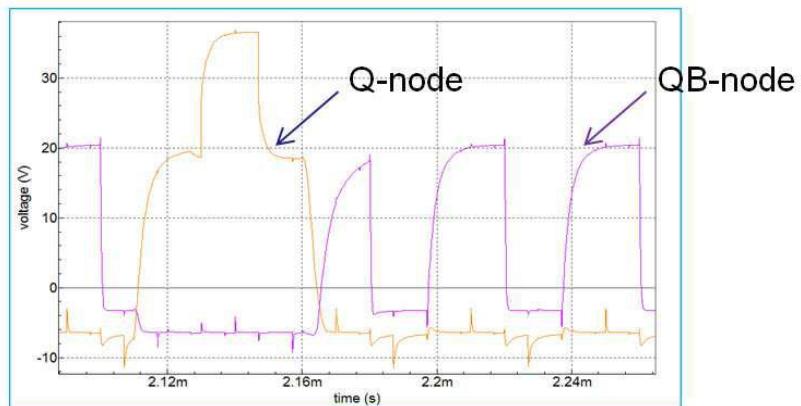

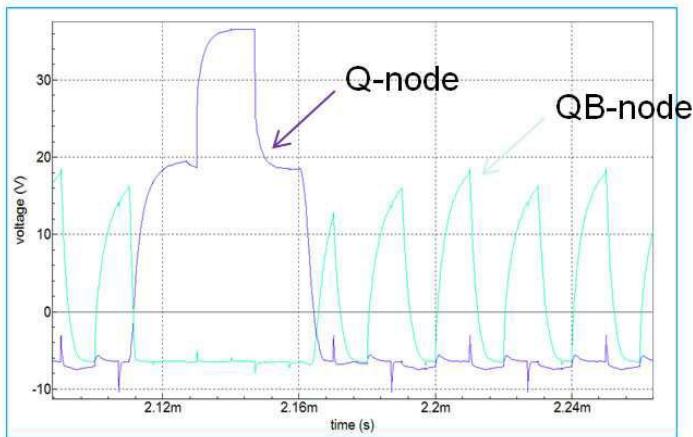

- [0082] 도 18 및 도 19는 전술한 일부 실시예들에 대한 시뮬레이션 결과를 보여주는 과정도들이다.

- [0083] 도 18은 도 5 및 도 7의 스테이지 회로 구성에 대한 시뮬레이션 결과이고, 도 19는 도 9의 스테이지 회로 구성에 대한 시뮬레이션 결과이다.

- [0084] 도 18 및 도 19에서 명확히 알 수 있듯이, QB 노드의 전위는 해당 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋되기 직전까지 종래와 같이 충전 상태로만 유지되지 않고 주기적으로 방전되고 있다. 이를 통해 본 발명은 TFT들의 문턱전압 열화(즉, 문턱전압 쉬프트량)를 줄여 회로의 신뢰성을 제고할 수 있다.

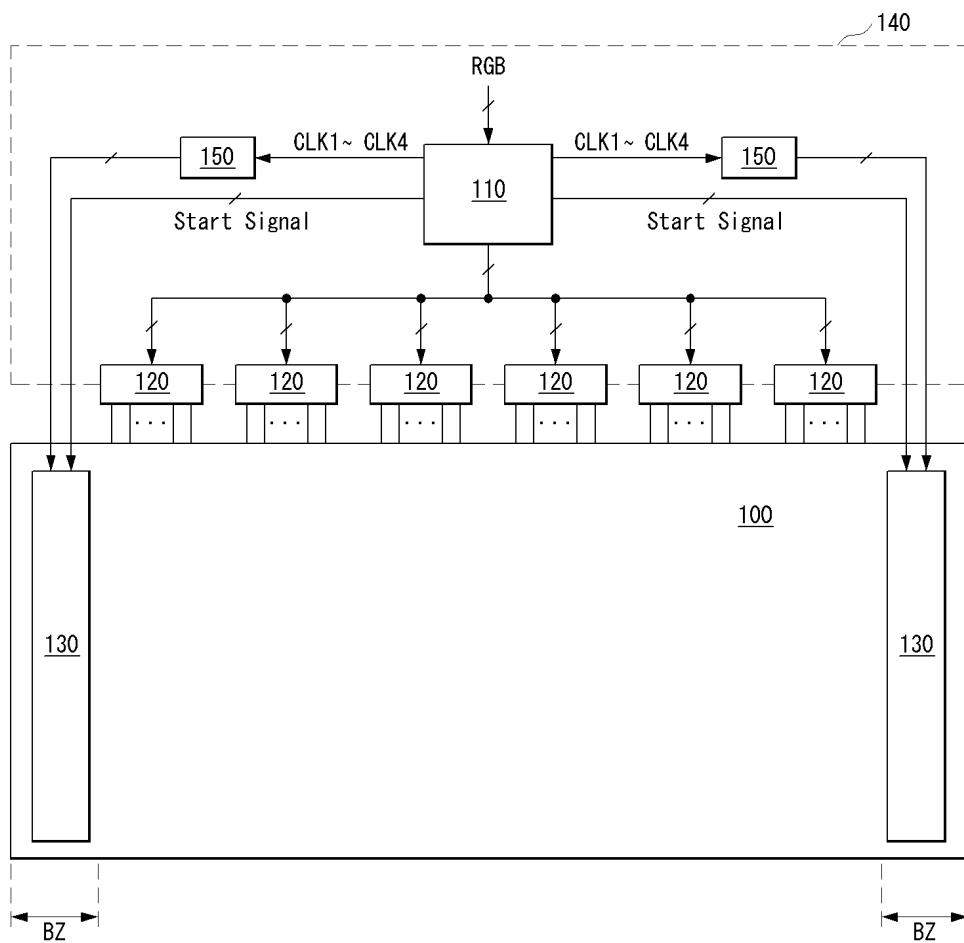

- [0085] 도 20은 본 발명의 실시예에 따른 표시장치를 개략적으로 보여준다.

- [0086] 도 20을 참조하면, 본 발명의 표시장치는 표시패널(100), 데이터 구동회로, 스캔 구동회로, 및 타이밍 콘트롤러(110) 등을 구비한다.

- [0087] 표시패널(100)은 서로 교차되는 데이터라인들 및 스캔라인들과, 매트릭스 형태로 배치된 픽셀들을 포함한다. 표시패널(100)은 액정표시장치(LCD), 유기발광다이오드 표시장치(OLED), 전기영동 표시장치(epd) 중 어느 하나의 표시패널로 구현될 수 있다.

- [0088] 데이터 구동회로는 다수의 소스 드라이브 IC들(120)을 포함한다. 소스 드라이브 IC들(120)은 타이밍 콘트롤러(110)로부터 디지털 비디오 데이터들(RGB)을 입력 받는다. 소스 드라이브 IC들(120)은 타이밍 콘트롤러(110)로부터의 소스 타이밍 제어신호에 응답하여 디지털 비디오 데이터들(RGB)을 감마보상전압으로 변환하여 데이터전압을 발생하고, 그 데이터전압을 스캔펄스에 동기되도록 표시패널(100)의 데이터라인들에 공급한다. 소스 드라이브 IC들은 COG(Chip On Glass) 공정이나 TAB(Tape Automated Bonding) 공정으로 표시패널(100)의 데이터라인들에 접속될 수 있다.

- [0089] 스캔 구동회로는 타이밍 콘트롤러(110)와 표시패널(100)의 스캔라인들 사이에 접속된 레벨 쉬프터(Level Shifter)(150), 및 게이트 쉬프트 레지스터(130)를 구비한다.

- [0090] 레벨 쉬프터(150)는 타이밍 콘트롤러(110)로부터 입력되는 i 상(예컨대, 4상) 게이트 쉬프트 클럭들(CLK1~CLK4)의 TTL(Transistor-Transistor-Logic) 로직 레벨 전압을 표시패널에 형성된 TFT를 스위칭시킬 수 있는 게이트 하이 전압과 게이트 로우 전압으로 레벨 쉬프팅한다.

- [0091] 게이트 쉬프트 레지스터(130)는 전술한 바와 같이 스타트신호를 게이트 쉬프트 클럭(CLK1~CLK4)에 맞추어 쉬프트시켜 순차적으로 게이트 출력신호를 생성하는 스테이지들로 구성된다. 게이트 쉬프트 레지스터(130)의 상세 구성 및 동작 등은 도 4 내지 도 19에서 설명한 바와 같다.

- [0092] 스캔 구동회로는 GIP(Gate In Panel) 방식으로 표시패널(100)의 하부 기판 상에 직접 형성될 수 있다. GIP 방식에서, 레벨 쉬프터(150)는 PCB(140) 상에 실장되고, 게이트 쉬프트 레지스터(130)는 표시패널(100)의 하부 기판 상에 형성될 수 있다. 게이트 쉬프트 레지스터(130)는 표시패널(100)에서 화상이 표시되지 않는 영역(즉, 베젤 영역(BZ))에 형성된다.

- [0093] 타이밍 콘트롤러(110)는 LVDS(Low Voltage Differential Signaling) 인터페이스, TMDS(Transition Minimized Differential Signaling) 인터페이스 등의 인터페이스를 통해 외부의 호스트 컴퓨터로부터 디지털 비디오 데이터(RGB)를 입력 받는다. 타이밍 콘트롤러(110)는 호스트 컴퓨터로부터 입력되는 디지털 비디오 데이터들(RGB)을 소스 드라이브 IC들(120)로 전송한다.

- [0094] 타이밍 콘트롤러(110)는 LVDS 또는 TMDS 인터페이스 수신회로를 통해 호스트 컴퓨터로부터 수직 동기신호(Vsync), 수평 동기신호(Hsync), 데이터 인에이블 신호(Data Enable, DE), 메인 클럭(MCLK) 등의 타이밍신호를 입력받는다. 타이밍 콘트롤러(110)는 호스트 컴퓨터로부터의 타이밍 신호를 기준으로 데이터 구동회로와 스캔 구동회로의 동작 타이밍을 제어하기 위한 타이밍 제어신호들을 발생한다. 타이밍 제어신호들은 스캔 구동회로의 동작 타이밍을 제어하기 위한 스캔 타이밍 제어신호, 소스 드라이브 IC들(120)의 동작 타이밍과 데이터전압의 극성을 제어하기 위한 데이터 타이밍 제어신호를 포함한다.

- [0095] 스캔 타이밍 제어신호는 게이트 스타트 펄스, 게이트 쉬프트 클럭(CLK1~CLK4), 도시하지 않은 게이트 출력 인에이블신호(Gate Output Enable, GOE) 등을 포함한다. 게이트 스타트 펄스는 게이트 쉬프트 레지스터(130)에 입력되어 쉬프트 스타트 타이밍을 제어한다. 게이트 쉬프트 클럭(CLK1~CLK4)은 레벨 쉬프터(150)를 통해 레벨 쉬프팅된 후에 게이트 쉬프트 레지스터(130)에 입력되며, 스타트 신호를 쉬프트시키기 위한 클럭신호로 이용된다. 게이트 출력 인에이블신호(GOE)는 게이트 쉬프트 레지스터(130)의 출력 타이밍을 제어한다.

- [0096] 데이터 타이밍 제어신호는 소스 스타트 펄스(Source Start Pulse, SSP), 소스 샘플링 클럭(Source Sampling Clock, SSC), 극성제어신호(Polarity, POL), 및 소스 출력 인에이블신호(Source Output Enable, SOE) 등을 포함한다. 소스 스타트 펄스(SSP)는 소스 드라이브 IC들(120)의 쉬프트 스타트 타이밍을 제어한다. 소스 샘플링 클럭(SSC)은 라이징 또는 폴링 에지에 기준하여 소스 드라이브 IC들(120) 내에서 데이터의 샘플링 타이밍을 제어하는 클럭신호이다. 극성제어신호(POL)는 소스 드라이브 IC들로부터 출력되는 데이터전압의 극성을 제어한다. 타이밍 콘트롤러(110)과 소스 드라이브 IC들(120) 사이의 데이터 전송 인터페이스가 mini LVDS 인터페이스라면, 소스 스타트 펄스(SSP)와 소스 샘플링 클럭(SSC)은 생략될 수 있다.

[0097]

상술한 바와 같이, 본 발명에 따른 게이트 쉬프트 레지스터와 이를 이용한 표시장치는, QB 노드의 전위를 해당 스테이지가 리셋 된 직후부터 그 다음 프레임에서 셋되기 직전까지 종래와 같이 충전 상태로만 유지시키지 않고 주기적으로 방전함으로써, QB 노드의 전위에 따라 스위칭되는 TFT들의 게이트 바이어스 스트레스를 감소시켜 스캔 구동회로의 수명을 증가시킬 수 있다.

[0098]

이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정 되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

### 부호의 설명

[0099]

100 : 표시패널

110 : 타이밍 콘트롤러

120 : 소스 드라이브 IC

130 : 게이트 쉬프트 레지스터

140 : PCB

150 : 레벨 쉬프터

### 도면

#### 도면1

#### 도면2

도면3a

도면3b

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

도면11

## 도면12

## 도면13

## 도면14

## 도면15

## 도면16

## 도면17

## 도면18

도면19

도면20

【심사관 직권보정사항】

【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 제14항, 5째줄

【변경전】

시프트

【변경후】

шу프트