(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4792748号

(P4792748)

(45) 発行日 平成23年10月12日(2011.10.12)

(24) 登録日 平成23年8月5日(2011.8.5)

(51) Int.Cl.

F 1

G09F 9/30 (2006.01)

G09F 9/30 338

H01L 27/32 (2006.01)

G09F 9/30 365Z

H01L 51/50 (2006.01)

H05B 33/14 A

請求項の数 12 (全 25 頁)

(21) 出願番号

特願2005-7852 (P2005-7852)

(22) 出願日

平成17年1月14日(2005.1.14)

(65) 公開番号

特開2006-195255 (P2006-195255A)

(43) 公開日

平成18年7月27日(2006.7.27)

審査請求日

平成19年9月12日(2007.9.12)

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(74) 代理人 110001254

特許業務法人光陽国際特許事務所

(74) 代理人 100090033

弁理士 荒船 博司

(74) 代理人 100093045

弁理士 荒船 良男

(72) 発明者 白寄 友之

東京都八王子市石川町2951番地5 カ

シオ計算機株式会社 八王子技術センター

内

最終頁に続く

(54) 【発明の名称】ディスプレイパネル

## (57) 【特許請求の範囲】

## 【請求項1】

基板と、

前記基板上に、トランジスタを備えた複数の画素回路と、

前記各トランジスタの上方を被覆するように形成され、表面に行方向に沿った溝が形成された絶縁膜と、

前記溝に埋設され、前記複数の画素回路にそれぞれ接続され、前記トランジスタのゲート、ソース、ドレインとは異なる導電層を有する複数の給電配線と、

前記複数の給電配線の各自の上及び当該給電配線の周囲の前記絶縁膜上に、前記給電配線の延在方向に沿ってそれぞれ形成された複数の導電性ラインと、

前記複数の導電性ラインを覆い、前記行方向及び列方向に格子状に形成された突条絶縁膜と、

前記突条絶縁膜のうち前記列方向に延在している部分上に形成されたバンクと、

前記絶縁膜上にそれぞれ設けられ、前記突条絶縁膜に囲まれた複数の画素電極と、

対向電極と、

前記複数の画素電極と前記対向電極との間で前記突条絶縁膜に囲まれた発光層と、

を具備することを特徴とするディスプレイパネル。

## 【請求項2】

前記トランジスタは、ソース、ドレインの一方が前記給電配線に接続された駆動トランジスタを有することを特徴とする請求項1に記載のディスプレイパネル。

## 【請求項 3】

前記トランジスタは、前記駆動トランジスタのドレイン - ソース間に書込電流を流すスイッチトランジスタと、発光期間に前記駆動トランジスタのゲートとソース又はドレインの一方との間の電圧を保持する保持トランジスタと、を有することを特徴とする請求項 2 に記載のディスプレイパネル。

## 【請求項 4】

前記溝に埋設され、前記スイッチトランジスタ及び前記保持トランジスタの少なくとも一方に接続された選択配線をさらに有し、

前記給電配線は、前記駆動トランジスタのソース、ドレインの一方に接続されていることとを特徴とする請求項 3 に記載のディスプレイパネル。 10

## 【請求項 5】

前記駆動トランジスタのソース、ドレインの他方に前記画素電極が設けられていることを特徴とする請求項 4 に記載のディスプレイパネル。

## 【請求項 6】

前記導電性ラインは、前記画素電極の元となる導電層をパターニングしてなるコンタクト層を有することを特徴とする請求項 1 から請求項 5 のいずれか一項に記載のディスプレイパネル。

## 【請求項 7】

前記給電配線は、前記トランジスタのゲート及びソース、ドレインの少なくとも一方と同一のトランジスタ用導電層を有することを特徴とする請求項 1 から請求項 6 のいずれか一項に記載のディスプレイパネル。 20

## 【請求項 8】

前記絶縁膜は、前記トランジスタを直接覆うトランジスタ保護絶縁膜を有することを特徴とする請求項 1 から請求項 7 のいずれか一項に記載のディスプレイパネル。

## 【請求項 9】

前記絶縁膜は、前記トランジスタ保護絶縁膜上に設けられた平坦化膜を有することを特徴とする請求項 8 に記載のディスプレイパネル。

## 【請求項 10】

隣接する前記画素電極間の前記バンク上に配置され、前記対向電極に接続された共通配線を備えることを特徴とする請求項 1 から請求項 9 のいずれか一項に記載のディスプレイパネル。 30

## 【請求項 11】

前記共通配線の延在方向は、前記給電配線の延在方向と直交していることを特徴とする請求項 10 に記載のディスプレイパネル。

## 【請求項 12】

前記共通配線は、前記対向電極とは異なる導電層によって形成されていることを特徴とする請求項 10 又は請求項 11 に記載のディスプレイパネル。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、ディスプレイパネルに係り、特に発光素子を用いたディスプレイパネルに関する。

## 【背景技術】

## 【0002】

近年、C R T (Cathode Ray Tube) に代替する新たな映像表示方式を利用した表示装置として、液晶パネルを利用した液晶ディスプレイ (L C D : Liquid Crystal Display)、エレクトロルミネッセンス (E L : Electro Luminescence) 現象を利用した E L ディスプレイ、プラズマディスプレイパネル (以下、P D P : Plasma Display Panel) を利用したプラズマディスプレイ等が開発されている。

## 【0003】

10

20

30

40

50

このうち、ELディスプレイには、エレクトロルミネッセンス素子（以下、EL素子）に無機化合物を用いた無機ELディスプレイと、有機化合物を用いた有機ELディスプレイとに大別され、カラー化が容易であり、無機ELディスプレイと比較して低電圧での動作が可能であるとの観点から、有機ELディスプレイの開発が進められている。

#### 【0004】

この有機ELディスプレイに用いられる有機ELディスプレイパネルの駆動方式は、パッシブマトリクス駆動方式と、アクティブマトリクス駆動方式とが挙げられ、アクティブマトリクス駆動方式を採用した有機ELディスプレイパネルは、高コントラストかつ高精細であるため、パッシブマトリクス駆動方式よりも優れている。

#### 【0005】

例えば、特許文献1に記載された従来のアクティブマトリクス駆動方式の有機ELディスプレイパネルにおいては、有機EL素子と、画像データに応じた電圧信号がゲートに印加されて有機EL素子に電流を流す駆動トランジスタと、この駆動トランジスタのゲートに画像データに応じた電圧信号を供給するためのスイッチングを行うスイッチ用トランジスタとが、画素毎に設けられている。このような有機ELディスプレイパネルでは、走査線が選択されるとスイッチング用トランジスタがオンとなり、瞬時に輝度を表すレベルの電圧が信号線を介して駆動トランジスタのゲートに印加される。これによって、駆動トランジスタがオンとなり、ゲート電圧のレベルに応じた大きさの駆動電流が電源から駆動トランジスタのドレイン - ソースを介して有機EL素子に流れ、有機EL素子が電流の大きさに応じた輝度で発光する。走査線の選択が終了してから次にその走査線が選択されるまでの間では、スイッチ用トランジスタがオフとなっても駆動トランジスタのゲート電圧のレベルが保持され続け、有機EL素子は、駆動電流の大きさに応じた輝度で発光するようになっている。

10

【特許文献1】特開平8-330600号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

しかしながら、上述した有機ELディスプレイパネルの場合、電源線のような複数の有機EL素子に同時に電流を流す配線の電気抵抗によって、電圧降下や、配線を通じた信号の遅延が生じるという問題が生じている。これら電圧降下及び信号遅延を抑制するための対応策として、配線の厚さ寸法又は幅寸法を大きくすることにより配線を低抵抗化する方法が検討されている。ところが、この配線を、有機EL素子を動作させる駆動トランジスタ等の薄膜トランジスタのゲートメタルやソース、ドレインメタルを用いて形成すると、薄膜トランジスタにおける電極の厚さ寸法が要求される特性に応じて設計されているため、言い換えれば発光素子に電流を流すことを前提として設計していないため、配線からまとめて複数の発光素子に電流を流そうとすると、配線の電気抵抗によって、電圧降下が発生したり、配線を通じた電流の流れの遅延が生じたりする。電圧降下及び電流遅延を抑えるために配線を低抵抗化することが望まれるが、そのためにトランジスタのソース、ドレイン電極となる金属層やゲート電極となる金属層を電流が十分に流れる程度にかなり幅広にパターニングして低抵抗配線としたりすると、配線が他の配線や導電体等と平面視して重なる面積が増えてしまい、それらの間で寄生容量が発生してしまい、電流の流れを遅くする要因を発生してしまい、或いはトランジスタアレイ基板側からEL光を射出するいわゆるボトムエミッション構造の場合、EL素子からの発光を配線が遮光してしまうので、発光面積の割合である開口率の低下を招いてしまっていた。また低抵抗化するために薄膜トランジスタのゲート電極を厚くすると、エッティング精度が低くなるばかりでなくゲート電極の段差を平坦化するための平坦化膜（例えば薄膜トランジスタが逆スタガ構造の場合、ゲート絶縁膜に相当）まで厚くしなければならず、トランジスタ特性が大きく変化してしまう恐れがあり、またソース、ドレイン電極を厚くすると、ソース、ドレイン電極のエッティング精度が低下してしまうため、やはりトランジスタの特性に悪影響を及ぼす恐れがある。

20

30

40

50

## 【0007】

本発明は前記した点に鑑みてなされたものであり、電圧低下、電流信号の遅延を抑制することが可能なディスプレイパネルを提供することを目的とする。

## 【課題を解決するための手段】

## 【0008】

以上の課題を解決するために、請求項1に記載の発明に係るディスプレイパネルは、

基板と、

前記基板上に、トランジスタを備えた複数の画素回路と、

前記各トランジスタの上方を被覆するように形成され、表面に行方向に沿った溝が形成

された絶縁膜と、

前記溝に埋設され、前記複数の画素回路にそれぞれ接続され、前記トランジスタのゲート、ソース、ドレインとは異なる導電層を有する複数の給電配線と、

前記複数の給電配線の各々の上及び当該給電配線の周囲の前記絶縁膜上に、前記給電配線の延在方向に沿ってそれぞれ形成された複数の導電性ラインと、

前記複数の導電性ラインを覆い、前記行方向及び列方向に格子状に形成された突条絶縁膜と、

前記突条絶縁膜のうち前記列方向に延在している部分上に形成されたバンクと、

前記絶縁膜上にそれぞれ設けられ、前記突条絶縁膜に囲まれた複数の画素電極と、

対向電極と、

前記複数の画素電極と前記対向電極との間で前記突条絶縁膜に囲まれた発光層、

を具備することを特徴とする。

## 【発明の効果】

## 【0010】

請求項1記載の発明によれば、配線が、複数の画素回路のトランジスタの上方を被覆する保護絶縁膜に形成された溝に埋設されているので、配線の厚さを大きくすることで、低抵抗化を図ることが可能となり、これによって電圧低下及び電流信号遅延の抑制を図ることができる。

## 【発明を実施するための最良の形態】

## 【0012】

以下、本発明を実施するための最良の形態について図面を用いて説明する。但し、以下に述べる実施形態には、本発明を実施するために技術的に好ましい種々の限定が付されているが、発明の範囲を以下の実施形態及び図示例に限定するものではない。

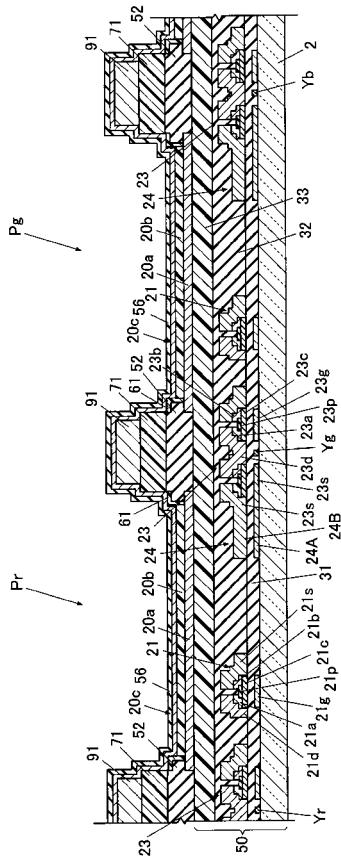

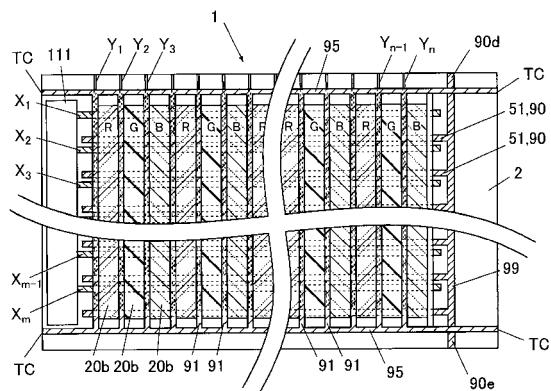

図1から図15を参照しながら、本発明に係るディスプレイパネルについて説明する。

まず始めに、ディスプレイパネルの平面構成について説明する。

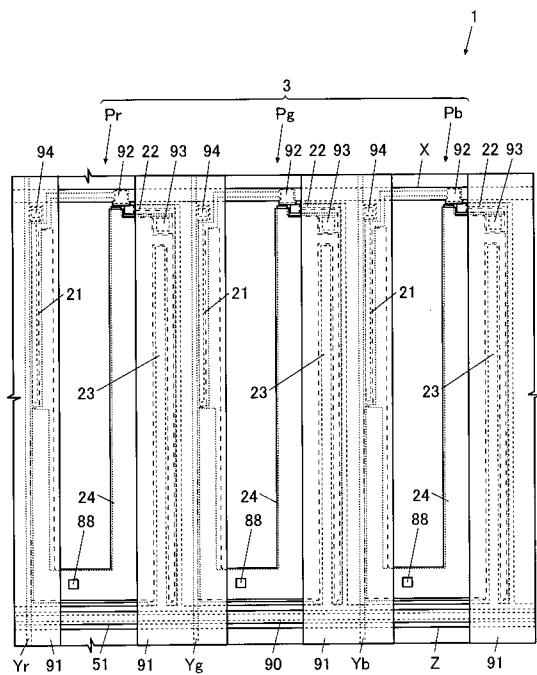

本実施形態におけるディスプレイパネル1は、図1に示すように、画素3がマトリクス状に配置されている。これらの画素3は、略長方形状の1ドットの赤サブピクセルPrと、1ドットの緑サブピクセルPgと、1ドットの青サブピクセルPbとから構成されており、各サブピクセルPr, Pg, Pbは、画素3において、互いの長手方向（以下、垂直方向）が平行となるように、かつ、長手方向と直交する方向（以下、水平方向）に赤サブピクセルPr、緑サブピクセルPg、青サブピクセルPbの順となるように配列されている。

ここで、以下の説明において、これら赤サブピクセルPr、緑サブピクセルPg、青サブピクセルPbのうち、任意のサブピクセルをサブピクセルPと表し、このサブピクセルPについての説明は、赤サブピクセルPr、緑サブピクセルPg、青サブピクセルPbの何れについても適用されるものとする。

## 【0013】

また、図1に示すように、垂直方向の赤サブピクセルPrの列と、青サブピクセルPbの列との間には、信号線Yrが配列されている。また、垂直方向の緑サブピクセルPgの列と、赤サブピクセルPrの列との間には、信号線Ygが配列されている。さらに、垂直方向の青サブピクセルPbの列と、緑サブピクセルPgの列との間には、信号線Ybがそ

10

20

30

40

50

それぞれ配設されている。したがって、水平方向の配列順に着目すると、信号線 Y r、信号線 Y g、信号線 Y b の順に繰り返し配列されており、これら信号線 Y r、信号線 Y g 及び信号線 Y b は、垂直方向に延在すると共に、互いが平行となるように配設されている。

#### 【 0 0 1 4 】

これら信号線 Y r、信号線 Y g 及び信号線 Y b は、垂直方向に沿って一列に配列された全ての赤サブピクセル P r、全ての緑サブピクセル P g、全ての青サブピクセル P b にそれぞれ信号を供給するようになっている。

ここで、以下の説明において、信号線 Y は、赤サブピクセル P r の場合には図 1 の信号線 Y r を表す。また、緑サブピクセル P g の場合には図 1 の信号線 Y g を表す。さらに、青サブピクセル P b の場合には図 1 の信号線 Y b をそれぞれ表す。また、信号線 Y についての説明は、信号線 Y r、信号線 Y g、信号線 Y b の何れについても適用されるものとする。

#### 【 0 0 1 5 】

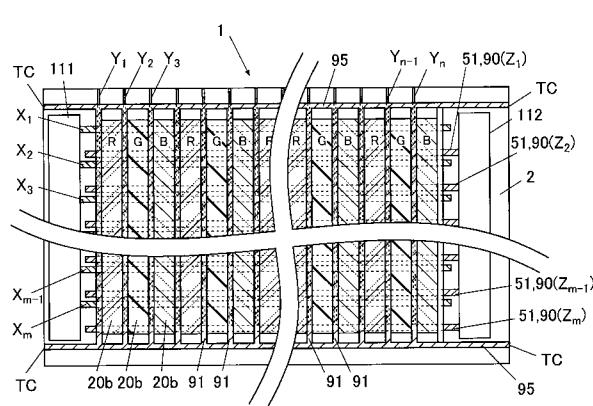

ここで信号線 Y は n 本あり、垂直方向(列方向)に延在した信号線 Y<sub>1</sub> ~ Y<sub>n</sub> は、水平方向(行方向)に延在している m 本の走査線 X<sub>1</sub> ~ X<sub>m</sub>、m 本の給電配線 90, 90, ... 及び m 本の供給線 Z<sub>1</sub> ~ Z<sub>m</sub> と直交している。また、m, n はそれぞれ 2 以上の自然数であり、且つ n は 3 の倍数であり、走査線 X に下付けした数字は、図 7、図 9 において上からの配列順を表し、供給線 Z に下付けした数字は、図 7、図 9 において上からの配列順を表し、信号線 Y に下付けした数字は図 7、図 9 において左からの配列順を表し、サブピクセル P に下付けした数字の前側が上からの配列順を表し、後ろ側が左からの配列順を表す。すなわち、1 ~ m のうちの任意の自然数を i とし、1 から n のうちの任意の自然数を j とした場合に、走査線 X<sub>i</sub> は上から i 行目であり、供給線 Z<sub>i</sub> は左から i 行目であり、信号線 Y<sub>j</sub> は左から j 列目であり、サブピクセル P<sub>i, j</sub> は上から i 行目、左から j 列目であり、サブピクセル P<sub>i, j</sub> は走査線 X<sub>i</sub>、供給線 Z<sub>i</sub> 及び信号線 Y<sub>j</sub> に接続されている。より具体的に、画素 3 における垂直方向の上側には、複数の走査線 X が水平方向に沿って延在して配設されている。一方、画素 3 を挟んで走査線 X と対向する下側には、複数の供給線 Z と、複数の給電配線 90 とが、走査線 X に対して平行に配設されている。したがって、垂直方向の配列順に着目すると、走査線 X、画素 3 の列、供給線 Z の順に繰り返し配列されている。これら走査線 X 及び供給線 Z は、水平方向に沿った一行に配列された各サブピクセル P r, P g, P b に信号を供給するようになっている。

#### 【 0 0 1 6 】

次に、サブピクセル P r, P g, P b の回路構成について説明する。

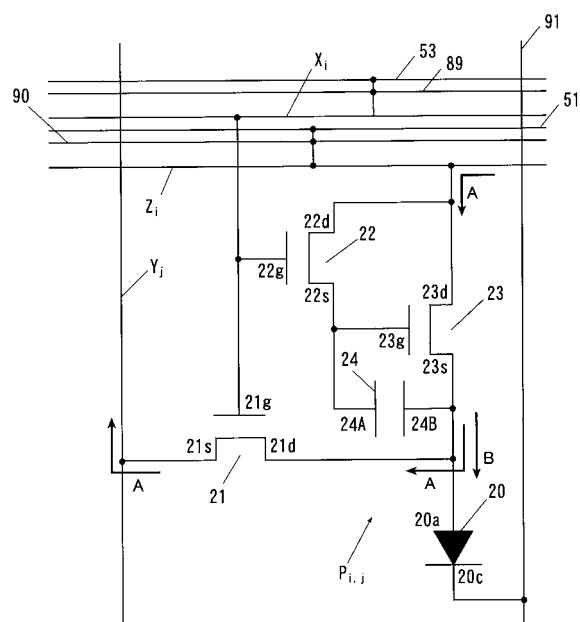

何れのサブピクセル P r, P g, P b も同様に構成されており、1 ドットのサブピクセル P には、図 2 に示すように、いずれも N チャネル型アモルファスシリコン薄膜トランジスタであるスイッチトランジスタ 2 1、保持トランジスタ 2 2 及び駆動トランジスタ 2 3 と、キャパシタ 2 4 とが具備されている画素回路と、有機 EL 素子 2 0 とが設けられている。

#### 【 0 0 1 7 】

有機 EL 素子 2 0 は、画素電極としてサブピクセル電極 2 0 a と、有機 EL 層 2 0 b (図 5 に図示) と、対向電極 2 0 c とを有している。このうち、対向電極 2 0 c は、共通配線 9 1 に導通されている。

#### 【 0 0 1 8 】

スイッチトランジスタ 2 1 は、ソース 2 1 s と、ドレイン 2 1 d と、ゲート 2 1 g を有する。このうち、ソース 2 1 s は、信号線 Y と導通され、ドレイン 2 1 d は、有機 EL 素子 2 0 のサブピクセル電極 2 0 a と、駆動トランジスタ 2 3 のソース 2 3 s と、キャパシタ 2 4 の電極 2 4 b とに導通され、ゲート 2 1 g は、保持トランジスタ 2 2 のゲート 2 2 g と、走査線 X と導通されている。

#### 【 0 0 1 9 】

保持トランジスタ 2 2 は、ソース 2 2 s と、ドレイン 2 2 d と、ゲート 2 2 g を有する。このうち、ソース 2 2 s は、駆動トランジスタ 2 3 のゲート 2 3 g と、キャパシタ 2

10

20

30

40

50

4の電極24Aと導通され、ドレイン22dは、駆動トランジスタ23のドレイン23dと、供給線Zと導通され、ゲート22gは、スイッチトランジスタ21のゲート21gと、走査線Xとに導通されている。なお、保持トランジスタ22のドレイン22dは、駆動トランジスタ23のドレイン23dと導通せずに走査線Xに接続されていてもよい。

【0020】

駆動トランジスタ23は、ソース23sと、ドレイン23dと、ゲート23gとを有する。このうち、ソース23sは、有機EL素子20のサブピクセル電極20aと、スイッチトランジスタ21のドレイン21dと、キャパシタ24の電極24Bとに導通され、ドレイン23dは、保持トランジスタ22のドレイン22dと、供給線Zとに導通され、ゲート23gは、保持トランジスタ22のソース22sと、キャパシタ24の電極24Aとに導通されている。

10

【0021】

キャパシタ24は、絶縁基板2上に上下方向に重なるように形成された電極24A及び電極24Bと、電極24Aと電極24Bとの間に介在する誘電体とを有している。何れのサブピクセルPr, Pg, Pbでもキャパシタ24は同様の層構造になっている。

【0022】

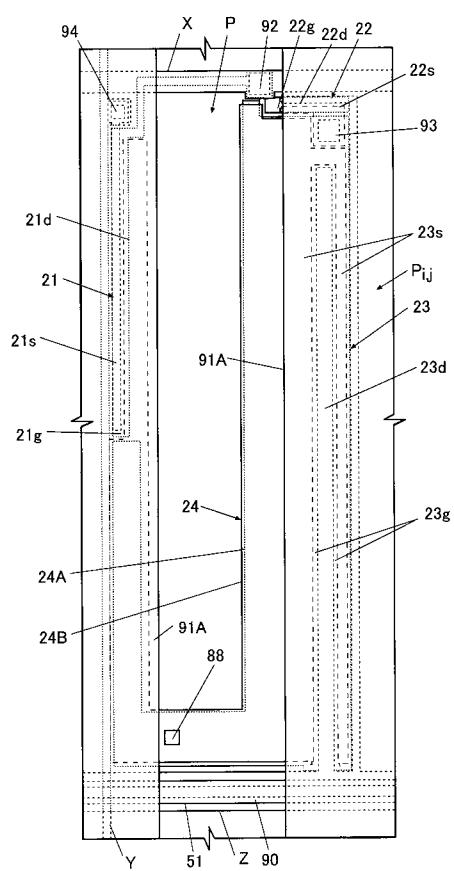

次に、サブピクセルの平面構成について説明する。

図3に示すように、各サブピクセルPr, Pg, Pbについて平面視した場合、スイッチトランジスタ21は、信号線Yに沿って配置されている。また、保持トランジスタ22は、走査線Xに隣接するサブピクセルPの角部に配置されている。さらに、駆動トランジスタ23は、隣接する信号線Yに沿ってそれぞれ配置されており、キャパシタ24は、駆動トランジスタ23に沿って配置されている。

20

【0023】

また、ディスプレイパネル1全体を平面視して、各サブピクセルPr, Pg, Pbにおけるスイッチトランジスタ21、保持トランジスタ22及び駆動トランジスタ23のそれぞれに着目すると、各トランジスタ21, 22, 23は、マトリクス状にそれぞれ配列されている。

【0024】

有機EL素子20のサブピクセル電極20aは、図1及び図3において、トランジスタ21, 22, 23を見やすくするとの観点から省略されているが、これらサブピクセル電極20aは、水平方向に隣接する信号線Yと、垂直方向に隣り合う供給線Z及び走査線Xとによって囲繞された矩形領域内に配置されている。また、サブピクセル電極20aは、その矩形領域に沿うように矩形状に形成されているため、ディスプレイパネル1全体を平面視して、各サブピクセルPr, Pg, Pbのサブピクセル電極20aだけに着目すると、複数のサブピクセル電極20aがマトリクス状に配列されている。

30

【0025】

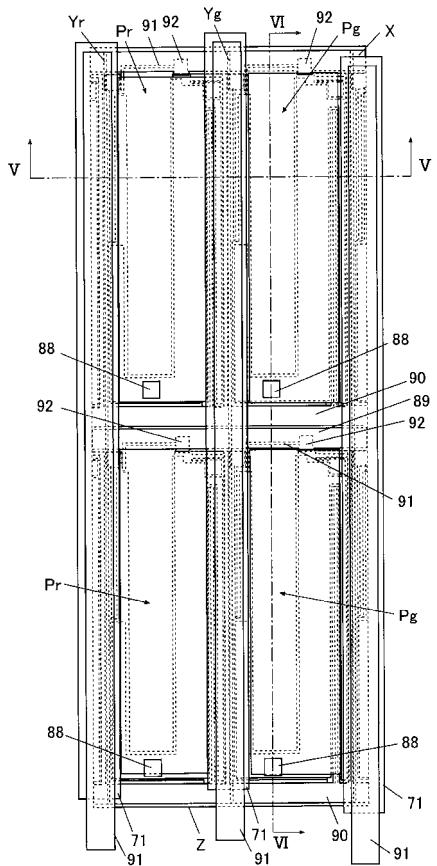

次に、ディスプレイパネル1の層構造について説明する。

図5は、図4に示された破断線V-Vに沿って絶縁基板2の厚さ方向に切断した矢視断面図であり、図6は、図4に示された破断線VI-VIに沿って絶縁基板2の厚さ方向に切断した矢視断面図である。ディスプレイパネル1には、図5に示すように、光透過性を有する可撓性を有するシート状、または剛性を有する板状の絶縁基板2が具備されており、この絶縁基板2の上面には、スイッチトランジスタ21、保持トランジスタ22、駆動トランジスタ23及びキャパシタ24が層構造となるように形成されている。

40

【0026】

図5に示すように、スイッチトランジスタ21は、絶縁基板2の上面に形成されたゲート21gと、ゲート21gの上部に形成されたゲート絶縁膜31と、ゲート絶縁膜31を挟んでゲート21gに対向した半導体膜21cと、半導体膜21cの中央部上に形成されたチャネル保護膜21pと、半導体膜21cの両端部上において互いに離間するよう形成され、チャネル保護膜21pに一部重なった不純物半導体膜21a, 21bと、不純物半導体膜21aの上部に形成されたドレイン21dと、不純物半導体膜21bの上部に形成

50

されたソース 2 1 s とを有している。

【0027】

なお、ドレイン 2 1 d 及びソース 2 1 s は、一層構造であってもよいし、二層以上の積層構造であってもよい。

【0028】

また、保持トランジスタ 2 2 は、その層構造について図示しないが、スイッチトランジスタ 2 1 と同様に、絶縁基板 2 の上面に形成されたゲート 2 2 g と、ゲート 2 2 g の上に形成されたゲート絶縁膜 3 1 と、ゲート絶縁膜 3 1 を挟んでゲート 2 2 g に対向した半導体膜 2 2 c と、半導体膜 2 2 c の中央部上に形成されたチャネル保護膜 2 2 p と、半導体膜 2 2 c の両端部上において互いに離間するよう形成され、チャネル保護膜 2 2 p に一部重なった不純物半導体膜 2 2 a, 2 2 b と、不純物半導体膜 2 2 a の上に形成されたドレイン 2 2 d と、不純物半導体膜 2 2 b の上に形成されたソース 2 2 s と、を有している。

【0029】

図 5 に示すように、駆動トランジスタ 2 3 は、絶縁基板 2 の上面に形成されたゲート 2 3 g と、ゲート 2 3 g の上部に形成されたゲート絶縁膜 3 1 と、ゲート絶縁膜 3 1 を挟んでゲート 2 3 g に対向した半導体膜 2 3 c と、半導体膜 2 3 c の中央部上に形成されたチャネル保護膜 2 3 p と、半導体膜 2 3 c の両端部上において互いに離間するよう形成され、チャネル保護膜 2 3 p に一部重なった不純物半導体膜 2 3 a, 2 3 b と、不純物半導体膜 2 3 a の上に形成されたドレイン 2 3 d と、不純物半導体膜 2 3 b の上に形成されたソース 2 3 s とから構成されている。このような駆動トランジスタ 2 3 は、図 3 及び図 4 に示すように、コの字状に形成されることで、チャンネル幅が広くなるようになっている。

【0030】

なお、ドレイン 2 3 d 及びソース 2 3 s は、一層構造であってもよいし、二層以上の積層構造であってもよい。

【0031】

キャパシタ 2 4 は、絶縁基板 2 の上面に形成された電極 2 4 A と、誘電体として電極 2 4 A の上部に形成されたゲート絶縁膜 3 1 と、ゲート絶縁膜 3 1 を挟んで電極 2 4 A に対向した電極 2 4 B と、を有している。

【0032】

これらスイッチトランジスタ 2 1 、保持トランジスタ 2 2 、駆動トランジスタ 2 3 及びキャパシタ 2 4 は、何れのサブピクセル P r , P g , P b においても同様の層構造となっている。

【0033】

また、スイッチトランジスタ 2 1 のゲート 2 1 g 、保持トランジスタ 2 2 のゲート 2 2 g 、駆動トランジスタ 2 3 のゲート 2 3 g 、キャパシタ 2 4 の電極 2 4 A 及び全ての信号線 Y r , Y g , Y b は、絶縁基板 2 の上面にベタ一面に成膜された導電性膜を、フォトリソグラフィー法や、エッチング法によってパターニングすることで形成されている。

ここで、スイッチトランジスタ 2 1 のゲート 2 1 g 、保持トランジスタ 2 2 のゲート 2 2 g 、駆動トランジスタ 2 3 のゲート 2 3 g 、キャパシタ 2 4 の電極 2 4 A 及び信号線 Y r , Y g , Y b は、絶縁基板 2 上にべた一面に成膜された導電性膜をフォトリソグラフィー法・エッチング法によってパターニングすることで形成されたものである。以下では、スイッチトランジスタ 2 1 のゲート 2 1 g 、保持トランジスタ 2 2 のゲート 2 2 g 、駆動トランジスタ 2 3 のゲート 2 3 g 及びキャパシタ 2 4 の下層電極 2 4 A 並びに信号線 Y r , Y g , Y b の元となる導電性膜を、以下、ゲートレイヤーという。

【0034】

スイッチトランジスタ 2 1 、保持トランジスタ 2 2 、駆動トランジスタ 2 3 及びキャパシタ 2 4 の上には、ゲート絶縁膜 3 1 がベタ一面に成膜されており、このゲート絶縁膜 3 1 は、スイッチトランジスタ 2 1 のゲート 2 1 g 、保持トランジスタ 2 2 のゲート 2 2 g 、駆動トランジスタ 2 3 のゲート 2 3 g 、キャパシタ 2 4 の電極 2 4 A 及び信号線 Y r , Y g , Y b を被覆するようになっている。

10

20

30

40

50

## 【0035】

さらに、スイッチトランジスタ21のドレイン21d及びソース21s、保持トランジスタ22のドレイン22d及びソース22s、駆動トランジスタ23のドレイン23d及びソース23s、キャパシタ24の電極24B及び全ての走査線X並びに供給線Zは、ゲート絶縁膜31の上面にベタ一面に成膜された導電性膜を、フォトリソグラフィー法や、エッチング法によってパターニングすることで形成されている。

ここで、スイッチトランジスタ21のドレイン21d及びソース21s、保持トランジスタ22のドレイン22d及びソース22s、駆動トランジスタ23のドレイン23d及びソース23s、キャパシタ24の電極24B及び走査線X並びに供給線Zの元となる導電性膜を、以下、ドレインレイヤーという。

10

## 【0036】

図3に示すように、ゲート絶縁膜31であって、平面視して、走査線Xと重畳する箇所には、1ドットのサブピクセルP当たり1つのコンタクトホール92が形成され、スイッチトランジスタ21のゲート21g及び保持トランジスタ22のゲート22gが、コンタクトホール92を介して走査線Xと導通されている。

また、ゲート絶縁膜31であって、平面視して、信号線Yと重畳する箇所には、1ドットのサブピクセルP当たり1つのコンタクトホール94が形成され、スイッチトランジスタ21のソース21sが、コンタクトホール94を介して信号線Yと導通されている。

さらに、ゲート絶縁膜31であって、電極24Aと重畳する箇所には、1ドットのサブピクセルPにつき1つのコンタクトホール93が形成され、保持トランジスタ22のソース22sが、コンタクトホール93を介して駆動トランジスタ23のゲート23gと、キャパシタ24の電極24Aとに導通されている。

20

なお、信号線Y<sub>r</sub>、Y<sub>g</sub>、Y<sub>b</sub>の上方には、ゲート絶縁膜31を介して半導体膜23cと同じ層をパターニングしてなる保護膜41と、チャネル保護膜23pと同じ層をパターニングしてなる保護膜42と、が積層されている。保護膜41及び保護膜42は、ゲート絶縁膜31にピンホールが形成されてしまった場合、このピンホールを介して信号線Y<sub>r</sub>、Y<sub>g</sub>、Y<sub>b</sub>が供給線Zと短絡してしまうことを防止するための保護膜である。

## 【0037】

これらスイッチトランジスタ21、保持トランジスタ22、駆動トランジスタ23並びに全ての走査線X及び供給線Zは、ベタ一面に成膜された窒化シリコンや酸化シリコン等のトランジスタ保護絶縁膜32によって被覆されている。

30

なお、詳細については後述するが、トランジスタ保護絶縁膜32は、平面視して、供給線Zに重畳する箇所で、矩形状に分断されている。

## 【0038】

トランジスタ保護絶縁膜32の上面には、ポリイミド等の光硬化性樹脂を硬化させた平坦化膜33が表面を平坦にするように積層されており、スイッチトランジスタ21、保持トランジスタ22、駆動トランジスタ23、走査線X及び供給線Zによる凹凸が解消されている。

## 【0039】

なお、本実施形態におけるディスプレイパネル1を、ボトムエミッション型として用いる場合、すなわち、絶縁基板2の各トランジスタ21、22、23が配設された面側を表示面として用いる場合には、ゲート絶縁膜31、トランジスタ保護絶縁膜32及び平坦化膜33には、透明な材料が用いられる。

40

ここで、絶縁基板2から平坦化膜33までの積層構造を、トランジスタアレイ基板50という。

## 【0040】

トランジスタ保護絶縁膜32及び平坦化膜33であって、平面視して、各供給線Zと重畳する箇所には、水平方向に沿って長尺な第一溝34が形成されている。また、これら第一溝34と隣接する箇所であって、各信号線Xと重畳する箇所には、水平方向に沿って長尺な第二溝35が形成されている。これら第一溝34及び第二溝35によって、トランジ

50

スタ保護絶縁膜32及び平坦化膜33が矩形状に分断されている。さらに、第一溝34及び第二溝35には、給電配線90と、選択配線89とがそれぞれ埋設されており、このうち第一溝34の内部において、給電配線90が供給線Zの上に積層されている。一方、第二溝35の内部において、選択配線89が信号線Xの上に積層されている。

【0041】

給電配線90は、トランジスタ保護絶縁膜32及び平坦化膜33に第一溝34を形成後に無電解メッキ法或いは第一溝34から露出された供給線Zを下地電極として電解メッキ法により形成された導電層であって、信号線Yr、信号線Yg、信号線Yb、走査線X及び供給線Zよりも厚さ寸法が大きい。給電配線90の上部には、アルミニウム等の第1コンタクト層96、及びサブピクセル電極20aの元となる導電層をパターニングしてなる第2コンタクト層97が設けられている。給電配線90上の第1コンタクト層96及び第2コンタクト層97で構成される導電性ライン51は、給電配線90と同一の帯状になっている。また、選択配線89は、無電解メッキ法或いは第二溝35から露出された供給線Xを下地電極として電解メッキ法により形成された導電層であって、信号線Yr、信号線Yg、信号線Yb、走査線X及び供給線Zよりも厚さ寸法が大きい。選択配線89の上部には、アルミニウム等の第1コンタクト層101、及びサブピクセル電極20aの元となる導電層をパターニングしてなる第2コンタクト層102が設けられている。選択配線89上の第1コンタクト層101及び第2コンタクト層102で構成される導電性ライン53は、選択配線89と同一の帯状になっている。これら選択配線89及び給電配線90の厚さ寸法は、トランジスタ保護絶縁膜32と、平坦化膜33との厚さ寸法の総計とほぼ等しく、平坦化膜33の表面と、選択配線89又は給電配線90の表面とがほぼ均一となっている。銅、アルミ、金若しくはニッケルのうちの少なくともいずれかを含むことが好ましい。

【0042】

平坦化膜33の表面、すなわちトランジスタアレイ基板50の上面には、複数のサブピクセル電極20aがマトリクス状に配列されている。サブピクセル電極20aは、有機EL素子20のアノードとして機能する電極であるため、仕事関数が比較的高く、有機EL層20bに正孔を効率よく注入するものが好ましい。

【0043】

また、サブピクセル電極20aは、ボトムエミッションの場合、可視光に対して透過性を有しており、原料としては、例えは錫ドープ酸化インジウム(ITO)、亜鉛ドープ酸化インジウム、酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )又はカドミウム-錫酸化物(CTO)を主成分とするものが適用可能である。

【0044】

なお、本実施形態におけるディスプレイパネル1をトップエミッション型として用いる場合、すなわち、有機EL層20bの発光を、有機EL層20bの上面側から出射させて表示させる場合には、サブピクセル電極20aと、平坦化膜33との間に、導電性かつ可視光反射性の高い反射膜が成膜されているか、或いはサブピクセル電極20a自体を反射性電極とすることが好ましい。

【0045】

1ドットのサブピクセルPであって、平坦化膜33及びトランジスタ保護絶縁膜32のサブピクセル電極20aと重複する箇所には、1つのコンタクトホール88が形成され、これらコンタクトホール88には、導電性パッド87が埋設されている。これによって、サブピクセル電極20aが、コンタクトホール88を介してキャパシタ24の電極24B、スイッチトランジスタ21のドレイン21dと、駆動トランジスタ23のソース23sとに導通されている。導電性パッド87は、給電配線90とともに形成され、特に無電解メッキ法或いは上層電極24Bを下地電極として電解メッキ法により形成されることが好ましい。導電性パッド87の上部には、平面視してコンタクトホール88と略同一形状のアルミニウム等のコンタクト層103が設けられている。コンタクト層103は、導電性ライン51の第1コンタクト層96及び導電性ライン53の第1コンタクト層101とと

10

20

30

40

50

もに同一の導電性膜をパターニングして形成されている。

【0046】

サブピクセル電極20aは、ベタ一面に成膜された導電性膜をフォトリソグラフィー法や、エッチング法により、導電性ライン51の第2コンタクト層97及び導電性ライン53の第2コンタクト層102とともに平坦化膜33の上面にパターニングされたものである。サブピクセル電極20aはコンタクト層103を被覆して導電性パッド87と接続している。導電性ライン51は、図3に示すように、給電配線90の延在方向に沿って形成されている。導電性ライン53は、選択配線89の延在方向に沿って形成されている。

【0047】

隣接するサブピクセル電極20aと、サブピクセル電極20aとの間には、平面視して、各サブピクセル電極20aの左側及び右側を囲繞するように垂直方向に沿って延在する突条であって、平面視した場合、信号線Yr, Yg, Ybに重畠している絶縁膜52が形成されている。また、この絶縁膜52は、導電性ライン51も被覆している。絶縁膜52の表面61には、サブピクセル電極20aの表面61に成膜される有機EL層20bの少なくとも一層を構成する材料を溶解した溶液に対して撥液性を示す処理がなされている。絶縁膜52は、この有機EL層20bとなる溶液をサブピクセル電極20a上に塗布した際の間仕切りとして機能するため、塗布される溶液の高さよりも十分高い厚さに形成されていることが好ましい。

【0048】

水平方向及び垂直方向に格子状に形成された絶縁膜52のうち垂直方向に延在している部分の上には、ポリイミド等の感光性絶縁樹脂からなるバンク71が、フォトリソグラフィー法により、形成されている。つまりバンク71は、垂直方向に沿って延在する突条であって、平面視した場合、信号線Yr, Yg, Ybに重畠している。すなわち、バンク71は、垂直方向に並んだ複数の赤サブピクセルPrからなる列と、垂直方向に並び且つこれら赤サブピクセルPrからなる列に水平方向に隣接する複数の緑サブピクセルPgからなる列との間、緑サブピクセルPgからなる列と、これら緑サブピクセルPgからなる列に水平方向に隣接する複数の青サブピクセルPbからなる列との間、並びに青サブピクセルPbの列と、これら青サブピクセルPbからなる列に水平方向に隣接する複数の赤サブピクセルPrからなる列との間にそれぞれ配設されている。バンク71の表面には、サブピクセル電極20aの表面61に成膜される有機EL層20bの少なくとも一層を構成する材料を溶解した溶液に対して撥液性を示す処理がなされていることが好ましい。また、絶縁膜52の高さが、サブピクセル電極20a上にインクジェット法等により塗布されたときの有機EL層20bとなる溶液の高さよりも低い場合、絶縁膜52及びバンク71を間仕切りとして機能するため、絶縁膜52の高さとバンク71の高さの和が塗布される溶液の高さよりも十分高く形成されていることが好ましい。

【0049】

サブピクセル電極20aの上には、有機EL層20bが形成されている。有機EL層20bは、広義の発光層であり、有機化合物である発光材料が含有されている。また、有機EL層20bは、サブピクセル電極20aから順に正孔輸送層、狭義の発光層と積層した二層構造となっている。このうち、正孔輸送層は、導電性高分子であるPEDOT(ポリチオフェン)及びドーパントであるPSS(ポリスチレンスルホン酸)からなり、狭義の発光層は、ポリフルオレン系発光材料からなり、赤サブピクセルPrの場合には、有機EL層20bが赤色に発光し、緑サブピクセルPgの場合には、有機EL層20bが緑色に発光し、青サブピクセルPbの場合には、有機EL層20bが青色に発光する。

【0050】

また、有機EL層20bは、絶縁膜52またはバンク71による制限によって水平方向に分離独立し、且つ垂直方向に沿って連続した長尺な帯状に形成されており、各サブピクセルPr, Pg, Pbにおいて垂直方向に一列に配列された複数のサブピクセル電極20aが被覆される。

【0051】

10

20

30

40

50

なお、絶縁膜 5 2 やバンク 7 1 をサブピクセル電極 2 0 a の前後左右を囲繞するように設けることによって、有機 E L 層 2 0 b は、サブピクセル電極 2 0 a ごとに独立して設けられ、平面視した場合、複数の有機 E L 層 2 0 b がマトリクス状に配列されていても良い。

#### 【 0 0 5 2 】

これら有機 E L 層 2 0 b は、バンク 7 1 の形成後に湿式塗布法、例えばインクジェット法等によって成膜される。この有機 E L 層 2 0 b を成膜する際には、サブピクセル電極 2 0 a に対して有機化合物含有液が塗布されるが、水平方向に隣接するサブピクセル電極 2 0 a と、サブピクセル電極 2 0 a との間には、絶縁膜 5 2 またはバンク 7 1 がトランジスタアレイ基板 5 0 の表面に対して凸設されているため、サブピクセル電極 2 0 a に塗布された有機化合物含有液が隣のサブピクセル電極 2 0 a に漏れることがないようになっている。

10

#### 【 0 0 5 3 】

なお、有機 E L 層 2 0 b は、上記した二層構造の他に、サブピクセル電極 2 0 a から順に正孔輸送層、狭義の発光層、電子輸送層となる三層構造であってもよいし、狭義の発光層からなる一層構造であってもよい。また、これら層構造において適切な層間に、電子若しくは正孔の注入層が介在した積層構造であってもよいし、その他の積層構造であってもよい。

#### 【 0 0 5 4 】

有機 E L 層 2 0 b の上には、有機 E L 素子 2 0 のカソードとして機能する対向電極 2 0 c が成膜されている。対向電極 2 0 c は、各サブピクセル P r , P g , P b に共通して形成された共通電極であり、対向電極 2 0 c がベタ一面に成膜されることで、バンク 7 1 も対向電極 2 0 c によって被覆される。

20

#### 【 0 0 5 5 】

対向電極 2 0 c は、サブピクセル電極 2 0 a よりも仕事関数の低い材料、例えば、マグネシウム、カルシウム、リチウム、バリウム、インジウム、希土類金属の少なくとも一種を含む単体又は合金で形成されていることが好ましい。この対向電極 2 0 c は、上記した各種材料の層が積層された積層構造となっていてもよいし、以上の各種材料の層に加えてシート抵抗を低くするために酸化されにくい金属層が堆積した積層構造となっていてもよい。具体的には、有機 E L 層 2 0 b と接する界面側に設けられた仕事関数の低い高純度のバリウム層と、このバリウム層を被覆するように設けられたアルミニウム層との積層構造や、下層にリチウム層、上層にアルミニウム層が設けられた積層構造等が挙げられる。またトップエミッショング構造の場合、対向電極 2 0 c を上述のような低仕事関数の薄膜とその上に I T O 等の透明導電膜を積層した透明電極としてもよい。

30

#### 【 0 0 5 6 】

対向電極 2 0 c の下面であって、バンク 7 1 の上方には、有機 E L 素子 2 0 の上部電極のシート抵抗を下げるために共通配線 9 1 が凸設されている。したがって、共通配線 9 1 は、平面視した場合、列方向に沿って設けられたバンク 7 1 に重畠している。また、共通配線 9 1 と、対向電極 2 0 c とは接しているため、図 2 に示すように、対向電極 2 0 c は、共通配線 9 1 と導通されている。これら共通配線 9 1 群は、メッキ法等により形成されており、対向電極 2 0 c や、スイッチトランジスタ 2 1 、保持トランジスタ 2 2 及び駆動トランジスタ 2 3 の各電極よりも厚さ寸法が大きく低抵抗に設定されている。また共通配線 9 1 群は、図 7 及び図 9 に示すように、画素領域の外の非画素領域において水平方向に延在する引き回し配線 9 5 によって導通され、引き回し配線 9 5 は、絶縁基板 2 の周縁部に複数の端子部 T c に導通している。共通配線 9 1 群及び対向電極 2 0 c には、外部回路から端子部 T c に印加された電圧 V com によって等電位となる。共通配線 9 1 群は、銅、アルミ、金若しくはニッケルのうちの少なくともいずれかを含むことが好ましく、いずれも有機 E L 層 2 0 b の発光する光に対して不透明なくらい厚い。

40

#### 【 0 0 5 7 】

ここで、E L ディスプレイパネル 1 の画素数を W X G A ( 7 6 8 × 1 3 6 6 ) としたと

50

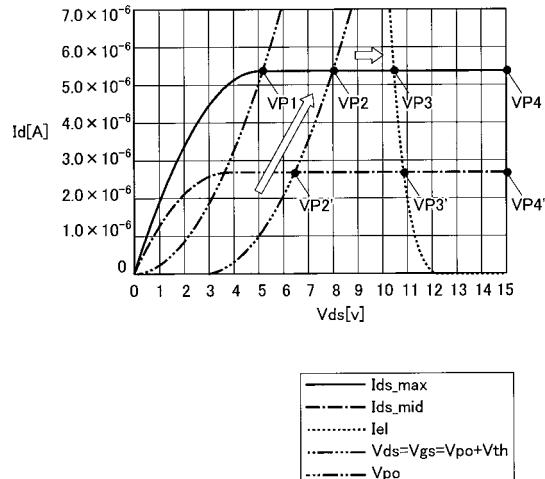

きに、上記した選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の望ましい幅寸法及び断面積を定義する。図 1 1 は、各サブピクセル P の駆動トランジスタ 2 3 及び有機 E L 素子 2 0 の電流 - 電圧特性を示すグラフである。

#### 【 0 0 5 8 】

図 1 1 において、縦軸は 1 つの駆動トランジスタ 2 3 のドレイン 2 3 d - ソース 2 3 s 間を流れる書込電流の電流値又は 1 つの有機 E L 素子 2 0 のアノード - カソード間を流れる駆動電流の電流値であり、横軸は 1 つの駆動トランジスタ 2 3 のドレイン 2 3 d - ソース 2 3 s 間の電圧（同時に 1 つの駆動トランジスタ 2 3 のゲート 2 3 g - ソース 2 3 s 間の電圧）である。図中、実線  $I_{ds\ max}$  は、最高輝度階調（最も明るい表示）のときの書込電流及び駆動電流であり、一点鎖線  $I_{ds\ mid}$  は、最高輝度階調と最低輝度階調との間の中間輝度階調のときの書込電流及び駆動電流であり、二点鎖線  $V_{po}$  は後述する閾値電圧  $V_{th}$  が 0 V の場合の駆動トランジスタ 2 3 の不飽和領域（線形領域）と飽和領域との閾値つまりピンチオフ電圧であり、三点鎖線  $V_{ds}$  は駆動トランジスタ 2 3 の - ドレイン 2 3 d - ソース 2 3 s 間を流れる書込電流であり、破線  $I_{el}$  は有機 E L 素子 2 0 のアノード - カソード間を流れる駆動電流である。

#### 【 0 0 5 9 】

ここで電圧  $V_{P1}$  は、最高輝度階調時の駆動トランジスタ 2 3 のピンチオフ電圧であり、電圧  $V_{P2}$  は、駆動トランジスタ 2 3 の閾値電圧  $V_{th}$  が 0 V を越える場合に、飽和領域において駆動トランジスタ 2 3 に最高輝度階調の書込電流を流すために要する最低限のドレイン - ソース間電圧であり、電圧  $V_{ELmax}$ （電圧  $V_{P4}$  - 電圧  $V_{P3}$ ）は、有機 E L 素子 2 0 が最高輝度階調の書込電流にしたがった電流値の最高輝度階調の駆動電流で発光するときのアノード - カソード間の電圧である。電圧  $V_{P2'}$  は、駆動トランジスタ 2 3 が中間輝度階調の書込電流が流れるときのドレイン - ソース間電圧であり、電圧（電圧  $V_{P4'}$  - 電圧  $V_{P3'}$ ）は有機 E L 素子 2 0 が中間輝度階調の書込電流と電流値にしたがった電流値の中間輝度階調の駆動電流で発光するときのアノード - カソード間電圧である。

#### 【 0 0 6 0 】

駆動トランジスタ 2 3 及び有機 E L 素子 2 0 はいずれも飽和領域で駆動させるために、「選択配線 8 9 又は給電配線 9 0 の発光期間時の電圧  $V_H$ 」から「共通配線 9 1 の発光期間時の電圧  $V_{com}$ 」を減じた値  $V_X$  は下記の式（1）を満たす。

#### 【 0 0 6 1 】

$$V_X = V_{po} + V_{th} + V_m + V_{EL} \quad \dots \dots (1)$$

ここで、 $V_{th}$ （最高輝度時の場合  $V_{P2} - V_{P1}$  に等しい）は、駆動トランジスタ 2 3 のドレイン - ソース間電流が流し始まる閾値電圧、 $V_{EL}$ （最高輝度時の場合  $V_{ELmax}$  に等しい）は、有機 E L 素子 2 0 のアノード - カソード間電圧、 $V_m$  は、有機 E L 素子 2 0 の経時的高抵抗化による電圧差分のマージンや駆動トランジスタ 2 3 の経時劣化によって閾値電圧  $V_{th}$  が正方向（図 1 1 中の右方向）にシフトした際のマージン等を含むように設定された許容電圧である。

#### 【 0 0 6 2 】

図 1 1 から明らかなように、電圧  $V_X$  のうち、輝度階調が高くなる程、トランジスタ 2 3 のドレイン - ソース間に要する電圧  $V_{po}$  分が高くなるとともに有機 E L 素子 2 0 のアノード - カソード間に要する電圧  $V_{EL}$  が高くなる。したがって、輝度階調が高くなる程、許容電圧  $V_m$  は低くなり、最高輝度階調時では  $V_{P3} - V_{P2}$  となる。

#### 【 0 0 6 3 】

有機 E L 素子 2 0 は、低分子 E L 材料及び高分子 E L 材料にかかわらず一般的に経時劣化し、高抵抗化する。1 0 0 0 0 時間後のアノード - カソード間電圧は初期時の 1.4 倍程度になることが確認されている。つまり、電圧  $V_{EL}$  は、同じ輝度階調時でも時間が経つ程高くなる。このため、駆動初期時の許容電圧  $V_m$  が高い程長期間にわたって動作が安定するので、電圧  $V_{EL}$  が 8 V 以上、より望ましくは 13 V 以上となるように電圧  $V_X$  を設定している。

#### 【 0 0 6 4 】

10

20

30

40

50

この許容電圧  $V_m$  には、経時の高抵抗による電圧差分ばかりでなく、さらに、選択配線 89 又は給電配線 90 による電圧降下の分も含まれる。

【0065】

選択配線 89 及び給電配線 90 の配線抵抗の影響により、電圧降下が大きいと EL ディスプレイパネル 1 の消費電力が著しく増大してしまう。このため、選択配線 89 及び給電配線 90 の電圧降下は、それぞれ 1V 以下に設定することが特に好ましい。

【0066】

行方向の一つの画素の長さである画素幅  $W_p$  と、行方向の画素数 (1366) と、画素領域以外における第一の引き回し配線から一方の配線端子までの延長部分と、画素領域以外における第一の引き回し配線から他方の配線端子までの延長部分とを考慮した結果、EL ディスプレイパネル 1 のパネルサイズが 32 インチ、40 インチの場合、第一の引き回し配線の全長はそれぞれ 706.7mm、895.2mm に設定する。ここで、選択配線 89 の線幅  $WL$ 、給電配線 90 の線幅  $WL$  及び共通配線 91 の線幅  $WL$  が広くなると、構造上有機 EL 層 20b の面積が小さくなり、さらに他の配線との重なり寄生容量を発生してさらなる電圧降下をもたらすため、選択配線 89 の幅  $WL$ 、給電配線 90 の幅  $WL$  及び共通配線 91 の線幅  $WL$  はそれぞれ画素幅  $W_p$  の 5 分の 1 以下に抑えることが望ましい。このようなことを考慮すると、EL ディスプレイパネル 1 のパネルサイズが 32 インチ、40 インチの場合、幅  $WL$  はそれぞれ 34  $\mu m$  以内、44  $\mu m$  以内となる。また、選択配線 89、給電配線 90 及び共通配線 91 の最大膜厚  $H_{max}$  はアスペクト比を考慮すると、トランジスタ 21 ~ 23 の最小加工寸法 4  $\mu m$  の 1.5 倍、つまり 6  $\mu m$  となる。したがって、選択配線 89、給電配線 90 及び共通配線 91 の最大断面積  $S_{max}$  は 32 インチ、40 インチで、それぞれ 204  $\mu m^2$ 、264  $\mu m^2$  となる。

10

20

30

【0067】

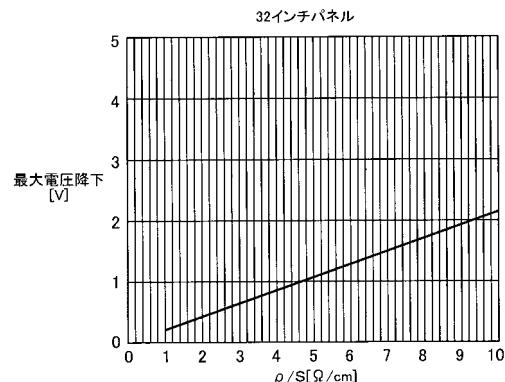

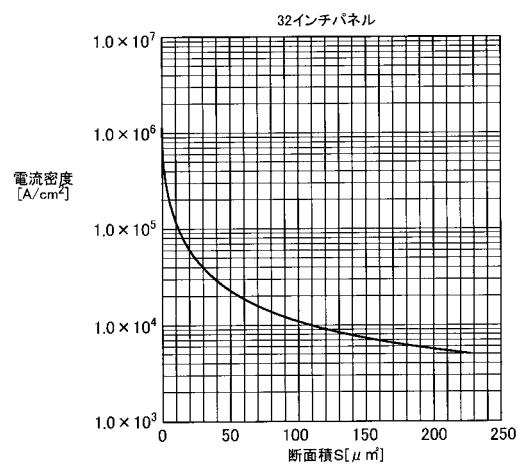

このような 32 インチの EL ディスプレイパネル 1 について、最大電流が流れるように全点灯したときの選択配線 89、給電配線 90 及び共通配線 91 のそれぞれの最大電圧降下を 1V 以下にするためには、図 12 に示すように、選択配線 89、給電配線 90 及び共通配線 91 のそれぞれの配線抵抗率 / 断面積  $S$  は 4.7 / cm 以下に設定される必要がある。また、図 13 において、32 インチの EL ディスプレイパネル 1 の選択配線 89、給電配線 90 及び共通配線 91 のそれぞれの断面積と電流密度の相関関係を示す。なお、上述した選択配線 89、給電配線 90 及び共通配線 91 の最大断面積  $S_{max}$  時に許容される抵抗率は、32 インチで 9.6  $\mu cm$ 、40 インチで 6.4  $\mu cm$  となる。

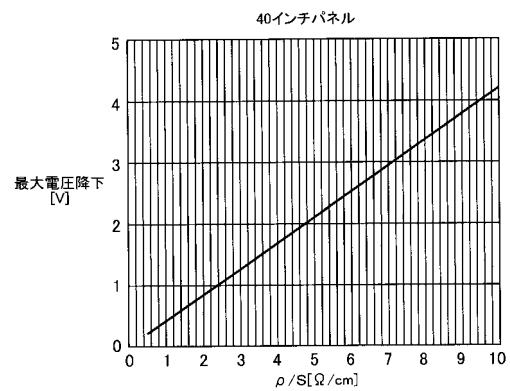

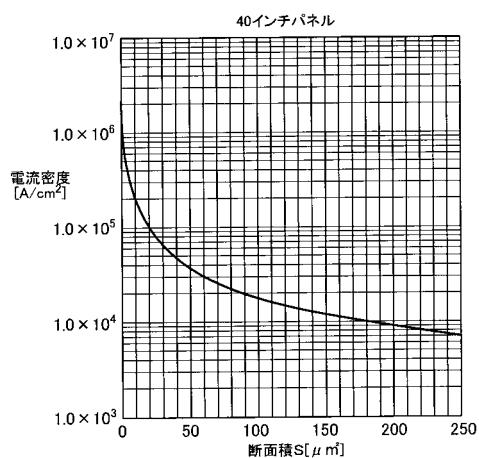

【0068】

そして、40 インチの EL ディスプレイパネル 1 について、最大電流が流れるように全点灯したときの選択配線 89、給電配線 90 及び共通配線 91 のそれぞれの最大電圧降下を 1V 以下にするためには、図 14 に示すように、選択配線 89、給電配線 90 及び共通配線 91 のそれぞれの配線抵抗率 / 断面積  $S$  は 2.4 / cm 以下に設定される必要がある。図 15 において、40 インチの EL ディスプレイパネル 1 の選択配線 89、給電配線 90 及び共通配線 91 のそれぞれの断面積と電流密度の相関関係を表す。

【0069】

選択配線 89、給電配線 90 及び共通配線 91 の故障により動作しなくなる故障寿命  $M_{TF}$  は、下記の式 (2) を満たす。

40

【0070】

$$M_{TF} = A \exp(E_a / K_b T) / J^2 \dots \dots (2)$$

ここで、 $E_a$  は活性化エネルギー、 $K_b T = 8.617 \times 10^{-5}$  eV、 $A$  は、選択配線 89、給電配線 90 及び共通配線 91 の抵抗率、 $J$  は電流密度である。

【0071】

選択配線 89、給電配線 90 及び共通配線 91 の故障寿命  $M_{TF}$  は、抵抗率の増大やエレクトロマイグレーションに律速する。選択配線 89、給電配線 90 及び共通配線 91 を A1 系 (A1 単体或いは A1 Ti や A1 Nd 等の合金) に設定し、 $M_{TF}$  が 10000 時間、85 の動作温度で試算すると、電流密度  $J$  は  $2.1 \times 10^{-4}$  A / cm<sup>2</sup> 以下にする

50

必要がある。これと同様に、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 を Cu 系に設定すると、 $2.8 \times 10^6 \text{ A/cm}^2$  以下にする必要がある。なお、Al 合金内の Al 以外の材料は Al よりも低い抵抗率であることを前提としている。

これらのこと考慮して、32インチのELディスプレイパネル1では、全点灯状態で10000時間に給電配線 9 0 及び共通配線 9 1 が故障しないような Al 系の選択配線 8 9、給電配線 9 0 及び共通配線 9 1 のそれぞれの断面積 S は、図 13 に示すように、 $57 \mu\text{m}^2$  以上必要になり、同様に Cu 系の選択配線 8 9、給電配線 9 0 及び共通配線 9 1 のそれぞれの断面積 S は、図 13 に示すように、 $0.43 \mu\text{m}^2$  以上必要になる。

#### 【0072】

そして、40インチのELディスプレイパネル1では、全点灯状態で10000時間に選択配線 8 9、給電配線 9 0 及び共通配線 9 1 が故障しないような Al 系の選択配線 8 9、給電配線 9 0 及び共通配線 9 1 のそれぞれの断面積 S は、図 15 に示すように、 $92 \mu\text{m}^2$  以上必要となる。同様に、Cu 系の選択配線 8 9、給電配線 9 0 及び共通配線 9 1 のそれぞれの断面積 S は、図 15 に示すように、 $0.69 \mu\text{m}^2$  以上必要になる。

#### 【0073】

Al 系の選択配線 8 9、給電配線 9 0 及び共通配線 9 1 では、Al 系の抵抗率が仮に $4.00 \mu\text{cm}$  とすると、32インチのELディスプレイパネル1では上述のように配線抵抗率 / 断面積 S が $4.7 / \text{cm}$  以下なので、最小断面積 S<sub>min</sub> は $85.1 \mu\text{m}^2$  となる。このとき、上述したように、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の配線幅 WL が $34 \mu\text{m}$  以内となるため、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の最小膜厚 H<sub>min</sub> は $2.50 \mu\text{m}$  となる。

#### 【0074】

また、Al 系の選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の 40 インチの EL ディスプレイパネル1では、上述したように配線抵抗率 / 断面積 S が $2.4 / \text{cm}$  以下となるため、最小断面積 S<sub>min</sub> は $167 \mu\text{m}^2$  となる。このとき上述のように選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の配線幅 WL が $44 \mu\text{m}$  以内であるため、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の最小膜厚 H<sub>min</sub> は $3.80 \mu\text{m}$  となる。

#### 【0075】

一方、Cu 系の選択配線 8 9、給電配線 9 0 及び共通配線 9 1 では、仮に Cu 系の抵抗率が $2.10 \mu\text{cm}$  とすると、32インチのELディスプレイパネル1では、上述のように配線抵抗率 / 断面積 S が $4.7 / \text{cm}$  以下となるため、最小断面積 S<sub>min</sub> は $44.7 \mu\text{m}^2$  となる。このとき、上述したように、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の配線幅 WL が $34 \mu\text{m}$  以内となるため、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の最小膜厚 H<sub>min</sub> は $1.31 \mu\text{m}$  となる。

#### 【0076】

また、Cu 系の選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の 40 インチの EL ディスプレイパネル1では、上述したように配線抵抗率 / 断面積 S が $2.4 / \text{cm}$  以下となるため、最小断面積 S<sub>min</sub> は $87.5 \mu\text{m}^2$  となる。このとき、上述したように、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の配線幅 WL が $44 \mu\text{m}$  以内となるため、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 の最小膜厚 H<sub>min</sub> は $1.99 \mu\text{m}$  となる。

#### 【0077】

以上より、ELディスプレイパネル1を正常かつ消費電力を低く動作させるには、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 での電圧降下を 1V 以下に設定することが好ましく、このような条件に設定するためには、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 が Al 系の 32 インチのパネルでは、厚さ寸法 H が $2.50 \mu\text{m} \sim 6 \mu\text{m}$ 、幅寸法 WL が $14.1 \mu\text{m} \sim 34.0 \mu\text{m}$ 、抵抗率が $4.0 \mu\text{cm} \sim 9.6 \mu\text{cm}$  となり、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 が Al 系の 40 インチのパネルでは、選択配線 8 9、給電配線 9 0 及び共通配線 9 1 が Al 系の場合、厚さ寸法 H が $3.80 \mu\text{m} \sim 6 \mu\text{m}$ 、幅寸法 WL が $27.8 \mu\text{m} \sim 44.0 \mu\text{m}$ 、抵抗率が $4.0 \mu\text{cm} \sim 9.6 \mu\text{cm}$  となる。

10

20

30

40

50

## 【0078】

総じてA1系の選択配線89、給電配線90及び共通配線91の場合、厚さ寸法Hが2.50  $\mu\text{m}$  ~ 6  $\mu\text{m}$ 、幅寸法WLが14.1  $\mu\text{m}$  ~ 44  $\mu\text{m}$ 、抵抗率が4.0  $\mu\text{cm}$  ~ 9.6  $\mu\text{cm}$ となる。

同様に、選択配線89、給電配線90及び共通配線91がCu系の32インチのパネルでは、厚さ寸法Hが1.31  $\mu\text{m}$  ~ 6  $\mu\text{m}$ 、幅寸法WLが7.45  $\mu\text{m}$  ~ 34  $\mu\text{m}$ 、抵抗率が2.1  $\mu\text{cm}$  ~ 9.6  $\mu\text{cm}$ となり、選択配線89、給電配線90及び共通配線91がCu系の40インチのパネルでは、選択配線89、給電配線90及び共通配線91がCu系の場合、厚さ寸法Hが1.99  $\mu\text{m}$  ~ 6  $\mu\text{m}$ 、幅寸法WLが14.6  $\mu\text{m}$  ~ 44.0  $\mu\text{m}$ 、抵抗率が2.1  $\mu\text{cm}$  ~ 9.6  $\mu\text{cm}$ となる。

## 【0079】

総じてCu系の選択配線89、給電配線90及び共通配線91の場合、厚さ寸法Hが1.31  $\mu\text{m}$  ~ 6  $\mu\text{m}$ 、幅寸法WLが7.45  $\mu\text{m}$  ~ 44  $\mu\text{m}$ 、抵抗率が2.1  $\mu\text{cm}$  ~ 9.6  $\mu\text{cm}$ となる。

したがって、選択配線89、給電配線90及び共通配線91としてA1系材料又はCu系材料を適用した場合、ELディスプレイパネル1の選択配線89、給電配線90及び共通配線91は、厚さ寸法Hが1.31  $\mu\text{m}$  ~ 6  $\mu\text{m}$ 、幅寸法WLが7.45  $\mu\text{m}$  ~ 44  $\mu\text{m}$ 、抵抗率が2.1  $\mu\text{cm}$  ~ 9.6  $\mu\text{cm}$ となる。勿論、A1系材料やCu系材料と同等、或いはA1系材料とCu系材料との間の抵抗率の材料であればA1系材料又はCu系材料でなくてもこの範囲の厚さ寸法H及び幅寸法WLでよい。

## 【0080】

また、対向電極20cの上面には、封止保護絶縁膜56が成膜されている。この封止保護絶縁膜56によって、対向電極20c全体が被覆されると共に、共通配線91も被覆されることで、共通配線91及び対向電極20cの劣化を防止するようになっている。

## 【0081】

なお、本実施形態におけるディスプレイパネル1をトップエミッション型として用いる場合には、対向電極20c及び封止保護絶縁膜56を薄膜に形成することより、または対向電極20c及び封止保護絶縁膜56を透明な材料を用いることにより、対向電極20c及び封止保護絶縁膜56の可視光透過性を高めることが可能である。

## 【0082】

上記して構成されたELディスプレイパネル1の駆動方法について説明する。

ELディスプレイパネル1の駆動方法は、パッシブマトリクス方式による駆動方法と、アクティブマトリクス方式による駆動方法とに大別されるが、本実施形態においては、アクティブマトリクス方式による2種類の駆動方法について説明する。

## 【0083】

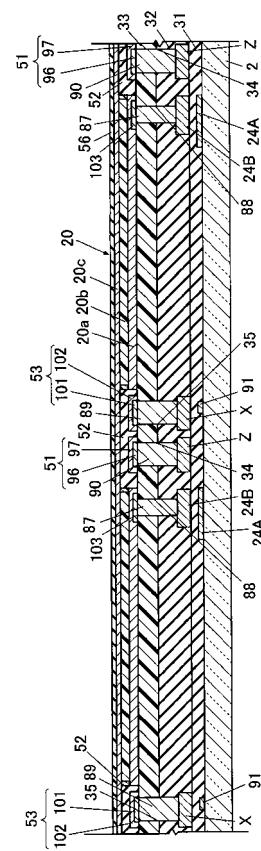

まず始めに、第一のディスプレイパネル1の構造では、図7に示すように、走査線X<sub>1</sub> ~ X<sub>m</sub>がそれぞれ接続された選択ドライバ111が絶縁基板2の第一の周縁部に配置され、互いに電気的に絶縁された給電配線90, 90, ... (供給線Z<sub>1</sub> ~ Z<sub>m</sub>)が接続された給電ドライバ112が絶縁基板2の第一の周縁部と対向する周縁部である第二周縁部に配置されている。

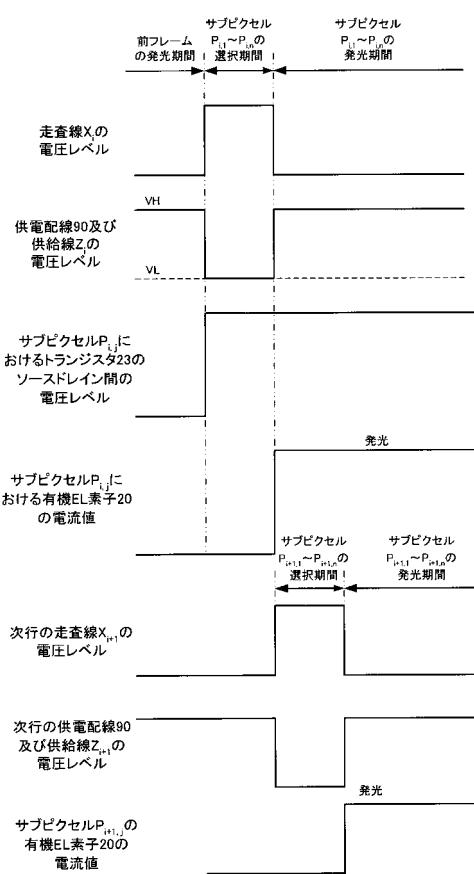

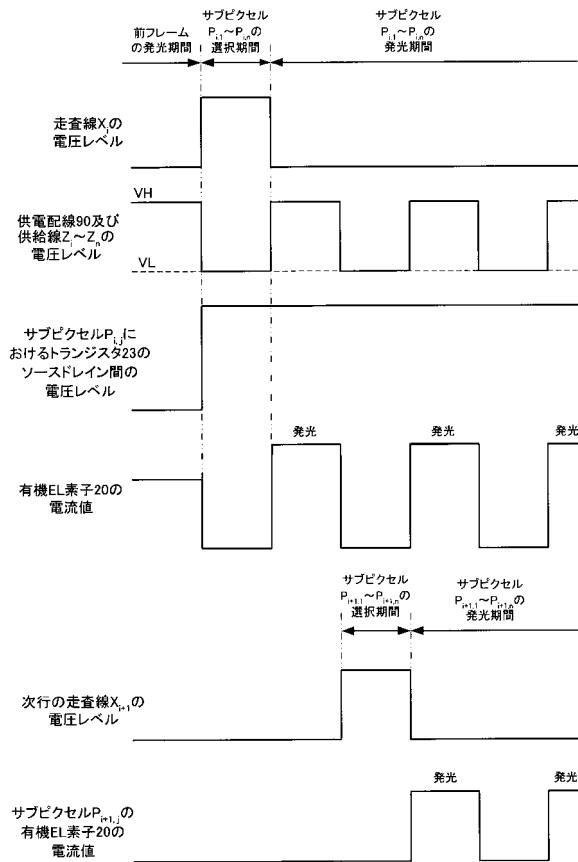

この第一のディスプレイパネル1をアクティブマトリクス方式で駆動するには、次のようになる。すなわち、図8に示すように、走査線X<sub>1</sub> ~ X<sub>m</sub>に接続された選択ドライバ111によって、走査線X<sub>1</sub>から走査線X<sub>m</sub>への順(走査線X<sub>m</sub>の次は走査線X<sub>1</sub>)にハイレベルのシフトパルスを順次出力することにより走査線X<sub>1</sub> ~ X<sub>m</sub>を順次選択する。また、選択期間に各給電配線90を介して供給線Z<sub>1</sub> ~ Z<sub>m</sub>にそれぞれ接続された駆動トランジスタ23に書き電流を流すための書き給電電圧VLを印加し、発光期間に駆動トランジスタ23を介して有機EL素子20に駆動電流を流すための駆動給電電圧VHを印加する給電ドライバ112が各給電配線90に接続されている。この給電ドライバ112によって、選択ドライバ111と同期するよう、供給線Z<sub>1</sub>から供給線Z<sub>m</sub>への順(供給線Z<sub>m</sub>の次は供給線Z<sub>1</sub>)にローレベル(有機EL素子20の対向電極の電圧より低レベル)の書き給電電圧

10

20

30

40

50

VLを順次出力することにより供給線 $Z_1 \sim Z_m$ を順次選択する。また、選択ドライバ111が各走査線 $X_1 \sim X_m$ を選択している時に、データドライバが書込電流である書込電流(電流信号)を所定の行の駆動トランジスタ23のドレイン-ソース間を介して全信号線 $Y_1 \sim Y_n$ に流す。なお、対向電極20c及び共通配線91群は引き回し配線95及び配線端子Tcによって外部と接続され、一定のコモン電位 $V_{com}$ (例えば、接地=0ボルト)に保たれている。

#### 【0084】

各選択期間において、データドライバ側の電位は、給電配線90, 90, ...及び供給線 $Z_1 \sim Z_m$ に出力された書込給電電圧VL以下で且つこの書込給電電圧VLはコモン電位 $V_{com}$ 以下に設定されている。したがってこの時、有機EL素子20から信号線 $Y_1 \sim Y_n$ に流れることはないので、図2に示すように、データドライバによって階調に応じた電流値の書込電流(書込電流)が矢印Aの通り、信号線 $Y_1 \sim Y_n$ に流れ、サブピクセル $P_{i,j}$ においては給電配線90及び供給線 $Z_i$ から駆動トランジスタ23のドレイン-ソース間、スイッチトランジスタ21のドレイン-ソース間を介して信号線 $Y_j$ に向かった書込電流(書込電流)が流れる。このように駆動トランジスタ23のドレイン-ソース間を流れる電流の電流値は、データドライバによって一義的に制御され、データドライバは、外部から入力された階調に応じて書込電流(書込電流)の電流値を設定する。書込電流(書込電流)が流れている間、 $i$ 行目の $P_{i,1} \sim P_{i,n}$ の各駆動トランジスタ23のゲート23g-ソース23s間の電圧は、それぞれ信号線 $Y_1 \sim Y_n$ に流れる書込電流(書込電流)の電流値、つまり駆動トランジスタ23の $V_{g-I_{ds}}$ 特性の経時変化にかかわらず駆動トランジスタ23のドレイン23d-ソース23s間を流れる書込電流(書込電流)の電流値に見合うように強制的に設定され、この電圧のレベルに従った大きさの電荷がキャパシタ24にチャージされて、書込電流(書込電流)の電流値が駆動トランジスタ23のゲート23g-ソース23s間の電圧のレベルに変換される。その後の発光期間では、走査線 $X_i$ がローレベルになり、スイッチトランジスタ21及び保持トランジスタ22がオフ状態となるが、オフ状態の保持トランジスタ22によってキャパシタ24の電極24A側の電荷が閉じ込められてフローティング状態になり、駆動トランジスタ23のソース23sの電圧が選択期間から発光期間に移行する際に変調しても、駆動トランジスタ23のゲート23g-ソース23s間の電位差がそのまま維持される。この発光期間では、供給線 $Z_i$ 及びそれに接続された給電配線90の電位が駆動給電電圧 $VH$ となり、有機EL素子20の対向電極20cの電位 $V_{com}$ より高くなることによって、供給線 $Z_i$ 及びそれに接続された給電配線90から駆動トランジスタ23を介して有機EL素子20に駆動電流が矢印Bの方向に流れ、有機EL素子20が発光する。駆動電流の電流値は駆動トランジスタ23のゲート23g-ソース23s間の電圧に依存するため、発光期間における駆動電流の電流値は選択期間における書込電流(引抜電流)の電流値に等しくなる。

#### 【0085】

そして、第二のディスプレイパネル1の構造は、図9に示すように、走査線 $X_1 \sim X_m$ がそれぞれ接続された選択ドライバ111が絶縁基板2の第一の周縁部に配置され、給電配線90, 90, ...が互いに電気的に接続されるよう給電配線90, 90, ...と一体的に形成された引き回し配線99が絶縁基板2の第一の周縁部と対向する周縁部である第二周縁部に配置されている。引き回し配線99は、第一周縁部及び第二周縁部と直交する第三の周縁部及び第四の周縁部のそれぞれに位置する端子部90d及び端子部90eの両方からクロック信号が入力されている。第二のディスプレイパネル1のアクティブマトリクス駆動方法は次のような。すなわち、図10に示すように、外部の発振回路が端子部90d及び端子部90eから引き回し配線99を介して給電配線90, 90, ...及び供給線 $Z_1 \sim Z_m$ に対してクロック信号を出力する。また、選択ドライバ111によって走査線 $X_1$ から走査線 $X_m$ への順(走査線 $X_m$ の次は走査線 $X_1$ )にハイレベルのシフトパルスを順次出力することにより走査線 $X_1 \sim X_m$ を順次選択するが、選択ドライバ111が走査線 $X_1 \sim X_m$ の何れか1つがハイレベルつまりオンレベルのシフトパルスを出力している時には発振回路のクロック信号がローレベルになる。また、選択ドライバ111が各走査線 $X_1$

10

20

30

40

50

～ $X_m$ を選択している時に、データドライバが書込電流である引抜電流（電流信号）を駆動トランジスタ23のドレイン-ソース間を介して全信号線 $Y_1$ ～ $Y_n$ に流す。なお、対向電極20c及び給電配線90の一定のコモン電位 $V_{com}$ （例えば、接地=0ボルト）に保たれている。

【0086】

走査線 $X_i$ の選択期間においては、 $i$ 行目の走査線 $X_i$ にシフトパルスが出力されているから、スイッチトランジスタ21及び保持トランジスタ22がオン状態となる。各選択期間において、データドライバ側の電位は、給電配線90, 90, ... 及び供給線 $Z_1$ ～ $Z_m$ に出力されたクロック信号のローレベル以下で且つこのクロック信号のローレベルはコモン電位 $V_{com}$ 以下に設定されている。したがってこの時、有機EL素子20から信号線 $Y_1$ ～ $Y_n$ に流れることはないので、図2に示すように、データドライバによって階調に応じた電流値の書込電流（引抜電流）が矢印Aの通り、信号線 $Y_1$ ～ $Y_n$ に流れ、サブピクセル $P_{i,j}$ においては給電配線90及び供給線 $Z_i$ から駆動トランジスタ23のドレイン-ソース間、スイッチトランジスタ21のドレイン-ソース間を介して信号線 $Y_j$ に向かった書込電流（引抜電流）が流れる。このように駆動トランジスタ23のドレイン-ソース間を流れる電流の電流値は、データドライバによって一義的に制御され、データドライバは、外部から入力された階調に応じて書込電流（引抜電流）の電流値を設定する。書込電流（引抜電流）が流れている間、 $i$ 行目の $P_{i,1}$ ～ $P_{i,n}$ の各駆動トランジスタ23のゲート23g-ソース23s間の電圧は、それぞれ信号線 $Y_1$ ～ $Y_n$ に流れ書込電流（引抜電流）の電流値、つまり駆動トランジスタ23の $V_g - I_{ds}$ 特性の経時変化にかかわらず駆動トランジスタ23のドレイン23d-ソース23s間を流れる書込電流（引抜電流）の電流値に見合うように強制的に設定され、この電圧のレベルに従った大きさの電荷がキャパシタ24にチャージされ、書込電流（引抜電流）の電流値が駆動トランジスタ23のゲート23g-ソース23s間の電圧のレベルに変換される。その後の発光期間では、走査線 $X_i$ がローレベルになり、スイッチトランジスタ21及び保持トランジスタ22がオフ状態となるが、オフ状態の保持トランジスタ22によってキャパシタ24の電極24A側の電荷が閉じ込められてフローティング状態になり、駆動トランジスタ23のソース23sの電圧が選択期間から発光期間に移行する際に変調しても、駆動トランジスタ23のゲート23g-ソース23s間の電位差がそのまま維持される。この発光期間のうち、いずれの行の選択期間でもない間、つまり、クロック信号が給電配線90及び供給線 $Z_i$ の電位が有機EL素子20の対向電極20c及び給電配線90の電位 $V_{com}$ より高いハイレベルの間、より高電位の給電配線90及び供給線 $Z_i$ から駆動トランジスタ23のドレイン-ソース間を介して有機EL素子20に駆動電流が矢印Bの方向に流れ、有機EL素子20が発光する。駆動電流の電流値は駆動トランジスタ23のゲート23g-ソース23s間の電圧に依存するため、発光期間における駆動電流の電流値は、選択期間における書込電流（引抜電流）の電流値に等しくなる。また発光期間において、いずれかの行の選択期間の間、つまりクロック信号がローレベルである時は、給電配線90及び供給線 $Z_i$ の電位が対向電極20c及び給電配線90の電位 $V_{com}$ 以下であるので、有機EL素子20に駆動電流は流れず発光しない。

【0087】

何れの駆動方法においても、スイッチトランジスタ21は、駆動トランジスタ23のソース23sと、信号線 $Y$ との間ににおける電流のオン（選択期間）・オフ（発光期間）を行うものとして機能するようになっている。また、保持トランジスタ22は、選択期間に駆動トランジスタ23のドレイン23d-ソース23s間に電流が流れることができる状態にし、発光期間に駆動トランジスタ23のゲート23g-ソース23s間に印加した電圧を保持するものとして機能するようになっている。そして、駆動トランジスタ23は、発光期間中に供給線 $Z$ 及び給電配線90がハイレベルになった時に、階調に応じた大きさの電流を有機EL素子20に流して有機EL素子20を駆動するものとして機能するようになっている。

【0088】

10

20

30

40

50

以上のように、給電配線 90, 90, ... をそれぞれ流れる電流の大きさは一列の供給線  $Z_i$  に接続された  $n$  個の有機 EL 素子 20 に流れる駆動電流の大きさの和になるので、VGA 以上の画素数で動画駆動するための選択期間に設定した場合、給電配線 90, 90, ... のそれぞれの寄生容量が増大してしまい、トランジスタ 21 ~ 23 のような薄膜トランジスタのゲート電極又はソース、ドレイン電極を構成する薄膜からなる配線では  $n$  個の有機 EL 素子 20 に書込電流（つまり駆動電流）を流すには抵抗が高すぎるが、本実施形態では、サブピクセル  $P_{1,1} \sim P_{m,n}$  の薄膜トランジスタのゲート電極やソース、ドレイン電極とは異なる導電層によって給電配線 90, 90, ... をそれぞれ構成しているので各給電配線 90, 90, ... による電圧降下は小さくなり、短い選択期間であっても遅延なく十分に書込電流（引抜電流）を流すことができる。そして、給電配線 90, 90, ... を厚くすることで給電配線 90, 90, ... を低抵抗化したので、給電配線 90, 90, ... の幅を狭くすることができる。そのため、ボトムエミッションの場合、画素開口率の減少を最小限に抑えることができる。10

#### 【0089】

同様に、発光期間に共通配線 91 に流れる駆動電流の大きさは、選択期間に給電配線 90 に流れる書込電流（引抜電流）の大きさと同じであるが、共通配線 91 は、サブピクセル  $P_{1,1} \sim P_{m,n}$  の薄膜トランジスタのゲート電極やソース、ドレイン電極を構成する導電層とは異なる導電層を用いているので十分な厚さにすることができるため、共通配線 91 を低抵抗化することができ、さらに対向電極 20c 自体が薄膜化してより高抵抗になっても対向電極 20c の電圧を面内で一様にすることができます。従って、仮に全てのサブピクセル電極 20a に同じ電位を印加した場合でも、どの有機 EL 層 20b の発光強度もほぼ等しくなり、面内の発光強度を一様することができます。また、EL ディスプレイパネル 1 をトップエミッション型として用いた場合、対向電極 20c をより薄膜化することが可能なので、有機 EL 層 20b を発した光が対向電極 20c を透過中に減衰し難くなる。更に、平面視して水平方向に隣り合うサブピクセル電極 20a の間に共通配線 91 が設けられているため、画素開口率の減少を最小限に抑えることができる。20

#### 【0090】

さらに、サブピクセル電極 20a、20a 間の非画素領域に配置された信号線  $Y_1 \sim Y_n$  の上方に共通配線 91 群を配置したので、サブピクセル電極 20a の面積を小さくせずに済む。30

#### 【0091】

上述した二通りの駆動方法のうち第二のディスプレイパネル 1 の駆動方法でディスプレイパネル 1 においては、給電配線 90, 90, ... は、絶縁基板 2 の第二の周縁部の引き回し配線 99、端子部 90d 及び端子部 90e を介して外部の発振回路からのクロック信号により等電位となるため、すみやかに有機 EL 素子 20, 20, ... から給電配線 90, 90, ... 全体に電流を供給することができる。

#### 【0092】

第一及び第二の EL ディスプレイパネル 1 の共通配線 91, 91, ... は、絶縁基板 2 の第三周縁部及び第四周縁部に設けられた引き回し配線 95, 95 によって互いに接続され、共通電圧  $V_{com}$  が印加されている。共通配線 91, 91, ... 及び引き回し配線 95, 95 は、走査線  $X_1 \sim X_m$ 、信号線  $Y_1 \sim Y_n$ 、供給線  $Z_1 \sim Z_m$  と電気的に絶縁されている。40

#### 【0093】

##### 【変形例 1】

本実施形態では、各トランジスタ 21, 22, 23 は、N チャンネル型の電界効果トランジスタであるが、本実施形態に限定されず、P チャンネル型の電界効果トランジスタであってもよい。この場合、図 2 に示す回路構成では、各トランジスタ 21, 22, 23 のソース 21s, 22s, 23s と、ドレイン 21d, 22d, 23d の関係が逆となる。例えば、駆動トランジスタ 23 が P チャンネル型の電界効果トランジスタの場合には、駆動トランジスタ 23 のドレイン 23d が有機 EL 素子 20 のサブピクセル電極 20a に導通され、ソース 23s が供給線  $Z$  に導通されている。また駆動信号の波形が逆位相になる。50

## 【0094】

## [変形例2]

また、本実施形態では、信号線Yがゲートレイヤーからパターニングされたものであるが、本実施形態に限定されず、信号線Yがドレインレイヤーからパターニングされたものであってもよい。この場合、走査線X及び供給線Zがゲートレイヤーからパターニングされたものとなり、信号線Yが走査線X及び供給線Zよりも上層となる。

## 【0095】

## [変形例3]

さらに、本実施形態では、1ドットのサブピクセルP当たり3つのトランジスタ21, 22, 23が具備されているが、本実施形態に限定されず、1ドットのサブピクセルP当たり1又は複数のトランジスタが具備され、これらトランジスタを用いてアクティブマトリクス方式により駆動することができるディスプレイパネルであってもよい。

10

## 【0096】

## [変形例4]

さらに、本実施形態では、画素3は3つのサブピクセルP<sub>r</sub>, P<sub>g</sub>, P<sub>b</sub>から構成されているが、本実施形態に限定されず、赤、緑、青の各色の中間色からなるサブピクセルを含んで構成されていてもよい。

## 【0097】

## [変形例5]

また、上記各実施形態では、対向電極20cを有機EL素子20のカソードとし、サブピクセル電極20aを有機EL素子20のアノードとしたが、対向電極20cを有機EL素子20のアノードとし、サブピクセル電極20aを有機EL素子20のカソードとしてもよい。

20

## [変形例6]

また上記各実施形態では、各選択配線89は、スイッチトランジスタ21及び保持トランジスタ22の両方に接続されたが行毎のスイッチトランジスタ21のゲート21gに接続されたスイッチトランジスタ用選択配線と、スイッチトランジスタ用選択配線と分離して行毎の保持トランジスタ22のゲート22gに接続された保持トランジスタ用選択配線と、によって構成されてもよい。

## 【図面の簡単な説明】

30

## 【0098】

【図1】本発明に係る表示装置における画素を示す平面図である。

【図2】サブピクセルPの等価回路図である。

【図3】サブピクセルPの電極を示す平面図である。

【図4】本発明に係る表示装置における画素を示す平面図である

【図5】図4における破断線V-Vに沿って絶縁基板2の厚さ方向に切断した矢視断面図である。

【図6】図4における破断線VI-VIに沿って絶縁基板2の厚さ方向に切断した矢視断面図である。

【図7】ディスプレイパネルの配線構造を示した略平面図である。

40

【図8】図7のディスプレイパネルの駆動方法を説明するためのタイミングチャートである。

【図9】ディスプレイパネルの配線構造を示した略平面図である。

【図10】図9のディスプレイパネルの駆動方法を説明するためのタイミングチャートである。

【図11】サブピクセルPにおける駆動トランジスタ23及び有機EL素子20の電流-電圧特性を示すグラフである。

【図12】32インチのELディスプレイパネル1における給電配線90及び共通配線91のそれぞれの最大電圧降下と、配線抵抗率 / 断面積Sとの相関を示すグラフである。

【図13】32インチのELディスプレイパネル1における給電配線90及び共通配線9

50

1のそれぞれの断面積と、電流密度との相関を示すグラフである。

【図14】40インチのELディスプレイパネル1における給電配線90及び共通配線91のそれぞれの最大電圧降下と、配線抵抗率 / 断面積Sとの相関を示すグラフである。

【図15】40インチのELディスプレイパネル1における給電配線90及び共通配線91のそれぞれの断面積と、電流密度との相関を示すグラフである。

【符号の説明】

【0099】

1 ディスプレイパネル

2 絶縁基板

20a サブピクセル電極

10

20b 有機EL層

20c 対向電極

21 スイッチトランジスタ

22 保持トランジスタ

23 駆動トランジスタ

21d, 22d, 23d ドレイン

21s, 22s, 23s ソース

21g, 22g, 23g ゲート

31 トランジスタ保護絶縁膜

34 第一溝

20

35 第二溝

50 トランジスタアレイ基板

71 バンク

89 選択配線

90 給電配線

91 共通配線

P<sub>r</sub>, P<sub>g</sub>, P<sub>b</sub> サブピクセル

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【 図 7 】

【 図 8 】

【図9】

【図10】

【図11】

【図12】

【図 1 3】

【図 1 4】

【図 1 5】

---

フロントページの続き

(72)発明者 当山 忠久

東京都八王子市石川町2951番地5 カシオ計算機株式会社 八王子技術センター内

(72)発明者 尾崎 剛

東京都八王子市石川町2951番地5 カシオ計算機株式会社 八王子技術センター内

(72)発明者 小倉 潤

東京都八王子市石川町2951番地5 カシオ計算機株式会社 八王子技術センター内

審査官 渡邊 吉喜

(56)参考文献 特開2004-101948 (JP, A)

特開2004-029528 (JP, A)

特開2004-004663 (JP, A)

特開2004-227870 (JP, A)

特開2001-203080 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09F 9/30 - 9/46