#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2014/179366 A1

(43) International Publication Date 6 November 2014 (06.11.2014)

(51) International Patent Classification:

H01L 31/18 (2006.01) H01L 31/04 (2014.01)

H01L 31/024 (2014.01)

(21) International Application Number:

PCT/US2014/035961

(22) International Filing Date:

29 April 2014 (29.04.2014)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/816,830 29 April 2013 (29.04.2013) US 61/827,252 24 May 2013 (24.05.2013) US 61/859,166 26 July 2013 (26.07.2013) US

- (71) Applicant: SOIEXEL, INC. [US/US]; 1530 McCarthy Blvd, Milpitas, CA 95035 (US).

- (72) Inventors; and

- (71) Applicants: RANA, Virendra, V. [US/US]; 1530 McCarthy Blvd., San Jose, CA 95035 (US). MOSLEHI, Mehrdad, M. [US/US]; 956 Stanley Ave., Los Altos, CA 94024 (US). KAPUR, Pawan [US/US]; 1530 McCarthy Blvd., San Jose, CA 95035 (US). BENJAMIN, Rattle [US/US]; 1530 McCarthy Blvd., San Jose, CA 95035 (US). DESHAZER, Heather [US/US]; 1530 McCarthy Blvd., San Jose, CA 95035 (US). COUTANT, Solene [US/US]; 1530 McCarthy Blvd., San Jose, CA 95035 (US). KOMMERA, Swaroop [US/US]; 1530 McCarthy Blvd., San Jose, CA 95035 (US).

- (74) Agent: WOOD, John Ryan, C.; Solexel, Inc., 1530 Mccarthy Blvd., Milpitas, CA 95035 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

#### Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: ANNEALING FOR DAMAGE FREE LASER PROCESSING FOR HIGH EFFICIENCY SOLAR CELLS

(57) Abstract: Annealing solutions providing damage-free laser patterning utilizing auxiliary heating to anneal laser damaged ablation regions are provided herein. Ablation spots on an underlying semiconductor substrate are annealed during or after pulsed laser ablation patterning of overlying transparent passivation layers.

# ANNEALING FOR DAMAGE FREE LASER PROCESSING FOR HIGH EFFICIENCY SOLAR CELLS

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the benefit of U.S. provisional patent applications 61/816,830 filed on April 29, 2013, 61/827,252 filed May 24, 2013, and 61/859,166 filed July 26, 2013, which are all hereby incorporated by reference in their entirety. This application is a continuation-in-part of U.S. Pat. App. Nos. 13/90115 filed May 29, 2013 and 14/137,172 filed December 20, 2013, which are all hereby incorporated by reference in their entirety.

# **FIELD**

5

10

15

20

25

30

[0002] The present disclosure relates in general to the fields of solar photovoltaic (PV) cells, and more particularly to laser processing of photovoltaic solar cell substrates.

# **BACKGROUND**

[0003] Laser processing offers several advantages in terms of efficiency enhancement and manufacturing cost reduction for high-performance, high-efficiency solar cell processing. Firstly, advanced crystalline silicon solar cells may benefit from having the dimensions of the critical features such as electrical contacts be much smaller than the current industrial practice. For front contacted solar cells the contact area of the front metallization to the emitter as well as the contact area of the back metal to the base needs to be low (or the contact area ratios should be fairly small, preferably much below 10%). For an all back-contact, back-junction solar cell, where the emitter and base regions forming the p/n junction and the metallization are on the same side (the cell backside opposite the sunny side), the dimensions of the various features are typically small for high efficiency. In these cells where typically the emitter and base regions form alternate stripes, the width of these regions (in particular the width of the base contact) tends to be small. Also, the dimensions of the metal contacts to these regions tend to be proportionally small. The metallization connecting to the emitter and base regions then needs to be patterned to a correspondingly finer scale. Generally, lithography and laser processing are the technologies that have the relatively fine resolution capability to provide the small dimensions

and the control required. Of these techniques, only laser processing offers the low cost advantage required in solar cell making. While lithography requires consumables such as photoresist and subsequent resist developer and stripper (which add to the process cost and complexity), laser processing is a non-contact, dry, direct write method and does not require any material consumables, making it a simpler and lower cost process for solar cell fabrication. Moreover, laser processing is an excellent choice for environmentally benign manufacturing since it is an all-dry process which does not use any consumables such as chemicals.

[0004] Further, to reduce the cost of solar cells there is a push to reduce the thickness of the crystalline silicon used and also at the same time increase the cell area for more power per cell and lower manufacturing cost per watt. Laser processing is suitable for these thin wafers and thin-film cell substrates as it is a completely non-contact, dry process and can be easily scaled to larger cell sizes.

[0005] Laser processing is also attractive as it is generally a "green" and environmentally benign process, not requiring or using poisonous chemicals or gases. With suitable selection of the laser and the processing system, laser processing presents the possibility of very high productivity with a very low cost of ownership.

[0006] Despite these advantages, the use of laser processing in crystalline silicon solar cell making has been limited because laser processes that provide high performance cells have not been developed. Disclosed here are laser processes using schemes that are tailored for each key application to produce solar cells with high efficiency. Specific embodiments are also disclosed for applications of laser processing in manufacturing thin-film crystalline silicon solar cells, such as those manufactured using sub-50-micron silicon substrates formed by epitaxial silicon growth.

## **SUMMARY**

5

10

15

20

25

30

[0007] Various laser processing schemes are disclosed herein for producing hetero-junction and homo-junction solar cells. The methods include base and emitter contact opening, front and back surface field formation, selective doping, metal ablation, annealing, and passivation. In particular, annealing solutions providing damage-free laser patterning utilizing auxiliary heating to anneal laser damaged ablation regions are provided herein. Also, laser processing schemes are disclosed that are suitable for selective amorphous silicon ablation and selective doping for hetero-junction solar cells. These laser processing techniques may be applied to semiconductor

substrates, including crystalline silicon substrates, and further including crystalline silicon substrates which are manufactured either through wire saw wafering methods or via epitaxial deposition processes, that are either planar or textured/three-dimensional. These techniques are highly suited to thin crystalline semiconductor, including thin crystalline silicon films.

5

10

15

20

25

30

[8000]Laser processing schemes are disclosed that meet the requirements of base to emitter isolation (including but not limited to shallow trench isolation) for all back-contact homojunction emitter solar cells (such as high-efficiency back-contact crystalline silicon solar cells), opening for base doping, and base and emitter contact opening (with controlled small contact area ratios, for instance substantially below 10% contact area ratio, for reduced contact recombination losses and increased cell efficiency), selective doping (such as for base and/or emitter contact doping), and metal ablation (formation of patterned metallization layers such as creating the patterned metallization seed layer on a thin-film monocrystalline silicon solar cell prior to subsequent attachment of a backplane to the cell and its release from a reusable host template) for both front-contact and all back-contact/back-junction homo-junction emitter solar cells. Also, laser processing schemes are disclosed that are suitable for selective amorphous silicon ablation and oxide (such as a transparent conductive oxide (TCO)) ablation, and metal ablation for metal patterning for hetero-junction solar cells (such as back-contact solar cells comprising hetero-junction amorphous silicon emitter on monocrystalline silicon base). These laser processing techniques may be applied to semiconductor substrates, including crystalline silicon substrates, and further including crystalline silicon substrates which are manufactured either through wire saw wafering methods or using epitaxial deposition processes, which may be either planar or textured/three-dimensional, where the three-dimensional substrates may be obtained using epitaxial silicon lift-off techniques using porous silicon seed/release layers or other types of sacrificial release layers. These techniques are highly suited to thin crystalline semiconductor, including thin crystalline silicon films obtained using epitaxial silicon deposition on a template comprising a porous silicon release layer or other techniques known in the industry.

[0009] An all back-contact homo-junction solar cell may be formed in the crystalline silicon substrate, wherein laser processing is used to perform one or a combination of the following: micromachine or pattern the emitter and base regions including base to emitter isolation as well as openings for base, provide selective doping of emitter and base, make openings to base and

emitter for metal contacts, provide metal patterning, provide annealing, and provide passivation. A front contacted homo-junction (emitter) solar cell may be made using laser processing for selective doping of emitter and making openings for metal contacts for both frontside and backside metallization. A hetero-junction all back-contact back-contact solar cell may be made using laser processing for defining the base region and conductive oxide isolation.

# **BRIEF DESCRIPTION OF THE DRAWINGS**

5

10

15

- [0010] The features, nature, and advantages of the disclosed subject matter will become more apparent from the detailed description set forth below when taken in conjunction with the drawings, in which like reference numerals indicate like features and wherein:

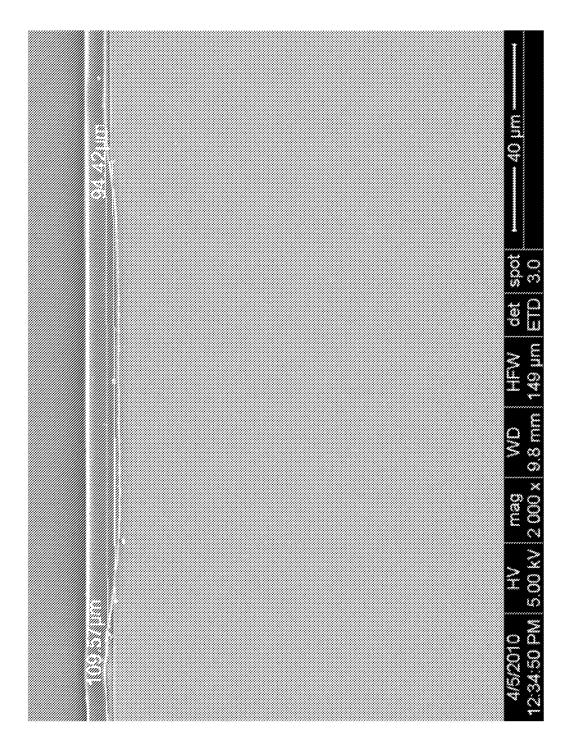

- [0011] FIG. 1 shows a scanning electron microscope (SEM) image of a shallow trench made in silicon for application in an all back contact back-junction solar cell, in accordance with the present disclosure;

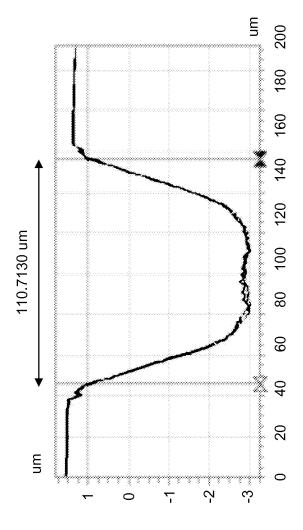

- [0012] FIG. 2 shows a profile of a shallow trench in silicon for application in all back contact back junction solar cells;

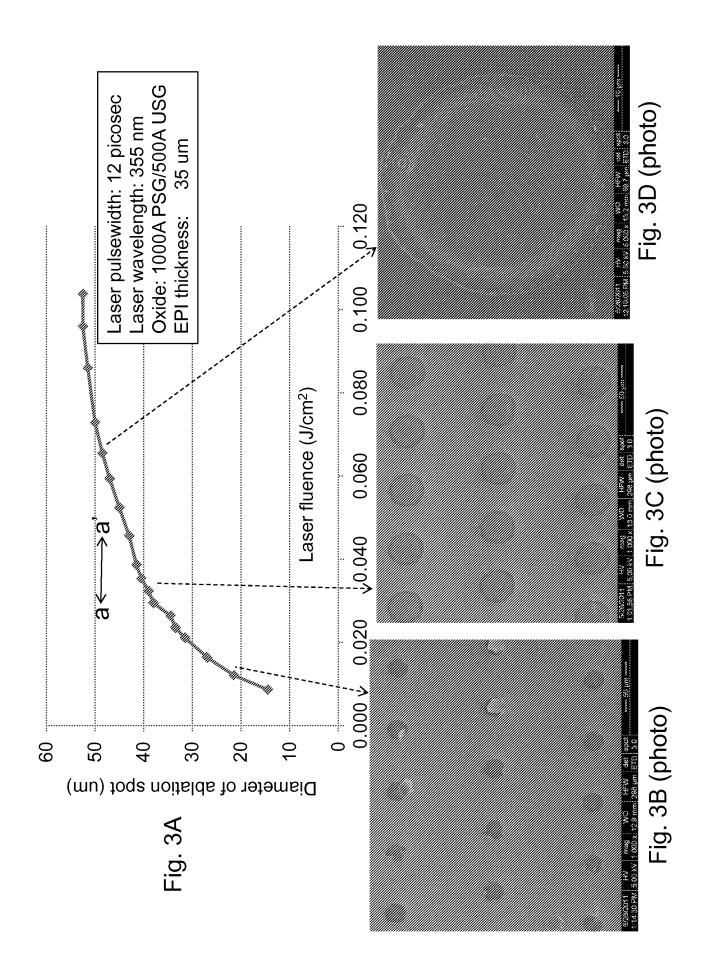

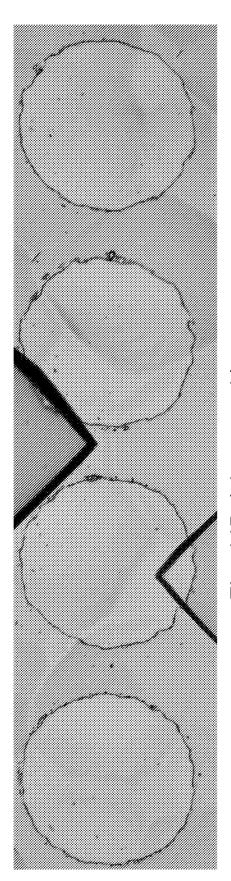

- [0013] FIGS. 3A-3D show the procedure for selecting the laser fluence to obtain reduced damage silicon dioxide (or oxide) ablation. FIG. 3A shows the dependence of the size of the ablation spot on the laser fluence; FIG. 3B shows irregular delamination of oxide; FIG. 3C shows a damage-free spot; and FIG. 3D shows highly damaged silicon in the spot opening;

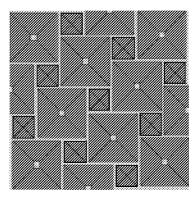

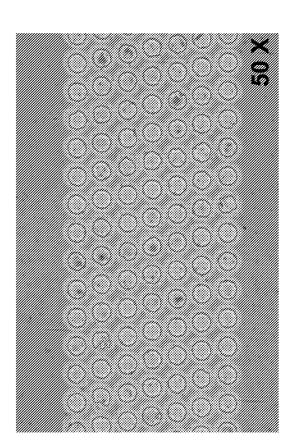

- 20 **[0014] FIG. 4** shows substantially parallel rows of contacts opened in oxide using pulsed laser ablation in accordance with the present disclosure;

- [0015] FIG. 5 shows a screenshot with oxide ablation spots for metal contacts;

- [0016] FIG. 6A and 6B show the laser-ablated area formed by making ablation spots that are overlapped in both the x and y-direction; FIG. 6A shows a 180 micron wide strip opened in 1000A BSG (boron-doped oxide)/500A USG (undoped oxide) for base isolation region; and FIG. 6B shows a ~90 micron wide stripe opened in 1000A USG (undoped oxide) for base region;

- [0017] FIG. 7A shows the threshold for oxide damage, below which metal can be removed without metal penetration of the oxide layer;

- FIG. 7B shows that after 20 scans the metal runners are fully isolated;

- [0019] FIG. 7C shows an optical micrograph of the trench formed in this metal stack;

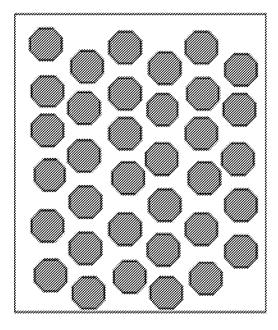

[0020] FIGS. 8A and 8B show a top view and a cross-sectional view of a pyramidal TFSC;

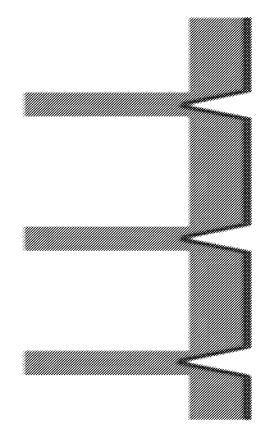

- [0021] FIGS. 9A and 9B show a top view and a cross-sectional view of a prism TFSC;

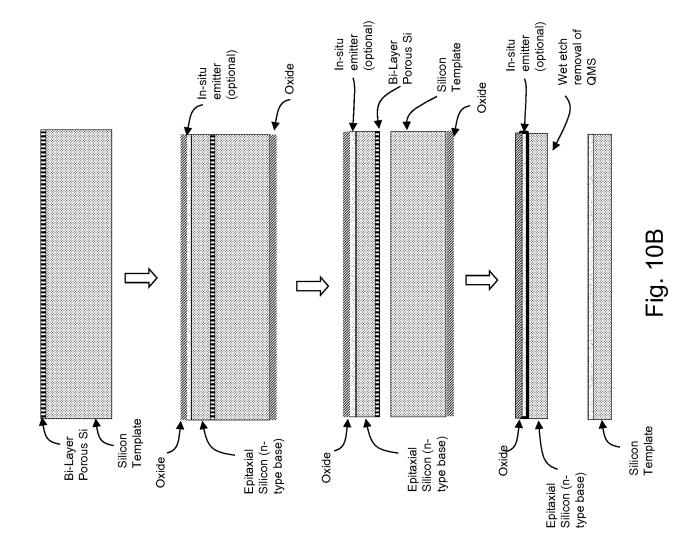

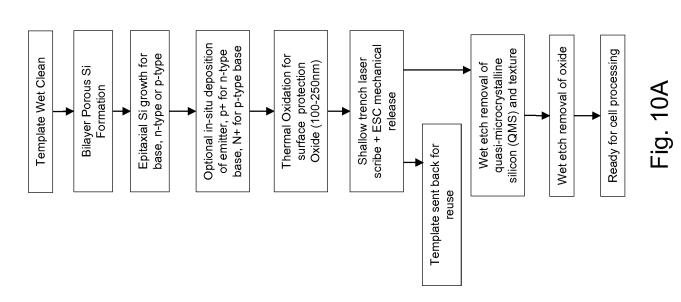

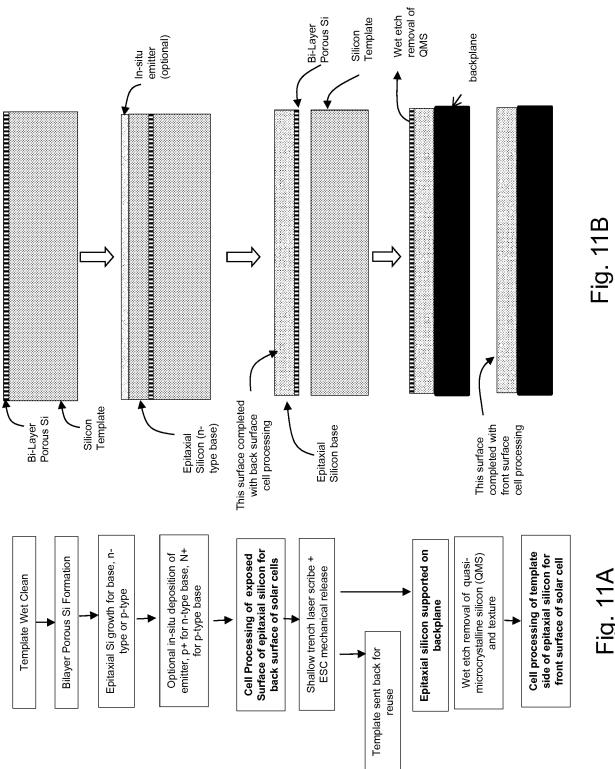

- [0022] FIGS. 10A and 10B show a process flow for creation and release of a planar epitaxial thin film silicon solar cell substrate (TFSS);

- 5 **[0023]** FIGS. 11A and 11B show a process flow for planar epitaxial thin film silicon solar cell substrate in case the TFSS is too thin to be free standing or self-supporting;

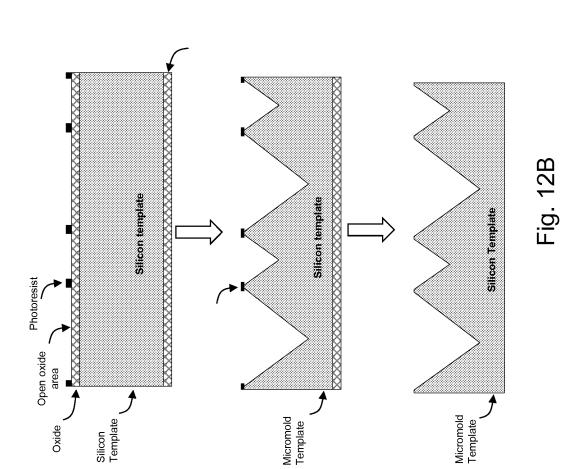

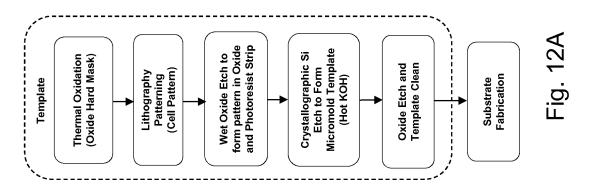

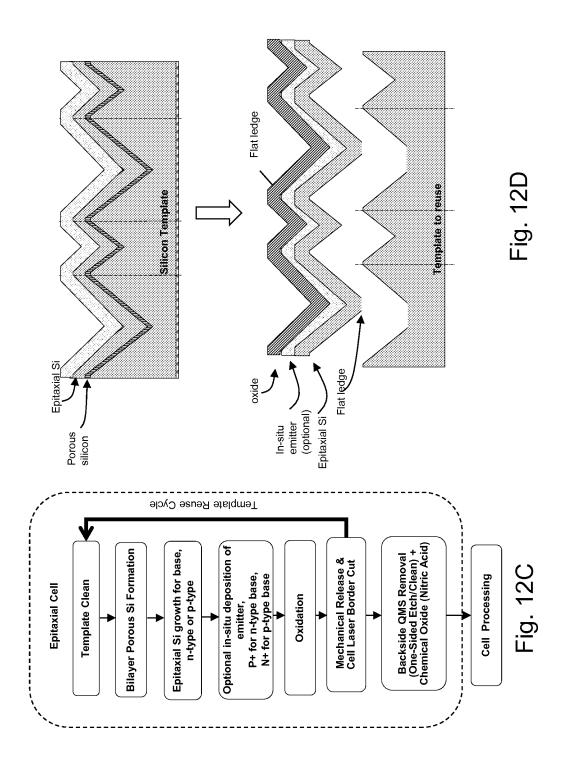

- [0024] FIGS. 12A and 12B show a process flow for micromold template (or reusable template) creation for making a 3-D TFSS;

- [0025] FIGS. 12C and 12D show a process flow for 3-D TFSS creation using the reusable micromold template;

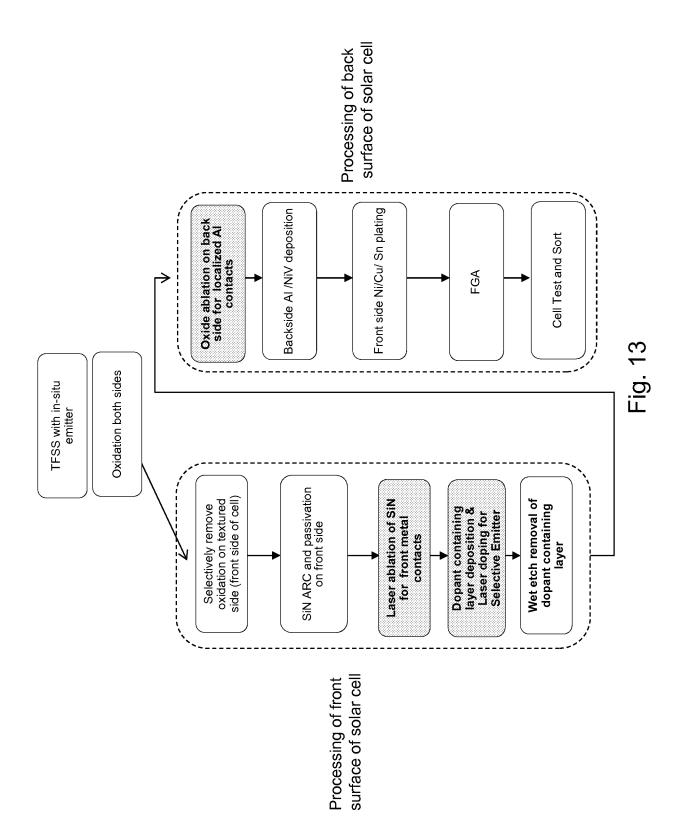

- [0026] FIGS. 13 shows a process flow for making a planar front contacted solar cell where the TFSS is thick enough to be free standing and self-supporting (e.g. thicker than approximately 50 microns for smaller 100 mm x 100 mm substrates and thicker than approximately 80 microns for 156 mm x 156 mm substrates), in accordance with the present disclosure;

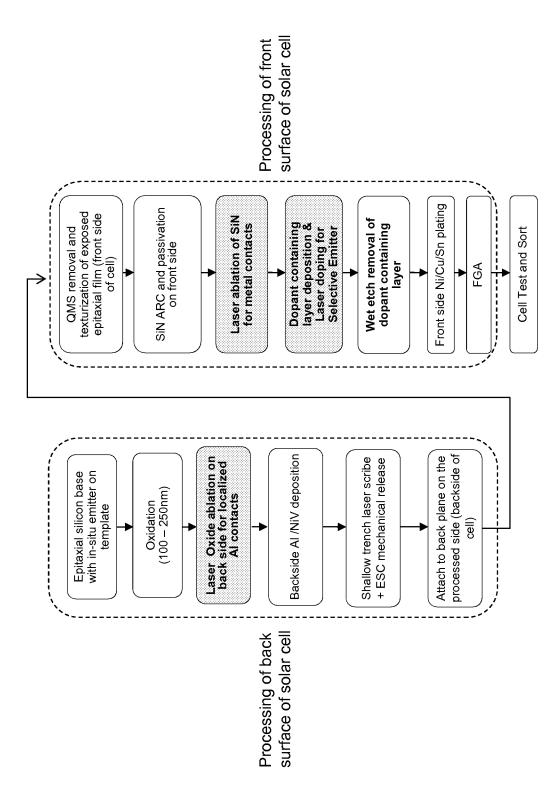

- 15 **[0027] FIGS. 14** shows a process flow for making a planar front contact solar cell where the TFSS is too thin to be self supporting, in accordance with the present disclosure;

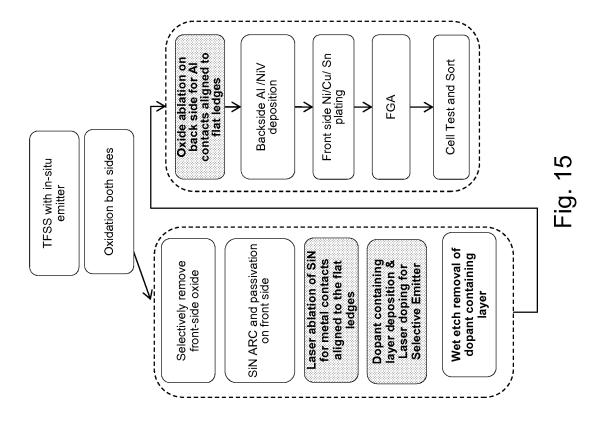

- [0028] FIG. 15 shows a process flow for making a 3-D front contact solar cell in accordance with the present disclosure;

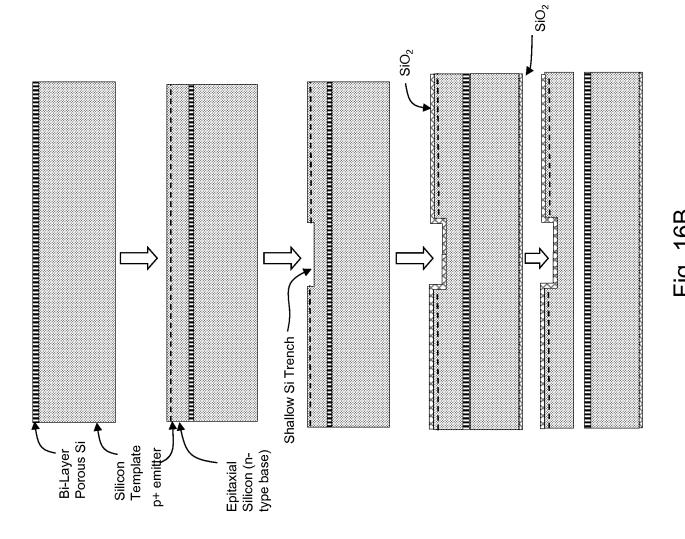

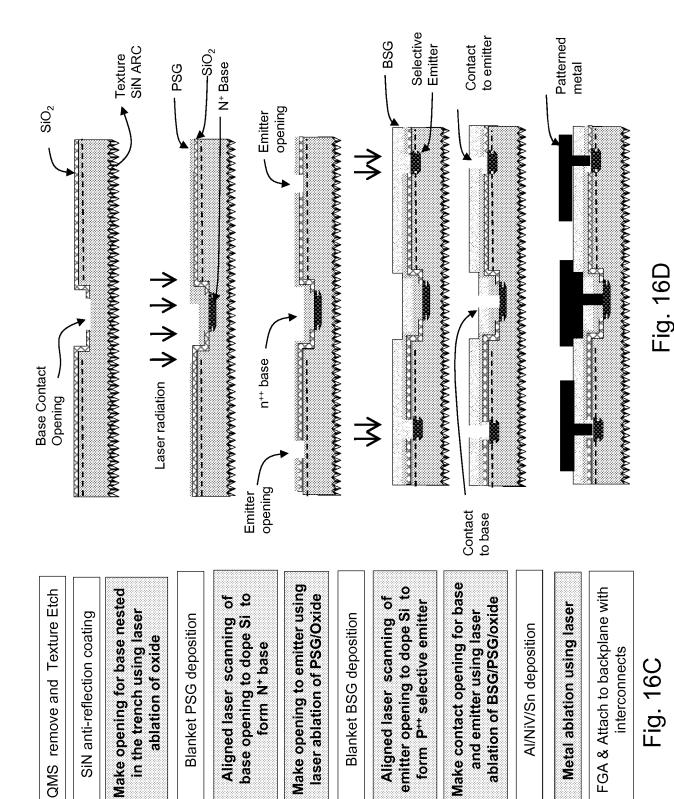

- [0029] FIGS. 16A–16D show a process flow for making an interdigitated back contact

back-junction solar cell where the TFSS is thick enough to be self supporting, in accordance with the present disclosure;

- [0030] FIG. 17 shows a process flow for making an interdigitated back-contact back-junction solar cell using thick TFSS where the in-situ emitter is not deposited. Instead, a BSG (boron-doped oxide) layer is deposited on the epitaxial silicon film and patterned to open the base isolation region, in accordance with the present disclosure;

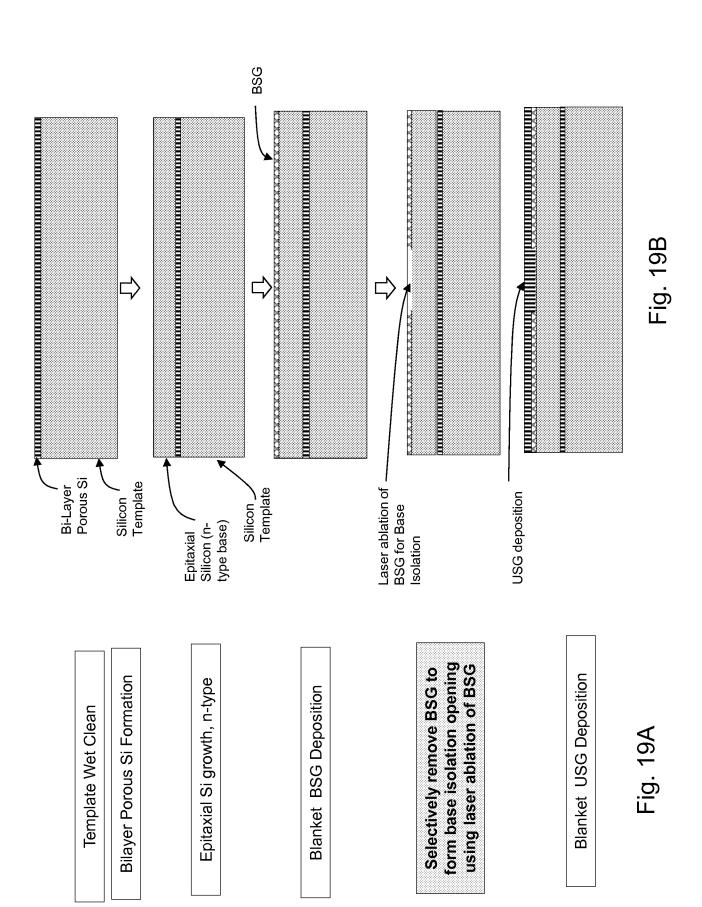

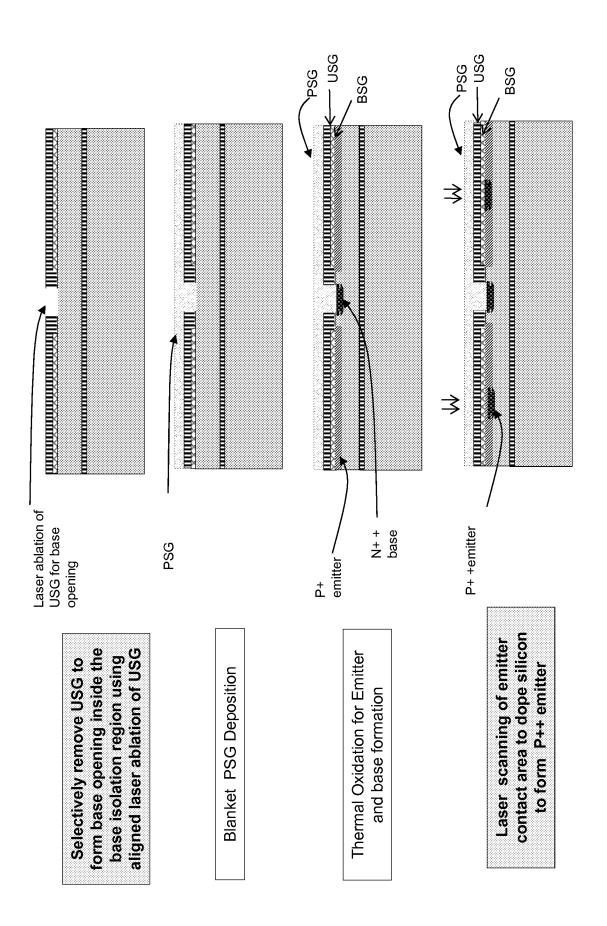

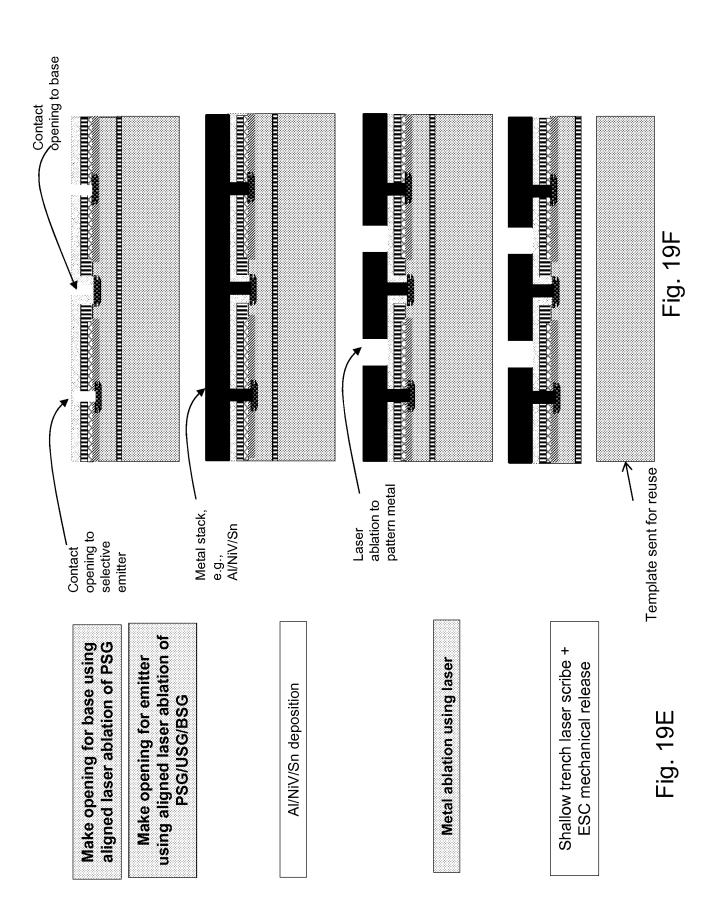

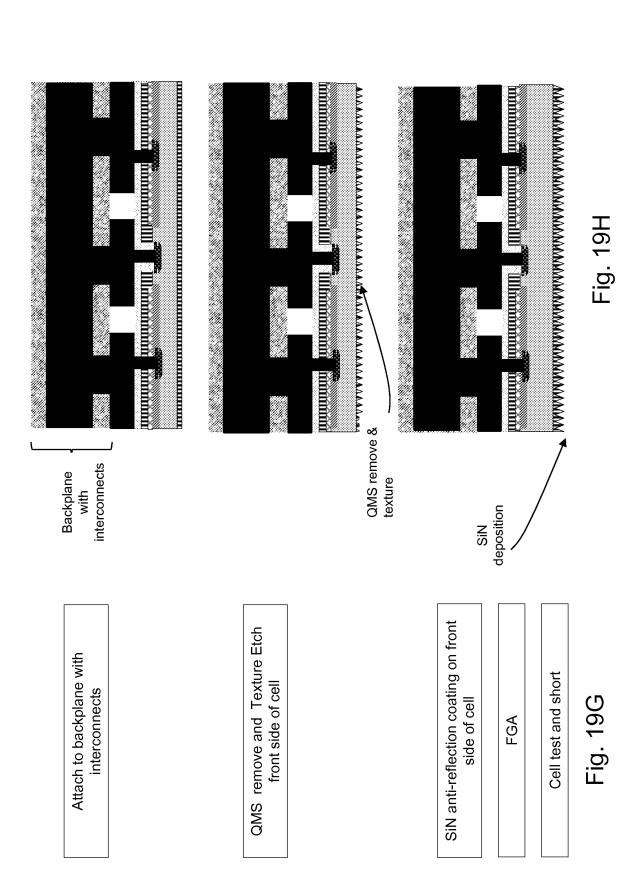

- **FIG. 18** shows a process flow for making an interdigitated back-contact back-junction solar cell where the TFSS is not thick enough to be self supporting, where *in-situ* emitter and laser ablation of silicon is used to form the base isolation opening, in accordance with the present disclosure;

- **FIGS. 19A–19H** show a process flow for making an interdigitated back-contact back-junction solar cell where the TFSS is not thick enough to be self supporting, and where

instead of *in-situ* emitter BSG (boron-doped oxide) deposition and selective laser etchback is used to form the base isolation opening, in accordance with the present disclosure;

- [0033] FIG. 20 shows a process flow for making an interdigitated back-contact back-junction solar cell using a 3-D TFSS, in accordance with the present disclosure;

- 5 [0034] FIG. 21 shows a process flow for making an interdigitated back-contact back-junction hetero-junction solar cell, in accordance with the present disclosure;

- [0035] FIGs 22 through 30 are not found in U.S. Patent Application No. 13/118,295 "LASER PROCESSING FOR HIGH-EFFICIENCY THIN CRYSTALLINE SILICON SOLAR CELL FABRICATION" by Virendra V. Rana and filed on May 27, 2011;

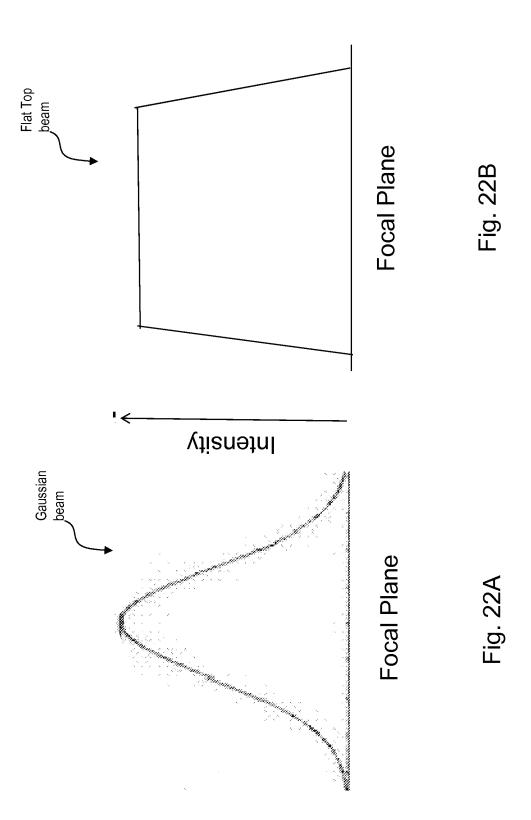

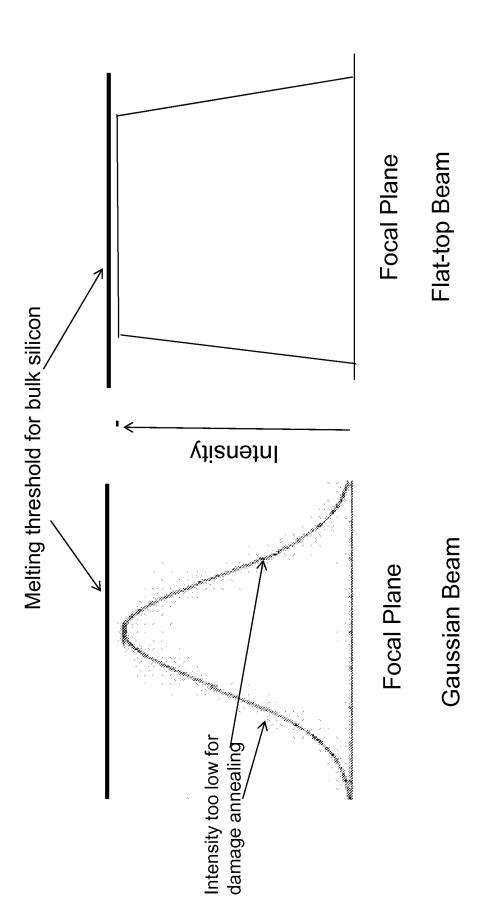

- 10 [0036] FIG. 22A and 22B are schematics showing the profile of a Gaussian beam and a flat top beam, respectively;

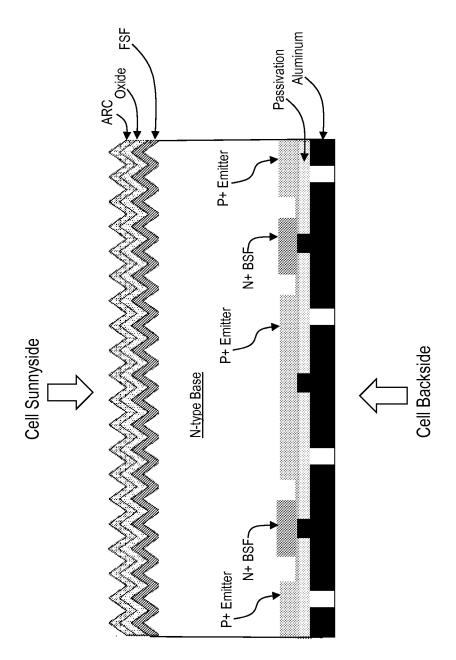

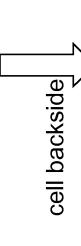

- [0037] FIG. 23 is a cross-sectional diagram of a back-contact /back-junction cell;

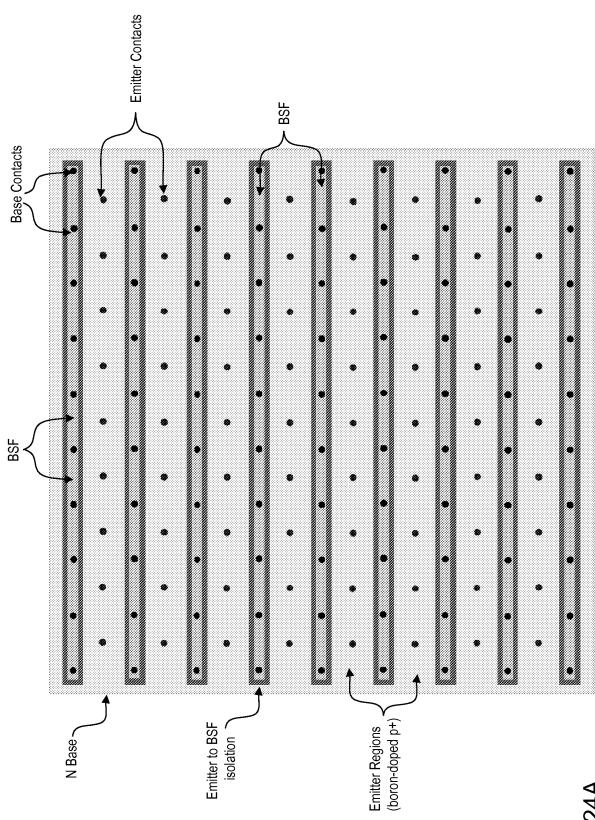

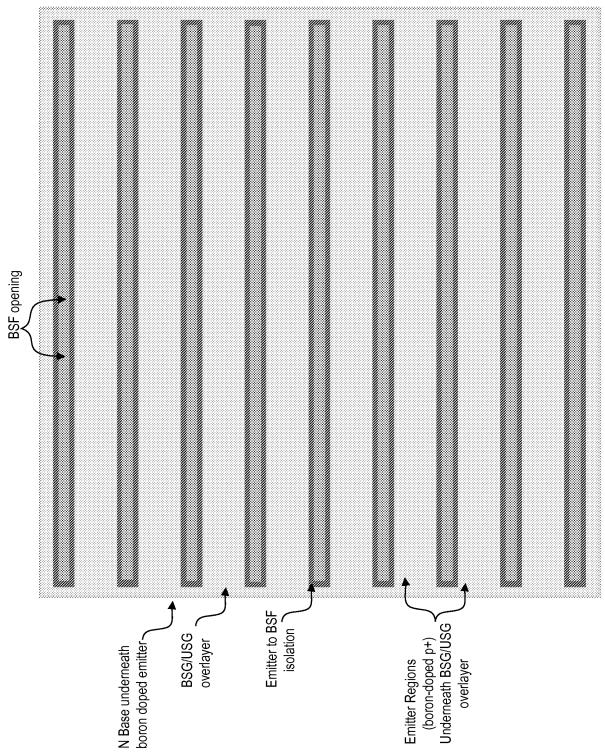

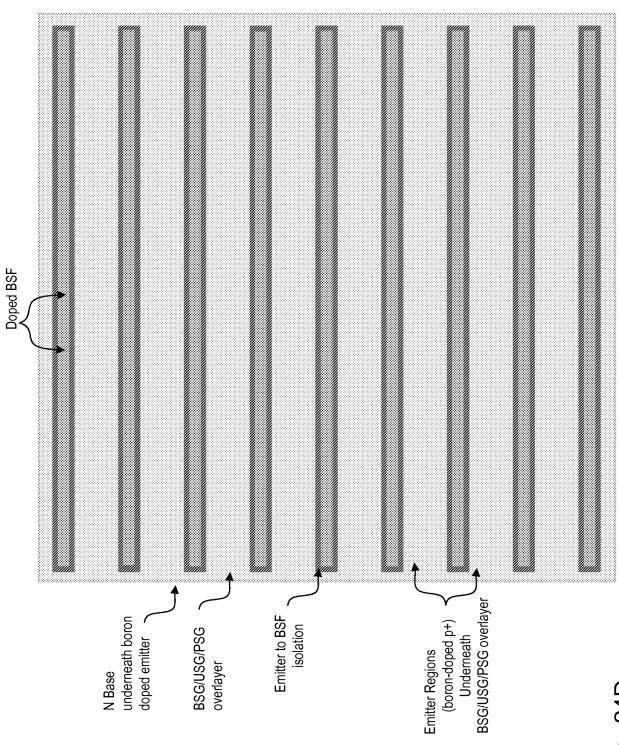

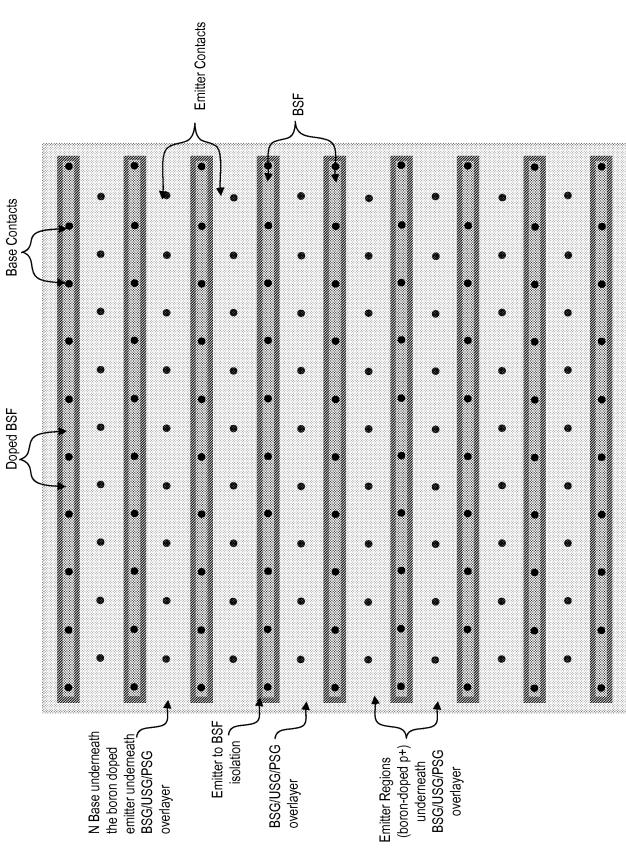

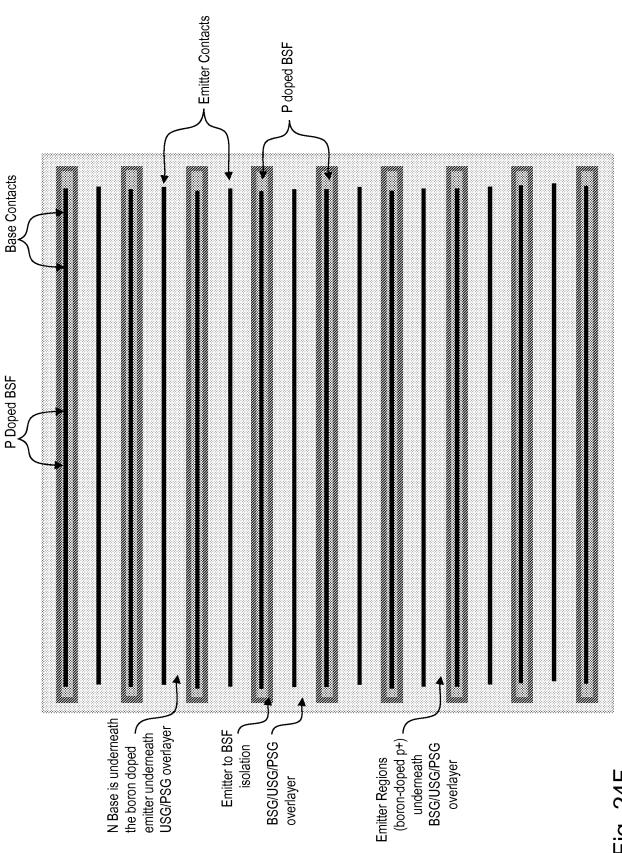

- [0038] FIGs 24A 24F are rear/backside views of a back contact solar cell during fabrication;

- 15 [0039] FIG. 25 is a rear/backside view of the back contact solar cell of FIG. 24A with alternating metal lines contacting the emitter and base regions;

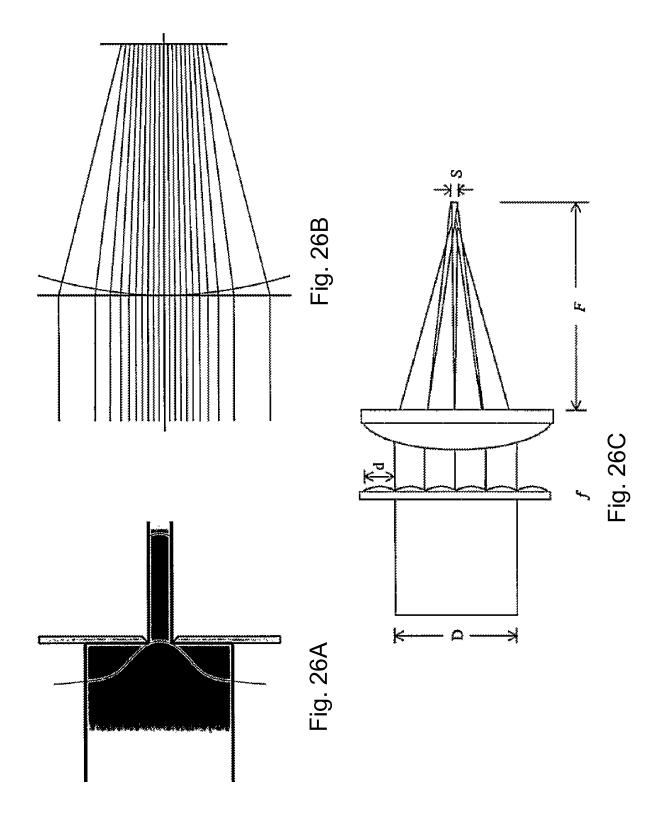

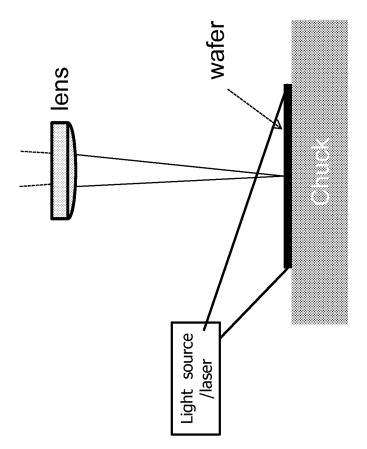

- [0040] FIGs 26A 26C are diagrams illustrating three ways a flat-top beam profile may be created;

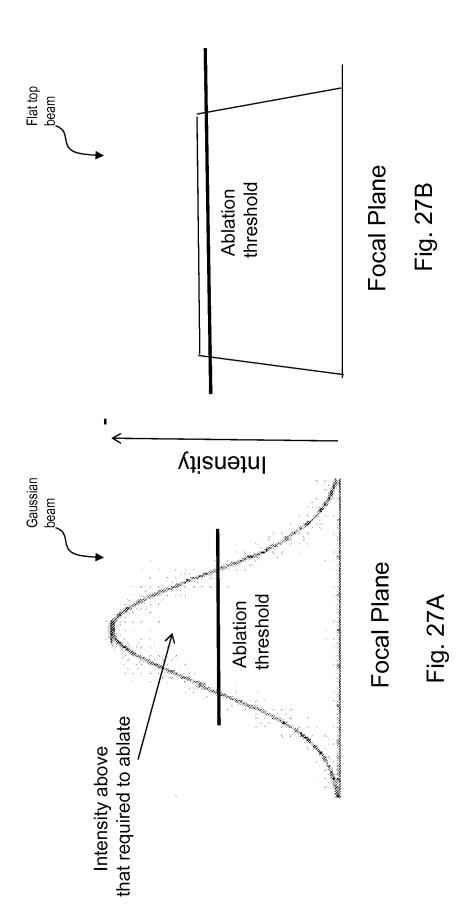

- [0041] FIG. 27A and 27B are schematics showing the profile of a Gaussian beam and a flat top beam highlighting the ablation threshold;

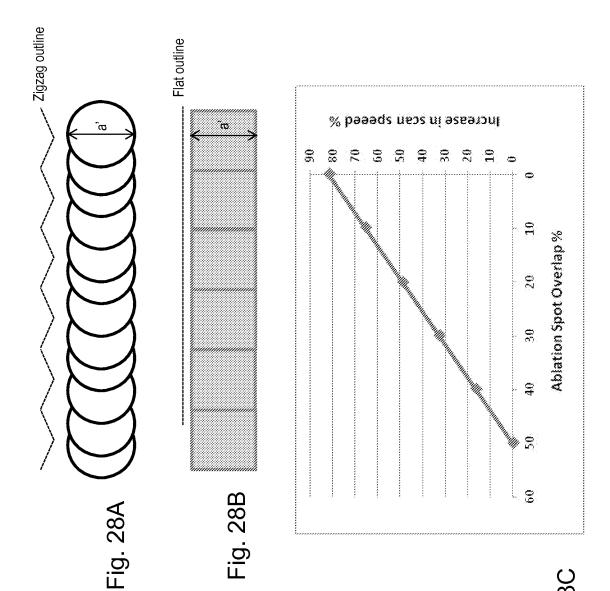

- [0042] FIGs 28A and 28B are diagrams showing a Gaussian beam and a flat top beam ablate region profile/footprint, respectively;

- [0043] FIG 28C is a graph of overlap and scan speed;

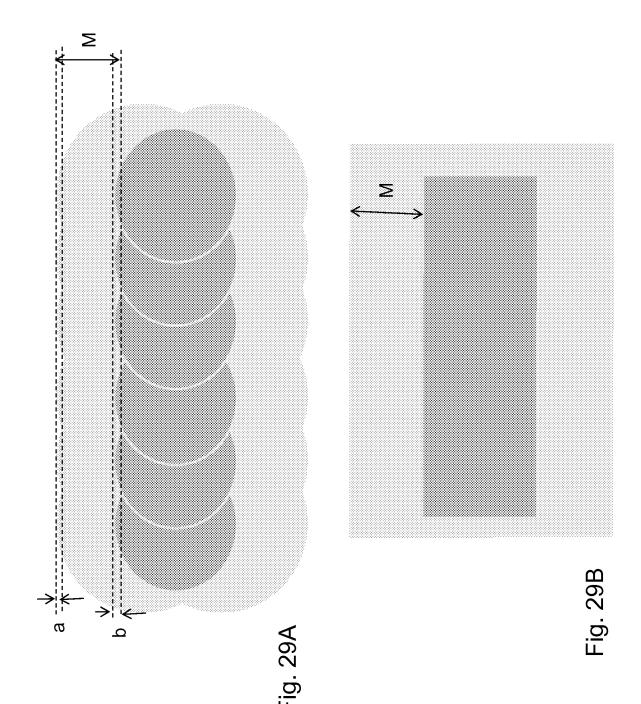

- [0044] FIG 29A and 29B are diagrams illustrating a beam alignment window of a Gassian beam and flat top beam, respectively;

- [0045] FIG 29C and 29D are diagrams showing a Gaussian beam region profile and a flat top beam region profile, respectively; and

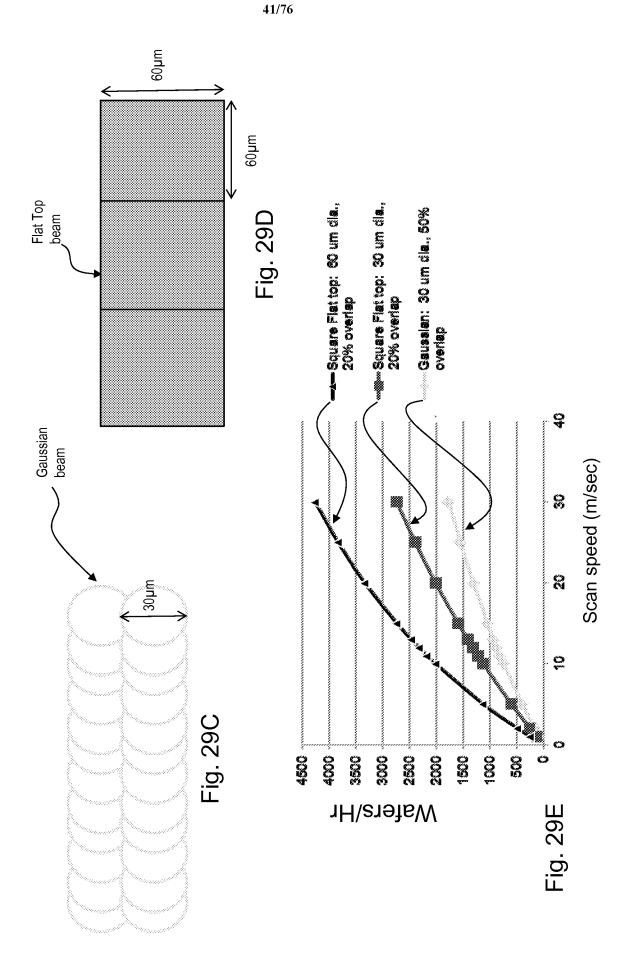

- [0046] FIG. 29E graphically depicts the results of Table 1;

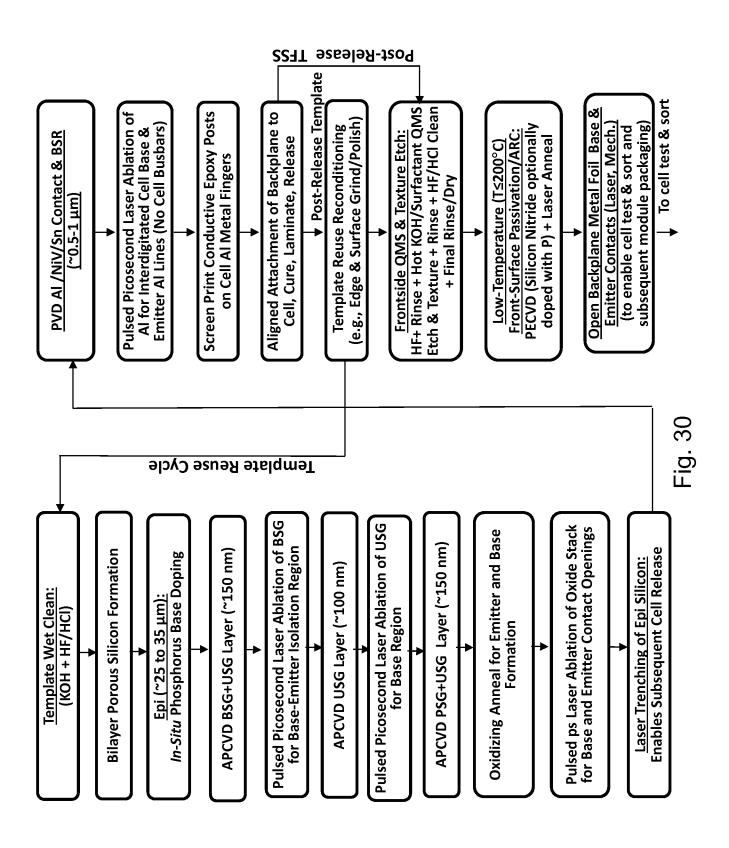

- [0047] FIG. 30 shows a process flow for an NBLAC cell;

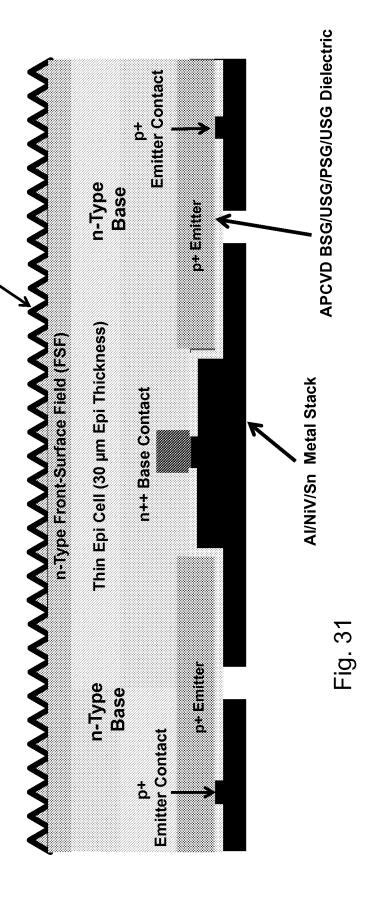

- 30 [0048] FIG. 31 shows a schematic cross section of an NBLAC cell;

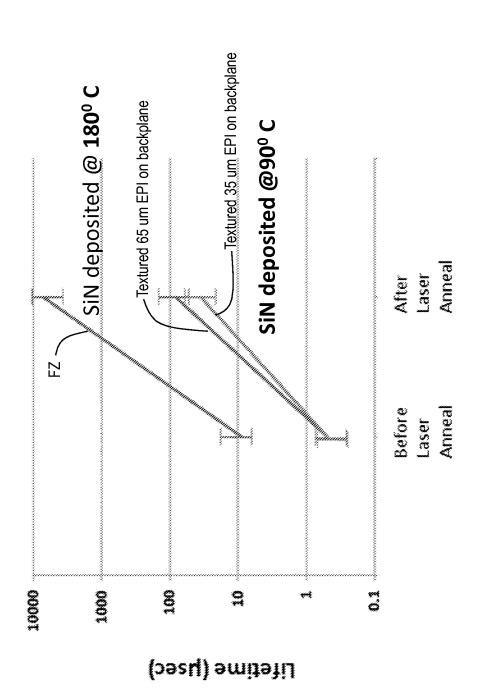

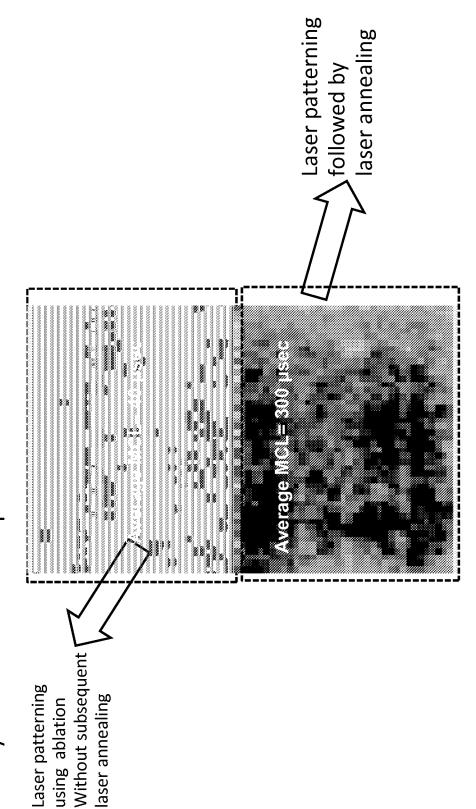

- [0049] FIG. 32 shows a graph of minority carrier lifetime with and without laser annealing;

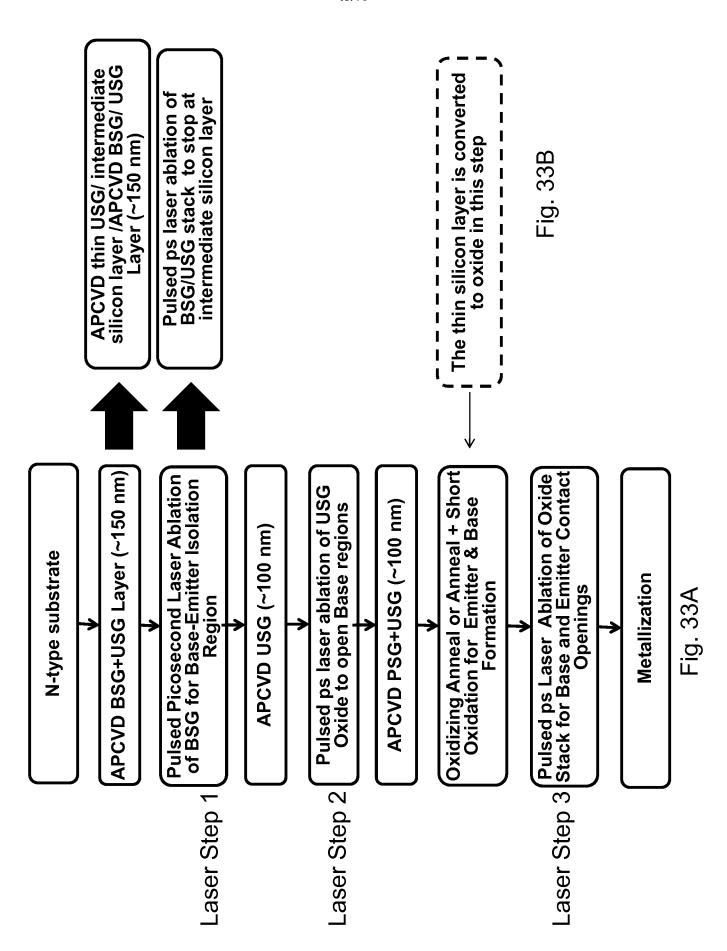

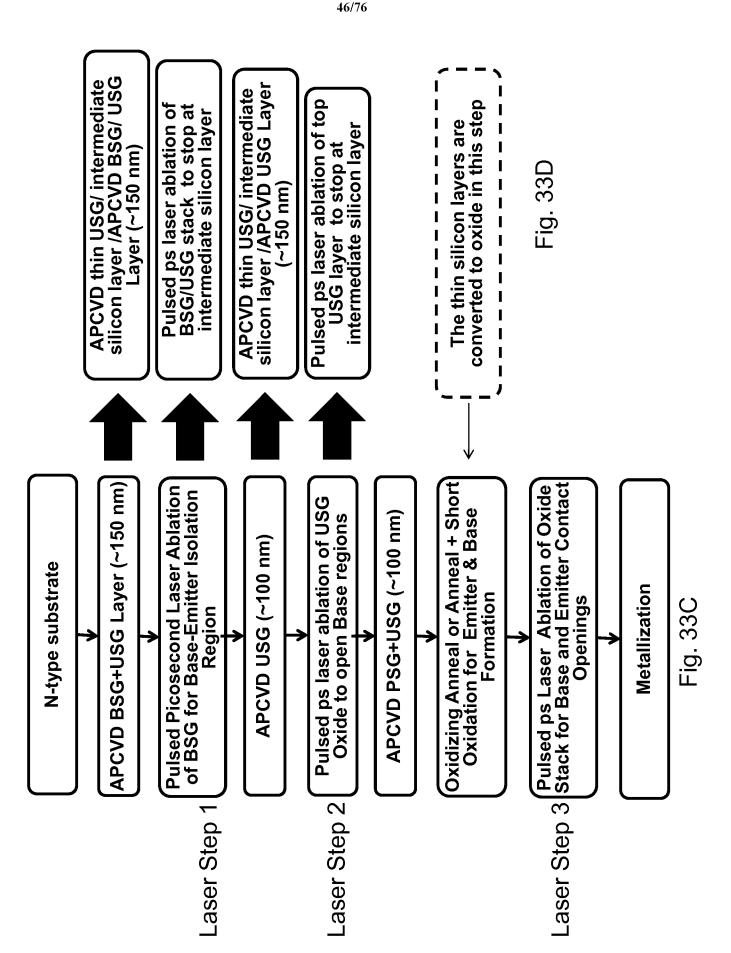

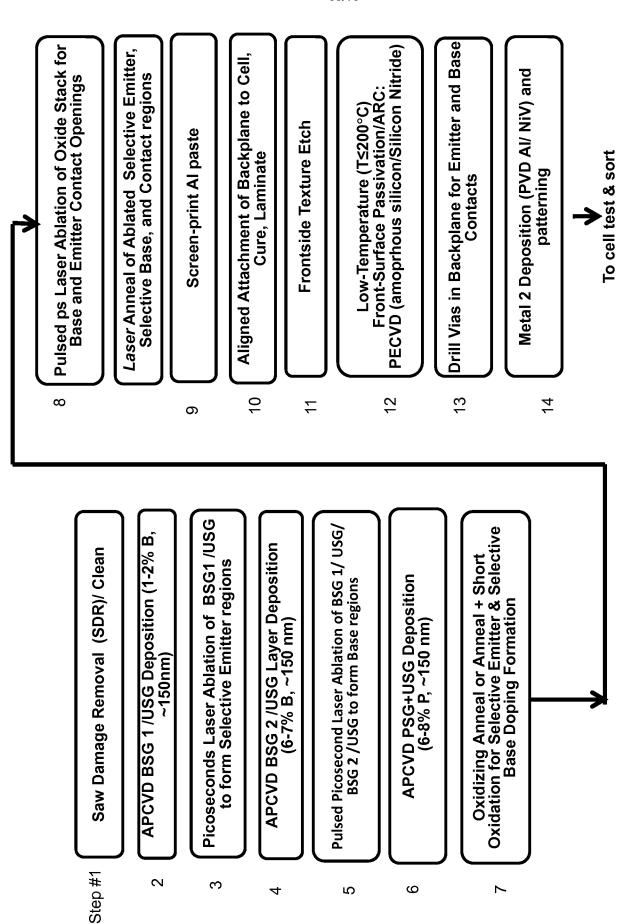

[0050] FIGS. 33A and 33B show process flows for all back contact solar cells with oxide ablation;

- [0051] FIGS. 33C and 33D show process flows for all back contact solar cells with oxide ablation;

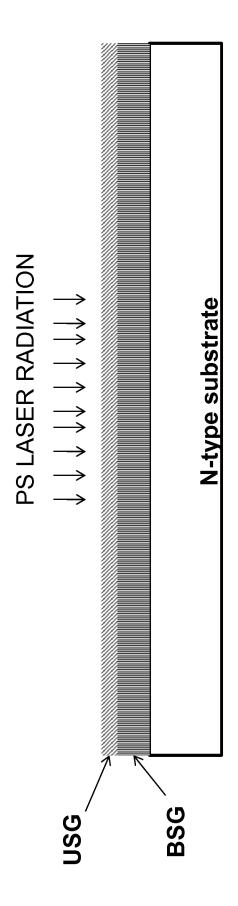

- 5 [0052] FIGS. 34A and 34B show an oxide ablation process;

- [0053] FIGS. 35A and 35B show an oxide ablation process using an amorphous silicon layer;

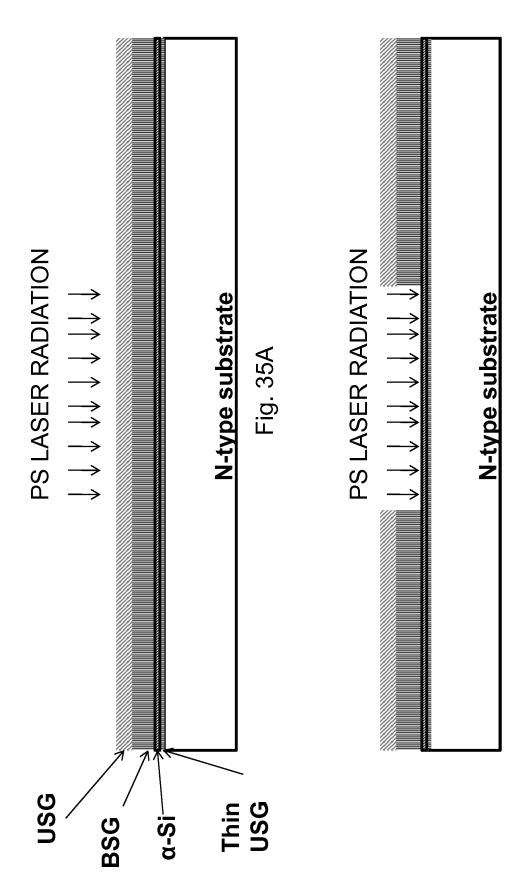

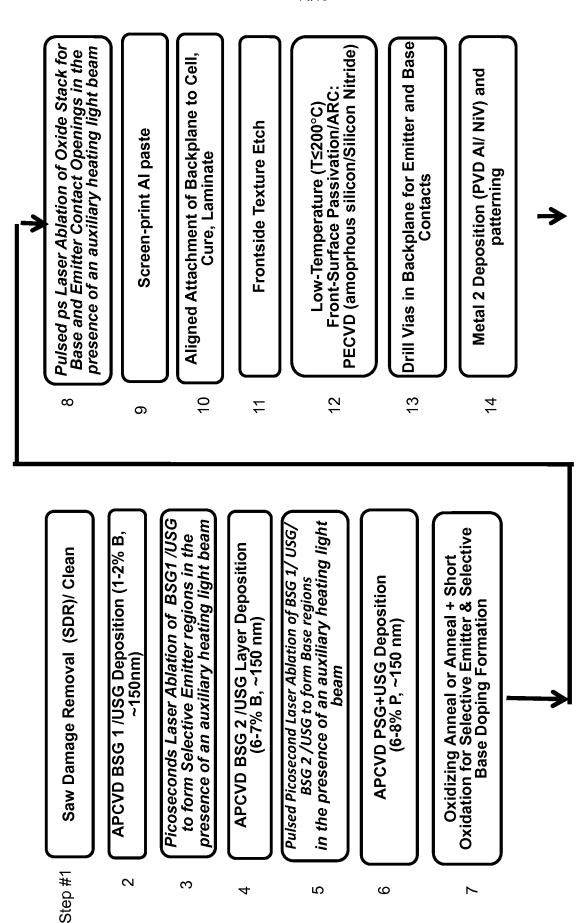

- [0054] Fig. 36 outlines the process flow to form back-junction, back-contact solar cell using a starting wafer;

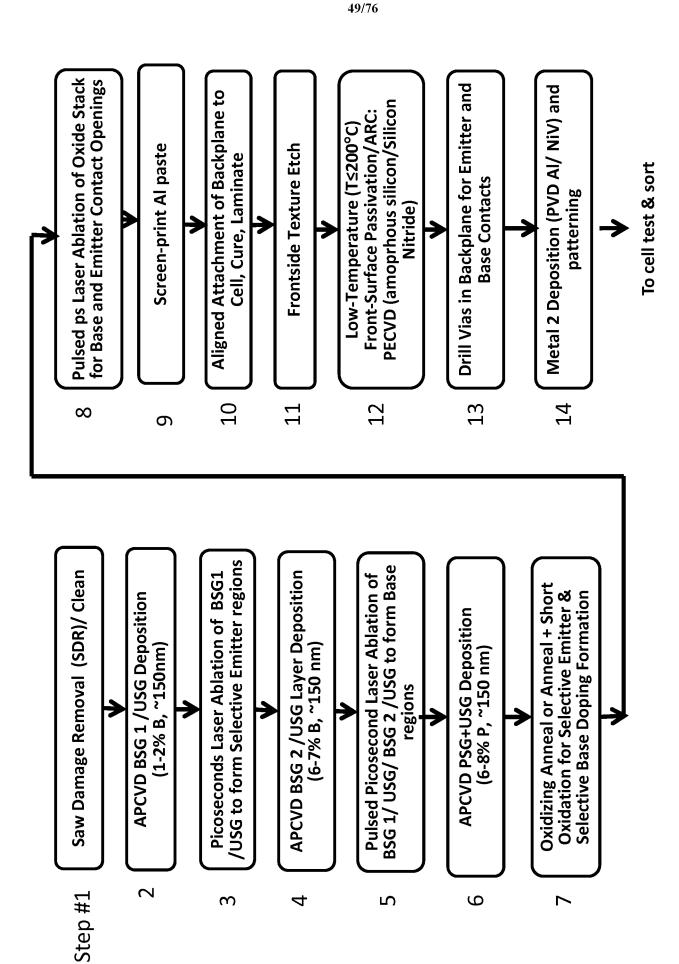

- 10 **[0055]** Figs. 37A and 37B are cross-sectional diagrams of a solar cell having an interdigitated orthogonal back contact metallization pattern;

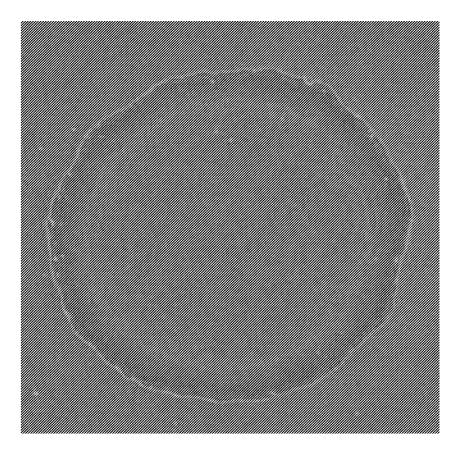

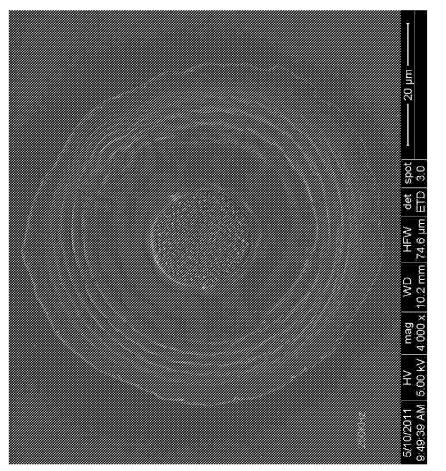

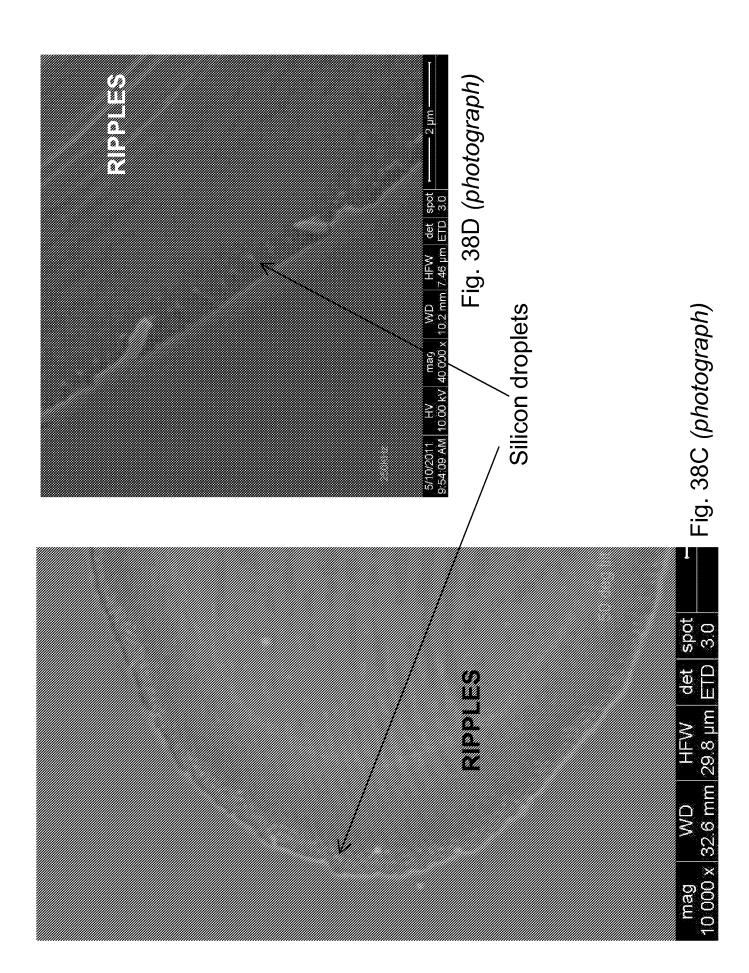

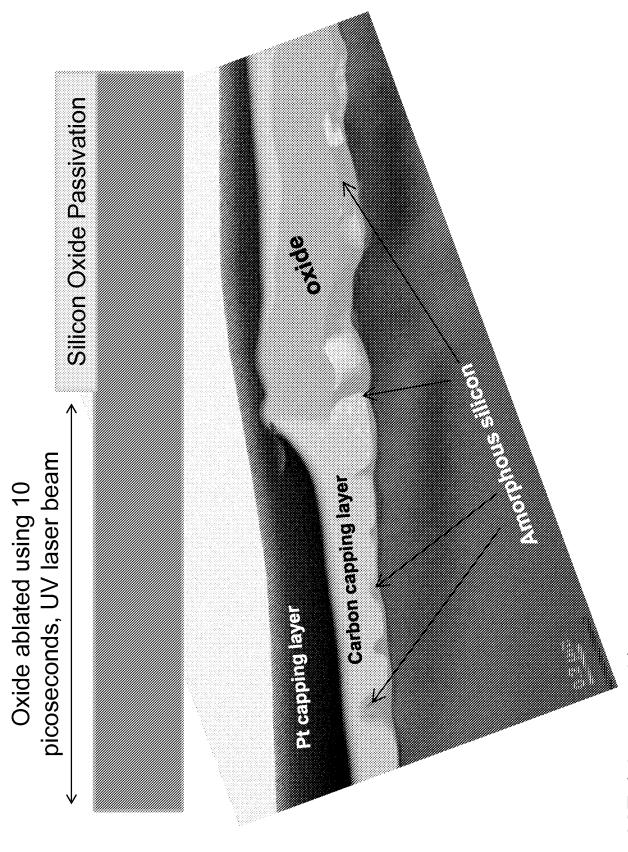

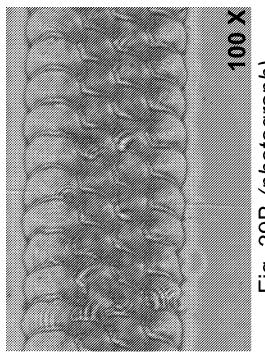

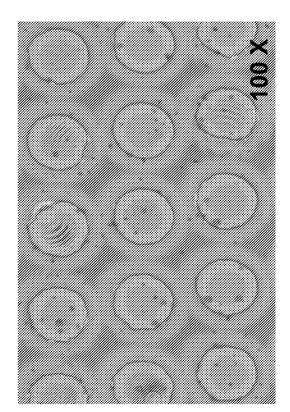

- [0056] Figs. 38A through 38E are scanning electron microscope (SEMS) images highlighting damage to an underlying silicon substrate during oxide ablation;

- [0057] Fig. 39A is a scanning electron microscope (SEMS) image of overlapping ablation spots;

- [0058] Fig. 39B is an expanded view of the image of Fig. 39A;

- [0059] Fig. 39C is a scanning electron microscope (SEMS) image of nonoverlapping ablation spots;

- [0060] Fig. 39D is an expanded view of the image of Fig. 39C;

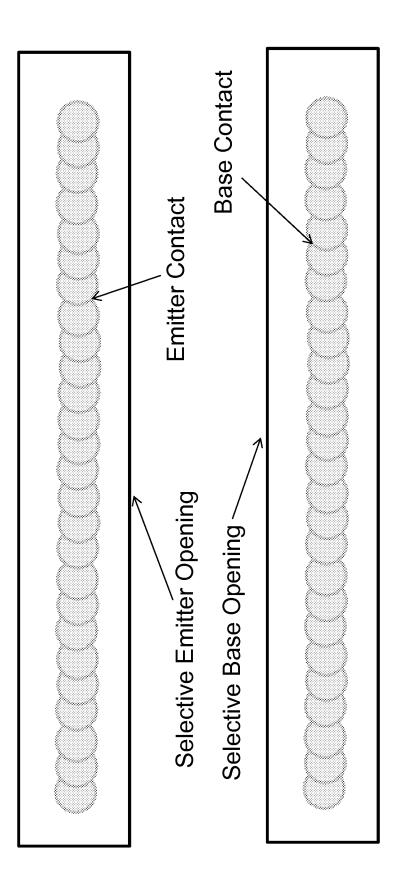

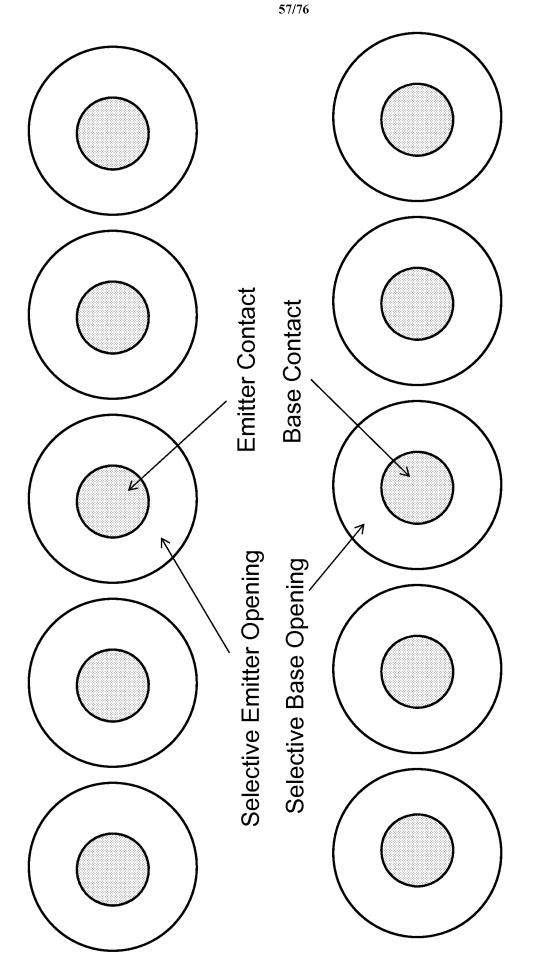

- 20 [0061] Figs. 40A and 40B are schematic diagrams showing two laser patterning opening and contact schemes;

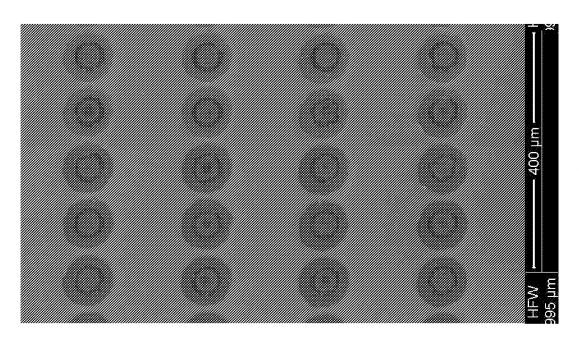

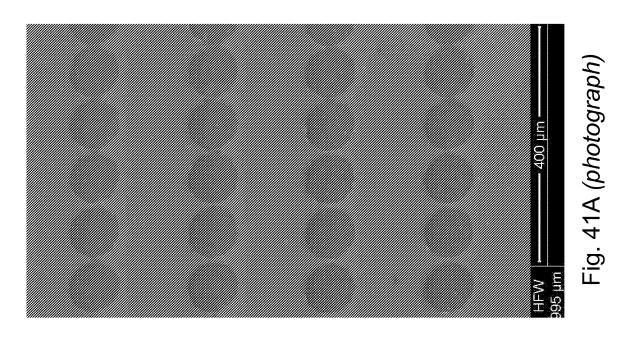

- [0062] Figs. 41A and 41B are scanning electron micrographs of a spot-in-spot laser pattern;

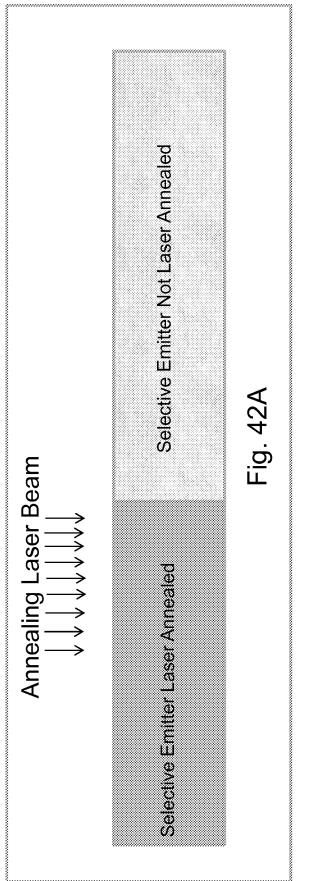

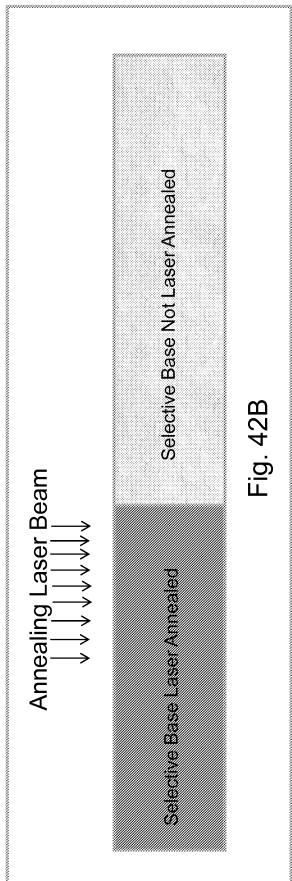

- [0063] Figs. 42A and 42B are schematic diagrams showing laser annealing of damaged silicon in selective emitter and selective base ablations, respectively;

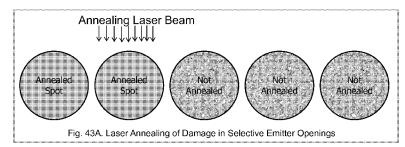

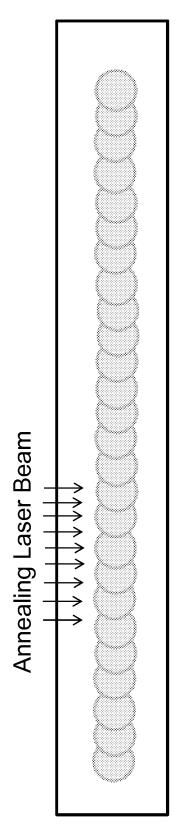

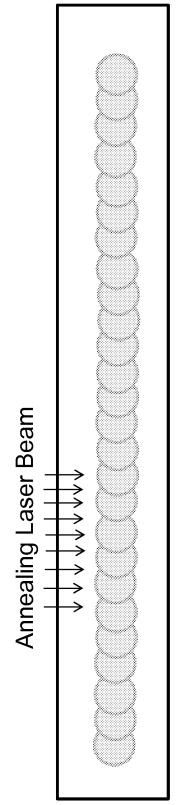

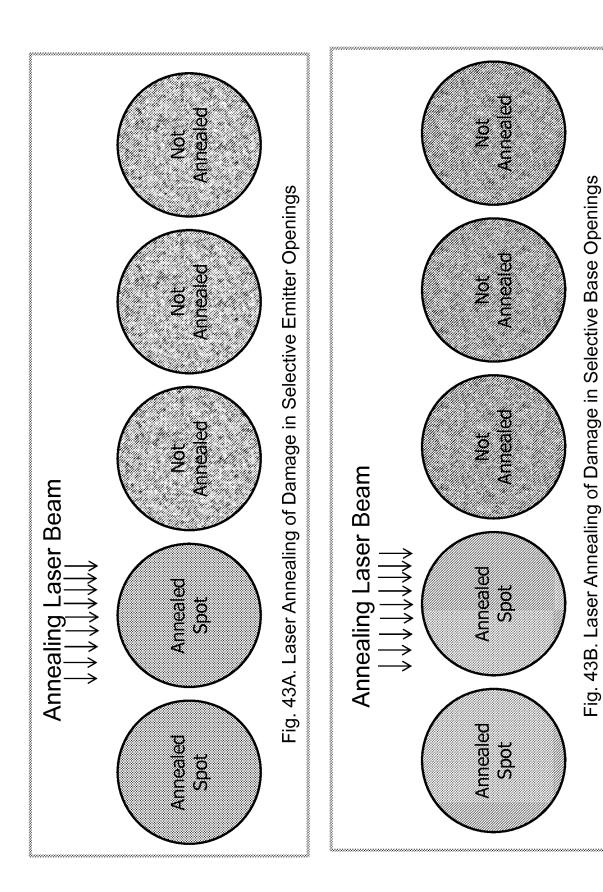

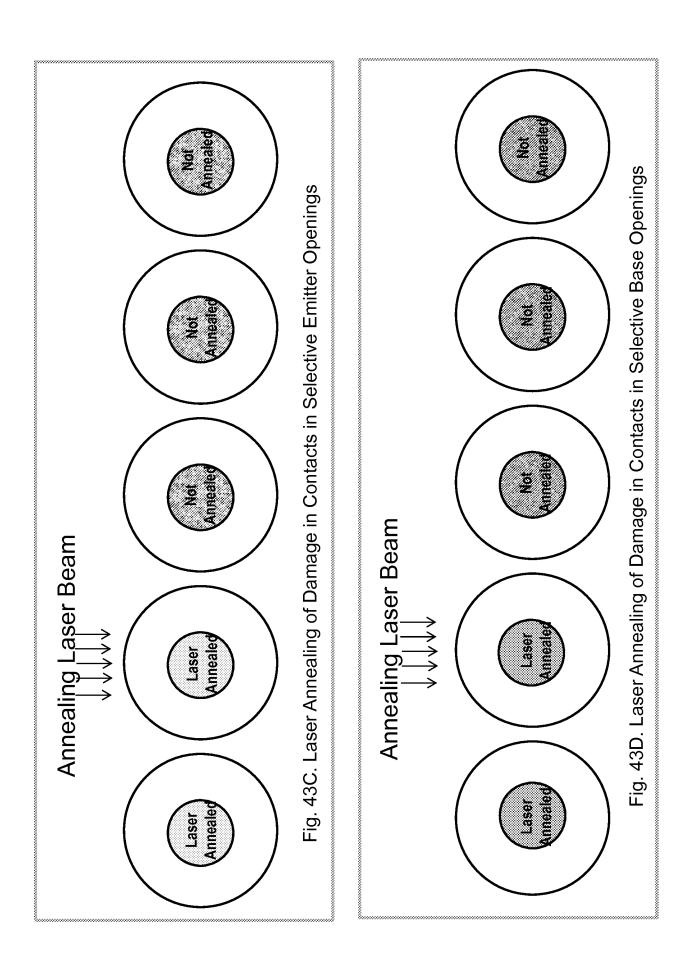

- 25 **[0064]** Figs. 43A and 43B are schematic diagrams showing spot by spot laser annealing of damaged silicon in ablations in a spot-in-spot patterning scheme;

- [0065] Figs. 44A and 44B are optical micrographs showing laser ablation spots before laser anneal and the same ablation spots after annealing;

- [0066] Fig. 45 is a minority carrier lifetime map of a silicon substrate after oxide ablation;

- Fig. 46 is process flow for the formation of a back contact back junction solar cell utilizing laser annealing of laser ablation damage;

[0068] Fig. 47 is an alternative process flow for the formation of a back contact back junction solar cell utilizing laser annealing of laser ablation damage;

- [0069] Fig. 48 is an alternative process flow for the formation of a back contact back junction solar cell utilizing laser annealing;

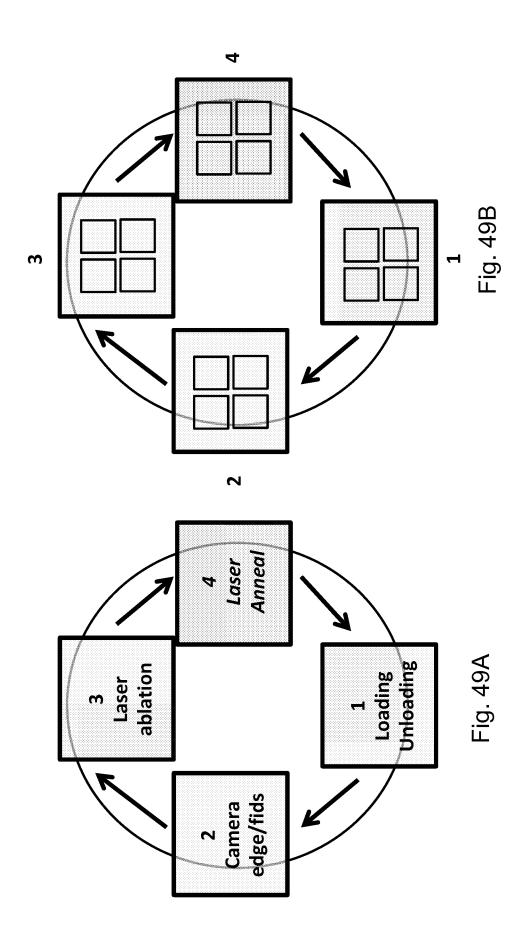

- 5 **[0070]** Figs. 49A and 49B are schematic diagrams of a laser tool configuration a highly cost-effective multi-station platform that provides for high-throughput parallel processing at different stations;

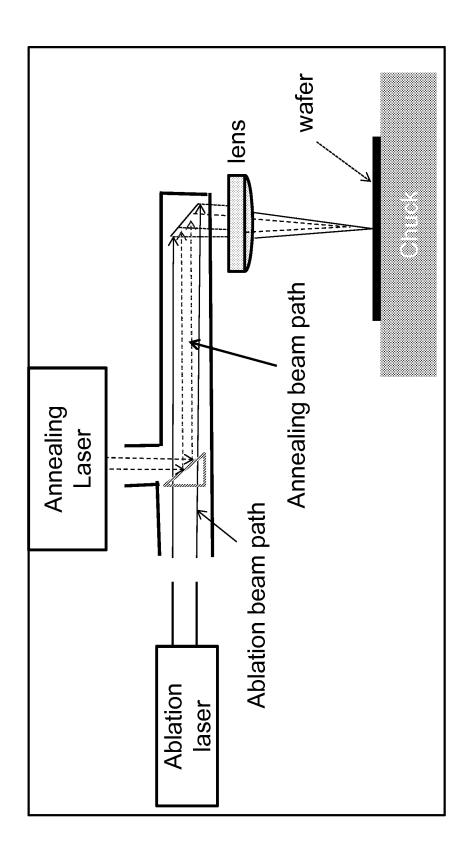

- [0071] Fig. 50 is a schematic diagram of a high throughput laser ablation laser annealing system;

- 10 **[0072]** Fig. 51 is a schematic diagram outlining same station laser ablation and corresponding laser annealing using collinear (coaxial) laser beams;

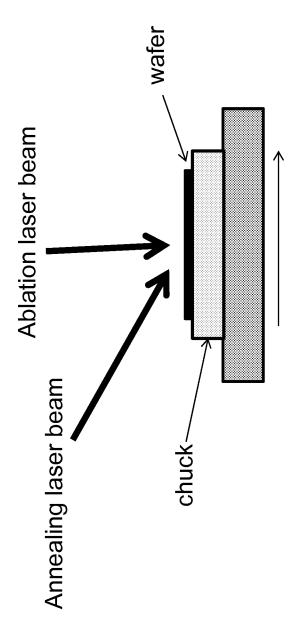

- [0073] Fig. 52 is a schematic diagram showing a same station ablation and annealing using separate laser beams;

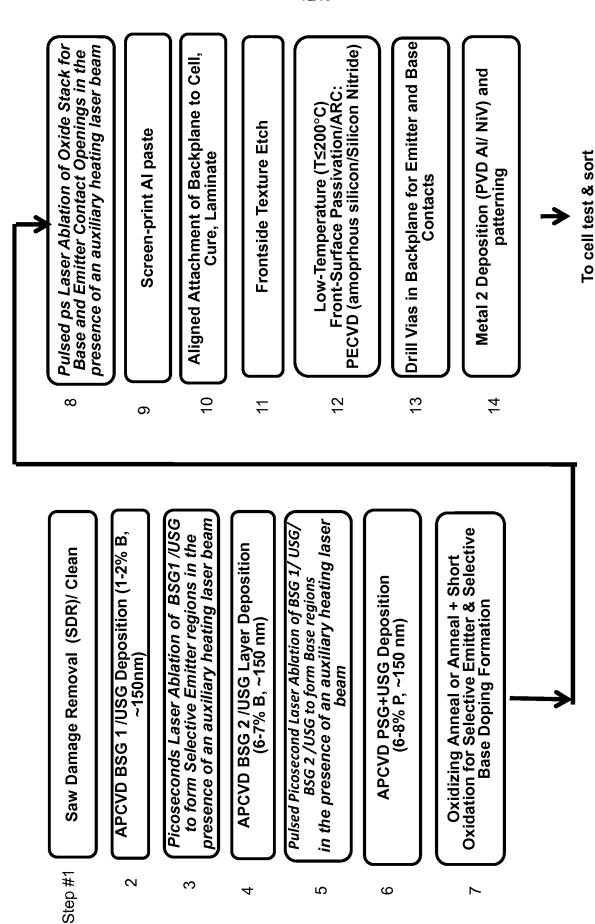

- [0074] Fig. 53 is a process flow for the formation of a back contact back junction solar cell showing oxide ablation carried out in the presence of a heating beam;

- [0075] Fig. 54 is a schematic diagram showing a same station ablation and annealing using wafer heating;

- [0076] Fig. 55 is a process flow for the formation of a back contact back junction solar cell showing oxide ablation carried out in the presence of a heating light;

- 20 **[0077]** Fig. 56 is a process flow for the formation of a back contact back junction solar cell using flash annealing; and

- [0078] Fig. 57 shows representative/idealized profiles of a Gaussian laser beam and a flattop (top-hat) laser beam.

25

30

15

## **DETAILED DESCRIPTION**

[0079] Although the present disclosure is described with reference to specific embodiments, one skilled in the art could apply the principles discussed herein to other areas and/or embodiments without undue experimentation.

[0080] We disclose here laser processing, more specifically pulsed laser processing, schemes that have been developed to address the varying requirements of different processes.

[0081] The disclosed methods may be useful in the area of semiconductor device ablation, particularly crystalline silicon ablation. Typically removal of silicon with a laser involves silicon melting and evaporation that leaves undesirable residual damage in the silicon substrate. This damage causes minority carrier lifetime degradation and increased surface recombination velocity (SRV) that reduces the solar cell efficiency. Hence, wet cleaning of the silicon substrate is typically used to remove this damage layer. We present a scheme to reduce this damage to a level acceptable for high efficiency solar cell manufacturing that does not require post-laser-processing wet cleaning, hence simplifying the process flow and reducing the manufacturing cost.

5

10

15

20

25

30

[0082]The damage remaining in the silicon substrate upon ablating a certain thickness of it using a laser is related to the amount of laser energy absorbed in the substrate that is not used by the ablated material. If it can be managed that most of the laser energy is used in removing the material then the fraction of the incident energy that seeps into the silicon substrate is minimized, thus minimizing the laser-induced substrate damage and SRV degradation. The penetration of laser energy into silicon depends on the laser pulse length (also called pulse width) and wavelength. The infrared (IR) laser beam, wavelength 1.06 microns, has a long penetration depth in silicon, up to about 1000 microns, while a green laser beam, with a wavelength of 532 nm, penetrates only to a depth of approximately 3 to 4 microns. The penetration of UV laser beam, with a wavelength of 355 nm, is even shorter, only about 10 nm. It is clear that using ultra-short pulses of UV or EUV wavelength limits the penetration of the laser energy into silicon. Additionally, shorter laser pulse length results in shorter diffusion of heat into silicon. While a nanoseconds pulse can lead to heat diffusion in silicon to approximately 3 to 4 microns range, the picoseconds pulse reduces it to about 80 to 100 nm, while a femtoseconds pulse is so short that typically there is no heat diffusion into silicon during the laser ablation process. Hence going to shorter pulses with a shorter wavelength lead to diminishing damage to the laser-ablated substrate. For higher production throughput, green or IR wavelengths can be used depending on the extent of laser damage acceptable. Since even under ideal conditions a certain fraction of the energy would still seep into the substrate, this absorption and its undesirable side effects can be further reduced by reducing the laser power. However, this results in a smaller thickness of

silicon being ablated (or a lower silicon ablation rate or lower throughput). It has been found that reducing the pulse energy but causing the silicon removal by increasing the overlap of the laser pulses makes the silicon shallow isolation trench smoother. This is an indication of low silicon surface damage. At very low pulse energies the thickness of silicon removed may be small. The desired depth may then be obtained by using multiple overlapped scans of the pulsed laser beam.

5

10

15

20

25

30

[0083] A pulsed laser beam with pulse length in the picoseconds range and a wavelength of approximately 355 nm or below is suitable for silicon ablation with low damage enabling low surface recombination velocity (SRV) for passivated ablated surfaces. FIG. 1 shows a 2.25 micron deep and nearly 100 micron wide trench made in a silicon substrate using a picoseconds UV laser beam of Gaussian profile ( $M^2 \le 1.3$ ), nearly 110 microns in diameter with 4 microjoule pulse energy, with the laser spots overlapped nearly 15 times. This depth of ablation was obtained using twenty overlapped scans of the laser with each scan removing about 112 nm of silicon. FIG. 2 shows the smooth profile of a 4 micron deep and 110 micron wide trench in silicon obtained using the same picoseconds laser beam with the UV wavelength. The smoothness of the profile should be noted. Such an ablation of silicon is used in all back-contact back-junction solar cells to form regions that isolate base regions from emitter regions. Use of a femtoseconds laser may provide further reduction of laser damage during silicon ablation.

[0084] The embodiments of this disclosure are also applicable to the ablation of amorphous silicon. A similar scheme may be used to ablate a desired thickness of amorphous silicon using a pulsed laser beam with femtoseconds pulse length and in some embodiments a UV or green wavelength. Since ablation of amorphous silicon requires much lower energy than crystalline silicon, such a scheme may effectively be used to selectively ablate amorphous silicon films from the crystalline silicon surface for application to hetero-junction solar cells.

[0085] This disclosure is also applicable to oxide ablation selective to the underlying substrate, which may be crystalline or amorphous silicon. The oxide film is transparent to laser beams of wavelength down to UV. If a nanoseconds pulse length laser is used to remove the overlying oxide, the removal of oxide takes place by heating and melting of silicon underneath. Because of the pressure from the ablated silicon underneath, the overlying oxide is cracked and removed. This however, creates heavy damage in the silicon substrate so that a wet cleaning treatment is typically used to remove this damaged layer for use in high efficiency cells.

[0086] We present here a scheme where the oxide layer is selectively removed from the silicon surface without any appreciable damage to the silicon surface. During the laser ablation, besides heating the material to melt or evaporate it, other effects such as plasma formation take place. Sometimes complex processes can take place at an interface. Using a laser with picoseconds pulse length, the oxide to silicon interface is affected. Using a picoseconds laser with a UV wavelength, the interface effects are enhanced so that separation and delamination of the oxide film takes place from the silicon surface. The silicon surface left behind is virtually free of damage. Picoseconds laser radiation with green or infra-red (IR) wavelength can also be used depending on how much penetration damage of silicon substrate is acceptable. This disclosure will outline the procedure to obtain damage free selective ablation of oxide from the silicon surface.

**FIGS. 3A–3D** disclose the procedure for obtaining damage-free ablation of oxide. **FIG. 3A** shows the variation of laser spot opening in a 1000A PSG (phosphorus-doped oxide)/500A USG (undoped oxide) stack on a 35 micron thick epitaxial silicon film on a template, using a picoseconds UV laser beam. The oxide layers were deposited using APCVD (atmospheric-pressure CVD) technique. For a given thickness of oxide the spot size depends on the laser fluence (J/cm²). The laser fluence is the laser pulse energy divided by the area of the laser beam. In this case, the laser beam was about 100 microns in diameter with a Gaussian profile (M²<1.3). At very low fluence, the spots are irregular and there is irregular delamination of oxide from the silicon surface as shown in **FIG. 3B**, while at very high fluence there is extensive damage of silicon as shown in **FIG. 3D**. The range of fluence shown by line a-a' indicates the optimum range where the damage to the silicon substrate is minimal as seen in **FIG. 3C**.

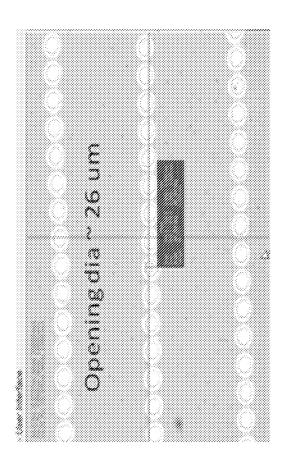

[0088] FIG. 4 shows rows of cell contact openings that are selectively opened in the oxide for application in all back-contact (and back-junction) solar cells. FIG. 5 is a close-up of these contacts. The laser ablation spots can be overlapped in both x and y direction to open up an area of any desired length and width on the wafer as shown in FIGS. 6A and 6B. FIG. 6A shows a 180 micron wide opening made by selectively removing the BSG (boron-doped oxide) for base isolation region using picoseconds UV laser beam with ablation spots overlapping in both x and y-direction. Similarly, FIG. 6B shows a 90 micron wide area opened up in USG (undoped oxide) for forming the base region.

[0089] The selective ablation of oxide from a silicon surface as disclosed here can be used in solar cell making in several ways. In one application, when using *in-situ* emitter for backcontact cells, this process is used to open tracks in an oxide film to expose the underlying emitter. The emitter so exposed may be removed using wet etching. This region is then used for base to emitter isolation and with base formed inside it.

5

10

15

20

25

30

[0090] In another application, this process is used to open regions that are then used for making metal contacts. For front contacted cells, the oxide passivation can be used on the backside of the cells. The scheme described here is then used to open contacts for the metal that is subsequently deposited on these contacts. In this manner, the metal has localized contact that is conducive to high cell efficiency. For back contacted cells, contacts for both base and emitter may be opened using this scheme.

[0091] In a solar cell process flow, a doped oxide may need to be removed without causing any doping of the silicon underneath (i.e., without any appreciable heating of the doped oxide and silicon structure). Since, as described above, the oxide is removed by separation at the oxide/silicon substrate interface when using a picoseconds laser beam, the removal of oxide happens with limited pickup of the dopant from the oxide film being ablated.

[0092] The selective ablation of silicon nitride  $(SiN_x)$  is used for front contacted solar cells. Using laser ablation, the contact area to the emitter surface can be reduced thereby minimizing the area where the SiN passivation is removed. This leads to higher  $V_{OC}$ . Picosecond lasers with either UV or green wavelength are suitable for this application, although nanoseconds UV lasers can also be used.

[0093] Selective metal ablation from the oxide surface has historically been difficult using lasers. This is because at the high pulse energies needed to ablate metal, the energy is high enough to damage the oxide underneath and cause penetration of metal into oxide. In fact, this is the basis for the process of "laser fired contacts" (LFC) used in solar cells.

[0094] We disclose three schemes for selectively removing metal from the oxide (or another dielectric) surface with no metal penetration of oxide (or other dielectrics such as silicon nitride) and breaking or cracking of oxide. In all these schemes, aluminum is the first metal in contact with base and emitter (aluminum being used as the contact and light trapping rear mirror layer).

A laser with picoseconds pulse length is suitable for this application. For high metal removal rate the IR wavelength is quite suitable. According to the first scheme, metal is ablated at a pulse

energy that is lower than the threshold for oxide ablation. If the thickness of metal removed in one scan is lower than the desired thickness, multiple overlapping scans are used to remove the full thickness of metal. Since the pulse energy is below the oxide ablation threshold, a clean removal of metal from the oxide surface is obtained. However, the exact recipe used highly depends on the type of metal in the stack, their thickness and surface roughness, etc.

5

10

15

20

25

30

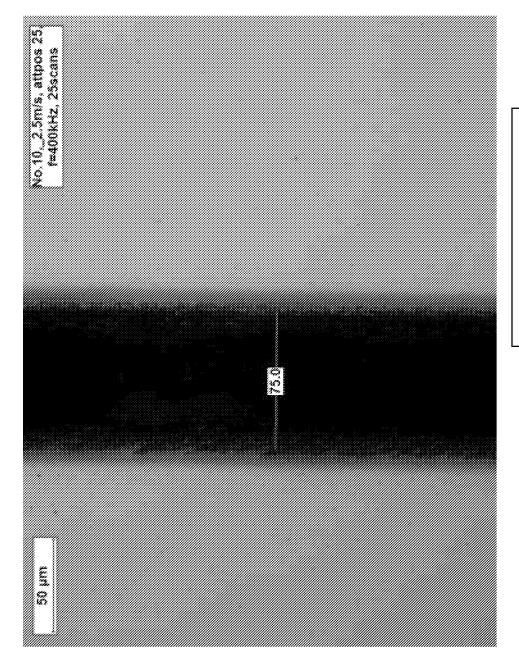

[0095] FIGS. 7A–7C shows the ablation results when patterning a PVD-deposited bi-layer stack of 2400A of NiV on 1200A of Al on oxide. It is desired that the metal be removed completely between the runners without breaking through the oxide layer underneath (to prevent shunts in the cell). FIG. 7A shows the threshold for pulse energy, below which this metal stack can be removed without penetration of oxide. This threshold, besides depending on the metal stack characteristics described above, depends on the laser parameters such as spot overlap obtained using a certain pulse repetition rate of the laser as well as the scan speed. With increasing pulse overlap the threshold pulse energy would decrease, because of the energy accumulation in the metal. FIG. 7B shows that using a pulse energy below the threshold for oxide damage, more than twenty scans provided complete isolation of metal runners as determined by the 100M-ohm resistance between parallel lines. FIG. 7C shows a clean 75 micron trench formed in the 2400A NiV/1200 Al metal stack.

[0096] According to the second, high-throughput scheme higher pulse energies are used, since a substantial part of the incident energy is absorbed as it is being ablated thereby reducing damage to the oxide. This approach makes the laser ablation of metal a very high throughput process. Using this scheme we have ablated 1250A Al/100-250A of NiV, with or without a tin (Sn) overlayer up to a thickness of 2500A successfully using a two step process. In the first step the softer metal is removed using 15 microjoule pulses, followed by 30 microjoule pulses both overlapped fifteen times. For thicker aluminum such as 2000A the second step can be carried out at 50 microjoules with the same number of overlapping of pulses.

[0097] The third scheme of metal ablation is applicable to highly reflective films, for example Al/Ag stack (with Al in contact with the cell and Ag on top of Al), such that most of the incident energy of the picoseconds laser is reflected and ablation is drastically reduced. In that case the surface of the reflective metal (Ag) is first dented using a long pulse length nanoseconds laser, pulse length from 10 to 800 nanoseconds, followed by picoseconds cleanup of the aluminum underneath.

[0098] This disclosure is also applicable to the selective doping of a substrate. For successful doping of silicon using an overlying layer of the dopant-containing material, the pulse energy should be high enough to melt the silicon but not high enough to ablate it or the dopant layer above it. As the silicon melts, the dopant is dissolved into it. Upon recrystallization of this silicon layer, a doped layer is obtained. For this application a nanoseconds pulse length laser with green wavelength is quite suitable because of its limited penetration into silicon.

5

10

15

20

25

30

[0099] The laser processing techniques described above are applicable to planar and 3-D thin-film crystalline silicon substrates. The laser processes described here are suitable for any thickness of the silicon substrate. These include the current standard wafer thickness of ≥150 microns used for crystalline silicon solar cells. However, they become even more advantageous for thin, fragile wafers or substrates as the process in carried out without any contact with the substrate. These include the wafers thinner than 150 micron obtained from monocrystalline CZ ingots or multi-crystalline bricks using advanced wire sawing techniques or by other techniques such as hydrogen implantation followed by annealing to separate the desired thickness of wafer, or thin-film monocrystalline substrates (such as in the thickness range of from a few microns up to 80 microns) obtained using epitaxial deposition of silicon on a sacrificial separation / release layer such as porous silicon and its subsequent lift off.

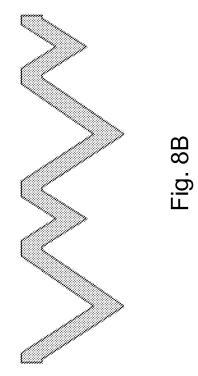

[00100] The laser processing is particularly suited to three dimensional substrates obtained using pre-structuring of reusable templates and silicon micromachining techniques. One such method is described in the '713 Application (published as US2010/0304522). FIGS. 8A through 9B show the 3-D thin film silicon substrates obtained using the technique described in that publication. FIG. 8A shows the top view while FIG. 8B shows the cross-section of the TFSS so obtained. For pyramidal substrates, the tips may be flat or may end in a sharp point. FIGS. 9A and 9B show the TFSS with prism structure obtained using a reusable pre-structured 3D template described in the reference above.

[00101] Although the laser processes and the process flows described here are applicable to any thickness of the silicon substrate (from less than one micron to over 100 microns), we disclose here their application to solar cells made using thin silicon substrates in the thickness range of from less than 1 micron to about 80 microns, including but not limited to those that are obtained using epitaxial silicon on porous silicon (or other sacrificial layer) surface of a reusable template as described in the '713 Application. To facilitate the understanding of our application,

the process flow for obtaining a desired thickness (e.g. from about less than 10 microns up to about 120 microns) of planar monocrystalline TFSSs according to that publication is shown in FIGS. 10A and 10B for planar TFSS that are typically greater than about 50 microns so that they can be handled as self supporting substrates during cell processing, and FIGS. 11A and 11B for planar TFSS that are typically thinner than about 50 microns so that they are not self supporting during cell processing (and hence, are reinforced prior to separation from their host templates). FIGS. 12A–12D show the process flow for obtaining three-dimensional pyramidal silicon substrates. Three-dimensional prism-shaped substrates can be obtained with similar processes, but using a lithography or screen printed pattern that provides for that structure.

5

10

15

20

25

30

[00102] The thin planar substrate obtained using the process flow of FIGS. 10A and 10B may be processed according to the process flow of FIG. 13 to obtain high efficiency front contacted solar cells. It should be noted for self-supporting TFSSs it is advantageous to process the template side of the TFSS first before proceeding to the other side. Since the template side of the TFSS is textured during the removal of the quasi-monocrystalline silicon remaining on the TFSS after its separation from the template it is preferably the frontside or sunnyside of the solar cell. The laser processes of selective ablation of silicon oxide and silicon nitride (SiN) are used to advantage in making this front contacted solar cell.

[00103] FIG. 14 shows the application of various laser processes for making high efficiency front contacted solar cells using planar TFSSs where the TFSS is too thin to be free standing or self supporting during cell processing. It should be noted that in this case the non-template side surface is processed first with the TFSS on the template. Once this processing is complete the TFSS is first attached to a reinforcement plate or sheet (also called a backplane) on the exposed processed side and then separated from the template. After separation of the backplane-attached (or backplane-laminated) thin-film crystalline silicon solar cell, removal of residual porous silicon, texture etch, and SiN passivation/ARC deposition, and forming-gas anneal (FGA) operation processes are carried out on the released face of TFSS (which will end up being the front surface of the solar cell).

[00104] FIG. 15 shows the application of various laser processes for making high efficiency front contacted solar cells using 3-D front TFSS. For this application it is advantageous to have pyramid tips on the template side not be sharp but end in flat ledges.

[00105] The processes described here are further uniquely suited to simplifying the all back-contact cell process flow.

5

10

15

20

25

30

[00106] FIGS. 16A–16D show the laser processes used on the planar epitaxial substrate to make a back-contact/back-junction solar cell where the TFSS is self supporting (i.e., no backplane attachment to the cell). In this application the epitaxial emitter is deposited in-situ during silicon epitaxy following the deposition of the epitaxial silicon base. The ablation of silicon is then used to remove the emitter from the base isolation regions. At the same time four fiducials are etched into oxide to align subsequent ablation to this pattern. Next, a thermal oxide is grown to passivate the silicon surface that will become the back surface of the back-contact back-junction solar cell. The epitaxial silicon film is then disconnected or released from the template (by mechanical release from the porous silicon interface). Next, the residual porous silicon layer is wet etched and the surface is textured (both can be done using an alkaline etch process). This will become the textured front surface or the sunnyside of the solar cell. Now, the thermal oxide is ablated using a picoseconds UV laser to form base openings inside the base isolation region. The base opening is aligned inside the base isolation region (trench) formed by silicon ablation earlier using the fiducials that were etched in silicon earlier as mentioned above. Next a phosphorous containing oxide layer (PSG) is blanket deposited on the surface. Scanning with a nanosecond green or IR laser aligned to base opening using the fiducials in silicon causes the base to be doped. Also, the region that will have the contact openings to emitter is also doped in a similar manner using the aligned scans of nanosecond green or IR laser. Next, contact opening are made to these doped base and emitter areas using a picoseconds UV laser. Again, the alignment of these contact openings is made using fiducials in silicon. Now, a metal stack layer comprising aluminum as its first layer in contact with the cell (e.g., a stack of 1250A Al/ 100-250A NiV/2250 Sn) is deposited using a suitable method such as a PVD (physical vapor deposition) technique. Next, this layer is patterned using a picoseconds IR laser so that the metal runners are separately connected to the base and emitter regions. After an optional forming gas anneal (FGA), the cell is connected to and reinforced with a backplane with either embedded (Al or Cu) high-conductivity interconnects or no embedded interconnects (in the latter, the final cell metallization can be formed by a copper plating process). The cell is now ready for test and use. FIG. 17 shows the laser processes used on the planar epitaxial substrate to make a back-contact solar cell where epitaxial silicon base is not deposited with an emitter layer. Instead, a boron

containing oxide (BSG) layer is deposited and patterned to open the base isolation region. A similar process to that described above is followed except that now the emitter and base are formed simultaneously during a thermal oxidation step according to the process flow outlined in **FIG. 17**.

- 5 **[00107]** FIG. 18 shows a process flow using laser processes on the epitaxial substrate to make a planar back-contact/back-junction solar cell where the TFSS is not self-supporting (hence, a backplane is used). This flow uses the silicon ablation of in-situ doped emitter to form the base isolation region.

- [00108] FIG. 19A–19H show a process flow using laser processes on the epitaxial substrate to make a planar back contact solar cell where the TFSS is not self-supporting. In this flow, instead of an in-situ emitter layer, the BSG deposition and selective laser ablation followed by thermal oxidation (or a thermal anneal or a thermal oxidizing anneal) is used to form the emitter as well as the base isolation region.

10

15

20

25

- [00109] FIG. 20 shows a process flow for making back contacted 3-D solar cells, it is advantageous to have the template side of pyramids end in relatively sharp points. Since the 3-D TFSS can be self-supporting to relatively low thickness (e.g., silicon as thin as about 25 microns), the process flow is similar to that shown in FIG. 16. It should be clear that we again have a choice of using the in-situ emitter followed by laser ablation of silicon, or BSG deposition and selective laser ablation followed by thermal oxidation (or thermal anneal, or thermal oxidizing anneal).

- [00110] For applications in hetero-junction solar cells, a hetero-junction emitter may be formed by a doped amorphous silicon layer in contact with an oppositely doped crystalline silicon base. For interdigitated back contact solar cells we pattern the amorphous silicon layer and the transparent conducting oxide (TCO) using laser ablation that is selective to the crystalline layer. Femtoseconds pulsewidth lasers with either UV or green wavelength are suitable for this application. A process flow is described in **FIG. 21**. Several variations of this process flow are possible.

- [00111] Various embodiments and methods of this disclosure include at least one of the following aspects: the process to obtain silicon ablation of crystalline and amorphous silicon with reduced damage; the process to obtain oxide ablation for both doped and undoped oxides with no or reduced damage to silicon; the process to obtain fully isolated metal patterns on a

dielectric surface for solar cell metallization; the process to selectively dope the emitter and base contact regions; the use of pulsed laser processing on very thin wafers, including planar and 3-D silicon substrate; the use of pulsed laser processing on substrates obtained using epitaxial deposition on a reusable template made using template pre-structuring techniques; the use of various pulsed laser processes in making front contacted homo-junction solar cells; the use of various pulsed laser processes in making all-back contacted homo-junction solar cells; and the use of various pulsed laser processes in making hetero-junction solar cells.

5

10

15

20

25

30

**[00112]** Although the front contact solar cells are described with p-type base and back-contact back-junction solar cells are described with n-type base, the laser processes described here are equally suited to the substrate with opposite doping, i.e., n-type for front contact solar cell with  $P^+$  emitter, and p-type base for back-contact back-junction solar cells with p-type base and  $n^+$  emitter.

[00113] The following description, tables, and figures disclose the application of flat top laser beams to laser processing methods for interdigitated back-contact cells (IBC). The description following is directed towards methods for the formation of back contact solar cells utilizing flat top laser beams as compared to traditional Gaussian laser beams. Further, the implementation of flat top laser beams to the laser processing methods described throughout this application provides substantial reduction in damage to silicon, improvement in solar cell fabrication throughput, and a bigger alignment window for defining patterns (e.g. patterns of emitter and base regions) that are inset inside another pattern.

[00114] FIG. 22A and 22B are schematics showing the profile of a Gaussian beam, FIG. 22A, and a flat top beam, FIG. 22B. The beam intensity of the Gaussian beam has a smooth decrease from a maximum at the beam center to the outside of the beam. In contrast, the intensity is "flat" or uniform for the flat top beam through most of its profile (center to outside).

[00115] As disclosed herein, high-efficiency back-contacted, back-junction cells with interdigitated back contact (IBC) metallization benefits from the use of at least one or several steps of pulsed laser processing. Laser processing may be utilized in several processing throughout the formation of the back contact cell, including: defining emitter and base regions (or base-to-emitter isolation), defining back-surface field (BSF) regions, doping to form back surface fields, opening contacts in the dielectric to base and emitter, and metal patterning. Some of these steps require laser processing of wide areas that are typically produced by overlapping

Gaussian beam laser spots. Overlapping severely reduces cell processing speed and may cause silicon damage, resulting in degradation of cell performance and yield. By replacing smaller diameter Gaussian spots with a relatively wide flat top laser beam, substantial improvement in throughput is obtained. And because the overlapping of spots is dramatically reduced, the semiconductor (e.g., crystalline silicon) substrate damage is reduced significantly. FIGs 23-25 illustrate embodiments of back contact solar cells that may be formed according to the disclosed flat top laser beam processing methods.

5

10

15

25

30

[00116] FIG. 23 is a cross-sectional diagram of a back-contact /back-junction cell with interdigitated back-contact (IBC) metallization formed from an n-type substrate, such as that disclosed herein. As shown in FIG. 23, alternating emitter and base regions are separated by relatively lightly n-doped substrate regions (the n-type base). The rear/backside surface is covered by a surface passivation layer that provides good surface passivation with low back surface recombination velocity, made of, for example: thermal silicon dioxide, deposited silicon dioxide, or silicon oxide/silicon nitride layers which may be deposited using techniques such as PECVD or APCVD (and/or aluminum oxide deposited by atomic layer deposition or ALD). This surface passivation process may then be followed by making openings in this passivation layer which act as 'localized contacts' to the emitter and base regions. Then conductor deposition and patterning (e.g., aluminum as shown in FIG. 23) may be performed to separately connect the emitter and base regions.

[00117] FIG. 24A is a rear/backside view of a back contact solar cell illustrating an 20 interdigitated back contact base and emitter design with the emitter and base regions laid out in alternating parallel rows. This backside may be formed, for example, by starting with a surface that is completely covered by an emitter region, then delineating a base region resulting in the formation of the patterned emitter regions. Then doping base contact regions with phosphorous is carried out and contacts are opened to the base and emitter regions in preparation for metallization.

[00118]FIGs 24B-24F are rear/backside views of a back contact solar cell illustrating the back contact cell after key processing steps, wherein any one step or combination of steps may be performed according to a laser process which may or may not utilize a flat top beam. The various laser patterning steps of this particular exemplary method are outlined in FIGs 24B -24E. Starting with an n-type silicon substrate, a BSG layer is deposited over the whole surface.

Next, the emitter to BSF isolation region is defined using laser ablation of the BSG as shown in **FIG. 24B.** This step, the delineation of base and emitter regions, is referred to herein as the "BSG Opening" step. Alternatively, an in-situ boron doped layer may be deposited during silicon epitaxy and the BSF region defined using laser ablation of silicon.

- 5 [00119] After the emitter to BSF isolation region is defined in the BSG Open step, a USG layer is deposited on the wafer followed by laser ablation of this layer in patterns that are inlaid to the the BSG Open region, as shown in FIG. 24C. This patterning step is referred to herein as the BSF Opening step or base opening step. The BSF openings should be isolated from the edges of the BSG Openings to prevent shunt formation as shunts are deleterious to the solar cell efficiency.

- [00120] Next, a PSG layer is deposited on the wafer and the silicon exposed to PSG in the BSF opening is doped using selective laser scans of this area. The doped BSF regions (base regions) are outlined in FIG. 24D

- [00121] Next, the contacts to base and emitter are made using laser ablation as shown in FIG.

- 24E. It should be noted that the contacts may be point contacts as shown in FIG. 24E or line contacts as shown in FIG. 24F. Also, the number of contacts or the number of lines should be optimized for minimum series resistance of the current conduction path for the solar cell thus the designs and methods of the disclosed subject matter are not limited to the exemplary embodiments shown herein. It is also important that the contact openings are properly aligned inside the particular doped area so that there is no current leakage.

- [00122] As disclosed previously, a picoseconds pulse length laser may be used for oxide ablation processes of BSG open, BSF opening, and contact opening, although a nanoseconds pulse length laser may also be used. Further, although IR wavelength may be used, green or UV or smaller wavelengths are more suitable because of their reduced penetration into silicon.

- 25 [00123] For BSF doping particularly, a nanoseconds pulse length laser may be more suitable because of its penetration into silicon. And although IR wavelength may be used, green wavelength, because of its reduced penetration compared to IR, may be more suitable for the depth of doping typically desired.

- [00124] FIG. 25 is a rear/backside view of the back contact solar cell of FIG. 24A with alternating metal lines contacting the emitter and base regions. Note that the metal lines for the emitter and base regions are separately connected to busbars not shown in FIG. 25 for simplicity

of the figure. This metal pattern may be formed by blanket deposition of a metal followed by laser ablation of the metal to isolate base contacts from emitter contacts. Because relatively thick metal lines are required for good current conduction (usually lines 20 µm thick or thicker), a thinner metal stack such as aluminum/nickel-vanadium/Tin may be first deposited and patterned by lasers, followed by the selective deposition of a thicker metal such as copper using electro or electroless plating. Alternatively, a backplane with relatively thick conductors may be applied and attached to the cell with thin conductor lines. A picoseconds pulse length laser with IR wavelength may be most suitable for ablating the metal stack with good selectivity to the underlying oxide layer.

5

10

15

20

25

30

[00125] The disclosed flat top laser beam processing steps that may be utilized to make this structure possible include, but are not limited to: delineation of emitter and base regions (BSF and emitter to BSF isolation) by laser ablation of an emitter or deposited boron doping dielectric (such as boro-silicate glass BSG deposited by APCVD); delineation of the BSF region by opening the dielectric covering the opening made in the BSG; N+ doping of the base (e.g., with phosphorus); opening of metallization contacts to base and emitter regions; and metal patterning using metal laser ablation to isolate base and emitter contacts. **FIGs 26A – 26C** are diagrams illustrating three ways a flat-top beam profile may be created (diagrams reproduced from F.M. Dickey and S. C. Holswade, "Laser Beam Shaping: Theory and Techniques", Mercel Dekker Inc., NY, which is hereby incorporated by reference in its entirety). **FIG 26A** illustrates one technique for creating a flat top beam profile, the so –called "aperturing of the beam." Using this method, the Gaussian beam is made flatter by expanding it and an aperture is used to select a reasonable flat portion of the beam and to cut-out the gradually decreasing 'sidewall' areas of the beam. Using this method, however, may cause a significant loss of beam power.

[00126] A second example method for creating a flat top beam, as shown **FIG 26B**, uses beam integration wherein multiple-aperture optical elements, such as a micro-lens array, break the beam into many smaller beams and recombine them at a fixed plane. This beam integration method may work very well with beams of high M<sup>2</sup> value.

[00127] A third beam shaping system for creating a flat top beam, as shown **FIG 26C**, uses a diffractive grating or a refractive lens to redistribute the energy and map it to the output plane. Any known method, including the three example techniques disclosed in **FIGs 26A-26C**, may be used obtain the flat top beam profile for applications described herein. The suitability and choice

of a flat top laser beam formation method depends on a variety of factors including the available beam characteristics and the results desired.

[00128] FIG. 27A and 27B are schematics showing the profile of a Gaussian beam and a flat top beam highlighting the ablation threshold. As shown in FIGS 27A and 27B, a flat top laser beam, particularly as compared to a Gaussian beam, can substantially reduce the laser damage during ablation and doping processing. For Gaussian beams there is substantial excessive laser intensity above that required for ablation, particularly in the center of the beam, that can cause damage of silicon (as shown in FIG. 27A). The flat top beam can be configured so the peak intensity is only slightly above that required to ablate the material (the ablation threshold as shown in FIG. 27B) and the damage that may be caused by the high intensity of the Gaussian beam is avoided.

5

10

15

20

25

30

[00129] A flat top beam, whether having a square or rectangular cross section, offers throughput advantages particularly as compared to a Gaussian beam. FIG 28A is diagram showing a Gaussian beam ablated region profile/footprint. The circular shaped spots of a Gaussian beam are required to overlap substantially to the minimize the zigzag outline of the pattern, typically as much as 50% overlap (FIG. 28A). FIG 28B is diagram showing a flat top beam ablate region profile/footprint. Since the square or rectangular flat top beam have flat edges, thus creating a flat outline, the overlap can be significantly reduced (FIG. 28B). FIG 28C is a graph showing the improvement in scan speed as beam overlap is reduced. Note that even for an overlap of 30%, a scan speed increase of 33% may be realized.

[00130] FIG 29A is a diagram illustrating a beam alignment window of a Gaussian beam and FIG 29B is a diagram illustrating a beam alignment window of a flat top beam. As can be seen in FIGs 29A and 29B, yet another advantage of using a flat top beam for making inlaid patterns is the larger alignment window the flap top beam provides. The circular shaped spots obtained from a Gaussian beam create zigzag edges of the ablated regions (FIG. 29A). The alignment margin of M as shown in FIG. 29A is reduced and limited to M-a-b due to the waviness of the zigzag edge profile.

[00131] However, the ablation region edges created using a flat top beam are straight allowing the alignment margin to stay at M. For the back contact back junction solar cells described herein, BSF openings are formed inside the BSG Open regions, and contact openings are formed inside the BSF region. Hence, a larger alignment margin is important as it allows for

smaller BGS Open, BSF, and contact regions. Thus reducing the electrical shading and improving solar cell performance.

5

10

15

[00132] Since the overlap of square or rectangular flat top beam can be reduced in both x and y direction while making a large area ablation or doping, the throughput is significantly enhanced. Also, since the size of the square or rectangular flat top can be increased without causing excessive zigzagging of the perimeter, throughput is further increased. Table 1 shows the reduction in the number of scans needed to open a 150 um wide line, such as used for delineating the base area by ablating the BSG film.

[00133] Table 1 below shows the throughput of Gaussian vs. Flat Top laser beams for creating a 90µm wide base opening. The results of Table 1 are shown graphically in **FIG. 29E.**

| PROCESS                | Width<br>of line<br>(um) | Spot<br>Size<br>(um) | Overlap<br>% | Pitch<br>of<br>scans<br>(um) | Number<br>of scans<br>per line |

|------------------------|--------------------------|----------------------|--------------|------------------------------|--------------------------------|

| BSG Ablation with      |                          |                      |              |                              |                                |

| Gaussian               | 150                      | 30                   | 50           | 15                           | 9                              |

| BSG Ablation with Flat |                          |                      |              |                              |                                |

| Тор                    | 150                      | 30                   | 20           | 24                           | 6                              |

| BSG Ablation with Flat |                          |                      |              |                              |                                |

| Тор                    | 150                      | 60                   | 20           | 48                           | 3                              |

Table 1.

[00134] FIG. 29E shows the throughput advantage of flat top beams (the 60µm flat top beam region profile is depicted in FIG. 29D) as compared to the Gaussian beam (the 30µm flat top beam region profile is depicted in FIG. 29C), for a high productivity laser system that can process four wafers at a time. To further reduce cost, for example, two lasers may be utilized with each laser beam further split into two. However, many variations of this flat top laser beam hardware and fabrication scheme are possible.

[00135] Also, because overlap is significantly reduced in both x and y directions when using a flat top beam, the laser induced damage of silicon is greatly reduced as compared to the Gaussian beam.

5

10

15

20

25

30

[00136] Similar throughput advantages may also result when utilizing a flat top beam for opening the oxide region for BSF, doping the BSF region using the overlying PSG, forming base and metal contact openings if they are line contacts, and the metal ablation isolation lines - all with the concurrent advantage of reduced silicon damage. Additionally, utilizing a flat top beam provides the advantage of increased alignment window for BSF opening inside the BSG opening and contact opening inside the BSF. Flat top laser processing methods may also increase throughput for forming a back surface field. For example, the back surface field may be formed by doping the base region, opened as described, with an n-type dopant such as phosphorous. For this process the base is covered with a phosphorus-doped silicon oxide (PSG) layer and the doping may be performed by irradiating this region with a laser beam. While uniformly doping this region using Gaussian laser beams requires overlapping, overlapping is minimized or may be completely reduced using a flat top beam. And as with the base and emitter region delineation and back surface field delineation described herein, utilizing a flat top laser beam provides a substantial throughput and reduced damage advantage as required overlapping is decreased. It should be noted that for forming a back surface field, the beam need to be flat top beam only in one direction - normal to the scan, whereas it may be Gaussian in the direction of the scan. This type of beam is called a hybrid flat top beam.

[00137] Importantly, for forming isolated base or emitter contacts, although overlap is not an issue, the silicon damage is still reduced using a flat top beam because of the absence, unlike Gaussian, of a high intensity peak in the center of the beam (as shown in FIG 27A and 27B).

[00138] Another aspect of this disclosure relates to the use of laser annealing to improve the conversion efficiency performance of crystalline semiconductor solar cells in general, and crystalline silicon solar cells in particular, by improving the passivation properties of dielectric-coated surfaces, and more specifically silicon nitride (SiN)-coated surfaces. The improved front surface passivation properties are manifested as reduced Front-Surface Recombination Velocity (or reduced FSRV) and increased effective minority carrier lifetime. This technique is especially advantageous for high-efficiency back-junction, back-contacted cells with interdigitated metallization (IBC) where annealing of SiN-coated front surface may also be used to

concurrently result in the annealing of emitter and base metal contacts on the solar cell back surface, thereby, lowering the specific contact resistivity and improving the solar cell fill factor (FF). The laser annealing methods of this disclosure are applicable to crystalline semiconductor solar cells using semiconductor absorber layers over a wide range of thicknesses, i.e., thick wafer-based solar cells such as crystalline silicon wafer solar cells with wafer thicknesses of 10's to 100's of microns. Moreover and more specifically, the non-contact laser annealing process and methods of this disclosure are applicable to extremely thin (e.g., crystalline semiconductor layers from a few microns to ~50 microns thick) crystalline silicon solar cells where unsupported cell mechanical handling can result in cell breakage. It is also an in-line replacement for the batch furnace annealing processes. The laser annealing process and methods can be used as the last step in the cell manufacturing process flow or immediately after deposition of the front-surface passivation and anti-reflection coating (ARC) layer. The processes and methods of this disclosure enable formation of high-quality surface passivation and ARC layers using low-temperature, low-thermal budget deposition processes for passivation & ARC layers such as silicon nitride deposited by low-temperature PECVD.

[00139] The passivation of the surface of phosphorous-rich N<sup>+</sup> emitter with silicon nitride for standard front contact solar cells with p-type silicon bulk (or p-type base), is well known and widely utilized in the solar industry. While the SiN film acts as an antireflection coating to reduce the optical reflection losses and to increase sunlight trapping, it also serves a very important task of passivating the surface of the phosphorous-rich N<sup>+</sup> emitter by the well-known hydrogenation process. The hydrogen released from the hydrogen-containing SiN layer satisfies the open bond on the silicon surface (or silicon dangling bonds causing surface states and traps), thereby reducing the surface recombination velocity or rate of minority carriers by these dangling bond sites. For cells made from multi-crystalline or polycrystalline silicon, this hydrogen provided by the SiN layer further reacts with the impurities and defects in the bulk of the silicon wafer as well as removes the grain boundary trap sites, thereby reducing the overall minority carrier recombination and increasing the effective minority carrier lifetime in the bulk of the material.

[00140] The release of hydrogen and hence the surface and bulk passivation of silicon is typically obtained during the so-called "metal firing" process in the standard front-junction/front-contact solar cell manufacturing process flow, currently widely used in the solar cell

manufacturing industry. The screen-printed metal firing process consists of multiple-step heating of the solar cell using a carefully designed temperature and time sequence with a final dwell at about 850-900°C before a desired cooling sequence. This firing cycle is optimized after careful experimentation. Since hydrogen is a small atom it can diffuse out of the wafer if the wafer temperature is too high or the annealing times are too long. On the other hand, the hydrogen passivation may be unsatisfactory if the temperature is too low or annealing times are too short. Hence, the hydrogen-passivation phenomenon has been a subject of intense investigation and research in the solar cell industry and is considered not just science but also an art by many (since there are still many areas yet to be fully understood). It is clear that a process that can provide a high degree of control is thus desired.

5

10

15

20

25

30

[00141] For the standard mainstream front-contact solar cell with p-type silicon bulk (or p-type boron-doped base) and n<sup>+</sup> phosphorus-doped emitter, the front contact surface is contacted by silver while the back surface is contacted by aluminum—which may be screen printed as a blanket layer or make selective contacts through openings made in the backside dielectric surface. To obtain low resistance contacts, the intermixing of silver with silicon in the front and aluminum in the back is promoted during the metal firing process that has been described above. Based on the description of the metal firing process above, the practice of obtaining low resistance contacts and hence high FF in the solar cell is complicated. Again, a process that can provide a high degree of control is desired.

[00142] Additionally, the all back-contact, back-junction solar cells that use the same metal, aluminum, in contact with both n<sup>+</sup> and p<sup>+</sup> contacts on the back side cannot be heated too high as the doping of n<sup>+</sup> contact by aluminum, a p-type dopant, will increase the contact resistance, thereby lowering the fill factor of the cell. Moreover, overheating of aluminum much above 450°C can result in degradation of optical reflectance of aluminum (and thus increased optical losses of the infrared photons in the cell). A controlled low-temperature heating, preferably in the range of 200- 450°C, of the contacts where aluminum makes intimate contact with silicon by reducing and absorbing the oxide at the silicon surface, is highly desirable.

[00143] We disclose here a process where the front surface or sunnyside of the solar cell is substantially uniformly or in selected areas irradiated with the laser beam, selectively heating the semiconductor (e.g., silicon) such that hydrogen atoms are released from SiN thereby effectively passivating the silicon surface, reducing the surface state density, reducing the front-surface

recombination velocity (FSRV), and increasing the effective minority carrier lifetime of the solar cell. The processes and methods of this disclosure may also reduce the bulk trap density and enhance the bulk minority carrier lifetime. One embodiment of the disclosed method is based on using a pulsed laser source with a wavelength smaller than that of the semiconductor (e.g., silicon) bandgap. In this embodiment (for instance, using a pulsed green or UV laser source for crystalline silicon surface annealing), the front-surface is selectively heated using pulsed laser source irradiation, while the backside of the cell remains substantially cooler than the frontside of the cell. Another embodiment of the disclosed method is based on using a pulsed laser source with a wavelength near to or larger than that of the semiconductor bandgap. In this embodiment (for instance, using a pulsed IR laser source for crystalline silicon surface annealing) while the front-surface is heated using pulsed laser source irradiation, the backside of the cell is also heated and annealed. Using this alternative embodiment, at the same time the laser beam penetrates to the back of the solar cell heating the Al/silicon contacts to decrease the contact resistance and to improve the overall cell fill factor and efficiency. The laser annealing process and methods of this disclosure may be performed at the end of the solar cell fabrication process flow or immediately after formation of the passivation/ARC layer and before the cells are tested and sorted for module packaging. Alternatively, the laser annealing process and methods of this disclosure may be performed after assembling and packaging the cells in a PV module and through the front glass cover of the module assembly. In this case wavelengths need to be used that can go through the glass, such as infrared.

5

10

15

20

25

30

[00144] It is important that the laser anneal process should be optimized (including the laser source wavelength, pulse width, power, etc.) such that the passivation layer (e.g., the PECVD SiN layer) is not degraded during this process so that the sunlight can pass through this antireflection coating without significant optical absorption losses. Also, the surface texture should not be affected so that the light trapping is not reduced. It is clear that the type of the pulsed laser source and the laser process parameters should be carefully chosen to meet all these requirements.

[00145] The laser pulse length should be long enough so that there is no non-linear optical interaction with the passivation/ARC layer (e.g., SiN layer) so that the passivation/ARC layer) is unaffected. Although, lasers with pulse length from 1 nanosecond to microseconds or continuous wave can be used for this application, the choice depends on the depth to which the heat

penetration is desired. Using shorter pulse length the heat is limited to shallow depths. Wavelength also should be chosen based upon the depth of semiconductor (e.g., crystalline silicon) that is required to be heated. For applications to single crystal solar cells where only front surface passivation is required to be improved, green wavelength may be more suitable. For applications where improved bulk silicon passivation is required and/or back contact annealing is desired, IR wavelength may be more suited. It should be clear that based on the desired application a range of laser pulse length and wavelengths can be used.

5

10

15

20

25

30

[00146] Processes for back contacted cells with interdigitated metallization, called NBLAC cells, have been described in related applications (see, e.g., U.S. Patent Application Serial No. 13/057,104).

[00147] FIG. 30 outlines one of the embodiments of the NBLAC process flow, while FIG. 31 is the schematic of the cross section of the cell (the backplane is not shown for clarity). The low-temperature front-surface passivation/ARC: PECVD (silicon nitride) + laser anneal process step in FIG. 30 involves the deposition of SiN at lower temperatures than is used in the industry (<350C). The surface is then subjected to pulsed laser irradiation causing preferential silicon frontside annealing that results in improved passivation of the silicon surface with hydrogen from the SiN. In particular, the laser annealing processes and methods of this invention enable formation of high-quality passivation and ARC layers (like single layer SiN and bilayer SiN with amorphous silicon) deposited at low temperature as low as 90°C, and more typically in the deposition temperature range of 90°C to 250°C.

[00148] In some embodiments, the SiN being annealed may contain a desired amount of phosphorus dopant. In this case, the annealing step also causes silicon doping with phosphorus. This process is discussed in connection with **FIG. 36** below.

[00149] Besides SiN, silicon oxynitride (Si<sub>x</sub>O<sub>y</sub>N<sub>z</sub>), or silicon carbide (Si<sub>x</sub>C<sub>y</sub>) single layers or a bilayer stack with SiN on amorphous silicon ( $\alpha$ -Si), a bilayer stack with SiN on silicon oxide (SiO<sub>2</sub>), or a bilayer stack with SiN on silicon oxynitride, can also be used for silicon surface passivation. For example, it is known that an amorphous silicon layer can passivate the silicon surface quite well. However, for the current industrial process, significant surface cleaning of silicon and process optimization of the  $\alpha$ -Si deposition process is required. Laser annealing of  $\alpha$ -Si films covered with hydrogenated SiN can activate the hydrogen in SiN and lead to dramatic

enhancement of passivation, as measured by substantially increased effective minority carrier lifetime and substantially reduced front-surface recombination velocity.

[00150] The PVD Al/NiV/Sn contact & backside reinforcement BSR step and the pulsed picosecond laser ablation of Al for interdigitated cell base & emitter Al lines step in FIG. 30 form the metal contacts to the base and emitter on the back surface of the solar cell. These contacts are shown in the cross section in FIG. 31. It should clear that the laser beam that penetrates to the back of the silicon film will concurrently anneal the back contacts, resulting in reduced contact resistance and increased fill factor of the solar cell.

5

10

15

20

25

30