(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6546387号

(P6546387)

(45) 発行日 令和1年7月17日(2019.7.17)

(24) 登録日 令和1年6月28日(2019.6.28)

(51) Int.Cl.

F 1

|             |              |                  |      |       |   |

|-------------|--------------|------------------|------|-------|---|

| <b>H05B</b> | <b>33/26</b> | <b>(2006.01)</b> | H05B | 33/26 | Z |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | H05B | 33/14 | A |

| <b>H05B</b> | <b>33/12</b> | <b>(2006.01)</b> | H05B | 33/12 | B |

| <b>H05B</b> | <b>33/22</b> | <b>(2006.01)</b> | H05B | 33/22 | Z |

| <b>H05B</b> | <b>33/06</b> | <b>(2006.01)</b> | H05B | 33/22 | C |

請求項の数 14 (全 19 頁) 最終頁に続く

(21) 出願番号 特願2014-219280 (P2014-219280)

(22) 出願日 平成26年10月28日 (2014.10.28)

(65) 公開番号 特開2016-85913 (P2016-85913A)

(43) 公開日 平成28年5月19日 (2016.5.19)

審査請求日 平成29年10月20日 (2017.10.20)

(73) 特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 110000154

特許業務法人はるか国際特許事務所

(72) 発明者 佐藤 敏浩

東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

(72) 発明者 車司 雅和

東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

審査官 横川 美穂

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の画素と前記第1の画素と隣接する第2の画素とを有する表示装置であって、

基材と、

前記第1の画素と前記第2の画素との境界に位置し、前記基材に形成されたバンクと、

前記第1の画素と前記第2の画素と前記バンクとに跨って配置された発光素子層と、

前記発光素子層の前記基材の側に、前記第1の画素と前記第2の画素との各々に独立して形成された第1の電極と、

前記発光素子層の前記第1の電極とは反対側に、記第1の画素と前記第2の画素とに跨って形成された第2の電極と、

平面的に見て前記バンクと重畳する領域に、前記発光素子層に接して形成された第3の電極と、

を有し、

前記第2の電極は、前記バンクと重畳する前記領域にスリットを有し、

前記第3の電極は、前記スリットに、且つ前記第2の電極と同層に位置していることを特徴とする表示装置。

## 【請求項 2】

請求項1に記載の表示装置において、

前記第2の電極と前記第3の電極とには、異なる電位が印加され、

前記第1の電極と前記第3の電極との間の電位差は、前記第1の電極と前記第2の電極

10

20

との間の電位差よりも大きいことを特徴とする表示装置。

**【請求項 3】**

請求項1に記載の表示装置において、

前記第1の画素は、第3の画素と前記第2の画素とは異なる方向で隣接し、

前記第3の電極は、前記第1の画素と前記第2の画素との前記境界に沿って延在する延在部と、前記延在部から突き出た突起部とを有し、

前記突起部は、前記第1の画素と前記第3の画素との境界の少なくとも一部に位置していることを特徴とする表示装置。

**【請求項 4】**

第1の画素と前記第1の画素と隣接する第2の画素とを有する表示装置であつて、

10

基材と、

前記第1の画素と前記第2の画素との境界に位置し、前記基材に形成されたバンクと、

前記第1の画素と前記第2の画素と前記バンクとに跨って配置された発光素子層と、

前記発光素子層の前記基材の側に、前記第1の画素と前記第2の画素との各々に独立して形成された第1の電極と、

前記発光素子層の前記第1の電極とは反対側に、記第1の画素と前記第2の画素とに跨って形成された第2の電極と、

平面的に見て前記バンクと重畳する領域に、前記発光素子層に接して形成された第3の電極と、

を有し、

20

前記第3の電極は、前記発光素子層の前記基材とは反対側に位置し、且つ前記バンクと重畳する前記領域で絶縁膜に覆われ、

前記第2の電極は、前記バンクと重畳する前記領域で、前記絶縁膜を介して、前記第3の電極を覆っていることを特徴とする表示装置。

**【請求項 5】**

第1の画素と前記第1の画素と隣接する第2の画素とを有する表示装置であつて、

基材と、

前記第1の画素と前記第2の画素との境界に位置し、前記基材に形成されたバンクと、

前記第1の画素と前記第2の画素と前記バンクとに跨って配置された発光素子層と、

前記発光素子層の前記基材の側に、前記第1の画素と前記第2の画素との各々に独立して形成された第1の電極と、

30

前記発光素子層の前記第1の電極とは反対側に、記第1の画素と前記第2の画素とに跨って形成された第2の電極と、

平面的に見て前記バンクと重畳する領域に、前記発光素子層に接して形成された第3の電極と、

を有し、

前記バンクの上面には凹部が形成され、

前記第3の電極は、前記発光素子層と前記バンクとの間に位置し、且つ前記凹部を充填することを特徴とする表示装置。

**【請求項 6】**

40

請求項5に記載の表示装置において、

前記発光素子層は、少なくとも発光層と正孔輸送層とを有し、

前記第3の電極は、正孔輸送層と接していることを特徴とする表示装置。

**【請求項 7】**

請求項5に記載の表示装置において、

前記発光素子層は、少なくとも発光層と正孔注入層とを有し、

前記第3の電極は、正孔注入層と接していることを特徴とする表示装置。

**【請求項 8】**

画像表示領域に画素となる発光領域が複数配列された表示装置であつて、

前記画素の境界に沿って基材上に形成されたバンクと、

50

前記バンクが形成された前記基材上に、少なくとも前記発光領域に形成されキャリアを注入されて発光する発光層とキャリア移動性を有し前記画像表示領域に亘って形成された補助層とを含む複数層が積層されて形成された発光素子層と、

前記発光素子層の下に前記画素ごとに設けられた画素電極と、

前記発光素子層の上に配置され前記画素電極と共に前記発光素子層に電圧を印加する対向電極と、

前記画素間の境界領域にて前記発光素子層の上に配置され、前記発光素子層に電気的に接続された境界電極と、

を有し、

前記境界電極は、前記発光素子層の前記境界領域における前記キャリアを引き寄せる電位を印加されて当該キャリアを吸収すること、

を特徴とする表示装置。

#### 【請求項 9】

画像表示領域に画素となる発光領域が複数配列された表示装置であって、

前記画素の境界に沿って基材上に形成されたバンクと、

前記バンクの上に置かれた境界電極と、

前記バンク及び前記境界電極が形成された前記基材上に、少なくとも前記発光領域に形成されキャリアを注入されて発光する発光層とキャリア移動性を有し前記画像表示領域に亘って形成された補助層とを含む複数層が積層されて形成された発光素子層と、

前記発光素子層の下に前記画素ごとに設けられた画素電極と、

前記発光素子層の上に配置され前記画素電極と共に前記発光素子層に電圧を印加する対向電極と、

を有し、

前記バンクはその上面に凹部を形成され、

前記境界電極は、前記凹部を充填し、且つ前記発光素子層に電気的に接続され、前記発光素子層の前記境界領域における前記キャリアを引き寄せる電位を印加されて当該キャリアを吸収すること、

を特徴とする表示装置。

#### 【請求項 10】

請求項8に記載の表示装置において、

前記境界電極は、前記対向電極と同層で形成されること、を特徴とする表示装置。

#### 【請求項 11】

請求項8に記載の表示装置において、

前記対向電極は前記画像表示領域に亘り形成された透明導電材からなり、前記各画素に共通の基準電位を印加し、

前記画素電極は前記各画素の映像信号に応じた量のキャリアを前記発光素子層へ供給し、

前記境界電極は、前記対向電極の下に形成された不透明導電材からなること、

を特徴とする表示装置。

#### 【請求項 12】

請求項9に記載の表示装置において、

前記対向電極は前記各画素に共通の基準電位を印加し、

前記画素電極は前記各画素の映像信号に応じた量のキャリアを前記発光素子層へ供給し、

前記発光素子層は、前記画素電極から供給される前記キャリアについてのキャリア輸送層又はキャリア注入層を前記補助層として有し、当該補助層の上に前記発光層が積層されること、

を特徴とする表示装置。

#### 【請求項 13】

請求項8から請求項12のいずれか1つに記載の表示装置において、

10

20

30

40

50

前記対向電極は前記各画素に共通の基準電位を印加し、

前記画素電極は前記各画素の映像信号に応じた量の前記キャリアを前記発光素子層へ供給し、

前記境界電極は、前記画素電極との電位差が前記画素電極と前記基準電位との電位差より大きくなる電位を印加されること、

を特徴とする表示装置。

**【請求項 14】**

請求項8から請求項12のいずれか1つに記載の表示装置において、

前記画像表示領域は発光色の異なる複数種類の前記画素を含み、

前記境界電極は、前記発光色が異なる隣接した各画素対において当該画素間の境界の少なくとも一部に沿って配置されていること、

を特徴とする表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は電圧印加により発光する自発光素子を用いた表示装置に関する。

**【背景技術】**

**【0002】**

表示装置として、有機エレクトロルミネッセンス(electroluminescence: E L)素子などの自発光素子を用いたものの開発が進められている。有機エレクトロルミネッセンス素子は一般にO L E D(organic light emitting diode)と称され、発光ダイオードの一種である。O L E Dは有機化合物からなる発光層にキャリア(電子や正孔)が注入され発光する。O L E Dは電圧の印加時に発光層に効率的にキャリアが注入されるように、電極と発光層との間などに、キャリア移動性を有した補助的な層を設ける構造が一般的となっている。

**【0003】**

例えば、補助的な層として、アノードと発光層(emitting layer: E M L)との間に、正孔輸送層(hole transport layer: H T L)や正孔注入層(hole injection layer: H I L)が設けられる。また、カソードと発光層との間には、電子輸送層(electron transport layer: E T L)や電子注入層(electron injection layer: E I L)が設けられる。これら補助層は例えば蒸着法などにより、複数の画素が配列された画像表示領域全体に亘って、即ち複数の画素に跨って連続して形成される。

**【先行技術文献】**

**【特許文献】**

**【0004】**

【特許文献1】特開2012-155953号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

上述したO L E DにおけるH T L, H I Lのようなキャリア移動性を有した層が画像表示領域に亘って連続する共通層として形成される発光素子を用いた表示装置は、当該共通層を通して隣接する画素間でのキャリアのリーク、即ち隣接画素へのリーク電流が発生し得る。隣接画素へのリーク電流は当該隣接画素の意図しない発光を招くという問題があった。具体的には、リーク電流によって画像の解像度の劣化が生じる。また、発光色が異なる画素間におけるリーク電流では、色再現性(色純度)の低下が生じる。特に、高精細化による画素サイズの縮小に伴い隣接画素の開口部(又は発光領域)が接近すると、当該問題がより顕著となる。

**【0006】**

本発明は上記問題点を解決するためになされたものであり、隣接する画素の自発光素子へのリーク電流が抑制され、隣接画素の意図しない発光が防止される表示装置を提供する

ことを目的とする。

【課題を解決するための手段】

【0007】

(1) 本発明に係る表示装置は、第1の画素と前記第1の画素と隣接する第2の画素とを有する表示装置であって、基材と、前記第1の画素と前記第2の画素との境界に位置し、前記基材に形成されたバンクと、前記第1の画素と前記第2の画素と前記バンクとに跨って配置された発光素子層と、前記発光素子層の前記基材の側に、前記第1の画素と前記第2の画素との各々に独立して形成された第1の電極と、前記発光素子層の前記第1の電極とは反対側に、記第1の画素と前記第2の画素とに跨って形成された第2の電極と、平面的に見て前記バンクと重畠する領域に、前記発光素子層に接して形成された第3の電極と、を有する。10

【0008】

(2) 他の本発明に係る表示装置は、画像表示領域に画素となる発光領域が複数配列された表示装置であって、前記画素の境界に沿って基板上に形成されたバンクと、前記バンクが形成された前記基板上に、少なくとも前記発光領域に形成されキャリアを注入されて発光する発光層とキャリア移動性を有し前記画像表示領域に亘って形成された補助層とを含む複数層が積層されて形成された発光素子層と、前記発光素子層の下に前記画素ごとに設けられた画素電極と、前記発光素子層の上に配置され前記画素電極と共に前記発光素子層に電圧を印加する対向電極と、前記画素間の境界領域にて前記発光素子層の上に配置され、前記発光素子層に電気的に接続された境界電極と、を有し、前記境界電極は、前記発光素子層の前記境界領域における前記キャリアを引き寄せる電位を印加されて当該キャリアを吸収する。20

【0009】

(3) さらに他の本発明に係る表示装置は、画像表示領域に画素となる発光領域が複数配列された表示装置であって、前記画素の境界に沿って基板上に形成されたバンクと、前記バンクの上に置かれた境界電極と、前記バンク及び前記境界電極が形成された前記基板上に、少なくとも前記発光領域に形成されキャリアを注入されて発光する発光層とキャリア移動性を有し前記画像表示領域に亘って形成された補助層とを含む複数層が積層されて形成された発光素子層と、前記発光素子層の下に前記画素ごとに設けられた画素電極と、前記発光素子層の上に配置され前記画素電極と共に前記発光素子層に電圧を印加する対向電極と、を有し、前記境界電極は、前記発光素子層に電気的に接続され、前記発光素子層の前記境界領域における前記キャリアを引き寄せる電位を印加されて当該キャリアを吸収する。30

【図面の簡単な説明】

【0010】

【図1】本発明の実施形態に係る有機EL表示装置の概略の構成を示す模式図である。

【図2】本発明の実施形態に係る有機EL表示装置の表示パネルの模式的な平面図である。

【図3】本発明の第1の実施形態に係る有機EL表示装置の表示領域の模式的な部分平面図である。40

【図4】本発明の第1の実施形態に係る有機EL表示装置の表示領域における上部電極及び境界電極のレイアウトの一例を示す模式的な平面図である。

【図5】本発明の第1の実施形態に係る表示パネルの図3に示すV-V線に沿った位置での模式的な垂直断面図である。

【図6】本発明の第1の実施形態の変形例に係る有機EL表示装置の表示領域の模式的な部分平面図である。

【図7】本発明の第2の実施形態に係る有機EL表示装置の表示領域の模式的な部分平面図である。

【図8】本発明の第2の実施形態に係る表示パネルの図7に示すVIII-VIII線に沿った位置での模式的な垂直断面図である。50

【図9】本発明の第3の実施形態に係る表示パネルの図7に示すVIII-VIII線に沿った位置での模式的な垂直断面図である。

【図10】本発明の第3の実施形態に係る表示パネルの製造工程の概略のフロー図である。

【図11】本発明の第3の実施形態の変形例に係る表示パネルの図7に示すVII-VII線に沿った位置での模式的な垂直断面図である。

#### 【発明を実施するための形態】

##### 【0011】

以下、本発明の実施の形態（以下実施形態という）について、図面に基づいて説明する。

10

##### 【0012】

なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更が容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。

##### 【0013】

以下に説明する各実施形態の表示装置は有機EL表示装置である。有機EL表示装置は、アクティブマトリックス型表示装置であり、テレビ、パソコン、携帯端末、携帯電話等に搭載される。

20

##### 【0014】

表示装置の画像表示領域には、画像を構成する複数の画素が2次元配列される。ここで、画像に対応する2次元の直交座標系の1つの座標軸に沿った方向を行方向、もう1つの座標軸に沿った方向を列方向とする。以降の説明では、行方向、列方向は基本的には画像の水平方向、垂直方向とするが、これは便宜的な定義である。例えば、同一の画像表示領域にて画像の縦横を切り換えて表示することができる表示装置では、画像表示領域の行方向、列方向はそれぞれ画像の垂直方向、水平方向となる場合がある。また、表示装置の構造自体も、以下に説明するものに対し行方向と列方向とを入れ替えたものとすることができる。

30

##### 【0015】

また、以下の実施形態では、画像表示領域には発光色が互いに異なる複数種類の画素（サブピクセル）が配列されカラー画像を表示可能な表示装置を説明する。なお、カラー画像における画素は、表示装置における複数種類のサブピクセルからなる一組のサブピクセルに対応するが、表示装置ではサブピクセルが構成上の単位であり、例えば、サブピクセルごとにOLEDや画素回路が形成される。そこで以下の説明では、基本的にサブピクセルを画素と扱う。

##### 【0016】

#### [第1の実施形態]

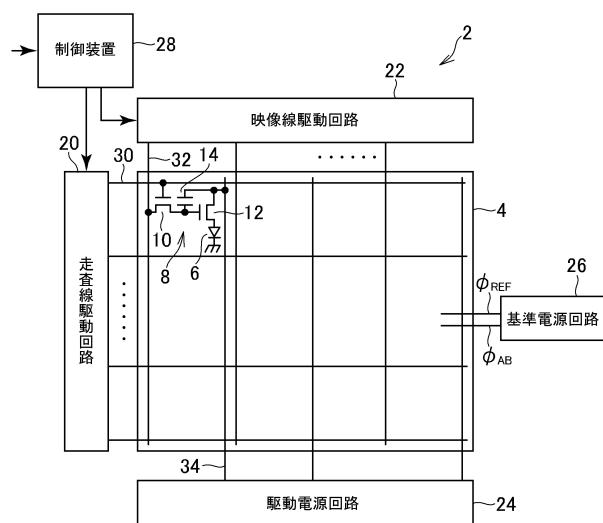

図1は実施形態に係る有機EL表示装置2の概略の構成を示す模式図である。有機EL表示装置2は、画像を表示する画素アレイ部4と、当該画素アレイ部を駆動する駆動部とを備える。有機EL表示装置2はガラス基板や可撓性を有した樹脂フィルムなどからなる基材の上に薄膜トランジスタ（thin film transistor：TFT）やOLEDなどの積層構造が形成されている。

40

##### 【0017】

画素アレイ部4には画素に対応してOLED6及び画素回路8がマトリクス状に配置される。画素回路8は複数のTFT10, 12やキャパシタ14で構成される。

##### 【0018】

一方、駆動部は走査線駆動回路20、映像線駆動回路22、駆動電源回路24、基準電源回路26及び制御装置28を含み、画素回路8を駆動しOLED6の発光を制御するな

50

どの機能を担う。

**【0019】**

走査線駆動回路20は画素の水平方向の並び(画素行)ごとに設けられた走査信号線30に接続されている。走査線駆動回路20は制御装置28から入力されるタイミング信号に応じて走査信号線30を順番に選択し、選択した走査信号線30に、点灯TFT10をオンする電圧を印加する。

**【0020】**

映像線駆動回路22は画素の垂直方向の並び(画素列)ごとに設けられた映像信号線32に接続されている。映像線駆動回路22は制御装置28から映像信号を入力され、走査線駆動回路20による走査信号線30の選択に合わせて、選択された画素行の映像信号に応じた電圧を各映像信号線32に出力する。当該電圧は、選択された画素行にて点灯TFT10を介してキャパシタ14に書き込まれる。駆動TFT12は書き込まれた電圧に応じた電流をOLED6に供給し、これにより、選択された走査信号線30に対応する画素のOLED6が発光する。

**【0021】**

駆動電源回路24は画素列ごとに設けられた駆動電源線34に接続され、駆動電源線34及び選択された画素行の駆動TFT12を介してOLED6に電流を供給する。

**【0022】**

基準電源回路26は、OLED6のカソード電極を構成する共通電極(図示せず)と、画素間の境界領域に配置されOLED6に電気的に接続された境界電極(図示せず)とに定電位を与える。

**【0023】**

本実施形態においてOLED6の下部電極(第1の電極)は画素ごとに形成された画素電極であり、OLED6の上部電極(第2の電極)が画素電極に対向配置された対向電極となる。下部電極は駆動TFT12に接続される。一方、上部電極は全画素のOLED6に共通の電極で構成される。本実施形態では下部電極がOLED6の陽極(アノード)であり、上部電極が陰極(カソード)である。

**【0024】**

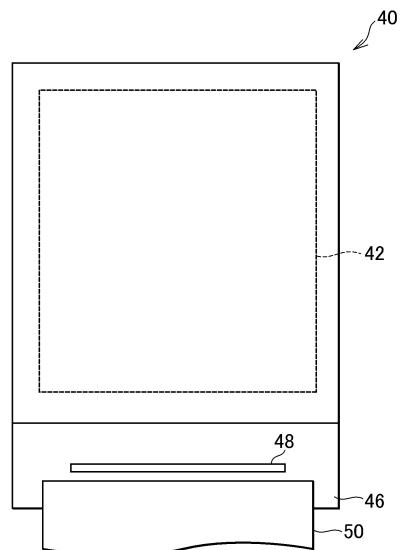

図2は有機EL表示装置2の表示パネル40の模式的な平面図である。表示パネル40の表示領域42に図1に示した画素アレイ部4が設けられ、上述したように画素アレイ部4にはOLEDが配列される。矩形である表示パネル40の一辺には部品実装領域46が設けられ、表示領域42につながる配線が配置される。さらに部品実装領域46には駆動部を構成するドライバIC48が搭載されたり、FPC50が接続されたりする。FPC50は制御装置28やその他の回路20, 22, 24, 26等に接続されたり、FPC50の主面上にICを搭載されたりする。

**【0025】**

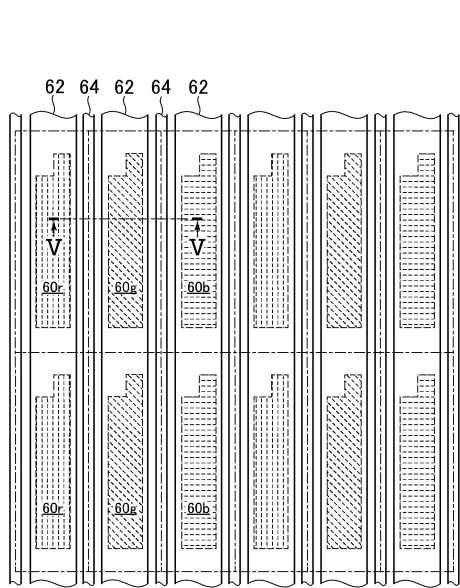

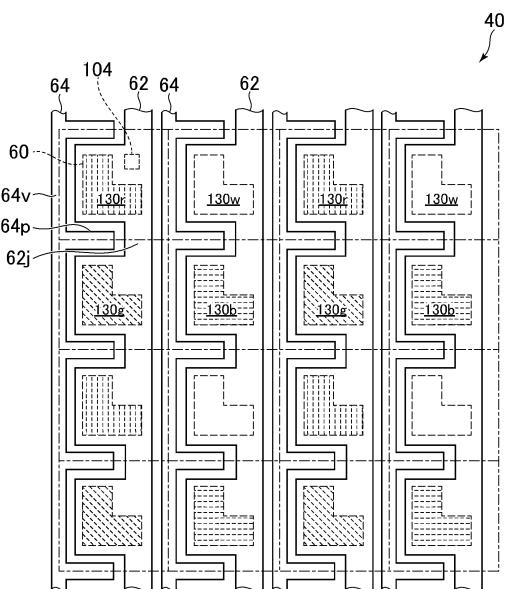

図3は表示領域42の模式的な部分平面図である。本実施形態の表示パネル40は、発光色が赤色(R)、緑色(G)及び青色(B)の3種類の画素(サブピクセル)が行方向に周期的に配置され、列方向に同じ種類の画素(サブピクセル)が並ぶストライプ配列である。表示領域42にはRGB画素それぞれに対応して発光領域となる画素開口60r, 60g, 60bが配列され、それら画素開口同士の間は画素間の境界領域となり、該境界領域にはバンクが形成される。

**【0026】**

上部電極62は各画素列に沿って延在し画素開口60を覆う。隣接する画素列の境界領域には境界電極64(第3の電極)が延在する。上述したように本実施形態ではRGB画素がストライプ配列され、行方向に隣り合う各画素対は互いに発光色が異なる。つまり、境界電極64は発光色が互いに異なる隣接画素間(例えば隣接する第1の画素と第2の画素との間)の境界に沿って配置されている。

**【0027】**

本実施形態の有機EL表示装置2はトップエミッション型であり、OLED6で生じた

10

20

30

40

50

光を上部電極 6 2 側へ出射させるため、上部電極 6 2 は透明導電材で形成される。境界電極 6 4 は例えば、上部電極 6 2 と同層の導電膜で形成することができる。具体的には、表示領域 4 2 に亘る透明導電膜を O L E D 6 上に成膜し、当該膜をパターニングして上部電極 6 2 及び境界電極 6 4 を形成する。

#### 【 0 0 2 8 】

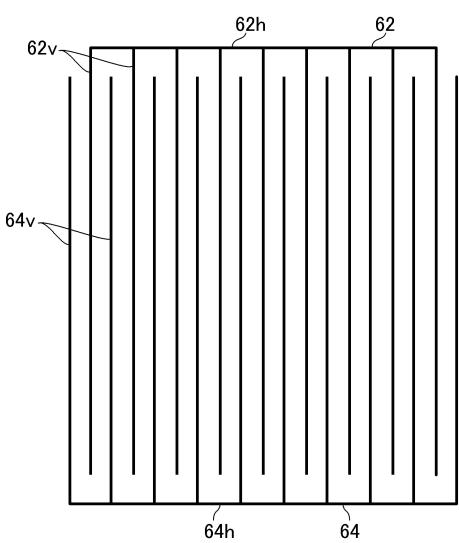

図 4 は表示領域 4 2 における上部電極 6 2 及び境界電極 6 4 のレイアウトの一例を示す模式的な平面図である。上部電極 6 2 は図 3 に示した各画素列に垂直方向に延在される垂直部 6 2 v と、水平方向に延在し当該垂直部 6 2 v を互いに接続する水平接続部 6 2 h とを有するくし状の平面形状とすることができます。即ち、上部電極 6 2 は、各画素列境界に、換言すればバンクと平面的に見て重畠する領域に、スリットを設けた形状をしている。同様に、境界電極 6 4 は図 3 に示した各画素列境界に垂直方向に延在される垂直部 6 4 v と、水平方向に延在し当該垂直部 6 4 v を互いに接続する水平接続部 6 4 h とを有するくし状の平面形状とすることができます。上部電極 6 2 及び境界電極 6 4 はそれぞれ基準電源回路 2 6 に接続される。各画素の上部電極 6 2 は共通の電位（基準電位 <sub>R\_E\_F</sub>）が印加される。また、境界電極 6 4 の各部は共通の電位（電荷吸収電位 <sub>A\_B</sub>）が印加される。

#### 【 0 0 2 9 】

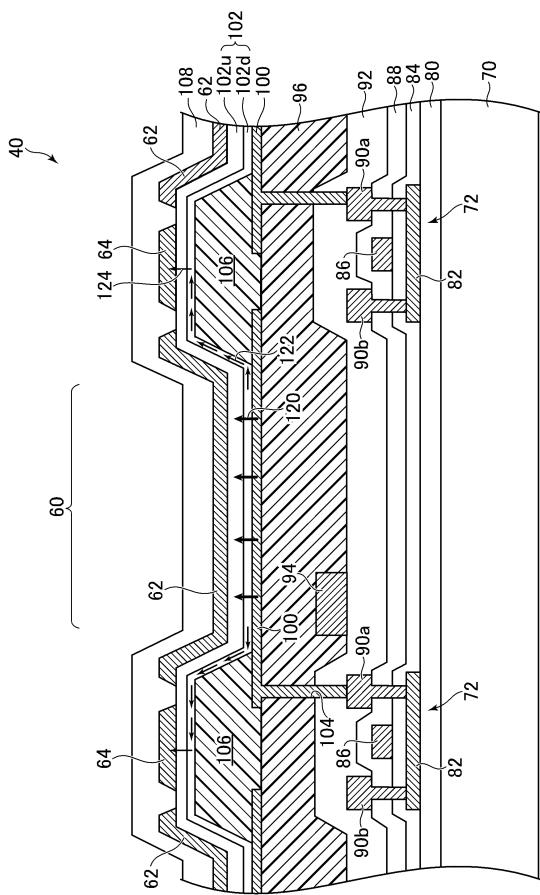

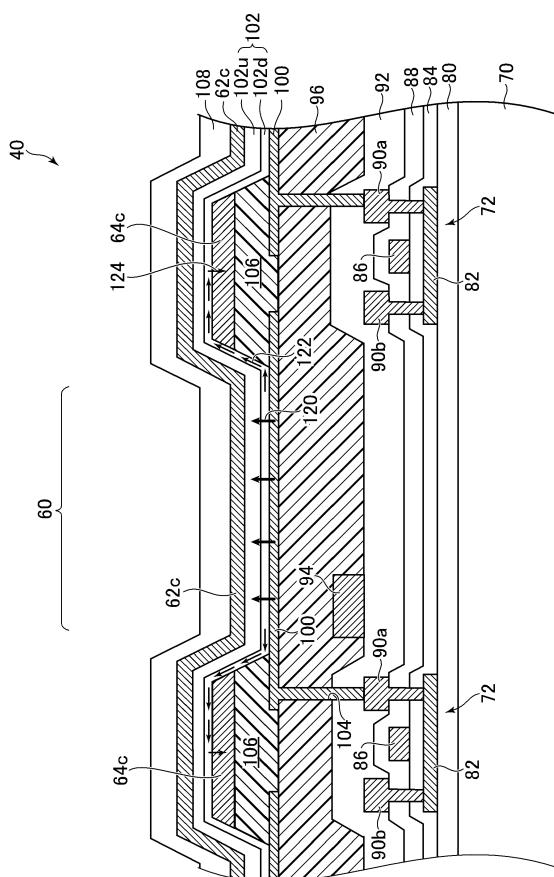

図 5 は図 3 に示す V - V 線に沿った位置での表示パネル 4 0 の模式的な垂直断面図である。表示パネル 4 0 には T F T 7 2 などからなる回路や O L E D 6 などが形成される。この表示パネル 4 0 の構造はガラスや樹脂フィルムからなる基材 7 0 の上に各種の層を積み重ね、またパターニングすることによって形成される。画素アレイ部 4 はトップエミッション型であるので、O L E D 6 で生じた光は基材 7 0 とは反対側、つまり図 5 において上向きに出射される。

#### 【 0 0 3 0 】

具体的には基材 7 0 の上に、窒化シリコン (SiN<sub>y</sub>) や酸化シリコン (SiO<sub>x</sub>) などの無機絶縁材料からなる下地層 8 0 を介して、ポリシリコン (p-Si) 膜が形成され、当該 p-Si 膜をパターニングし、回路層で用いる箇所の p-Si 膜を選択的に残す。例えば、p-Si 膜を用いてトップゲート型の T F T 7 2 のチャネル部及びソース・ドレイン部となる半導体領域 8 2 が形成される。T F T 7 2 のチャネル部の上にはゲート絶縁膜 8 4 を介してゲート電極 8 6 が配置される。ゲート電極 8 6 はスパッタリング等で形成した金属膜をパターニングして形成される。この後、ゲート電極 8 6 を覆う層間絶縁膜 8 8 を積層する。T F T 7 2 のソース部、ドレイン部となる p-Si にはイオン注入により不純物が導入され、さらにそれに電気的に接続されたソース電極 9 0 a 及びドレイン電極 9 0 b が形成される。このようにして T F T 7 2 を形成した後、層間絶縁膜 9 2 を積層する。層間絶縁膜 9 2 の表面には、スパッタリング等で形成した金属膜をパターニングして配線 9 4 等を形成することができ、当該金属膜とゲート電極 8 6、ソース電極 9 0 a 及びドレイン電極 9 0 b の形成に用いた金属膜とで例えば、図 1 に示した走査信号線 3 0、映像信号線 3 2、駆動電源線 3 4 を多層配線構造で形成することができる。この上に例えば、アクリル樹脂等の有機材料を積層して平坦化膜 9 6 が形成され、これにより平坦化された表示領域 4 2 に O L E D 6 が形成される。

#### 【 0 0 3 1 】

O L E D 6 は下部電極 1 0 0、発光素子層 1 0 2 及び上部電極 6 2 で構成され、これら下部電極 1 0 0、発光素子層 1 0 2 及び上部電極 6 2 は基材 7 0 の側からこの順に積層される。

#### 【 0 0 3 2 】

図 5 に示す T F T 7 2 が n チャネルを有した駆動 T F T 1 2 であるとすると、下部電極 1 0 0 は T F T 7 2 のソース電極 9 0 a に接続される。具体的には、上述した平坦化膜 9 6 の形成後、下部電極 1 0 0 を T F T 7 2 に接続するためのコンタクトホール 1 0 4 が形成され、平坦化膜 9 6 の表面及びコンタクトホール 1 0 4 内に形成した導電体膜をパターニングして、T F T 7 2 に接続された下部電極 1 0 0 が画素ごとに分離して形成される。

#### 【 0 0 3 3 】

10

20

30

40

50

例えば、下部電極 100 は ITO、IZO などで形成される。また、本実施形態はトップエミッション型であるので、下部電極 100 は光反射率が高い材料で形成された反射層上に透明導電膜を積層した構造とすることができます。例えば、反射層はアルミニウム (Al) や銀 (Ag) 等で形成することができ、発光層からの光を表示面、つまり上部電極 62 側へ反射させる。

#### 【0034】

上述したように、駆動 TFT12 は各画素の映像信号に応じて OLED6 に流れる電流を制御し、下部電極 100 は各画素の映像信号に応じた量のキャリアを発光素子層 102 へ供給する。具体的には本実施形態では下部電極 100 はアノードであり、キャリアとして正孔が下部電極 100 から発光素子層 102 へ供給される。

10

#### 【0035】

下部電極 100 の形成後、バンク 106 を形成する。バンク 106 は例え、アクリル、ポリイミド等の感光性樹脂をフォトリソグラフィ技術やインクジェット方式でパターニングして、隣接する画素の境界領域に形成される。なお、バンク 106 は SiNy や SiO<sub>x</sub> などの無機絶縁材料で形成することもできる。バンク 106 で囲まれた領域が図 3 に示す画素開口 60 となり、当該領域には下部電極 100 が露出する。

#### 【0036】

バンク 106 の形成後、発光素子層 102 を構成する各層が下部電極 100 の上に順番に積層される。発光素子層 102 はキャリアが注入されて発光する発光層 (EML)、及び発光層への効率的にキャリアを供給する機能を担う補助層を含む。発光素子層 102 は補助層として HIL 及び HTL の少なくとも一方を含む。

20

#### 【0037】

例え、OLED6 は RGB 画素それぞれの発光色に対応した単色発光の OLED であり、アノードである下部電極 100 側から順に HIL、HTL、EML、ETL が積層された構造である。当該構造では HIL、HTL 及び ETL が補助層である。このうち HIL 及び HTL は正孔を供給するアノード (下部電極 100) と発光層 (EML) との間に、表示領域 42 全体に亘って、即ち複数の画素に跨って連続して成膜される。また ETL は電子を供給するカソード (上部電極 62) と発光層 (EML) との間に、表示領域 42 全体に亘って成膜される。尚、発光層 (EML) は発光色ごとに異なる有機発光材料で形成される。

30

#### 【0038】

また、OLED6 は白色発光とすることもできる。この場合、OLED6 の上方にカラーフィルタを配置して、画素に対応した色の光を射出させる。例え、白色発光の OLED6 は発光色が異なる複数の発光素子層 102 を光透過性の中間層を介して電気的に直列接続したタンデム構造とすることができます。タンデム構造では中間層として設けられる電荷発生層 (charge generation layer : CGL) も HIL、HTL 等と同様、キャリア移動性を有する補助層である。

#### 【0039】

図 5 では発光素子層 102 を HIL 及び HTL からなる下層 102d と EML 及び ETL からなる上層 102u とに分けて示している。上層 102u には、更に EIL が含まれる場合もある。

40

#### 【0040】

例え、HTL / HIL は、ポリ(3,4-エチレンジオキシチオフェン) - ポリ(ステレンスルホン酸)(PEDOT - PSS) やその他の導電性有機材料で形成される。

#### 【0041】

発光素子層 102 の上に上部電極 62 と共に境界電極 64 が形成される。図 5 に示すように、上部電極 62 はその端部をバンク 106 の端部にオーバーラップさせて画素開口 60 の上に形成され、境界電極 64 はバンク 106 の上に形成される。

#### 【0042】

上部電極 62 及び境界電極 64 の表面に封止膜 108 が形成される。封止膜 108 は、

50

水分などの透過を阻止し、OLED6を保護する機能を有する。封止膜108として例えば、SiN<sub>y</sub>膜がCVD法によって成膜される。

#### 【0043】

また、図5には示していないが、上部電極62の上を有機膜で覆うことで平坦化し、その後で全面を被覆するため封止膜108を形成してもよい。封止膜108は無機膜と有機膜の複数の積層構成を有してもよい。さらに、表示パネル40の表面の機械的な強度を確保するため、封止膜108の上には保護膜を形成してもよい。また、封止膜108の上には基材70のような基材(対向基材)を配置する(基材70に貼り付ける)こともできる。この場合、対向基材と封止膜108との間のスペースに充填材を充填してもよい。

#### 【0044】

上述したように、有機EL表示装置2の駆動時においては、発光層(EML)に映像信号に応じたキャリアが供給されて、各画素のOLED6が発光する。図5には当該駆動時に下部電極100から発光素子層102へ供給されるキャリアである正孔の流れを矢印で模式的に示している。上部電極62には下部電極100より低い電位が印加され、各画素の下部電極100から発光素子層102の下層102dへ供給される正孔は基本的には当該下部電極100とこれに対向配置された上部電極62との間の電界に従い、矢印120で示すように発光素子層102の上層102uへ引き寄せられ当該画素の発光層(EML)に注入される。

#### 【0045】

一方、下部電極100から下層102dに供給された正孔の一部は矢印122で示すように下層102d内を移動し、上述した隣接画素へ向かうリーク電流となる。有機EL表示装置2は、このリーク電流となる正孔を矢印124で示すように境界電極64で吸収する。これにより、隣接画素へのリーク電流の到達が阻止され、リーク電流による隣接画素の発光が防止される。よって、画像の解像度の低下が抑制される。また、境界電極64を互いに発光色が異なる隣接画素間の境界に配置することで、リーク電流による混色が抑制され高い色純度が得られ、好適な色再現性を実現できる。

#### 【0046】

リーク電流となる正孔を境界電極64で吸収するために、境界電極64に印加する電荷吸収電位<sub>A\_B</sub>は、発光素子層102内を隣接画素に向かって伝導するキャリアを、画素の境界領域にて引き寄せる電位に設定される。具体的には、本実施形態では正孔を吸収するために、電荷吸収電位<sub>A\_B</sub>は下部電極100より低い電位に設定される。

#### 【0047】

さらに、当該キャリアを効果的に吸収するには、境界電極64に印加する電荷吸収電位<sub>A\_B</sub>と下部電極100の電位との差を、上部電極62に印加される基準電位<sub>R\_E\_F</sub>と下部電極100の電位との差より大きく設定することが好適である。すなわち、電荷吸収電位<sub>A\_B</sub>を基準電位<sub>R\_E\_F</sub>より低い電位とすることでリーク電流となる正孔が境界電極64に吸収されやすくなる。例えば、基準電位<sub>R\_E\_F</sub>を0V、電荷吸収電位<sub>A\_B</sub>を-2Vに設定することができる。

#### 【0048】

なお、上部電極62と境界電極64との間隙部分における下層102dの電位は、上部電極62や境界電極64が配置された部分における下層102dの電位より高くなり、正孔の移動に対する電位障壁を形成し得る。つまり、リーク電流の進行方向に対して、隣接画素の上部電極62が配置された部分より手前に当該上部電極62と境界電極64との間隙による電位障壁が形成され得る。このような効果を利用して、<sub>A\_B < R\_E\_F</sub>でなくとも隣接画素へのリーク電流の到達を阻止できる構成とすることはできる。

#### 【0049】

OLED6がタンデム構造である場合には、境界電極64は電荷発生層(CGL)を経由して隣接画素へ移動する正孔も吸収し、CGL経由のリーク電流も抑制する。

#### 【0050】

上述の説明では上部電極62と境界電極64とは同層の導電膜をパターニングして形成

10

20

30

30

40

50

したが、両電極を別工程で形成することもできる。この場合、境界電極 6 4 は上部電極 6 2 とは別の導電材料で形成することができ、例えば、ITOやIZOなどの透明導電材料より低抵抗な材料や不透明な材料を用いて境界電極 6 4 を形成することができる。例えば、境界電極 6 4 を不透明な金属で形成することで、隣接画素への光漏れを抑制して混色防止を図ることができる。

#### 【0051】

##### [第1の実施形態の変形例]

上記第1の実施形態ではRGB画素がストライプ配列された有機EL表示装置2における境界電極64によるリーク電流抑制構造を説明したが、当該リーク電流抑制構造は他の画素配列においても適用することができる。

10

#### 【0052】

図6は第1の実施形態の変形例に係る有機EL表示装置2aの表示領域42の模式的な部分平面図である。有機EL表示装置2aの表示領域42には発光色が異なる4種類の画素がマトリクス状に配列され、2行2列の4画素が互いに異なる色で発光する。4種類の画素は奇数行及び偶数行それぞれに2種類ずつ行方向に交互に配置されるか、または奇数列及び偶数列それぞれに2種類ずつ列方向に交互に配置される。具体的には、図6に示す例では、4種類の発光色はRGBに加え、白色(W)であり、例えば、奇数行にR画素130r、W画素130wが交互に配列され、偶数行にG画素130g、B画素130bが交互に配列される。なお、各行各列の2種類の発光色の組み合わせは図6に示したものに限定されない。

20

#### 【0053】

上記第1の実施形態のストライプ配列では列方向には同じ色の画素が並ぶので、列方向に隣接する画素間でのリーク電流は混色による画質劣化を生じない。そのため、画素行間の境界領域への境界電極64の配置は省略し、画素列間の境界領域にのみ境界電極64を配置する例を示した。

#### 【0054】

これに対し、図6に示す画素配列では行方向に隣接する画素間と列方向に隣接する画素間との両方にてリーク電流を抑制し、混色を防止することが好ましい。そこで、例えば、境界電極64は図3に示した、各画素列境界に垂直方向に延在される垂直部64v(延在部)、及び水平接続部64hに加え、各垂直部64vから各画素行境界に沿って突き出した水平突起部64pを備え、行方向と列方向との両方のリーク電流を抑制する。

30

#### 【0055】

ここで、上部電極62と境界電極64とを同層の導電膜で形成するので、画素行境界には列方向に隣接する画素間にて上部電極62をつなぐ接続部62jが必要になる。そのため、水平突起部64p(突起部)は列方向に隣接する画素の境界の全体に沿ってではなく一部のみに沿って形成される。

#### 【0056】

コンタクトホール104上に下部電極100を平坦に形成することが難しいことから、例えば図5においては、コンタクトホール104を画素開口60の領域内に形成するのではなく、バンク106が配置される領域内に形成している。しかし、画素の微細化に伴い、コンタクトホール104を画素の境界領域に納めることができなくなる場合がある。図6の画素レイアウトでは、画素開口60を矩形の一部を切り欠いたL字形状とし、切り欠いた領域にコンタクトホール104及びバンク106を形成している。このような画素レイアウトでは列方向に隣接する画素間における境界のうち、画素開口60間の距離が小さい個所と大きい個所とが生じる。そこで、画素開口60間の距離が小さい個所に水平突起部64pを設けリーク電流を好適に防止しつつ、画素開口60間の距離が大きい個所に接続部62jを設け上部電極62を列方向に接続することができる。

40

#### 【0057】

##### [第2の実施形態]

以下、本発明の第2の実施形態に係る有機EL表示装置2bを説明する。本実施形態と

50

上記第1の実施形態とは境界電極64及びそれに付随する構造に相違点を有し、その他の点では基本的に共通である。以下、第2の実施形態について第1の実施形態との相違点を中心に説明する。

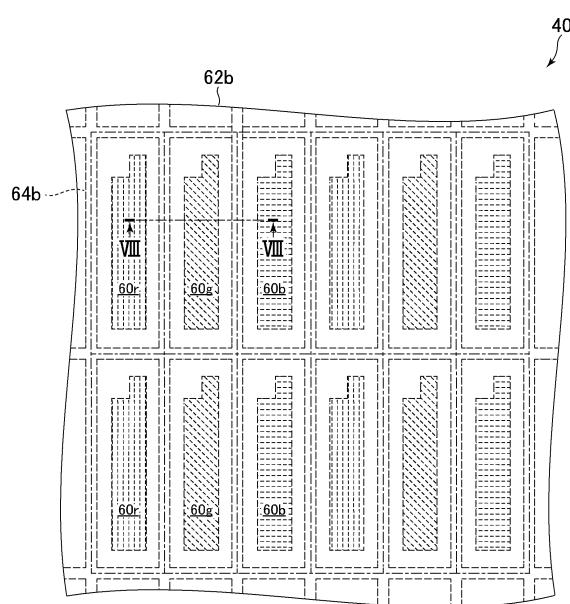

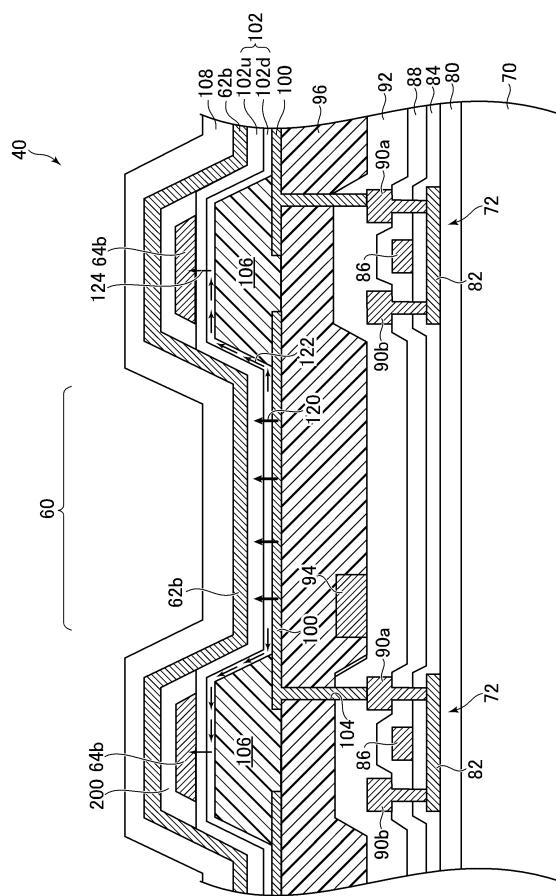

#### 【0058】

図7は有機EL表示装置2bの表示パネル40の表示領域42の模式的な部分平面図であり、図8は図7に示すVII - VII線に沿った位置での表示パネル40の模式的な垂直断面図である。有機EL表示装置2bは第1の実施形態と同様、RGB画素がストライプ配列された表示パネル40を備える。

#### 【0059】

本実施形態では上部電極62と境界電極64とは別々の導電膜で形成され、これにより両電極の平面形状の自由度が高くなる。具体的には、境界電極64bをバンク106上にて発光素子層102の上面に接して形成し、その後、上部電極62bを形成する。この構造では境界電極64bは各画素を取り囲む画素境界の全周に沿って配置することができる。すなわち、境界電極64bは格子状の平面形状とされ、画素列間の境界領域だけでなく画素行間の境界領域にも配置される。一方、上部電極62bは境界電極64bの上にも形成でき、基本的に表示領域42全体に亘って共通に形成される。なお、上部電極62bと境界電極64bとが重なる部分には両電極間に絶縁膜200が形成される。

#### 【0060】

本実施形態によっても第1の実施形態と同様、HTL/HIL等のキャリア移動性を有した補助層を経由したリーク電流による隣接画素の発光を阻止することができる。また、本実施形態は、各画素の画素境界の全周に境界電極64を配置できるので、より好適に隣接画素へのリーク電流を抑制できる。

#### 【0061】

境界電極64bは上部電極62bとは別の導電材料で形成することができ、第1の実施形態で述べたように、ITOやIZOなどの透明導電材料より低抵抗な材料や不透明な材料を用いて境界電極64bを形成することができる。例えば、境界電極64bを不透明な金属で形成することで、隣接画素への光漏れを抑制して混色防止を図ることができる。

#### 【0062】

なお、本実施形態は第1の実施形態の変形例で述べたような、ストライプ配列以外の画素配列に容易に適用することができる。

#### 【0063】

##### [第3の実施形態]

以下、本発明の第3の実施形態に係る有機EL表示装置2cを説明する。本実施形態と上記第1及び第2の実施形態とは境界電極64及びそれに付随する構造に相違点を有し、その他の点では基本的に共通である。以下、第3の実施形態について上記各実施形態との相違点を中心に説明する。

#### 【0064】

有機EL表示装置2cの表示パネル40の表示領域42の模式的な部分平面図は、第2の実施形態について示した図7と基本的には同じであり、これを援用する。図9は図7に示すVII - VII線に沿った位置での有機EL表示装置2cの表示パネル40の模式的な垂直断面図である。

#### 【0065】

本実施形態は第2の実施形態と同様、上部電極62と境界電極64とは別々の導電膜で形成され、これにより両電極の平面形状の自由度が高くなる。例えば、第2の実施形態と同様、境界電極64cは画素境界に沿った格子状の平面形状とし、上部電極62cは基本的に表示領域42全体に亘って共通に形成される。

#### 【0066】

本実施形態が第2の実施形態と異なる点は、境界電極64cが発光素子層102の下に配置される点である。すなわち、バンク106の上面に境界電極64cが配置され、その後、発光素子層102、上部電極62が順次積層される。

10

20

30

40

50

**【0067】**

図9に示すように、境界電極64cはバンク106の上面及び側面に沿って積層されることが、換言すれば、境界電極64cはバンク106の側面とほぼ同じテーパー形状を有し且つバンク106の上面の上面全域に配置されることが、望ましい。これにより、境界電極64cの上層に配置される発光素子層102が、段切れなどの不具合が起こることなく、画素境界領域に好適に被覆されることになる。また、境界電極64cをパターニングする際のエッチングをウェットエッチングなどとし境界電極64cの端部の傾斜を緩やかにする等、画素境界領域の表面における角や段差を抑制する工夫をすることがさらに好適である。

**【0068】**

10

本実施形態によっても第2の実施形態と同様、HTL/HIL等のキャリア移動性を有した補助層を経由したリーク電流による隣接画素の発光を好適に阻止することができる。

**【0069】**

なお、補助層のうち下層102dに含まれるHILやHTLは、上層102uに含まれるETLやEILよりも比較的厚く形成されることが多い。よって、リーク電流となるキャリアの多くは、下層102d内を移動する。図9に示す本実施形態では、境界電極64が下層102dと接しているので、即ち、HIL或いはHTLの何れかと接しているので、当該キャリアを効率よく吸収し、下層102d内を経由するリーク電流を好適に抑制することができる。

**【0070】**

20

また、境界電極64cは上部電極62cとは別の導電材料で形成することができ、例えば、境界電極64cを低抵抗な金属で形成することができる。

**【0071】**

なお、本実施形態も第1の実施形態の変形例で述べたような、ストライプ配列以外の画素配列に容易に適用することができる。

**【0072】**

30

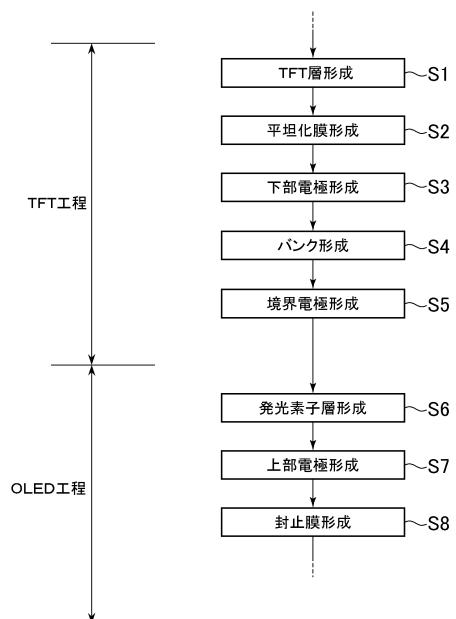

図10は、本実施形態に係る表示パネル40の製造工程の概略のフロー図である。表示パネル40の製造では、生産効率を高めるために、1枚の大きな基材70上に複数面の表示パネル40を同時に形成する手法が採用される。この製造手法では基材上へのTFTの形成などの工程は複数面の表示パネル40を一体に行われ、一方、OLED形成工程は複数面の表示パネル40を分割して行われる。つまり、この製造方法は、複数面の表示パネル40がつながった状態で加工される前段工程と、表示パネル40ごとに分割されて残りの加工が施される後段工程とに分けられ、ここでは前段工程をTFT工程、後段工程をOLED工程と呼ぶ。

**【0073】**

TFT工程は基本的に、集積回路などを製造する半導体製造プロセスを利用して行うことができる工程からなり、比較的にプロセス条件の自由度が高く、例えば、数百程度の高温プロセスを利用するよう製造工程を設計することも可能である。一方、OLED工程は、有機材料からなる発光素子層の劣化を防ぐため、雰囲気温度の上限が数十程度に制限され得る。つまり、OLED工程は、表示パネル40をそれぞれ加工することにより工数が増加し、またTFT工程に比べてより確実にプロセス条件を制御する必要がある。そのため、表示パネル40の製造工程においてTFT工程の占める割合を大きくし、OLED工程の占める割合を小さくすることで、表示パネル40の製造コストの低減や製造期間の短縮を図ることができる。

40

**【0074】**

本実施形態ではTFT工程として、基材70の上にTFT72などからなる回路を形成する工程(ステップS1)、その上に平坦化膜96を積層する工程(ステップS2)、下部電極100を形成する工程(ステップS3)、及びバンク106を形成する工程(ステップS4)が行われる。これらは第1の実施形態と同様に行うことができる。

**【0075】**

50

本実施形態では、さらに境界電極 64c を形成する工程（ステップ S5）が TFT 工程として行われ、これにより、上に述べた製造コスト低減や製造期間短縮の効果が得られる。例えば、境界領域にバンク 106 が形成された後、表示領域 42 の全面に導電膜を形成し、フォトリソグラフィ技術を用いて当該導電膜をパターニングして、境界電極 64c が形成される。

#### 【0076】

なお、OLED 工程は境界電極 64c の形成後の工程、具体的には発光素子層 102 を形成する工程（ステップ S6）、上部電極 62c を形成する工程（ステップ S7）、封止膜 108 を形成する工程（ステップ S8）などを含む。

#### 【0077】

本実施形態によっても上記各実施形態と同様、HTL/HIL 等のキャリア移動性を有した補助層を経由したリーク電流による隣接画素の発光を阻止することができる。また、本実施形態は、各画素の画素境界の全周に境界電極 64 を配置できるので、より好適に隣接画素へのリーク電流を抑制できる。

#### 【0078】

なお、本実施形態は第 1 の実施形態の変形例で述べたような、ストライプ配列以外の画素配列に容易に適用することができる。

#### 【0079】

##### [第 3 の実施形態の変形例]

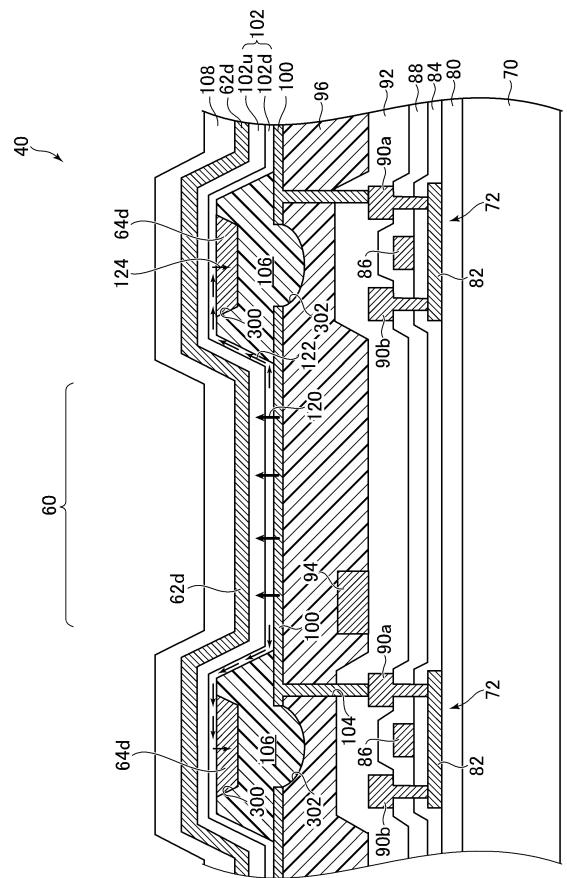

図 11 は第 3 の実施形態の変形例に係る有機 EL 表示装置 2d の表示パネル 40 の模式的な部分断面図であり、第 3 の実施形態と同様、図 7 に示す VILI - VILI 線に沿った位置での垂直断面図である。

#### 【0080】

本変形例ではバンク 106 の上面に凹部 300 が形成され、当該凹部 300 に境界電極 64d が充填される。例えば、境界電極 64d は Ag などのナノ粒子を含んだナノインクで形成することができる。ナノインクは例えば、インクジェット法で凹部 300 に塗布・充填され、また、塗布後、減圧乾燥等により流動しにくくされる。その後、熱処理を施して、ナノインク層を溶融、焼成する。なお、凹部 300 を境界電極 64d で埋めることで境界電極 64d 形成後の画素境界領域の表面はなだらかになり、その上に発光素子層 102 を画素境界領域に被覆することができる。

#### 【0081】

凹部 300 は、バンク 106 を形成した後、エッチングで形成することができる。また、図 11 に示すようにバンク 106 が配置される個所の平坦化膜 96 の表面に凹部 302 を形成した後、バンク 106 を積層することでバンク 106 の上面の凹部 300 を形成することができる。例えば、平坦化膜 96 の凹部 302 は下部電極 100 をパターニングする際のエッチングで形成することができる。

#### 【0082】

上記各実施形態及び変形例では、下部電極 100 が OLED 6 のアノード、上部電極 62 が OLED 6 のカソードである場合を説明した。しかし、本発明は、下部電極 100 が OLED 6 のカソード、上部電極 62 が OLED 6 のアノードである場合にも適用できる。その場合、発光素子層 102 における各層の積層順序は上述の構成とは逆転する。例えば、カソードである下部電極 100 側から順に EIL、ETL、EML、HTL、HIL が積層された構造となる。また、当業者が理解し得るように、電流の向きや電位の大小関係が基本的に上記実施形態とは逆転する。

#### 【0083】

本発明の実施形態として上述した有機 EL 表示装置 2（2a, 2b, 2c, 2d を含む）を基にして、当業者が適宜設計変更して実施し得る全ての有機 EL 表示装置も、本発明の要旨を包含する限り、本発明の範囲に属する。また、有機 EL 表示装置以外の表示装置、例えば発光層として量子ドット素子を採用した量子ドット表示装置等も本発明の範囲に属する。

## 【0084】

本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。例えば、前述の各実施形態に対して、当業者が適宜、構成要素の追加、削除若しくは設計変更を行ったもの、又は、工程の追加、省略若しくは条件変更を行ったものも、本発明の要旨を備えている限り、本発明の範囲に含まれる。

## 【0085】

また、本実施形態において述べた様によりもたらされる他の作用効果について本明細書記載から明らかなもの、又は当業者において適宜想到し得るものについては、当然に本発明によりもたらされるものと解される。

10

## 【符号の説明】

## 【0086】

2 有機EL表示装置、4 画素アレイ部、6 OLED、8 画素回路、10 点灯TFT、12 駆動TFT、14 キャパシタ、20 走査線駆動回路、22 映像線駆動回路、24 駆動電源回路、26 基準電源回路、28 制御装置、30 走査信号線、32 映像信号線、34 駆動電源線、40 表示パネル、42 表示領域、44 陰極、46 部品実装領域、48 ドライバIC、50 FPC、60 画素開口、62 上部電極、64 境界電極、70 基材、72 TFT、80 下地層、82 半導体領域、84 ゲート絶縁膜、86 ゲート電極、88, 92 層間絶縁膜、90a ソース電極、90b ドレイン電極、94 配線、96 平坦化膜、100 下部電極、102 発光素子層、104 コンタクトホール、106 バンク、108 封止膜、200 絶縁膜、300 凹部。

20

【図1】

【図2】

【 図 3 】

【 図 4 】

【図5】

【 四 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

| (51)Int.Cl. |       | F I       |         |       |

|-------------|-------|-----------|---------|-------|

| H 0 5 B     | 33/28 | (2006.01) | H 0 5 B | 33/22 |

| H 0 1 L     | 27/32 | (2006.01) | H 0 5 B | 33/06 |

| G 0 9 F     | 9/30  | (2006.01) | H 0 5 B | 33/28 |

|             |       |           | H 0 1 L | 27/32 |

|             |       |           | G 0 9 F | 9/30  |

|             |       |           |         | 3 6 5 |

(56)参考文献 特開2014-053236 (JP, A)

特開2013-206738 (JP, A)

特開2008-311212 (JP, A)

米国特許出願公開第2008/0284323 (US, A1)

特開2012-155953 (JP, A)

特開2014-078399 (JP, A)

特開2008-051959 (JP, A)

特開2009-231264 (JP, A)

特開2009-302025 (JP, A)

特開2012-059641 (JP, A)

特開2013-089293 (JP, A)

特開2008-004362 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

|         |           |

|---------|-----------|

| H 0 5 B | 3 3 / 0 0 |

| G 0 9 F | 9 / 3 0   |

| H 0 1 L | 2 7 / 3 2 |

| H 0 1 L | 5 1 / 5 0 |