(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6098366号

(P6098366)

(45) 発行日 平成29年3月22日(2017.3.22)

(24) 登録日 平成29年3月3日(2017.3.3)

(51) Int.CI.

G 0 6 T 1/60 (2006.01)

F 1

G O 6 T 1/60 4 5 O F

請求項の数 6 (全 24 頁)

(21) 出願番号 特願2013-110560 (P2013-110560)

(22) 出願日 平成25年5月27日 (2013.5.27)

(65) 公開番号 特開2014-229227 (P2014-229227A)

(43) 公開日 平成26年12月8日 (2014.12.8)

審査請求日 平成28年1月28日 (2016.1.28)

(73) 特許権者 514315159

株式会社ソシオネクスト

神奈川県横浜市港北区新横浜2丁目10番

23

(74) 代理人 100092152

弁理士 服部 毅巖

(72) 発明者 田中 将輝

愛知県春日井市高蔵寺町二丁目1844番

2 富士通VLSI株式会社内

審査官 新井 則和

最終頁に続く

(54) 【発明の名称】 画像データ処理装置及び画像データ処理方法

## (57) 【特許請求の範囲】

## 【請求項1】

撮像素子のN(N-2)本の読み出しライン分の画素データを保持するN×N個の記憶部と、

前記N×N個の記憶部に含まれる記憶部を列方向または行方向に選択して、N画素ずつ前記画素データを書き込み、Nライン分の前記画素データの書き込みごとに、前記記憶部の選択方向を切り替える書き込み制御部と、

Nの倍数ライン目の前記画素データの書き込み時、当該書き込み時における前記記憶部の選択方向とは異なる方向でN個の前記記憶部を選択し、前記書き込まれた前記Nライン分の画素データの並列読み出しを開始する読み出し制御部と、を有し、

前記N×N個の記憶部のうち、前記Nの倍数ライン目の画素データの書き込みで最初に選択される記憶部は、読み出しと書き込みを異なる端子を用いて行い、他の記憶部は、読み出しと書き込みを共通の端子を用いて行う、

ことを特徴とする画像データ処理装置。

## 【請求項2】

前記列方向または前記行方向で選択される前記N個の記憶部への1ライン分の前記画素データの書き込み開始前に、当該N個の記憶部に書き込まれている画素データの読み出しが完了している、ことを特徴とする請求項1に記載の画像データ処理装置。

## 【請求項3】

前記読み出し制御部は、前記Nの倍数ラインの画素データのうち、1ワード分の書き込

10

20

みが完了すると、前記並列読み出しを開始させる、ことを特徴とする請求項 1 または 2 に記載の画像データ処理装置。

**【請求項 4】**

前記撮像素子からの前記画素データの読み出し順で、前記画素データを受け取り、それそれが、前記読み出し順に対して N 画素ずつ飛び飛びのデータ並びとなる N 並列の第 1 の並列データを生成する並列化部を有し、

書き込み時に選択される前記記憶部には、前記並列化部からの前記第 1 の並列データが N 画素ずつ書き込まれ、

読み出し時に選択される前記 N 個の記憶部から読み出される N 並列の第 2 の並列データのそれぞれのデータ並びは、前記読み出し順である、

ことを特徴とする請求項 1 乃至 3 の何れか一項に記載の画像データ処理装置。

**【請求項 5】**

前記 N の倍数ラインの前記画素データの書き込みで最初に選択される記憶部と、前記他の記憶部とを、同じ制御信号またはアドレスで動作させる 2 種類のインターフェースを有することを特徴とする請求項 1 乃至 4 の何れか一項に記載の画像データ処理装置。

**【請求項 6】**

書き込み制御部が、撮像素子の N ( N - 2 ) 本の読み出しどり分の画素データを保持する N × N 個の記憶部に含まれる記憶部を列方向または行方向に選択して、N 画素ずつ前記画素データを書き込み、N ライン分の前記画素データの書き込みごとに、前記記憶部の選択方向を切り替え、

読み出し制御部が、N の倍数ライン目の前記画素データの書き込み時、当該書き込み時における前記記憶部の選択方向とは異なる方向で N 個の前記記憶部を選択し、前記書き込まれた前記 N ライン分の画素データの並列読み出しを開始し、

前記 N × N 個の記憶部のうち、前記 N の倍数ライン目の画素データの書き込みで最初に選択される記憶部は、読み出しと書き込みを異なる端子を用いて行い、他の記憶部は、読み出しと書き込みを共通の端子を用いて行う、

ことを特徴とする画像データ処理方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、画像データ処理装置及び画像データ処理方法に関する。

**【背景技術】**

**【0002】**

近年、撮像素子の性能向上により、その動作周波数が高周波数化傾向にある。撮像素子の出力は、その後段につながる I S P ( Image Signal Processor ) の動作に関係なく出力されるが、I S P は、メモリの動作可能周波数の性能限界の影響で、撮像素子からの入力をリアルタイムに処理するための高周波数化には限度がある。

**【0003】**

そこで、撮像素子からラスタ走査順に読み出される画素データを、I S P が複数画素ずつ受け取り、並列に処理することで I S P 内の周波数を下げる考えられる。

ただ、撮像素子からラスタ走査順に入力される画素データを複数画素ずつ受け取り並列に出力するだけでは、各並列出力のデータの並びは、ラスタ走査順ではなく、飛び飛びのデータとなり、このままでは後段の回路で並列に処理することができない。そのため、ラインバッファなどを用いて、飛び飛びの並列データを後段の回路で並列処理できるように並べ替えることが行われる。

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献 1】**特開平 8 - 96116 号公報

**【特許文献 2】**特開 2001 - 67265 号公報

10

20

30

40

50

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

N画素並列に処理しようとする場合、N本のラインバッファ（たとえば、RAM（Random Access Memory））を用いることが考えられる。前述したように、撮像素子からの出力（読み出し）はISPの動作に関係なく次々に発生する。そこで、Nライン分のデータ書き込み完了時点で、次のラインの書き込み領域を確保できるだけの読み出しを完了しておため、Nライン目の書き込みと読み出しをオーバーラップさせることが考えられる。

## 【0006】

しかし、このような処理を行う場合、並列数が増えると前のラインの読み出しが完了していないにも関わらず、新たなラインのデータの書き込みが同じアドレス上で発生してしまい、前のラインのデータを上書きし破壊してしまう可能性がある。これを避けるために、ラインバッファ数をN本よりも増やすことが考えられるが、面積の増加につながってしまう。

10

## 【課題を解決するための手段】

## 【0007】

発明の一観点によれば、撮像素子のN（N-2）本の読み出しライン分の画素データを保持するN×N個の記憶部と、前記N×N個の記憶部に含まれる記憶部を列方向または行方向に選択して、N画素ずつ前記画素データを書き込み、Nライン分の前記画素データの書き込みごとに、前記記憶部の選択方向を切り替える書き込み制御部と、Nの倍数ライン目の前記画素データの書き込み時、当該書き込み時における前記記憶部の選択方向とは異なる方向でN個の前記記憶部を選択し、前記書き込まれた前記Nライン分の画素データの並列読み出しを開始する読み出し制御部と、を有し、前記N×N個の記憶部のうち、前記Nの倍数ライン目の画素データの書き込みで最初に選択される記憶部は、読み出しと書き込みを異なる端子を用いて行い、他の記憶部は、読み出しと書き込みを共通の端子を用いて行う、画像データ処理装置が提供される。

20

## 【0008】

また、発明の一観点によれば、書き込み制御部が、撮像素子のN（N-2）本の読み出しライン分の画素データを保持するN×N個の記憶部に含まれる記憶部を列方向または行方向に選択して、N画素ずつ前記画素データを書き込み、Nライン分の前記画素データの書き込みごとに、前記記憶部の選択方向を切り替え、読み出し制御部が、Nの倍数ライン目の前記画素データの書き込み時、当該書き込み時における前記記憶部の選択方向とは異なる方向でN個の前記記憶部を選択し、前記書き込まれた前記Nライン分の画素データの並列読み出しを開始し、前記N×N個の記憶部のうち、前記Nの倍数ライン目の画素データの書き込みで最初に選択される記憶部は、読み出しと書き込みを異なる端子を用いて行い、他の記憶部は、読み出しと書き込みを共通の端子を用いて行う、画像データ処理方法が提供される。

30

## 【発明の効果】

## 【0009】

開示の画像データ処理装置及び画像データ処理方法によれば、小規模な回路で画素データを並列化できる。

40

## 【図面の簡単な説明】

## 【0010】

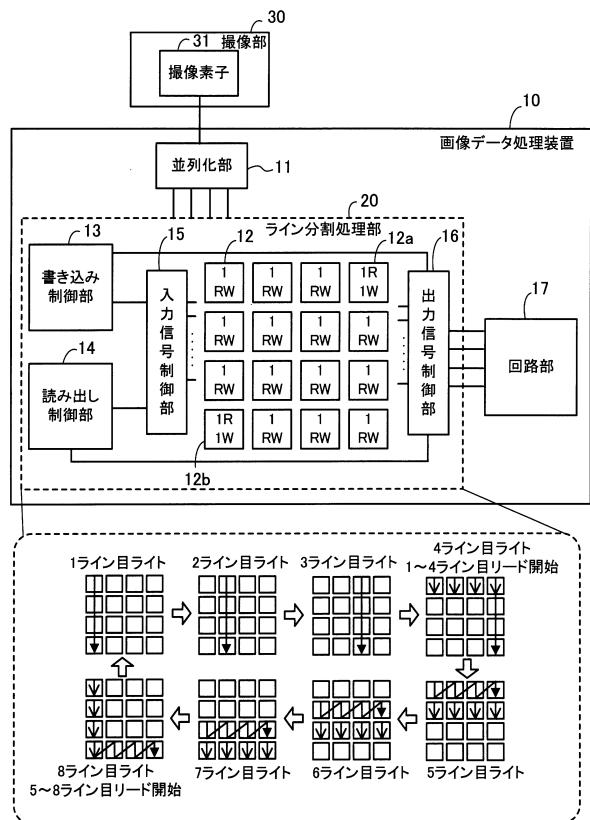

【図1】第1の実施の形態の画像データ処理装置と画像データ処理方法の一例を示す図である。

【図2】画像データ処理装置が4画素ずつデータを受け取り4並列で処理を行う例を示す図である。

【図3】並べ替え処理に用いられるRAMの例を示す図である。

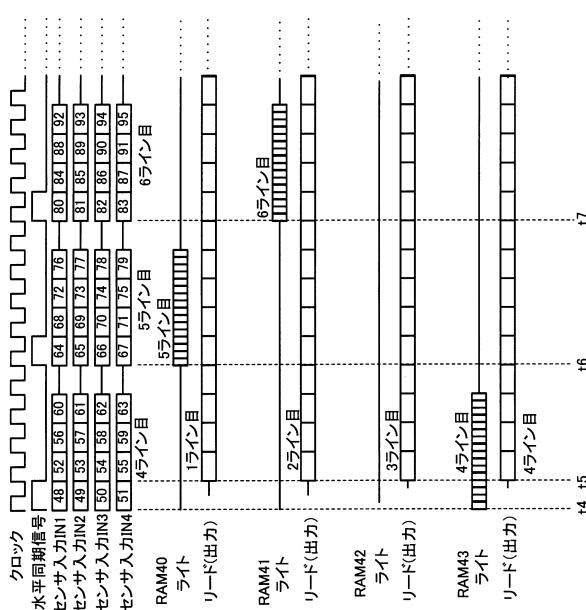

【図4】4つのRAMを用いた並べ替え処理の一例の様子を示すタイミングチャートである（その1）。

50

【図5】4つのRAMを用いた並べ替え処理の一例の様子を示すタイミングチャートである（その2）。

【図6】第2の実施の形態の画像データ処理装置が適用される撮像装置の一例を示す図である。

【図7】ライン分割処理部の一例を示す図である。

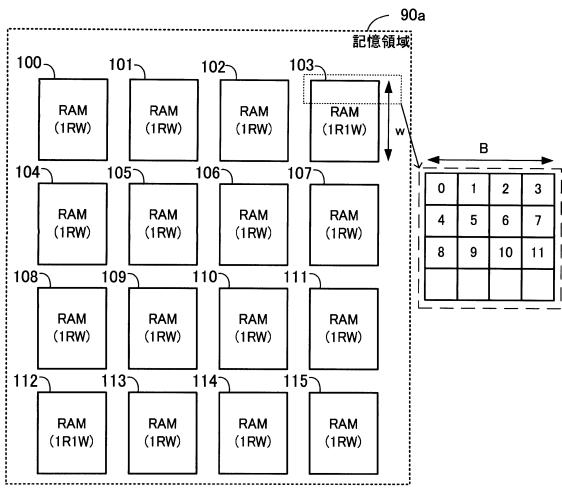

【図8】並列数N=4としたときの、RAM周辺部の一例を示す図である。

【図9】入力信号制御部の入出力信号の関係の例を示す図である。

【図10】出力信号制御部の入出力信号の関係の例を示す図である。

【図11】並列数N=4としたときの、記憶領域の例を示す図である。

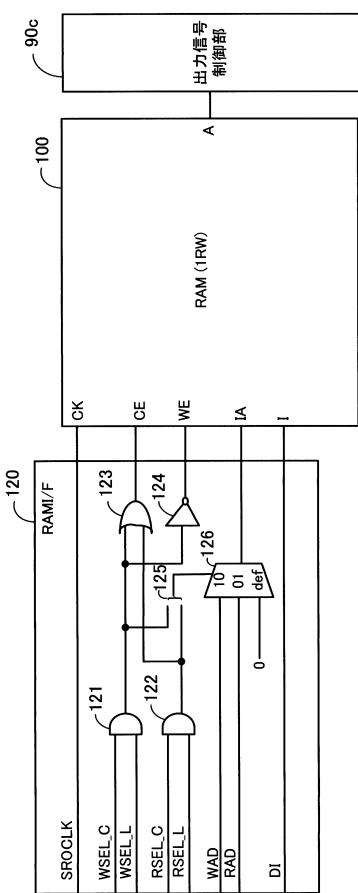

【図12】1RWの1ポートRAMに用いられるRAMI/Fの一例を示す図である。 10

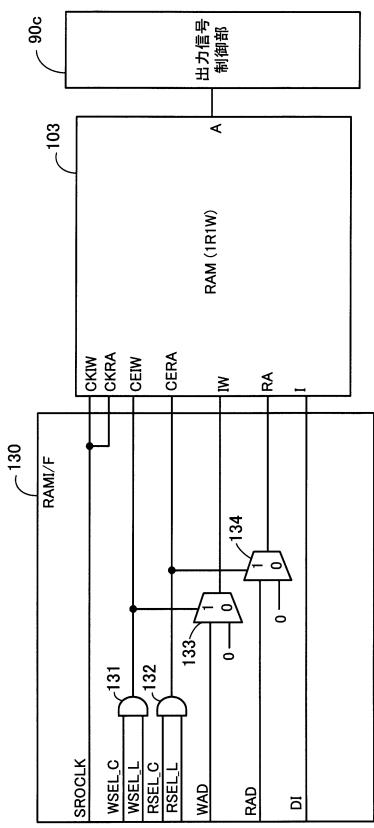

【図13】1R1Wの2ポートRAMに用いられるRAMI/Fの一例を示す図である。

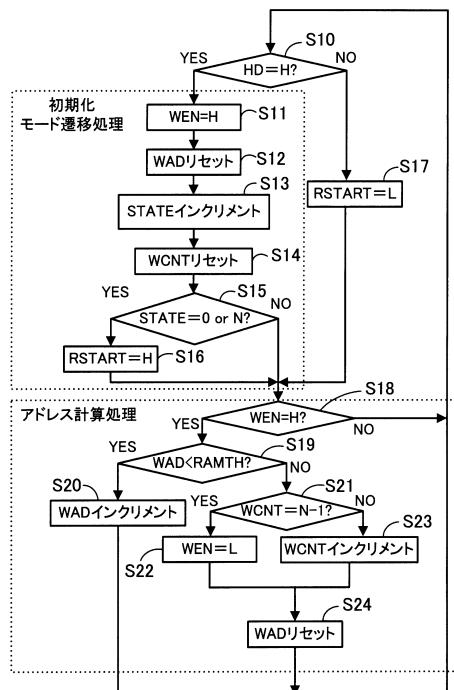

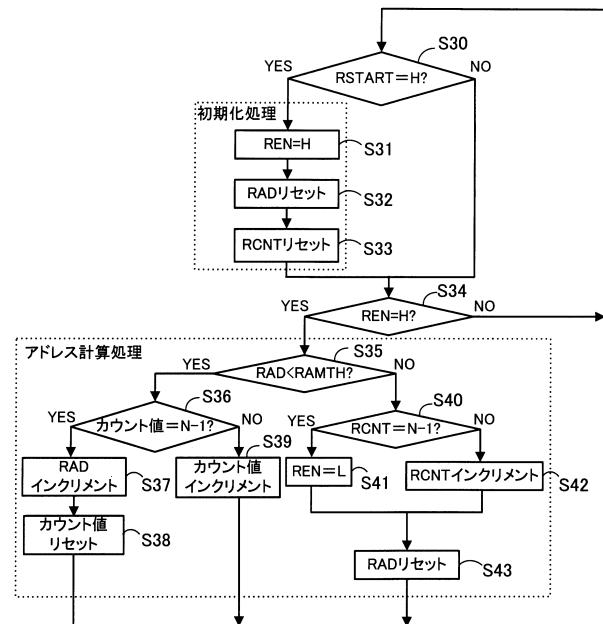

【図14】並列データのライト処理の一例の流れを示すフローチャートである。

【図15】並列データのリード処理の一例の流れを示すフローチャートである。

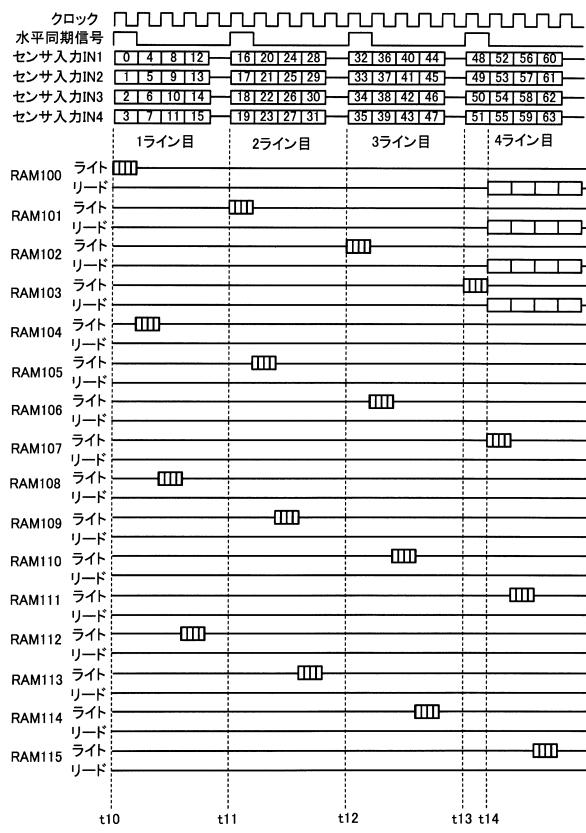

【図16】並列数N=4のときのライン分割処理部によるデータの並べ替え処理の一例の様子を示すタイミングチャートである（その1）。

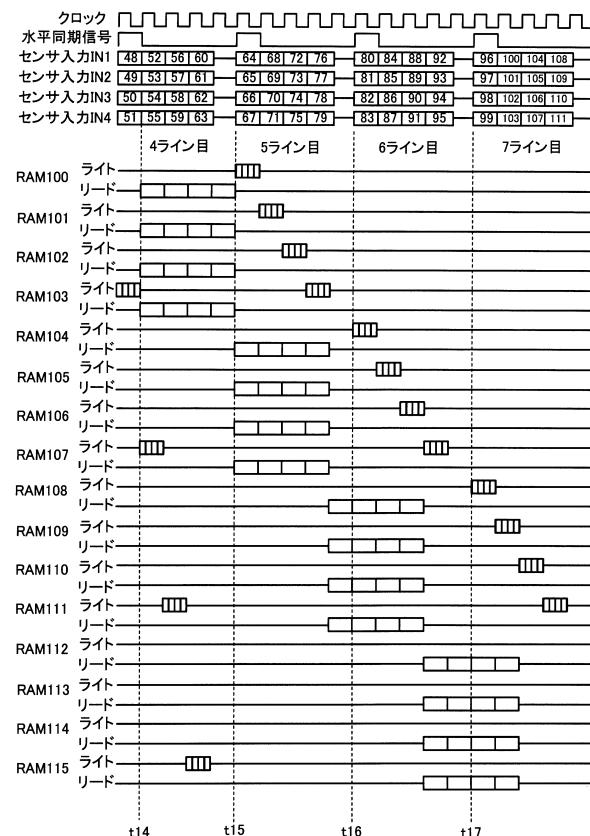

【図17】並列数N=4のときのライン分割処理部によるデータの並べ替え処理の一例の様子を示すタイミングチャートである（その2）。

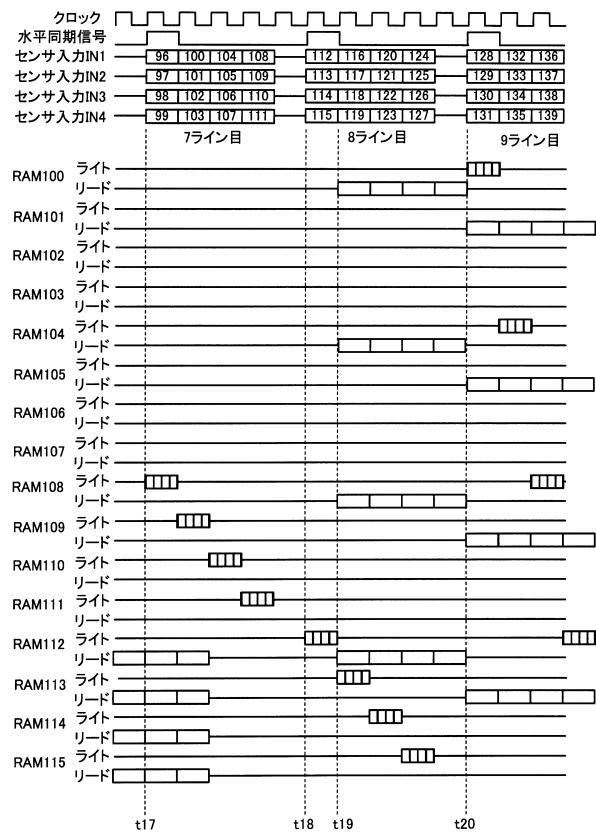

【図18】並列数N=4のときのライン分割処理部によるデータの並べ替え処理の一例の様子を示すタイミングチャートである（その3）。

【図19】3×3個のRAMに対するライトとリードの制御例を示す図である。 20

【発明を実施するための形態】

【0011】

以下、発明を実施するための形態を、図面を参照しつつ説明する。

（第1の実施の形態）

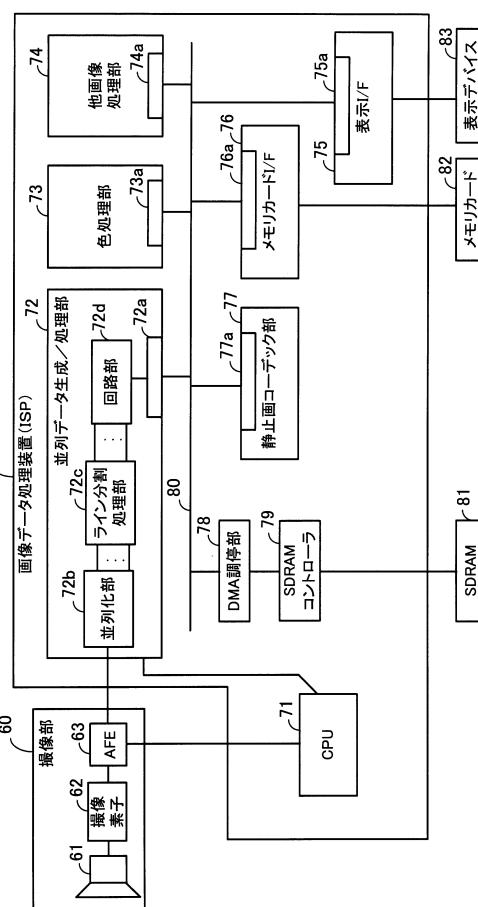

図1は、第1の実施の形態の画像データ処理装置と画像データ処理方法の一例を示す図である。

【0012】

画像データ処理装置10は、並列化部11、N×N（N=2、ただし図1の例ではN=4）個の記憶部12（ただし、後述するように2つの記憶部12a, 12bは他のものとは種類が異なるため別の符号を付している）を有している。さらに、画像データ処理装置10は、書き込み制御部13、読み出し制御部14、入力信号制御部15、出力信号制御部16、回路部17を有している。以下の説明では、記憶部12, 12a, 12b、書き込み制御部13、読み出し制御部14、入力信号制御部15、出力信号制御部16を含む部分をライン分割処理部20と呼ぶ。 30

【0013】

並列化部11は、撮像部30の撮像素子31から画素データの読み出し順（ラスタ走査順）で、画素データを受け取り、それぞれが、ラスタ走査順に対してN画素ずつ飛び飛びのデータ並びとなるN並列の並列データを生成する。これにより、画像データ処理装置10内の周波数を撮像素子31の周波数の1/Nにすることができる。なお、並列化部11は、たとえば、撮像部30に含まれるようにしてよい。 40

【0014】

ライン分割処理部20は、並列化部11から出力される各並列出力のデータを、後段の回路部17で処理できるようにラスタ走査順に並び替え、ラスタ走査順に並び変えられたN並列の画素データを出力する。

【0015】

ライン分割処理部20内の、N×N個の記憶部12, 12a, 12bは、撮像素子31のN本の読み出しライン（たとえば、水平方向の読み出しライン）分の画素データを保持する容量を有している。N=4の場合は、16個の記憶部12, 12a, 12bによって、4ライン分の画素データが保持される。

【0016】

10

20

30

40

50

書き込み制御部 13 は、 $N \times N$  個の記憶部 12, 12a, 12b に含まれる記憶部を、列方向または行方向に  $N$  個選択して、 $N$  画素ずつ並列化部 11 から出力される画素データを書き込む。そして、書き込み制御部 13 は、 $N$  ライン分の画素データの書き込みごとに、記憶部の選択方向を切り替える。

【0017】

読み出し制御部 14 は、 $N$  の倍数ライン目の画素データの書き込み時、その書き込み時における記憶部の選択方向とは異なる方向で  $N$  個の記憶部を選択し、 $N$  ライン分の画素データの並列読み出しを開始する。

【0018】

入力信号制御部 15 は、書き込み制御部 13 と読み出し制御部 14 の制御のもと、行選択信号や列選択信号を生成し、 $N \times N$  個の記憶部 12, 12a, 12b のうち、読み書きを行う記憶部を選択する。

【0019】

出力信号制御部 16 は、書き込み制御部 13 と読み出し制御部 14 の制御のもと、 $N \times N$  個の記憶部 12, 12a, 12b のうち適切な  $N$  個を選択し、 $N$  並列の画素データを出力し、後段の回路部 17 に供給する。

【0020】

なお、図 1 の例では、並列化部 11 と  $N \times N$  個の記憶部 12, 12a, 12b とを接続するデータ線や、入力信号制御部 15 及び出力信号制御部 16 と  $N \times N$  個の記憶部 12, 12a, 12b とを接続する信号線などは、図示を省略している。

【0021】

以下、第 1 の実施の形態の画像データ処理装置 10 の動作の一例を説明する。

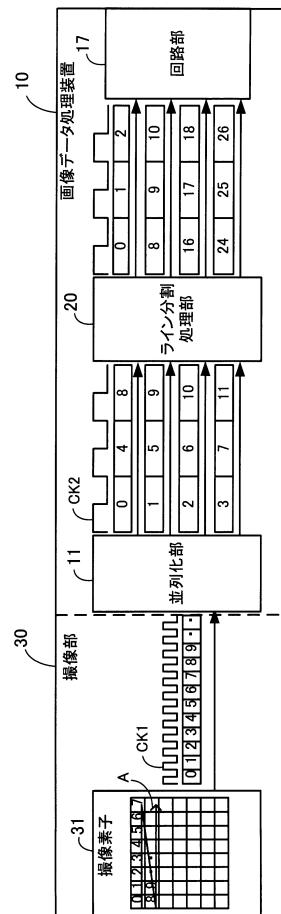

図 2 は、画像データ処理装置が 4 画素ずつデータを受け取り 4 並列で処理を行う例を示す図である。

【0022】

図 2 では、クロック CK 1 に同期して撮像素子 31 から矢印 A で示されている読み出し順（ラスタ走査順）で読み出される画素データが、0 ~ 26 で示されている。画像データ処理装置 10 では、撮像部 30 でのクロック CK 1 の 1/4 の速さのクロック CK 2 に同期した動作が行われる。

【0023】

並列化部 11 は、ラスタ走査順で撮像素子 31 から読み出される画素データを、図 2 のような 4 つの並列データとして出力する。このとき各並列データは、0, 4, 8, ..., 1, 5, 9, ... のように、ラスタ走査順に対して、4 画素ずつ飛び飛びの画素データとなっているため、ライン分割処理部 20 で、各並列データがラスタ走査順になるように並べ替えられて、後段の回路部 17 に供給される。

【0024】

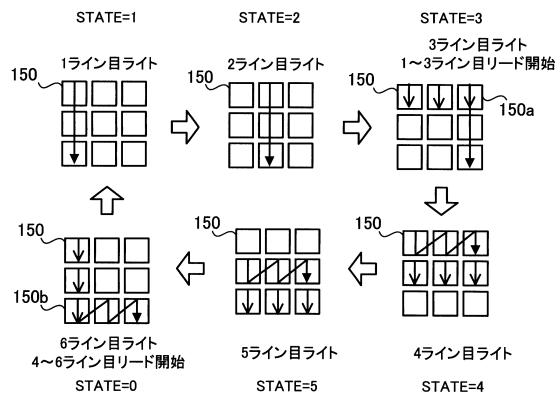

図 1 の下側には、画像データ処理装置 10 が 4 画素ずつデータを受け取り 4 並列で処理を行う際の、ライン分割処理部 20 における画素データのライトとリードの制御例が示されている。4 × 4 個の記憶部 12, 12a, 12b に対してライトまたはリードが行われる 8 つの状態の例が示されている。

【0025】

書き込み制御部 13 は、4 × 4 個の記憶部 12, 12a, 12b から、列方向に記憶部を順に選択して、並列化部 11 から 4 画素ずつ並列に入力される画素データを書き込ませる。これにより、まずは撮像素子 31 の水平方向の読み出しラインの画素データが、1 ライン目から順に、列方向に選択された記憶部にライトされる。

【0026】

そして、書き込み制御部 13 は、4 ライン分の画素データのライトが終わると、記憶部の選択方向を、列方向から行方向に切り替えている。また、書き込み制御部 13 は、さらに 4 ライン分の画素データのライトが終わると、記憶部の選択方向を、行方向から列方向に切り替えている。

10

20

30

40

50

## 【0027】

読み出し制御部14は、列方向で記憶部を選択しての4ライン目の画素データのライト中に、行方向の4個の記憶部を選択し、1～4ライン目の画素データのリード（並列読み出し）を開始させる。4ライン目の画素データのライト完了時には、1行目の4つの記憶部からのリードが完了する（その理由については後述する）。そのため、すぐにその行の記憶部に5ライン目の画素データをライトすることができる。これによって、読み出されていない1～4ライン目の画素データが、5ライン目の画素データによって上書きされ破壊されることを防ぐことができる。

## 【0028】

また、読み出し制御部14は、行方向で記憶部を選択しての8ライン目の画素データのライト中に、列方向の4個の記憶部を選択し、画素データのリード（並列読み出し）を開始させる。8ライン目の画素データのライト完了時には、1列目の4つの記憶部からのリードが完了する。そのため、すぐにその列の記憶部に9ライン目の画素データをライトすることができる。これによって、読み出されていない5～8ライン目の画素データが、9ライン目の画素データによって上書きされ破壊されることを防ぐことができる。

10

## 【0029】

撮像素子31の9ライン目以降の画素データに対しても同様の制御が行われる。

以上のような制御によれば、 $4 \times 4$ 個の記憶部12, 12a, 12bのうち、記憶部12a, 12b以外の記憶部12は、ライトアクセスとリードアクセスが異なるタイミングで発生する。そのため、記憶部12には、ライトとリードを共通の端子で行う記憶装置（たとえば、1RWなどの1ポートRAM）が用いられる。一方、4の倍数ライン目の画素データの書き込み中に指定される最初のアドレスがある記憶部12a, 12bは、ライトとリードを別々の端子を用いて行う記憶装置（たとえば、1R1Wなどの2ポートRAM）が用いられる。

20

## 【0030】

これにより、記憶部12, 12a, 12bを全て、1R1Wなどの2ポートRAMを用いる場合よりも回路面積を削減できる。並列数が多くなるほど、2ポートRAMの割合を減らせるので、回路面積の削減効果は大きい。また、前のラインのリードが完了していないにも関わらず、新たなラインのデータのライトが同じアドレス上で発生することも抑制できるので、前のラインの画素データが上書きされ破壊されてしまうことを防ぐことができる。

30

## 【0031】

以下比較例として、4画素ずつデータを受け取り4並列で処理を行う他の画像データ処理方法の例を示す。

（比較例）

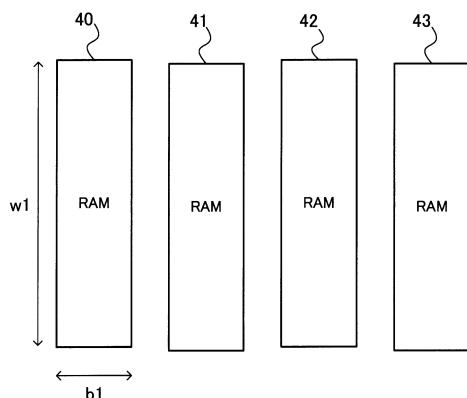

図3は、並べ替え処理に用いられるRAMの例を示す図である。

## 【0032】

4画素ずつデータを受け取り、4並列で処理を行う際に、第1の実施の形態の画像データ処理装置10と異なり、図3に示すように、4つのRAM40～43を用いる場合を考える。各RAM40～43は、撮像素子31の水平方向の1ライン分の画素データを保持する。各RAM40～43のビット数b1は4画素分である。また、各RAM40～43のワード数w1（1ワードは4画素分）は最大の水平方向画素サイズの1/4である。

40

## 【0033】

このようなRAM40～43に対するライト及びリードは、たとえば、以下のようになる。

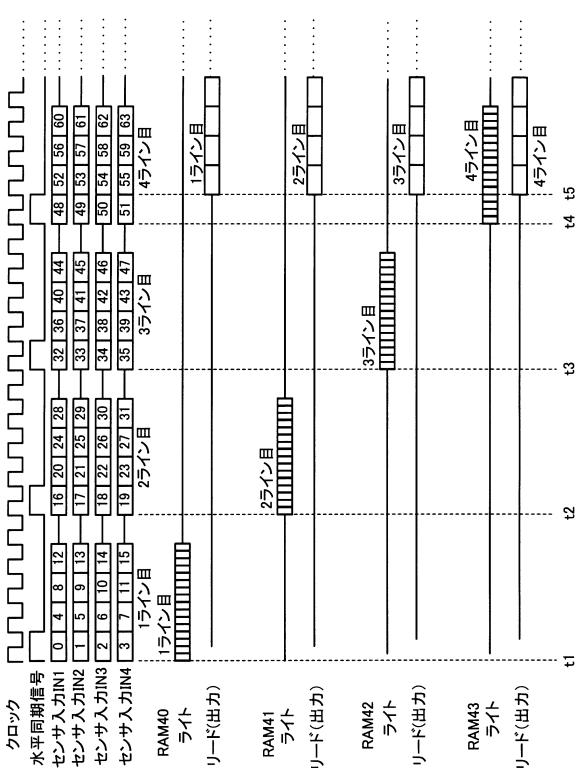

図4、図5は、4つのRAMを用いた並べ替え処理の一例の様子を示すタイミングチャートである。

## 【0034】

上から、画像データ処理装置10のクロック、水平同期信号、RAM40～43へ供給される4並列の画素データ（センサ入力IN1～IN4）、各RAM40～43のライト

50

及びリード(出力)の様子が示されている。

【0035】

水平同期信号がL(Low)レベルからH(High)レベルに立ち上ると(タイミングt1)、撮像素子31の1ライン目の画素データが並列化部11で並列データとなり、図4のようなセンサ入力IN1～IN4としてRAM40にライトされる。なお、水平同期信号は次のクロックの立ち上がりでLレベルに立ち下がる。すなわち、水平同期信号は、1クロック周期分のパルス幅をもつパルスである。

【0036】

撮像素子31からの1ライン目の画素データのリード後、わずかなブランクを挟み水平同期信号のパルスが生成されると(タイミングt2)、2ライン目の画素データが、並列化部11で並列データとなり、図4のようなセンサ入力IN1～IN4としてRAM41にライトされる。

10

【0037】

タイミングt3, t4でも同様に、水平同期信号のパルスが生成されると、3ライン目及び4ライン目の画素データのRAM42, 43へのライトが行われる。ただし、次の5ライン目の画素データをライト可能な領域を確保するために、4ライン目の1ワード分の画素データが書き込まれた時点(タイミングt5)で、1～4ライン目の画素データの並列読み出しが開始される。

【0038】

しかしながら、タイミングt6で、5ライン目の画素データのライトが開始されると、RAM40では、1ライン目の画素データのリードが完了しておらず、5ライン目の画素データによって、リードが済んでいないのに上書きされる画素データが発生する。

20

【0039】

タイミングt7に関しても同様に、6ライン目の画素データのライトが開始されると、RAM41では、2ライン目の画素データのリードが完了しておらず、6ライン目の画素データによって、リードが済んでいないのに上書きされる画素データが発生する。

【0040】

このように、4つのRAM40～43を用いた並列データの並べ替え処理では、ライトがリードを追い越してしまうことによるデータの上書きにより、データ破壊が生じる。そのため、RAMの数を、たとえば、2つ増やすことが考えられるが、回路規模が増加する。また、この比較例のような並べ替え処理では、タイミングt4～t6のように、ライトとリードが同時に発生するため、RAM40～43は、1R1Wなどの2ポートRAMが用いられる。これによっても回路規模が増加する。このようなデータ破壊は、並列数が3以上になると生じやすくなる。

30

【0041】

これに対して、第1の実施の形態の画像データ処理装置10では、N×N個の記憶部12, 12a, 12bを用いて、前述したようなライト及びリードの制御を行うことで、データ破壊の発生を抑制できる。また、記憶部12a, 12b以外の大部分の記憶部12に1ポートRAMを用いることができる。そのため、並列の画素データの並べ替え時のデータ破壊の発生を小規模な回路で抑制できる。

40

【0042】

以下、第2の実施の形態の画像データ処理装置を説明する。

(第2の実施の形態)

図6は、第2の実施の形態の画像データ処理装置が適用される撮像装置の一例を示す図である。

【0043】

撮像装置50は、撮像部60、画像データ処理装置70を有している。

撮像部60は、レンズや反射鏡などの撮像光学系61、CCD(Charge Coupled Device)などである撮像素子62、アンプやフィルタ、ADC(Analog to Digital Converter)などを含むアナログフロントエンド63(図6ではAFEと表記されている)を有する

50

。

## 【0044】

画像データ処理装置70は、たとえば、ISPであり、CPU(Central Processing Unit)71により各部が制御される。画像データ処理装置70は、並列データ生成/処理部72、色処理部73、他画像処理部74、表示インターフェース(以下表示I/Fと表記する)75、メモリカードI/F76、静止画コーデック部77、DMA(Direct Memory Access)調停部78、SDRAM(Synchronous Dynamic Random Access Memory)コントローラ79を有している。また、並列データ生成/処理部72、色処理部73、他画像処理部74、表示I/F75、メモリカードI/F76、静止画コーデック部77は、DMAコントローラ72a, 73a, 74a, 75a, 76a, 77aを有しており、内部バス80に接続されている。10

## 【0045】

並列データ生成/処理部72は、撮像部60に接続されており、並列化部72b、ライン分割処理部72c、回路部72dをさらに有している。これらは、たとえば、前述した図1の、並列化部11、ライン分割処理部20、回路部17と同様の機能を行う。回路部72dは、DMAコントローラ72aに接続されている。また、回路部72dとしては、たとえば、シェーディング補正部、欠陥画素補正部、ノイズリダクション部、AE(Auto Exposure)/AF(Auto Focus)/AWB(Auto White Balance)検波部などがある。

## 【0046】

色処理部73は、撮像画像の色に関する処理を行い、他画像処理部74は、その他の種々画像処理を行う。表示I/F75とメモリカードI/F76は、画像データ処理装置70と、表示デバイス83及びメモリカード82との間で情報の送受信を行う。静止画コーデック部77は、たとえば、JPEG(Joint Photographic Experts Group)など種々の符号化方式でのエンコードやデコードを行う。DMA調停部78は、DMAコントローラ72a, 73a, 74a, 75a, 76a, 77aからのデータ転送の要求に対して内部バス80の使用権の調停を行う。また、DMA調整部78は、SDRAM81を制御するSDRAMコントローラ79に接続されている。なお並列化部72bは、撮像部60に含まれていてもよい。20

## 【0047】

以下、並列データ生成/処理部72のライン分割処理部72cの一例を説明する。30

(ライン分割処理部72c)

図7は、ライン分割処理部の一例を示す図である。

## 【0048】

ライン分割処理部72cは、RAM周辺部90、書き込み制御部91、読み出し制御部92を有している。

RAM周辺部90は、記憶領域90a、入力信号制御部90b、出力信号制御部90cを有している。記憶領域90aは、生成する並列データの並列数(N)に対応して、 $N \times N$ 個のRAMを有している。記憶領域90aには、並列化部72bで並列化されたN並列の画素データや、ライトアドレス(WAD)や、リードアドレス(RAD)が入力される。40

## 【0049】

入力信号制御部90bは、書き込み制御部91と読み出し制御部92の制御のもと、行選択信号や列選択信号を生成し、 $N \times N$ 個のRAMのうち、読み書きを行う記憶部を選択する。

## 【0050】

出力信号制御部90cは、書き込み制御部91と読み出し制御部92の制御のもと、 $N \times N$ 個のRAMのうち適切なN個を選択し、N並列の画素データを出力し、後段の回路部72dに供給する。

## 【0051】

書き込み制御部91は、STATEカウント用レジスタ91a、WEN生成部91b、50

WADカウント用レジスタ91c、比較部91d、WCNTカウント用レジスタ91e、

START生成部91fを有する。

【0052】

STATEカウント用レジスタ91aは、水平同期信号HDの立ち上がり回数をカウントし、そのカウント値STATEをライト/リード状態として保持する。たとえば、並列数N=4である場合には、図1に示したように8つのライト/リード状態があり、STATEカウント用レジスタ91aは、3ビットの値を保持する。なお、水平同期信号HDは、たとえば、撮像部60とのI/F部(図示せず)で生成される。

【0053】

WEN生成部91bは、水平同期信号HDの立ち上がりに同期してライトイネーブル信号WENをアサートする。 10

WADカウント用レジスタ91cは、ライトイネーブル信号WENがアサートされている間、ライトアドレスWADを、画像データ処理装置70の図示しないクロックに同期して、毎サイクルインクリメントする。

【0054】

比較部91dは、ライトアドレスWADと、選択するRAMを切り替えるアドレスの閾値RAMTHとを比較する。そして比較部91dは、ライトアドレスWADが閾値RAMTHに達すると、WCNTカウント用レジスタ91eに対するイネーブル信号をアサートするとともに、WADカウント用レジスタ91cに、ライトアドレスWADの値をリセットさせる。N=4の場合、像素子62の1水平方向ラインの画素データが、4つのRAMにライトされる。このとき、各RAMに対して同じコラム(列)アドレスまたはロウ(行)アドレスで4画素並列にライトされる。そのため、閾値RAMTHは、像素子62の最大の水平方向画素サイズの1/16の値となる。 20

【0055】

WCNTカウント用レジスタ91eは、比較部91dがイネーブル信号をアサートするごとにカウント値WCNTをインクリメントする。カウント値WCNTは、ライトが行われるRAMを示す。また、WCNTカウント用レジスタ91eは、N回ライトアドレスWADが閾値RAMTHに達すると1ライン分の書き込みが完了したことになるので、ライトイネーブル信号WENをネゲートさせる。 30

【0056】

START生成部91fは、カウント値STATEが“0”または“N”的ときにリード開始信号STARTを生成する。リード開始信号STARTは、たとえば、1ショットのパルスである。 30

【0057】

読み出し制御部92は、REN生成部92a、タイミング調整用カウンタ92b、AND回路92c、RADカウント用レジスタ92d、比較部92e、RCNTカウント用レジスタ92fを有する。 40

【0058】

REN生成部92aは、リード開始信号STARTを受け取ると、リードイネーブル信号RENをアサートする。

タイミング調整用カウンタ92bは、リードイネーブル信号RENがアサートされてから図示しないクロックのNサイクルに1回アサートされ、リードイネーブル信号RENを有効にする信号“1”を送出する。これによって、読み出しのためのRAMアクセスをNサイクルに1回にするタイミングの調整が行われる。 40

【0059】

AND回路92cは、タイミング調整用カウンタ92bから“1”が出力されているときには、リードイネーブル信号RENの値を出力し、タイミング調整用カウンタ92bから“0”が出力されているときには、“0”を出力する。

【0060】

RADカウント用レジスタ92dは、タイミング調整用カウンタ92bが飽和するタイ 50

ミング、つまり、リードイネーブル信号 REN が “1” を出力するタイミングで、リードアドレス RAD をインクリメントする。

【0061】

比較部 92e は、リードアドレス RAD と、選択する RAM を切り替えるアドレスの閾値 RAMTH とを比較する。そして比較部 92e は、リードアドレス RAD が閾値 RAMTH に達すると、RCNT カウント用レジスタ 92f に対するイネーブル信号をアサートするとともに、RAD カウント用レジスタ 92d に、リードアドレス RAD の値をリセットさせる。

【0062】

RCNT カウント用レジスタ 92f は、比較部 92e がイネーブル信号をアサートするごとにカウント値 RCNT をインクリメントする。カウント値 RCNT は、リードが行われる RAM を示す。また、RCNT 用レジスタ 92f は、N 回、リードアドレス RAD が閾値 RAMTH に達すると読み出しが完了したことになるので、リードイネーブル信号 REN をネゲートさせる。

【0063】

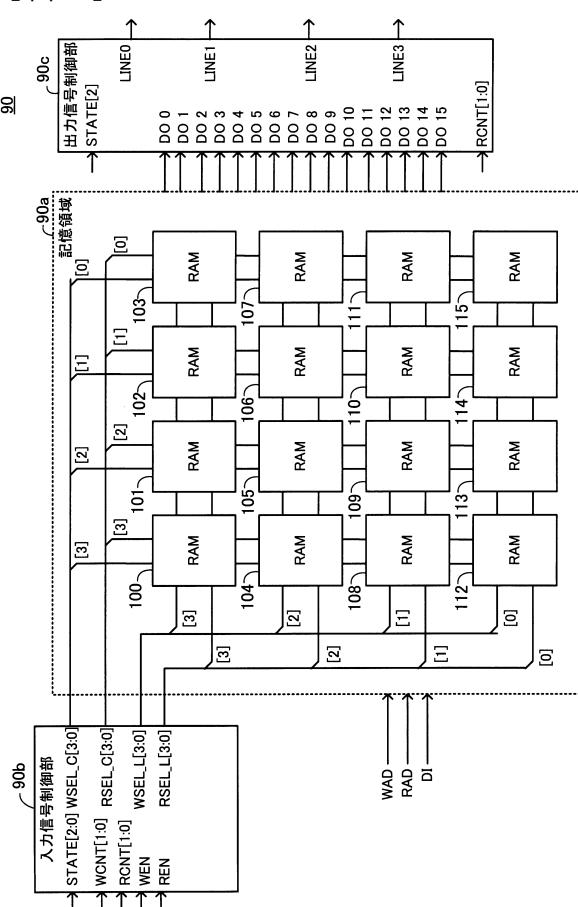

次に、ライン分割処理部 72c の RAM 周辺部 90 の一例を説明する。

(RAM 周辺部 90)

図 8 は、並列数 N = 4 としたときの、RAM 周辺部の一例を示す図である。

【0064】

ライトアドレス WAD、リードアドレス RAD、4 並列の画素データ ( 入力データ DI ) については、全ての RAM 100 ~ 115 に入力され、結線の図示は煩雑となるので省略されている。またそれぞれの RAM 100 ~ 115 からの出力 DO0 ~ 15 の結線の図示も省略されている。

【0065】

入力信号制御部 90b は、STATE カウント用レジスタ 91a の 3 ビットのカウント値 STATE を入力する。また、入力信号制御部 90b は、WCNT カウント用レジスタ 91e の 2 ビットのカウント値 WCNT、RCNT カウント用レジスタ 92f の 2 ビットのカウント値 RCNT、ライトイネーブル信号 WEN、リードイネーブル信号 REN を入力する。入力信号制御部 90b は、これらの信号をもとに、それぞれ 4 ビットの、ライト用の列選択信号 WSEL\_C、行選択信号 WSEL\_L、リード用の列選択信号 RSEL\_C、行選択信号 RSEL\_L を生成して出力する。

【0066】

ライト用の列選択信号 WSEL\_C と、リード用の列選択信号 RSEL\_C の最上位ビット [3] により、RAM 100, 104, 108, 112 が選択され、その次のビット [2] により、RAM 101, 105, 109, 113 が選択される。さらに、その次のビット [1] により、RAM 102, 106, 110, 114 が選択され、最下位ビット [0] により、RAM 103, 107, 111, 115 が選択される。

【0067】

また、ライト用の行選択信号 WSEL\_L と、リード用の行選択信号 RSEL\_L の最上位ビット [3] により、RAM 100, 101, 102, 103 が選択され、その次のビット [2] により、RAM 104, 105, 106, 107 が選択される。さらに、その次のビット [1] により、RAM 108, 109, 110, 111 が選択され、最下位ビット [0] により、RAM 112, 113, 114, 115 が選択される。

【0068】

図 9 は、入力信号制御部の入出力信号の関係の例を示す図である。

図 9 では、入力信号制御部 90b への入力 (input) として、STATE カウント用レジスタ 91a の 3 ビットのカウント値 STATE が示されている。また、入力信号制御部 90b からの出力 (output) として、ライト及びリード用の、列選択信号 WSEL\_C, RSEL\_C、行選択信号 WSEL\_L, RSEL\_L が示されている。

【0069】

10

20

30

40

50

たとえば、カウント値 STATE が“001”的ときは、ライト用の列選択信号 WSEL\_C は“1000”、行選択信号 WSEL\_L は、カウント値 RCNT となる。また、リード用の列選択信号 RSEL\_C は、カウント値 RCNT、行選択信号 RSEL\_L “1111”となる。

【0070】

これによって、ライト時には、RAM100, 104, 108, 112が、カウント値 RCNT がインクリメントされるごとに順に選択される。またリード時には、RAM100～103, 104～107, 108～111, 112～115の順で、カウント値 RCNT がインクリメントされるごとに4つずつ選択される。

【0071】

なお、列選択信号 WSEL\_C と、行選択信号 WSEL\_L については、ライトイネーブル信号 WEN との AND 論理がとられ、列選択信号 RSEL\_C と、行選択信号 RSEL\_L については、リードイネーブル信号REN との AND 論理がとられて出力される。

【0072】

一方、図8の出力信号制御部 90c は、STATE カウント用レジスタ 91a のカウント値 STATE の最上位ビットと、RAM100～115からの出力 D00～D015 と、RCNT カウント用レジスタ 92f のカウント値 RCNT を入力する。そして出力信号制御部 90c は、これらの信号をもとに、4つの並列データ LINE0, LINE1, LINE2, LINE3 を出力する。

【0073】

図10は、出力信号制御部の入出力信号の関係の例を示す図である。

図10では、出力信号制御部 90c への入力として、STATE カウント用レジスタ 91a のカウント値 STATE の最上位ビット STATE [2] 及びカウント値 RCNT が示されている。また、出力信号制御部 90c からの出力として、4つの並列データ LINE0, LINE1, LINE2, LINE3 が示されている。

【0074】

カウント値 STATE の最上位ビット STATE [2] が“0”的ときは、図9に示したように、リード用の列選択信号 RSEL\_C は、カウント値 RCNT となり、行選択信号 RSEL\_L は、“1111”となる。

【0075】

たとえば、カウント値 RCNT が“1000”的場合には、RAM100, 104, 108, 112 が選択されることから、図10に示すように、並列データ LINE0～LINE3 は、出力 D00, D04, D08, D012 の値となる。

【0076】

一方、カウント値 STATE の最上位ビット STATE [2] が“1”的ときは、図9に示したように、リード用の列選択信号 RSEL\_C は、“1111”となり、行選択信号 RSEL\_L は、カウント値 RCNT となる。

【0077】

たとえば、カウント値 RCNT が“1000”的場合には、RAM100, 101, 102, 103 が選択されることから、図10に示すように、並列データ LINE0～LINE3 は、出力 D00, D01, D02, D03 の値となる。

【0078】

以下、記憶領域 90a の一例を説明する。

(記憶領域 90a)

図11は、並列数 N = 4としたときの、記憶領域の例を示す図である。

【0079】

並列数 N = 4とした場合、RAM100～115のうち、同一行方向または同一列方向の4つのRAMにより、撮像素子 62 の水平方向の1ライン分の画素データを保持する。各 RAM100～115 のビット数 b は4画素分である。また、各 RAM100～115 のワード数 w (1ワードは4画素分) は最大の水平方向画素サイズの 1 / 16 である。

10

20

30

40

50

## 【0080】

なお、図8において、RAM103, 112は、ライトアクセス中にリードアクセスが発生するRAMであるため、1R1Wの2ポートRAMが用いられるが、他のRAMについては、1RWの1ポートRAMが用いられる。

## 【0081】

このように、本実施の形態では、2種類のRAMが用いられるが、同様に扱えるように、たとえば、以下のようなI/Fが適用される。

図12は、1RWの1ポートRAMに用いられるRAMI/Fの一例を示す図である。

## 【0082】

RAMI/F120は、AND回路121, 122、OR回路123、インバータ回路124、ビット連結回路125、選択回路126を有している。

AND回路121の2つの入力端子には、ライト用の列選択信号WSEL\_Cと行選択信号WSEL\_Lが入力される。AND回路122の2つの入力端子には、リード用の列選択信号RSEL\_Cと行選択信号RSEL\_Lが入力される。OR回路123の2つの入力端子には、AND回路121, 122の出力信号が入力され、OR回路123の出力信号は、RAM100のチップイネーブル端子CEに入力される。インバータ回路124には、AND回路121の出力信号が入力され、インバータ回路124の出力信号は、RAM100のライトイネーブル端子WEに入力される。

## 【0083】

ビット連結回路125は、AND回路121, 122の出力信号を連結して2ビットの選択信号を選択回路126に供給する。選択回路126は、ライトアドレスWADとリードアドレスRADと値“0”を入力し、入力される選択信号が“10”的ときにはライトアドレスWADを出力し、選択信号が“01”的ときにはリードアドレスRADを出力する。また、選択回路126は、選択信号が“10”, “01”以外の値defのときには、“0”を出力する。選択回路126の出力信号は、RAM100のアドレス端子IAに入力される。その他、RAM100のクロック端子CKには、図示しないクロック供給部からのクロックSROCLKが入力され、ライトデータ入力端子Iには、入力データDIが入力される。また、RAM100のリードデータ出力端子Aから読み出されたリードデータは、出力信号制御部90cに供給される。

## 【0084】

記憶領域90aのその他の1RWの1ポートRAMについても同様のI/Fが用いられる。

図13は、1R1Wの2ポートRAMに用いられるRAMI/Fの一例を示す図である。

## 【0085】

RAMI/F130は、AND回路131, 132、選択回路133, 134を有している。

AND回路131の2つの入力端子には、ライト用の列選択信号WSEL\_Cと行選択信号WSEL\_Lが入力される。AND回路132の2つの入力端子には、リード用の列選択信号RSEL\_Cと行選択信号RSEL\_Lが入力される。AND回路131の出力信号は、RAM103のライトイネーブル端子CEIWに入力されるとともに、選択信号として選択回路133に供給される。AND回路132の出力信号は、RAM103のリードイネーブル端子CERAに入力されるとともに、選択信号として選択回路134に供給される。

## 【0086】

選択回路133は、ライトアドレスWADと値“0”を入力し、入力される選択信号が“1”的ときにはライトアドレスWADを出力し、選択信号が“0”的ときには“0”を出力する。選択回路133の出力信号は、RAM103のライトアドレス端子IWに入力される。

## 【0087】

10

20

30

40

50

選択回路 134 は、リードアドレス R A D と値 “ 0 ” を入力し、入力される選択信号が “ 1 ” のときにはリードアドレス R A D を出力し、選択信号が “ 0 ” のときには “ 0 ” を出力する。選択回路 134 の出力信号は、R A M 103 のリードアドレス端子 R A に入力される。

#### 【 0088 】

その他、R A M 103 のライト用クロック端子 C K I W 及びリード用クロック端子 C K R A には、図示しないクロック供給部からのクロック S R O C L K が入力され、ライトデータ入力端子 I には、入力データ D I が入力される。また、R A M 103 のリードデータ出力端子 A から読み出されたリードデータは、出力信号制御部 90c に供給される。

#### 【 0089 】

1 R 1 W の 2 ポート R A M である R A M 112 についても同様の I / F が用いられる。

図 12、図 13 のような R A M I / F 120, 130 を用いることで、異なるタイプの R A M を同じように扱うことが可能となる。

#### 【 0090 】

次に、本実施の形態のライン分割処理部 72c の動作を説明する。

( ライン分割処理部 72c の動作 )

図 14 は、並列データのライト処理の一例の流れを示すフローチャートである。

#### 【 0091 】

書き込み制御部 91 の W E N 生成部 91b は、水平同期信号 H D が H レベルであるか判定し (ステップ S 10) 、水平同期信号 H D が H レベルである場合には、ライトイネーブル信号 W E N を H レベル (アサート) とする (ステップ S 11) 。これにより、以下の初期化及びモード遷移処理が開始される。

#### 【 0092 】

ライトイネーブル信号 W E N が H レベルとなると、W A D カウント用レジスタ 91c は、ライトアドレス W A D を “ 0 ” にリセットする (ステップ S 12) 。その後、S T A T E カウント用レジスタ 91a は、カウント値 S T A T E をインクリメントし (ステップ S 13) 、W C N T カウント用レジスタ 91e は、カウント値 W C N T を “ 0 ” にリセットする (ステップ S 14) 。なお、カウント値 S T A T E をインクリメントする度に、たとえば、図 1 に示したようなライトとリードの状態が遷移する。N = 4 の場合には、その状態は図 1 に示したように 8 つある。カウント値 S T A T E が “ 1 ” のときは、左上の状態 (1 ライン目をライトする状態) になる。

#### 【 0093 】

その後、R S T A R T 生成部 91f は、カウント値 S T A T E が “ 0 ” か、並列数 N であるか判定し (ステップ S 15) 、その何れかである場合には、リード開始信号 R S T A R T を H レベルとする (ステップ S 16) 。たとえば、並列数 N = 4 の場合、カウント値 S T A T E が “ 4 ” または “ 0 ” になると、図 1 に示したように 4 ライン目または 8 ライン目のライトとともに、リードが開始される。

#### 【 0094 】

カウント値 S T A T E が “ 0 ” でも N でもない場合には、ステップ S 18 の処理が行われる。なお、ステップ S 10 の処理において、水平同期信号 H D が L レベルの場合には、R S T A R T 生成部 91f は、リード開始信号 R S T A R T を L レベルとし (ステップ S 17) 、その後、ステップ S 18 の処理が行われる。

#### 【 0095 】

ステップ S 18 の処理では、W A D カウント用レジスタ 91c は、ライトイネーブル信号 W E N が H レベルであるか否か判定する。ライトイネーブル信号 W E N が L レベルである場合には、ステップ S 10 からの処理が繰り返される。ライトイネーブル信号 W E N が H レベルである場合には、以下のアドレス計算処理が行われる。

#### 【 0096 】

ライトイネーブル信号 W E N が H レベルである場合、ライトが行われ、比較部 91d は、ライトアドレス W A D が、閾値 R A M T H に達したか否かを判定する (ステップ S 19)

10

20

30

40

50

）。ライトアドレスWADが閾値RAMTHに達していない状態（WAD < RAMTH）である場合には、WADカウント用レジスタ91cは、ライトアドレスWADをインクリメントし（ステップS20）、ライトを継続させる。その後、ステップS10からの処理が繰り返される。

【0097】

ライトアドレスWADが閾値RAMTHに達した場合、N×N個のRAMの1つに対するライトが終わる。そのとき、WCNTカウント用レジスタ91eは、カウント値WCNTがN-1であるか否か判定する（ステップS21）。ここでは、各行または各列のN個のRAMに対して、撮像素子62の水平方向1ライン分の画素データのライトを終えたか否かが判定される。

10

【0098】

そして、カウント値WCNTがN-1である場合には、WCNTカウント用レジスタ91eは、WEN生成部91bにライトイネーブル信号WENをLレベルにさせる（ステップS22）。これによりライトが停止する。カウント値WCNTがN-1ではない場合には、WCNTカウント用レジスタ91eは、カウント値WCNTをインクリメントする（ステップS23）。これにより、次のRAMが選択される。ステップS22, S23の後、WADカウント用レジスタ91cは、ライトアドレスWADを“0”にリセットする（ステップS24）。その後、ステップS10からの処理が繰り返される。

【0099】

なお、上記の処理中において、たとえば、画像データ処理装置70の電源がオフになると、ライト処理が終了する。

20

図15は、並列データのリード処理の一例の流れを示すフローチャートである。

【0100】

読み出し制御部92のREN生成部92aは、リード開始信号STARTがHレベルであるか判定し（ステップS30）、リード開始信号STARTがHレベルである場合には、リードイネーブル信号RENをHレベルとする（ステップS31）。これにより、まず、以下の初期化処理が開始される。

【0101】

初期化処理では、RADカウント用レジスタ92dは、リードアドレスRADを“0”にリセットし（ステップS32）、RCNTカウント用レジスタ92fは、カウント値RCNTを“0”にリセットする（ステップS33）。ステップS33の処理後、またはステップS30の処理で、リード開始信号がLレベルであったときには、ステップS34の処理が行われる。

30

【0102】

ステップS34の処理では、RADカウント用レジスタ92dは、リードイネーブル信号RENがHレベルであるか否か判定する。リードイネーブル信号RENがLレベルである場合には、ステップS30からの処理が繰り返される。リードイネーブル信号RENがHレベルである場合には、以下のアドレス計算処理が行われる。

【0103】

リードイネーブル信号RENがHレベルである場合、比較部92eは、リードアドレスRADが、閾値RAMTHに達したか否かを判定する（ステップS35）。リードアドレスRADが閾値RAMTHに達していない状態（RAD < RAMTH）である場合には、タイミング調整用カウンタ92bは、カウント値がN-1であるか否か判定する（ステップS36）。カウント値がN-1である場合、リードを開始させるために、RADカウント用レジスタ92dは、リードアドレスRADをインクリメントし（ステップS37）、タイミング調整用カウンタ92bはカウント値をリセットする（ステップS38）。カウント値がN-1に達していない場合には、タイミング調整用カウンタ92bは、リードを開始させるタイミングを調整するためのカウント値をインクリメントする（ステップS39）。ステップS38及びステップS39の処理後は、ステップS30からの処理が繰り返される。

40

50

## 【0104】

リードアドレス R A D が、閾値 R A M T H に達した場合、1列または1行の N 個の R A M のリードが完了する。このとき、R C N T カウント用レジスタ 92f は、カウント値 R C N T が N - 1 であるか否か判定する（ステップ S 4 0）。カウント値 R C N T が N - 1 である場合には、N × N 個の R A M に対する N ライン分のリードが終わる。そのとき、R C N T カウント用レジスタ 92f は、R E N 生成部 92a にリードイネーブル信号 R E N を L レベルにさせる（ステップ S 4 1）。カウント値 R C N T が N - 1 に達していない場合には、R C N T カウント用レジスタ 92f は、カウント値 R C N T をインクリメントする（ステップ S 4 2）。ステップ S 4 1 及びステップ S 4 2 の処理後は、R A D カウント用レジスタ 92d は、リードアドレス R A D をリセットする（ステップ S 4 3）。その後、ステップ S 3 0 からの処理が繰り返される。これにより、次の行または列の N 個の R A M のリードが行われる。10

## 【0105】

なお、上記の処理中において、たとえば、画像データ処理装置 70 の電源がオフになると、リード処理が終了する。

次に、並列数 N = 4 のときの、ライン分割処理部 72c によるデータの並べ替え処理の一例を示す。

## 【0106】

図 16、図 17、図 18 は、並列数 N = 4 のときのライン分割処理部によるデータの並べ替え処理の一例の様子を示すタイミングチャートである。20

上から、画像データ処理装置 70 のクロック、水平同期信号、ライン分割処理部 72c に入力される 4 並列の画素データ（センサ入力 I N 1 ~ I N 4）、各 R A M 1 0 0 ~ 1 1 5 のライト及びリードの様子が示されている。

## 【0107】

1 クロック周期の水平同期信号のパルスが生成されると（タイミング t 1 0）、撮像素子 62 から 1 ライン目の画素データが並列化部 72b で並列データとなる。そして、図 16 に示されるようなセンサ入力 I N 1 ~ I N 4 として、まずは列方向の R A M 1 0 0, 1 0 4, 1 0 8, 1 1 2 の順に 4 画素ずつライトされる。

## 【0108】

1 ライン目の 16 画素がライトされ、次に水平同期信号のパルスが生成されると（タイミング t 1 1）、2 ライン目の画素データが並列化部 72b で並列データとなる。そして、センサ入力 I N 1 ~ I N 4 として、2 列目の R A M 1 0 1, 1 0 5, 1 0 9, 1 1 3 の順に 4 画素ずつライトされる。30

## 【0109】

タイミング t 1 2 でも同様に、水平同期信号のパルスが生成されると、3 ライン目の画素データが、3 列目の R A M 1 0 2, 1 0 6, 1 1 0, 1 1 4 の順に 4 画素ずつライトされる。

## 【0110】

タイミング t 1 3 において、水平同期信号のパルスが生成されると、4 ライン目の画素データが、4 列目の R A M 1 0 3, 1 0 7, 1 1 1, 1 1 5 の順に 4 画素ずつライトされるが、1 ワード目のライトが完了した時点でリードが開始される（タイミング t 1 4）。40

## 【0111】

タイミング t 1 4 から開始されるリードは、行方向の 4 個の R A M 1 0 0 ~ 1 0 3 が同時に選択され、タイミング t 1 4 までの間にライトされた画素データが並列にリードされる。

## 【0112】

タイミング t 1 5 からは、ライト時の R A M の選択方向が列方向から行方向に変わる。タイミング t 1 5 において、水平同期信号のパルスが生成されると、5 ライン目の画素データが、リードが完了した 1 行目の R A M 1 0 0 ~ 1 0 3 に順にライトされる。また、1 行目の R A M 1 0 0 ~ 1 0 3 からのリードが完了すると、連続して 2 行目の R A M 1 0 4 50

～107からのリード、3行目のRAM108～111からのリード、4行目のRAM112～115からのリードが行われる。

【0113】

タイミングt16において、水平同期信号のパルスが生成されると、6ライン目の画素データが、リードが完了した2行目のRAM104～107に順にライトされる。同様に、タイミングt17において、水平同期信号のパルスが生成されると、7ライン目の画素データが、リードが完了した3行目のRAM108～111に順にライトされる。

【0114】

タイミングt18において、水平同期信号のパルスが生成されると、8ライン目の画素データが、リードが完了した4行目のRAM112～115に順にライトされる。また、1ワード目のライトが完了した時点でリードが開始される（タイミングt19）。

10

【0115】

タイミングt19から開始されるリードは、RAMの選択方向が行方向から列方向に変わり、まず、列方向の4個のRAM100, 104, 108, 112が同時に選択され、タイミングt19までの間にライトされた画素データが並列にリードされる。

【0116】

一方、4行目のRAM112～115に対するライトが完了し、次に、タイミングt20において、水平同期信号のパルスが生成されると、9ライン目の画素データが、リードが完了した1列目のRAM100, 104, 108, 112に順にライトされる。つまり、ライトされるRAMの選択方向が、行方向から列方向に変わる。

20

【0117】

なお、RAM100, 104, 108, 112のリードが完了すると、連続して2列目のRAM101, 105, 109, 113のリードが行われる。

以降も同様のライト及びリードが行われる。

【0118】

このような処理により、ラスタ走査順ではなく飛び飛びの順序であった各並列データ（センサ入力IN1～IN4）のデータの順序が並び替えられる。そして、それぞれがラスタ走査順のデータ並びとなる4つの並列データLINE0, LINE1, LINE2, LINE3として出力される。

30

【0119】

以上説明してきた、画像データ処理装置70及び画像データ処理方法によれば、撮像素子62からリードされるデータをN（2）並列で処理することができるため、撮像素子62の動作周波数の1/Nで処理が可能となる。

【0120】

また、並列数N=4としても、図16～図18に示したように、4つのRAMのリードが完了してからそのRAMに対するライトが行われるため、リードが完了していないにも関わらず、データを上書きしてしまうということがない。

【0121】

なお、図16～図18などでは、撮像素子62からのリードにおいて、ラインとラインの間の期間（ブランク）を、最小の1サイクル（クロック1周期分）として説明したが、実際の撮像素子62からのリードでは、数10サイクル以上のブランクが含まれる。リードは一度スタートすると各ラインのライトタイミングに関係なく、図16～図18に示したように水平画素サイズ分のサイクルをかけて一気に行われる。ブランクのサイクル数によっては、図16～図18に示したよりも早いタイミングでリードが完了するが、最小のブランクでも図16～図18に示したように、ライトがリードを追い越すことはないのでデータの上書きによる破壊は起こらない。

40

【0122】

また、たとえば、N=4のときは、図8、図11などに示したように4×4のRAM100～115は、4ライン分の画素データを保持できる容量をもつ。そのため、データ破壊を回避するために、6ライン分の画素データを保持するようなRAMを用いる場合より

50

もRAM容量の増加を抑えられる。

【0123】

また、図16～図18に示したように、RAM103とRAM112以外のRAMでは、ライトとリードが独立して行われている。RAM103とRAM112は、ライトアクセスの際にリードアクセスが生じるため、1R1Wのような2ポートRAMが用いられるが、その他のRAMには1RWのような1ポートRAMを用いることができる。1ポートRAMは、2ポートRAMに比べて面積がかなり小さいため、面積の増加を抑えることができる。

【0124】

なお、図16～図18では、リードは4, 8ライン目のライトに対して、1サイクル遅れて開始されているが、数サイクル遅れて開始されることも考えられる。その場合、たとえば、リードが、図17に示したタイミングt15で終了せず、RAM103, 112以外でもライトとリードの同時アクセスが発生する可能性がある。しかし、前述したブランクがライトとリードの開始タイミングのずれ分のサイクル数よりも大きければ、そのようなRAMのライトとリードの同時アクセスは発生しない。ライトとリードの開始タイミングのずれは1ワード分のライトを待つだけの数サイクル分である（図16～図18では1サイクル分）。もともと他の回路での処理のために、ブランクは数10サイクルである。

【0125】

このため、RAM103, 112以外のRAMではライトとリードの同時アクセスは発生しないものとすることができる。

このように、本実施の形態の画像データ処理装置70及び画像データ処理方法によれば、小規模な回路で画素データを適切に並列化できる。

【0126】

RAMに関してはプロセスによりサイズが異なるが、一例として65nmテクノロジー、水平方向最大サイズ=6784画素、1画素=14ビットとしたとき、1ライン分の1R1Wの容量は7Mバイトである。たとえば、2並列処理を行う場合に、2ライン分の1R1WのRAMを用いると、 $7 \times 2 = 14$ Mバイトの容量となる。4並列処理を行う場合に、データ破壊を回避するために、6ライン分の画素データを保持するように、1R1WのRAMを6つ使用すると、 $7 \times 6 = 42$ Mバイトの容量となる。

【0127】

これに対し、本実施の形態の画像データ処理装置70において4並列処理を行う場合、RAM100～115は、それぞれ1/4ライン分の画素データを保持し、容量は1R1WのRAMで1.7Mバイト、1RWのRAMで0.9Mバイトとなる。前述したように16個のRAM100～115のうち、RAM103, 112以外は、1RWのRAMを適用できるので、トータルの容量は、 $1.7 \times 2 + 0.9 \times 14 = 16$ Mバイトとなる。このように、1R1WのRAMを6つ使用する場合よりも大幅に、RAM容量を削減でき、面積を小さくすることができる。また、2並列処理を行うために、2ライン分の1R1WのRAMを使う場合に対しても、4並列処理を行っても、本実施の形態の画像データ処理装置70によれば14%の容量増加に抑えることができる。

【0128】

以上、実施の形態に基づき、本発明の画像データ処理装置及び画像データ処理方法の一観点について説明してきたが、これらは一例にすぎず、上記の記載に限定されるものではない。

【0129】

たとえば、上記では、N並列処理の例として、主にN=4の場合について説明したが、N=2, 3でもN=5でも同様に、本発明を適用できる。

以下にN=3の場合、すなわち画像データ処理装置70が3画素ずつデータを受け取り3並列で処理を行う際の、ライン分割処理部72cにおける画素データのライトとリードの制御例を説明する。

【0130】

10

20

30

40

50

図19は、3×3個のRAMに対するライトとリードの制御例を示す図である。

図19には、3×3個のRAMに対してライトまたはリードが行われる6つの状態の例が示されている。状態は、前述したカウント値STATEの値で表されている。

#### 【0131】

3×3個のRAM150の各列または各行の3つのRAM150により、撮像素子62の1ライン分の画素データが保持できる。

書き込み制御部91は、3×3個のRAM150から、列方向にRAM150を順に選択して、並列化部72bから3画素ずつ並列に入力される画素データを書き込ませる。これにより、まずは撮像素子62の水平方向の読み出しラインの画素データが、1ライン目から順に、列方向に選択されたRAM150にライトされる。

10

#### 【0132】

そして、書き込み制御部91は、3ライン分の画素データのライトが終わると、RAM150の選択方向を、列方向から行方向に切り替えている。また、書き込み制御部91は、さらに3ライン分の画素データのライトが終わると、RAM150の選択方向を、行方向から列方向に切り替える。

#### 【0133】

読み出し制御部92は、列方向でRAM150を選択しての3ライン目の画素データのライト中(STATE=3)に、行方向の3個のRAM150を選択し、1~3ライン目の画素データのリードを開始させる。3ライン目の画素データのライト完了時には、1行目の3つのRAMからのリードを完了させる。そのため、すぐにその行のRAM150に4ライン目の画素データをライトすることができる。

20

#### 【0134】

また、読み出し制御部92は、行方向でRAM150を選択しての6ライン目の画素データのライト中(STATE=0)に、列方向の3個のRAM150を選択し、画素データのリードを開始させる。6ライン目の画素データのライト完了時には、1列目の3つのRAM150からのリードが完了する。そのため、すぐにその列のRAM150に7ライン目の画素データをライトすることができる。

#### 【0135】

撮像素子62の7ライン目以降の画素データに対しても同様の制御が行われる。

以上のような制御によれば、3×3個のRAM150のうち、カウント値STATE=3, 0でライトアクセスとリードアクセスが同じタイミングで行われるRAM150a, 150b以外のRAM150は、ライトとリードが異なるタイミングで行われる。そのため、RAM150a, 150b以外のRAM150は、1RWなどの1ポートRAMを用いることができるため、回路面積を小さくできる。また、前のラインのリードが完了していないにも関わらず、新たなラインのデータのライトが同じアドレス上で発生することも抑制できるので、前のラインの画素データが上書きされてしまうことを防ぐことができる。

30

#### 【符号の説明】

#### 【0136】

10 画像データ処理装置

40

11 並列化部

12, 12a, 12b 記憶部

13 書き込み制御部

14 読み出し制御部

15 入力信号制御部

16 出力信号制御部

17 回路部

20 ライン分割処理部

30 撮像部

31 撮像素子

50

【図1】

【図2】

【図3】

【図4】

【 図 5 】

〔 7 〕

〔 図 6 〕

( 8 )

【図9】

| input | output |        |        |        |        |

|-------|--------|--------|--------|--------|--------|

|       | STATE  | WSEL_C | WSEL_L | RSEL_C | RSEL_L |

| 001   | 1000   | WCNT   |        | RCNT   | 1111   |

| 010   | 0100   | WCNT   |        | RCNT   | 1111   |

| 011   | 0010   | WCNT   |        | RCNT   | 1111   |

| 100   | 0001   | WCNT   |        | 1111   | RCNT   |

| 101   | WCNT   | 1000   |        | 1111   | RCNT   |

| 110   | WCNT   | 0100   |        | 1111   | RCNT   |

| 111   | WCNT   | 0010   |        | 1111   | RCNT   |

| 000   | WCNT   | 0001   |        | RCNT   | 1111   |

【図10】

| input |          | output |       |       |       |

|-------|----------|--------|-------|-------|-------|

| RCNT  | STATE[2] | LINE0  | LINE1 | LINE2 | LINE3 |

| 1000  | 0        | DO0    | DO4   | DO8   | DO12  |

| 0100  | 0        | DO1    | DO5   | DO9   | DO13  |

| 0010  | 0        | DO2    | DO6   | DO10  | DO14  |

| 0001  | 0        | DO3    | DO7   | DO11  | DO15  |

| 1000  | 1        | DO0    | DO1   | DO2   | DO3   |

| 0100  | 1        | DO4    | DO5   | DO6   | DO7   |

| 0010  | 1        | DO8    | DO9   | DO10  | DO11  |

| 0001  | 1        | DO12   | DO13  | DO14  | DO15  |

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(56)参考文献 特開平03-069090 (JP, A)

特開平06-189080 (JP, A)

特開平11-145851 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 6 T 1 / 0 0 - 9 / 4 0