(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-121663

(P2006-121663A)

(43) 公開日 平成18年5月11日(2006.5.11)

(51) Int.C1.

HO4L 7/04

(2006.01)

F 1

HO4L 7/04

B

テーマコード(参考)

5KO47

審査請求 未請求 請求項の数 31 O L 外国語出願 (全 28 頁)

(21) 出願番号 特願2005-256873 (P2005-256873)

(22) 出願日 平成17年9月5日 (2005.9.5)

(31) 優先権主張番号 0419625.9

(32) 優先日 平成16年9月3日 (2004.9.3)

(33) 優先権主張国 英国(GB)

(特許庁注: 以下のものは登録商標)

1. イーサネット

(71) 出願人 593081408

ソニー・ユナイテッド・キングダム・リミテッド

Sony United Kingdom Limited

イギリス国 サリー, ウエーブリッジ, ブルックランズ, ザ ハイツ(番地なし)

(74) 代理人 100067736

弁理士 小池 晃

(74) 代理人 100086335

弁理士 田村 榮一

(74) 代理人 100096677

弁理士 伊賀 誠司

最終頁に続く

(54) 【発明の名称】データ伝送

(57) 【要約】 (修正有)

【課題】通信リンクを介して、送信ノードと受信ノードとの間で通信を行うデータ通信システムの提供。

【解決手段】送信ノードは、通信リンクの各伝送バスを介して、少なくとも2つのストリーミングデータ信号からのデータを送信するデータ送信手段と、通信リンクを介して、少なくとも2つのベースクロック信号のタイミング情報を送信するタイミング送信手段と、各伝送バスと、対応するベースクロック信号の1つとの間の各関係を特定し、伝送バスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信する。受信ノードは、通信リンクの伝送バスからデータを受信するデータ受信手段と、コンフィグレーションデータに応じてベースクロック信号のタイミング情報を処理し、各伝送バスに対応する各サンプリングクロックを生成する処理手段と、サンプリングクロックを各伝送バスからのデータに関連付け、ストリーミングデータ信号を再生する。

【選択図】 図5

**【特許請求の範囲】****【請求項 1】**

通信リンクの各伝送バスを介して、少なくとも 2 つのストリーミングデータ信号からのデータを送信するデータ送信手段と、

上記通信リンクを介して、少なくとも 2 つのベースクロック信号のタイミング情報を送信するタイミング送信手段と、

上記各伝送バスと、対応する上記ベースクロック信号の 1 つとの間の各関係を特定し、該伝送バスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信するコンフィグレーション送信手段とを有する送信ノードと、

上記通信リンクの上記伝送バスからデータを受信するデータ受信機と、

上記コンフィグレーションデータに応じて上記ベースクロック信号の上記タイミング情報を処理し、各伝送バスに対応する各サンプリングクロックを生成するプロセッサと、

上記コンフィグレーションデータに基づいて、上記サンプリングクロックを上記各伝送バスからのデータに関連付け、上記ストリーミングデータ信号を再生するロジックとを有する受信ノードとを備えるデータ通信システム。

**【請求項 2】**

上記ストリーミングデータ信号のデータは、上記通信リンクを介して、データフレームによって搬送されることを特徴とする請求項 1 記載のデータ通信システム。

**【請求項 3】**

上記タイミング情報は、上記データフレームのヘッダに含まれていることを特徴とする請求項 2 記載のデータ通信システム。

**【請求項 4】**

上記コンフィグレーションデータは、上記ストリーミングデータ信号の少なくとも 1 つについて、上記対応するベースクロック信号と、上記各ストリーミングデータ信号のサンプリングレートとの間の関係を指定する乗数を表し、上記プロセッサは、上記ベースクロック信号及び上記乗数に基づいて上記サンプリングクロックを生成することを特徴とする請求項 1 記載のデータ通信システム。

**【請求項 5】**

上記コンフィグレーションデータは、上記ベースクロック信号のそれぞれの公称周波数値を表すことを特徴とする請求項 1 記載のデータ通信システム。

**【請求項 6】**

上記コンフィグレーションデータは、上記少なくとも 2 つのベースクロックのそれぞれの公差の値を含むことを特徴とする請求項 5 記載のデータ通信システム。

**【請求項 7】**

上記コンフィグレーションデータは、上記ストリーミングデータ信号のそれぞれのデータフォーマットを特定するデータを含むことを特徴とする請求項 1 記載のデータ通信システム。

**【請求項 8】**

上記受信ノードは、該受信ノードが上記特定のデータフォーマットを扱うことができるか否かを示す情報を上記送信ノードに送信することを特徴とする請求項 7 記載のデータ通信システム。

**【請求項 9】**

上記コンフィグレーション送信手段は、上記通信リンクの開始時にコンフィグレーションデータを送信することを特徴とする請求項 1 記載のデータ通信システム。

**【請求項 10】**

上記受信ノードは、上記コンフィグレーションデータの受信の確認応答を送信する確認応答送信手段を備えることを特徴とする請求項 9 記載のデータ通信システム。

**【請求項 11】**

上記コンフィグレーション送信手段は、上記確認応答を受信すると、上記コンフィグレーションデータの送信を終了することを特徴とする請求項 1 記載のデータ通信システム。

10

20

30

40

50

**【請求項 1 2】**

上記コンフィグレーションデータは、周期的に送信されることを特徴とする請求項 9 記載のデータ通信システム。

**【請求項 1 3】**

上記通信リンクは、イーサネット通信リンクであることを特徴とする請求項 1 記載のデータ通信システム。

**【請求項 1 4】**

上記タイミング情報は、周期的な基準クロックに関連して定義されることを特徴とする請求項 1 記載のデータ通信システム。

**【請求項 1 5】**

上記周期的な基準クロックは、イーサネット物理層クロックであることを特徴とする請求項 1 3 記載のデータ通信システム。

**【請求項 1 6】**

上記タイミング情報は、所定の基準点に関して、上記対応するベースクロック信号の周波数を所定の整数で除算した値に等しい周波数を有するベース関連クロック信号のエッジ位置を指定することを特徴とする請求項 1 3 記載のデータ通信システム。

**【請求項 1 7】**

上記所定の基準点は、上記送信ノードにおけるフレームヘッダの出力の完了に対応することを特徴とする請求項 1 5 記載のデータ通信システム。

**【請求項 1 8】**

上記タイミング情報は、上記所定の基準点と、上記ベース関連クロック信号の後続するエッジ位置との間の上記周期的な基準クロックのサイクル数を指定することを特徴とする請求項 1 5 記載のデータ通信システム。

**【請求項 1 9】**

上記後続するエッジ位置は、次のベース関連クロック信号のエッジ位置であることを特徴とする請求項 1 6 記載のデータ通信システム。

**【請求項 2 0】**

上記後続するエッジ位置は、1つおいて隣のベース関連クロック信号のエッジ位置であることを特徴とする請求項 1 6 記載のデータ通信システム。

**【請求項 2 1】**

上記ストリーミングデータ信号は、オーディオデータ信号であることを特徴とする請求項 1 記載のデータ通信システム。

**【請求項 2 2】**

データ通信システムにおいて使用する送信ノードにおいて、

通信リンクの各伝送バスを介して、少なくとも2つのストリーミングデータ信号からのデータを送信するデータ送信手段と、

上記通信リンクを介して、少なくとも2つのベースクロック信号のタイミング情報を送信するタイミング送信手段と、

上記各伝送バスと、対応する上記ベースクロック信号の1つとの間の各関係を特定し、該伝送バスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信するコンフィグレーション送信手段とを備える送信ノード。

**【請求項 2 3】**

データ通信システムにおいて使用する受信ノードにおいて、

上記通信リンクの上記伝送バスから、少なくとも2つのベースクロック信号のタイミング情報と、少なくとも2つのストリーミングデータ信号からのデータと、上記各伝送バスと、対応する上記ベースクロック信号の1つとの間の各関係を特定し、該伝送バスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータとを含むデータを受信するデータ受信機と、

上記コンフィグレーションデータに応じて上記ベースクロック信号の上記タイミング情報を処理し、各伝送バスに対応する各サンプリングクロックを生成するプロセッサと、

10

20

30

40

50

上記コンフィグレーションデータに基づいて、上記サンプリングクロックを上記各伝送パスからのデータに関連付け、上記ストリーミングデータ信号を再生するロジックとを備える受信ノード。

【請求項 2 4】

通信リンクを介して、送信ノードと受信ノードとの間で通信を行う通信方法において、上記送信ノードにおいて、

通信リンクの各伝送パスを介して、少なくとも 2 つのストリーミングデータ信号からのデータを送信するステップと、

上記通信リンクを介して、少なくとも 2 つのベースクロック信号のタイミング情報を送信するステップと、

上記各伝送パスと、対応する上記ベースクロック信号の 1 つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信するステップと、

上記受信ノードにおいて、

上記通信リンクの上記伝送パスからデータを受信するステップと、

上記コンフィグレーションデータに応じて上記ベースクロック信号の上記タイミング情報を処理し、各伝送パスに対応する各サンプリングクロックを生成するステップと、

上記コンフィグレーションデータに基づいて、上記サンプリングクロックを上記各伝送パスからのデータに関連付け、上記ストリーミングデータ信号を再生するステップとを有する通信方法。

【請求項 2 5】

データ通信システムにおいて使用する送信ノードの動作方法において、

通信リンクの各伝送パスを介して、少なくとも 2 つのストリーミングデータ信号からのデータを送信するステップと、

上記通信リンクを介して、少なくとも 2 つのベースクロック信号のタイミング情報を送信するステップと、

上記各伝送パスと、対応する上記ベースクロック信号の 1 つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信するステップとを有する送信ノードの動作方法。

【請求項 2 6】

データ通信システムにおいて使用する受信ノードの動作方法において、

上記通信リンクの上記伝送パスから少なくとも 2 つのベースクロック信号のタイミング情報をと、少なくとも 2 つのストリーミングデータ信号からのデータと、上記各伝送パスと、対応する上記ベースクロック信号の 1 つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータとを含むデータを受信するステップと、

上記コンフィグレーションデータに応じて上記ベースクロック信号の上記タイミング情報を処理し、各伝送パスに対応する各サンプリングクロックを生成するステップと、

上記コンフィグレーションデータに基づいて、上記サンプリングクロックを上記各伝送パスからのデータに関連付け、上記ストリーミングデータ信号を再生するステップとを有する受信ノードの動作方法。

【請求項 2 7】

請求項 2 4 記載の通信方法のステップを実現するプログラムコードを有するコンピュータソフトウェア。

【請求項 2 8】

請求項 2 7 記載のコンピュータソフトウェアを提供する媒体。

【請求項 2 9】

当該媒体は、記録媒体であることを特徴とする請求項 2 8 記載の媒体。

【請求項 3 0】

当該媒体は、通信媒体であることを特徴とする請求項 2 8 記載の媒体。

**【請求項 3 1】**

少なくとも 2 つのベースクロック信号のタイミング情報と、少なくとも 2 つのストリーミングデータ信号からのデータと、上記各伝送バスと、対応する上記ベースクロック信号の 1 つとの間の各関係を特定し、該伝送バスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータとを含むデータストリーム。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、データ伝送に関する。

**【背景技術】****【0 0 0 2】**

ストリーミングデータ (streamed data) 及びその関連するサンプルクロックを別々のケーブルを用いて伝送する、通信リンクを介したストリーミングデータ信号の伝送が知られている。

**【0 0 0 3】**

また、複数の入力データストリームのデータをパケット化し、通信リンクを介して伝送することが知られている。多くの大規模通信システムでは、それぞれ異なる関連したサンプルクロックを有する多種多様なデータフォーマットをサポートしていることが必要である。通信リンクを介して、高品質クロックを転送することができることが望ましい。このことは、帯域が制限されている状況では、サポートしなければならないデータフォーマットの種類が増大するにつれて、益々困難になっている。

**【0 0 0 4】**

例えば、オーディオストリーミングデータの場合、市場で入手できる、標準ケーブルリンクフラストラクチャを用いた様々なマルチチャンネルオーディオ相互接続技術が知られている。これらの既存のシステムの大部分は、分散ルーティングを用いたネットワーク技術に基づいている。以前に提案された技術によると、データ通信システムにおいて、デジタルオーディオデータのポイントツーポイント接続を実現するために、高速イーサネット (100 Mbit / s) の物理層を用いている。しかしながら、このようなデータ通信システムの容量を大きくしたいという要求が高まるとともに、それに関連するクロック信号を有する多種多様なオーディオデータを取り扱いたいという要求が増している。

**【発明の開示】****【発明が解決しようとする課題】****【0 0 0 5】**

そこで、本発明の目的は、それぞれ異なるクロック信号を有する様々な異なるデータフォーマットを取り扱うことができるとともに、貴重な帯域幅を効率的に活用できるデータ伝送技術を提供することである。

**【課題を解決するための手段】****【0 0 0 6】**

本発明の第 1 の側面であるデータ通信システムは、通信リンクの各伝送バスを介して、少なくとも 2 つのストリーミングデータ信号からのデータを送信するデータ送信手段と、通信リンクを介して、少なくとも 2 つのベースクロック信号のタイミング情報を送信するタイミング送信手段と、各伝送バスと、対応するベースクロック信号の 1 つとの間の各関係を特定し、伝送バスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信するコンフィグレーション送信手段とを有する送信ノードと、通信リンクの伝送バスからデータを受信するデータ受信手段と、コンフィグレーションデータに応じてベースクロック信号のタイミング情報を処理し、各伝送バスに対応する各サンプリングクロックを生成する処理手段と、コンフィグレーションデータに基づいて、サンプリングクロックを各伝送バスからのデータに関連付け、ストリーミングデータ信号を再生する関連付け手段とを有する。

**【0 0 0 7】**

10

20

30

40

50

本発明者らは、通信リンクを介して、個別にベースロックを送信し、異なる伝送バスからのデータと、ベースロックとの間の関係を特定するコンフィグレーションデータを提供することにより、ベースロックと所定の伝送バスからのデータとを厳密に1対1に関係づける必要がなくなるため、高い柔軟性を実現できることを見出した。例えば、所定のベースロックを2つ以上の伝送バスからのデータに関連付けることができ、これにより、帯域幅を節約することができる。

#### 【0008】

本発明の第2の側面である通信方法は、通信リンクを介して、送信ノードと受信ノードとの間で通信を行う通信方法であって、送信ノードにおいて、通信リンクの各伝送バスを介して、少なくとも2つのストリーミングデータ信号からのデータを送信するステップと、通信リンクを介して、少なくとも2つのベースロック信号のタイミング情報を送信するステップと、各伝送バスと、対応するベースロック信号の1つとの間の各関係を特定し、伝送バスをいずれかのベースロック信号に関連付けるコンフィグレーションデータを送信するステップと、受信ノードにおいて、通信リンクの伝送バスからデータを受信するステップと、コンフィグレーションデータに応じてベースロック信号のタイミング情報を処理し、各伝送バスに対応する各サンプリングクロックを生成するステップと、コンフィグレーションデータに基づいて、サンプリングクロックを各伝送バスからのデータに関連付け、ストリーミングデータ信号を再生するステップとを有する。

#### 【0009】

本発明のこの他の様々な側面及び特徴は添付の特許請求の範囲に記載されている。独立請求項の特徴は、請求項において明示している場合に限らず、従属請求項の特徴に適切に組み合わせることができる。

#### 【発明を実施するための最良の形態】

#### 【0010】

以前に提案されたデータ通信システムでは、高速イーサネット（I E E E 8 0 2 . 3 1 0 0 B A S E - T X ）の物理層を用い、ビットレートが1 0 0 M b i t / s のチャンネルを有する単一のリンクを介して、様々なオーディオデータフォーマットを有する複数のオーディオチャンネルを送受することができる。このリンクは、4本の信号対を有するカテゴリ5非シールドのツイストペア線である。これらの信号対のうち、2本の信号対が、オーディオデータの送信と受信に使用され、残りの2本の信号対が、サンプリングクロック（sample clock）をリンクの両方向に搬送するために使用される。サンプリングクロックは、オーディオサンプルの同期を維持するために用いられる。

#### 【0011】

この以前に提案されたデータ通信システムにおいて説明されている物理層データ通信リンクは、1ビットのデルタ-シグマ変調オーバサンプリングフォーマットと、3 8 4 k H z のP C M フォーマットとを含む広範囲に亘るオーディオサンプリングレートをサポートすることができる。この1 0 0 M b i t / s ポイントツーポイントイーサネット物理層相互接続がサポートするオーディオフォーマットの具体的な範囲を以下の表1に示す。例えば、表1に示すように、このリンクは、48チャンネルの各方向において、44.1 k H z のP C M データ、又は24チャンネルの各方向において、2.8224 M H z のD S D データをサポートしている。

#### 【0012】

10

20

30

40

【表1】

| オーディオフォーマット             | サンプリングレート | チャンネル(各方向)<br>100Mbpsリンク |

|-------------------------|-----------|--------------------------|

| 24ビットAES3互換PCM          | 44.1kHz   | 48                       |

|                         | 48kHz     | 48                       |

|                         | 88.2kHz   | 24                       |

|                         | 96kHz     | 24                       |

|                         | 176.4kHz  | 12                       |

|                         | 192kHz    | 12                       |

|                         | 352.8kHz  | 6                        |

|                         | 384kHz    | 6                        |

| 24ビットPCM、非AES3<br>メタデータ | 352.8kHz  | 8                        |

| 1ビットデルタシグマ変調            | 2.8224MHz | 24                       |

|                         | 5.6448MHz | 12                       |

10

20

30

40

50

## 【0013】

100Mbit/sポイントツーポイント物理層リンクは、オーディオサンプリングクロックの周波数及び位相情報をリンクを介して両方向に搬送し、リンクの両端の機器がそれぞれのオーディオサンプリングクロックに同期するまでは、オーディオデータのスループットは起きない。オーディオの待ち時間は、オーディオモードに依存した所定の数のオーディオサンプリング周期に対応している。なお、待ち時間は、常に、100μs未満である。このリンクは、両方向で、対称性を有する。ポイントツーポイントリンクの帯域幅の一部は、オーディオストリームに多重化される補助データ用に予約されている。補助データがパケット交換されるのに対して、オーディオチャンネルデータは、(遅延時間が短い)回線交換される。

## 【0014】

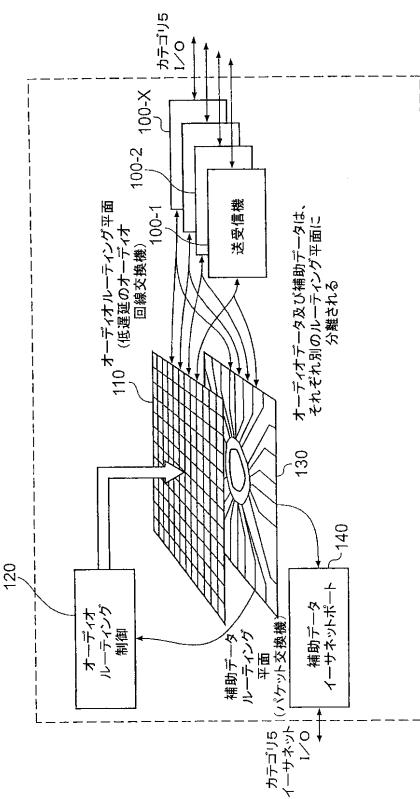

図1は、本発明に基づくルータのアーキテクチャを示すブロック図である。ルータは、イーサネットの物理層を介してデータを送受信する複数、すなわちN台の送受信機100-1~100-Xと、オーディオチャンネル回線交換機110と、オーディオルーティング制御モジュール120と、補助データパケット交換機130と、補助データイーサネットポート140とを備える。送受信機100-1~100-Xは、イーサネットの物理層を介してデータを送受信する。ルーティングは、オーディオデータと補助データとに対して別々に実行され、ルーティングの観点からは、オーディオデータと補助データは、図1に示すように、2つの独立した平面に論理的に分離される。補助データルーティング平面が、標準のイーサネットスイッチング集積回路を実現するパケット交換機130からなるのに対して、オーディオデータルーティング平面は、待ち時間が短いオーディオチャンネル回線交換機110からなる。オーディオルーティング制御モジュール120は、オーディオチャンネル交換処理を制御し、任意の入力と任意の出力間のオーディオルーティングを、クロスポイントスイッチに類似した方法で行うことができる。補助データイーサネットポート140は、補助データのルーティングを管理する。イーサネットポート140は、オーディオルーティングを制御するローカルホストマイクロプロセッサシステムに接続されている。これにより、如何なる送受信機ノードからもルータを遠隔制御することができる。

## 【0015】

本発明は、より大容量のギガビット(1000BASE-Tとして知られている)イーサネットポイントツーポイントリンクを提供する。これは、各方向において、上述した以前に提案されているデータ通信システムと同じ容量(100Mbps)をそれぞれ有する8本の並列データ伝送バスを提供するものと考えることができる。更に、補助データを、オーディオデータに多重化するのではなく、ギガビットリンクに亘って別々のフレームで

、100 Mbit/s(全二重)のレートで転送する。以下の表2は、ギガビットポイントツーポイントリンクのオーディオフォーマット及びサンプリングレートを示している。なお、表2に示す各オーディオフォーマットのチャンネルの数は、単純に、表1(100 Mbpsリンク)に示す対応したチャンネル数の8倍である。

【0016】

上述のように、100 Mbit/sリンクでは、カテゴリ5ケーブルを用いている。ギガビットリンクでは、銅線又は光ファイバのいずれも使用することができる。銅線は、カテゴリ5e/6ケーブルであり、1000BASE-T物理層を介したデータ伝送に使用され、その最大リンク長は100mである。光ファイバは、IEEE802.3の1000BASE-SXに準拠したマルチモード光ファイバであり、マルチモード光ファイバの場合、スパン距離は、最大500mである。シングルモード光ファイバを用いる場合は、スパン距離を更に長くすることができる。

【0017】

【表2】

| オーディオフォーマット             | サンプリングレート | チャンネル(各方向)<br>ギガビットリンク |

|-------------------------|-----------|------------------------|

| 24ビットAES3互換PCM          | 44.1kHz   | 384                    |

|                         | 48kHz     | 384                    |

|                         | 88.2kHz   | 192                    |

|                         | 96kHz     | 192                    |

|                         | 176.4kHz  | 96                     |

|                         | 192kHz    | 96                     |

|                         | 352.8kHz  | 48                     |

|                         | 384kHz    | 48                     |

| 24ビットPCM、非AES3<br>メタデータ | 352.8kHz  | 64                     |

| 1ビットデルタシグマ変調            | 2.8224MHz | 192                    |

|                         | 5.6448MHz | 96                     |

【0018】

本発明に基づくギガビットポイントツーポイント物理層リンクは、上述した周知の100 Mbit/sポイントツーポイント物理層リンクと相補的であると考えることができる。オーディオデータ相互接続のためのチャンネル数の要求は、通常、アナログ/デジタル(A/D)変換において必要とされるチャンネル数に依存する。現在(本願出願時)、ギガビットポイントツーポイント物理層リンクに関連したハードウェアは、100 Mbit/s物理層リンクに関連したハードウェアよりも著しく高価であるため、オーディオデータシステムにおいて異なる接続に対しては、100 Mbit/sリンクとギガビットリンクの両方を用いた方が有益である場合がある。100 Mbit/sリンクで収容できる数を超えるチャンネル数を必要とする幾つかの重要な用途の具体例としては、ライブ音響システムがあり、舞台とフロントオブハウス(front-of-house)設備との間で、300m以上のリンクスパンを必要とし、また、352.8kHzのPCMオーディオのような極めて高い分解能のオーディオ処理システムでは多くのチャンネル数を必要とし、さらに、放送スタジオシステムでは、通常、多くのチャンネル数と、放送スタジオ間に亘る長いリンク長との両方を必要とする。本発明に基づくギガビットポイントツーポイント物理層リンクを実現するオーディオデータシステムの実施形態を図2、図3及び図4に示す。

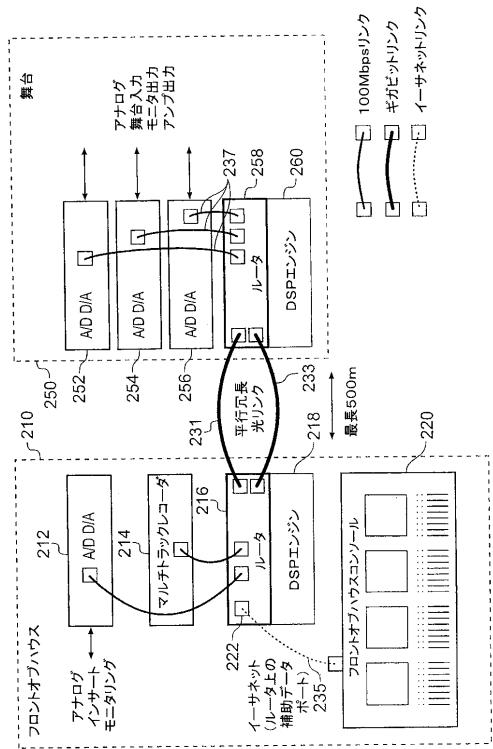

【0019】

図2は、ライブ音響システムの構成を示すブロック図である。このライブ音響システムは、「フロントオブハウス」設備セット210を含み、このフロントオブハウス設備セット210は、アナログ/デジタル(A/D)変換器/デジタル/アナログ(D/A)変換器212と、マルチトラックレコーダ214と、第1のルータ216と、第1のデジタル

10

20

30

40

50

シグナルプロセッシング( D S P )エンジン 2 1 8 と、フロントオブハウスコンソール 2 2 0 とを備える。更に、このライブ音響システムは、舞台設備セット 2 5 0 を含み、舞台設備セット 2 5 0 は、3 個の A / D 変換器 / D / A 変換器 2 5 2 、 2 5 4 、 2 5 6 と、第 2 のルータ 2 5 8 と、第 2 の D S P エンジン 2 6 0 とを備える。第 1 及び第 2 のルータ 2 1 6 、 2 5 8 は、D S P エンジン 2 1 8 、 2 6 0 のそれぞれの筐体に内蔵されている。ルータ 2 1 6 、 2 5 6 は、それぞれ 1 0 0 M b p s リンクポート及びギガビットリンクポートの両方を備えている。

#### 【 0 0 2 0 】

フロントオブハウス設備セット 2 1 0 内の A / D 変換器 / D / A 変換器 2 1 2 及びマルチトラックレコーダ 2 1 4 は、それぞれ 1 0 0 M b p s のポイントツーポイント物理層リンクによって第 1 のルータ 2 1 6 に接続されている。

#### 【 0 0 2 1 】

舞台設備セット 2 5 0 内の A / D 変換器 / D / A 変換器 2 5 2 、 2 5 4 、 2 5 6 は、それぞれ 1 0 0 M b p s のポイントツーポイント物理層リンク 2 3 7 によって第 2 のルータ 2 5 8 に接続されている。また、A / D 変換器 / D / A 変換器 2 5 2 、 2 5 4 、 2 5 6 及び第 2 のルータ 2 5 8 間の 1 0 0 M b p s のポイントツーポイント物理層リンク 2 3 7 は、A / D 変換器 / D / A 変換器 2 5 2 、 2 5 4 、 2 5 6 の遠隔からの利得制御及びミュート制御のために用いられる補助データ(各方向において約 5 M b p s に制限される)用のバスも提供する。

#### 【 0 0 2 2 】

第 1 のルータ 2 1 6 及び第 2 のルータ 2 5 8 は、マルチモード光ファイバ上で動作する、本発明に基づく 2 本の平行なギガビットポイントツーポイント物理層リンク(ギガビットリンク) 2 3 1 、 2 3 3 を介して通信する。D S P エンジン 2 1 8 、 2 6 0 は、ギガビットリンク 2 3 1 、 2 3 3 上を転送されるイーサネットの制御及び状態データによって制御される。

#### 【 0 0 2 3 】

第 1 のルータ 2 1 6 の補助データポート 2 2 2 は、イーサネットリンク 2 3 5 によってフロントオブハウスコンソール 2 2 0 に接続されている。これにより、フロントオブハウスコンソール 2 2 0 は、第 1 のルータ 2 1 6 を遠隔制御する。第 1 及び第 2 のルータ 2 1 6 、 2 5 8 は、図 1 に示す原理に基づいて動作する。

#### 【 0 0 2 4 】

舞台設備セット 2 5 0 内の A / D 変換器 / D / A 変換器 2 5 2 、 2 5 4 、 2 5 6 は、マイク入力、及びフロントオブハウス出力をモニタリングするために、第 2 のルータ 2 5 8 に接続されており、一方、フロントオブハウス設備セット 2 1 0 内の A / D 変換器 / D / A 変換器 2 1 2 は、アナログインサー(舞台から受け取った信号に対応する)をモニタリングするために、第 1 のルータ 2 1 6 に接続されている。

#### 【 0 0 2 5 】

図 2 に示すライブ音響システムの構成では、システムクロックだけではなく、全てのオーディオデータ及び制御データは、1 0 0 M b p s 及びギガビット物理層リンクを介して伝送される。

#### 【 0 0 2 6 】

システムが 9 6 k H z の 2 4 ビット P C M モードで動作している場合(表 1 参照)、各 1 0 0 M b p s リンクでは、6 サンプル分の待ち時間が生じ、各ギガビットリンク 2 3 1 、 2 3 3 は、2 サンプル分の待ち時間が生じる。

#### 【 0 0 2 7 】

具体例として、図 2 に示すライブ音響システムにおける待ち時間に関して、最長経路(critical path)について検討する。最長経路は、舞台設備セット 2 5 0 から、A / D 変換器 / D / A 変換器 2 1 2 のアナログインサーを介して、フロントオブハウス設備セット 2 1 0 に至り、舞台設備セット 2 5 0 に戻るまでの経路である。この経路の各段において生じる待ち時間の詳細について以下の表 3 に示す。表 3 に示すように、1 0 0 M b p s

10

20

30

40

50

及びギガビット物理層リンク、及び2つのルータ216、258の全てが起因した総待ち時間は、 $292 \mu s$ に達する。これは、標準のA/D変換器/D/A変換器の典型的な待ち時間に比べて非常に短い。なお、例えば音楽録音及び映画、又はテレビジョン放送のポスト編集システム(post-production system)のような他の大規模デジタルミキシングコンソール用途にも、図2に示すライブ音響システムと同様の手法に基づき、100Mbps及びギガビット物理層リンクを適用することができる。

【0028】

【表3】

| リンク                                   | 待ち時間<br>(サンプル) | 待ち時間<br>(マイクロ秒) |

|---------------------------------------|----------------|-----------------|

| 100Mbpsリンク257:<br>舞台ボックスから舞台<br>ルータ   | 6              |                 |

| ギガビットリンク231:<br>舞台からFoH               | 2              |                 |

| 100Mbpsリンク:<br>FoHルータからインサー<br>トA/D/A | 6              |                 |

| 100Mbpsリンク:イン<br>サートA/D/AからFo<br>Hルータ | 6              |                 |

| ギガビットリンク233:<br>FoHから舞台               | 2              |                 |

| 100Mbpsリンク237:<br>舞台ルータから舞台ボッ<br>クス   | 6              |                 |

| 合計:                                   | 28             | 291.6667        |

10

20

30

40

【0029】

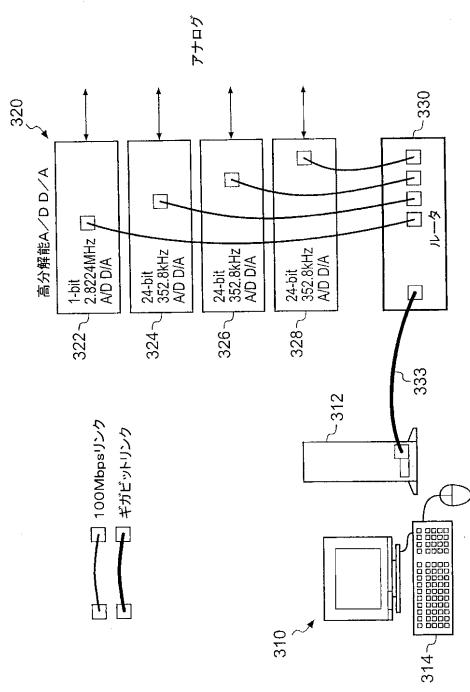

図3は、本発明に基づく高分解能オーディオワークステーションの構成を示すブロック図である。この構成は、ワークステーション310と、高分解能のA/D変換器/D/A変換器320とを備え、ワークステーション310は、システムユニット312と、キーボード314を有し、高分解能のA/D変換器/D/A変換器320は、1台の8チャンネル1ビット2.8224MHz変換器モジュール322と、3台の8チャンネル24ビット352.8kHzPCM変換器モジュール324、326、328とを有する。更に、この構成は、ルータ330を備え、ルータ330は、4台の変換器モジュール322、324、326、328のそれぞれへの4本の100Mbpsポイントツーポイントリンクと、ワークステーション310のシステムユニット312内のペリフェラルコンポーネントインターフェクト(peripheral component interconnect: PCI)カードにルータ自身を接続するギガビットリンク333とを有する。ギガビットリンク333は、A/D変換器/D/A変換器320とワークステーション310間で、352.8kHzPCM及び2.8224MHz1ビットオーディオストリームの全てを転送する。ワークステーション310は、ルータ330と、4台の変換器モジュール322、324、326、328のそれぞれの動作を制御するために用いられる。制御データは、ルータ330の補助データルーティング平面上を通過する。また、図2に示すライブ音響システムと同様に、全てのオーディオのクロックは、100Mbps及びギガビット物理層リンクを介して送受される。

【0030】

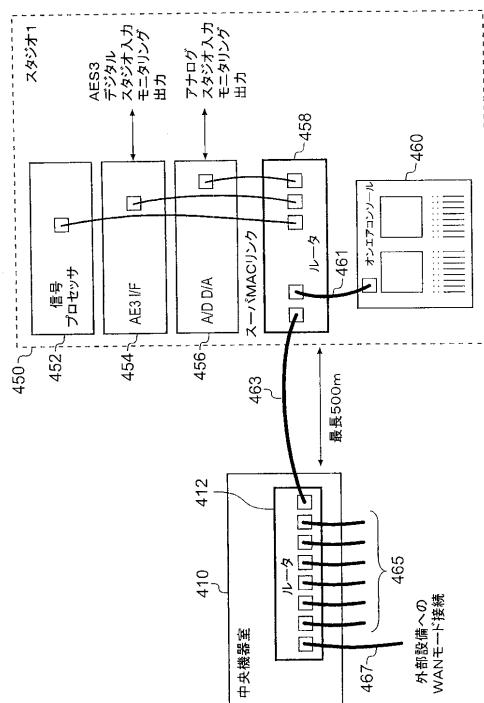

図4は、本発明に基づくオーディオ放送スタジオの構成を示すブロック図である。中央機器室(central equipment room)410と制作スタジオ450は接続されている。ルータ412は、中央機器室410内に設置されている。制作スタジオ450は、信号プロセッサ452と、AES3フォーマットのデジタルスタジオ入力を受け取り、モニタリング

50

出力を出力する A E S 3 インタフェース 4 5 4 と、アナログスタジオ入力を受け取り、モニタリング出力を出力する A / D 変換器 / D / A 変換器 4 5 6 とを含む複数の設備を有する。信号プロセッサ 4 5 2、A E S 3 インタフェース 4 5 4 及び A / D 変換器 / D / A 変換器 4 5 6 は、それぞれ、スタジオルータ 4 5 8 への 1 0 0 M b p s リンクを有する。スタジオルータ 4 5 8 には、ギガビットリンク 4 6 1 を介してオンエア制御コンソール 4 6 0 が接続されている。更なるギガビットリンク 4 6 3 によって、スタジオルータ 4 5 8 は中央機器室 4 1 0 内のルータ 4 1 2 に接続されている。ギガビットリンク 4 6 3 の光ファイバの長さは、最大 5 0 0 m である。更に、中央機器室 4 1 0 内のルータ 4 1 2 は、制作スタジオ 4 5 0 からのギガビットリンク 4 6 3 に加えて、他の 6 つのスタジオへの独立したギガビットリンク 4 6 5 と、外部の設備へのワイドエリアネットワーク (W A N) ギガビットリンク 4 6 7 とを有する。この構成の各ギガビットリンクは、スタジオから中央機器室 4 1 0 内のルータ 4 1 2 に、3 8 4 チャンネルの 4 8 k H z P C M オーディオを伝送する（表 2 参照）。

### 【 0 0 3 1 】

上述のように、1 0 0 M b p s 物理層リンクは、カテゴリ 5 ケーブルを使用し、オーディオデータの送信と受信のために 2 本の信号対を使用し、残る 2 本の予備の信号対は、高周波サンプリングクロックをそれぞれの方向に伝送する。なお、ギガビット物理層リンクの場合、カテゴリ 5 e / 6 ケーブルには、クロック信号を専用に伝送するための予備のリンクはなく、光インターフェースには、各方向毎に、1 つの受光口 (bearer) しかない。したがって、本発明では、ギガビットリンクにおいて、クロック情報を伝送するための他の方法を提供する。ギガビットリンクを、最大で 4 つの非同期オーディオサンプリングクロックドメイン (asynchronous audio sample clock domain) を搬送するように構成する。これらの 4 つのサンプリングクロックをオーディオ「ベースクロック (audio base clock)」と呼ぶ。なお、本明細書では、「ベースクロック」という用語は、クロック信号を指す一般的な意味で使用し、音響工学の分野で定義されているような如何なる特定の意味にも関係しない。この構成に基づく 4 つの可能なオーディオベースクロックは、以下の通りである。

### 【 0 0 3 2 】

ベースクロック A : 4 4 . 1 k H z  $\pm$  1 0 0 p p m ( 1 0 0 万分の 1 )

ベースクロック B : 4 8 k H z  $\pm$  1 2 . 5 %

ベースクロック C : 4 4 . 1 k H z  $\pm$  1 2 . 5 %

ベースクロック D : 4 8 k H z  $\pm$  1 0 0 p p m

したがって、可能な最小ベースクロック周波数は、3 8 . 5 8 7 5 k H z ( 4 4 . 1 k H z - 1 2 . 5 % ) であり、可能な最大ベースクロック周波数は、5 4 k H z ( 4 8 k H z + 1 2 . 5 % ) である。多くの実際の装置 (implementations) が  $\pm$  1 2 . 5 % の動作をサポートしないので、ベースクロック A は、互換性を保証するために、常に、 $\pm$  1 0 0 p p m で動作するように構成する。各オーディオストリーム（表 2 参照）は、4 つの可能なベースクロックのうちの 1 つに同期しなければならない。各オーディオデータストリームには、適切なサンプリングクロックレートを実現するために、オーディオベースクロックに乗算する係数を指定するサンプリングレート乗数 (sample rate multiplier) を割り当てる。表 2 に示す使用可能な各サンプリングレートについて、関連するベースクロック及びサンプリングレート乗数を以下の表 4 に示す。

### 【 0 0 3 3 】

10

20

30

40

【表4】

| オーディオフォーマット        | サンプリングレート               | チャンネル(各方向)<br>ギガビットリンク | サンプリングレート乗数 | ベースクロック周波数 |

|--------------------|-------------------------|------------------------|-------------|------------|

| 24ビット<br>AES3互換PCM | 44.1kHz                 | 384                    | ×1          | 44.1kHz    |

|                    | 48kHz                   | 384                    | ×1          | 48kHz      |

|                    | 88.2kHz                 | 192                    | ×2          | 44.1kHz    |

|                    | 96kHz                   | 192                    | ×2          | 48kHz      |

|                    | 176.4kHz                | 96                     | ×4          | 44.1kHz    |

|                    | 192kHz                  | 96                     | ×4          | 48kHz      |

|                    | 352.8kHz                | 48                     | ×8          | 44.1kHz    |

|                    | 384kHz                  | 48                     | ×8          | 48kHz      |

|                    | 24ビットPCM、非AES<br>3メタデータ | 352.8kHz               | 64          | ×8         |

| 1ビットデルタシグマ<br>変調   | 2.8224MHz               | 192                    | ×64         | 44.1kHz    |

|                    | 5.6448MHz               | 96                     | ×128        | 44.1kHz    |

10

【0034】

なお、特定の実施例において、必ずしも、4つのベースクロックの全てを用いられなければならないというわけではない。例えば、以下の表5に示すように、3つの異なるサンプリングレートを有するオーディオバスを有するオーディオシステムもある。この実施例では、オーディオベースクロックC及びDは、使用されず、ベースクロックAは、(異なるサンプリングレート乗数によって)2つの異なる入力データストリームに関連付けられている。

20

【0035】

【表5】

| アプリケーションオーディオバスのサンプリングレート | 適切なベースクロック | サンプリングレート乗数 |

|---------------------------|------------|-------------|

| 176.4kHz±100ppm           | ベースクロックA   | ×4          |

| 88.2kHz±100ppm            | ベースクロックA   | ×2          |

| 48kHz±12.5%               | ベースクロックB   | ×1          |

30

【0036】

ギガビット物理層リンクでは、各オーディオベースクロック用のクロック情報を、オーディオフレームヘッダの部分に格納する。125MHzの周波数を有する物理層のクロックは、4つのオーディオベースクロックのそれぞれのオーディオベースクロックタイミング情報を搬送するために使用する。

40

【0037】

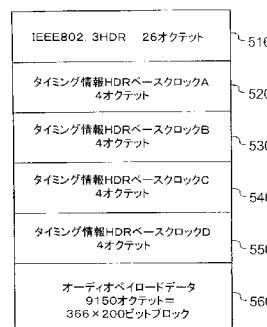

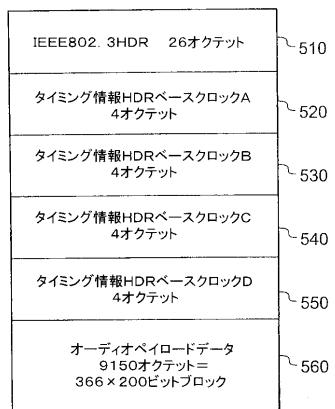

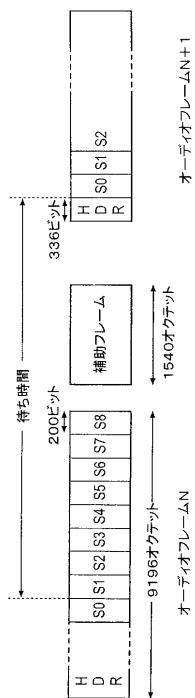

図5は、フレームヘッダ内に4つの全てのベースクロック用のタイミング情報を含む、本発明に基づくオーディオフレームの構造を示す図である。オーディオフレームは、合計9196オクテットのデータを含む。ヘッダデータ510の最初の26オクテットは、8オクテットのIEEE802.3ブリアンブルデータと、6オクテットのメディアアクセス制御(Media Access Control: MAC)送信元アドレスフィールド及びMAC宛先アドレスフィールド(ポイントツーポイントリンクの場合は無視される)と、ジャンボフレームの有効性を指定する2オクテットのデータと、MACタイプを指定する2オクテットのデータと、プロトコルIDを指定する2オクテットのデータとからなる。MACは、データのカプセル化及びメディアアクセス管理機能(衝突回避及び処理)を有するイーサネットプロトコル層である。ヘッダデータの次の部分は、4オクテットのベースクロックA用タイミング情報ヘッダ520と、4オクテットのベースクロックB用のタイミング情報530と、4オクテットのベースクロックC用のタイミング情報ヘッダ540と、4オクテットのベースクロックD用のタイミング情報ヘッダ550とからなる。ペイロードデータ

50

560は、 $366 \times 200$ ビットブロックとして構成された9150オクテットからなる。

### 【0038】

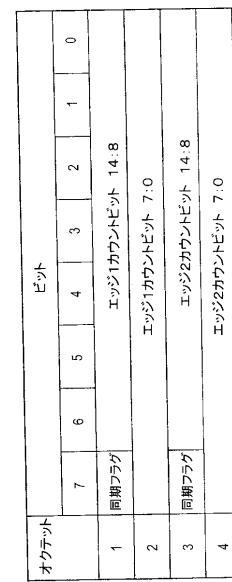

図6は、タイミング情報ヘッダ520、530、540、550のうちの1つの内容を代表的に示している。4オクテットのタイミング情報は、送信機において、オーディオフレームヘッダの最後と、次のオーディオベースクロック「イベント」との間に出現する125MHzのギガビット物理層クロックのエッジの数を特定する15ビットの値である「エッジ1カウント(edge 1 count)」を含む。また、タイミング情報は、フレームヘッダの最後から、1つおいて隣の(すなわち後続の)オーディオベースクロックイベントまでに出現する125MHzのギガビット物理層クロックエッジの数を特定する15ビットの値である「エッジ2カウント(edge 2 count)」を含む。

### 【0039】

なお、オーディオベースクロック「イベント」は、実際には、オーディオベースクロックエッジではなく、9.64kHz~13.5kHzの周波数である、対応するベースクロック周波数の1/4の周波数を有するクロックに対応するクロックエッジである。上述のように、オーディオベースクロック周波数範囲は、38.5875kHz~54kHzである。第1のオクテットの最上位ビット及び第3のオクテットの最上位ビットは、同期フラグである。同期フラグは、関連したベースクロックイベントがオーディオベースクロックを2048で除算した値に等しい周波数を有する同期マーカに同期したことを、示している。これらの同期マーカは、待ち時間制御のために用いられる。

### 【0040】

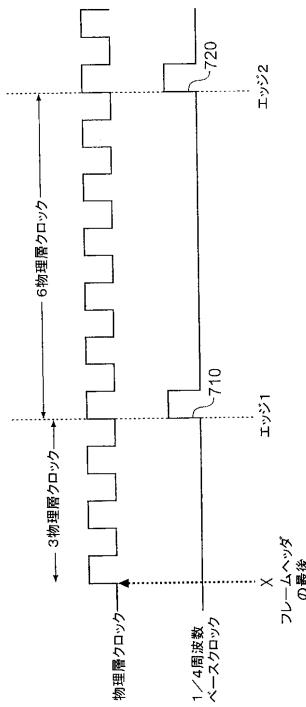

タイミング情報をどのように導出するかを図7を用いて説明する。図7に示すように、フレームヘッダの最後と、次のベースクロックイベント710との間には、3個の物理層クロックエッジがあり、一方、このフレームヘッダの最後と、1つおいて隣のベースクロックイベント720との間には、6+3、すなわち合計9個の物理層クロックエッジがある。したがって、この簡略化された具体例では、「エッジ1カウント」の値は、3(十進法)であり、「エッジ2カウント」の値は、9(十進法)である。物理層クロックの周波数は125MHzであり、(オーディオベースクロック)/4の周波数範囲は、9.64~13.5kHzであるので、実際のカウント値は、これより遙かに大きいことは明らかである。

### 【0041】

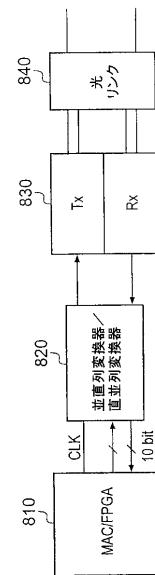

ギガビットリンクの物理層にデータを送信し、及びギガビットリンクの物理層からデータを受信する構成を図8に示す。この構成は、フィールドプログラマブルゲートアレー(field programmable gate array: 以下、FPGAという。)810と、並直列変換器/直並列変換器820と、送信/受信モジュール830と、光リンクインターフェース840とを備える。FPGA810は、従来のイーサネットシステムにおけるMACの役割を担い、したがって、データのカプセル化及びメディアアクセス管理の機能を実行する。FPGA810は、送信と受信を同時に実行し、全二重データ接続を実現する。データは、10ビット幅の送信データバス及び10ビット幅の受信データバスを介して、FPGA810と並直列変換器/直並列変換器820間で送受される。データは、ギガビット物理層の125MHzのクロックレートで、FPGA810から10ビットデータバスに出力される。送信/受信モジュール830は、光リンクインターフェース840を介して物理層に出力するデータを準備する。図7のエッジカウントイベント710、720は、送信機において、相対的に適切に調整する必要があり、10ビットのヘッダデータ部分の出力と10ビットのペイロードデータ部分の出力との間に遷移があったときに、10ビットの信号は、クロックに従って、すなわち時間に関連して、並直列変換器/直並列変換器820に出力される。これにより、パイプライン遅延及び10ビット符号化にかかる時間が補償される。同様に、オーディオサンプリングクロックを再生するときは、受信機は、パイプライン遅延及び10ビット復号化の遅延を補償する必要がある。

### 【0042】

10

20

30

40

50

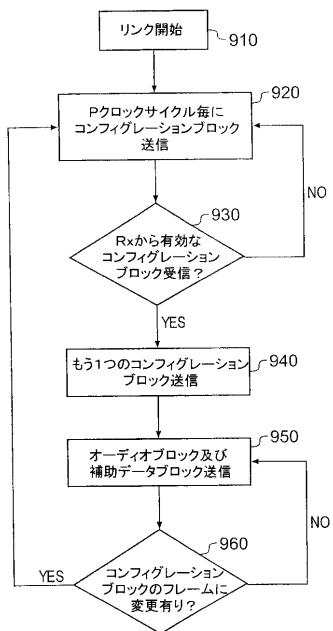

図9は、送信機と受信機の間で、4つの可能なベースサンプリングクロックの1つに各オーディオデータストリームを関連付けるデータを含むコンフィグレーションデータを通信する手順を説明するフローチャートである。処理は、ステップ910から開始され、ここで、ギガビット物理層リンクを初期化する。なお、送信装置及び受信装置がそれらのオーディオサンプリングクロックに同期するまでは、オーディオデータのスループットは起こらない。そして、ステップ920において、コンフィグレーションブロック(configuration block)の伝送を開始する。コンフィグレーションブロックは、リンクの開始の直後から、周期的(P個の物理層クロックサイクル毎に)に送信する。各コンフィグレーションブロックは、以下のデータを含む。

## 【0043】

- ・各オーディオストリームのオーディオモード(表5のサンプリングレート乗数を含む)

- ・各オーディオデータストリームのベースクロック選択(4つの可能なベースクロックからの選択)

- ・各ベースクロックの公称周波数を指定するデータ

- ・各ベースクロックの公差(±100 ppm及び±12.5%のいずれか)

- ・受信機が有効なコンフィグレーションブロックを受信したこと、及び受信機が要求されたオーディオモードで動作できることを示すフラグフィールド(フラグフィールドは送信機ではなく受信機によって提供される)

ステップ930において、送信機は、送信したコンフィグレーションの確認応答として、有効なコンフィグレーションブロックが受信機から返信されたか否か判定する。受信機が、要求したオーディオモードを処理することができる場合、確認応答コンフィグレーションブロックのインジケータフラグは、このことを確認するように設定される。ステップ930において、受信機からの確認応答コンフィグレーションブロックがないと判定した場合、処理は、ステップ920に戻り、送信機は、コンフィグレーションデータブロックを受信機に周期的に送信し続ける。一方、ステップ930において、確認応答コンフィグレーションブロックが受信されたと判定した場合、処理は、ステップ940に進み、送信機は、更にもう1つのコンフィグレーションブロックを送信する。確認応答コンフィグレーションブロックを受信し、ステップ940において更にもう1つのコンフィグレーションブロックを送信した送信機は、ステップ950において、オーディオデータブロック及び補助データブロックの送信を開始する。補助データフレームは、本発明に基づくギガビットリンクのオーディオフレーム間で送信される。

## 【0044】

オーディオデータ及び補助データの送信は、コンフィグレーションブロックパラメータが変化しない限り継続される。一方、ステップ960において、1つ以上のコンフィグレーションブロックパラメータが実際に変更されていると判定した場合、処理は、ステップ920に戻り、送信機は、変更されたコンフィグレーションブロックを受信機に周期的に送信する。なお、この構成において、コンフィグレーションデータは、リンクの開始時及びコンフィグレーションデータパラメータが変化したときに、専用のデータブロックで送受されるが、変形例として、例えば、補助データフレーム又はオーディオフレームヘッダにコンフィグレーションデータを含ませてもよい。

## 【0045】

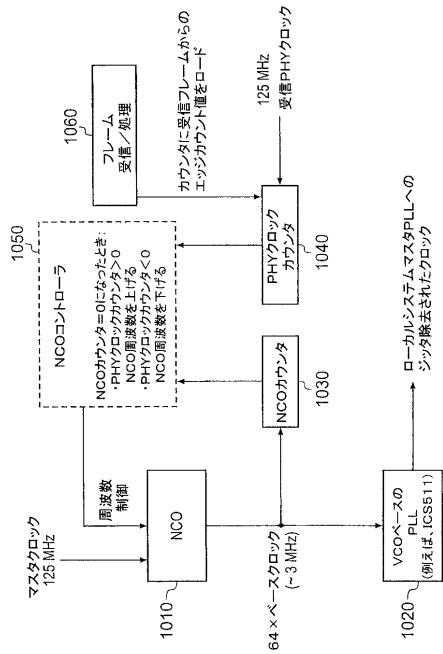

図10は、オーディオベースクロックを再生する受信機の構成を示すブロック図である。この構成は、数値制御発振器(Numerically Controlled Oscillator:以下、NCOという。)1010と、電圧制御発振器(Voltage Controlled Oscillator:以下、VCOという。)1020と、NCOカウンタ1030と、物理層(PHY)クロックカウンタ1040と、NCOコントローラ1050と、フレーム受信/処理ユニット1060とを備える。オーディオベースクロック用のタイミング情報は、図5及び図6に示すように、オーディオフレームのヘッデータ内に格納されている。このタイミング情報は、ギガビットリンクの1

10

20

30

40

50

25 M Hz の物理層クロックに対して可能な 4 つのベースクロックのそれぞれの 2 つのエッジカウントを含んでいる。各エッジカウントイベントは、対応するベースクロックの周波数の 1 / 4 の周波数を有するクロックのクロックエッジを表す。したがって、((オーディオベースクロック) / 4 イベント) の周波数は、9.64 kHz ~ 13.5 kHz となり、125 M Hz の物理層クロックを用いるオーディオベースクロックイベントをサンプリングする結果として生じる少なくとも 8 ns ( $8 \times 10^{-9}$  s = 1 / (125 × 10<sup>6</sup> Hz)) のジッタを有する。受信タイミングデータは、PLL1020 に供給され、PLL1020 は、このジッタを除去するとともに、使用可能なオーディオサンプリングクロック周波数に乗算する。図 10 に示す受信機のフレーム受信 / 処理ユニット 1060 は、タイミング情報ヘッダ 520、530、540、550 からタイミング情報を抽出し、順次、各ベースクロックについて、受信フレームからエッジカウント値 710 を PHY クロックカウンタ 1040 にロードする。また、受信した 125 M Hz の物理層クロック信号は、入力として PHY クロックカウンタ 1040 に供給され、この PHY クロックカウンタ 1040 のクロックとして用いられる。NCO1010 には、受信機の 125 M Hz のマスタクロックが入力として供給される。NCO1020 からは、オーディオベースクロックの周波数を 64 倍した周波数を有するクロック信号が出力され、このクロック信号は、NCO カウンタ 1030 と VCO ベースの PLL1020 の両方に供給される。NCO コントローラ 1050 は、NCO カウンタ 1030 の値と PHY カウンタ 1040 の値間の比較に基づいて、NCO1010 の周波数を制御する。具体的には、NCO カウンタ 1030 が 0 を示したときに、PHY クロックカウンタ 1040 のカウント値が 1 以上である場合、NCO1010 の周波数を上げ、一方、NCO カウンタ 1030 のカウント値が 0 になったときに、PHY クロックカウンタ 1040 のカウント値が 0 より小さい場合、NCO1010 の周波数を下げる。一方、NCO カウンタ 1030 及び PHY クロックカウンタ 1040 カウント値が等しい場合は、周波数を調整する必要はない。NCO1010 の出力は、VCO ベースの PLL1020 に供給され、PLL1020 は、ジッタを除去したクロック信号を受信機のマスタ PLL に供給する。NCO1010 は、VCO ベースの PLL1020 の VCO に供給する十分に高い周波数のベースクロックを得るために必要とされる。VCO ベースの PLL1020 は、クロック信号を受信機のクロックマスターの高性能 PLL に用いることができるよう、ベースクロックジッタを許容できる低いレベル ( 例えば 500 ps、すなわち  $500 \times 10^{-12}$  s 未満 ) までに減衰させる。

【 0046 】

図 5 を参照して説明したように、オーディオデータは、ギガビットリンクの物理層を介して、合計 42 オクテットのヘッダデータと 9150 オクテットのオーディオペイロードデータとからなるオーディオデータフレームで転送される。以下の表 6 は、ギガビットリンクオーディオフレームフォーマットの概要を示している。

【 0047 】

【表6】

| フィールド      | オクテット | 注記                   |

|------------|-------|----------------------|

| プリアンブル／SFD | 8     | IEEE802.3参照          |

| MAC送信元     | 6     | ポイントツーポイント接続の場合無視される |

| MAC宛先      | 6     |                      |

| Qtag TPID  | 1     | ジャンボフレーム有効性のために必要    |

| Qtag TCI   | 1     |                      |

| MACタイプ     | 2     | Ethertype 未定         |

| プロトコルID    | 2     | プロトコルID 未定           |

| タイミングHDR   | 16    |                      |

| ペイロード      | 9150  | 366個の25オクテットブロック     |

| FCS        | 4     | CRC-32               |

| 合計         | 9196  |                      |

10

## 【0048】

オーディオデータペイロードは、9150オクテットからなり、リンクを介して送信するため、独立した200ビット（25オクテット）のブロックに分割される。各ブロックは、ギガビットリンクに亘る8つのデータ伝送バスの1つに対応する192ビットのオーディオペイロードデータと、8ビットのブロックラベルとからなる。8ビットのブロックラベルは、以下の情報を特定する。

## 【0049】

・オーディオペイロードデータが関連付けられているギガビットリンクのデータ伝送バス

2

048

・ブロック内のオーディオデータが、送信機における（オーディオベースクロック／2048）同期フラグに対応したオーディオフレームの最初から始まっているか否かを示すオーディオストリーム同期マーカ（Audio Stream Synchronisation Marker: ASSM）

ギガビットリンクの8つの独立したそれぞれのデータ伝送バスは、送信機内の関連したFIFO（ファーストインファーストアウト）バッファと、受信機内の対応したFIFOバッファとを有する。

## 【0050】

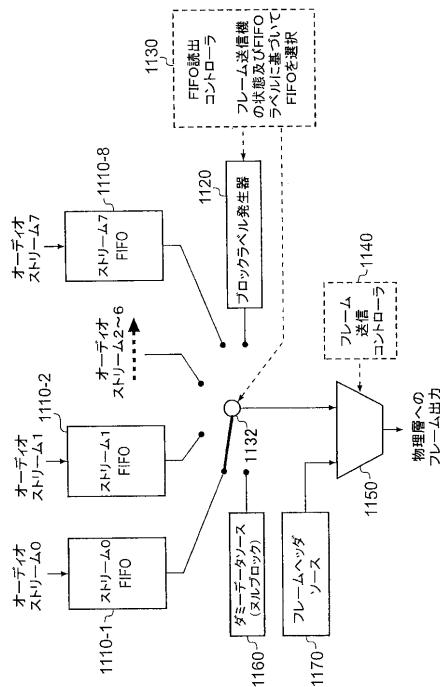

図11は、本発明に基づくギガビットリンク送信機のバッファリング及びフレーム組立の構成を示すブロック図である。この構成は、それぞれがギガビットリンクの各データ伝送バスの1つに対応した、8つからなる一連のFIFOバッファ1110-1~1110-8と、ブロックラベル発生器1120と、FIFO読出コントローラ1130と、フレーム送信コントローラ1140と、マルチプレクサ1150と、ダミーデータソース1160と、フレームヘッダソース1170とを備える。8つのFIFOバッファ1110-1~1110-8のそれぞれは、対応する入力オーディオデータストリームのデータを受け取るように構成されている。入力オーディオストリームからのデータは、異なるデータフォーマット及びサンプリングレートを有することができ、各データフォーマットは、上述した表2から選択される。FIFO読出コントローラ1130は、バッファ順序シーケンスに基づいて切換スイッチ1132を切り換えることによって、一連のFIFOバッファ1110-1~1110-8のそれぞれから順番に192ビットのデータブロックを読み出す。この特定の構成では、シーケンスの順序は、8つのFIFOバッファ1110-1~1110-8のそれぞれを順番に循環する順序である（すなわち、バッファリング順序は、周期的である）。FIFO読出コントローラ1130は、フレーム送信コントローラ1140の状態に基づいて、フレーム送信シーケンス内の適切な位置で、データを読み出すFIFOバッファを選択する。

## 【0051】

しかしながら、特定のFIFOバッファがFIFO読出コントローラ1130によって

30

40

50

選択されたときに、FIFOバッファの現在の占有レベルは、データブロックを FIFOバッファから読み出してマルチプレクサ1150に供給し、データ伝送ストリームとして出力するためには、所定の閾値以上である必要がある。ここで、FIFOバッファ内のデータが不十分な場合（すなわち、占有レベルが所定の閾値以下の場合）、FIFO読出コントローラ1130は、ダミーデータソース1160からのデータバスをマルチプレクサ1150に接続するように切換スイッチ1132を設定し、これにより、現在選択中のFIFOバッファからのデータに代えて、トランスポートデータストリーム内の対応する位置にダミーデータのブロックを挿入する。なお、本発明に基づく代替的構成例では、データストリームに挿入するための、識別子を有するダミーデータを積極的に生成しなくてもよい。これに代えて、例えば、物理層が、フレームペイロードのブロック間に有効なギャップができるように、データを出し、これにより、積極的に生成したダミーデータブロックと同様にデータフローを平滑化する機能を果たすことができる。

10

20

30

40

50

## 【0052】

ロックラベル発生器1120は、FIFOバッファ1110-1~1110-8の1つから読み出された各オーディオデータブロックに8ビットのロックラベルを関連付ける。ロックラベルは、関連するブロックの前に送信され、これにより、受信機は、入力データをどのFIFOバッファにルーティングすべきかを前もって決定することができる。フレーム送信コントローラ1140は、フレーム送信状態を監視し、フレーム送信のタイミングを制御する。フレームヘッダソース1170は、各データフレームの始めに、オーディオフレームのヘッダデータ（42オクテット）をマルチプレクサ1150に供給する。マルチプレクサ1150は、オーディオデータフレームを含むデータ伝送ストリームを、伝送のために、ギガビットイーサネットリンクの物理層に供給する。

## 【0053】

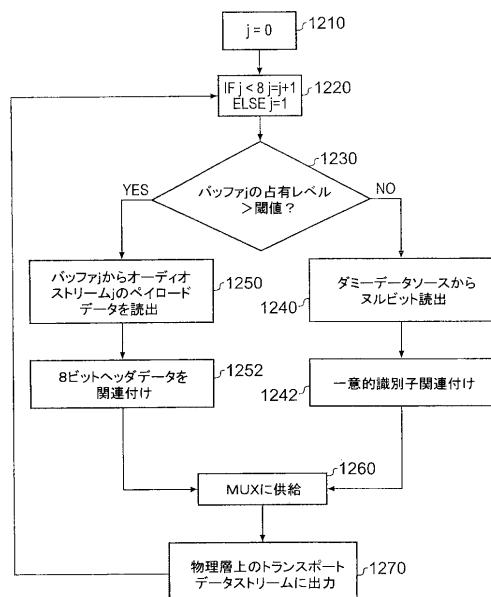

図11に示す送信機における、本発明に基づく伝送バッファリング及びフレームの組立処理のフローチャートを図12に示す。ステップ1210において、バッファインデクスjを0に初期化し、ステップ1220において、jを1インクリメントし、8つのFIFOバッファのうちの1番目のFIFOバッファ1110-1を選択する。ステップ1230において、FIFO読出コントローラ1130（図11参照）は、バッファjの占有レベルが192ビット（所定の閾値）以上であるかを判定する。この条件が満たされない場合、ステップ1240において、FIFO読出コントローラ1130は、切換スイッチ1132をダミーデータソース1160に切り換え、192ビットのダミーデータを読み出す。ステップ1242において、オーディオペイロードデータとダミーデータブロックを区別するために、8ビットの一意的な識別子をダミーデータに関連付ける。一方、ステップ1230において、選択されたFIFOバッファの現在の占有レベルが所定の閾値以上であると判定された場合、処理は、ステップ1250に進み、FIFO読出コントローラ1130の制御の下で、192ビットのオーディオペイロードデータをFIFOバッファから読み出す。次に、ステップ1252において、入力データストリームjを特定する適切な8ビットのロックラベルをオーディオペイロードデータに関連付ける。この8ビットのロックラベルは、ルーティングデータもプロトコルデータも含んでいない。ステップ1260において、ステップ1252で得られた200ビットのダミーデータブロックと、ステップ1242で得られた200ビットのオーディオデータブロックのいずれかをマルチプレクサ1150に供給し、ステップ1270において、これらのブロックをギガビットイーサネット物理層上の伝送データストリームとして出力する。そして、処理は、ステップ1220に戻り、jの値をインクリメントし（j=8の場合は、シーケンス順序における第1のバッファに対応する1にjをリセットする）、選択の順序における次のFIFOバッファに移行し、処理を続行する。代替的構成として、データブロックの伝送開始時において、閾値が、ブロックの終わりまでには192ビットのデータが供給されることを保証できる程度に十分大きければ、閾値は、192ビット未満であってもよい。更に、代替的構成として、FIFOバッファの順序は、循環的ではなく、擬似ランダム的であってもよい。なお、循環的なバッファ順序は、代替的構成におけるバッファ順序に比べて

、受信機のバッファリング要求を低くできるので、待ち時間を最も短くできるという利点がある。

#### 【0054】

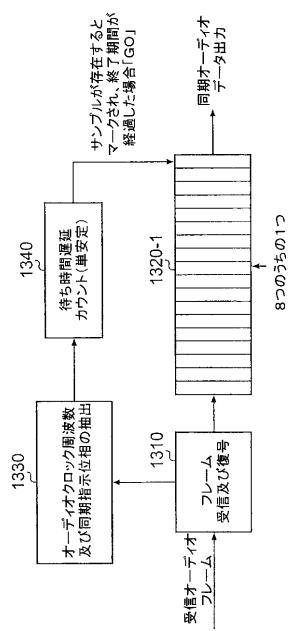

図13は、図11に示す送信機に対応した受信機におけるフレーム受信及びバッファリングの構成の代表的な部分を示すブロック図である。図13では、8つのバッファ受信構成のうちの代表的な1つを示している。この構成は、復号ユニット1310と、受信機 FIFOバッファ1320-1と、クロック抽出ユニット1330と、単安定カウンタ1340とを備える。復号ユニット1310は、ギガビットリンクの物理層を介して伝送されてきたフレーム化されたデータを受信し、オーディオフレームのヘッダデータ（上述の表6参照）を用いて、フレーム化されたデータを復号する。復号ユニット1310は、オーディオデータブロックの8ビットのブロックラベルを用いて、オーディオペイロードデータブロックがどの入力オーディオデータストリームに関連付けられているかに基づき、受信機の8つのIFOバッファの適切な1つにオーディオペイロードデータを供給する。図5、図6及び図7を参照して、先に説明したオーディオサンプル同期メカニズムを採用することにより、ギガビットリンクの両端において（伝播遅延のための僅かな位相オフセットは無視する）、オーディオサンプリングクロックの位相とマスタクロックの周波数は実質的に同じになる。送信機において、（オーディオベースクロック）/2048の同期マーカと同時に、ローカルのオーディオシステムから受信されるオーディオペイロードサンプルは、タイミング情報ヘッダ内のフィールド（図6参照）によって標識が付けられている。この同期マーカは、受信機の対応するFIFOバッファ1320-1によって用いられる。タイミング情報（図6参照）によって特定される、オーディオフレームヘッダ内の同期フラグの出現は、受信機内の単安定タイマ1340をトリガし、単安定タイマ1340は、リンクの所定の待ち時間に等しいタイムアウト遅延を発生する。受信機からのオーディオ出力は、単安定タイマ1340のタイムアウト遅延が終了するまで禁止される。すなわち、同期マーカのセットを有するオーディオサンプルが受信機のFIFOバッファ1320-1内に存在し、単安定カウンタ1340がタイムアウト値が終了したことを示すと、受信機のFIFOバッファ1320-1からの同期オーディオデータ出力が開始される。単安定タイマ1340によって実現されるタイムアウト遅延は、ギガビットリンクを介した伝播及び処理の両方による最大遅延よりも、若干長く設定される。可変のサンプリングレートをサポートするためには、タイムアウト遅延は、絶対時間の値ではなく、オーディオサンプルの数として設定される。

#### 【0055】

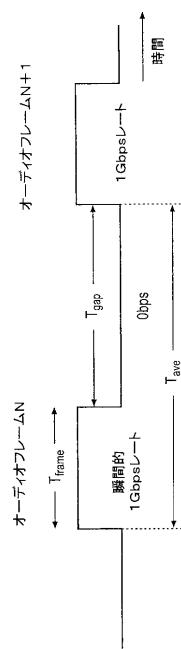

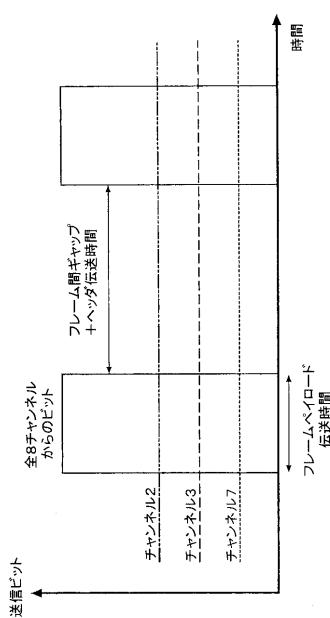

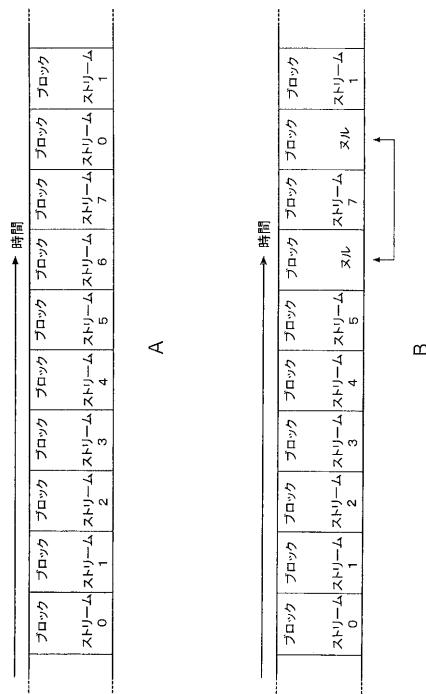

図14Aは、オーディオフレームペイロードがギガビットリンクを介してどのように伝送されるかを説明するためのタイミングチャートである。パケット伝送では、データはバースト的に伝送される。オーディオフレームNのデータ（ヘッダ及びペイロード）は、ギガビットイーサネットリンクを介して、1ギガビット/秒（20%のオーバヘッドを有する1.25Gbps）の「瞬間的な」伝送レートで伝送される。瞬間的なデータ伝送レートは、時間尺度 $T_{frame}$ に対するデータ転送レートに対応している。受信機では、オーディオデータは、関連するベースクロック周波数に対応したそれぞれのデータ転送レートで、8つの独立した連続データストリームとして出力される。なお、乗数（表4参照）は、チャンネル数が出力データ転送レートを補償するように変更されるため、この出力データ転送レートに影響しない。

#### 【0056】

図14Bは、パケット化されたオーディオデータペイロード（フレームヘッダを除く）の瞬間的なデータフローを、8つのチャンネルのうち3つのチャンネルの連続したデータフローと共に示すタイムチャートである。図14Bに示すように、8つの全てのチャンネルからのオーディオペイロードデータは、フレームペイロード伝送時間（ヘッダ伝送時間を減算するため、図14Aの $T_{frame}$ より短い）の間に伝送される。各バーストのオーディオペイロードデータは、受信機において、8つのストリーミングされた出力データチャンネルに振り分けられ、各データブロックの適切な出力チャンネルは、関連するブロ

10

20

30

40

50

ックラベルによって指定される。図14Bには、瞬間的なデータフローと共に、8つのストリーミングされた出力データチャンネルのうちの代表的な3つの出力データチャンネルの連続出力データフローを示している。図14Bにおける3つのチャンネルのそれぞれは、すなわちチャンネル2、チャンネル3、チャンネル7は、(表2に示したフォーマットから選択された)異なるオーディオフォーマットに対応したデータを搬送する。したがって、3つのチャンネルのストリーミングされたデータ転送レートは異なる。この具体例では、チャンネル2が最も高い出力データ転送レートを有する。なお、バースト内の瞬間的な伝送レートは、フレーム間のギャップを補償し、連続した出力データ転送レートを確実に維持するために、十分高くななくてはならない。

## 【0057】

10

したがって、オーディオフレームに含まれる1チャンネル当たりのビットの総数を $T_{ave}$ ( $T_{frame}$ 及びフレーム間ギャップ時間 $T_{gap}$ の和)で除算することによって得られる「平均データ転送レート」が、8つのチャンネルの全ての連続するデータ転送レート以上でなくてはならないという待ち時間の制約条件がある。したがって、課せられる待ち時間制約条件は、以下の通りである。

## 【0058】

$T_{ave}$ (= $T_{frame}$ + $T_{gap}$ )に亘って平均化された1チャンネル当たりのオーディオペイロードのデータ転送レート 受信機における(連続した)最大出力オーディオデータ転送レート

20

この場合、受信機における最大出力オーディオデータ転送レートは、各方向において合計384チャンネル(1ストリーム当たり48のチャンネル)を有する、表2の(48kHz+12.5% = 54kHz)における24ビットPCMのオーディオフォーマット(24ビットのオーディオ+4ビットのAES3メタデータ)に対応する。この場合、最大出力オーディオデータ転送レートは、28ビット×48チャンネル×54kHz = 72.6Mbpsである。また、オーディオフレーム伝送時間 = 9196×8ビット/1Gbps = 73.5μsであり、補助データ伝送時間 = 1540×8ビット/1Gbps = 12.3μsである。したがって、ギガビットリンクの潜在的に同等な連続するデータ転送レートは、(192ビット×366/8 = 8784ビット)/(73.5+12.3μs) = 102.4Mbpsである。したがって、この構成では、ギガビットリンクは、許容可能なレベルの待ち時間で最大データ転送レートをサポートするために必要とされる性能を上回る能力を有する。

30

## 【0059】

上述のように、待ち時間制約条件は、潜在的に同等な連続したデータ転送レート(102.4Mbps)が、最大データ転送レート(72.6Mbps)よりも高くななくてはならないという条件である。最大データ転送レートを下回る入力データストリームに対しては、オーディオデータストリームのペイロードにヌルデータを挿入することにより、最大データ転送レートと、特定の入力データストリームの実際のデータ転送レートの間の差分を補償することができる。これにより、入力データストリームの物理層リンクを介するデータフローをより平滑化ことができる。

## 【0060】

40

図15は、2つのオーディオデータフレームと、挿入された補助データフレームとを含むギガビットリンク上のフレーム伝送シーケンスを示している。各オーディオデータフレームは、42オクテット(336ビット)のヘッダデータと、388個の200ビットブロック(200ビットブロック当たり8ビットのブロックラベルを含む)のペイロードデータとからなる。挿入される補助データフレームは、合計1540オクテット(12320ビット)からなる。オーディオデータシステムは、満足に動作するためには、非常に短い待ち時間(100μs未満)が必要である。全体的な待ち時間は、オーディオペイロードデータのトランスポートストリームにおける中断の最大継続時間に略々比例すると考えることができ、この中断は、例えば、フレーム間ギャップ及び連続したオーディオフレーム間の補助データフレームの伝送に起因するものである。待ち時間制約条件を満たすため

50

には、送信機の FIFO バッファは、少なくとも、オーディオデータの中断を埋めるのに十分な容量を有する必要がある。なお、送信機におけるバッファリングは、待ち時間を生じるので、バッファ容量は、できるだけ小さき維持することが望ましい。図 15 に示すように、バッファ容量は、1 つのオーディオフレームのオーディオペイロード伝送の最後と、次のオーディオフレームのオーディオペイロード伝送の最初との間のギャップを埋めるのに十分なデータをバッファリングできる容量でなければならず、さらに、補助データフレームの伝送のための所要時間とオーディオフレームヘッダを伝送するためにかかる時間を確保しなければならない。この構成では、2 つのオーディオフレームの間で最大サイズの補助データフレームが伝送されると仮定すると、オーディオデータ伝送における最大のギャップは、12.9 μs である。

10

## 【0061】

受信機において、様々な連続した出力オーディオデータ転送レートに対応するためには、フレーム間ギャップがあるのにも拘わらず、連続したデータ出力を維持するように、最大出力データ転送レートを検討しなければならない。なお、この最大データ転送レートより低いデータ転送レートで出力されるオーディオストリームについては、ダミーデータブロックを用いて、ペイロードデータフローを平滑化して、オーディオペイロードデータが、要求される連続した出力データ転送レートに一致するデータ転送レートで受信機に到着するようにすることができる。また、上述した待ち時間制約条件を満たすために必要とされる容量を超える容量のリンクでは、ダミーデータビットをオーディオフレームペイロードに挿入してもよい。ダミーデータからなるブロックのトランスポートデータストリームへの挿入は、図 11 を用いて説明した通りである。

20

## 【0062】

図 16 A 及び図 16 B は、本発明に基づき、図 11 に示すマルチプレクサ 1150 に供給されるデータブロックのシーケンスを示す図である。図 16 A では、8 個の入力データストリームの全てが最大データ転送レートで伝送されており、マルチプレクサ 1550 に供給されるデータブロックは、送信機の 8 つの FIFO バッファ 1110-1 ~ 1110-8 のそれぞれから読み出したオーディオペイロードデータのブロックからなる。この場合、ギガビットリンクの容量は、リンクの最大データ転送レートに対応することができ、如何なるダミーデータブロックもマルチプレクサ 1150 に供給されない。一方、図 16 B は、ストリーム 0 及びストリーム 6 が、最大データ転送レートを下回るオーディオフォーマットに関係するとともに、ストリーム 1 ~ ストリーム 5 及びストリーム 7 が最大データ転送レートを有する場合に、マルチプレクサ 1150 に供給されるデータブロックのシーケンスを示している。この場合、FIFO バッファの出力シーケンスは、図示するシーケンスの最後の方のストリーム 0 及びストリーム 6 において、オーディオペイロードを有するブロックを置換したヌルブロック（すなわち、ダミーデータブロック）を含んでいる。これらのヌルブロックは、バッファ順序シーケンスに従い、オーディオペイロードブロックを読み出すために、FIFO 読出コントローラ 1130 によってストリーム 0 の FIFO バッファ 1110-1 及びストリーム 6 の FIFO バッファ 1110-7 が選択されたときに、ストリーム 0 の FIFO バッファ 1110-1 及びストリーム 6 の FIFO バッファ 1110-7 に含まれているオーディオデータが不十分（所定の占有閾値以下）であると判定された場合に、挿入される。ここで、ダミーデータブロックを挿入するのではなく、図 16 B のシーケンスの最後に、ストリーム 5 のブロック、ストリーム 7 のブロック及びストリーム 1 のブロックを連続して出力すると、事実上、ストリーム 1 及びストリーム 7 の平均伝送レートを一時的に高めることができるが、この場合、受信機では、より多くのバッファ容量が必要となる。ダミーデータブロックを挿入することにより、様々なデータストリームに対する平均データ伝送レートを平滑化することができ、この結果、バッファリング要求を低減することができる。

30

40

## 【0063】

本発明は、ソフトウェア、プログラミング可能なハードウェア（例えば、FPGA、ASIC）、ハードウェア及びこれらの組合せのいずれにより実現してもよい。ソフトウェ

50

アコンポーネントを用いる場合、本発明には、このようなソフトウェアを提供する（例えば、記録媒体、伝送媒体等の）媒体も含まれる。

#### 【0064】

ここでは、図面を参照して本発明の実施の形態を例示的に詳細に説明したが、本発明はこれらの詳細な具体例に限定されるものではなく、当業者は、特許請求の範囲に定義されている本発明の範囲及び思想から逸脱することなく、ここに説明した実施の形態を様々に変更及び修正することができる。

#### 【図面の簡単な説明】

#### 【0065】

【図1】本発明に基づくルータのアーキテクチャを示すブロック図である。

10

【図2】ギガビットポイントツーポイント物理層リンクを実現するライブ音生成システムを図式的に示す図である。

【図3】ギガビットポイントツーポイント物理層リンクを実現する高分解能オーディオワークステーション構成を図式的に示す図である。

【図4】ギガビットポイントツーポイント物理層リンクを実現するオーディオ放送スタジオ構成を図式的に示す図である。

【図5】フレームヘッダ内の4つのベースクロックの全てのタイミング情報を含む、本発明に基づくオーディオフレーム構造を図式的に示す図である。

【図6】図5に示すタイミング情報ヘッダのうちの1つの内容を図式的に示す図である。

20

【図7】タイミング情報がどのように導出されるかを説明する図である。

【図8】ギガビットリンクの物理層にデータを送信し及びギガビットリンクの物理層からデータを受信するための構成を図式的に示す図である。

【図9】各オーディオデータストリームを4つの可能なベースサンプリングクロックの1つに関連付けるデータを含むコンフィグレーションデータを送信機及び受信機の間で通信するための処理を説明するフローチャートである。

【図10】オーディオベースクロックを再生するための受信機構成を図式的に示す図である。

【図11】本発明に基づくギガビットリンク送信機のバッファリング及びフレーム組立の構成を図式的に示す図である。

【図12】図11に示す送信機における、本発明に基づく伝送バッファリング及びフレームの組立処理のフローチャートである。

【図13】図11に示す送信機に対応する受信機のフレーム受信及びバッファリング構成の代表的部分を図式的に示す図である。

【図14A】オーディオフレームペイロードがギガビットリンクを介してどのように送信されるかを説明する図である。

【図14B】パケット化されたオーディオデータペイロードの瞬間的なデータフローを、8つのチャンネルのうち3つのチャンネルの連続したデータフローと共に図式的に示す図である。

【図15】2つのオーディオデータフレームと、挿入された補助データフレームとを含むギガビットリンク上のフレーム伝送シーケンスを示す図である。

30

【図16】本発明に基づき、図11に示すマルチプレクサ1150に供給されるデータブロックのシーケンスを図式的に示す図である。

40

【 図 1 】

【 図 2 】

【図3】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図 13】

【図 14 A】

【図 14 B】

【図 15】

【図16】

フロントページの続き

(72)発明者 ページ ミッ切尔

イギリス国 K T 1 3 O X W サリー、ウエイブリッジ、ブルックランズ、ザ ハイツ

(番地無し) ソニー ユナイテッド キングダム リミテッド内

F ターム(参考) 5K047 AA15 BB15 DD01 GG02 GG08

【外國語明細書】

2006121663000001.pdf

2006121663000002.pdf

2006121663000003.pdf

2006121663000004.pdf