(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4615241号

(P4615241)

(45) 発行日 平成23年1月19日(2011.1.19)

(24) 登録日 平成22年10月29日(2010.10.29)

(51) Int.Cl.

F 1

G 11 C 16/06 (2006.01)

G 11 C 16/02 (2006.01)G 11 C 17/00 631

G 11 C 17/00 612 Z

G 11 C 17/00 612 F

請求項の数 19 (全 18 頁)

(21) 出願番号 特願2004-107313 (P2004-107313)

(22) 出願日 平成16年3月31日 (2004.3.31)

(65) 公開番号 特開2004-311016 (P2004-311016A)

(43) 公開日 平成16年11月4日 (2004.11.4)

審査請求日 平成19年1月19日 (2007.1.19)

(31) 優先権主張番号 2003-021969

(32) 優先日 平成15年4月8日 (2003.4.8)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 2003-079510

(32) 優先日 平成15年11月11日 (2003.11.11)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

SAMSUNG ELECTRONICS

CO., LTD.

大韓民国京畿道水原市靈通区梅灘洞 416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do 442-742

(KR)

(74) 代理人 100086368

弁理士 萩原 誠

(72) 発明者 禹 東 ▲ヒュク▼

大韓民国ソウル冠岳区新林9洞 クンヨン

3次アパート1棟405号

最終頁に続く

(54) 【発明の名称】マルチチップでマルチセクタ消去動作モードを実行する半導体メモリチップ及びマルチチップパッケージ、及びマルチセクタ消去方法

## (57) 【特許請求の範囲】

## 【請求項 1】

マルチチップのマルチセクタ消去動作モードを実行する半導体メモリチップにおいて、アドレスカウントアップ信号とカレントチップ信号とに応答してアドレスロック信号を発生するようにするアドレスロックドライバと、前記アドレスロック信号に応答してチップ情報とセクタ情報とを有するアドレスを発生するカウンタと、

前記アドレスカウントアップ信号と、前記カレントチップ信号と、前記アドレスのセクタ情報が消去されるセクタに対応するか否かをチェックするセクタチェック信号とを発生する制御回路とを含み、

前記アドレスロック信号は、前記セクタ消去動作を実行している半導体メモリチップと前記セクタ消去動作を実行していない半導体メモリチップとで共有されることを特徴とする半導体メモリチップ。

## 【請求項 2】

前記制御回路は、チップ選択情報を有しており、該チップ選択情報が前記カウンタのチップ情報と一致する時に、セクタ情報をチェックすることを特徴とする請求項1に記載の半導体メモリチップ。

## 【請求項 3】

前記アドレスロックドライバの出力は、前記制御回路のチップ選択情報と前記カウンタのチップ情報とが一致しない時に、フローティング状態にあることを特徴とする請求項

1に記載の半導体メモリチップ。

【請求項4】

前記制御回路のチップ選択情報は、ヒューズまたはボンディングでハードコーディングされたオプションフラグ形態であることを特徴とする請求項2または3に記載の半導体メモリチップ。

【請求項5】

前記カウンタは、アドレスを順次に発生することを特徴とする請求項1に記載の半導体メモリチップ。

【請求項6】

前記カウンタで発生したアドレスのチップ情報は、最上位アドレスビットに該当することを特徴とする請求項5に記載の半導体メモリチップ。 10

【請求項7】

マルチチップのマルチセクタ消去動作モードを実行する半導体メモリチップにおいて、複数個のセクタからなるメモリセルアレイと、

消去するセクタ情報を有するレジスタと、

アドレスカウントアップ信号とカレントチップ信号とに応答してアドレスクロック信号を発生するようにするアドレスクロックドライバと、

前記アドレスクロック信号に応答してチップ情報とセクタ情報を有するアドレスを発生するカウンタと、

前記レジスタのセクタ情報を前記カウンタでのセクタ情報とが一致するか否かをチェックして、一致しない時には前記アドレスカウントアップ信号を発生し、一致する時には消去イネーブル信号を発生した後前記アドレスカウントアップ信号を発生する制御回路と、

前記消去イネーブル信号に応答して該当のセクタに対する消去動作を実行するコアドライバとを含み、

前記アドレスクロック信号は、前記セクタ消去動作を実行している半導体メモリチップと前記セクタ消去動作を実行していない半導体メモリチップとで共有されることを特徴とする半導体メモリチップ。

【請求項8】

前記制御回路は、チップ選択情報を有しており、該チップ選択情報が前記カウンタのチップ情報と一致する時に、セクタ情報をチェックすることを特徴とする請求項7に記載の半導体メモリチップ。 30

【請求項9】

前記アドレスクロックドライバの出力は、前記制御回路のチップ選択情報と前記カウンタのチップ情報とが一致しない時に、フローティング状態にあることを特徴とする請求項7に記載の半導体メモリチップ。

【請求項10】

前記制御回路のチップ選択情報は、ヒューズまたはボンディングでハードコーディングされたオプションフラグ形態であることを特徴とする請求項8または9に記載の半導体メモリチップ。

【請求項11】

前記カウンタは、アドレスを順次に発生することを特徴とする請求項7に記載の半導体メモリチップ。

【請求項12】

前記カウンタで発生したアドレスのチップ情報は、最上位アドレスビットに該当することを特徴とする請求項11に記載の半導体メモリチップ。

【請求項13】

マルチセクタ消去動作を実行するマルチチップパッケージにおいて、

制御信号を伝達する第1バスと、

アドレス及びデータを伝達する第2バスと、

前記第1バス及び前記第2バスに各々連結されて、前記マルチセクタ消去動作モードを 50

実行する複数の半導体メモリチップとを含み、

前記半導体メモリチップの各々は、

複数個のセクタからなるメモリセルアレイと、

消去するセクタ情報を有するレジスタと、

アドレスカウントアップ信号とカレントチップ信号とに応答してアドレスロック信号

を発生するようにするアドレスクロックドライバと、

前記アドレスロック信号に応答してチップ情報とセクタ情報を有するアドレスを発生するカウンタと、

前記レジスタのセクタ情報を前記カウンタでのセクタ情報とが一致するか否かをチェックして、一致しない時には前記アドレスカウントアップ信号を発生し、一致する時には消去イネーブル信号を発生した後前記アドレスカウントアップ信号を発生する制御回路と、

前記消去イネーブル信号に応答して、該当のセクタに対する消去動作を実行するコアドライバとを含み、

前記アドレスロック信号は、前記セクタ消去動作を実行している半導体メモリチップと前記セクタ消去動作を実行していない半導体メモリチップとで共有されることを特徴とするマルチチップパッケージ。

#### 【請求項 1 4】

前記制御回路は、チップ選択情報を有しており、該チップ選択情報が前記カウンタのチップ情報を一致する時に、セクタ情報をチェックすることを特徴とする請求項 1 3 に記載のマルチチップパッケージ。

#### 【請求項 1 5】

前記アドレスクロックドライバの出力は、前記制御回路のチップ選択情報と前記カウンタのチップ情報を一致しない時に、フローティング状態にあることを特徴とする請求項 1 3 に記載のマルチチップパッケージ。

#### 【請求項 1 6】

前記制御回路のチップ選択情報は、ヒューズまたはボンディングでハードコーディングされたオプションフラグ形態であることを特徴とする請求項 1 4 または 1 5 に記載のマルチチップパッケージ。

#### 【請求項 1 7】

前記カウンタは、アドレスを順次に発生することを特徴とする請求項 1 3 に記載のマルチチップパッケージ。

#### 【請求項 1 8】

前記カウンタで発生したアドレスのチップ情報は、最上位アドレスビットに該当することを特徴とする請求項 1 7 に記載のマルチチップパッケージ。

#### 【請求項 1 9】

複数個のセクタからなるメモリセルアレイと、

消去するセクタ情報を有するレジスタと、

アドレスカウントアップ信号とカレントチップ信号とに応答して、セクタ消去動作を実行している半導体メモリチップと前記セクタ消去動作を実行していない半導体メモリチップとで共有されるアドレスロック信号を発生するようにするアドレスクロックドライバと、

前記アドレスロック信号に応答してチップ情報とセクタ情報を有するアドレスを発生するカウンタと、

前記アドレスカウントアップ信号と、前記カレントチップ信号と、前記アドレスのセクタ情報を消去されるセクタに対応するか否かをチェックするセクタチェック信号とを発生する制御回路とを備えた複数の半導体メモリチップで構成されたマルチチップパッケージのマルチセクタ消去方法において、

前記カウンタのアドレスを初期化する段階と、

前記カウンタのチップ情報を前記制御回路のチップ選択情報とが一致するか否かを判断する段階と、

10

20

30

40

50

前記チップ情報が前記チップ選択情報と一致しない場合に、最後のセクタでなければ、前記カウンタのアドレスを増加する段階と、

前記チップ情報と前記チップ選択情報とが一致する場合に、前記カウンタのセクタ情報と前記レジスタのセクタ情報とが一致するか否かを判断する段階と、

前記セクタ情報が一致しない場合に、最後のセクタでなければ、前記カウンタのアドレスを増加する段階と、

前記セクタ情報が一致する場合にセクタ消去動作を実行する段階と、

消去されたセクタが前記最後のセクタでない場合に、前記カウンタのアドレスを増加する段階と、

前記消去されたセクタが最後のセクタであれば終了する段階とを含むことを特徴とするマルチセクタ消去方法。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体メモリ装置に関するものであり、さらに具体的には、マルチチップでマルチセクタ消去動作モードを支援する半導体メモリチップ及びマルチチップパッケージ、及びマルチセクタ消去方法に関するものである。

【背景技術】

【0002】

フラッシュメモリのセルは、よく知られたようにフローティングゲートとコントロールゲートを有する。フラッシュメモリセルの消去動作は、コントロールゲートにマイナスの高電圧を印加してF-Nトンネリング現象を誘発させることによって、フローティングゲート内の電子を基板に放出されることによってなされる。フラッシュメモリセルは高集積化のためにバルク領域を共有するので、一つのセクタに含まれるセルは同時に消去される。したがって、フラッシュメモリのセルアレイは消去の単位になる多数のセクタで構成されている。

【0003】

CPUまたはコントローラが消去動作のためのコマンドと消去するセクタアドレスを入力すれば、チップ内のアドレスカウンタでアドレスを順次に増加させながら、各セクタに対する消去動作を実施する。このように一回に多数のセクタを消去する消去動作をマルチセクタ消去動作という。 30

【0004】

マルチセクタ消去動作を実施するためには、チップ内に、消去しようとするセクタアドレスを貯蔵するレジスタがセクタ数だけ具備されなければならない、かつセクタアドレスを一つずつ増加させながら消去するセクタであるか否かを検出し、前記検出結果によって消去動作を実行させる手段が必要である。

【0005】

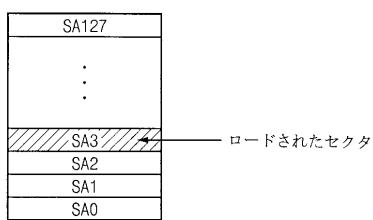

図1は單一チップでマルチセクタ消去動作を説明するための概念図である。図1に示した例は128個のセクタで構成されたフラッシュメモリであり、各セクタにはセクタアドレスSA0～SA127が割り当てられており、セクタアドレスSA3に該当するセクタを消去しようとしている。 40

【0006】

消去動作を命じるコマンドと消去するセクタアドレスは外部コントローラによって入力される。この時に、コントローラは、一つのセクタアドレスを入力して消去動作が行われるようにすることもでき、いくつかのセクタアドレスを入力して、一回に多くのセクタを消去することもできる。このように消去しようとするセクタアドレスを入力することをセクタローディングと呼ぶ。

【0007】

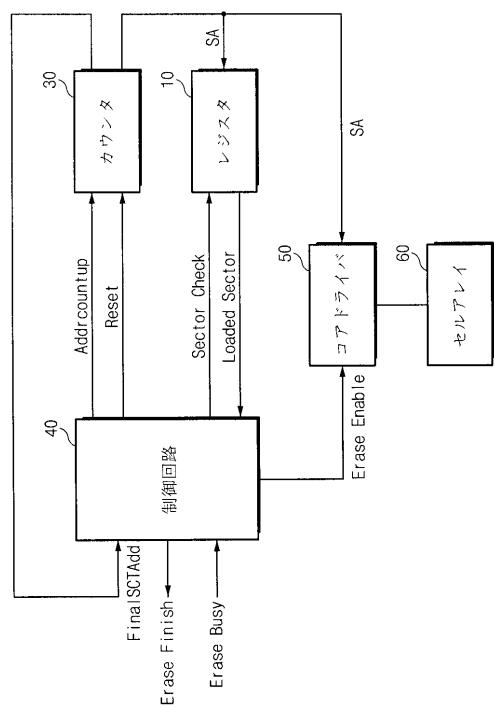

図2は、單一チップでマルチセクタ消去動作を説明するためのブロック図である。図2を参照すると、單一チップでマルチセクタ消去動作モードを支援する半導体メモリチップ

10

20

30

40

50

は、複数個のセクタからなるメモリセルアレイ 60 と、消去するセクタアドレスを貯蔵するレジスタ 10 と、アドレスカウントアップ信号に応答してアドレスを順次に発生するカウンタ 30 と、前記レジスタ 10 に貯蔵されたセクタアドレスと前記カウンタ 30 で発生されたセクタアドレスが一致するか否かをチェックして、一致する場合には消去イネーブル信号を発生し、一致しない場合には前記アドレスカウントアップ信号を発生する制御回路 40 と、前記消去イネーブル信号に応答して該当セクタに対する消去動作を実行するコアドライバ 50 とを含む。

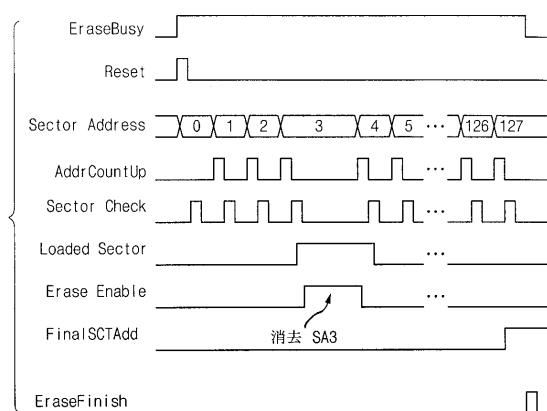

#### 【 0 0 0 8 】

図 3 は单一チップでマルチセクタ消去動作を説明するためのタイミング図である。図 2 と図 3 を参照して、单一チップでマルチセクタ消去動作を説明すれば、次の通りである。

10

#### 【 0 0 0 9 】

外部コントローラは消去動作を命ずるコマンドと消去するセクタアドレス SA 3 を入力する。この時に、外部コントローラは一つのセクタアドレスを入力して、一つのセクタを消去することができ、いくつかのセクタアドレスを一回に入力して、多くのセクタを消去することもできる。後者のように、いくつかのセクタが一回に消去されることを单一チップでのマルチセクタ消去動作という。

#### 【 0 0 1 0 】

消去命令が入力されれば、チップ内部のレジスタ 10 に消去するセクタアドレス SA 3 が貯蔵される。前記レジスタ 10 は各セクタに一つずつ割り当てられたレジスタであり、消去するセクタに割り当てられたレジスタ値は“1”にセッティングされる。実際の消去動作時に、各セクタを消去するか否かはこのレジスタ値を通じて判断する。

20

#### 【 0 0 1 1 】

消去動作が始まれば、チップ内部の制御回路 40 はアドレスカウンタ 30 を‘0’に初期化する。例えば、128(27)個のセクタのメモリセルの場合は、セクタアドレス SA <6 : 0>を‘0’に初期化する。前記制御回路 40 はセクタチェック信号 S e c t o r C h e c k を発生して、一番目のセクタアドレス SA 0 に対する消去可否を判断する。一番目のセクタアドレス SA 0 が前記レジスタ 10 に貯蔵されたセクタアドレス SA 3 と一致しないので、前記制御回路 40 はアドレスカウントアップ信号 A d d r C o u n t U p を発生する。

#### 【 0 0 1 2 】

30

この時に、カウンタ 30 はセクタアドレスを増加させる。前記制御回路 40 は次のセクタアドレスに対してセクタチェックを続ける。レジスタ 10 に貯蔵されたセクタアドレス SA 3 とカウンタ 30 で発生したセクタアドレス SA 3 が一致する場合には、セクタチェック時にロードセクタ信号 L o a d e d S e c t o r が発生される。この時に、制御回路 40 は消去イネーブル信号 E r a s e E n a b l e を活性化して、コアドライバ 50 が該当のセクタに対する消去動作を実行するようとする。

#### 【 0 0 1 3 】

前記動作の繰り返しを通じてセクタアドレスが最後に至れば、前記カウンタ 30 は最終セクタアドレス信号 F i n a l S C T A d d を発生する。すると、前記制御回路 40 は消去終了信号 E r a s e F i n i s h を発生することによって消去動作を終了する。

40

#### 【 0 0 1 4 】

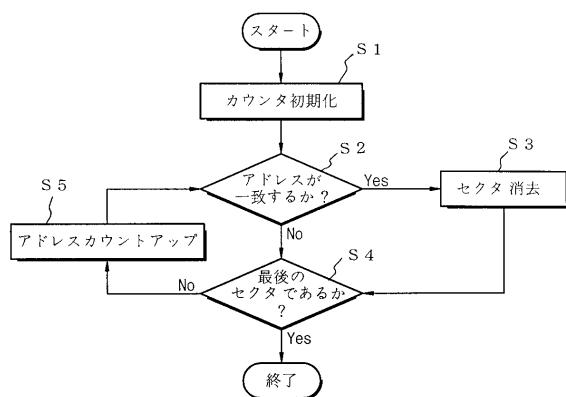

図 4 は单一チップのマルチセクタ消去方法を説明するための順序図である。図 4 を参照して单一チップのマルチセクタ消去動作を説明すれば、次の通りである。

#### 【 0 0 1 5 】

マルチセクタ消去動作は外部から消去動作コマンドと消去するアドレス情報が入力されて消去ビジー信号 E r a s e B u s y が活性化されれば始まる。

#### 【 0 0 1 6 】

第 1 段階 S 1 は、カウンタのアドレスを‘0’に初期化する段階である。第 2 段階 S 2 は、前記カウンタで発生されたセクタアドレスとレジスタに貯蔵されたセクタアドレスが一致するか否かを判断する段階である。第 3 段階 S 3 は、前記セクタアドレスが一致する

50

場合にはセクタ消去動作を実行する段階である。第4段階S4は、セクタアドレスが一致しない場合、またはセクタ消去動作を実行した場合に、最後のセクタであるか否かを判断する段階である。最後のセクタであるか否かを判断して、最後のセクタであれば終了する。最後のセクタではなければ、第5段階S5でアドレスをカウントアップして、セクタアドレスが一致するか否かを判断する第2段階S2に戻る。

#### 【0017】

すべてのセクタに対する消去動作が終われば、消去終了信号Eraser Finishが発生して消去動作が終わる。

#### 【0018】

図1乃至図4では、單一チップでのマルチセクタ消去動作に対して説明した。しかし、最近は、半導体メモリの容量を増やすために、いくつかの同一のチップを一つのパッケージに実装して、一つのメモリシステムを構成する方法が研究されている。この時に、各半導体メモリチップはアドレス及びデータバスと制御バスとを共有して、2倍または4倍の容量を有するメモリチップのように動作する。

10

#### 【0019】

そこで、上述の單一チップでのマルチセクタ消去動作を拡張して、マルチチップでマルチセクタ消去動作を実現することができる半導体メモリチップ、または前記半導体メモリチップで構成されたマルチチップパッケージが出現することが望まれている。

20

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0020】

本発明は上記の点に鑑みなされたもので、第1の目的は、マルチチップでマルチセクタ消去動作を実行することができる半導体メモリチップを提供することにある。

#### 【0021】

本発明の第2の目的は、前記半導体メモリチップで構成されたマルチチップパッケージを提供することにある。

#### 【0022】

本発明の第3の目的は、前記マルチチップパッケージでマルチセクタ消去動作方法を提供することにある。

30

#### 【課題を解決するための手段】

#### 【0023】

本発明は、マルチチップでマルチセクタ消去動作を実行することができる半導体メモリチップと、前記半導体メモリチップで構成されたマルチチップパッケージと、前記マルチチップパッケージでのマルチセクタ消去方法とに関するものである。

#### 【0024】

本発明によるマルチチップでマルチセクタ消去動作モードを支援する半導体メモリチップは、アドレスカウントアップ信号に応答して前記マルチチップで同時にアドレスクロック信号を発生するようにするアドレスクロックドライバと、前記アドレスクロック信号に応答してチップ情報とセクタ情報とを有するアドレスを発生するカウンタと、前記アドレスのチップ情報が消去されるセクタに対応するか否かをチェックして、前記アドレスカウントアップ信号を発生する制御回路とを含むことを特徴とする。

40

#### 【0025】

好ましい形態として、前記制御回路は、チップ選択情報を有しており、該チップ選択情報が前記カウンタのチップ情報と一致する時に、セクタ情報をチェックする。

#### 【0026】

好ましい形態として、前記アドレスクロックドライバの出力は、前記制御回路のチップ選択情報と前記カウンタのチップ情報とが一致しない時に、フローティング状態にある。

#### 【0027】

好ましい形態として、前記制御回路のチップ選択情報は、ヒューズまたはボンディングでハードコーディングされたオプションフラグ形態である。

50

**【0028】**

好ましい形態として、前記カウンタは、アドレスを順次に発生する。

**【0029】**

好ましい形態として、前記カウンタで発生したアドレスのチップ情報は、最上位アドレスビットに該当する。

**【0030】**

本発明の他の特徴によるマルチチップでマルチセクタ消去動作モードを支援する半導体メモリチップは、複数個のセクタからなるメモリセルアレイと、消去するセクタ情報を有するレジスタと、アドレスカウントアップ信号に応答して前記マルチチップで同時にアドレスクロック信号を発生するようにするアドレスクロックドライバと、前記アドレスクロック信号に応答してチップ情報とセクタ情報を有するアドレスを発生するカウンタと、前記レジスタのセクタ情報を前記カウンタでのセクタ情報とが一致するか否かをチェックして、一致する時には消去イネーブル信号を発生し、一致しない時には前記アドレスカウントアップ信号を発生する制御回路と、前記消去イネーブル信号に応答して該当のセクタに対する消去動作を実行するコアドライバとを含むことを特徴とする。10

**【0031】**

好ましい形態として、前記制御回路は、チップ選択情報を有しており、該チップ選択情報が前記カウンタのチップ情報と一致する時に、セクタ情報をチェックする。

**【0032】**

好ましい形態として、前記アドレスクロックドライバの出力は、前記制御回路のチップ選択情報と前記カウンタのチップ情報とが一致しない時に、フローティング状態にある。20

**【0033】**

好ましい形態として、前記制御回路のチップ選択情報は、ヒューズまたはボンディングでハードコーディングされたオプションフラグ形態である。

**【0034】**

好ましい形態として、前記カウンタは、アドレスを順次に発生する。

**【0035】**

好ましい形態として、前記カウンタで発生したアドレスのチップ情報は、最上位アドレスビットに該当する。

**【0036】**

本発明によるマルチセクタ消去動作を実行するマルチチップパッケージは、制御信号を伝達する第1バスと、アドレス及びデータを伝達する第2バスと、前記第1バス及び前記第2バスに各々連結されて前記マルチセクタ消去動作モードを支援する複数の半導体メモリチップとを含み、前記各々の半導体メモリチップは、複数個のセクタからなるメモリセルアレイと、消去するセクタ情報を有するレジスタと、アドレスカウントアップ信号に応答して前記マルチチップで同時にアドレスクロック信号を発生するようにするアドレスクロックドライバと、前記アドレスクロック信号に応答してチップ情報とセクタ情報を有するアドレスを発生するカウンタと、前記レジスタのセクタ情報を前記カウンタでのセクタ情報をとが一致するか否かをチェックして、一致する時には消去イネーブル信号を発生し、一致しない時には前記アドレスカウントアップ信号を発生する制御回路と、前記消去イネーブル信号に応答して、該当のセクタに対する消去動作を実行するコアドライバとを含むことを特徴とする。3040

**【0037】**

好ましい形態として、前記制御回路は、チップ選択情報を有しており、該チップ選択情報が前記カウンタのチップ情報と一致する時に、セクタ情報をチェックする。

**【0038】**

好ましい形態として、前記アドレスクロックドライバの出力は、前記制御回路のチップ選択情報と前記カウンタのチップ情報が一致しない時に、フローティング状態にある。

**【0039】**

好ましい形態として、前記制御回路のチップ選択情報は、ヒューズまたはボンディング50

でハードコーディングされたオプションフラグ形態である。

**【0040】**

好ましい形態として、前記カウンタは、アドレスを順次に発生する。

**【0041】**

好ましい形態として、前記カウンタで発生したアドレスのチップ情報は、最上位アドレスビットに該当する。

**【0042】**

本発明によるマルチチップパッケージのマルチセクタ消去方法は、カウンタのアドレスを初期化する段階と、前記カウンタのチップ情報と制御回路のチップ選択情報とが一致するか否かを判断する段階と、前記チップ情報と前記チップ選択情報とが一致する場合に、前記カウンタのセクタ情報とレジスタのセクタ情報とが一致するか否かを判断する段階と、前記セクタ情報が一致する場合に、セクタ消去動作を実行する段階と、前記消去されたセクタが最後のセクタであれば終了する段階とを含むことを特徴とする。

10

**【0043】**

好ましい形態として、前記チップ情報と前記チップ選択情報とが一致しない場合に、最後のセクタでなければ、前記カウンタのアドレスを増加し、最後のセクタであれば終了する段階を含む。

**【0044】**

好ましい形態として、前記セクタ情報が一致しない場合に、最後のセクタでなければ前記カウンタのアドレスを増加し、最後のセクタであれば終了する段階を含む。

20

**【0045】**

好ましい形態として、前記消去されたセクタが最後のセクタでない場合に、前記カウンタのアドレスを増加する段階を含む。

**【発明の効果】**

**【0046】**

本発明によると、同一の複数の半導体メモリチップを一つのパッケージに実装して、マルチセクタ消去動作モードを実行するマルチチップパッケージを構成することができる。

**【発明を実施するための最良の形態】**

**【0047】**

以下、本発明の望ましい実施の形態を添付図面を参照して詳細に説明する。

30

**【0048】**

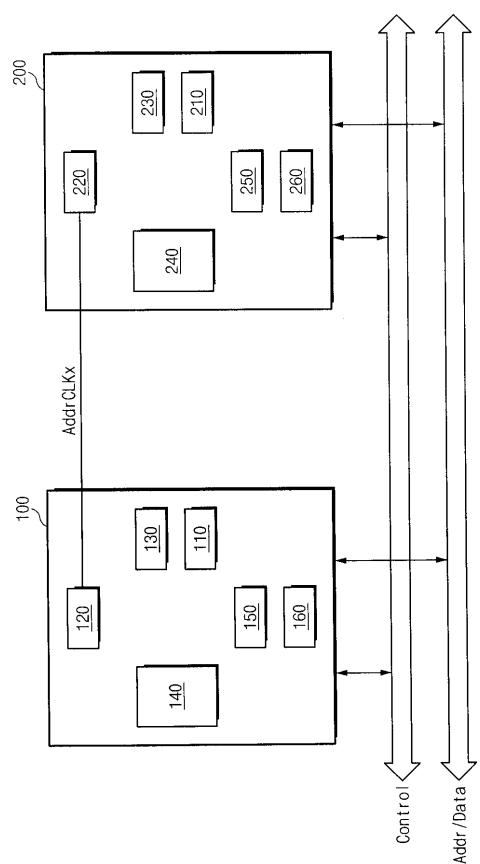

図5は本発明によるマルチセクタ消去動作を実行するマルチチップパッケージを示すブロック図である。本発明によるマルチチップパッケージは同一の構造を有する二つ以上の半導体メモリチップで構成され、一つのパッケージに実装される。以下、図5に示したように、二つの半導体メモリチップ100、200に対してだけ説明するが、二つ以上の半導体メモリチップに対しても同一の原理が適用されることは自明である。

**【0049】**

図5を参照すると、半導体メモリチップ100、200はアドレス/データバスと制御バスとを共有して容量が大きい一つのマルチチップパッケージを構成する。外部から消去動作コマンドと消去するアドレス情報が入力されれば、消去開始信号Erase Bus yが活性化されて第1チップ100から順次に消去動作が開始される。消去動作の開始は外部コントローラから与えられる消去開始コマンドによってなされることもでき、チップ内にタイマを置いて最終的に消去するセクタアドレスが入力された後から、一定の時間が経過した後に消去動作を開始させることもできる。

40

**【0050】**

本発明によるマルチチップパッケージはすべてのチップ100、200にアドレスクロック信号Addr CLK xが同時に印加されることを特徴とする。これを通じて第1チップ100の消去動作が終わった後に、すぐに第2チップ200の消去動作が実行される。前記第1チップ100及び第2チップ200に対する内部構造及び動作原理は後述する図7を参照して詳細に説明する。

50

**【 0 0 5 1 】**

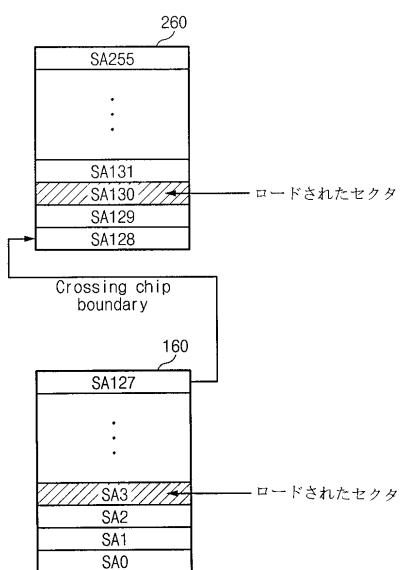

図6はマルチチップパッケージでマルチセクタ消去動作を示す概念図である。図6は各々128個のセクタで構成された二つの半導体メモリチップを一つのパッケージに実装した例である。前記マルチチップパッケージは外部的に256個のセクタを有する一つの半導体メモリチップとして動作する。第1チップのセルアレイ160と第2チップのセルアレイ260は同一の内部構造を有する。

**【 0 0 5 2 】**

図6を参照すると、消去のためにロードされたセクタは二つであり、各々SA3とSA130に該当するセクタである。これらセクタに対する情報は後述するレジスタ110、210に貯蔵される。

10

**【 0 0 5 3 】**

本発明によるマルチチップパッケージでセクタ消去動作を実行するアルゴリズムは上述の単一チップシステムでのセクタ消去動作と大部分同一である。ただ、マルチチップパッケージにおいては、各チップを区分する手段とアドレスロック信号を共有する手段とをさらに要する。第1チップ100のすべてのセクタに対する消去動作が完了した後に、すぐに第2チップ200に対するセクタ消去動作が実行されるようにするためである。

**【 0 0 5 4 】**

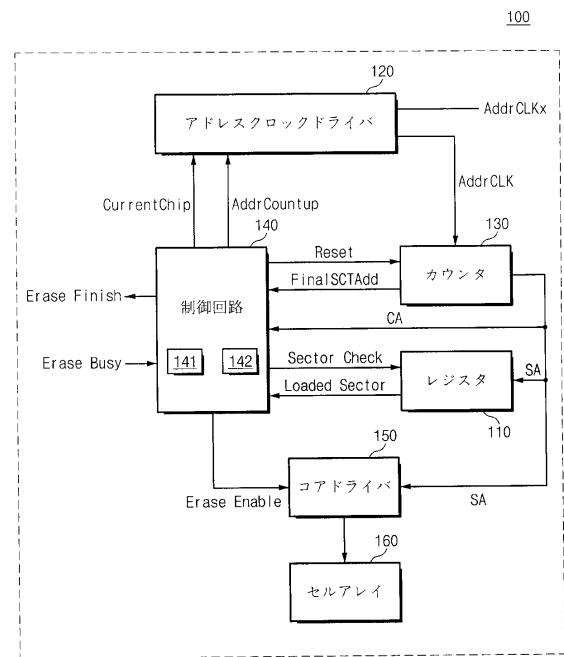

図7は本発明によるマルチチップのマルチセクタ消去動作を実現するためのチップの内部構造を示すブロック図である。図7では、第1チップ100の内部構成のみを示すが、第2チップ200もこれと同一の内部構成を有する。

20

**【 0 0 5 5 】**

マルチチップパッケージを構成するための前記第1チップ100は、レジスタ110とアドレスロックドライバ120とカウンタ130と制御回路140とコアドライバ150とセルアレイ160とを含む。前述のように、第2チップ200も第1チップ100と同一構成であるが、図5に示すように、第2チップ200の各部には、第1チップ100の各部の百番台の符号から2百番台の符号に変えて第1チップ100の各部と同一符号を付す。すなわち、210は第2チップ200のレジスタ、220は第2チップ200のアドレスロックドライバ、230は第2チップ200のカウンタ、240は第2チップ200の制御回路、250は第2チップ200のコアドライバ、260は第2チップ200のセルアレイである。

30

**【 0 0 5 6 】**

前記第1チップ100の構成要素の各々は次の通りである。

**【 0 0 5 7 】**

前記レジスタ110には消去するセクタアドレス(例えば、SA3とSA130)に対する情報が貯蔵される。前記レジスタ110は各セクタごとに一つずつ割り当てられたレジスタであり、消去するセクタに割り当てられたレジスタ値は“1”にセッティングされる。実際の消去動作時に、各セクタを消去するか否かはこのレジスタ値を通じて判断される。

**【 0 0 5 8 】**

前記アドレスロックドライバ120はアドレスカウントアップ信号AddrCountUpとカレントチップ信号CurrentChipに応答してアドレスロック信号AddrCLKを発生する。アドレスロック信号AddrCLKはカウンタ130に伝達される。

40

**【 0 0 5 9 】**

前記アドレスロックドライバ120で発生したアドレスロック信号AddrCLKはすべてのチップのカウンタ130、230に同時に伝達される。これは第1チップ100に対する消去動作が完了すれば、すぐに第2チップ200に対する消去動作が実行されるようになるためである。前記アドレスロックドライバ120の内部構成及び動作原理は後述する図8を参照して詳細に説明する。

**【 0 0 6 0 】**

50

前記カウンタ130は前記アドレスクロック信号AddrCLKに応答して順次にアドレスを増加させる。マルチチップパッケージにおいて、前記カウンタ130で発生されたアドレスはセクタアドレス(Sector Address, SA)だけではなく、各チップを区分するチップアドレス(Chip Address, CA)を含む。

#### 【0061】

実施の形態として、前記チップアドレスは前記カウンタ130で発生されたアドレスビットのうち最上位アドレスビットに割り当てられる。2-チップシステムを例としてあげて説明すると、各々のチップが128(27)個のセクタの場合に、チップアドレスのビット数は1ビットでありSA<7>に該当し、セクタアドレスはSA<6:0>になる。4-チップシステムの場合には、チップアドレスのビット数は2ビットであり、SA<8:7>に該当し、セクタアドレスはSA<6:0>になる。

10

#### 【0062】

したがって、各々のチップが2N個のセクタの2-チップシステムの場合に、前記カウンタ130、230では(N+1)ビットに該当するアドレスが発生される。ここで、チップアドレスに該当するSA<N>は制御回路140に入力され、セクタアドレスに該当するSA<N-1:0>は前記レジスタ110とコアドライバ150に入力される。

#### 【0063】

前記制御回路140は前記レジスタ110、前記アドレスクロックドライバ120、前記カウンタ130、及び前記コアドライバ150と各種制御信号を取り交わして、マルチセクタ消去動作を実行する。前記制御回路140に対する動作説明は図10を参照して説明する。

20

#### 【0064】

前記制御回路140は消去開始信号EraseBusyに応答して前記カウンタ130を初期化する。図10を参照すると、消去開始信号EraseBusyがイネーブルされれば、前記カウンタ130を初期化するリセット信号Resetが活性化されて、前記カウンタ130を初期化する。この時に、初期化過程はマルチチップパッケージ内にあるすべてのカウンタ130、230で同時に実行される。

#### 【0065】

前記制御回路140は前記カウンタ130で発生されたチップアドレス(CA; SA<7>=0)を見て、前記チップアドレスが該当チップを示すか否かを判断する。図10を参照すると、第1チップ100のチップアドレスはSA<7>=0であり、第2チップ200のチップアドレスはSA<7>=1である。したがって、第1チップ100だけチップアドレスが一致するので、図10のように、第1カレントチップ信号CurrentChip1はイネーブルされ、第2カレントチップ信号CurrentChip2はディセーブルされる。

30

#### 【0066】

前記制御回路140は前記レジスタ110にセクタチェック信号SectorCheckを発生して前記レジスタ110に貯蔵されたセクタアドレスSA3と前記カウンタ130で発生したセクタアドレスSA0が一致するか否かをチェックする。この場合はセクタアドレスが一致しないので、前記制御回路140はアドレスカウントアップ信号AddrCountUpを活性化して前記カウンタ130のアドレスを増加させる。

40

#### 【0067】

もし、前記レジスタ110に貯蔵されたセクタアドレスSA3と前記カウンタ130で発生したセクタアドレスSA3が一致すれば、前記制御回路140は前記レジスタ110から発生されたロードセクタ信号LoadedSectorに応答して消去イネーブル信号EraseEnableを活性化し、前記セクタアドレスSA3に該当するセクタを消去する。

#### 【0068】

前記のような過程を繰り返して第1チップ100の最後のセクタアドレスSA127に対する消去動作が実行された場合には、前記カウンタ130で発生されたチップアドレス

50

が  $S A < 7 > = 1$  になる。すると、第 1 カレントチップ信号 Current Chip 1 がディセーブルされ、第 2 カレントチップ信号 Current Chip 2 がイネーブルされて、第 2 チップ 200 に対する消去動作が開始される。

#### 【0069】

2 - チップシステムを例としてあげて説明すると、一つのチップが 128(27) 個のセクタの場合に、チップアドレス  $S A < 7 >$  が ‘0’ である時は、第 1 チップ 100 でだけセクタチェックが実行され、セクタチェック結果消去されるセクタであると判断されれば、消去イネーブル信号 Erase Enable が活性化されて消去動作を実行する。

#### 【0070】

前記コアドライバ 150 は前記カウンタ 130 で発生されたセクタアドレスを参照して消去動作に必要な高電圧を前記セルアレイ 160 の選択されたセクタに印加する。 10

#### 【0071】

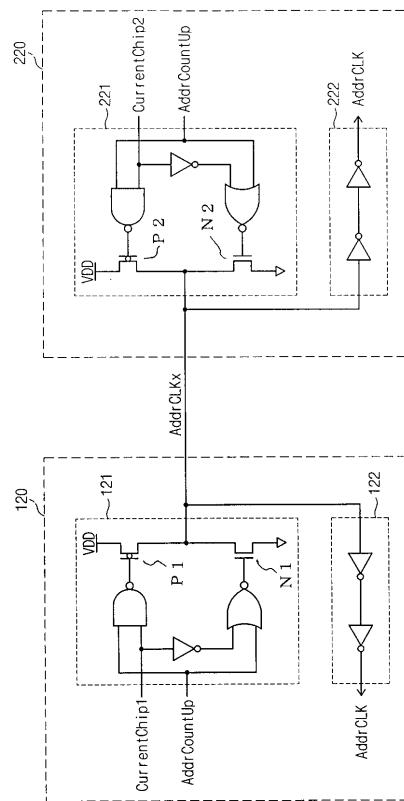

図 8 は図 5 および図 7 のアドレスクロックドライバ 120、120 の望ましい実施の形態を示す回路図である。図 8 では、2 - チップシステムでのアドレスクロックドライバを示す。アドレスクロックドライバ 120、220 はドライバ 121、221 とバッファ 122、222 で構成される。マルチチップパッケージでマルチセクタ消去動作を実行するためにはすべてのチップでアドレスが同時に増加しなければならない。

#### 【0072】

カウンタ 130 で発生したチップアドレス  $S A < 7 >$  が該当チップのチップアドレスと一致すれば、第 1 カレントチップ信号 Current Chip 1 がイネーブルされて、前記アドレスクロックドライバ 120 に供給される。前記第 1 カレントチップ信号 Current Chip 1 がイネーブルされた状態でアドレスカウントアップ信号 Addr Count Up が活性化されれば、図 8 のように、アドレスクロックドライバ 120 の PMOS トランジスタ P1 はターンオンされ、NMOS トランジスタ N1 はターンオフされる。したがって、電源電圧 VDD が第 1 チップ 100 と第 2 チップ 200 のバッファ 122、222 に同時に供給されて、アドレスクロック信号 Addr CLK を発生する。アドレスクロック信号 Addr CLK は第 1 チップ 100 と第 2 チップ 200 のカウンタ 130、230 に同時に供給される。

#### 【0073】

この時に、第 2 カレントチップ信号 Current Chip 2 はディセーブルされた状態にあるので、第 2 チップ 200 のアドレスクロックドライバ 220 の PMOS トランジスタ P2 と NMOS トランジスタ N2 がターンオフされて、出力はフローティング状態にあるようになる。したがって、第 2 チップ 200 は第 1 チップ 100 からアドレスクロック信号 Addr CLK を受けて前記バッファ 222 を通じてカウンタ 230 のアドレスを増加させる。結果的に、アドレスクロック信号 Addr CLK を第 1 チップ 100 と第 2 チップ 200 で共有することによって、第 1 チップ 100 に対するセクタ消去動作が完了した後に、すぐに第 2 チップ 200 に対するセクタ消去動作が実行されるようになる。 30

#### 【0074】

第 1 カレントチップ信号 Current Chip 1 がディセーブルされ、第 2 カレントチップ信号 Current Chip 2 がイネーブルされた場合には、第 2 チップ 200 のアドレスクロックドライバ 220 で供給されたアドレスクロック信号 Addr CLK を共有するようになる。 40

#### 【0075】

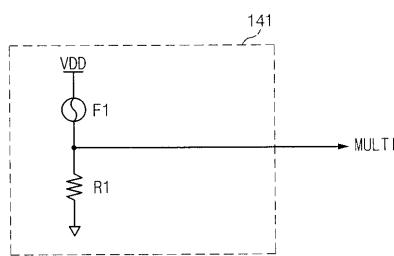

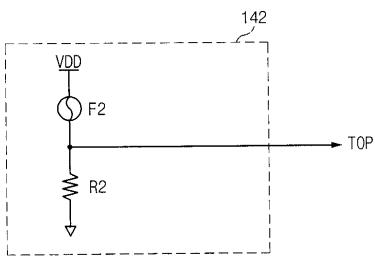

図 9 (A) 及び図 9 (B) は制御回路 140、240 に設けられる第 1 及び第 2 フラグ発生回路の望ましい実施の形態を示す回路図である。第 1 フラグ発生回路 141 は半導体メモリチップ 100、200 がマルチチップパッケージを構成するチップであるか否かを知らせる信号 MULTI を出力し、第 2 フラグ発生回路 142 はどの半導体メモリチップ 100、200 がアドレス領域を基準に上位領域に対応するか否かを示す信号 TOP ( すなわちチップ選択信号 ) を出力する。

#### 【0076】

前記第1フラグ発生回路141は該当チップがマルチチップパッケージの一部で動作するか否かを示すためのものである。マルチチップの一部で動作する場合にはヒューズF1が導通状態に維持されて信号MULTIが‘1’にセッティングされ、單一チップの場合にはヒューズF1が切断されて信号MULTIが‘0’にセッティングされており、前記制御回路140、240に伝達される。

#### 【0077】

第2フラグ発生回路142は該当チップが第1チップ100と第2チップ200のうちどのチップに該当するかを示すためのものである。第1チップ100である場合には、ヒューズF2が切断されて信号TOPが‘0’にセッティングされ、第2チップ200である場合には、ヒューズF2が導通状態に維持されて信号TOPが‘1’にセッティングされている。もし4-チップシステムの場合であれば、該当チップがどのチップに該当するかを示すために第2フラグ発生回路142は2ビットを有するようになる。10

#### 【0078】

前記第1及び第2フラグ発生回路141、142は各チップ内にヒューズまたはボンディングでハードコーディングされたオプションフラグ形態で存在する。

#### 【0079】

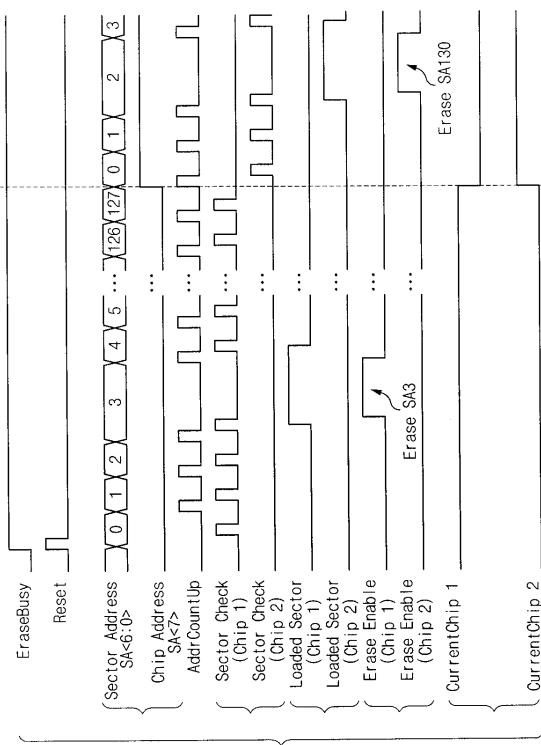

図10はマルチチップパッケージにおいて、マルチセクタ消去動作を説明するためのタイミング図である。

#### 【0080】

消去開始信号Eraser Busyがイネーブルされれば、前記制御回路140はリセット信号Resetを発生して前記カウンタ130を初期化する。この時に、チップアドレスSA<7>=0であるので、第1チップ100だけでセクタチェック信号Sector Checkが各々のアドレスごとに発生される。セクタチェックの結果、ローディングされたセクタアドレスSA3ではなければ、前記制御回路140はアドレスカウントアップ信号AddrCountUpを発生して、セクタアドレスを一つずつ増加させる。セクタチェックの結果、ローディングされたセクタアドレスSA3であると判断されれば、コードセクタ信号Loaded Sectorがイネーブルされて、該当セクタアドレスSA3に貯蔵されたデータを消去するように消去イネーブル信号Eraser Enableが発生される。消去イネーブル信号Eraser Enableが発生されれば、消去動作を実行する。20

#### 【0081】

第1チップ100に対する消去動作が実行される間に、第2チップ200の制御回路240はセクタチェック信号Sector Checkと消去イネーブル信号Eraser Enableを発生しない。しかし、アドレスが増加して第2チップ200の一番目のセクタアドレスであるSA128に至れば、チップアドレスSA<7>は‘1’に変更され、これによって、セクタチェックは第2チップ200でだけ生じるようになる。セクタチェックの結果、ローディングされたセクタSA130であると判断されれば、第1チップ100と同一のセクタ消去動作が実行される。この時に、第1チップ100のセクタチェック信号Sector Check及び消去イネーブル信号Eraser Enableは活性化されない。30

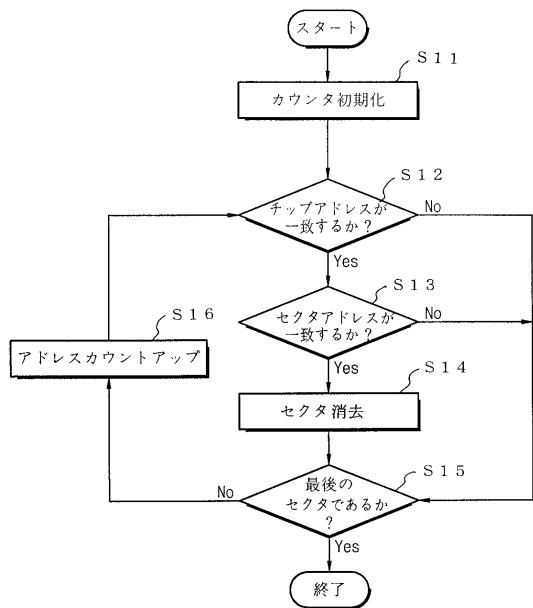

#### 【0082】

図11は本発明によるマルチチップパッケージのマルチセクタ消去方法を示す順序図である。図11を参照して本発明によるマルチチップパッケージのマルチセクタ消去動作を説明すれば次の通りである。

#### 【0083】

本発明によるマルチセクタ消去動作は外部から消去動作コマンドと消去するアドレス情報が入力されて消去開始信号Eraser Busyが活性化されることにより開始される。

#### 【0084】

第1段階S11は前記マルチチップパッケージのカウンタ130、230のアドレスを初期化する段階である。前記カウンタ130、230のアドレスはチップ情報とセクタ情4050

報を含む。

#### 【0085】

第2段階S12は前記カウンタ130、230のチップ情報と制御回路140、240のチップ情報が一致するか否かを判断する段階である。前記カウンタ130、230のチップ情報はアドレスの最上位ビットに保存される。前記制御回路140、240のチップ情報はヒューズまたはボンディングオプションになったフラグ信号である。チップ情報が一致しない場合には、第5段階S15に移動する。

#### 【0086】

第3段階S13は前記チップ情報が一致する場合に、前記カウンタ130、230のセクタ情報とレジスタ110、210のセクタ情報が一致するか否かを判断する段階である。セクタ情報が一致しない場合には、第5段階S15に移動する。

10

#### 【0087】

第4段階S14は前記セクタ情報が一致する場合にセクタ消去動作を実行する段階である。

#### 【0088】

第5段階S15は前記消去されたセクタが最後のセクタであるか否かを判断する段階である。最後のセクタであれば終了する。最後のセクタでない場合には、第6段階S16で前記カウンタ130、230のアドレスを増加する。

#### 【0089】

すべてのセクタに対する消去動作が終われば、消去終了信号Erase Finishが発生して消去動作が終わる。

20

#### 【0090】

以上で本発明の好ましい実施の形態を詳細に説明したが、本発明は、本発明の範囲から逸脱しない限度内で様々な変形が可能であることは勿論である。したがって、本発明の範囲は上述の実施の形態によって決まるものではなく、特許請求の範囲およびそれと均等なものなどによって決まらなければならない。

#### 【図面の簡単な説明】

#### 【0091】

【図1】単一チップでのマルチセクタ消去動作を説明するための概念図である。

【図2】単一チップでのマルチセクタ消去動作を説明するためのブロック図である。

30

【図3】単一チップでのマルチセクタ消去動作を説明するためのタイミング図である。

【図4】単一チップでのマルチセクタ消去動作を説明するための順序図である。

【図5】本発明によるマルチチップパッケージを示すブロック図である。

【図6】本発明によるマルチチップパッケージでのマルチセクタ消去動作を説明するための概念図である。

【図7】本発明による半導体メモリチップを示すブロック図である。

【図8】図5および図7のアドレスクロックドライバを示す回路図である。

【図9(A)】第1フラグ発生回路を示す回路図である。

【図9(B)】第2フラグ発生回路を示す回路図である。

【図10】本発明によるマルチチップパッケージでのマルチセクタ消去動作を説明するためのタイミング図である。

40

【図11】本発明によるマルチセクタ消去方法を説明するための順序図である。

#### 【符号の説明】

#### 【0092】

100, 200 半導体メモリチップ

110, 210 レジスタ

120, 220 アドレスクロックドライバ

130, 230 カウンタ

140, 240 制御回路

141, 142 フラグ発生回路

50

150, 250 コアドライバ

160, 260 セルアレイ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9(A)】

【図9(B)】

【図10】

【図11】

---

フロントページの続き

(72)発明者 任 興 淳

大韓民国京畿道龍仁市豊徳川2洞 サムスン5次アパート519棟904号

審査官 園田 康弘

(56)参考文献 特開平02-292798 (JP, A)

特開平11-120075 (JP, A)

特開2001-216787 (JP, A)

特開2003-007963 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 16 / 06

G 11 C 16 / 02