(11) Nummer: AT **394 461 B**

# **PATENTSCHRIFT**

(21) Anmeldenummer: 1297/88

(51) Int.Cl.<sup>5</sup> : **G06F** 11/18

(22) Anmeldetag: 18. 5.1988

(42) Beginn der Patentdauer: 15. 9.1991

(45) Ausgabetag: 10. 4.1992

(30) Priorität:

(12)

24. 6.1987 DE 3720879 beansprucht.

(56) Entgegenhaltungen:

DE-A1-3524647

(73) Patentinhaber:

SIEMENS AKTIENGESELLSCHAFT D-8000 MÜNCHEN (DE).

## (54) EINRICHTUNG ZUR FEHLERTOLERANTEN EIN/AUSGABE VON DATEN

(57) In einem Rechnersystem (Rl bis R3), bei dem die Daten über Parallel-/Serien-Wandler eingelesen und/oder über Serien/Parallel-Wandler (S/Pl bis S/P8) ausgelesen werden, ist vorgesehen, den Takt- und Steuereingängen dieser Wandler (m von n)-Majoritätsglieder (M101, M102, M103 bis M801, M802, M803) vorzuschalten, deren Eingänge an die betreffenden Takt- und Steuerausgänge aller Rechner des Rechnersystems angeschlossen sind. Die einzugebenden Daten werden allen Rechnern parallel zugeführt, während die auszugebenden Daten den seriellen Eingängen der Serien/Parallelwandler (SP1 bis SP/8) wiederum über (m von n) Majoritätsglieder (M104 bis M804) zugeführt werden; deren Eingänge sind an die entsprechenden Datenausgabeleitungen (D101, D201, D301 bis D108, D208, D308) der Rechner angeschlossen. Störungen durch Ausfall einzelner Majoritätsglieder oder Wandler (z.B. S/P1) bleiben auf die durch die Störung direkt betroffenen Bauelemente und die ihnen direkt zugeordneten Ein/Ausgabeeinrichtungen (T1 bis T8) beschränkt. Das System verkraftet auch den Ausfall eines Einzelrechners des Rechnersystems.

m

394 461

### AT 394 461 B

Die Erfindung bezieht sich auf eine Einrichtung zur fehlertoleranten Ein/Ausgabe von Daten in ein bzw. aus einem (m von n)-Rechnersystem unter Verwendung von Parallel/Serien- bzw. Serien/Parallel-Wandlern, deren Ein- bzw. Ausgänge jeweils an mehrere nacheinander abfragbare Ein- bzw. mehrere nacheinander mit Daten zu belegende Ausgabeeinrichtungen angeschlossen sind und deren serielle Aus- bzw. Eingänge über gesonderte Datenleitungen auf die Ein- bzw. Ausgänge von Registern geführt sind, die vom Rechnersystem byteweise gelesen bzw. beschrieben werden, wobei das Rechnersystem aus den byteweise nacheinander eingelesenen Daten bzw. den byteweise nacheinander zur Ausgabe anstehenden Daten jeweils die Transponierte bildet und die so umgesetzten Daten rechnerintern bewertet bzw. über die Serien/Parallel-Wandler an die Ausgabeeinrichtungen überträgt.

Aus der DE-OS 35 24 647 ist eine Einrichtung zur fehlertoleranten Ein/Ausgabe von Daten bekannt, bei der die Daten vor bzw. nach ihrer Übertragung an einen Rechner bzw. aus einem Rechner in Parallel/Serien-bzw. Serien/Parallel-Wandlern abgelegt sind. Diese Daten werden unter Steuerung eines Rechners in rechnerinterne Register eingeschrieben bzw. aus diesen ausgelesen und vor ihrer rechnerinternen Bewertung bzw. vor der Ausgabe an die Serien/Parallel-Wandler in definierter Weise so umgesetzt, daß der zuvor bzw. anschließend beim Einbzw. Ausgeben der Daten über die Register eintretende Datenumordnungsprozeß rückgängig gemacht bzw. aufgehoben wird. Der besondere Vorteil dieser bekannten Einrichtung liegt darin, daß die Adressierung der externen Ein/Ausgabeeinrichtungen zum Einlesen bzw. Ausgeben von Daten unterbleiben kann und daß diese Ein- und Ausgabeeinrichtungen bereichsweise durch Adressierung eines rechnerinternen Registers abgefragt bzw. mit Daten belegt werden können.

10

15

20

25

30

35

40

45

50

55

60

Aufgabe der vorliegenden Erfindung ist es, die bekannte Einrichtung zur fehlertoleranten Ein/Ausgabe von Daten an einem (m von n)-Rechnersystem zu betreiben. Dabei soll gewährleistet sein, daß etwaige Störungen, egal wo sie auftreten, in ihrer Auswirkung auf den Prozeß möglichst gering gehalten werden und nur zum Ausfall der durch die Störung direkt betroffenen Schaltmittel führen.

Die Erfindung löst diese Aufgabe dadurch, daß die zum Steuern der Wandler erforderlichen Takt- und Steuersignale den entsprechenen Takt- und Steuereingängen der einzelnen Wandler über vorgeschaltete (m von n)-Majoritätsglieder zugeführt werden, die eingangsseitig an die entsprechenden Takt- und Steuereingänge der Rechner angeschlossen sind, daß die Eingabe von Daten über die Parallel/Serien-Wandler mittels an die seriellen Ausgänge der einzelnen 7 Wandler angeschlossene n-Datenleitungen erfolgt, die an die Dateneingänge der Rechner ange-schlossen sind und/oder daß die Ausgabe von Daten an die Serien/Parallel-Wandler über den einzelnen Wandlern zugeordnete (m von n)-Majoritätsglieder erfolgt, die eingangsseitig an die Datenausgänge der Rechner angeschlos-sen sind.

Eine vorteilhafte Ausbildung der erfindungsgemäßen Einrichtung sieht vor, daß in die Verbindungsleitungen zwischen den Majoritätsgliedern und den Takt- und Steuerausgängen der Rechner sowie zwischen dem seriellen Ausgang der Parallel/Serienwandler und den Dateneingängen der Rechner und/oder zwischen den der Datenausgabe dienenden Majoritätsgliedern und den Rechnern Widerstände geschaltet sind.

Die dort angegebenen Mittel sorgen für eine ständige Entkopplung der Rechnerein- und Rechnerausgänge.

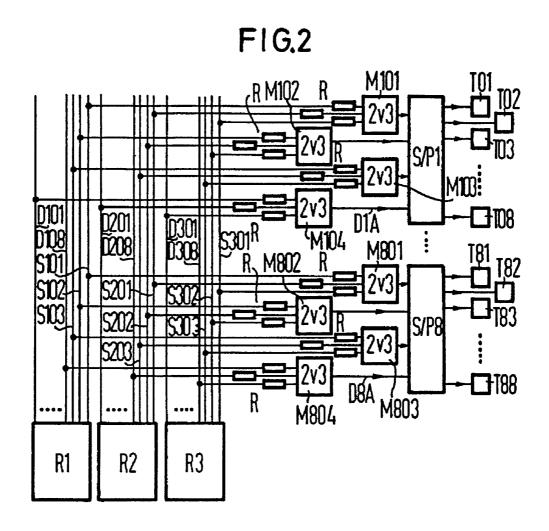

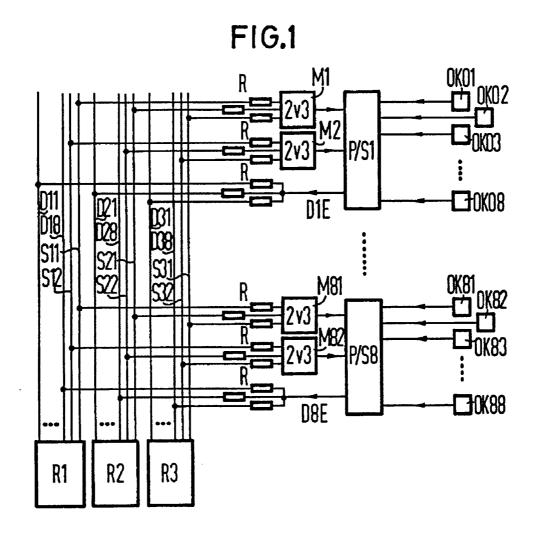

Die Erfindung ist nachstehend an Hand von in der Zeichnung dargestellten Ausführungsbeispielen näher erläutert. Fig. 1 zeigt schematisch den Aufbau der erfindungsgemäßen Einrichtung für die Dateneingabe und Fig. 2 die Ausbildung der erfindungsgemäßen Einrichtung für die Datenausgabe.

Das in Fig. 1 dargestellte (m von n)-Rechnersystem besteht aus drei Rechnern (R1 bis R3), die nach dem (2 von 3)-Prinzip arbeiten. An die Rechner angeschlossen sind Datenleitungen (D11 bis D18, D21 bis D28 und D31 bis D38) sowie je zwei Steuerleitungen (S11 und S12, S21 und S22 bzw. S31 und S32). Über die Datenleitungen werden die von Eingabeeinrichtungen anstehenden Daten, z. B. Meldungen über be-stimmte Schaltzustände in die Rechner eingelesen; die Steuerleitungen dienen zur Steuerung von Parallel/Serien-Wandlern (P/S1 bis P/S8), deren Eingängen die Daten zugeführt werden. Die Eingabeeinrichtungen sind als Optokoppler (OK01 bis OK88) ausgeführt. An die seriellen Ausgänge der Parallel/Serien-Wandler sind Daten-eingabeleitungen (D1E bis D8E) angeschlossen. Diese Dateneingabeleitungen verzweigen sich über die Datenleitungen (D11, D21 und D31 bzw. D18, D28 und D38) auf zugehörigen Dateneingänge der Rechner (R1 bis R3). Dort wird aus den übermittelten Daten in bekannter Weise die Transponierte abgeleitet und der rechnerinternen Bewertung der Daten zugeführt. In die Datenleitungen der (D11 bis D31 und D18 bis D38) sind Widerstände (R) geschaltet, die eine Entkopplung der Rechnereingänge bewirken.

Für die Steuerung der Parallel/Serien-Wandler werden zwei Takt- und Steuersignale benötigt. Diese werden jeweils an den einander entsprechenden Takt- und Steuerausgängen der Rechner abgegriffen und über die Steuerleitungen (S11, S21 und S31 bzw. S12, S22 und S32) den Parallel/Serien-Wandlern (P/S1 bis PS/8) zugeführt. Den entsprechenden Steuereingängen der Parallel/Serien-Wandler sind Majoritätsglieder (M1 und M2) vorgeschaltet, welche die Steuersignale einer (2 von 3)-Prüfung unterziehen.

So ist sichergestellt, daß die Steuerung der Parallel/Serien-Wandler jeweils vom Vorhandensein zweier übereinstimmender Steuersignale abhängig gemacht ist. In die Eingangskreise der Majoritätsglieder sind wiederum Widerstände (R) geschaltet, welche die Takt- und Steuerleitungen der Rechner entkoppeln.

In der Zeichnung nicht dargestellt sind die rechnerinternen Register zum Aufnehmen der von den Parallel/-Serienwandlern kommenden Eingabedaten sowie die Mittel zum Transponieren der Daten.

#### AT 394 461 B

Das Ausführungsbeispiel nach Fig. 2 bezieht sich auf die Ausgabe von Daten durch das Rechnersystem. Die Daten sollen Treibern (T01 bis T88) über vorgeschaltete Serien/Parallel-Wandler (S/P1 bis S/P8) zugeführt werden. Hiezu sind die Daten vom Rechnersystem her per Adresse auf die Datenleitungen (D101 bis D108, D201 bis D208 und D301 bis D308) zu legen. Diese Daten gelangen über Widerstände (R) auf zugehörige Majoritätsglieder (M104 bis M804) und von dort über Datenausgabeleitungen (D1A bis D8A) auf die seriellen Eingänge der Serien/Parallel-Wandler. Die Majoritätsglieder (M104 bis M804) stellen sicher, daß die Serien/Parallel-Wandler ausschließlich mit Daten belegt werden, die von einem funktionsfähigen Rechner-system stammen.

Für die Steuerung von Serien/Parallel-Wandlern werden drei Takt- und Steuersignale benötigt. Diese Signale werden von den Rechnern auf zugehörige Takt- und Steuerleitungen (S101 bis S103, S201 bis S203 und S301 bis S303) gelegt. Über diese Takt- und Steuerleitungen werden die von allen Rechnern kommenden Takt- und Steuersignale zugehörigen Majoritätsgliedern (M101 bis M103 bzw. M801 bis M803) zugeführt. Die Ausgänge dieser Majoritätsglieder sind an die zugehörigen Takt- und Steuersignage der Serien/Pa-rallel-Wandler angeschlossen. Die Verwendung von Majoritätsgliedern im Takt- und Steuerkreis der Serien/Paral-lel-Wandler hat den Zweck, diese Wandler nur dann für die Übertragung der Daten an die Ausgabeeinrichtungen zu aktivieren, wenn mindestens zwei der drei Rechner übereinstimmende Takt- und Steuersignale führen. Auch hier sind zur Entkopplung der Steuerleitungen in die Eingabekreise der Maioritätsglieder Widerstände geschaltet.

Fällt einer der Parallel/Serien- oder Serien/Parallel-Wandler aus, über die die Daten in das Rechnersystem eingegeben oder ausgegeben werden, so führt dies schlimmstenfalls zum Ausfall des von dieser Störung direkt betroffenen Wandlers; damit können dann aus dem von der Störung direkt betroffenen Bereich der zugehörigen Ein/Ausgabeeinrichtungen keine Daten mehr ein- bzw. ausgelesen werden. Die Ein/Ausgabeeinrichtungen, die über die übrigen Parallel/Serien- bzw. Serien/Parallel-Wandler abgefragt bzw. mit Daten versorgt werden, sind nach wie vor steuerbar, weil die eingetretene Störung auf den direkt betroffenen Wandler beschränkt ist. Das gleiche gilt für Störungen an einem der den Wandlern zugeordneten Majoritätsglieder. Bei Ausfall eines derartigen Majoritätsgliedes fällt der zugehörige Wandler für die Datenübertragung aus, während alle übrigen Wandler nach wie vor funktionsfähig sind. Kurzschlüsse im Eingang der Majoritätsglieder können sich wegen der in ihren Eingangskreis geschalteten Widerstände nicht auf das Funktionsverhalten anderer Majoritätsglieder auswirken, so daß auch hier die Störung beschränkt bleibt auf die an einen Wandler direkt angeschlossenen Ein- bzw. Ausgabeeinrichtungen,

#### **PATENTANSPRÜCHE**

40 1. Einrichtung zur fehlertoleranten Ein/Ausgabe von Daten in ein bzw. aus einem (m von n)-Rechnersystem unter Verwendung von Parallel/Serien- bzw. Serien/Parallel-Wandlern, deren Ein- bzw. Ausgänge jeweils an mehrere nacheinander abfragbare Ein- bzw. mehrere nacheinander mit Daten zu belegende Ausgabeeinrichtungen angeschlossen sind und deren serielle Aus- bzw. Eingänge über gesonderte Datenleitungen auf die Ein- bzw. Ausgänge von Registern geführt sind, die vom Rechnersystem byteweise gelesen bzw. beschrieben werden, 45 wobei das Rechnersystem aus den byteweise nacheinander eingelesenen Daten bzw. den byteweise nacheinander zur Ausgabe anstehenden Daten jeweils die Transponierte bildet und die so umgesetzten Daten rechnerintern bewertet bzw. über die Serien/Parallel-Wandler an die Ausgabeeinrichtungen überträgt, dadurch gekennzeichnet, daß die zum Steuern der Wandler (P/S1 bis P/S8, S/P1 bis S/P8) erforderlichen Takt- und Steuersignale den entsprechenen Takt- und Steuereingängen der einzelnen Wandler über vorgeschaltete (m von n)-Majoritätsglieder (M1, M2 bis M81, M82; M101, M102, M103 bis M801, M802, M803) zugeführt 50 werden, die eingangsseitig an die entsprechenden Takt- und Steuereingänge der Rechner (R1 bis R3) angeschlossen sind, daß die Eingabe von Daten über die Parallel/Serien-Wandler (P/S1 bis P/S8) mittels an die seriellen Ausgänge der einzelnen Wandler angeschlossene n-Datenleitungen (D1E bis D8E) erfolgt, die an die Dateneingänge der Rechner angeschlossen sind und/oder daß die Ausgabe von Daten an die Serien/Parallel-Wandler (S/P1 bis S/P8) über den einzelnen Wandlern zugeordnete (m von n)-Majoritätsglieder (M104 bis 55 M804) erfolgt, die eingangsseitig an die Datenausgänge der Rechner angeschlossen sind.

10

15

20

25

30

35

# AT 394 461 B

2. Einrichtung nach Anspruch 1, dadurch gekennzeichnet, daß in die Verbindungsleitungen zwischen den Majoritätsgliedern (M1, M2 bis M81, M82; M101, M102, M103 bis M801, M802, M803) und den Takt- und Steuerausgängen der Rechner (R1 bis R3) sowie zwischen dem seriellen Ausgang der Parallel/Serienwandler (P/S1 bis P/S8) und den Dateneingängen der Rechner und/oder zwischen den der Datenausgabe dienenden Majoritätsgliedern (M104 bis M804) und den Rechnern Widerstände (R) geschaltet sind.

5

10

Hiezu 2 Blatt Zeichnungen

Ausgegeben

10.4.1992

Int. Cl.5: G06F 11/18

Blatt 1

Ausgegeben

10.4.1992

Int. Cl.5: G06F 11/18

Blatt 2